Page 1

5

Vinafix.com

4

3

2

1

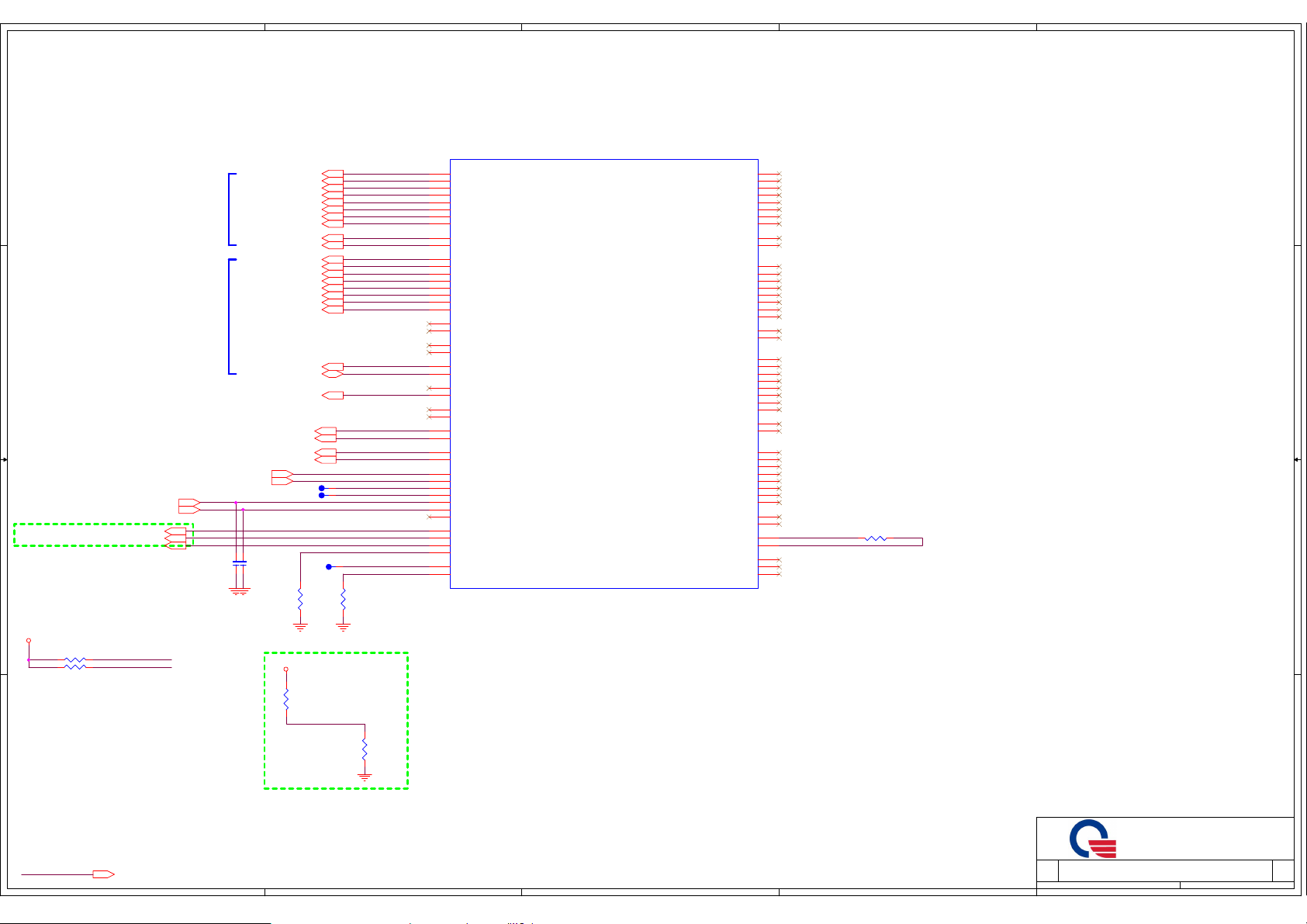

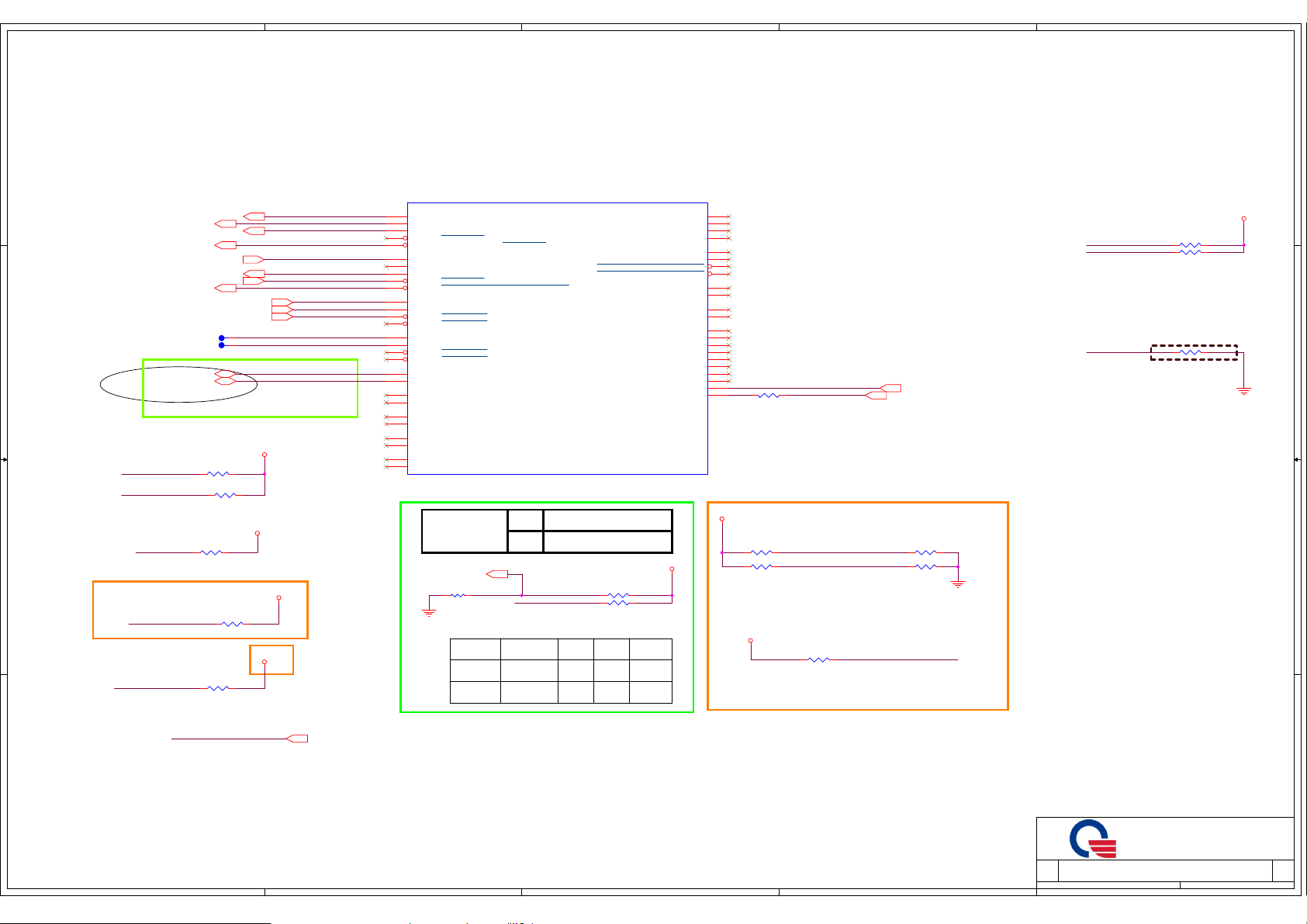

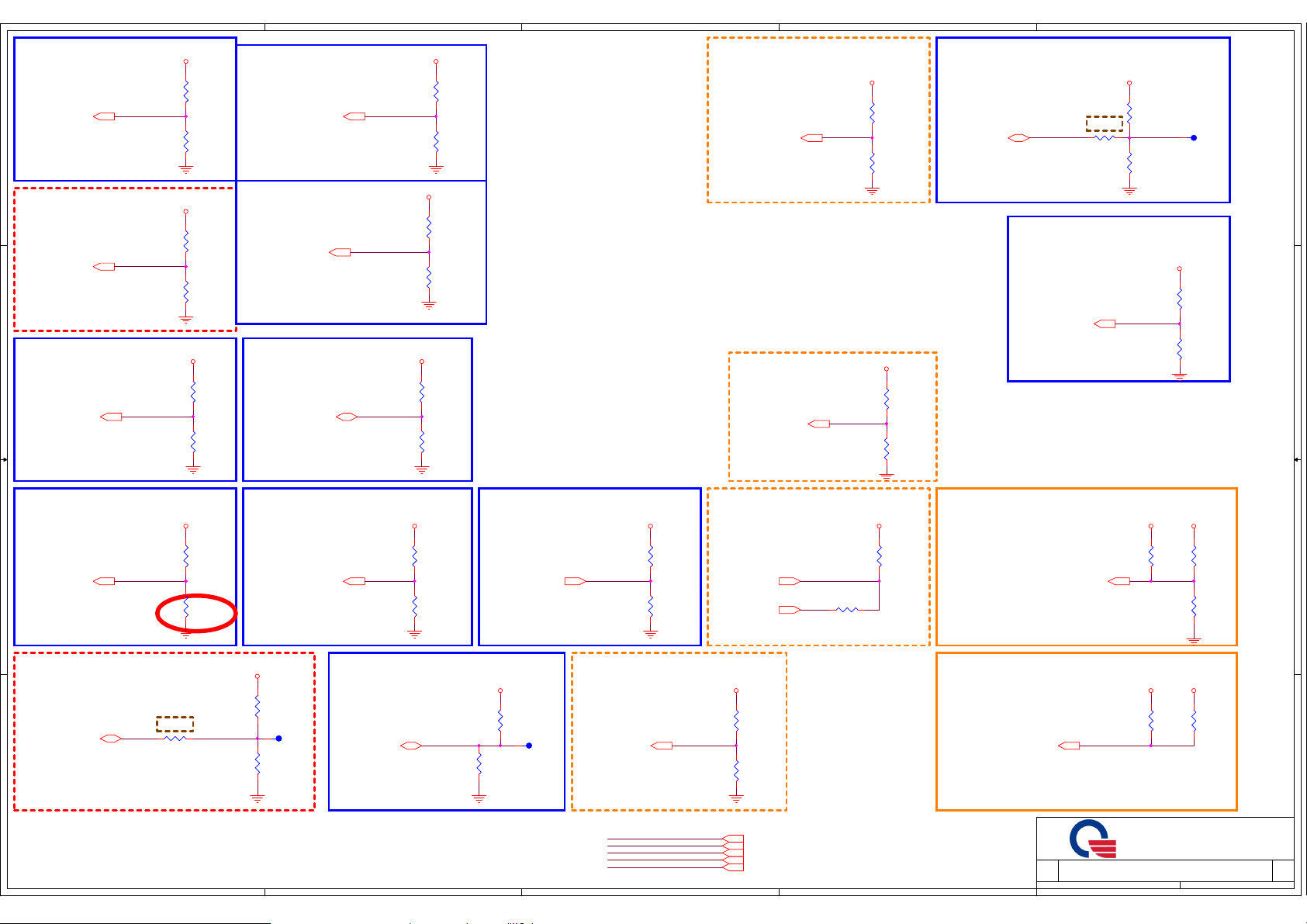

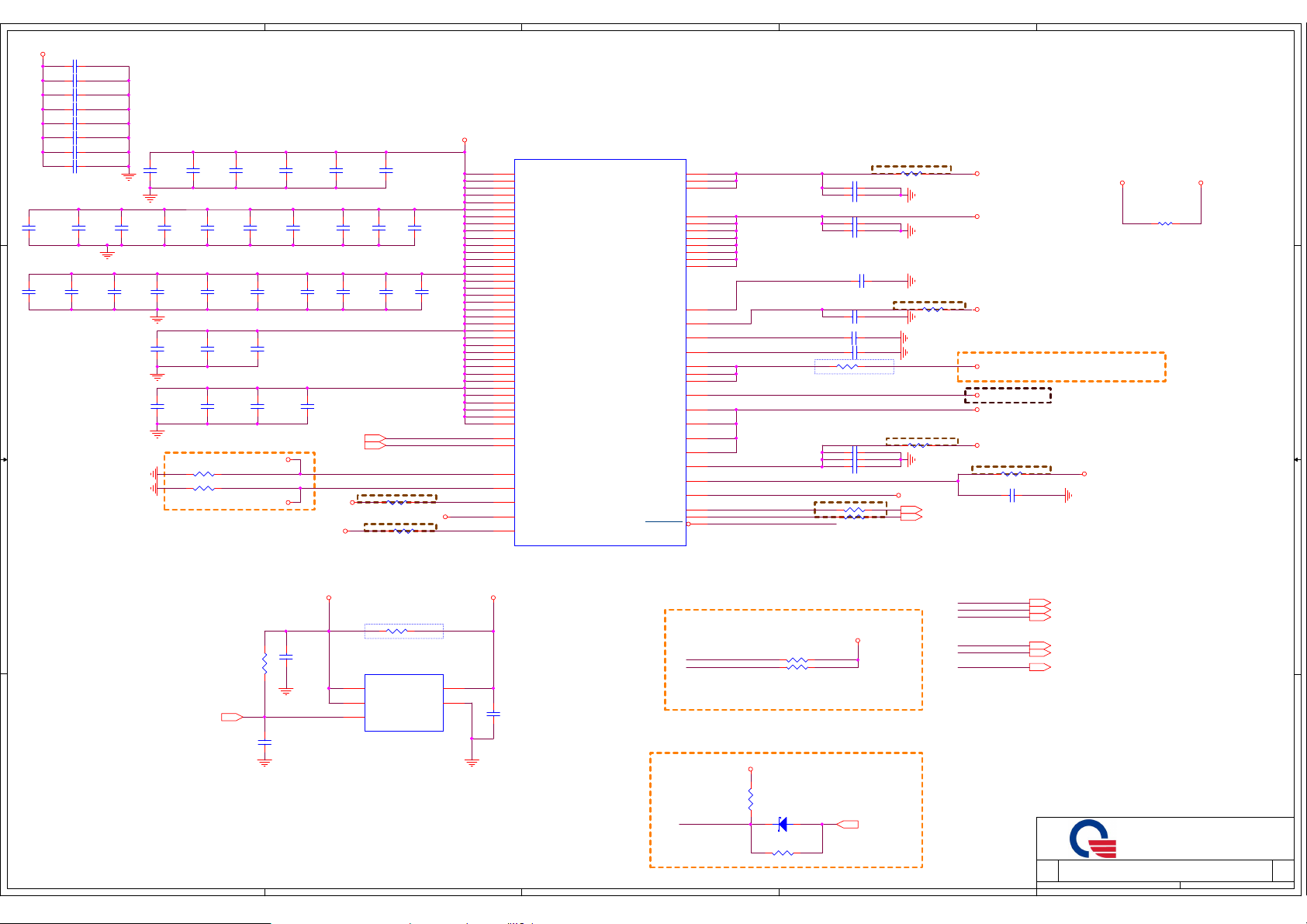

01ZAUI ICE lake series Platform Block Diagram (DIS/UMA )

D D

DDR4-Memory Down

CH. B CH. A

SATA0

SATA - HDD

Re-Driver

SN75LVCP601RTJR

P32

P32

SATA - ODD

(Reserve)

DDR4 24000/2666/3200 MT/s

DDR4-SoDIMM

P18

SATA1A

SSD

SATA/PCIe-SSD

P32

P17

SATA2/SATA1B

P33

PCIE 9~12

PCIE 5

P28

POA

(Reserve)

USB7

P31

LAN

25MHz

C C

RTL8111HSH-CG

RJ45

P28

PCIE 6

Wifi / BT

P33

USB2 4

M/B Type-C

P29

USB2 2 USB2 1

CCD

DMIC

P25

B B

BOM option

IV@ : UMA

EV@ : DIS

TPC@ : Type-C function

TPC_N@ :No Type-C function

TSI@ : Touch screen I2C

TPM@ : Trusted Platform Module

PBA@ : Finger Print on touch pad

KBL@ : Keyboard back light

GS@ : G-Sensor function

GS_N@ : No G-Sensor function

SSD@ : Solid State Disk

ODD@ : Optical Disc Drive

EMC@ : eMMC function

RAM@ : On Board Memory

SP@ : Power & VGA

HDD_R@ : Hard Disc Redriver

HDD_N@ : NO Hard Disc Redriver

CNV@ : Intel WIFI

CNV_N@ :NO Intel WIFI

A A

HDMI_R@ : HDMI Redirver

HDMI_N@ : No HDMI Redirver

Debug@ : for Debug Card

255@ : Codec 255

256@ : Codec 256

FOR15_17@ : Panel 15 or 17 inch

FOR14@ : Panel 14 inch

5

Power solution

Batery Charger

+3VPCU/+5VPCU

RT6258CGQUF

+3V/+5V

JW7110DFNC

+1V_S5

G5335QT2U

+1.2VSUS

RT8231BGQW

G9661MF11U

P37BQ24780SRUYR

P38

P38

P39

P40

4

USB3 3

MUX

PI2EQX632EXUBE

P29

USB2 5USB2 6

Touch Screen

P25P25

Daughter Board

+VCCIN_AUX

RT9610CGQW P42

+VCCIN_and

RT9610CGQW

+VCCSA

RT9610CGQW

+1.8V_S5

JW5213DFND

+1.5V

JW5222RSOTB

UB3/MB Port2

CR

(Reserve)

LED

P35

Speaker

+VGPU_CORE

RT8813DGQW P46

+1.35V_GFX

P43

G5335QT2U P47

+1V8_AON

P43

JW7110DFNC

+1.03_GFX

G9336ADJTP1U

P44

Thermal protection

P44

TMP708AIDBVR P44

USB3 2

P24

USB2 3

USB8

P35

D/B Head Phone

26

USB3 1

UB3/MB Port1

USB2 9

D/B USB 2.0

Audio Codec

ALC255-CG

Co-Lay 2566

P48

P48

P24

P35

P35

P26P

ICL U4+2

DDR

SATA

PCI-e

USB 3.0

USB 2.0

Processor : Daul Core

Power : 15 (Watt)

MCP 1526pins

Size : 50 X 25 (mm)

Integrated PCH

HDA

3

PCI-e

DDI

eDP

eDP

ESPI Interface

I2C

SPI

PCIE 1~4

HDMI 1.4 4K2K

PTN3366BS

LCD Panel

2 Lane for 4K2K

Battery

P13

32.768kHz

38.4MHz

TPM

NPCT750AAAYX

(Reserve)

Touch Pad

G-sensor

SPI ROM

PCB 8L STACK UP

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1

LAYER 4 : SVCC

LAYER 5 : IN2

LAYER 6 : IN3

LAYER 7 : SGND

LAYER 8 : BOT

2

GPU

N17S-G0/G2/G5 GDDR5 x32*2pcs

P19-22

HDMI

P27

P25

38.4MHz

U42 Reserve

P27

(Reserve)

VRAM

27MHz

FAN

P31

Embedded Controller

P31

P31

P10

IT5571

Keyboard BL

Keyboard

Hall Sensor

P34

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

P23

P30

P30

P30

P35

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

ZAUI

ZAUI

ZAUI

1 47Monday, November 04, 2019

1 47Monday, November 04, 2019

1 47Monday, November 04, 2019

3A

3A

3A

Page 2

5

Vinafix.com

4

3

2

1

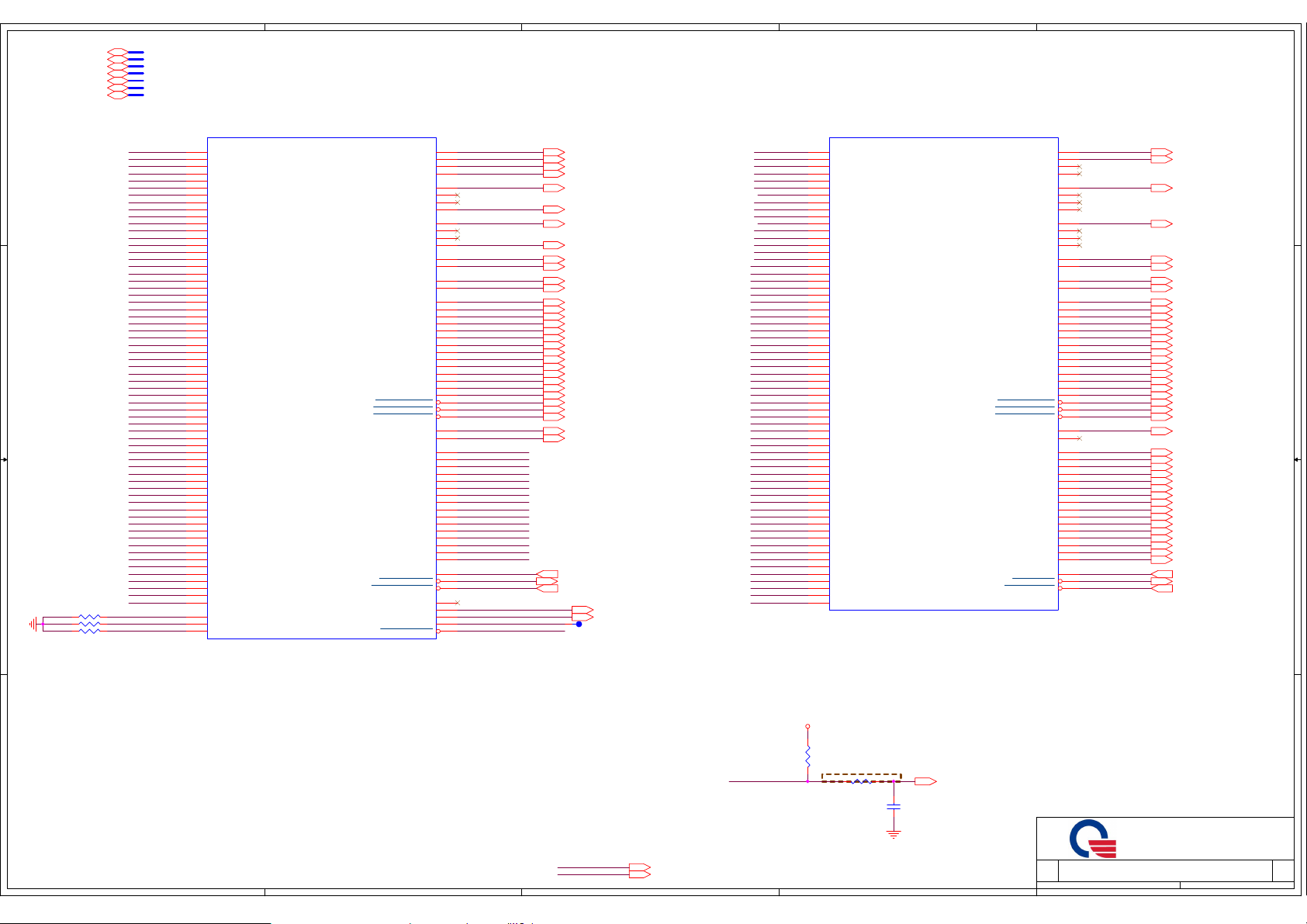

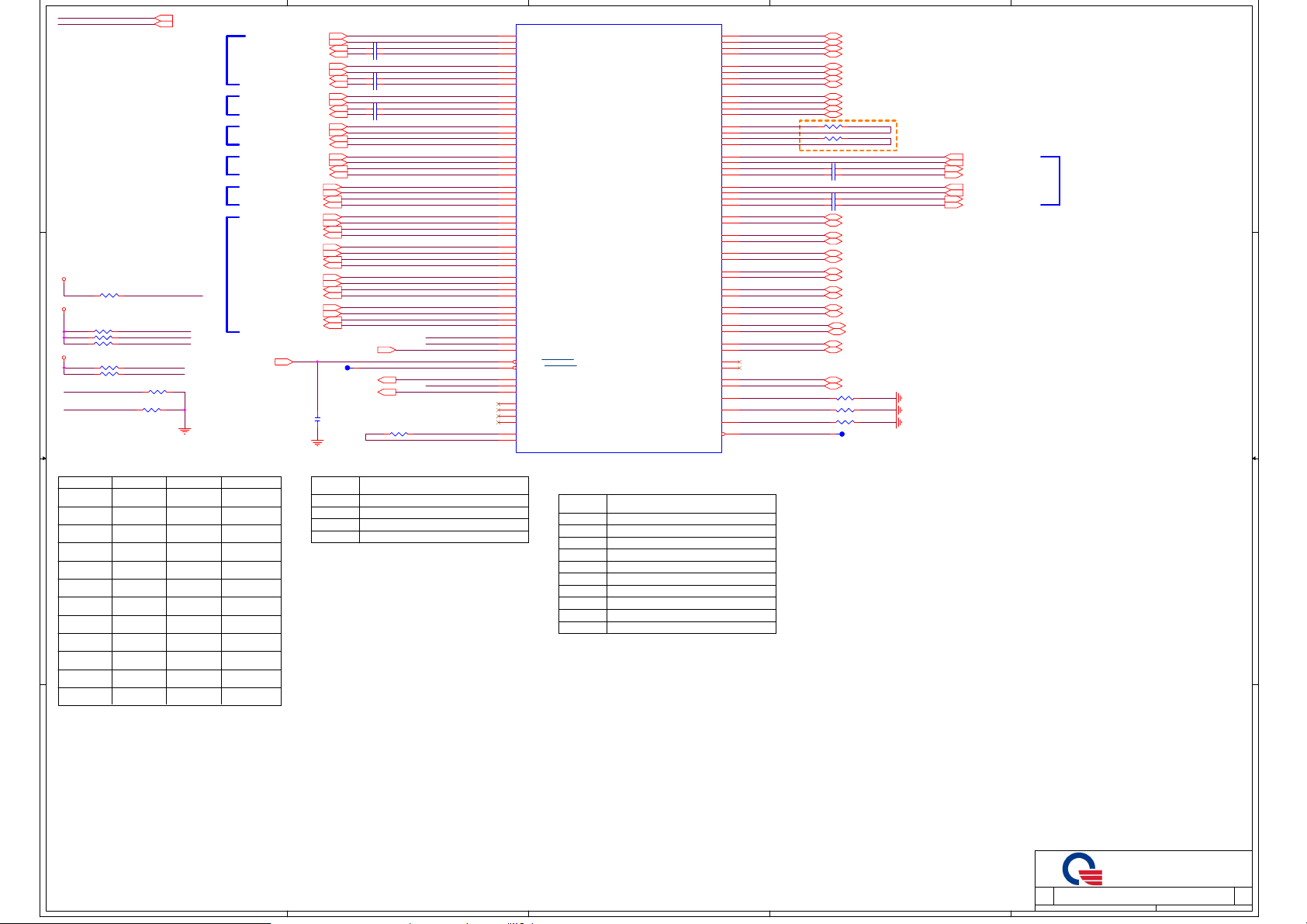

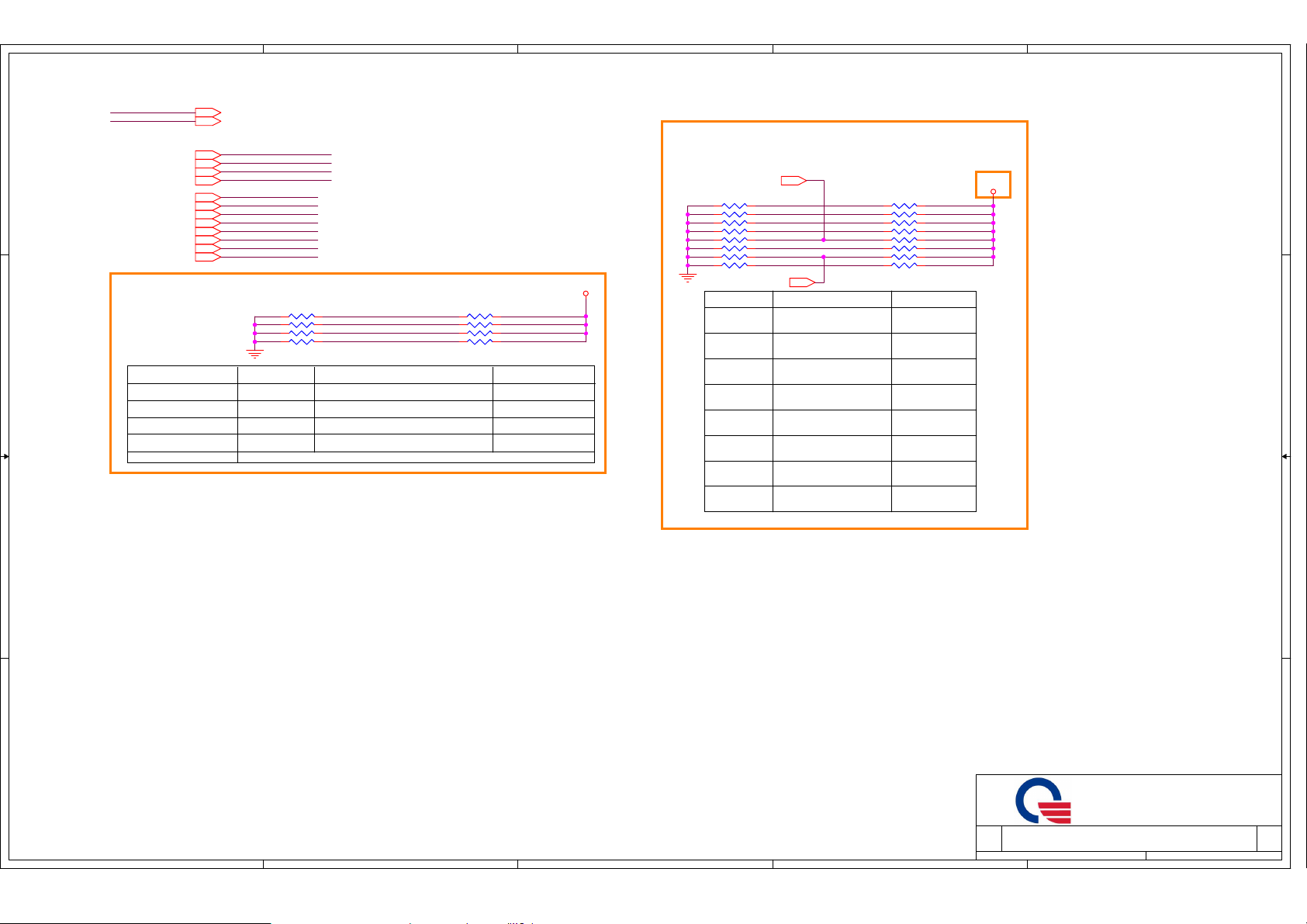

02

D D

INT_EDP_TXN025

INT_EDP_TXP025

INT_EDP_TXN125

INT_EDP_TXP125

INT_EDP_TXN225

RAM_ID015

RAM_ID115

RAM_ID215

RAM_ID315

PCH_DISP_ON

PCH_LVDS_BLON

PCH_DPST_PWM

0.1u/16V_2C344

0.1u/16V_2C329

INT_EDP_TXP225

INT_EDP_TXN325

INT_EDP_TXP325

INT_EDP_AUXN25

INT_EDP_AUXP25

SDVO_CLK27

SDVO_DATA27

GPP_E1910

R593

100K_1%_2

IN_D2#27

IN_D227

IN_D1#27

IN_D127

IN_D0#27

IN_D027

IN_CLK#27

IN_CLK27

@

TP26

@

TP28

@

TP64

eDP

HDMI

C C

ULT_EDP_HPD25

HDMI_HPD_CON27

USB_OC1#24

USB_OC2#35

PCH_DISP_ON25

PCH_LVDS_BLON25

DG : 330 nF or 100k

B B

PCH_DPST_PWM25

INT_EDP_TXN0

INT_EDP_TXP0

INT_EDP_TXN1

INT_EDP_TXP1

INT_EDP_TXN2

INT_EDP_TXP2

INT_EDP_TXN3

INT_EDP_TXP3

INT_EDP_AUXN

INT_EDP_AUXP

IN_D2#

IN_D2

IN_D1#

IN_D1

IN_D0#

IN_D0

IN_CLK#

IN_CLK

ULT_EDP_HPD

HDMI_HPD_CON

TBTA_HPD

TBTB_HPD

USB_OC1#

USB_OC2#

DSI_DE_TE_2

DISP_UTILS

DP_RCOMP

R610

150_1%_2

RAM_ID0

RAM_ID1

RAM_ID2

RAM_ID3

U24A

Y5

DDIA_TXN_0

Y3

DDIA_TXP_0

Y1

DDIA_TXN_1

Y2

DDIA_TXP_1

V2

DDIA_TXN_2

V1

DDIA_TXP_2

V3

DDIA_TXN_3

V5

DDIA_TXP_3

W4

DDIA_AUX_N

W3

DDIA_AUX_P

AE3

DDIB_TXN_0

AE5

DDIB_TXP_0

AE2

DDIB_TXN_1

AE1

DDIB_TXP_1

AC5

DDIB_TXN_2

AC3

DDIB_TXP_2

AC1

DDIB_TXN_3

AC2

DDIB_TXP_3

AD3

DDIB_AUX_N

AD4

DDIB_AUX_P

DP15

GPP_E22/DDPA_CTRL CLK/PCIE_LNK_DOWN

DJ17

GPP_E23/DDPA_CTRL DATA/BK4/SBK4

DL40

GPP_H16/DDPB_CTR LCLK

DP42

GPP_H17/DDPB_CTR LDATA

DL17

GPP_E18/DDP1_CTRLC LK/TBT_LSX0_TXD

DK17

GPP_E19/DDP1_CTRLD ATA/TBT_LSX0_RXD

DN17

GPP_E20/DDP2_CTRLC LK/TBT_LSX1_TXD

DP17

GPP_E21/DDP2_CTRLD ATA/TBT_LSX1_RXD

DK34

GPP_D9/ISH_SPI_CS_N/D DP3_CTRLCLK/GSPI2_CS0_N/TBT_LSX2_TX D

DL34

GPP_D10/ISH_SPI_CLK/DD P3_CTRLDATA/GSPI2_CLK/TBT_LSX2_RXD

DN33

GPP_D11/ISH_SPI_MISO/D DP4_CTRLCLK/GSPI2_MISO/TBT_LSX3_TXD

DL33

GPP_D12/ISH_SPI_MOSI/D DP4_CTRLDATA/GSPI2_MOSI/TBT_LSX3_RX D

DW11

GPP_E14/DPPE_HPDA /DISP_MISCA

CV42

GPP_A18/DDSP_HPD B/DISP_MISCB

CV39

GPP_A19/DDSP_HPD 1/DISP_MISC1

CY43

GPP_A20/DDSP_HPD 2/DISP_MISC2

CR41

GPP_A14/USB_OC1_N /DDSP_HPD3/DISP_MISC3

CT41

GPP_A15/USB_OC2_N /DDSP_HPD4/DISP_MISC4

DV14

GPP_E17

DN21

EDP_VDDEN

DL19

EDP_BKLTEN

DU19

EDP_BKLTCTL

J3

RSVD_1

D2

DISP_UTILS

R2

DISP_RCOMP

ICL-U 1.2G QPWA

CPU@

1 0f 19

TCP0_TX_N0

TCP0_TX_P0

TCP0_TX_N1

TCP0_TX_P1

TCP0_TXRX_N0

TCP0_TXRX_P0

TCP0_TXRX_N1

TCP0_TXRX_P1

TCP0_AUX_N

TCP0_AUX_P

TCP1_TX_N0

TCP1_TX_P0

TCP1_TX_N1

TCP1_TX_P1

TCP1_TXRX_N0

TCP1_TXRX_P0

TCP1_TXRX_N1

TCP1_TXRX_P1

TCP1_AUX_N

TCP1_AUX_P

TCP2_TX_N0

TCP2_TX_P0

TCP2_TX_N1

TCP2_TX_P1

TCP2_TXRX_N0

TCP2_TXRX_P0

TCP2_TXRX_N1

TCP2_TXRX_P1

TCP2_AUX_N

TCP2_AUX_P

TCP3_TX_N0

TCP3_TX_P0

TCP3_TX_N1

TCP3_TX_P1

TCP3_TXRX_N0

TCP3_TXRX_P0

TCP3_TXRX_N1

TCP3_TXRX_P1

TCP3_AUX_N

TCP3_AUX_P

TC_RCOMP_N

TC_RCOMP_P

GPP_A17/DISP_MISCC

GPP_A21

GPP_A22

BB5

BB6

AV6

AV5

BH2

BH1

BF1

BF2

AY5

AY6

AR5

AR6

AL5

AL3

BD2

BD1

BB1

BB2

AN3

AN5

BF6

BF5

BJ5

BJ6

BL1

BL2

BM2

BM1

BG6

BG5

BP6

BP5

BV5

BV6

BR1

BR2

BT2

BT1

BT6

BT5

AY1

AY2

CT38

CV43

CV41

TCRCOMP_DN

TCRCOMP_DP

R617 150_1%_2

+3V_S5

R678 10K_5%_2

R276 10K_5%_2

A A

USB_OC1#

USB_OC2#

+3V_S5 6,8,10,11,13,14,15,16,28,29,30,33,34,37,40,41

5

+3V

R327

*10K_1%_2

ULT_EDP_HPD

R343

100K_5%_4

4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ICL-U 1/14 (DDI/TBT/eDP)

ICL-U 1/14 (DDI/TBT/eDP)

ICL-U 1/14 (DDI/TBT/eDP)

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

PROJECT :

ZAUI

ZAUI

ZAUI

3A

3A

2 47Monday, November 04, 2019

2 47Monday, November 04, 2019

1

2 47Monday, November 04, 2019

3A

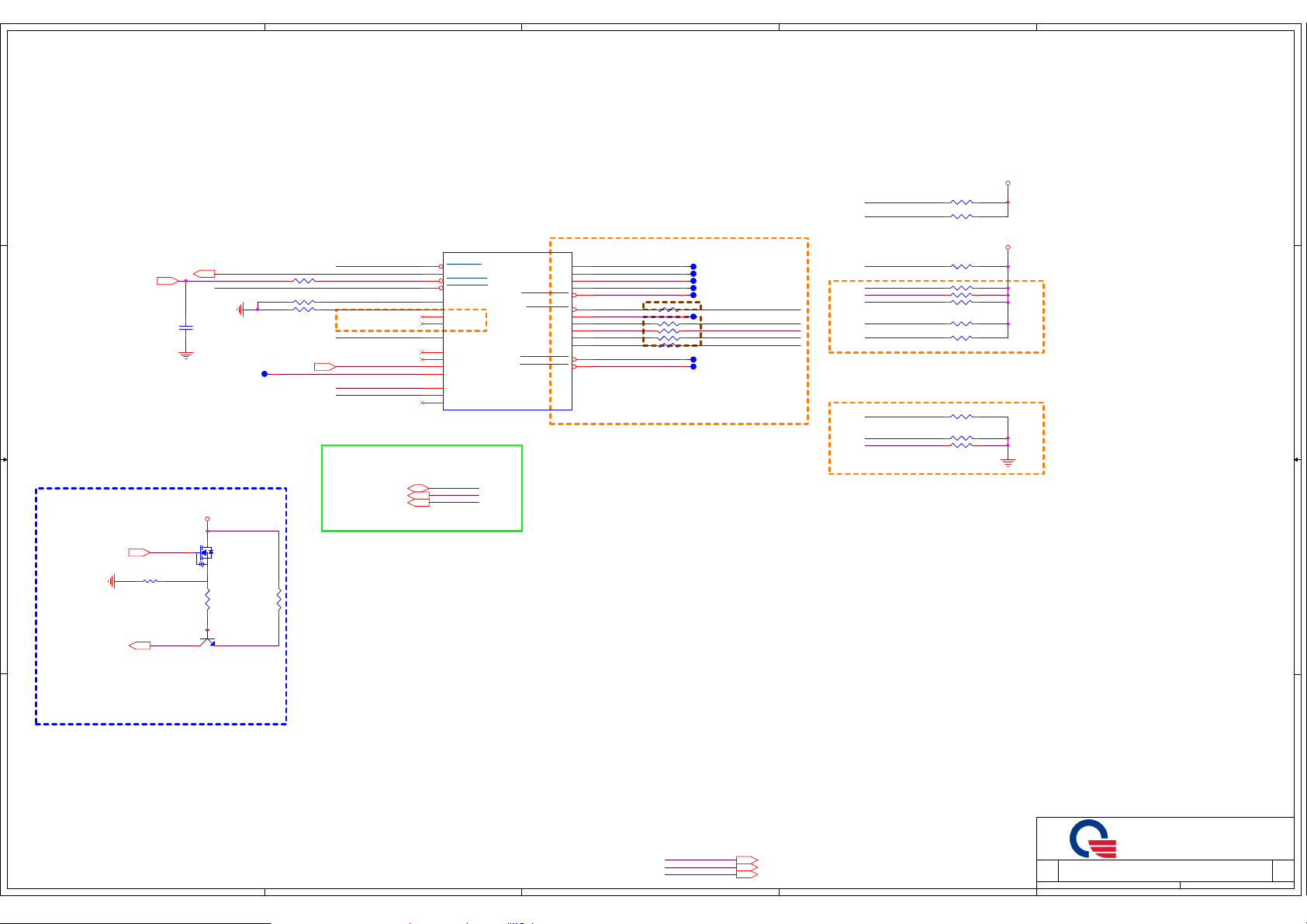

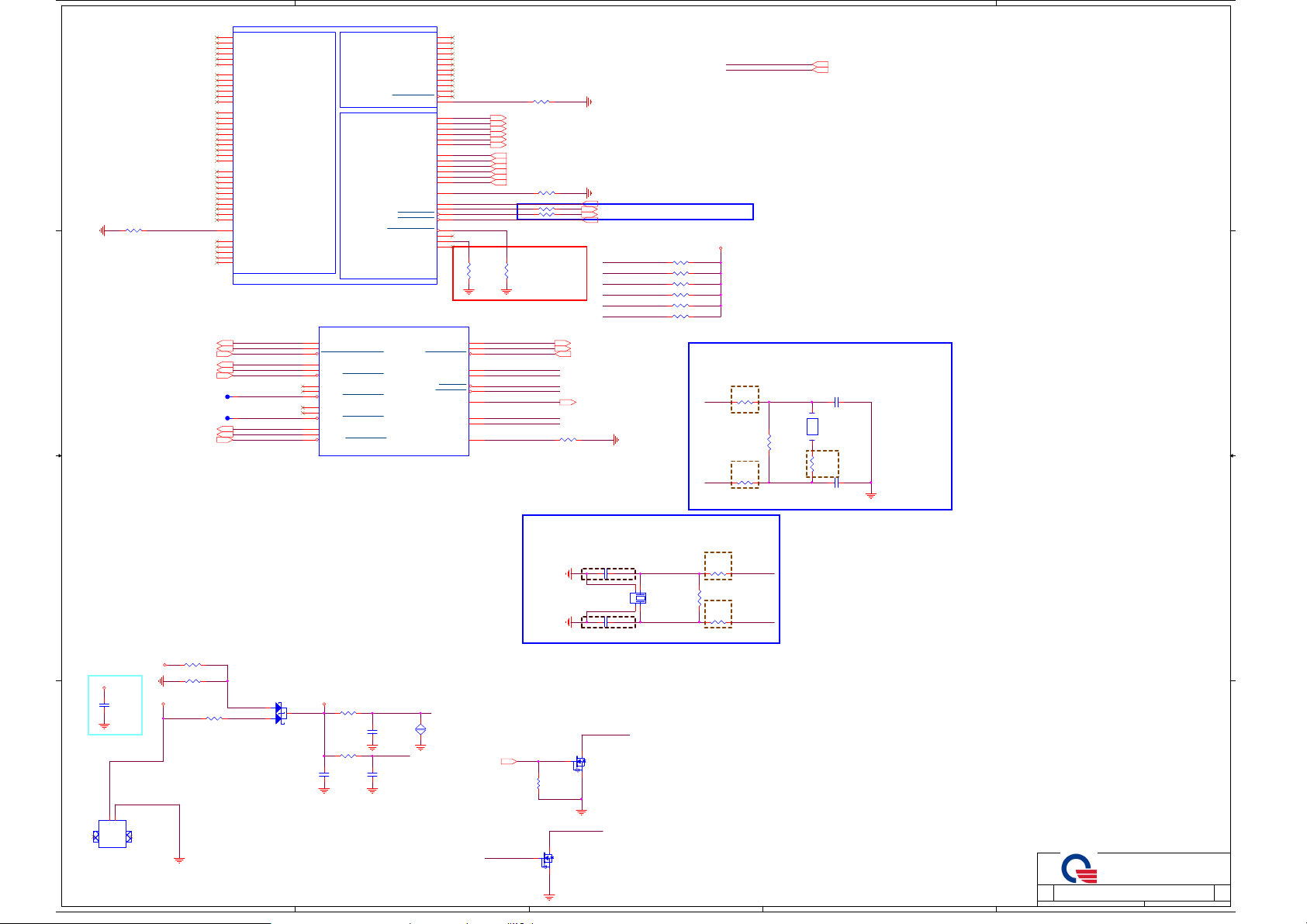

Page 3

5

Vinafix.com

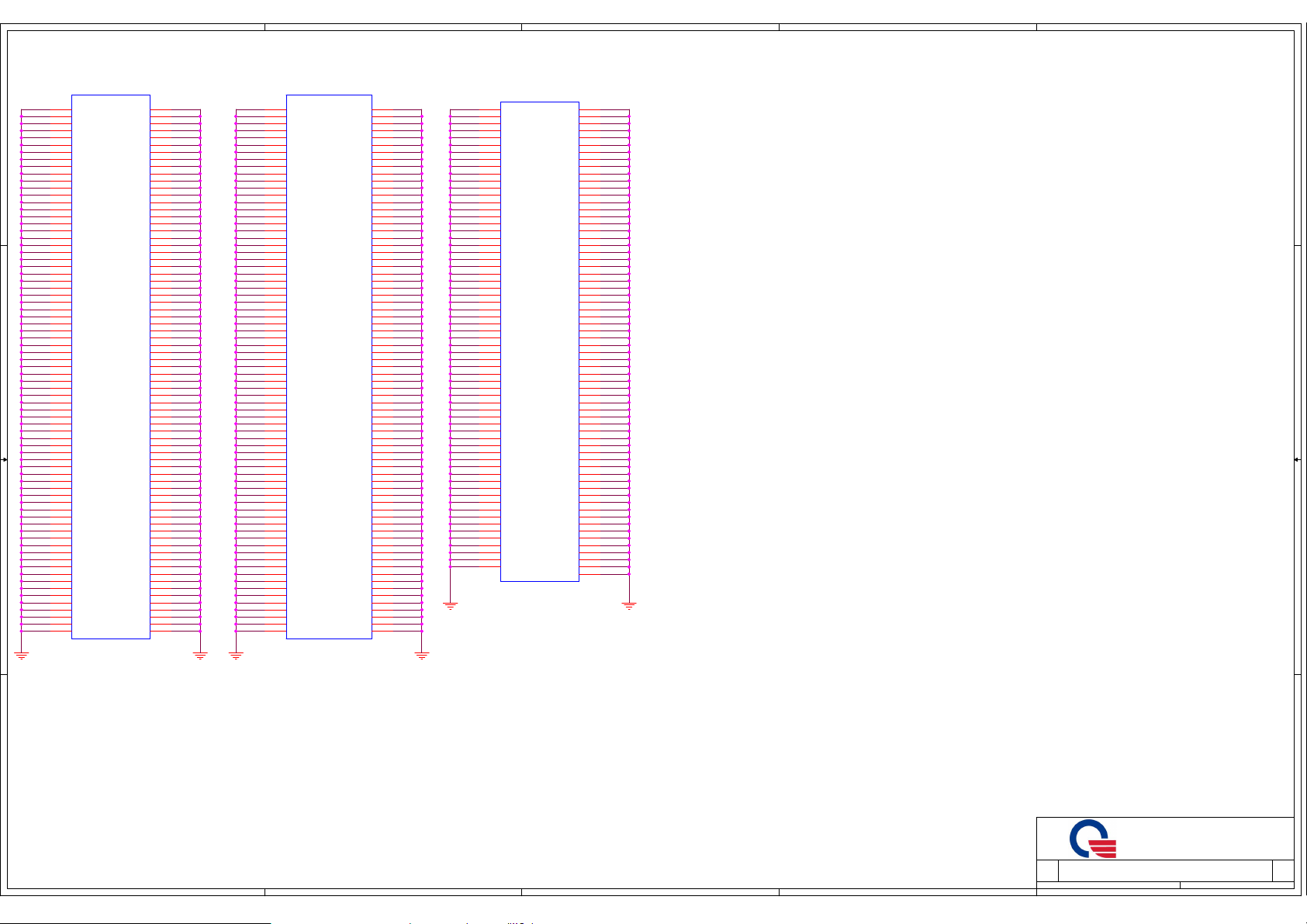

M_A_DQSN[7:0]17

M_A_DQSP[7:0]17

M_B_DQSN[7:0]3,18

M_B_DQSP[7:0]3,18

M_A_DQ[63:0]17

M_B_DQ[63:0]3,18

M_B_DQ[63:0]3,18

DDR CHANNEL A/B DDR CHANNEL C/D

D D

C C

B B

R576 100_1%_2

R575 100_1%_2

R577 100_1%_2

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

U24B

CA48

DDRA_DQ0_0/DDR0_D Q0_0

CA47

DDRA_DQ0_1/DDR0_D Q0_1

CA49

DDRA_DQ0_2/DDR0_D Q0_2

BV49

DDRA_DQ0_3/DDR0_D Q0_3

CA45

DDRA_DQ0_4/DDR0_D Q0_4

BV47

DDRA_DQ0_5/DDR0_D Q0_5

BV45

DDRA_DQ0_6/DDR0_D Q0_6

BV48

DDRA_DQ0_7/DDR0_D Q0_7

CC42

DDRA_DQ1_0/DDR0_D Q1_0

CC39

DDRA_DQ1_1/DDR0_D Q1_1

CC43

DDRA_DQ1_2/DDR0_D Q1_2

CE38

DDRA_DQ1_3/DDR0_D Q1_3

CC38

DDRA_DQ1_4/DDR0_D Q1_4

CE39

DDRA_DQ1_5/DDR0_D Q1_5

CE42

DDRA_DQ1_6/DDR0_D Q1_6

CE43

DDRA_DQ1_7/DDR0_D Q1_7

BT48

DDRA_DQ2_0/DDR0_D Q2_0

BT47

DDRA_DQ2_1/DDR0_D Q2_1

BT49

DDRA_DQ2_2/DDR0_D Q2_2

BN49

DDRA_DQ2_3/DDR0_D Q2_3

BT45

DDRA_DQ2_4/DDR0_D Q2_4

BN47

DDRA_DQ2_5/DDR0_D Q2_5

BN45

DDRA_DQ2_6/DDR0_D Q2_6

BN48

DDRA_DQ2_7/DDR0_D Q2_7

BV42

DDRA_DQ3_0/DDR0_D Q3_0

BV39

DDRA_DQ3_1/DDR0_D Q3_1

BV43

DDRA_DQ3_2/DDR0_D Q3_2

BW38

DDRA_DQ3_3/DDR0_D Q3_3

BV38

DDRA_DQ3_4/DDR0_D Q3_4

BW39

DDRA_DQ3_5/DDR0_D Q3_5

BW42

DDRA_DQ3_6/DDR0_D Q3_6

BW43

DDRA_DQ3_7/DDR0_D Q3_7

AY48

DDRB_DQ0_0/DDR0_D Q4_0

AY47

DDRB_DQ0_1/DDR0_D Q4_1

AY49

DDRB_DQ0_2/DDR0_D Q4_2

AU45

DDRB_DQ0_3/DDR0_D Q4_3

AY45

DDRB_DQ0_4/DDR0_D Q4_4

AU47

DDRB_DQ0_5/DDR0_D Q4_5

AU48

DDRB_DQ0_6/DDR0_D Q4_6

AU49

DDRB_DQ0_7/DDR0_D Q4_7

AY42

DDRB_DQ1_0/DDR0_D Q5_0

AY38

DDRB_DQ1_1/DDR0_D Q5_1

AY43

DDRB_DQ1_2/DDR0_D Q5_2

BB39

DDRB_DQ1_3/DDR0_D Q5_3

AY39

DDRB_DQ1_4/DDR0_D Q5_4

BB38

DDRB_DQ1_5/DDR0_D Q5_5

BB42

DDRB_DQ1_6/DDR0_D Q5_6

BB43

DDRB_DQ1_7/DDR0_D Q5_7

AR48

DDRB_DQ2_0/DDR0_D Q6_0

AR47

DDRB_DQ2_1/DDR0_D Q6_1

AR49

DDRB_DQ2_2/DDR0_D Q6_2

AM45

DDRB_DQ2_3/DDR0_D Q6_3

AR45

DDRB_DQ2_4/DDR0_D Q6_4

AM47

DDRB_DQ2_5/DDR0_D Q6_5

AM48

DDRB_DQ2_6/DDR0_D Q6_6

AM49

DDRB_DQ2_7/DDR0_D Q6_7

AT42

DDRB_DQ3_0/DDR0_D Q7_0

AT39

DDRB_DQ3_1/DDR0_D Q7_1

AR43

DDRB_DQ3_2/DDR0_D Q7_2

AT38

DDRB_DQ3_3/DDR0_D Q7_3

AR38

DDRB_DQ3_4/DDR0_D Q7_4

AR39

DDRB_DQ3_5/DDR0_D Q7_5

AR42

DDRB_DQ3_6/DDR0_D Q7_6

AT43

DDRB_DQ3_7/DDR0_D Q7_7

D47

DDR_RCOMP_0

E46

DDR_RCOMP_1

C47

DDR_RCOMP_2

ICL-U 1.2G QPWA

CPU@

DDRA_CLK_N/DDR0_ CLK_N_0

DDRA_CLK_P/DDR0_C LK_P_0

DDRB_CLK_N/DDR0_ CLK_N_1

DDRB_CLK_P/DDR0_C LK_P_1

DDRB_CA2/DDR0_M A14WE_N

DDRB_CA1/DDR0_M A15CAS_N

DDRB_CA3/DDR0_M A16RAS_N

DDRA_DQSN_0/DDR 0_DQSN_0

DDRA_DQSP_0/DDR 0_DQSP_0

DDRA_DQSN_1/DDR 0_DQSN_1

DDRA_DQSP_1/DDR 0_DQSP_1

DDRA_DQSN_2/DDR 0_DQSN_2

DDRA_DQSP_2/DDR 0_DQSP_2

DDRA_DQSN_3/DDR 0_DQSN_3

DDRA_DQSP_3/DDR 0_DQSP_3

DDRB_DQSN_0/DDR 0_DQSN_4

DDRB_DQSP_0/DDR 0_DQSP_4

DDRB_DQSN_1/DDR 0_DQSN_5

DDRB_DQSP_1/DDR 0_DQSP_5

DDRB_DQSN_2/DDR 0_DQSN_6

DDRB_DQSP_2/DDR 0_DQSP_6

DDRB_DQSN_3/DDR 0_DQSN_7

DDRB_DQSP_3/DDR 0_DQSP_7

2 of 19

4

DDRA_CKE0/DDR0_C KE0

DDRA_CKE1/NC

DDRB_CKE0/NC

DDRB_CKE1/DDR0_C KE1

DDRA_CS_0/DDR0_C S_N_0

DDRA_CS_1/NC

DDRB_CS_0/NC

DDRB_CS_1/DDR0_C S_N_1

DDRB_CA4/DDR0_BA 0

NC/DDR0_BA1

DDRA_CA5/DDR0_BG 0

NC/DDR0_BG1

NC/DDR0_MA0

NC/DDR0_MA1

DDRB_CA5/DDR0_M A2

NC/DDR0_MA3

NC/DDR0_MA4

DDRA_CA0/DDR0_M A5

DDRA_CA2/DDR0_M A6

DDRA_CA4/DDR0_M A7

DDRA_CA3/DDR0_M A8

DDRA_CA1/DDR0_M A9

NC/DDR0_MA10

NC/DDR0_MA11

NC/DDR0_MA12

DDRB_CA0/DDR0_M A13

NC/DDR0_ODT_0

NC/DDR0_ODT_1

NC/DDR0_PAR

NC/DDR0_ACT_N

NC/DDR0_ALERT_N

RSVD_73

DDR0_VREF_CA

DDR1_VREF_CA

DDR_VTT_CTL

DRAM_RESET_N

BL48

BL47

BF42

BF43

BG49

BJ47

BF38

BF41

BM38

BM42

BP42

BG42

BM43

BG39

BB49

BD47

BB48

BL49

BG38

BL45

BJ46

BG48

BE45

BG45

BG47

BE47

BJ38

BB47

BE48

BM39

BG43

BJ42

BM41

BJ39

BB45

BY47

BY46

CC41

CE41

BR47

BR46

BV41

BW41

AV46

AV47

AY41

BB41

AN46

AN47

AR41

AT41

BF39

BE49

BD46

M38

C44

B45

M39

DK47

3

ICELAKE Processor DDR4

M_A_CLKN0 17

M_A_CLKP0 17

M_A_CLKN1 17

M_A_CLKP1 17

M_A_CKE0 17

M_A_CKE1 17

M_A_CS#0 17

M_A_CS#1 17

M_A_BS#0 17

M_A_BS#1 17

M_A_BG#0 17

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_DQSN0

M_A_DQSP0

M_A_DQSN1

M_A_DQSP1

M_A_DQSN2

M_A_DQSP2

M_A_DQSN3

M_A_DQSP3

M_A_DQSN4

M_A_DQSP4

M_A_DQSN5

M_A_DQSP5

M_A_DQSN6

M_A_DQSP6

M_A_DQSN7

M_A_DQSP7

M_A_PARITY

M_A_ALERT#

SM_VREF

SMDDR_VREF_DQ1_M3

DDR_VTT_CTRL

DDR_DRAMRST#_R

M_A_BG#1 17

M_A_A0 17

M_A_A1 17

M_A_A2 17

M_A_A3 17

M_A_A4 17

M_A_A5 17

M_A_A6 17

M_A_A7 17

M_A_A8 17

M_A_A9 17

M_A_A10 17

M_A_A11 17

M_A_A12 17

M_A_A13 17

M_A_WE# 17

M_A_CAS# 17

M_A_RAS# 17

M_A_DIM0_ODT0 17

M_A_DIM0_ODT1 17

M_A_PARITY 17

M_A_ACT# 17

M_A_ALERT# 17

SM_VREF 17

SMDDR_VREF_DQ1_M3 18

TP59

For CH:A

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

U24C

LPDDR4 DDR4 NILLPDDR4 DDR4 NIL

AK48

DDRC_DQ0_0/DDR1_ DQ0_0

AK45

DDRC_DQ0_1/DDR1_ DQ0_1

AK49

DDRC_DQ0_2/DDR1_ DQ0_2

AG47

DDRC_DQ0_3/DDR1_ DQ0_3

AK47

DDRC_DQ0_4/DDR1_ DQ0_4

AG45

DDRC_DQ0_5/DDR1_ DQ0_5

AG48

DDRC_DQ0_6/DDR1_ DQ0_6

AG49

DDRC_DQ0_7/DDR1_ DQ0_7

AJ38

DDRC_DQ1_0/DDR1_ DQ1_0

AL39

DDRC_DQ1_1/DDR1_ DQ1_1

AJ39

DDRC_DQ1_2/DDR1_ DQ1_2

AL43

DDRC_DQ1_3/DDR1_ DQ1_3

AL38

DDRC_DQ1_4/DDR1_ DQ1_4

AJ42

DDRC_DQ1_5/DDR1_ DQ1_5

AL42

DDRC_DQ1_6/DDR1_ DQ1_6

AJ43

DDRC_DQ1_7/DDR1_ DQ1_7

AB49

DDRC_DQ2_0/DDR1_ DQ2_0

AB48

DDRC_DQ2_1/DDR1_ DQ2_1

AE49

DDRC_DQ2_2/DDR1_ DQ2_2

AE47

DDRC_DQ2_3/DDR1_ DQ2_3

AE48

DDRC_DQ2_4/DDR1_ DQ2_4

AB47

DDRC_DQ2_5/DDR1_ DQ2_5

AB45

DDRC_DQ2_6/DDR1_ DQ2_6

AE45

DDRC_DQ2_7/DDR1_ DQ2_7

AD38

DDRC_DQ3_0/DDR1_ DQ3_0

AD39

DDRC_DQ3_1/DDR1_ DQ3_1

AE39

DDRC_DQ3_2/DDR1_ DQ3_2

AE43

DDRC_DQ3_3/DDR1_ DQ3_3

AE38

DDRC_DQ3_4/DDR1_ DQ3_4

AD43

DDRC_DQ3_5/DDR1_ DQ3_5

AD42

DDRC_DQ3_6/DDR1_ DQ3_6

AE42

DDRC_DQ3_7/DDR1_ DQ3_7

J48

DDRD_DQ0_0/DDR1_ DQ4_0

J45

DDRD_DQ0_1/DDR1_ DQ4_1

J49

DDRD_DQ0_2/DDR1_ DQ4_2

G47

DDRD_DQ0_3/DDR1_ DQ4_3

J47

DDRD_DQ0_4/DDR1_ DQ4_4

G45

DDRD_DQ0_5/DDR1_ DQ4_5

G48

DDRD_DQ0_6/DDR1_ DQ4_6

E48

DDRD_DQ0_7/DDR1_ DQ4_7

J38

DDRD_DQ1_0/DDR1_ DQ5_0

G39

DDRD_DQ1_1/DDR1_ DQ5_1

G38

DDRD_DQ1_2/DDR1_ DQ5_2

G42

DDRD_DQ1_3/DDR1_ DQ5_3

J39

DDRD_DQ1_4/DDR1_ DQ5_4

J42

DDRD_DQ1_5/DDR1_ DQ5_5

G43

DDRD_DQ1_6/DDR1_ DQ5_6

J43

DDRD_DQ1_7/DDR1_ DQ5_7

B43

DDRD_DQ2_0/DDR1_ DQ6_0

D43

DDRD_DQ2_1/DDR1_ DQ6_1

A43

DDRD_DQ2_2/DDR1_ DQ6_2

C40

DDRD_DQ2_3/DDR1_ DQ6_3

C43

DDRD_DQ2_4/DDR1_ DQ6_4

D40

DDRD_DQ2_5/DDR1_ DQ6_5

B40

DDRD_DQ2_6/DDR1_ DQ6_6

A40

DDRD_DQ2_7/DDR1_ DQ6_7

B35

DDRD_DQ3_0/DDR1_ DQ7_0

D35

DDRD_DQ3_1/DDR1_ DQ7_1

A35

DDRD_DQ3_2/DDR1_ DQ7_2

D38

DDRD_DQ3_3/DDR1_ DQ7_3

C35

DDRD_DQ3_4/DDR1_ DQ7_4

C38

DDRD_DQ3_5/DDR1_ DQ7_5

B38

DDRD_DQ3_6/DDR1_ DQ7_6

A38

DDRD_DQ3_7/DDR1_ DQ7_7

ICL-U 1.2G QPWA

CPU@

2

1

03

DDRC_CLK_N/DDR 1_CLK_N_0

DDRC_CLK_P/DDR1_ CLK_P_0

DDRD_CLK_N/DDR 1_CLK_N_1

DDRD_CLK_P/DDR1_ CLK_P_1

DDRC_CKE0/DDR1_C KE0

DDRD_CKE1/DDR1_C KE1

DDRC_CS_0/DDR1_C S_N_0

DDRD_CS_1/DDR1_C S_N_1

DDRD_CA4/DDR1_BA 0

DDRC_CA5/DDR1_BG 0

DDRD_CA5/DDR1_M A2

DDRC_CA0/DDR1_M A5

DDRC_CA2/DDR1_M A6

DDRC_CA4/DDR1_M A7

DDRC_CA3/DDR1_M A8

DDRC_CA1/DDR1_M A9

DDRD_CA0/DDR1_M A13

DDRD_CA2/DDR1_M A14WE_N

DDRD_CA1/DDR1_M A15CAS_N

DDRD_CA3/DDR1_M A16RAS_N

DDRC_DQSN_0/DD R1_DQSN_0

DDRC_DQSP_0/DDR 1_DQSP_0

DDRC_DQSN_1/DD R1_DQSN_1

DDRC_DQSP_1/DDR 1_DQSP_1

DDRC_DQSN_2/DD R1_DQSN_2

DDRC_DQSP_2/DDR 1_DQSP_2

DDRC_DQSN_3/DD R1_DQSN_3

DDRC_DQSP_3/DDR 1_DQSP_3

DDRD_DQSN_0/DD R1_DQSN_4

DDRD_DQSP_0/DDR 1_DQSP_4

DDRD_DQSN_1/DD R1_DQSN_5

DDRD_DQSP_1/DDR 1_DQSP_5

DDRD_DQSN_2/DD R1_DQSN_6

DDRD_DQSP_2/DDR 1_DQSP_6

DDRD_DQSN_3/DD R1_DQSN_7

DDRD_DQSP_3/DDR 1_DQSP_7

3 of 19

NC/DDR1_ALERT_N

DDRC_CKE1/NC

DDRD_CKE0/NC

DDRC_CS_1/NC

DDRD_CS_0/NC

NC/DDR1_BA1

NC/DDR1_BG1

NC/DDR1_MA0

NC/DDR1_MA1

NC/DDR1_MA3

NC/DDR1_MA4

NC/DDR1_MA10

NC/DDR1_MA11

NC/DDR1_MA12

NC/DDR1_ODT_0

NC/DDR1_ODT_1

NC/DDR1_PAR

NC/DDR1_ACT_N

Y48

Y47

M43

M42

U45

V46

M41

P43

V42

V39

Y39

T39

T38

T42

R45

N47

P42

Y49

U48

Y45

U47

R49

U49

M47

M45

R47

P39

N46

R48

Y41

V41

Y42

V47

V43

V38

AH46

AH47

AJ41

AL41

AC47

AC46

AE41

AD41

H47

H46

G41

J41

C42

D42

D36

C36

P38

M48

M49

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_DQSN0

M_B_DQSP0

M_B_DQSN1

M_B_DQSP1

M_B_DQSN2

M_B_DQSP2

M_B_DQSN3

M_B_DQSP3

M_B_DQSN4

M_B_DQSP4

M_B_DQSN5

M_B_DQSP5

M_B_DQSN6

M_B_DQSP6

M_B_DQSN7

M_B_DQSP7

M_B_PARITY

M_B_ALERT#

M_B_CLKN0 18

M_B_CLKP0 18

M_B_CKE0 18

M_B_CS#0 18

M_B_BS#0 18

M_B_BS#1 18

M_B_BG#0 18

M_B_BG#1 18

M_B_A0 18

M_B_A1 18

M_B_A2 18

M_B_A3 18

M_B_A4 18

M_B_A5 18

M_B_A6 18

M_B_A7 18

M_B_A8 18

M_B_A9 18

M_B_A10 18

M_B_A11 18

M_B_A12 18

M_B_A13 18

M_B_WE# 18

M_B_CAS# 18

M_B_RAS# 18

M_B_DIM0_ODT0 18

M_B_DQSN0 3,18

M_B_DQSP0 3,18

M_B_DQSN1 3,18

M_B_DQSP1 3,18

M_B_DQSN2 3,18

M_B_DQSP2 3,18

M_B_DQSN3 3,18

M_B_DQSP3 3,18

M_B_DQSN4 3,18

M_B_DQSP4 3,18

M_B_DQSN5 3,18

M_B_DQSP5 3,18

M_B_DQSN6 3,18

M_B_DQSP6 3,18

M_B_DQSN7 3,18

M_B_DQSP7 3,18

M_B_PARITY 18

M_B_ACT# 18

M_B_ALERT# 18

+1.2VSUS

R278

A A

+3V_S5 2,6,8,10,11,13,14,15,16,28,29,30,33,34,37,40,41

+1.2VSUS 5,16,17,18,38,44

5

4

3

DDR_DRAMRST#_R

470_1%_2

R282 0_5%_2

DDR4_DRAMRST# 17,18

@

C353

*0.1u/10V_2

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ICL-U 2/14 (LPDDR4 I/F)

ICL-U 2/14 (LPDDR4 I/F)

ICL-U 2/14 (LPDDR4 I/F)

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

ZAUI

ZAUI

ZAUI

3 47Monday, November 04, 2019

3 47Monday, November 04, 2019

1

3 47Monday, November 04, 2019

3A

3A

3A

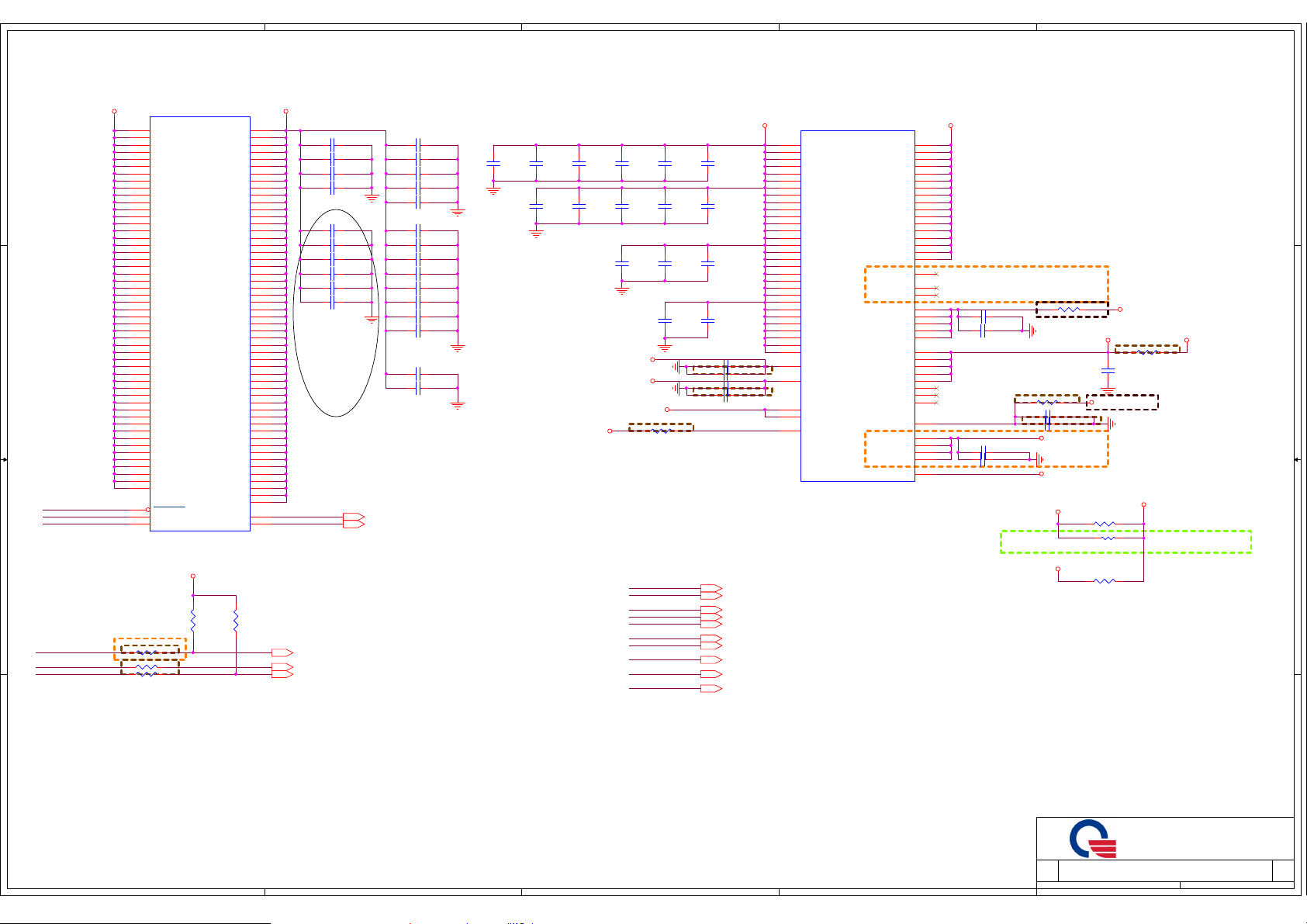

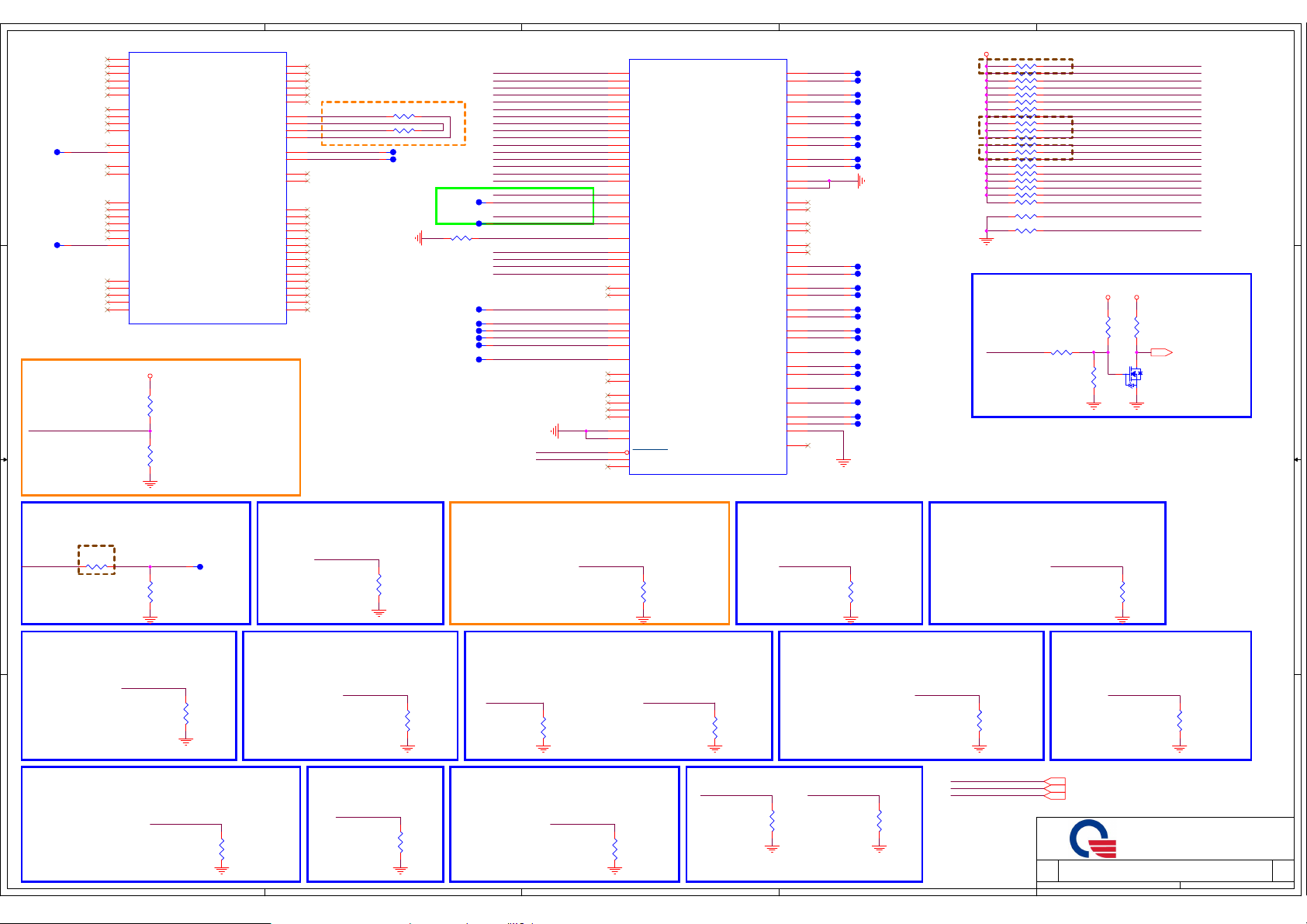

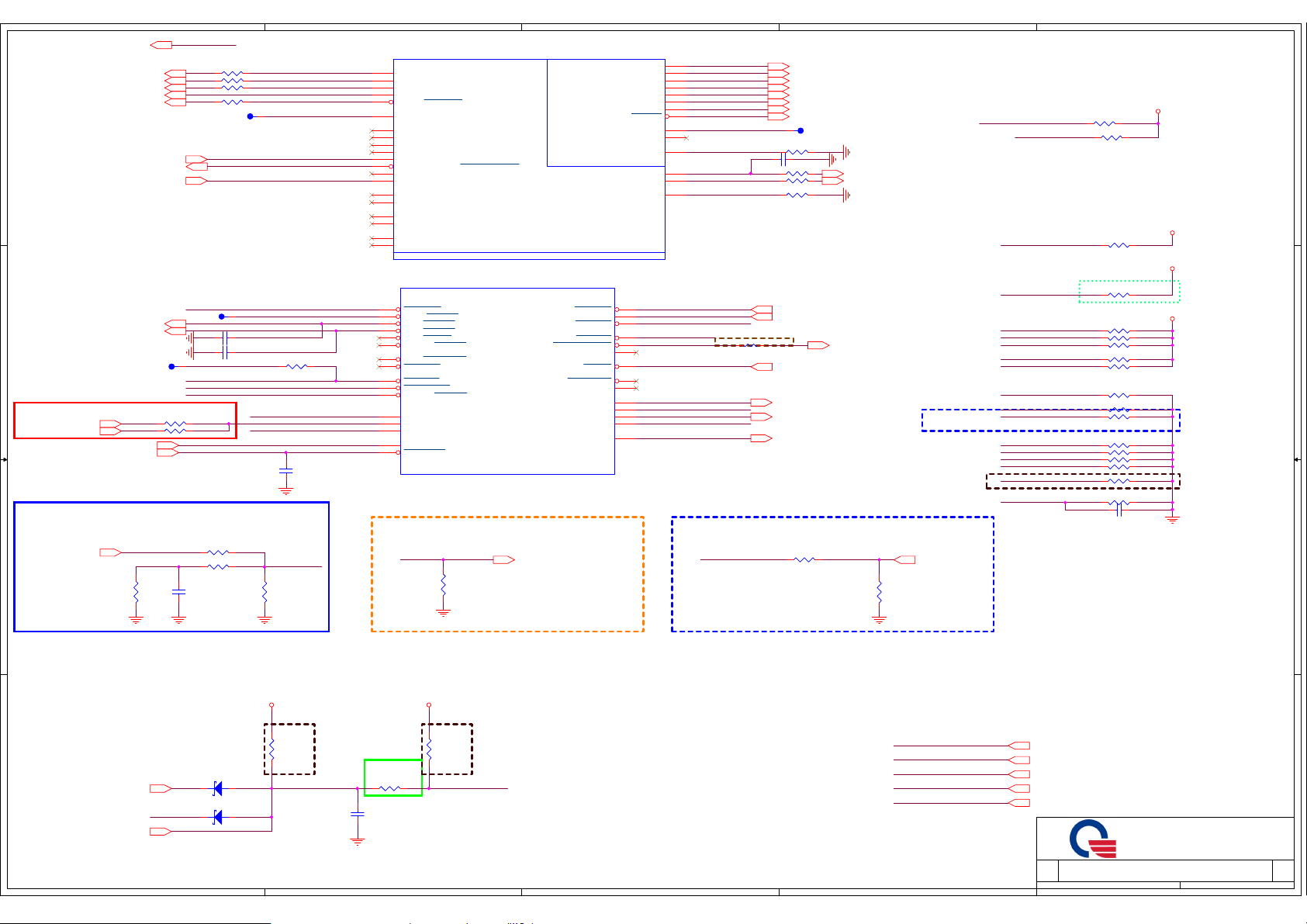

Page 4

5

Vinafix.com

Vinafix.com

4

3

2

1

04

D D

+VCCST

H_CATERR#

PM_THRMTRIP#

R591 49.9_1%_2

R584 1K_1%_2

H_CATERR#

EC_PECI34

H_PROCHOT#14,34,36,39

C C

H_PROCHOT#

C725

*0.1u/10V_2

DGPU_PW_CTRL#6

@

TP25

R583 499_1%_2

R230 49.9_1%_2

R296 49.9_1%_2

EC_PECI

PROCHOT#_CPU

PM_THRMTRIP#

CPU_POPI_RCOMP

PCH_OPI_RCOMP

DBG_PMODE

TBT_FORCE_PWR

GPP_E6

GPP _H2

U24D

J4

CATERR_N

CD5

PECI

C3

PROCHOT_N

E3

THRMTRIP_N

CJ41

PROC_POPIRCOMP

DU3

PCH_OPIRCOMP

A14

RSVD_25

B14

RSVD_26

DL15

DBG_PMODE

DV11

GPP_E3/CPU_GP0

DT11

GPP_E7/CPU_GP1

CR38

GPP_B3/CPU_GP2

CR39

GPP_B4/CPU_GP3

DT12

GPP_E6

DJ38

GPP_H2/CNV_BT_I2S_SDO

DL38

GPP_H19/TIME_SYNC0

ICL-U 1.2G QPW A

CPU@

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST_N

PCH_TRST_N

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_JTAGX

PROC_PRDY_N

PROC_PREQ_N

4 of 19

P3

K5

K3

P4

N1

N5

R5

K1

K2

N3

N2

P6

M6

XDP_TCK

XDP_TDI_CPU

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_JTAGX

CPU_PRDY#

CPU_PREQ#

R602 0_5%_2

R592 0_5%_2

R598 0_5%_2

R608 0_5%_2

R604 0_5%_2

@

TP69

@

TP66

@

TP67

@

TP70

@

TP68

XDP_TRST#PCH_TRST#

@

TP15

XDP_TDI_CPU

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TCK

@

TP14

@

TP12

H_PROCHOT#

PCH_TMS

PCH_TDO

PCH_TDI

CPU_PREQ#

XDP_TDO_CPU

XDP_TCK

PCH_TRST#

PCH_TCK

R582 1K_1%_2

R607 *51_1%_2@

R597 100_1%_2

R594 *51_1%_2@

R129 *51_1%_2@

R599 100_1%_2

R603 51_1%_2

R600 *51_1%_2@

R128 *51_1%_2@

+VCCSTG_TERM

Strap pin

DBG_PMODE10

THERMTRIP# (50ohm)

Trace Length: 1.1~12 inches

IMVP_PWRGD13,39

B B

R187 *100K_1%_4

SYS_SHDN#34,37,41

+VCCST

2

R188

1K/F_4

METR3904-G

3

Q12

DMG301NU-7

1

2

Q11

13

R196

1K/F_4

PM_THRMTRIP#

GPP_E610

GPP _H210

DBG_PMODE

GPP_E6

GPP _H2

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

5

PROJECT :

PROJECT :

+VCCSTG_TERM 5

+VCCST 5,13,16,36,39

+3V 2,6,9,10,11,12,13,17,20,22,25,26,27,28,30,31,32,33,34,35,37,38,39,40,41,42,43,44

4

3

2

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

ICL-U 3/14 (CPU MISC/JTA)

ICL-U 3/14 (CPU MISC/JTA)

ICL-U 3/14 (CPU MISC/JTA)

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

ZAUI

ZAUI

ZAUI

3A

3A

4 47Monday, November 04, 2019

4 47Monday, November 04, 2019

1

4 47Monday, November 04, 2019

3A

Page 5

5

Vinafix.com

4

3

2

1

05

BP39

BR37

BT38

AC35

BU37

BU49

CA39

CB49

L38

L49

N36

T49

AC37

AD35

AD36

AE36

AF49

C33

A33

B33

BG9

BJ9

BM9

BW1

BW2

R35

V34

T34

U35

AB34

W35

AA35

Y34

+VCC1.05_OUT_SFR_R

CD2

CG38

CG41

CG42

CG49

AD7

9.66A

need check RSVD or NOT

+VCCIN_AUX_OUT

+VCCPRG0

+

VCCPRG1

VCC1P8A

C282 10U/6.3V_6

C278 *1U/6.3V_4@

MV

C317 1U/6.3V_4

C316 *1U/6.3V_4@

R219 0_5%_6

R626 *Short_0402

C598 1U/6.3V_4

C595 1U/6.3V_4

+VCCPLL_OC

+VCCIO_OUT

+1.2VSUS

+1.2V_VCCPLL_OC

+1.8V_DEEP_SUS

PV

+VCCFPGM

R178 0_5%_6

C215

1U/6.3V_4

+VCC1.05_OUT_SFR

+VCCPLL_OC follow VDDQ

DDR4=1.2V

LPDDR4=1.1V

+VCCPLL_OC

R214 0_5%_6

R215 0_5%_8

R221 *0_5%_6

VCC1P8A: 0.7A

+VCCSTG_OUT_FUSE

VCCPLL: 0.09A

PV

VCCPLL_OC: 0.16A

for layout

+VCCIN +VCCIN

D D

C C

CPU_VIDALERT#

CPU_SVID_CLK

CPU_SVID_DAT

B B

CPU_VIDALERT#

CPU_SVID_CLK

CPU_SVID_DAT

ALERT#

Ra Neen check value

CLK & DAT

U24L

A19

VCCIN_1

AC12

VCCIN_2

V13

VCCIN_3

W12

VCCIN_4

Y13

VCCIN_5

K29

VCCIN_6

K31

VCCIN_7

B19

VCCIN_8

B23

VCCIN_9

B27

VCCIN_10

B29

VCCIN_11

BN10

VCCIN_12

BP11

VCCIN_13

BP9

VCCIN_14

BR10

VCCIN_15

BT11

VCCIN_16

A21

VCCIN_17

BT9

VCCIN_18

BU10

VCCIN_19

BV36

VCCIN_20

BV9

VCCIN_21

BW10

VCCIN_22

BW36

VCCIN_23

BW9

VCCIN_24

BY10

VCCIN_25

C19

VCCIN_26

C23

VCCIN_27

A23

VCCIN_28

C27

VCCIN_29

C29

VCCIN_30

CA36

VCCIN_31

CA9

VCCIN_32

CB10

VCCIN_33

CC11

VCCIN_34

CC36

VCCIN_35

CC9

VCCIN_36

CD10

VCCIN_37

CE11

VCCIN_38

A24

VCCIN_39

CE34

VCCIN_40

CE35

VCCIN_41

CF10

VCCIN_42

CF33

VCCIN_43

CG11

VCCIN_44

CG34

VCCIN_45

CG35

VCCIN_46

CH10

VCCIN_47

J30

VCCIN_48

CJ11

VCCIN_49

A27

VCCIN_50

CJ34

VCCIN_51

H1

VIDALERT

H2

VIDSCK

H3

VIDSOUT

ICL-U 1.2G QPWA

CPU@

Ra

R587 0_5%_2

R590 0_5%_2

R586 0_5%_2

12 of 19

+VCCST

VCCIN_52

VCCIN_53

VCCIN_54

VCCIN_55

VCCIN_56

VCCIN_57

VCCIN_58

VCCIN_59

VCCIN_60

VCCIN_61

VCCIN_62

VCCIN_63

VCCIN_64

VCCIN_65

VCCIN_66

VCCIN_67

VCCIN_68

VCCIN_69

VCCIN_70

VCCIN_71

VCCIN_72

VCCIN_73

VCCIN_74

VCCIN_75

VCCIN_76

VCCIN_77

VCCIN_78

VCCIN_79

VCCIN_80

VCCIN_81

VCCIN_82

VCCIN_83

VCCIN_84

VCCIN_85

VCCIN_86

VCCIN_87

VCCIN_88

VCCIN_89

VCCIN_90

VCCIN_91

VCCIN_92

VCCIN_93

VCCIN_94

VCCIN_95

VCCIN_96

VCCIN_97

VCCIN_98

VCCIN_99

VCCIN_100

VCCIN_101

VCCIN_102

VCCIN_103

VCCIN_104

VCCIN_SENSE

VSSIN_SENSE

R588

56_1%_2

CJ35

CK10

J32

CL34

CL35

CN34

CN35

CP33

CR34

A29

CR35

CT33

CT34

CT35

CU33

D19

D21

D23

D24

D27

AA12

D29

F19

F21

F23

F24

F27

F29

G1

G19

G23

AB1

G27

G29

H19

H23

H27

H29

J18

J20

J22

J23

AB13

J26

J28

K17

K19

K21

K23

K24

K27

M1

U1

F17

G17

R585

100_1%_2

VCCSENSE

VSSSENSE

VR_SVID_ALERT# 39

VR_SVID_CLK 39

VR_SVID_DATA 39

VCCIN: 70A

C232 1U/6.3V_4

C202 1U/6.3V_4

C207 1U/6.3V_4

C233 1U/6.3V_4

C218 *15P/25V_2

C300 *15P/25V_2

C298 *15P/25V_2

C301 *15P/25V_2

C234 *15P/25V_2

C306 *15P/25V_2

Add

C185 47U/6.3V_6

C229 47U/6.3V_6

C279 47U/6.3V_6

C296 47U/6.3V_6

C179 47U/6.3V_6

C271 22U/6.3V_6

C177 22U/6.3V_6

C292 22U/6.3V_6

C290 22U/6.3V_6

C307 22U/6.3V_6

C230 22U/6.3V_6

C221 22U/6.3V_6

C286 22U/6.3V_6

C556 10u/6.3V_4

C557 10u/6.3V_4

VCCSENSE 39

VSSSENSE 39

C330

1U/6.3V_4

+VCCST: 0.75A

+VCCSTG: 0.15A

C596

1U/6.3V_4

C553

10U/6.3V_6

+VCCSTG_TERM

C575

C267

1U/6.3V_4

1U/6.3V_4

C236

C552

10U/6.3V_6

10U/6.3V_6

C223

22U/6.3V_6

+VCCST

+VCCSTG

+VCCSTG_OUT_FUSE

C266

1U/6.3V_4

C247

10U/6.3V_6

C231

22U/6.3V_6

@

C354

*1U/6.3V_4

MV

R596 0_5%_6

+1.2VSUS +1.2VSUS

C274

1U/6.3V_4

C262

10U/6.3V_6

C241

22U/6.3V_6

@

C584

*1U/6.3V_4

C591 1U/6.3V_4

C592 1U/6.3V_4

C588 1U/6.3V_4

C589 1U/6.3V_4

+VCCSTG_OUT_LGC

+VCCIN 39

+1.2VSUS 3,16,17,18,38,44

+VCCIO_OUT 8

+VCC1.05_OUT_SFR 14

+VCC1.05_OUT_FET 10,14,16

+VCCST 4,13,16,36,39

+VCCSTG 16

+VCCSTG_TERM 4

+1.8V_DEEP_SUS 10,14,33

+1.2V_VCCPLL_OC 16

AA37

AG36

AJ36

AL36

AL49

AN36

AP37

AR36

AR37

AT36

AT49

AA49

AV36

AW37

AY36

BA37

BA49

BB36

BD36

BE37

BF36

BF37

AB36

BF49

BG36

BJ36

BL37

BM49

BN37

BP38

CB1

BY1

G33

F33

E5

U24M

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_24

VDDQ_25

VDDQ_26

VDDQ_27

VDDQ_28

VDDQ_29

VDDQ_30

VCCST

VCCSTG

VCCSTG_OUT_1

VCCSTG_OUT_2

VCCSTG_OUT_LGC

13 of 19

ICL-U 1.2G QPWA

CPU@

VDDQ_31

VDDQ_32

VDDQ_33

VDDQ_34

VDDQ_35

VDDQ_36

VDDQ_37

VDDQ_38

VDDQ_39

VDDQ_40

VDDQ_41

VDDQ_42

VDDQ_43

VDDQ_44

VDDQ_45

VDDQ_46

VDDQ_47

RSVD_77

RSVD_2

RSVD_3

VCC1P8A_1

VCC1P8A_2

VCC1P8A_3

VCC1P8A_4

VCC1P8A_5

VCCSTG_OUT_3

VCCSTG_OUT_4

VCCSTG_OUT_5

VCCSTG_OUT_6

VCCSTG_OUT_7

RSVD_74

RSVD_75

RSVD_76

VCCPLL_1

VCCPLL_OC_1

VCCPLL_OC_2

VCCPLL_OC_3

VCCPLL_OC_4

VCCIO_OUT

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ICL-U 4/14 (VCCIN/VDDQ)

ICL-U 4/14 (VCCIN/VDDQ)

ICL-U 4/14 (VCCIN/VDDQ)

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZAUI

ZAUI

ZAUI

3A

3A

3A

of

5 47Monday, November 04, 2019

5 47Monday, November 04, 2019

1

5 47Monday, November 04, 2019

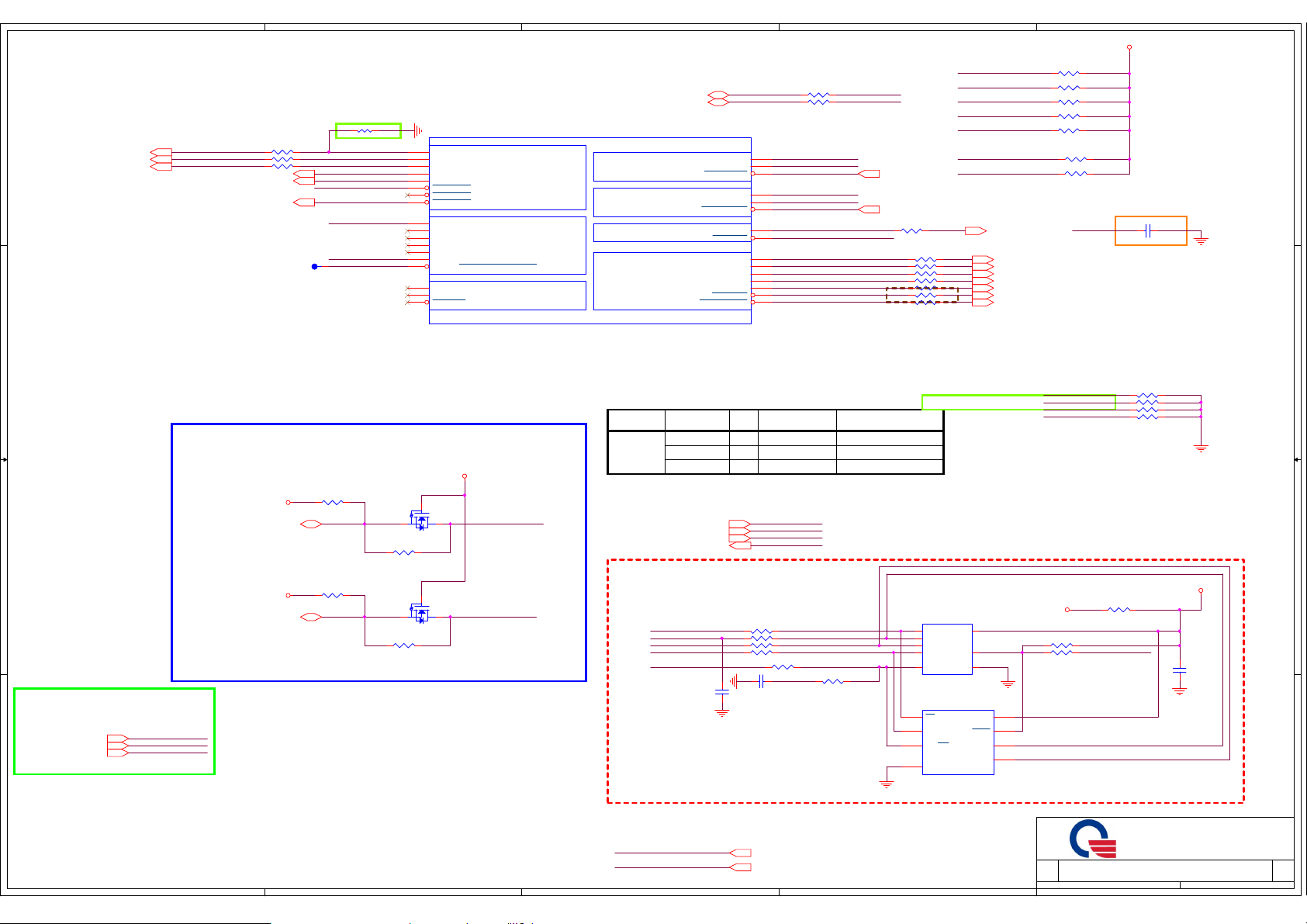

Page 6

5

Vinafix.com

4

3

2

1

06

D D

PD 75K WLAN side

need Check with BIOS

DGPU_HOLD_RST#19

GPP_B1810

DGPU_PWR_EN20,44

ACZ_SPKR10,26

GC6_FB_EN_Q20,22

GPU_EVENT#22

DGPU_PWROK19,22

GPP_B2310

ACCEL_INTA31

ODD_PRSNT#32

TPD_INT#30

TP90@

C C

TP86@

TP_I2C_DATA30

TP_I2C_CLK30

DGPU_HOLD_RST#

GPP_B18

DGPU_PWR_EN

ACZ_SPKR

GC6_FB_EN_Q

DGPU_PWROK

GPP_B23

UART2_RXD

UART2_TXD

TP_I2C_DATA

TP_I2C_CLK

DG : neet 33 ohm

+3V

ACCEL_INTA

ODD_PRSNT#

B B

Type C change

PCH_TypeC_UPFb#

SIO_EXT_SCI#

TPD_INT#

R733 10K_5%_2

R306 10K_5%_4

+3V_S5

R378 10K_1%_2

+3V_S5

R767 *20K_1%_2

+3V

R765

*20K_1%_2

U24F

CH48

GPP_B16/GSPI0_CLK

CF48

GPP_B18/GSPI0_MOSI

CF47

GPP_B17/GSPI0_MISO

CH49

GPP_B15/GSPI0_CS0_N

CH47

GPP_B14/SPKR/TIME_ SYNC1/GSPI0_CS1_N

CL47

GPP_B20/GSPI1_CLK

CK47

GPP_B22/GSPI1_MOSI

CK46

GPP_B21/GSPI1_MISO

CH45

GPP_B19/GSPI1_CS0_N

CL48

GPP_B23/SML1ALERT_N /PCHHOT_N/GSPI1_CS1_N

DP21

GPP_C8/UART0_RXD

DK21

GPP_C9/UART0_TXD

DL21

GPP_C10/UART0_RTS_ N

DJ22

GPP_C11/UART0_CTS_ N

DT22

GPP_C20/UART2_RXD

DW22

GPP_C21/UART2_TXD

DV22

GPP_C22/UART2_RTS_ N

DU22

GPP_C23/UART2_CTS_ N

DT24

GPP_C16/I2C0_SDA

DT23

GPP_C17/I2C0_SCL

DW23

GPP_C18/I2C1_SDA

DU23

GPP_C19/I2C1_SCL

DU41

GPP_H4/I2C2_SDA

DV41

GPP_H5/I2C2_SCL

DW41

GPP_H6/I2C3_SDA

DT41

GPP_H7/I2C3_SCL

DT40

GPP_H8/I2C4_SDA/CN V_MFUART2_RXD

DW40

GPP_H9/I2C4_SCL/CNV _MFUART2_TXD

ICL-U 1.2G QPWA

CPU@

DGPU_PW_CTRL#

DGPU_PW_CTRL#4

R388 EV@100K _1%_4

DGPU_PWROK PD on GPU side

UMA Only

SG/Optimise

GPP_D13/ISH_UART0_RX D

GPP_D15/ISH_UART0_RT S_N/GSPI2_CS1_N/IMGCLKOUT5

high

low

DGPU_PW_CTRL#

DGPU_PWROK

DGPU_PW_CTRL#

GPP_D16/ISH_UART0_CT S_N/CNV_WCEN

GPP_C14/UART1_RTS_ N/ISH_UART1_RTS_N

GPP_C15/UART1_CTS_ N/ISH_UART1_CTS_N

6 of 19

UMA Only

GPU power is control by PCH

GPIO (Discrete, SG or Optimize)

VGA H/W

Signal

1

UMA

GPU

0

GPP_D14/ISH_UART0_TXD

GPP_C12/UART1_RXD /ISH_UART1_RXD

GPP_C13/UART1_TXD/ ISH_UART1_TXD

GPP_B5/ISH_I2C0_SDA

GPP_B6/ISH_I2C0_SCL

GPP_B7/ISH_I2C1_SDA

GPP_B8/ISH_I2C1_SCL

GPP_B9/I2C5_SDA/ISH_I2C2_S DA

GPP_B10/I2C5_SCL/ISH_I2C2_SC L

R409 IV@1K/F_4

R658 *EV@10K_1%_2

Setup

Menu

Hidden

Hidden

GPP_D0/ISH_GP0

GPP_D1/ISH_GP1

GPP_D2/ISH_GP2

GPP_D3/ISH_GP3

GPP_D17/ISH_GP4

GPP_D18/ISH_GP5

GPP_E15/ISH_GP6

GPP_E16/ISH_GP7

UMA boot

GPU boot

DV33

DW33

DT33

DU33

DK22

DW24

DV24

DU24

CN43

CN42

CN41

CL43

CL41

CJ39

DU36

DV36

DW36

DT36

DU34

DW34

DT14

DU14

R764 *0_5%_4

+3V

+3V

R244 *EV@10K_5%_4

R261 EV@10K_5%_4

PCH_TypeC_UPFb#

SIO_EXT_SCI#

GPU Control PU/PD

DGPU_PWR_EN

GC6_FB_EN_Q

PCH_TypeC_UPFb# 29

SIO_EXT_SCI# 34

R245 EV@100K_5%_4

R262 *EV@10K_5%_4

UART2_RXD

UART2_TXD

GPP_B18

R758 *49.9K_1%_2

R757 *49.9K_1%_2

R657 *10K_5%_2

20131015 For GC6 NV DG GC6_FB_EN PD.1A-1

+3V

R659 10K_5%_2

DGPU_HOLD_RST#

+3V

PV

+3V 2,9,10,11,12,13,17,20,22,25,26,27,28,30,31,32,33,34,35,37,38,39,40,41,42,43,44

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ICL-U 5/14 (I2C/ISH)

ICL-U 5/14 (I2C/ISH)

ICL-U 5/14 (I2C/ISH)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZAUI

ZAUI

ZAUI

3A

3A

6 47Monday, November 04, 2019

6 47Monday, November 04, 2019

1

6 47Monday, November 04, 2019

3A

Page 7

5

Vinafix.com

4

3

2

1

U24O

A11

VSS_1

A46

VSS_2

BA45

VSS_3

BA47

VSS_4

BB11

D D

C C

B B

BB3

BB7

BC37

BD3

BD38

BD39

BD41

BD42

BD43

BD45

BD49

BD5

BD6

BD7

BE1

BE2

BF3

BF45

BF47

BF7

BG3

BG41

BG7

BH37

AA45

BJ41

BJ43

BJ45

BJ49

BM11

BM3

BM45

BM47

BM5

AA47

BM6

BM7

BP1

BP2

BP3

BP43

BP7

BR45

BR49

AB11

AB3

AB38

AB39

AB41

AB42

AB43

AB5

AB6

AC45

AC49

AD10

AD11

AD34

AD37

AE6

AF37

A48

A49

BJ1

BJ2

BJ3

BJ7

A17

A3

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

15 of 19

ICL-U 1.2G QPWA

CPU@

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

AF45

AF47

AG1

AG11

AG3

AG38

AG39

AG41

A31

AG42

AG43

AG5

AG9

AH2

AH37

AH45

AH49

AJ2

AJ3

A34

AK37

AL2

AL45

AL47

AL6

AM2

AM37

AN2

AN38

AN39

A36

AN41

AN42

AN43

AN45

AN49

AN6

AR1

AR11

AR2

AR3

A39

AR7

AR9

AT3

AT45

AT47

AT5

AT6

AT7

AU37

AV11

A42

AV3

AV38

AV39

AV41

AV42

AV43

AV45

AV49

AV7

AY3

A44

AY7

B17

B2

B21

B24

B3

B31

B48

BA1

BA2

BT39

BT41

BT42

BT43

BU45

BU47

BV11

BW3

BW37

BW5

BW6

BW7

BY37

BY45

BY49

CA3

CA38

CA41

CA42

CA43

CA7

CB37

CB45

CB47

CC3

CC7

CE37

CE45

CE49

CE9

CG37

CG39

CG43

CG45

CG47

CG9

CH3

CH5

CJ37

CJ42

CK45

CK49

CK9

CL37

CL42

CL49

CM45

CM47

CM9

CN3

CN37

CN39

CN5

CP9

CR32

BT3

BT7

BV1

BV2

BV3

BV7

C11

C13

C14

C17

C21

C24

C31

C34

C39

C48

C49

C6

CJ9

U24P

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

16 of 19

ICL-U 1.2G QPWA

CPU@

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

CR37

CR45

CR49

CT37

CT39

CT42

CT9

CU45

CU47

CU49

CV3

CV34

CV35

CV5

CV9

CY41

CY45

CY49

CY9

D13

D17

D31

D44

D49

DA10

DA33

DA9

DB32

DB35

DB38

DB45

DB47

DB49

DC3

DC49

DC5

DC6

DD37

DD42

DE10

DE13

DE17

DE18

DE20

DE22

DE23

DE26

DE28

DE29

DE33

DE45

DE6

DF13

DF22

DF28

DF33

DF35

DF39

DG10

DG12

DG13

DG15

DG22

DG23

DG47

DG6

DH1

DH3

DH45

DH5

DJ19

DJ21

DJ27

DJ31

DJ33

DJ36

DJ42

DK49

DL10

DL13

DL44

DL47

DM47

DN15

DN19

DN24

DN31

DN36

DN42

DP45

DR49

DT10

DT15

DT20

DT27

DT32

DT37

DT42

DT49

DU10

DU15

DU20

DU27

DU32

DU37

DU48

DU49

DV44

DV48

DW1

DW10

DW2

DW20

DW27

DW44

DW46

DW48

DW49

DW7

DK3

DK4

DK6

DK8

DT1

DT3

DT6

DT7

DT8

DU1

DU2

DU7

DV2

DV8

E11

E34

E36

E39

E42

E6

U24Q

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

VSS_361

17 of 19

ICL-U 1.2G QPWA

CPU@

VSS_362

VSS_363

VSS_364

VSS_365

VSS_366

VSS_367

VSS_368

VSS_369

VSS_370

VSS_371

VSS_372

VSS_373

VSS_374

VSS_375

VSS_376

VSS_377

VSS_378

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_385

VSS_386

VSS_387

VSS_388

VSS_389

VSS_390

VSS_391

VSS_392

VSS_393

VSS_394

VSS_395

VSS_396

VSS_397

VSS_398

VSS_399

VSS_400

VSS_401

VSS_402

VSS_403

VSS_404

VSS_405

VSS_406

VSS_407

VSS_408

VSS_409

VSS_410

VSS_411

VSS_412

VSS_413

VSS_414

VSS_415

VSS_416

VSS_417

VSS_418

VSS_419

VSS_420

VSS_421

VSS_422

VSS_423

VSS_424

VSS_425

VSS_426

VSS_427

F11

F31

F45

F47

F8

G21

G24

G3

G31

G36

G49

G5

H17

H21

H24

H31

H33

H36

H45

H49

J10

J13

J16

J36

J6

K11

K33

K8

L36

L39

L41

L42

L43

L45

L47

M10

M3

M36

M5

N45

N49

P11

P41

P8

R3

R37

T11

T36

T41

T43

T45

T47

U3

U37

U5

V11

V36

V45

V49

V9

W37

Y36

Y38

Y43

Y9

DE15

07

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ICL-U 6/14 (GND)

ICL-U 6/14 (GND)

ICL-U 6/14 (GND)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZAUI

ZAUI

ZAUI

3A

3A

7 47Monday, November 04, 2019

7 47Monday, November 04, 2019

1

7 47Monday, November 04, 2019

3A

Page 8

5

Vinafix.com

U24R

N34

RSVD_TP_27

AK10

RSVD_TP_28

BT36

RSVD_7

AH10

RSVD_TP_29

BC10

RSVD_TP_30

CH33

RSVD_TP_31

CJ32

RSVD_12

AM10

RSVD_TP_32

BH10

RSVD_TP_33

J34

R170

0_5%_2

AJ11

CG32

CK33

BP41

AL11

BG11

AN11

M13

M34

DU42

DW42

D33

Y11

L34

L13

K13

RSVD_TP_34

RSVD_9

RSVD_10

RSVD_17

RSVD_21

RSVD_22

RSVD_20

RSVD_23

RSVD_24

RSVD_16

RSVD_18

RSVD_19

RSVD_42

RSVD_43

RSVD_44

RSVD_45

RSVD_47

ICL-U 1.2G QPWA

CPU@

+3VPCU

R580

10K_5%_2

@

R581

*100K_5%_2

MIPI60_CFG0#_R

@

R168

*1K_5%_2

18/19

D D

C C

TP_L34

TP7@

TP_M34

TP8@

PROC_SELECT

U42_L_U43E_Z

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG0

1: (DEFAULT) NORMAL OPERATION; NO STALL

MIPI60_CFG0#

B B

MV

@

TP17

RSVD_TP_35

RSVD_TP_36

RSVD_TP_37

PCH_IST_TP_0

PCH_IST_TP_1

DA11

CL32

CN32

CY35

RSVD_32

DB37

RSVD_33

DF37

RSVD_34

BF11

IST_TP_0

BD11

IST_TP_1

BE10

IST_TRIG_0

BF10

IST_TRIG_1

CW33

CY32

CY37

RSVD_27

CV37

RSVD_28

G34

RSVD_35

H34

RSVD_46

DJ34

RSVD_48

DK31

RSVD_49

DK15

RSVD_50

CP3

RSVD_51

CP5

RSVD_52

AN9

RSVD_53

AN7

RSVD_54

AF10

RSVD_36

AE11

RSVD_37

H5

RSVD_38

D1

RSVD_39

DJ40

RSVD_40

DK40

RSVD_41

PCI EXPRESS STATIC LANE REVERSAL

FOR ALL PEG PORTS

CFG2

1: (DEFAULT)NORMAL OPERATION

0: LANE REVERSAL

always un-stuff

for INTEL Debug

(substitute test points)

IST_TP_0

IST_TP_1

IST_TRIG_0

IST_TRIG_1

PCH_IST_TP_0

PCH_IST_TP_1

MIPI60_CFG2#

4

R199 *0_5%_2@

R197 *0_5%_2@

@

R181

*1K_5%_2

TP24 @

TP22 @

NEED CHECK. 03/20

R173 49.9_1%_2

3

MIPI60_CFG0#

MIPI60_CFG1#

MIPI60_CFG2#

MIPI60_CFG3#

MIPI60_CFG4#

MIPI60_CFG5#

MIPI60_CFG6#

MIPI60_CFG7#

MIPI60_CFG8#

MIPI60_CFG9#

MIPI60_CFG10#

MIPI60_CFG11#

MIPI60_CFG12#

MIPI60_CFG13#

MIPI60_CFG14#

MIPI60_CFG15#

MIPI60_CFG16_STB_DN

TP13@

TP16@

TP76@

TP72@

TP73@

TP75@

TP74@

TP77@

PHYSICAL_DEBUG_ENABLED(DFX PRIVACY)

CFG4

1: DISABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED TO THE EMBEDDED DISPLAY PORT

0: ENABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO EMBEDDED DISPLAY PORT

MIPI60_CFG17_STB_DP

MIPI60_CFG18_STB_DN

MIPI60_CFG19_STB_DP

CFG_RCOMP

MBP0#

MBP1#

MBP2#

MBP3#

TP_AV1

TP_AT2

TP_AT1

TP_AU1

TP_AU2

TP_AV2

SKTOCC#

U42_L_U43E_Z

AG6

AE7

AG7

AD9

AE9

AB9

AJ6

AB7

V10

AJ5

Y10

AJ7

AB10

AL7

AL9

AJ9

V6

V7

Y6

Y7

AD6

T9

T7

T10

T6

BJ11

BL10

AV1

AT2

AT1

AU1

AU2

AV2

DP3

DT2

AR10

AP10

BP36

BM36

J15

K15

C5

D4

A5

MIPI60_CFG4#

U24S

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_RCOMP

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

RSVD_62

RSVD_63

RSVD_TP_17

RSVD_TP_18

RSVD_TP_20

RSVD_TP_19

RSVD_TP_21

RSVD_TP_22

RSVD_67

RSVD_68

RSVD_69

RSVD_71

RSVD_70

RSVD_72

VSS_430

VSS_431

SKTOCC_N

RSVD_78

RSVD_64

ICL-U 1.2G QPWA

CPU@

R166

1K_5%_2

19 of 19

TP_A47

A47

RSVD_TP_1

RSVD_TP_2

RSVD_57

RSVD_58

RSVD_TP_10

RSVD_TP_11

RSVD_79

RSVD_80

RSVD_TP_5

RSVD_TP_6

VSS_428

VSS_429

RSVD_55

RSVD_56

RSVD_65

RSVD_66

RSVD_59

RSVD_60

RSVD_TP_13

RSVD_TP_14

RSVD_TP_24

RSVD_TP_25

RSVD_TP_15

RSVD_TP_16

TP_3

TP_4

RSVD_TP_12

RSVD_TP_7

RSVD_TP_8

RSVD_TP_9

RSVD_TP_23

TP_1

TP_2

VSS_432

RSVD_TP_26

PEG DEFER TRAINING

CFG7

1: (DEFAULT) PEG TRAIN IMMEEDIATELY

FOLLOWING XXRESETB DEASSERTION

0: PEG WAIT FOR BIOS FOR TRAINING

TP_B47

B47

TP_C1

C1

TP_E1

E1

TP_CT32

CT32

TP_CV32

CV32

TP_G15

G15

TP_F15

F15

TP_BW11

BW11

TP_CA11

CA11

C16

A16

C2

A4

DP5

DR5

D14

E16

DV6

DW6

DP2

DP1

DW4

DV4

CM33

DB10

R1

DW3

DV3

DH49

DL8

DW47

DV47

DU47

P10

MIPI60_CFG7#

TP_DV6

TP_DW6

TP_DP2

TP_DP1

TP_DW4

TP_DV4

TP_CM33

TP_DB10

TP_R1

TP_DW3

TP_DV3

TP_DH49

TP_DL8

TP_DW47

TP_DV47

TP60 @

TP58 @

TP62 @

TP65 @

TP23 @

TP27 @

TP63 @

TP61 @

TP19 @

TP20 @

TP93 @

TP89 @

TP81 @

TP80 @

TP88 @

TP87 @

TP21 @

TP30 @

TP71 @

TP85 @

TP84 @

TP79 @

TP33 @

TP95 @

TP97 @

@

R146

*1K_5%_2

2

+VCCIO_OUT

R169 1K_5%_2

MV

R172 1K_5%_2

R180 *10K_1%_2

R162 *10K_1%_2

R167 *10K_1%_2

R152 *10K_1%_2

R176 *10K_1%_2

R147 *10K_1%_2

R126 1K_5%_2

R185 1K_5%_2

MV

R133 1K_5%_2

R179 *10K_1%_2

R141 1K_5%_2

MV

R182 1K_5%_2

R184 *10K_1%_2

R183 *10K_1%_2

R134 10K_1%_2

R135 10K_1%_2

R127 10K_1%_2

R136 10K_1%_2

R156 51_1%_2

R143 51_1%_2

SKTOCC_N -> H_PRESENT_N

R574

*10K_5%_2

SKTOCC#

R578 *0_5%_2@

NO SVID PROTOCOL CAPABLE VR CONNECTED

CFG9

1: VRS SUPPORTING SVID PROTOCOL ARE PRESENT

0: NO VR SUPPORTING SVID IS PRESENT. THE CHIP

WILL NOT GENERATE (OR RESPOND TO) SVID ACTIVITY

@

R572

*10K_5%_2

MIPI60_CFG9#

MIPI60_CFG0#_R

MIPI60_CFG1#

MIPI60_CFG2#

MIPI60_CFG3#

MIPI60_CFG4#

MIPI60_CFG5#

MIPI60_CFG6#

MIPI60_CFG7#

MIPI60_CFG8#

MIPI60_CFG9#

MIPI60_CFG10#

MIPI60_CFG11#

MIPI60_CFG12#

MIPI60_CFG13#

MIPI60_CFG14#

MIPI60_CFG15#

MBP0#

MBP1#

MBP2#

MBP3#

MIPI60_CFG16_STB_DN

MIPI60_CFG18_STB_DN

+3VPCU +3V_S5

@

3

2

1

@

R186

*1K_5%_2

1

@

R573

*10K_5%_2

@

Q32

*DMG1012T-7

08

RSMRST# 13,34

PCH/ PCH LESS MODE SELECTION

CFG1

1: (DEFAULT) NORMAL OPERATION

0: PCH-LESS MODE

DMI AC COUPLING - JUST A PLACE HOLDER.

A A

NOT APPLICABLE FOR ULX-ULT

CFG11

1:(DEFAULT)DMI WILL BE CONFIGURED AS HALF SWING DC COUPLED

0: DMI WILL BE CONFIGURED AS FULL SWING AC COUPLED

MIPI60_CFG1#

MIPI60_CFG11#

5

@

R171

*1K_5%_2

PHYSICAL_DEBUG_ENABLED(DFX PRIVACY)

CFG3

1: DISABLED

0: ENABLED

SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

@

R177

*1K_5%_2

MIPI60_CFG3#

PM SYNC LEGACY

CFG12

1: (DEFAULT) PMSYNC 2.0

0: LEGACY

MIPI60_CFG12#

4

@

R161

*1K_5%_2

@

R140

*1K_5%_2

PCIE PORT BIFURCATION STRAPS

CFG[6:5]

11: DEVICE1 FUNTION 1, DEVICE 1 FUNCTION2 DISABLED

10: DEVICE1 FUNCTION1 ENABLED DEVICE1 FUNCTION 2 DISABLED

01: DEVICE 1 FUNCTION 1 DISABLED, DEVICE 1 FUNCTION 2 ENABLED

00 DEVICE 1 FUNCTION 1 ENABLED, DEVICE 1 FUNCTION 2 ENABLED

MIPI60_CFG5# MIPI60_CFG6#

@

R151

*1K_5%_2

PMSYNC AYNC MODE- PM SYNC

CFG13

1: (DEFAULT)SYNCHCRONOUS (1 24 MHZ CYCLE PER BIT)

0: ASYNC - 4-24MHZ CYCLES PER BIT

MIPI60_CFG13#

@

R193

*1K_5%_2

3

@

R174

*1K_5%_2

ALLOW THE USE OF NOA ON LOCKED UNITS

CFG8

1: DISABLED(DEFAULT): IN THHIS CASE, NOA WILL BE

DISABLE IN LOCKED UNITS AND ENABLED IN UN-LOCKED UNITS

0: ENABLED: NOA WILL BE AVAILABLE REGARDLESS OF

THE LOCKING OF THE UNIT

MIPI60_CFG15#MIPI60_CFG14#

@

R192

*1K_5%_2

@

R191

*1K_5%_2

2

MIPI60_CFG8#

@

R125

*1K_5%_2

SAFE MODE BOOT

CFG10

1: POWER FEATURES ACTIVATED DURING RESETT

0: POWER FEATURES (ESPECIALLY CLOCK GATINE

ARE NOT ACTIVATED

+VCCIO_OUT 5

+3VPCU 12,16,25,26,28,30,31,34,35,36,37

+3V_S5 2,6,10,11,13,14,15,16,28,29,30,33,34,37,40,41

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

MIPI60_CFG10#

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ICL-U 7/14 (RSVD/XDP)

ICL-U 7/14 (RSVD/XDP)

ICL-U 7/14 (RSVD/XDP)

1

@

R132

*1K_5%_2

ZAUI

ZAUI

ZAUI

8 47Monday, November 04, 2019

8 47Monday, November 04, 2019

8 47Monday, November 04, 2019

3A

3A

3A

Page 9

5

Vinafix.com

4

3

2

+3V_DEEP_SUS

1

SMB_PCH_CLK

SMB_PCH_DAT

SMB_ML0_CLK

SMB_ML0_DAT

PCH_SUSPWRD NACK

SMB_ML1_CLK

SMB_ML1_DAT

GPP_C0/SMBCLK

GPP_A0/ESPI_IO0

GPP_A1/ESPI_IO1

GPP_A2/ESPI_IO2

GPP_A3/ESPI_IO3

2ND_MBCLK SMB_ML1_CLK

2ND_MBDATA SMB_ML1_DAT

2ND_MBCLK22,26,34

2ND_MBDATA22,26,34

D D

PCH_SPI1_CLK9,31,34

PCH_SPI1_SI9,10,31,34

PCH_SPI1_SO9,31,34

PCH_SPI1_CLK

PCH_SPI1_SI

PCH_SPI1_SO

R777 22_1%_4

R759 22_1%_4

R744 22_1%_4

PCH_SPI_IO210

PCH_SPI_IO310

SPI_TPM_CS#31

SSD

TP91

C C

R783 100K_1%_2

PCH_SPI0_CLK

PCH_SPI0_MOSI

PCH_SPI0_MISO

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

SPI_TPM_CS#

GPP_E11

GPP_E10

SATA_LED#

U24E

DB42

SPI0_CLK

DD43

SPI0_MOSI

DF43

SPI0_MISO

DF42

SPI0_IO2

DD41

SPI0_IO3

DB43

SPI0_CS0_N

DF41

SPI0_CS1_N

DB41

SPI0_CS2_N

DV16

GPP_E11/SPI1_CLK/BK1/ SBK1

DT16

GPP_E13/SPI1_MOSI/BK3/ SBK3

DU18

GPP_E12/SPI1_MISO/BK2/ SBK2

DT18

GPP_E1/SPI1_IO2

DW18

GPP_E2/SPI1_IO3

DW16

GPP_E10/SPI1_CS_N/BK 0/SBK0

DU16

GPP_E8/SATALED_N/ SPI1_CS1_N

DV19

CL_CLK

DW19

CL_DATA

DT19

CL_RST_N

ICL-U 1.2G QPWA

CPU@

SPI 0 SPI 1 MLINK

SMBUSSML 0SML1eSPI

GPP_C6/SML1CLK/S USWARN_N/SUSPW RDNACK

5 of 19

GPP_C1/SMBDATA

GPP_C2/SMBALERT_ N

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT_N

GPP_C7/SML1DATA/ SUSACK_N

GPP_A5/ESPI_CLK

GPP_A4/ESPI_CS_N

GPP_A6/ESPI_RESET_N

DK27

DP24

DL24

DK24

DJ24

DP22

DN22

DL22

CR47

CN45

CN48

CN49

CN47

CT45

CR46

R380 0_5%_2

R381 0_5%_2

SMB_PCH_CLK

SMB_PCH_DAT

GPP_C2

SMB_ML0_CLK

SMB_ML0_DAT

GPP_C5

SMB_ML1_CLK

SMB_ML1_DAT

ESPI_CLK_R

ESPI_0_R

ESPI_1_R

ESPI_2_R

ESPI_3_R

ESPI_CS#_R

ESPI_RESET#_R

GPP_C2 9,10

GPP_C5 10

R379 *0_5%_2

R240 49.9_1%_2

R231 10_5%_2

R233 10_5%_2

R236 10_5%_2

R237 10_5%_2

R254 0_5%_2

R242 0_5%_2

PCH SPI ROM(CLG)

DG : no neet PD

P/N

AKE3DZN0Z03

AKE3DF-KN01

PCH_SPI_CS0#

PCH_SPI1_CLK

PCH_SPI1_SI

PCH_SPI1_SO

R363 22_1%_4

C374 1u/6.3V_2

+3VSPI

MX25L12873FM2I-10G

W25Q128JVSIQ

GD25B127DSIGR

R351 100K_1%_4

PCH SPI ROM(CLG)

U32

1

CE#

6

SCK

5

SI

2

SO

3

WP#

BIOS SOCKET

DG008000012

U33

1

CS

2

IO1/DO

3

IO2/WP

4

GND

W25Q64FVSSIQ

VDD

HOLD#

VSS

8

7

4

VCC

IO3/HOLD

CLK

IO0/DI

HOLD#

C373

22p/50V_4

Size

16M

16M

16M

R384 0_5%_4

R312 22_1%_4

R323 22_1%_4

R382 22_1%_4

Vender

SMBus/Pull-up(CLG)

+3V

R800 4.7K_5%_2

+3V

SMB_RUN_DAT17,30,31

R790 *0_5%_2@

B B

R788 4.7K_5%_2

+3V

SMB_RUN_CLK17,30,31

R792 *0_5%_2@

Q41A

Q41B

5

2N7002KDW

2

2N7002KDW

34

61

SMB_PCH_DAT

DDR4

Touch Pad

SMB_PCH_CLK

Kabylake

POA 3.3V

MXIC

Winbond

GigaDevice AKE3D ZN0Q02

PCH_SPI_CS0#34

PCH_SPI1_CLK9,31,34

PCH_SPI1_SI9,10,31,34

PCH_SPI1_SO9,31,34

PCH_SPI_CS0# PCH_SPI_CS0#_R

PCH_SPI1_CLK PCH_SPI1_CLK_R

PCH_SPI1_SI PCH_SPI1_SI_R

PCH_SPI1_SO PCH_SPI1_SO_R

PCH_SPI_IO2 BIOS_WP#

strap pin

GPP_C29,10

GPP_E1110

GPP_E1010

A A

GPP_C2

GPP_E11

GPP_E10

P/N DG008000011 (Socket)

R801 2.2K_5%_2

R779 2.2K_5%_2

R361 2.2K_5%_2

R367 2.2K_5%_2

R383 *10K_5%_2

R356 2.2K_5%_2

R357 2.2K_5%_2

PCH_SUSPWRD NACK 34

ESPI_CLK 34

ESPI_0 34

ESPI_1 34

ESPI_2 34

ESPI_3 34

ESPI_CS# 34

ESPI_RESET# 34

GPP_E11

ESPI_CS#

ESPI_RESET#

PCH_SPI1_CLK

+3V_DEEP_SUS

+3VSPI

R324 100K_1%_4

R335 22_1%_4

8

7

6

5

EMI(near Ra)

ESPI_CLK

C326 *10P/50V_2

R728 100K_5%_2

R243 75K_1%_2

R239 100K_5%_2

R789 *100K_5%_2

R358 0_5%_6

PCH_SPI_IO3

+3VSPI

C370

0.1u/16V_2

09

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

+3V 2,6,10,11,12,13,17,20,22,25,26,27,28,30,31,32,33,34,35,37,38,39,40,41,42,43,44

+3V_DEEP_SUS 10,14

4

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ICL-U 8/14 (SMBus/SPI)

ICL-U 8/14 (SMBus/SPI)

ICL-U 8/14 (SMBus/SPI)

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

PROJECT :

PROJECT :

1

ZAUI

ZAUI

ZAUI

9 47Monday, November 04, 2019

9 47Monday, November 04, 2019

9 47Monday, November 04, 2019

3A

3A

3A

Page 10

5

Vinafix.com

TOP SWAP OVERRIDE

High: TOP SWAP ENABLED

Low: DISABLED

WEAK INTERNAL PD 20K

GPP_B14/SPKR

ACZ_SPKR6,26

D D

NO REBOOT

High: NO REBOOT

Low: REBOOT ENABLED

WEAK INTERNAL PD 20K

ACZ_SPKR

GPP_B18/GSPI0_MOSI

GPP_B186

TLS CONFIDENTIALITY

C C

HIGH - TLS CONFIDENTIALITY ENABLE

LOW - TLS CONFIDENTIALITY DISABLE

WEAK INTERNAL PD 20K

GPP_B18

GPP_C2/SMBALERT#

GPP_C29

+3V

@

R664

*4.7K_5%_2

@

R665

*20K_1%_2

+3V

@

R655

*4.7K_5%_2

@

R656

*20K_1%_2

+3V_DEEP_SUS

R346

4.7K_5%_2

@

R303

*20K_1%_2

(RSVD) XTAL INPUT MODE

High: XTAL INPUT IS SINGLE ENDED

Low: XTAL IS ATTACHED

WEAK INTERNAL PD 20K

GPD713

GPD7

This strap has no internal pull-up or pull-down.

0 = DDP1 I2C / TBT_LSX0 pins at 1.8V

1 = DDP1 I2C / TBT_LSX0 pins at 3.3V

GPP_E19

GPP_E192

(RSVD) A0 PERSONALITY STRAP

High: DISABLE

Low: ENABLE

External pull-up is required.

SPI0_IO3

PCH_SPI_IO39

PCH_SPI_IO3GPP_C2

4

GPD7

+3V_DEEP_SUS

R304

*4.7K_5%_2

R301

20K_1%_2

+3V_DEEP_SUS

@

+3V_S5

@

R413

*4.7K_5%_2

@

R405

*20K_1%_2

R721

100K_5%_2

@

R722

*4.7K_5%_2

3

CPUNSSC CLOCK FREQ

High: 19.2MHz CLOCK FROM INTERNAL DIVIDER

Low: 38.4MHz CLOCK FROM DIRECT CRYSTAL (Default)

WEAK INTERNAL PD 20K

+3V_DEEP_SUS +3V_DEEP_SUS

GPP_B23/SML1ALERT#

GPP_B236

3V SELECT STRAP

High: 3.0V +/-5%

Low: 3.3V +/-5%

INPUT3VSEL13

GPP_B23 XDP_PCH_S PI0_IO2PCH_SPI_IO2

INPUT3VSEL

@

R663

*4.7K_5%_2

@

R666

*20K_1%_2

+3V_DEEP_SUS

@

R705

*4.7K_5%_2

R706

100K_5%_2

2

(RSVD) CONSENT STRAP

High: DISABLE

Low: ENABLE

External pull-up is required.

SPI0_IO2

PCH_SPI_IO29

XTAL FREQUENCE SEL

High: 24MHZ

(25 MHZ WHEN XTAL FREQ DIVIDER NON ZERO)

Low: 38.4MHZ (DEFAULT)

WEAK INTERNAL PD 20K

MV

R723

0_5%_2

GPP_F0

CNV_BRI_DT12,33

R753

100K_5%_2

@

R743

*4.7K_5%_2

CNV_BRI_DT

1

+1.8V_DEEP_SUS

@

R353

*4.7K_5%_2

@

R337

*20K_1%_2

TP92

10

@

ESPI OR EC LESS

HIGH: ESPI IS DISABLED

LOW: ESPI SELECTED

WEAK INTERNAL PD 20K

MV

R755

0_5%_2

@

R347

*4.7K_5%_2

R334

20K_1%_2

GPP_C5/SML0ALERT#

B B

GPP_C59 GPP_E64

(RSVD) BOOT HALT XTAL INPUT FREQUENCY [1]

High: DISABLE

Low: ENABLE

External pull-up is required.

SPI0_MOSI

PCH_SPI1_SI9,31,34

A A

PCH_SPI1_SI XDP_PCH_SPI0_SI

5

(RSVD) JTAG ODT DISABLE

High: JTAG ODT Enable

Low: JTAG ODT Disable

External pull-up is required.

GPP_E6

+3V_DEEP_SUS

R771

100K_5%_2

@

TP96

@

R778

*4.7K_5%_2

R760

100K_5%_2

@

R736

*4.7K_5%_2

(RSVD) ITP PMODE

High: DFXTESTMODE DISABLED(DEFAULT)

Low: DFXTESTMODE ENABLED

WEAK INTERNAL PU 20K

DBG_PMODE4

ITP_PMODE

4

MAF/SAF STRAP

High: SAF ENABLE

Low: MAF ENABLE

WEAK INTERNAL PD 20K

GPP_H2

GPP_H24

R300

1K_5%_2

@

@

R290

*20K_1%_2

TP34

Flash Descriptor Security Override

High: DISABLE

+3V_DEEP_SUS+3V_DEEP_SUS +3V_DEEP_SUS +3V_DEEP_SUS

@

R415

GPP_H2GPP_E6GPP_C5 ACZ_SDOUT

STRAP FOR SPI 1.8V/3.3V SELECTION

High: SPI voltage is 1.8V

Low: SPI voltage is 3.3V

*2.2K_5%_2

@

R408

*20K_1%_2

INTRUDER#

INTRUDER#13

3

Low: ENABLE

WEAK INTERNAL PD 20K

ME_WR#34

+3V_RTC+VCC1.05_OUT_FET

INTRUDER#

GPP_R2

ACZ_SDOUT13

R712

*1M_5%_2

R713

10K_5%_2

+1.8V_DEEP_SUS 5,14,33

+3V 2,6,9,11,12,13,17,20,22,25,26,27,28,30,31,32,33,34,35,37,38,39,40,41,42,43,44

+3V_S5 2,6,8,11,13,14,15,16,28,29,30,33,34,37,40,41

+3V_DEEP_SUS 9,14

+VCC1.05_OUT_FET 14,16

R679 1K_5%_2

@

R677

*4.7K_5%_2

2

XTAL INPUT FREQUENCY [0]

00: DIVIDE BYPASS

01: DIVIDE BY 2 (HVM: 38.4MHZ INPUT)

10: DIVIDE BY 10 (HVM: 250MHZ INPUT)

11: DIVIDE BY 4 (BI: 100MHZ INPUT)

( QUALIFIED BY DFXTESTMODE)

NO INTERNAL PU/PD

GPP_E109

GPP_E10

00: DIVIDE BYPASS

01: DIVIDE BY 2 (HVM: 38.4MHZ INPUT)

10: DIVIDE BY 10 (HVM: 250MHZ INPUT)

11: DIVIDE BY 4 (BI: 100MHZ INPUT)

( QUALIFIED BY DFXTESTMODE)

NO INTERNAL PU/PD

GPP_E119

GPP_E11

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ICL-U 9/14 (HW STRAP)

ICL-U 9/14 (HW STRAP)

ICL-U 9/14 (HW STRAP)

Date: Sheet of

Date: Sheet of

Date: Sheet of

HVM ONLY

R747

20K_1%_2

+3V_DEEP_SUS

@

R735

*20K_1%_2

@

R725

*20K_1%_2

+1.8V_DEEP_SUS

HVM ONLY

R750

20K_1%_2

1

+3V_DEEP_SUS

@

R739

*20K_1%_2

ZAUI

ZAUI

ZAUI

10 47Monday, November 04, 2019

10 47Monday, November 04, 2019

10 47Monday, November 04, 2019

+1.8V_DEEP_SUS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

3A

3A

3A

Page 11

5

Vinafix.com

+3V 2,6,9,10,12,13,17,20, 22,25,26,27,28,30,31,32,33,34,35,37,38,39,40,41,42,43,44

+3V_S5 2,6,8,10,13,14,15,16,28,29,30,33,34,37,40,41

dGPU

D D

LAN

WLAN

HDD

ODD

SATA/PCIE

For SSD_DET

High: SSD SATA IF

+3V

Low: SSD PCIE IF

R253 *10K_5%_2

+3V

R742*10K_1%_2

R737* 10K_5%_4

C C

+3V_S5

PCI-E Port Mapp ing Table

PCI-E Port

Port5

R258* 10K_1%_2

R768 10K_5%_2

R272 10K_5%_2

R741 *10K_1%_2

SATAGP0

R250 *10K_1%_2

SATAGP1

Function

dGPU

Port6

Port7

Port8

Port9

B B

Port10

Port11

Port12

Port13

Port14

Port15

Port16

dGPU

dGPU

LAN

WLAN

HDD

ODD

PCIE SSDx4

PCIE SSDx4

PCIE SSDx4

PCIE SSDx4

/SATA SSD

NGFF_SATA_DET

DEVSLP0

DEVSLP1

DEVSLP2

USB_OC0#

USB_OC3#

CLK RQ Port

Port0

Port1dGPU

Port2

Port3

Port4

Port5

SSD

Function

VGA

SSD

Un-used

Un-used

LAN

WLAN

PEG_RXN719

PEG_RXP719

PEG_TXN719

PEG_TXP719

PEG_RXN819

PEG_RXP819

PEG_TXN819

PEG_TXP819

PCIE_RXN9_LAN28

PCIE_RXP9_LAN28

PCIE_TXN9_LAN28

PCIE_TXP9_LAN28

PCIE_RXN10_WLAN33

PCIE_RXP10_WLAN33

PCIE_TXN10_WLAN33

PCIE_TXP10_WLAN33

SATA_RXN0_HDD32

SATA_RXP0_HDD32

SATA_TXN0_HDD32

SATA_TXP0_HDD32

SATA_RXN1A_ODD32

SATA_RXP1A_ODD32

SATA_TXN1A_ODD32

SATA_TXP1A_ODD32

PCIE_RXN13_SSD33

PCIE_RXP13_SSD33

PCIE_TXN13_SSD33

PCIE_TXP13_SSD33

PCIE_RXN14_SSD33

PCIE_RXP14_SSD33

PCIE_TXN14_SSD33

PCIE_TXP14_SSD33

PCIE_RXN15_SSD33

PCIE_RXP15_SSD33

PCIE_TXN15_SSD33

PCIE_TXP15_SSD33

PCIE_RXN16_SSD33

PCIE_RXP16_SSD33

PCIE_TXN16_SSD33

PCIE_TXP16_SSD33

USB_OC0#24

0.1u/16V_2C654

TP32

NGFF_SATA_DET33

DEVSLP032

DEVSLP233

C621 0.22u/10V_2

C618 0.22u/10V_2

C614 0.22u/10V_2

C617 0.22u/10V_2

C611 0.1u/16V_2