Page 1

5

4

3

2

1

Dummy when use EZ4

Dummy when no EZ4

Dummy when use 10/100

Dummy when use Giga

D D

Dummy when use UMA

Dummy when use Discrete

Dummy when use SATA

Dummy when use IDE

CLK GEN

IDT CV137

LEDs

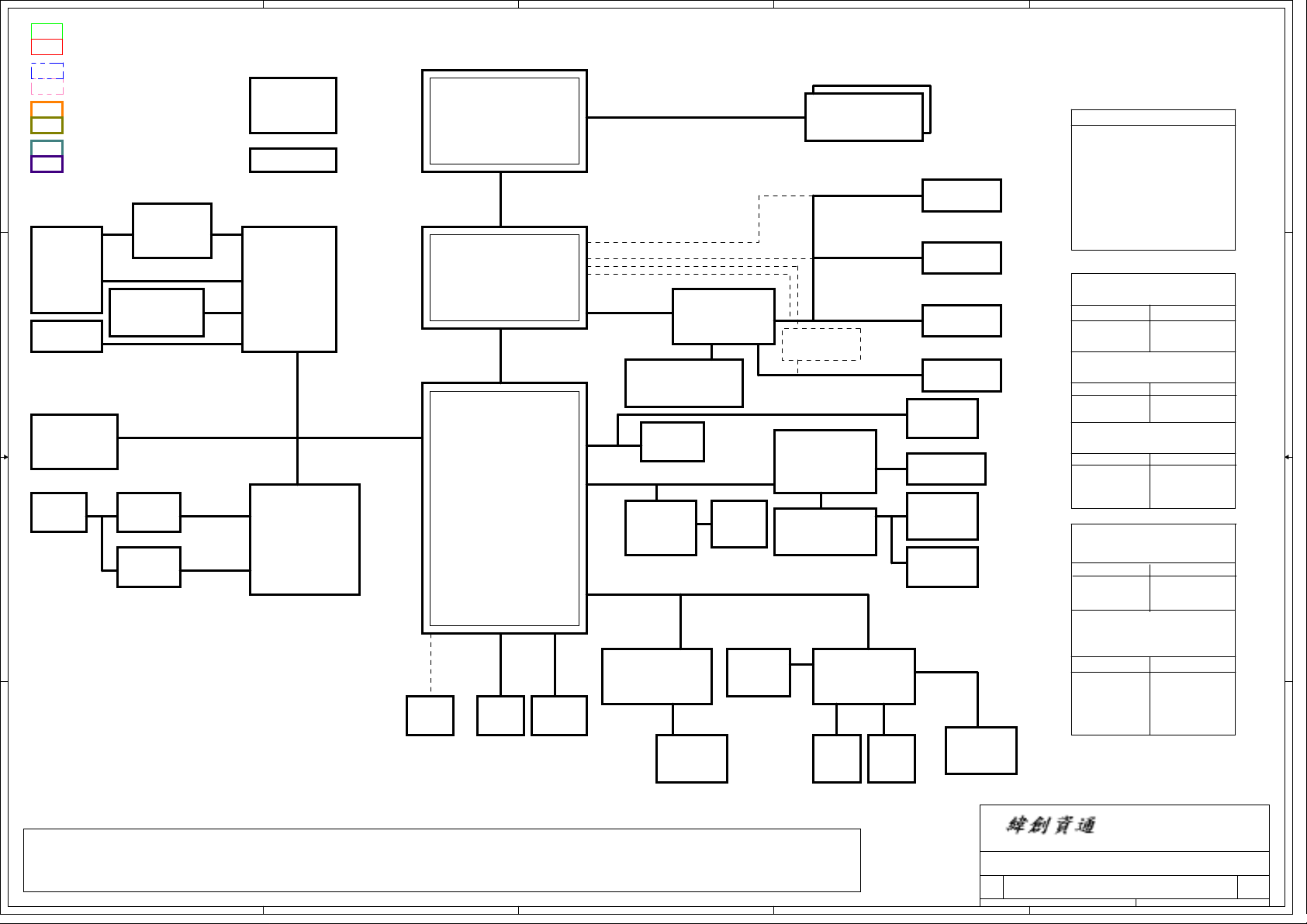

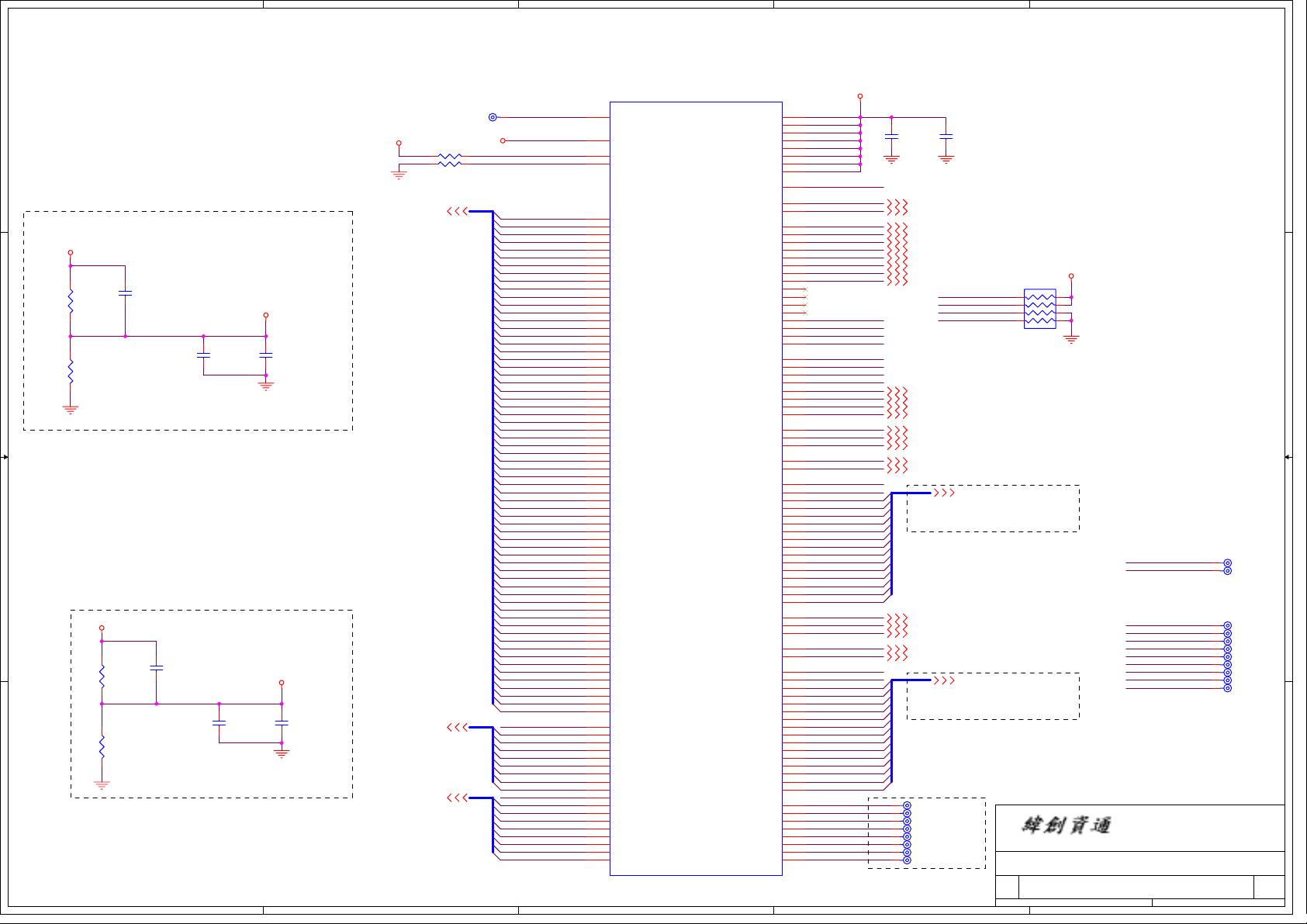

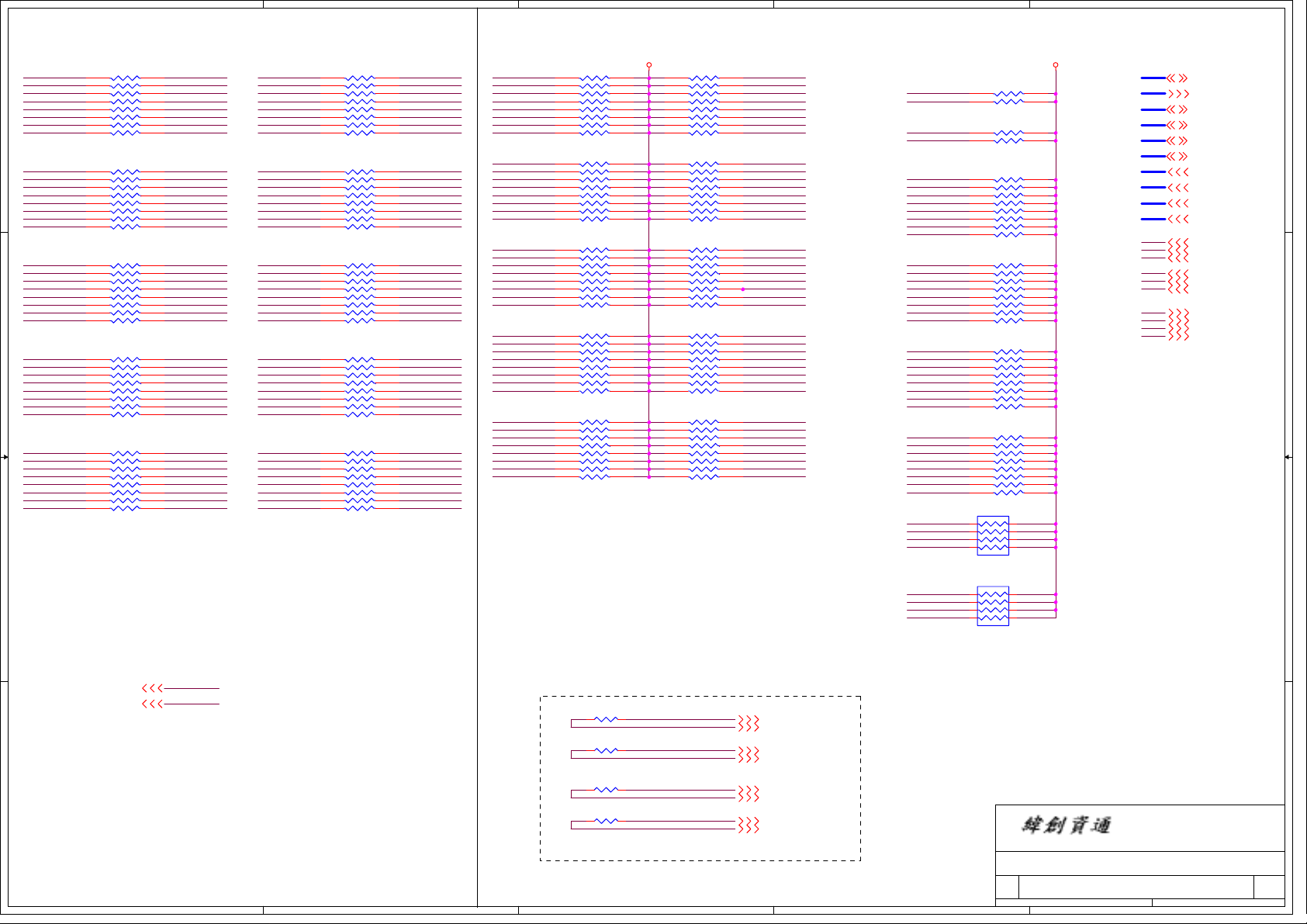

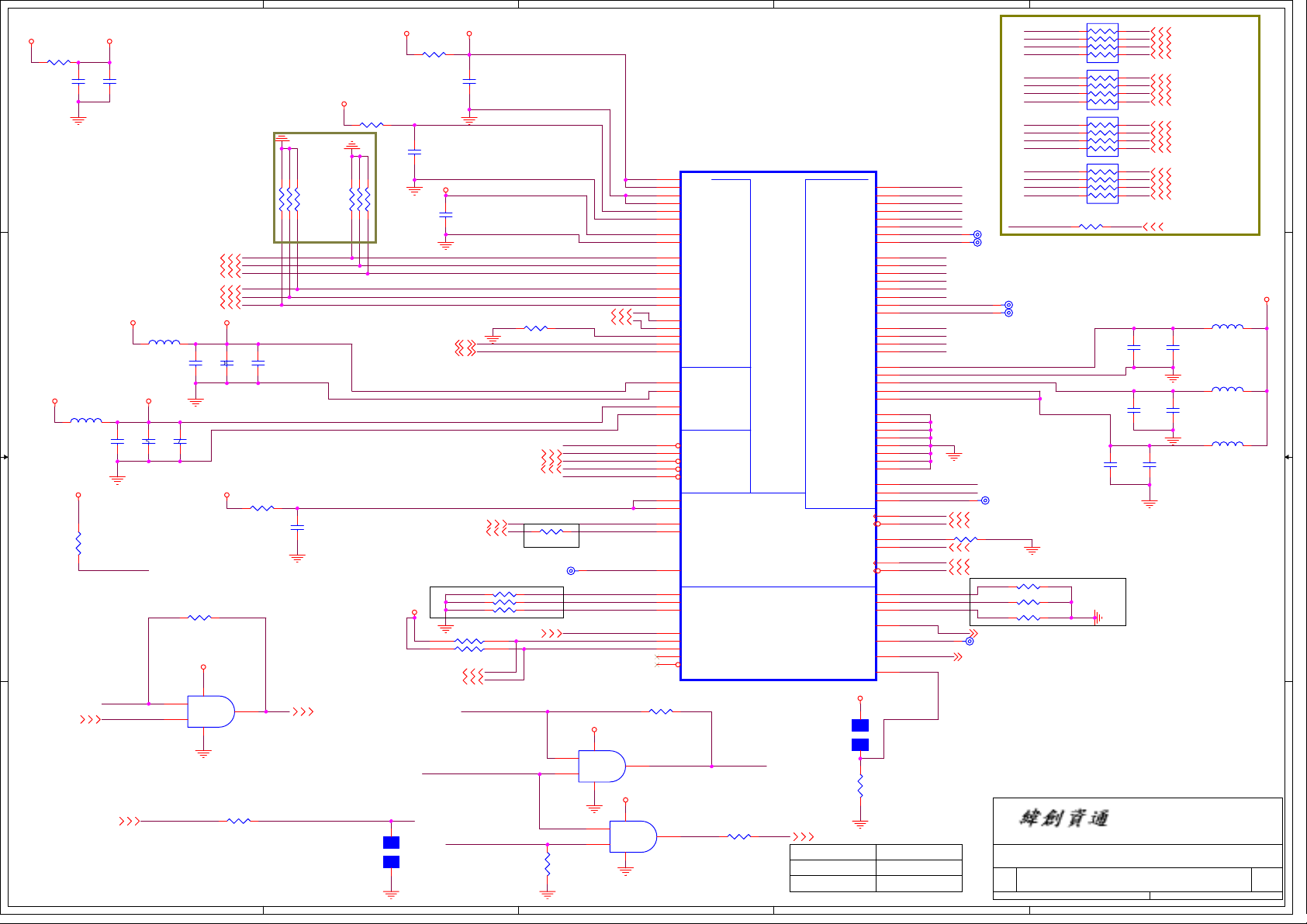

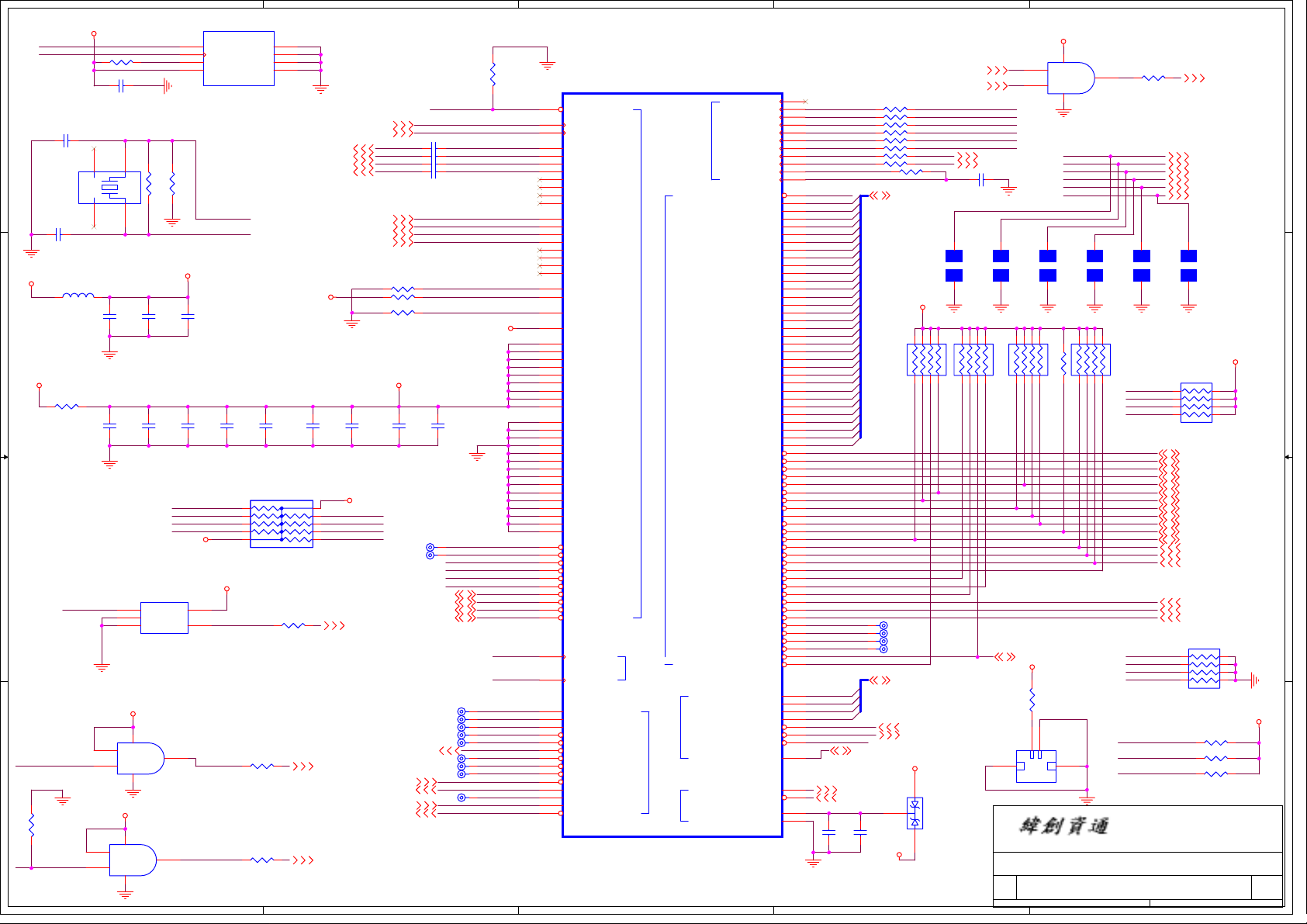

Bolsena Block Diagram

AMD CPU

3

17

35W/25W

4,5,6,7

DDR 333/400

HyperTransport

PWR SW

TSP2220A

PCMCIA

SLOT

Support

TypeII

28

1394 4pin

Conn

C C

28

PCMCIA I/F

MS/MSpro

SDIO/MMC/SD

5 in 1

28

28

Mini-PCI

802.11a/b/g

31

RJ45

30

TXFM

1000Mb

30

TI

PCI 7411

1* Slot Cardbus

1* 1394

26,27

PCI LAN

Realtek

AGTL+ CPU I/F + UMA

PCI Bus / 33MHz

PCI

RTL8110SBL

B B

TXFM

10/100Mb

30

1000/100/10

RTL8100C

100/10

29

ATA 133

6.4GB/S 16b/8b

ATI

RS480M

11,12,13,14

PCI-Express

x2

ATI

SB400

ACPI 2.0

18,19,20,21,22

6xUSB 2.0

6-CH

AC97 2.2

LPC I/F

PCI Express x16

VRAM x4

HY5DS573222F

USB x 4

AC97

MODEM

MDC Card

ATI

M26/M24

50,51,52

53,54

24

RJ11

CONN

91.4C501.001 (04243)

SiI1162

CODEC

ALC655

OP AMP

29

G1421

LPC Bus / 33MHz

200-PIN DDR SODIMM

DDR x2

8,9,10

SVIDEO/COMP

LVDS

RGB CRT

15

TMDS

BlueTooth

miniUSB

32

3324

TVOUT

LCD

CRT

DVI-D

(EZ4 only )

Line In

MIC In

Line Out

Int. SPKR

24

33

33

33

16

17

16

15

PCB Layer Stackup

L1: Signal 1

L2: GND

L3: Signal 2

L4: Signal 3

L5: VCC

L6: Signal 4

?modify power block

Battery Charger

INPUTS

AD+

BAT+

SYSTEM DC/DC

INPUT

DCBATOUT

SYSTEM DC/DC

INPUT

DCBATOUT 2D5V_S3

CPU V_CORE

INPUT

DCBATOUT

SYSTEM POWER

OUTPUTS

DCBATOUT

OUTPUT

5V_S5 ,

3D3V_S5

OUTPUT

1D8V_S5

1D2V_S0

OUTPUT

VCC_CORE_S0

48

44

45,46

42,43

47

37

Thermal

& Fan

G792

23

SATA

25

PIDE

HDD

25

SIDE

DVD/

CD-RW

NS SIO

PC87392

25

FIR

TFDU6102

A A

37

KBC

KB3910

Touch

Pad

35 35

Int.

KB

XBUS

34

ISA ROM

36

Port Replicator 4 (124 PIN)

AC

IN

RJ45-11

SEARIAL

PORT

5

CRT

PRINTER

PS2

4

MIC

LINE IN

LINE

OUT

TV

OUT

DVI PCIeX2 SMBUS

3

2

Title

BLOCK DIAGRAM

Size Document Number Rev

A3

Bolsena

Date: Sheet of

INPUT

2D5V_S3

DCBATOUT

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

OUTPUT

1D25V_S3

5V_AUX_S5

158Tuesday, December 28, 2004

1

SA

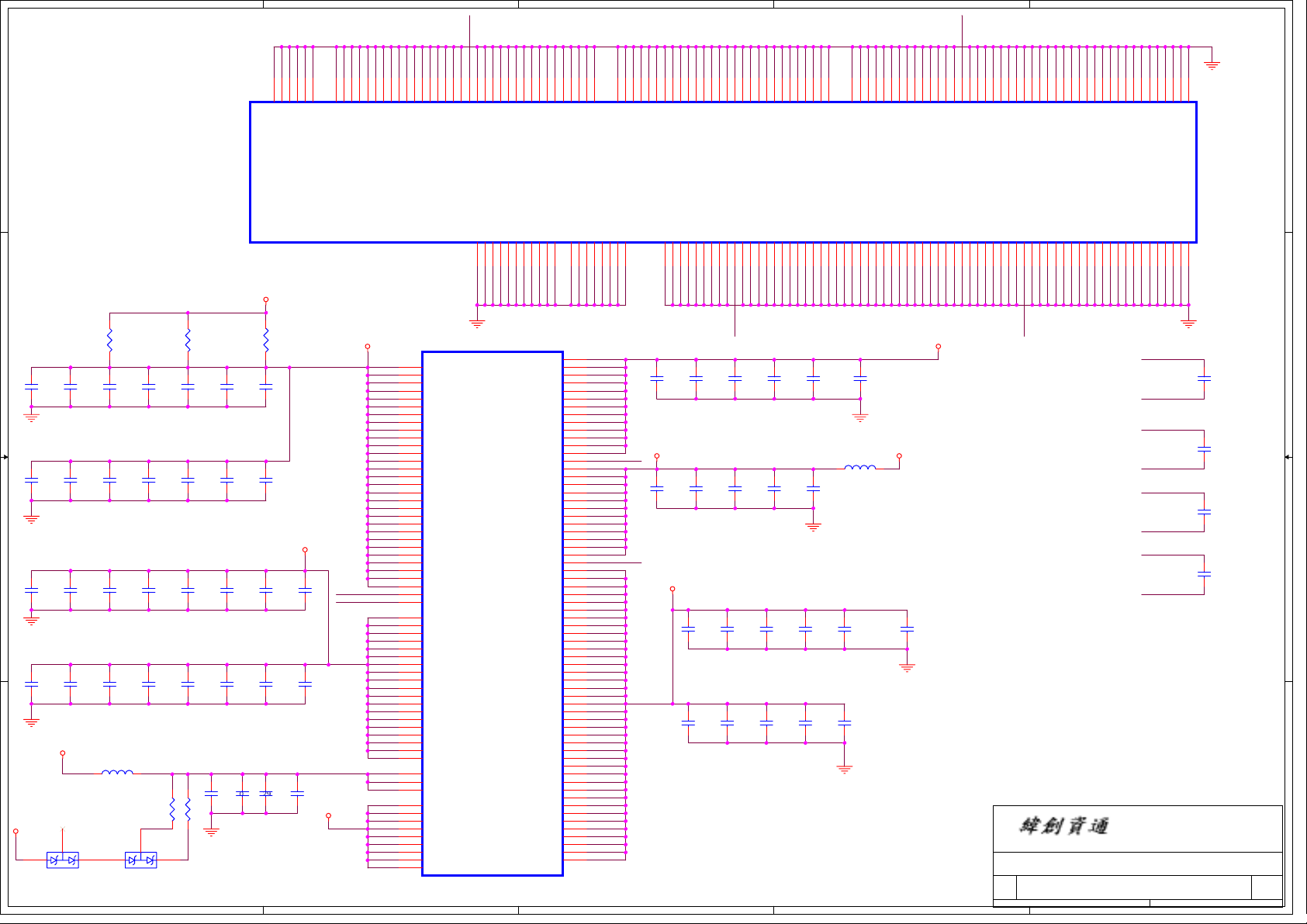

Page 2

5

D D

C C

4

3

2

1

B B

A A

5

4

3

2

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CHANGE HISTORY

Size Document Number Rev

Bolsena SA

A3

Date: Sheet

258Tuesday, December 28, 2004

1

of

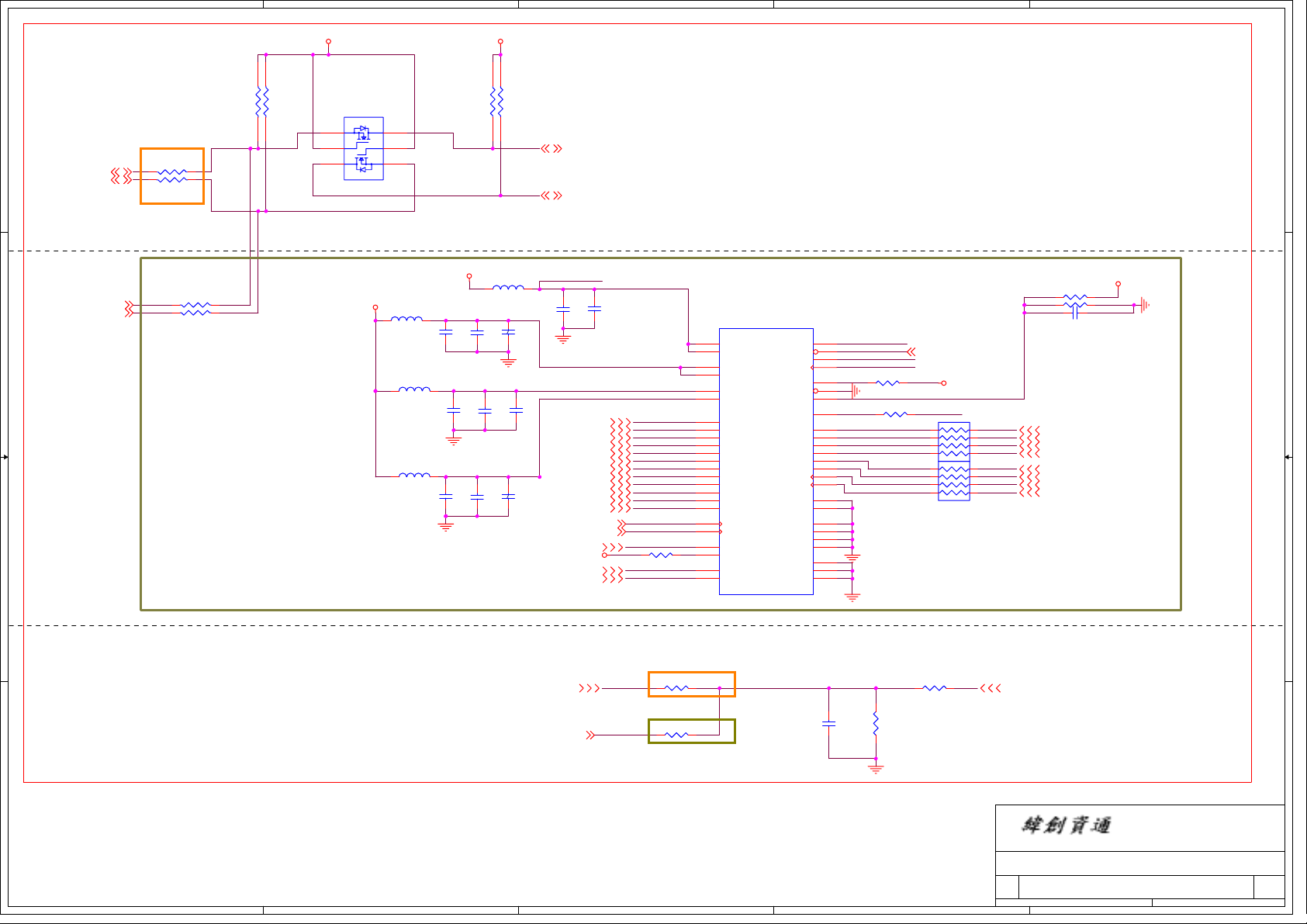

Page 3

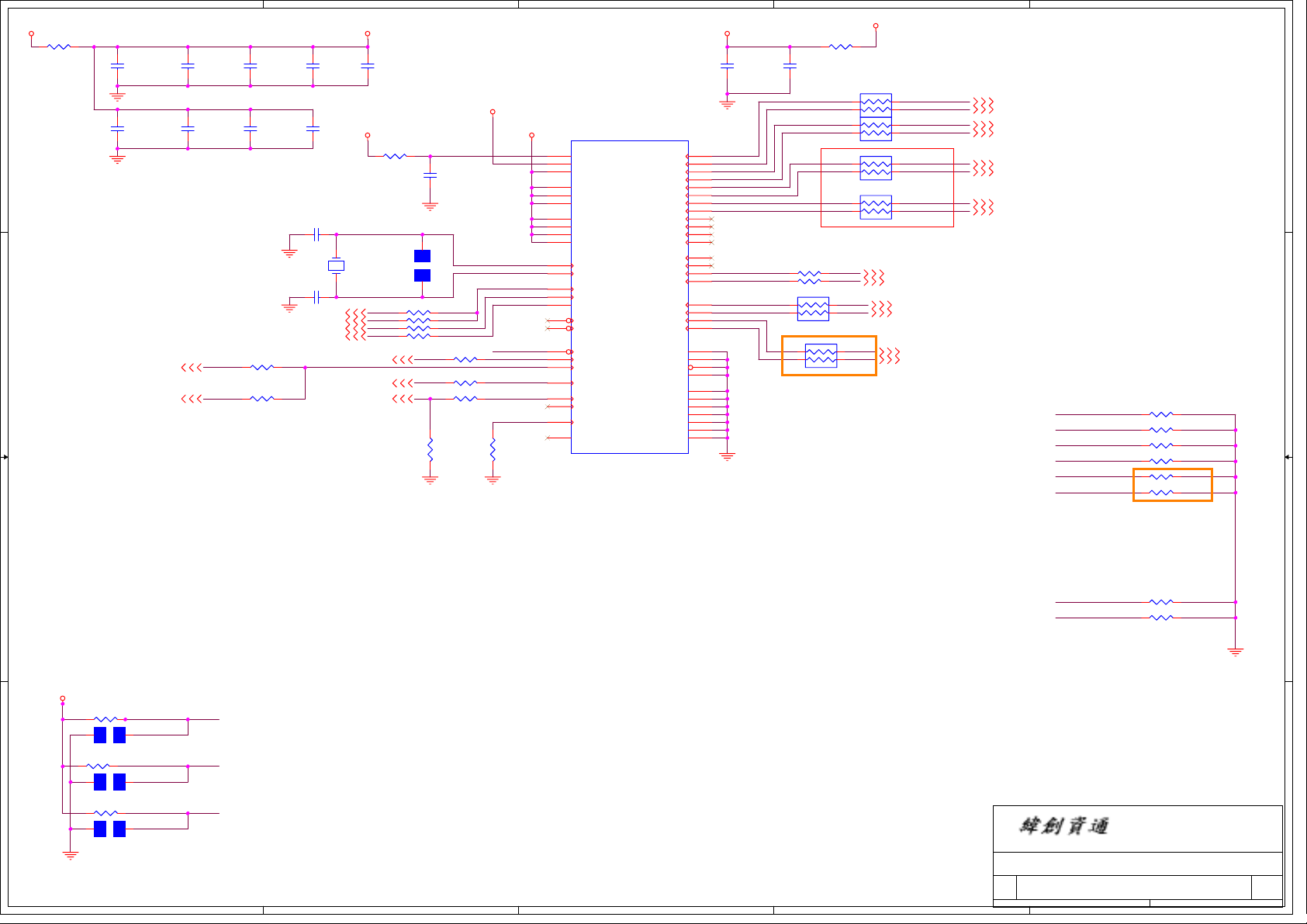

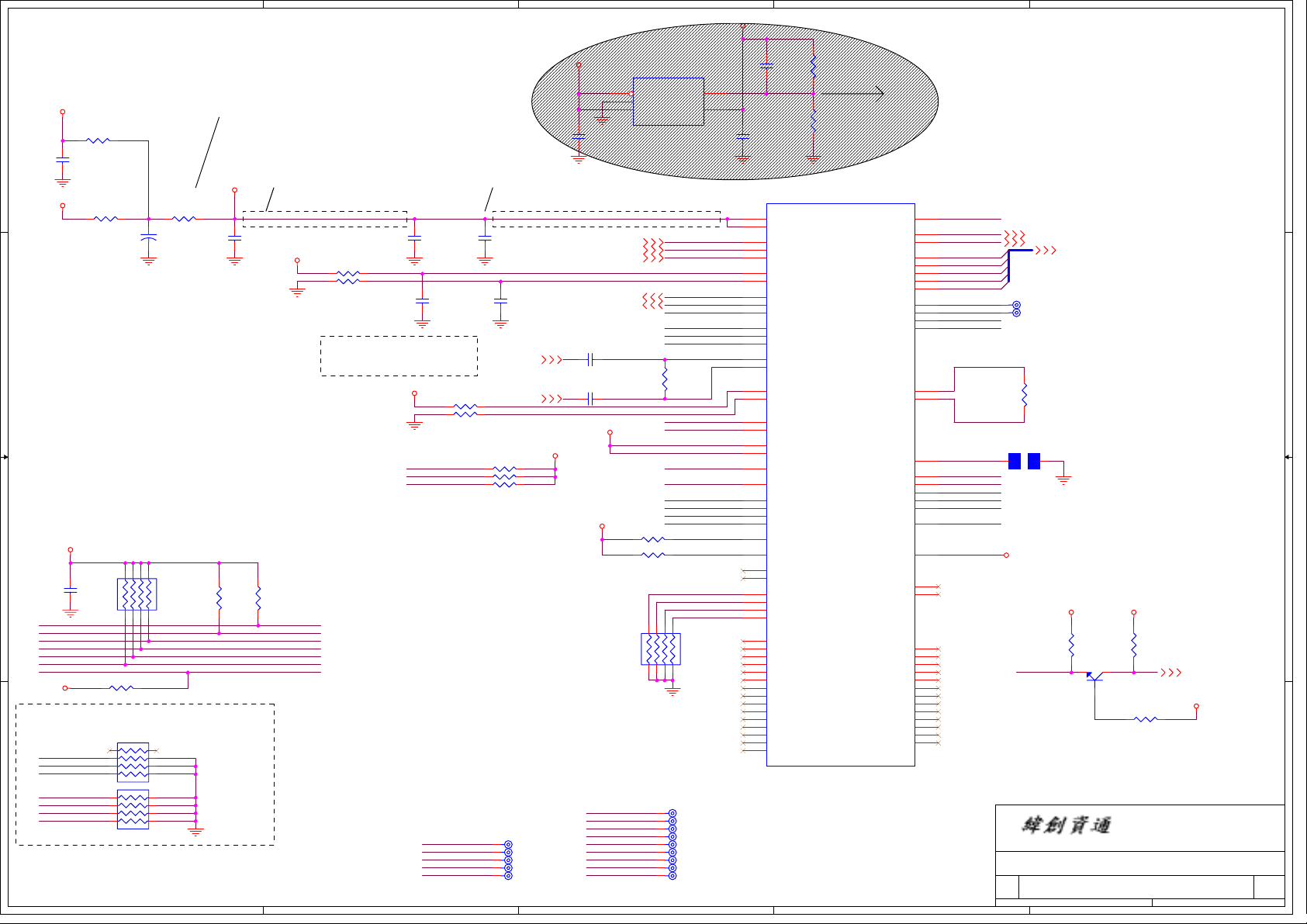

A

3D3V_S0

L1

1 2

0R3-U

4 4

3 3

SB_OSC_CLK21

CLK14_AUDIO32

12

12

C1

SCD1U16V

C8

SCD1U16V

12

12

C2

SCD1U16V

C9

SCD1U16V

12

C3

SCD1U16V

12

C10

SCD1U16V

1 2

1 2

CLK48_CARDBUS26

CLK48_USB21

SMBC_SB8,21,57

SMBD_SB8,21,57

R8

33R2

R11

33R2

12

12

1 2

1 2

CLK14_NB13

CLK14_SIO37

C4

SCD1U16V

C11

SCD1U16V

C13

SC33P50V2JN

X1

X-14D318MHZ-1-U1

1 2

C14

SC33P50V2JN

B

12

C5

SC22U10V6ZY-U

3D3V_CLK_VDDA

3D3V_S0 3D3V_CLK_VDD

3D3VDD48_S0

L3

1 2

0R3-U

12

C12

SC2D2U16V5ZY

XI_CLK

XO_CLK

HTREF_CLK13

12

DY

R4

1 2

R5

1 2

R7

1 2

R6

1 2

R2

DUMMY-R3

22R2

22R2

0R2-0

0R2-0

1 2

1 2

1 2

12

R15

49D9R2F

USB_48M

SMBC_CLK

SMBD_CLK

R9

33R2

R10

33R2

R12

33R2

IREF_CLKGEN

12

FS2

FS1

FS0

CLK_REF2

CLK_HTT66

R16

475R2F

U1

3

VDD_48

39

VDDA

32

VDD_SRC

21

VDD_SRC

14

VDD_SRC

35

VDD_SRC

56

VDD_REF

51

VDD_PC1

43

VDD_CPU

48

VDD_HTT

1

XIN

2

XOUT

4

USB_48

7

SCL

8

SDA

10

CLKREQ0#

11

CLKREQ1#

9

SEL24/24_48#

53

REF1

54

REF0

52

REF2

47

HTT66

50

PCI0

37

IREF

6

NC#6

IDTCV137PAG

C

SRCC0

SRCT0

SRCC3

SRCT3

SRCC4

SRCT4

SRCC5

SRCT5

SRCC6

SRCT6

SRCC7

SRCT7

CPUC1

CPUT1

CPUC0

CPUT0

SRCC1

SRCT1

SRCC2

SRCT2

VSS_SRC

VSS_SRC

RESET#

TURBO1

VSS_CPU

VSS_PCI

VSS_HTT

VSS_SRC

VSS_48

VSS_REF

VSSA

33

34

25

24

23

22

19

18

17

16

13

12

40

41

44

45

29

30

28

27

36

20

15

26

42

49

46

31

38

5

55

3D3V_CLK_VDDA3D3V_CLK_VDD

12

C6

SCD1U16V

SRC_CLK0#

SRC_CLK0

SRC_CLK3#

SRC_CLK3

SRC_CLK4#

SRC_CLK4

SRC_CLK5#

SRC_CLK5

CPUCLKJ_CY

CPUCLK_CY

ATI_CLK0#

ATI_CLK0

ATI_CLK1#

ATI_CLK1

3D3V_S0

L2

1 2

12

1 2

1 2

RN5

2 3

1

SRN33-2-U2

1

2 3

0R3-U

C7

SC22U10V6ZY-U

RN1

2 3

1

RN2

SRN33-2-U2

1

2 3

SRN33-2-U2

RN3

1

2 3

SRN33-2-U2

RN4

1

2 3

SRN33-2-U2

Dummy when no EZ4

R1

15R2J

R3

15R2J

4

RN6

4

SRN33-2-U2

Dummy when use UMA

D

4

4

4

4

CPUCLK# 6

CPUCLK 6

NBSRC_CLK# 13

NBSRC_CLK 13

GFX_CLK# 49

GFX_CLK 49

SBLINK_CLK# 13

SBLINK_CLK 13

SBSRC_CLK# 18

SBSRC_CLK 18

CLK_PCIE_DOCK1# 57

CLK_PCIE_DOCK1 57

CLK_PCIE_DOCK2# 57

CLK_PCIE_DOCK2 57

SBLINK_CLK#

SBLINK_CLK

SBSRC_CLK#

SBSRC_CLK

GFX_CLK#

GFX_CLK

E

1 2

1 2

1 2

1 2

1 2

1 2

R13

49D9R2F

R14

49D9R2F

R17

49D9R2F

R18

49D9R2F

R19

49D9R2F

R20

49D9R2F

Dummy when use UMA

2 2

NBSRC_CLK#

NBSRC_CLK

3D3V_CLK_VDD

1 1

1 2

1 2

1 2

1 2

1 2

1 2

R23

2K2R2

R24

DUMMY-R2

R25

2K2R2

R26

DUMMY-R2

R27

2K2R2

R28

DUMMY-R2

DY

FS0

DY

DY

FS1

DY

DY

FS2

DY

A

B

C

D

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet

CLKGEN_IDTCV137

Bolsena

1 2

1 2

E

R21

49D9R2F

R22

49D9R2F

358Tuesday, December 28, 2004

SA

of

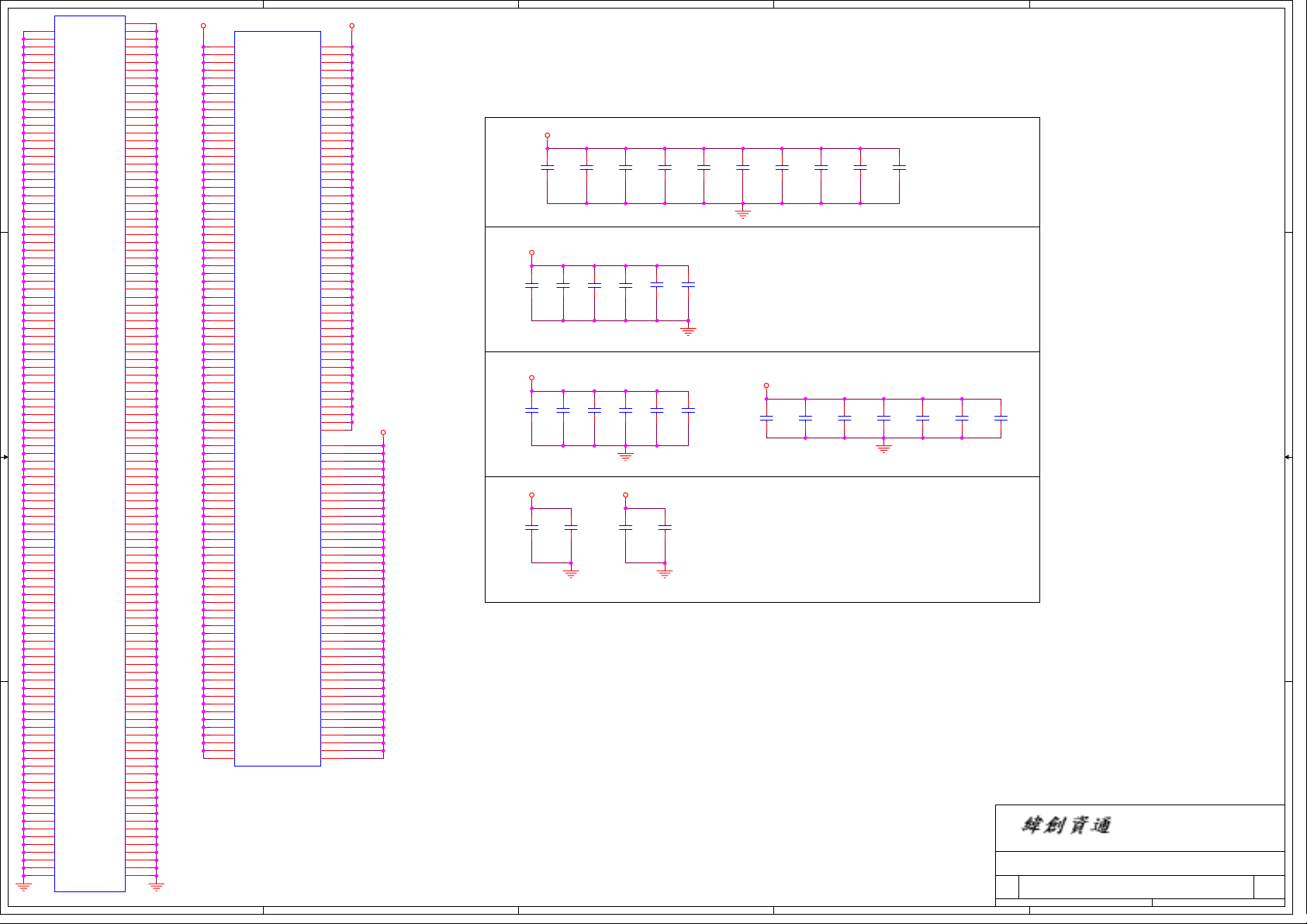

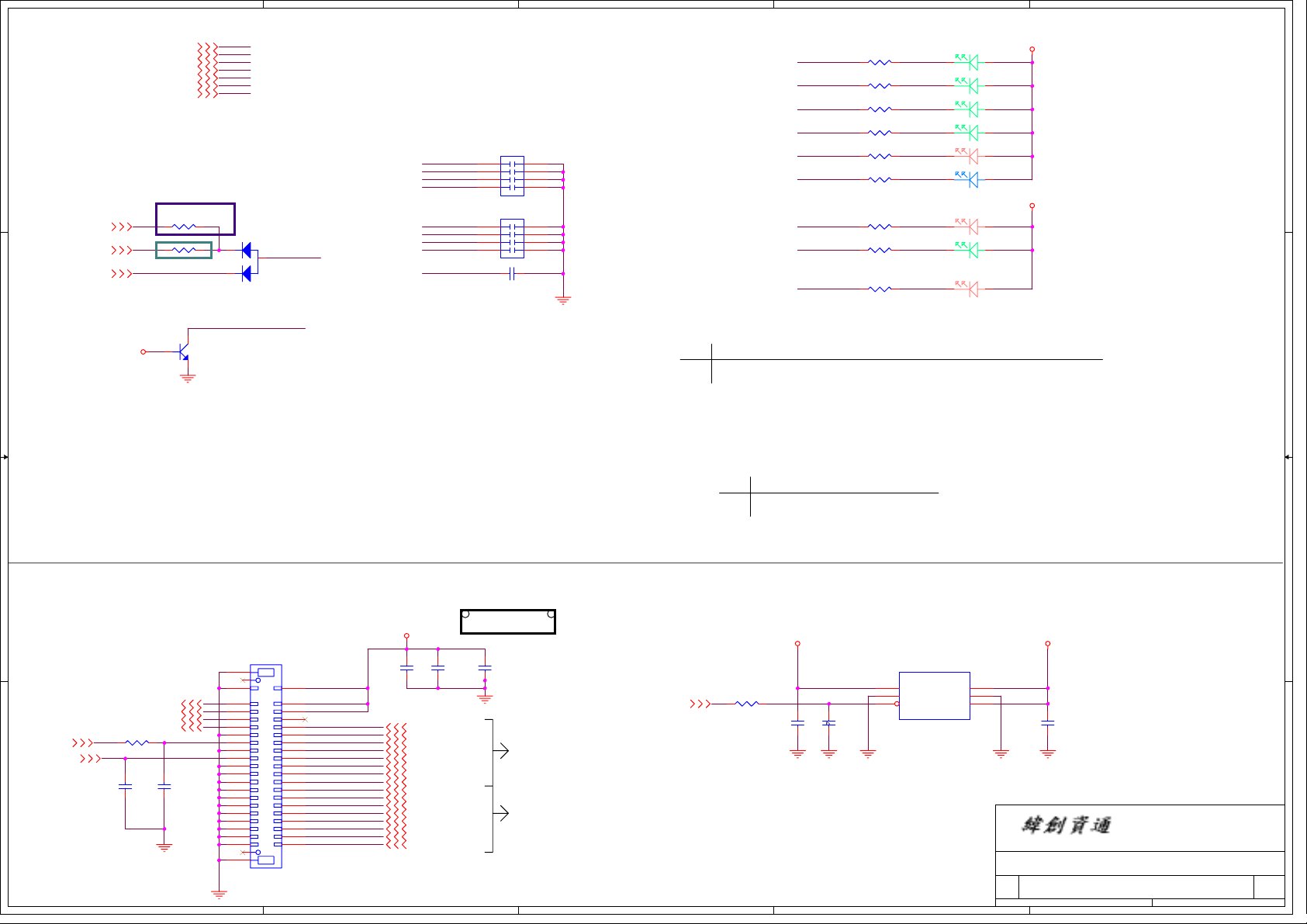

Page 4

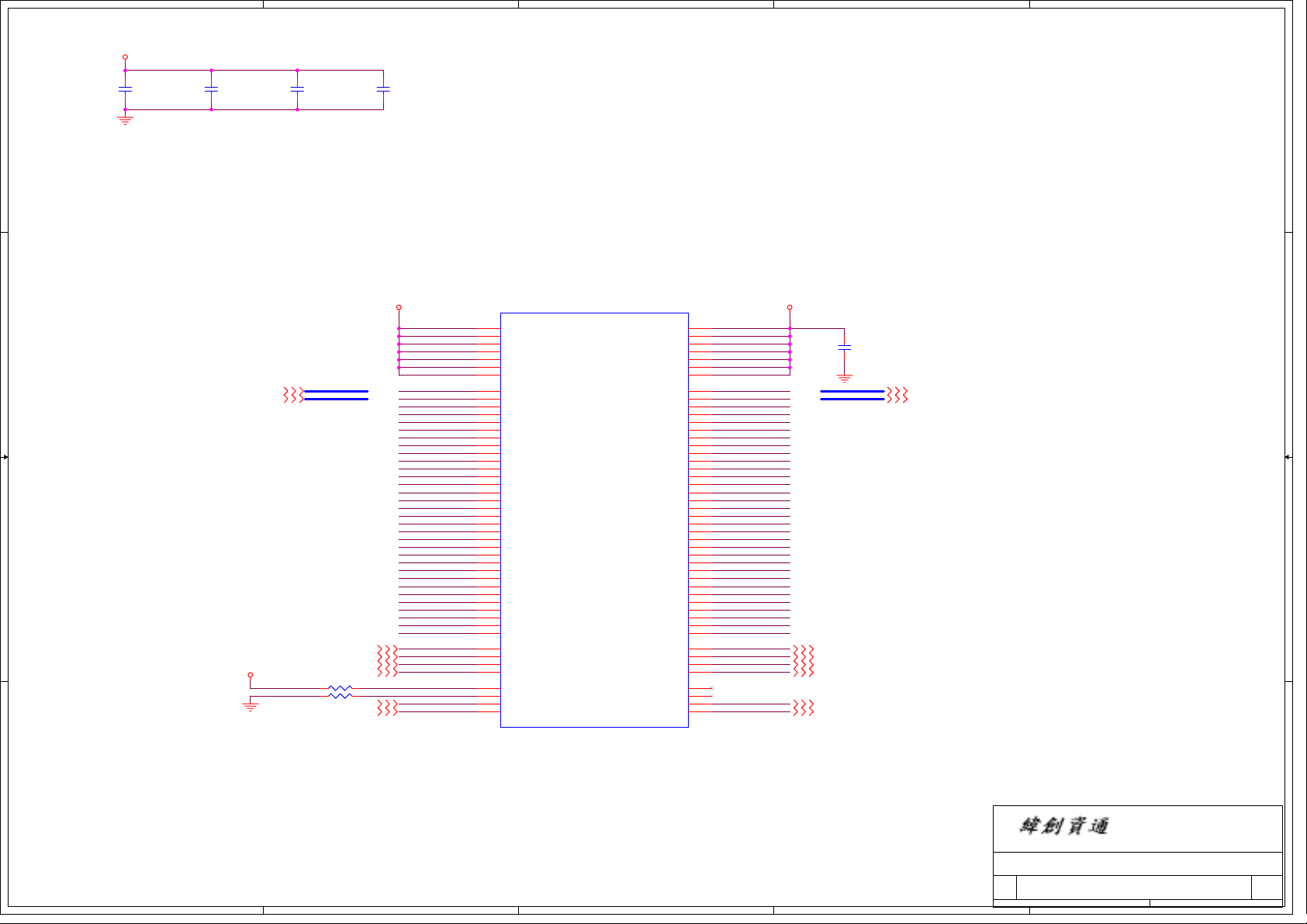

A

1D2V_HT0A_S0

B

C

D

E

12

C19

SCD22U16V3ZY

4 4

3 3

12

C20

SCD22U16V3ZY

NB0CADOUT[15..0]11

NB0CADOUTJ[15..0]11

12

C21

SCD22U16V3ZY

Used SideB Power Plane

2 2

NB0HTTCLKOUT111

NB0HTTCLKOUTJ 111

1D2V_HT0B_S0

NB0HTTCLKOUT011

NB0HTTCLKOUTJ 011

1 2

1 2

NB0HTTCTLOUT11

NB0HTTCTLOUTJ11

12

C22

SCD22U16V3ZY

HTT for CPU sideA

Transmit power

and NB sideA Receive

power

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

U2A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

62.10030.041

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

CPUCADOUT15

CPUCADOUTJ15

CPUCADOUT14

CPUCADOUTJ14

CPUCADOUT13

CPUCADOUTJ13

CPUCADOUT12

CPUCADOUTJ12

CPUCADOUT11

CPUCADOUTJ11

CPUCADOUT10

CPUCADOUTJ10

CPUCADOUT9

CPUCADOUTJ9

CPUCADOUT8

CPUCADOUTJ8

CPUCADOUT7

CPUCADOUTJ7

CPUCADOUT6

CPUCADOUTJ6

CPUCADOUT5

CPUCADOUTJ5

CPUCADOUT4

CPUCADOUTJ4

CPUCADOUT3

CPUCADOUTJ3

CPUCADOUT2

CPUCADOUTJ2

CPUCADOUT1

CPUCADOUTJ1

CPUCADOUT0

CPUCADOUTJ0

CPUHTTCLKOUT1

CPUHTTCLKOUTJ1

CPUHTTCLKOUT0

CPUHTTCLKOUTJ0

CPUHTTCTLOUT0

CPUHTTCTLOUTJ0

1D2V_HT0A_S0 1D2V_HT0B_S0

NB0CADOUT15

NB0CADOUTJ15

NB0CADOUT14

NB0CADOUTJ14

NB0CADOUT13

NB0CADOUTJ13

NB0CADOUT12

NB0CADOUTJ12

NB0CADOUT11

NB0CADOUTJ11

NB0CADOUT10

NB0CADOUTJ10

NB0CADOUT9

NB0CADOUTJ9

NB0CADOUT8

NB0CADOUTJ8

NB0CADOUT7

NB0CADOUTJ7

NB0CADOUT6

NB0CADOUTJ6

NB0CADOUT5

NB0CADOUTJ5

NB0CADOUT4

NB0CADOUTJ4

NB0CADOUT3

NB0CADOUTJ3

NB0CADOUT2

NB0CADOUTJ2

NB0CADOUT1

NB0CADOUTJ1

NB0CADOUT0

NB0CADOUTJ0

NB0HTTCLKOUT1

NB0HTTCLKOUTJ1

NB0HTTCLKOUT0

NB0HTTCLKOUTJ0

R29

49D9R3F

R30

49D9R3F

CPUHTTCTLIN1

CPUHTTCTLINJ1

NB0HTTCTLOUT

NB0HTTCTLOUTJ

HTT for CPU sideB

Receive power

and NB sideA

Transmit power

12

C23

SC4D7U10V5ZY

Used SideA Power Plane

CPUHTTCLKOUT1 11

CPUHTTCLKOUTJ1 11

CPUHTTCLKOUT0 11

CPUHTTCLKOUTJ0 11

CPUHTTCTLOUT0 11

CPUHTTCTLOUTJ0 11

LAYOUT: Place bypass cap on topside of board near

HTT power pins that are not connected directly to

downstream HTT device, but connected internally to

other HTT power pins.

CPUCADOUT[15..0] 11

CPUCADOUTJ[15..0] 11

By ME requset U11 P/N:

1 1

Main 62.10030.041

Second 62.10053.191

Third 62.10053.201

A

B

C

BGA754-SKT-U

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

D

Date: Sheet

CPU(1/4)_HyperTransport I/F

Bolsena

458Tuesday, December 28, 2004

E

of

SA

Page 5

A

B

C

D

E

U2B

MEMRESET_L

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

C

VTT_A

VTT_A

VTT_A

VTT_A

VTT_B

VTT_B

VTT_B

VTT_B

MEMCKEA

MEMCKEB

NC_E13

NC_C12

NC_E14

NC_D12

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

BGA754-SKT-U

4 4

2D5V_S3

VREF_DDR_CLAW

R32

1 2

34D8R2F

R31

1 2

34D8R2F

TP1

TPAD30

DDRVTT_SENSE

MEMZN

MEMZP

AE13

AG12

D14

C14

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

VREF_DDR_MEM

NOTE: Test wi th p assive probes only.

M_DATA[63..0]9

2D5V_S3

3 3

NOTE: Install to bypass op-amp

12

12

R33

100R3F

R34

100R3F

12

C27

SCD1U

12

VREF_DDR_MEM

C28

SCD1U

12

C25

SC1000P50V2KX

LAYOUT: L ocate close to D IMMs.

NOTE: Remove to bypass op-amp

2 2

VREF_DDR_CLAW

2D5V_S3

12

12

1 1

12

R35

100R3

R36

100R3

C29

SCD1U

12

C30

SCD1U

VREF_DDR_CLAW

LAYOUT: Locate close to CPU .

A

12

C31

SC1000P50V2KX

M_ADM[7..0]9

M_DQS[7..0]9

B

M_DATA63

M_DATA62

M_DATA61

M_DATA60

M_DATA59

M_DATA58

M_DATA57

M_DATA56

M_DATA55

M_DATA54

M_DATA53

M_DATA52

M_DATA51

M_DATA50

M_DATA49

M_DATA48

M_DATA47

M_DATA46

M_DATA45

M_DATA44

M_DATA43

M_DATA42

M_DATA41

M_DATA40

M_DATA39

M_DATA38

M_DATA37

M_DATA36

M_DATA35

M_DATA34

M_DATA33

M_DATA32

M_DATA31

M_DATA30

M_DATA29

M_DATA28

M_DATA27

M_DATA26

M_DATA25

M_DATA24

M_DATA23

M_DATA22

M_DATA21

M_DATA20

M_DATA19

M_DATA18

M_DATA17

M_DATA16

M_DATA15

M_DATA14

M_DATA13

M_DATA12

M_DATA11

M_DATA10

M_DATA9

M_DATA8

M_DATA7

M_DATA6

M_DATA5

M_DATA4

M_DATA3

M_DATA2

M_DATA1

M_DATA0

M_ADM8

M_ADM7

M_ADM6

M_ADM5

M_ADM4

M_ADM3

M_ADM2

M_ADM1

M_ADM0

M_DQS8

M_DQS7

M_DQS6

M_DQS5

M_DQS4

M_DQS3

M_DQS2

M_DQS1

M_DQS0

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

1D25V_S3

MEMRESET#

M_CKE#0

M_CKE#1

M_CLK7

M_CLK#7

M_CLK6

M_CLK#6

M_CLK5

M_CLK#5

M_CLK4

M_CLK#4

M_CLK1

M_CLK#1

M_CLK0

M_CLK#0

M_CS#7

M_CS#6

M_CS#5

M_CS#4

M_CS#3

M_CS#2

M_CS#1

M_CS#0

M_ARAS#

M_ACAS#

M_AWE#

M_ABS#1

M_ABS#0

RSVD_M_AA15

RSVD_M_AA14

M_AA13

M_AA12

M_AA11

M_AA10

M_AA9

M_AA8

M_AA7

M_AA6

M_AA5

M_AA4

M_AA3

M_AA2

M_AA1

M_AA0

M_BRAS#

M_BCAS#

M_BWE#

M_BBS#1

M_BBS#0

RSVD_M_BA15

RSVD_M_BA14

M_BA13

M_BA12

M_BA11

M_BA10

M_BA9

M_BA8

M_BA7

M_BA6

M_BA5

M_BA4

M_BA3

M_BA2

M_BA1

M_BA0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

12

12

C24

SCD1U

For REGISTED DIMM Only

UNBUFFER DIMM NC

TP16

TP15

TPAD30

TP18

TPAD30

TPAD30

TP17

TP20

TPAD30

TP19

TPAD30

TPAD30

TP22

TPAD30

TP21

TPAD30

D

C26

SC1000P50V2KX

M_CKE#0 8,9

M_CKE#1 8,9

M_CLK7 8,9

M_CLK#7 8,9

M_CLK6 8,9

M_CLK#6 8,9

M_CLK5 8,9

M_CLK#5 8,9

M_CLK4 8,9

M_CLK#4 8,9

M_CLK#1

M_CLK#0

M_CLK1

M_CLK0

M_CS#3 8,9

M_CS#2 8,9

M_CS#1 8,9

M_CS#0 8,9

M_ARAS# 8,9

M_ACAS# 8,9

M_AWE# 8,9

M_ABS#1 8,9

M_ABS#0 8,9

M_AA[13..0] 8,9

AMD suggested M_AA13

connect to DIMM pin123

M_BRAS# 8,9

M_BCAS# 8,9

M_BWE# 8,9

M_BBS#1 8,9

M_BBS#0 8,9

M_BA[13..0] 8,9

AMD suggested M_BA13

connect to DIMM pin123

<Variant Name>

Title

Size Document Number Rev

A3

Date: Sheet of

2D5V_S3

RN7

1

8

2

7

3

6

45

SRN10K-2

M_DQS8

M_ADM8

MEMRESET#

M_CS#7

M_CS#6

M_CS#5

M_CS#4

RSVD_M_AA15

RSVD_M_AA14

RSVD_M_BA15

RSVD_M_BA14

NOT SUPPORT ECC CHECK

AMD suggested remove

PULL-HI resistor.

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

CPU(2/4)_DDR

Bolsena

558Tuesday, December 28, 2004

E

TP5

TP4

TPAD30

TPAD30

TP7

TP6

TPAD30

TPAD30

TP8

TPAD30

TP10

TP9

TPAD30

TPAD30

TP11

TP12

TPAD30

TPAD30

TP14

TPAD30

TP13

TPAD30

SA

Page 6

A

2D5V_VDDA_S0

2D5V_S0

4 4

12

2D5V_CPUA_S0

R39

1 2

0R3-U

C35

SC10U10V5ZY

1 2

63.R0004.151

DY

2D5V_CPUR_S0

R40

0R3-U

12

1 2

TC1

ST100U4VBM-1

AMD SUGGEST TO USE 2D5V_CPUA_S0

KEMET,NT:5.7, B2 size

ST100U4VBM-1 (80.10716.321)

3 3

2D5V_S0

2 2

DBREQJ

DY

DBRDY

TCK

TMS

TDI

TRST_L

TDO

2D5V_S3

CHANGE FROM 1KR3 TO 680R2 FOR AMD

CHECK LIST

NC_AG17

NC_AJ18

NC_D18

NC_B19

1 1

NC_C19

NC_D20

NC_C21

Iripple=1.1A,ESR=70mohm

SANYO, NT$:6.1

Iripple=1.1A,ESR=70mohm

3.5/2.8/2.0

77.21071.031

678

C44

SCD1U

RN8

123

SRN680-U

DY

1 2

DY

RN10

1

2

3

4 5

RN11

SRN680-U

1

2

3

4 5

SRN680-U

R57

680R3

A

4 5

8

7

6

8

7

6

12

AMD SUGGEST TO USE 100 ~ 300UH

Change

L270H

2D5V_VDDA_S0

R59

0R5J-1

12

DY

LAYOUT: Rou te tr ace 50 mils wide and

500 to 750 mils long between these

caps.

12

C39

SC4D7U10V5ZY

78.47593.411

1D2V_HT0B_S0

12

R53

R54

680R3

680R3

DY

1 2

1 2

64.44R25.551

AMD suggest voltege

from 2D5V_S0 to 2D5V_S3

differentially im pedance 100

B

3D3V_S0

12

C33

SC1U10V3KX

LAYOUT: Route VDDA trace approx.

50 mils wid e (use 2x25 mil traces to

exit ball field) and 500 mils long.

1 2

1 2

12

C40

SCD22U16V3ZY

12

R46

820R3

R42

820R3

1 2

1 2

1 2

C41

SC1000P50V2KX

CPUCLK3

CPUCLK#3

R48

680R3

R43

680R3

R50

680R3

2D5V_S0

LDT_RST#18

SB_CPUPWRGD18

LDT_STP#13,18

1 2

1 2

COREFB#41

1D25V_S3

2D5V_S0

COREFB41

C42

SC3900P50V3KX

C38

SC3900P50V3KX

R44

44D2R3F

R41

44D2R3F

12

C36

SC3300P50V2KX

12

2D5V_S3

LDT_RST#

SB_CPUPWRGD

LDT_STP#

C37

SC1000P50V2KX

Validation Test Points

LAYOUT: Place close to the CPU.

NC_C15

NC_AE23

NC_AF23

NC_AF22

NC_AF21

B

TP28

TPAD30

TP30

TPAD30

TP34

TPAD30

TPAD30

TP35

TPAD30

LDT_RST#

CLKIN

CLKIN#

CORE_SENSE

VDDIOFB

VDDIOFBJ

VDDIOSENSE

NC_AE24

NC_AF24

C

Iomax=120mA

U3

1

SHDN#

2

GND

3

IN

G913C-U

DY

12

R51

1 2

680R3

R52

1 2

680R3

678

RN9

123

SRN680-U

DY

C

SET

OUT

L0_REF1

L0_REF0

COREFB

COREFB#

CORE_SENSE

VDDIOFB

VDDIOFBJ

VDDIOSENSE

CLKIN

R45

169R3F

CLKIN#

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_AE23

NC_AF23

NC_AF22

NC_AF21

4 5

TP26

TP25

TPAD30

TPAD30

TP27

TPAD30

TP29

TP31

TPAD30

TPAD30

TP33

TPAD30TP32

TP37

TP36

TPAD30

TPAD30

TP38

TPAD30

2D5V_CPUA_S0

2D5V_VDDA_VREF

5

4

NC_C18

NC_A19

12

C34

SC1U10V3KX

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

A23

A24

B23

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

C16

AG15

AH17

C15

E20

E17

B21

A21

C18

A19

A28

AJ28

AE23

AF23

AF22

AF21

C1

J3

R3

AA2

D3

AG2

B18

AH1

AE21

C20

AG4

C6

AG6

AE9

AG9

12

C32

SC22P50V2JN-1

U2C

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A

VTT_B

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

NC_C1

NC_J3

NC_R3

NC_AA2

NC_D3

NC_AG2

NC_B18

NC_AH1

NC_AE21

NC_C20

NC_AG4

NC_C6

NC_AG6

NC_AE9

NC_AG9

BGA754-SKT-U

D

12

R37

R1

20KR3F

12

DY

R38

20KR3F

Vout = 1.25*(1+ R1/R2)

R2

E

DY

THERMTRIP#

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

A20

A26

A27

AG13

AF14

AG14

AF15

AE15

AG18

AH18

AG17

AJ18

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

THERMDP 23

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

FBCLKOUT

FBCLKOUTJ

DBREQJ

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

THERMDN 23

TP23

TP24

TPAD30

TPAD30

LAYOUT: Route FBCLKOUT_H/L

differentially i mpedance 80

12

R47

80D6R3F-U

R49

1 2

DUMMY-R3

DY

2D5V_S3

VID[4..0] 41

THERMTRIP_L

FBCLKOUT_H

FBCLKOUT_L

Connect to VDDIO for AMD suggest.

D22

NC_D22

C22

NC_C22

NC_B13

NC_B7

NC_C3

NC_K1

NC_R2

NC_AA3

NC_F3

NC_C23

NC_AG7

NC_AE22

NC_C24

NC_A25

NC_C9

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

THERMTRIP#

2D5V_S0

12

2

R55

680R3

1

3D3V_S5

3

Q1

MMBT3904-U1

NS3

1 2

12

R56

10KR2

CPU_THERMTRIP# 21,23

2D5V_S0

R58

1KR2

THERMTRIP#Level shift to SB400

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

D

Date: Sheet of

CPU(3/4)_Control & Debug

Bolsena

658Tuesday, December 28, 2004

E

SA

Page 7

A

VCC_CORE_S0 2D5V_S3

N20

Y17

VSS

K17

VSS

H17

VSS

F17

U2E

VSS

E18

VSS

AJ26

VSS

AE29

VSS

AC16

VSS

AA16

VSS

J16

VSS

G16

VSS

E16

VSS

AH14

4 4

3 3

2 2

1 1

AD15

AB15

K15

E15

D16

AE14

AC14

AA14

G14

AF17

AD13

AB13

Y13

K13

H13

F13

AH12

AC12

AA12

G12

B12

AD11

AB11

Y11

K11

H11

F11

AH10

AC10

W10

U10

R10

N10

G10

B10

AD9

AH8

AC8

AD7

AB7

AH6

AC6

AA6

AH4

AH2

AD2

AB2

C29

AH28

AF28

AC28

W28

R28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L10

VSS

J10

VSS

VSS

VSS

VSS

Y9

VSS

V9

VSS

T9

VSS

P9

VSS

M9

VSS

K9

VSS

H9

VSS

F9

VSS

VSS

VSS

W8

VSS

U8

VSS

R8

VSS

N8

VSS

L8

VSS

J8

VSS

G8

VSS

B8

VSS

VSS

VSS

V7

VSS

T7

VSS

P7

VSS

M7

VSS

K7

VSS

H7

VSS

F7

VSS

VSS

VSS

VSS

U6

VSS

R6

VSS

N6

VSS

L6

VSS

J6

VSS

G6

VSS

B6

VSS

VSS

B4

VSS

VSS

VSS

VSS

Y2

VSS

V2

VSS

T2

VSS

P2

VSS

M2

VSS

K2

VSS

H2

VSS

F2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L20

J20

AF19

AD19

AB19

Y19

K19

H19

F19

D19

AC18

AA18

G18

B16

AD17

AB17

H15

F15

G28

D28

B28

C27

AH26

AF26

AD26

Y26

T26

M26

H26

D26

B26

C25

B25

AJ24

AG24

AC24

AA24

W24

U24

R24

N24

J24

G24

E24

AG23

AD23

AB23

Y23

V23

T23

P23

K23

H23

F23

D23

AJ22

AH22

AG22

AC22

AA22

AG29

U22

R22

N22

L22

J22

G22

E22

B22

AG21

AD21

Y21

V21

T21

P21

M21

K21

H21

F21

D21

AJ20

AG20

AE20

AC20

AA20

W20

U20

R20

G20

J18

AE16

Y15

B14

J12

AA10

AB9

AA8

Y7

W6

AF2

D2

AG27

AG25

L24

M23

W22

AB21

AH20

B2

A

AC15

H18

B20

E21

H22

H24

F26

V10

G13

K14

Y14

AB14

G15

AA15

H16

K16

Y16

AB16

G17

AA17

AC17

AE17

F18

K18

Y18

AB18

AD18

AG19

E19

G19

AC19

AA19

F20

H20

K20

M20

P20

T20

V20

Y20

AB20

AD20

G21

N21

R21

U21

W21

AA21

AC21

F22

K22

M22

P22

T22

V22

Y22

AB22

AD22

E23

G23

N23

R23

U23

W23

AA23

AC23

B24

D24

F24

K24

M24

P24

T24

V24

Y24

AB24

AD24

AH24

AE25

K26

P26

V26

L7

VDD

VDD

VDD

VDD

U2D

VDD

VDD

J23

VDD

VDD

VDD

N7

VDD

L9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

J15

VDD

VDD

VDD

VDD

VDD

VDD

VDD

J17

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

J19

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

J21

VDD

L21

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

L23

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

B

VCC_CORE_S0

B

VCC_CORE_S0

12

VCC_CORE_S0

C55

SCD22U16V3ZY

1 2

0.22u x 4

DY

2D5V_S3

12

C61

SCD22U16V3ZY

1D25V_S3

12

C74

SCD22U16V3ZY

0.22u x 2

C

LAYOUT: Place in uPGA socket cavity.

0.22u x 6

12

C45

C46

SCD22U16V3ZY

SCD22U16V3ZY

12

C47

SCD22U16V3ZY

12

C48

SCD22U16V3ZY

12

C49

SCD22U16V3ZY

12

C50

SCD22U16V3ZY

LAYOUT: Place on backside of processor.

C56

SCD22U16V3ZY

1 2

C57

SCD22U16V3ZY

1 2

C58

SCD22U16V3ZY

1 2

12

C59

SC10U10V5ZY

C60

SC10U10V5ZY

12

10u x 2

DY

DY

12

DY

12

C63

C62

SCD22U16V3ZY

SCD22U16V3ZY

12

C64

SCD22U16V3ZY

12

C65

SCD22U16V3ZY

12

C66

SCD22U16V3ZY

2D5V_S3

10u x 1 4.7u x 6

1D25V_S3

12

12

12

C75

SCD22U16V3ZY

C77

C76

SC4D7U10V5ZY

SC4D7U10V5ZY

4.7u x 2

C

12

12

C67

SC10U10V5ZY

10u x 4

12

C51

SC10U10V5ZY

12

C68

SC4D7U10V5ZY

12

C52

SC10U10V5ZY

12

C69

SC4D7U10V5ZY

D

12

C53

SC10U10V5ZY

12

C70

SC4D7U10V5ZY

D

BGA754-SKT-U

C54

SC10U10V5ZY

12

C71

SC4D7U10V5ZY

E

BGA754-SKT-U

12

12

78.47593.411

C72

C73

SC4D7U10V5ZY

SC4D7U10V5ZY

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet

CPU(4/4)_Power

Bolsena

758Tuesday, December 28, 2004

E

SA

of

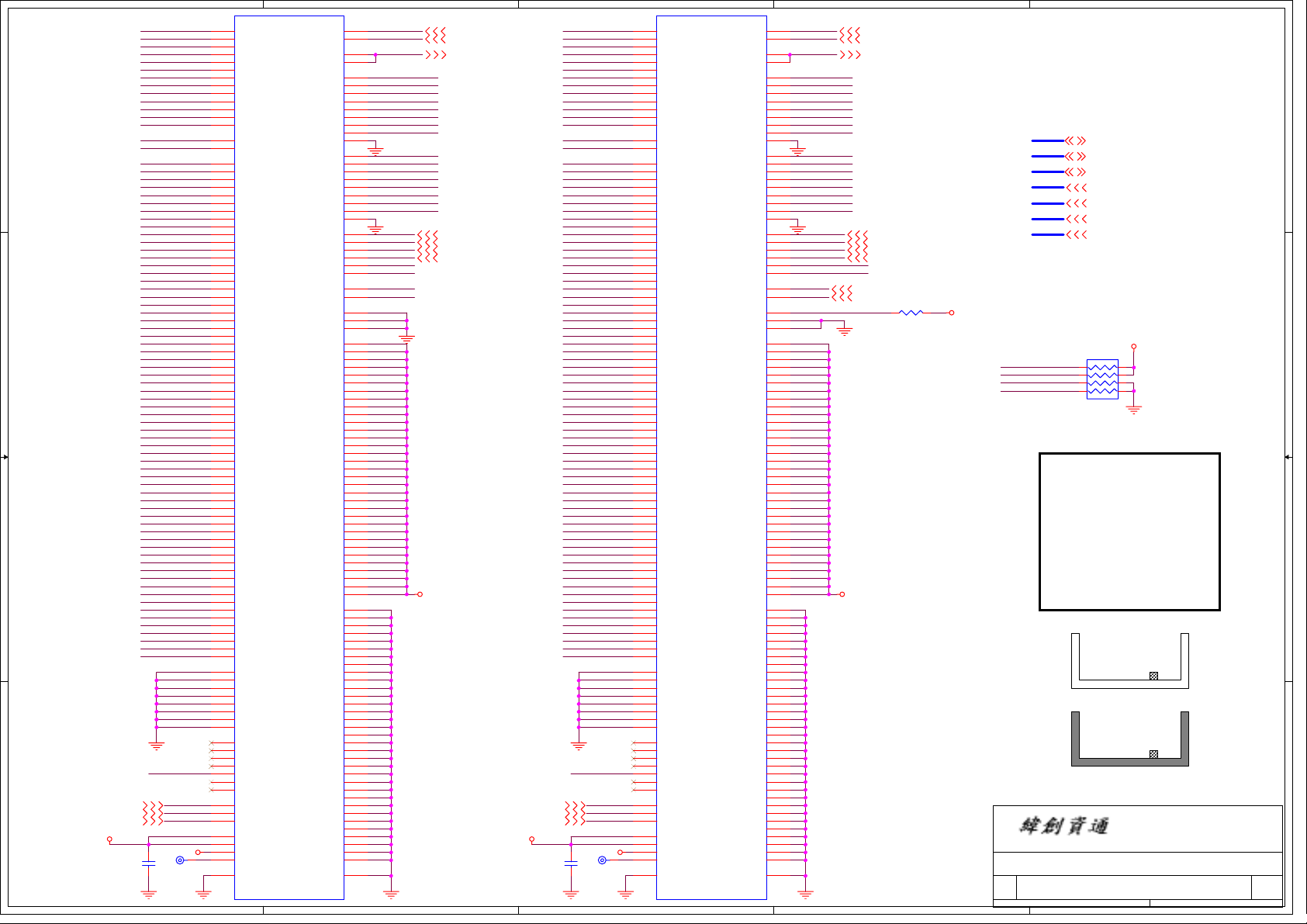

Page 8

A

M_AA0

M_AA1

M_AA2

M_AA3

M_AA4

M_AA5

M_AA6

M_AA7

M_AA8

M_AA9

M_AA10

M_AA11

4 4

3 3

2 2

1 1

M_ARAS#5,9

M_ACAS#5,9

M_AWE#5,9

VREF_DDR_MEM VREF_DDR_MEM

Layout trace 20 mil Layout trace 20 mil

M_AA12

M_ABS#0

M_ABS#1

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

12

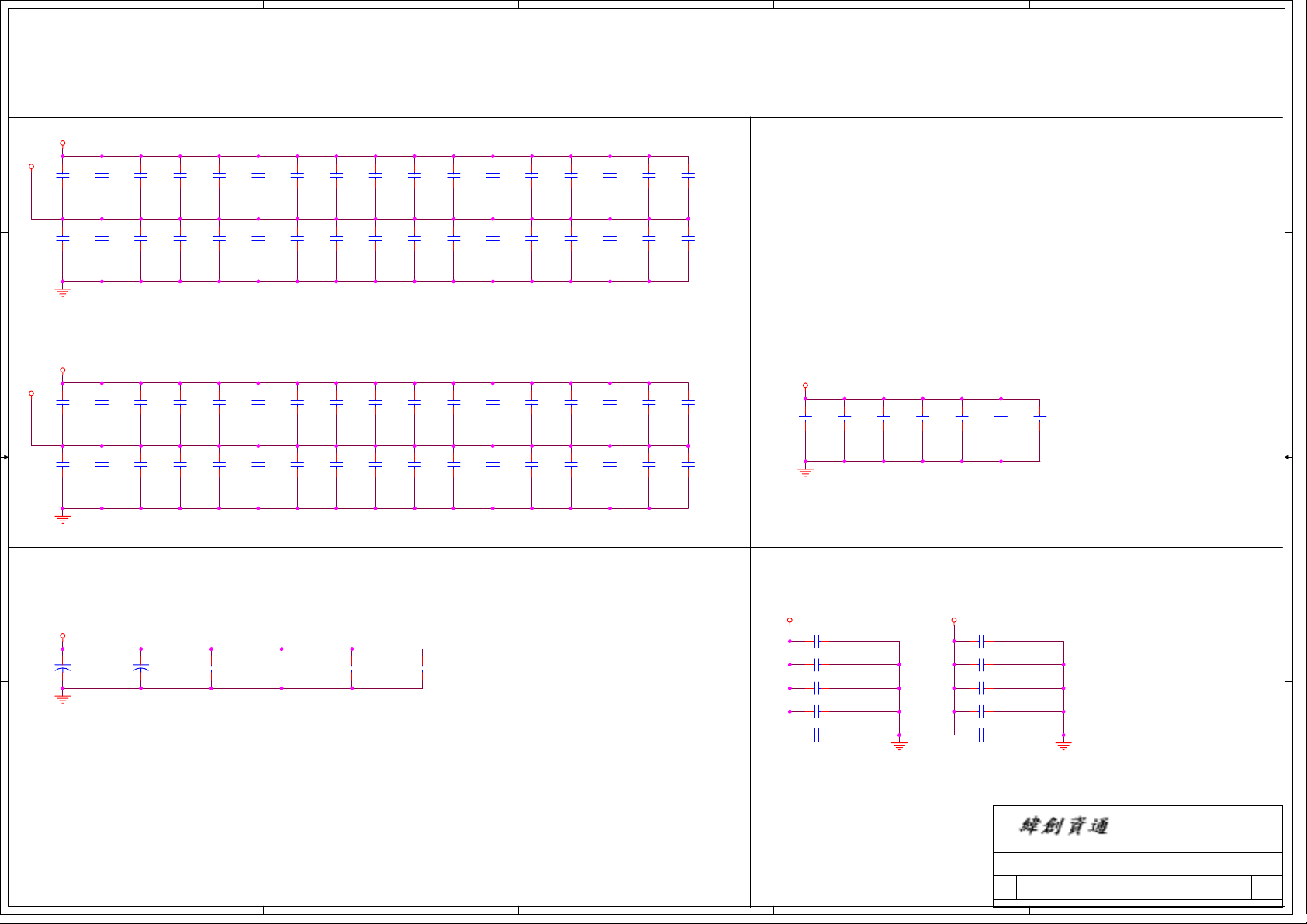

A

3D3V_S0

C519

SCD1U

TP126

TPAD30

DDR1

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC#85

86

NC#86/(RESET#)

97

NC#97/A13

98

NC#98/BA2

123

NC#123

124

NC#124

200

NC#200

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

201

GND

SKT-SODIMM200-24

/CS0

/CS1

CKE0

CKE1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

REVERSE TYPE 5.2MM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

121

122

96

95

11

25

47

61

133

147

169

183

77

12

26

48

62

134

148

170

184

78

35

37

160

158

89

91

195

193

194

196

198

9

10

21

22

33

34

36

45

46

57

58

69

70

81

82

92

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

202

B

M_CKE#0

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_ADM_R0

M_ADM_R1

M_ADM_R2

M_ADM_R3

M_ADM_R5

M_ADM_R6

M_ADM_R7

DDR_CLK0

DDR_CLK#0

SMBC_SB

SMBD_SB

NOT SUPPORT ECC CHECK

AMD suggested pull-low

2D5V_S3

M_ADM#0

M_ADM#1

M_ADM#2

M_ADM#3

M_ADM#4

M_ADM#5

M_ADM#6

M_ADM#7

M_CLK5 5,9

M_CLK#5 5,9

M_CLK7 5,9

M_CLK#7 5,9

62.10017.701

B

C

M_CS#0 5,9

M_CS#1 5,9

M_CKE#0 5,9 M_CKE#1 5,9

M_BRAS#5,9

M_BCAS#5,9

M_BWE#5,9

M_BA0

M_BA1

M_BA2

M_BA3

M_BA4

M_BA5

M_BA6

M_BA7

M_BA8

M_BA9

M_BA10

M_BA11

M_BA12

M_BBS#0

M_BBS#1

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_BA13M_AA13

12

3D3V_S0

C520

SCD1U

TP127

TPAD30

DDR2

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC#85

86

NC#86/(RESET#)

97

NC#97/A13

98

NC#98/BA2

123

NC#123

124

NC#124

200

NC#200

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

201

GND

SKT-SODIMM200-6U

C

121

/CS0

122

/CS1

96

CKE0

95

CKE1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

REVERSE TYPE 9.2MM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

11

25

47

61

133

147

169

183

77

12

26

48

62

134

148

170

184

78

35

37

160

158

89

91

195

193

194

196

198

9

10

21

22

33

34

36

45

46

57

58

69

70

81

82

92

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

202

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_ADM_R0

M_ADM_R1

M_ADM_R2

M_ADM_R3

M_ADM_R4M_ADM_R4

M_ADM_R5

M_ADM_R6

M_ADM_R7

DDR_CLK1

DDR_CLK#1

62.10017.391

2D5V_S3

D

M_CS#2 5,9

M_CS#3 5,9

M_ADM#0

M_ADM#1

M_ADM#2

M_ADM#3

M_ADM#4

M_ADM#5

M_ADM#6

M_ADM#7

M_CLK4 5,9

M_CLK#4 5,9

M_CLK6 5,9

M_CLK#6 5,9

SMBC_SB 3,21,57

SMBD_SB 3,21,57

1 2

D

?NEED CHANGE LIBRARY

R563

3D3V_S0

4K7R2

DDR_CLK#1

DDR_CLK#0

DDR_CLK1

DDR_CLK0

MD63

DDR1(Reverse 5.2mm)

DDR2(Reverse 9.2mm)

<Variant Name>

Title

Size Document Number Rev

A3

Date: Sheet

E

M_ADM_R[7..0] 9

M_DATA_R_[63..0] 9

M_DQS_R[7..0] 9

M_AA[13..0] 5,9

M_ABS#[1..0] 5,9

M_BA[13..0] 5,9

M_BBS#[1..0] 5,9

2D5V_S3

RN92

SRN10K-2

DY

1

2

3

45

8

7

6

AMD CPU

SMA10

SMA11

Pin 199

Pin 200 Pin 2

Pin 199 Pin 1

Pin 200 Pin 2

(Bottom view)

DDR SO-DIMM SKT

Bolsena

SMA14

SMA0

SMA12

Pin 1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

E

MD0

858Tuesday, December 28, 2004

SA

of

Page 9

A

SERIES DAMPING PARALLEL TERMINATION

PLACE RNs CLOSE TO FIRST DIMM, < 0.75"

STRICT EQUAL LENGTH LIMITATION WITH DQS,

CB PINS

M_DATA4

M_ADM0

M_DATA6

M_DATA7

M_DATA13

M_DATA12

4 4

M_ADM1

M_DATA1

M_DATA0

M_DQS0

M_DATA2

M_DATA3

M_DATA8

M_DATA9

M_DQS1

M_DATA14 M_DATA_R_14

M_DATA15

M_DATA21

M_DATA20

M_ADM2

M_DATA23 M_DATA_R_23

M_DATA22

M_DATA25 M_DATA_R_25

3 3

M_DATA11

M_DATA10

M_DATA17

M_DATA16

M_DQS2 M_DQS_R2

M_DATA19 M_DATA_R_19

M_DATA18

M_DATA24

M_DATA29

M_DATA28

M_ADM3

M_DATA26

M_DATA27

M_DATA30 M_DATA_R_30

M_DATA31

2 2

SRN10J-3

8 9

7

6

5

4

3

2

1

RN13

SRN10J-3

8 9

7

6

5

4

3

2

1

RN18

SRN10J-3

8 9

7

6

5

4

3

2

1

RN24

SRN10J-3

8 9

7

6

5

4

3

2

1

RN29

SRN10J-3

8 9

7

6

5

4

3

2

1

RN34

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

M_DATA_R_4

M_DATA_R_5M_DATA5

M_ADM_R0

M_DATA_R_6

M_DATA_R_7

M_DATA_R_13

M_DATA_R_12

M_ADM_R1

M_DATA_R_1

M_DATA_R_0

M_DQS_R0

M_DATA_R_2

M_DATA_R_3

M_DATA_R_8

M_DATA_R_9

M_DQS_R1

M_DATA_R_15

M_DATA_R_21

M_DATA_R_20

M_ADM_R2

M_DATA_R_22

M_DATA_R_11

M_DATA_R_10

M_DATA_R_17

M_DATA_R_16

M_DATA_R_18

M_DATA_R_24

M_DATA_R_29

M_DATA_R_28

M_DQS_R3M_DQS3

M_ADM_R3

M_DATA_R_26

M_DATA_R_27

M_DATA_R_31

M_DATA32

M_DATA33 M_DATA_R_33 M_DATA_R_33

M_DATA36 M_DATA_R_36

M_DQS4 M_DQS_R4

M_ADM4 M_ADM_R4

M_DATA34

M_DATA39

M_DATA35

M_DATA41

M_DATA40

M_DQS5

M_DATA42

M_DATA43

M_DATA49

M_DATA48

M_DATA38

M_DATA45

M_DATA44

M_ADM5

M_DATA47

M_DATA46

M_DATA53

M_DATA52

M_DQS6

M_DATA50

M_DATA51

M_DATA56

M_DATA57

M_DQS7

M_DATA58

M_DATA59

M_ADM6

M_DATA54

M_DATA55

M_DATA61

M_DATA60

M_ADM7

M_DATA62

M_DATA63

8 9

7

6

5

4

3

2

1

8 9

7

6

5

4

3

2

1

8 9

7

6

5

4

3

2

1

8 9

7

6

5

4

3

2

1

8 9

7

6

5

4

3

2

1

SRN10J-3

RN14

SRN10J-3

RN19

SRN10J-3

RN25

SRN10J-3

RN30

SRN10J-3

RN35

B

M_DATA_R_32 M_DATA_R_32

10

11

M_DATA_R_37M_DATA37 M_DATA_R_37

12

13

14

M_DATA_R_34

15

M_DATA_R_39

16

M_DATA_R_35

M_DATA_R_41

10

M_DATA_R_40

11

M_DQS_R5

12

M_DATA_R_42

13

M_DATA_R_43

14

M_DATA_R_49

15

M_DATA_R_48

16

M_DATA_R_38

M_DATA_R_45

10

M_DATA_R_44

11

M_ADM_R5

12

M_DATA_R_47

13

M_DATA_R_46

14

M_DATA_R_53

15

M_DATA_R_52

16

M_DQS_R6

M_DATA_R_50

10

M_DATA_R_51

11

M_DATA_R_56

12

M_DATA_R_57

13

M_DQS_R7

14

M_DATA_R_58

15

M_DATA_R_59

16

M_ADM_R6

M_DATA_R_54

10

M_DATA_R_55

11

M_DATA_R_61

12

M_DATA_R_60

13

M_ADM_R7

14

M_DATA_R_62

15

M_DATA_R_63

16

M_ADM_R1

M_DATA_R_13

M_DATA_R_12

M_DATA_R_7

M_DATA_R_6

M_ADM_R0

M_DATA_R_5

M_DATA_R_4

M_DATA_R_1

M_DATA_R_0

M_DQS_R0

M_DATA_R_2

M_DATA_R_3

M_DATA_R_8

M_DATA_R_9

M_DQS_R1

M_DATA_R_25

M_DATA_R_23

M_DATA_R_22

M_ADM_R2

M_DATA_R_21

M_DATA_R_20

M_DATA_R_15

M_DATA_R_14

M_DATA_R_11

M_DATA_R_10

M_DATA_R_16

M_DATA_R_17

M_DQS_R2

M_DATA_R_19

M_DATA_R_18

M_DATA_R_24

M_DATA_R_31

M_DATA_R_30

M_DATA_R_26

M_DATA_R_27

M_ADM_R3

M_DQS_R3

M_DATA_R_29

M_DATA_R_28

SRN68J-1

8 9

7

6

5

4

3

2

1

RN15

SRN68J-1

8 9

7

6

5

4

3

2

1

RN20

SRN68J-1

8 9

7

6

5

4

3

2

1

RN26

SRN68J-1

8 9

7

6

5

4

3

2

1

RN31

SRN68J-1

8 9

7

6

5

4

3

2

1

RN36

C

1D25V_S3 1D25V_S3

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

SRN68J-1

8 9

7

6

5

4

3

2

1

RN16

SRN68J-1

8 9

7

6

5

4

3

2

1

RN21

SRN68J-1

8 9

7

6

5

4

3

2

1

RN27

SRN68J-1

8 9

7

6

5

4

3

2

1

RN32

SRN68J-1

8 9

7

6

5

4

3

2

1

RN37

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

D

PULL HIGH STUBS < 0.8", PLACE RPs CLOSE TO SECOND DM ( DM2 )

NO EQUAL LENGTH LIMITATION

M_DATA_R_36

M_ADM_R4

M_DQS_R4

M_DATA_R_38

M_DATA_R_39

M_DATA_R_48

M_DATA_R_49

M_DATA_R_43

M_DATA_R_42

M_DQS_R5

M_DATA_R_41

M_DATA_R_40

M_DATA_R_34

M_DATA_R_35

M_DATA_R_44

M_DATA_R_45

M_ADM_R5

M_DATA_R_46

M_DATA_R_47

M_DATA_R_52

M_DATA_R_53

M_DATA_R_59

M_DATA_R_58

M_DQS_R7

M_DATA_R_57

M_DATA_R_56

M_DATA_R_51

M_DATA_R_50

M_DQS_R6

M_ADM_R6

M_DATA_R_54

M_DATA_R_55

M_DATA_R_60

M_DATA_R_61

M_ADM_R7

M_DATA_R_62

M_DATA_R_63

M_CKE#0

M_CKE#1

M_BA12

M_AA12

M_AA11

M_AA9

M_AA7

M_AA5

M_AA4

M_AA8

M_AA6

M_AA3

M_CS#3

M_BCAS#

M_BRAS#

M_BBS#1

M_CS#2

M_BA13

M_BA0

M_BA2

M_AA1

M_AA10

M_AA2

M_AA0

M_ABS#1

M_ARAS#

M_AWE#

M_ABS#0

M_BA7

M_BA3

M_BA6

M_BA9

M_BA10

M_BA1

M_BBS#0

M_BWE#

M_BA4

M_BA8

M_BA11

M_BA5

M_AA13

M_CS#0

M_ACAS#

M_CS#1

SRN47J

1 4

2

RN17

SRN47J

1 4

2

RN22

SRN47J-1-U

8 9

7

6

5

4

3

2

1

RN23

SRN47J-1-U

8 9

7

6

5

4

3

2

1

RN28

SRN47J-1-U

8 9

7

6

5

4

3

2

1

RN33

SRN47J-1-U

8 9

7

6

5

4

3

2

1

RN38

SRN47-1

4 5

3

2

1

RN39

SRN47-1

4 5

3

2

1

RN40

E

M_ADM_R[7..0] 8

3

3

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

10

11

12

13

14

15

16

6

7

8

6

7

8

M_ADM[7..0] 5

M_DATA[63..0] 5

M_DATA_R_[63..0] 8

M_DQS[7..0] 5

M_DQS_R[7..0] 8

M_AA[13..0] 5,8

M_ABS#[1..0] 5,8

M_BA[13..0] 5,8

M_BBS#[1..0] 5,8

M_AWE# 5,8

M_ACAS# 5,8

M_ARAS# 5,8

M_BWE# 5,8

M_BCAS# 5,8

M_BRAS# 5,8

M_CS#0 5,8

M_CS#1 5,8

M_CS#2 5,8

M_CS#3 5,8

M_CKE#05,8

M_CKE#15,8

05/10

Remove the damping resistor for AMD suggest.

1 1

M_CKE#0

M_CKE#1

R60

1 2

121R3F

R61

1 2

121R3F

R62

1 2

121R3F

R63

1 2

121R3F

A

B

M_CLK7

M_CLK#7

M_CLK6

M_CLK#6

M_CLK5

M_CLK#5

M_CLK4

M_CLK#4

C

M_CLK7 5,8

M_CLK#7 5,8

M_CLK6 5,8

M_CLK#6 5,8

M_CLK5 5,8

M_CLK#5 5,8

M_CLK4 5,8

M_CLK#4 5,8

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

D

Date: Sheet

DDR DAMPING & TERMINATION

Bolsena

958Tuesday, December 28, 2004

E

of

SA

Place it near CPU

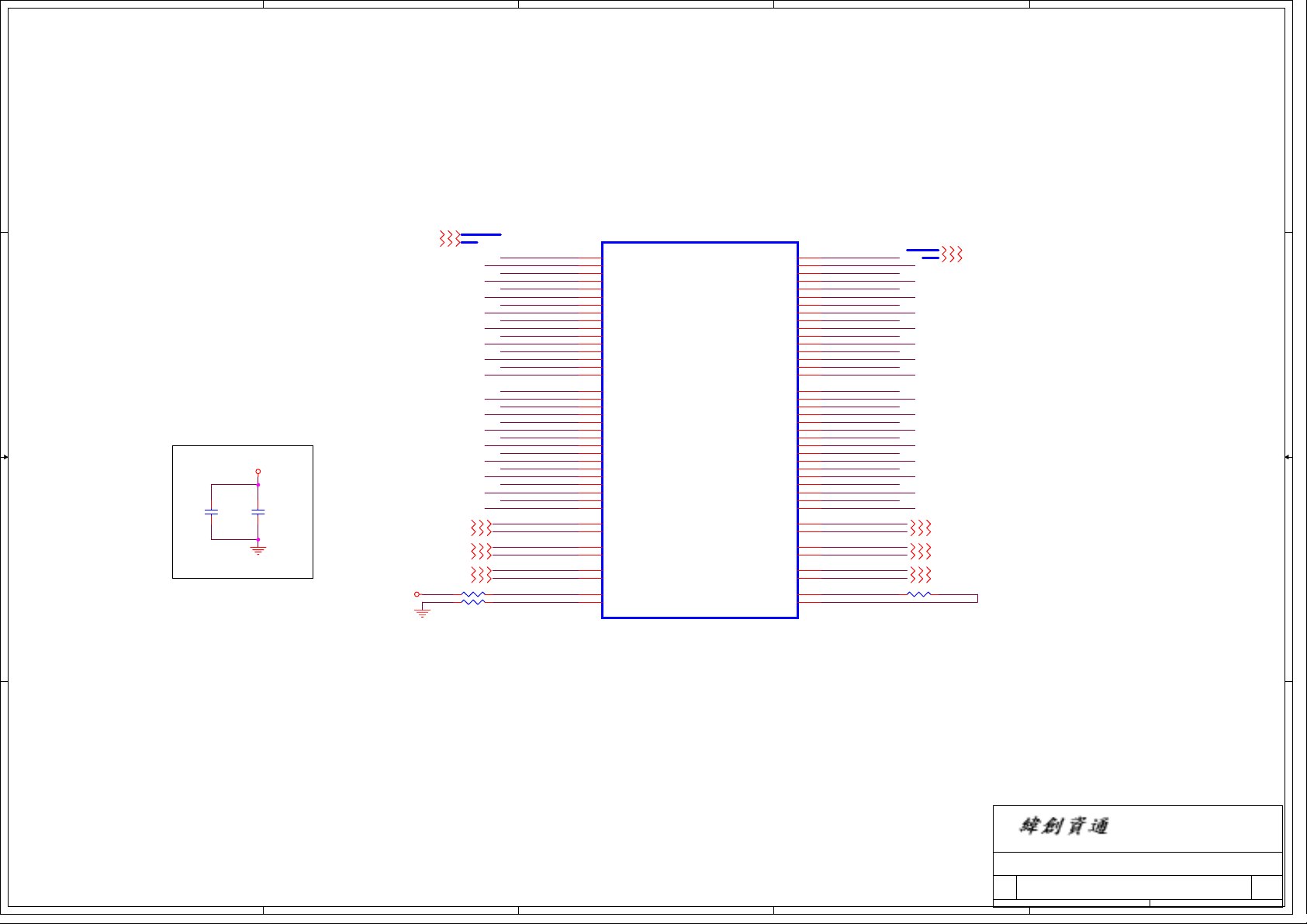

Page 10

A

B

C

D

E

4 4

2D5V_S3

1D25V_S3

12

12

C80

SCD1U

C81

SCD1U

12

C82

SCD1U

DY

12

12

C97

SCD1U

C98

SCD1U

12

C99

SCD1U

DY

3 3

2D5V_S3

1D25V_S3

12

C114

SCD1U

12

12

C122

SCD1U

C123

SCD1U

DY

12

C138

SCD1U

C139

SCD1U

C140

SCD1U

12

12

DY

2 2

LAYOUT:Place altemating caps to GND and 2D5_S3

12

C83

SCD1U

DY

12

C100

SCD1U

DY

12

C124

SCD1U

DY

12

C141

SCD1U

DY

12

12

C84

SCD1U

C85

SCD1U

12

C86

SCD1U

12

12

C87

SCD1U

C88

SCD1U

DY

12

12

12

C101

C102

SCD1U

SCD1U

C103

SCD1U

12

12

C104

C105

SCD1U

SCD1U

DY

C125

SCD1U

C126

SCD1U

C127

SCD1U

12

12

12

12

12

C128

SCD1U

C129

SCD1U

DY

12

12

C142

C143

SCD1U

SCD1U

12

12

C144

SCD1U

C145

SCD1U

12

C146

SCD1U

DY

12

12

C89

SCD1U

DY

12

C106

SCD1U

DY

12

C130

SCD1U

DY

12

C147

SCD1U

DY

12

12

C90

SCD1U

C91

SCD1U

C92

SCD1U

12

C93

SCD1U

DY

12

12

12

C107

C108

SCD1U

SCD1U

C109

SCD1U

12

C110

SCD1U

DY

12

12

C131

C132

SCD1U

SCD1U

12

12

C133

SCD1U

C134

SCD1U

DY

12

12

C148

C149

SCD1U

SCD1U

12

12

C150

SCD1U

C151

SCD1U

DY

12

12

C94

SCD1U

C95

SCD1U

12

C96

SCD1U

DY

12

12

C111

SCD1U

C112

SCD1U

12

C113

SCD1U

DY

12

C135

SCD1U

C136

SCD1U

C137

SCD1U

12

12

DY

12

12

12

C153

SCD1U

C154

SCD1U

C152

SCD1U

1D25V_S3

12

DY

C115

SCD1U

12

12

12

C116

SCD1U

DY

DY

C117

SCD1U

12

C118

SCD1U

DY

DY

C119

SCD1U

12

12

C120

C121

SCD1U

SCD1U

DY

DY

DY

LAYOUT:Place close to Power Pin of DDR socket.

LAYOUT:Place at end of the DIMMs

1D25V_S3

12

TC2

ST100U4VBM-U

12

TC3

ST100U4VBM-1

12

C157

SC22U10V6ZY-U

12

C158

SC22U10V6ZY-U

12

C159

SC22U10V6ZY-U

12

C160

SC22U10V6ZY-U

2D5V_S3 2D5V_S3

C155

1 2

SCD22U16V3ZY

C161

1 2

SCD22U16V3ZY

C163

1 2

DY

SCD22U16V3ZY

C165

1 2

DY

SCD22U16V3ZY

C167

1 2

SCD22U16V3ZY

1 2

1 2

1 2

DY

1 2

DY

1 2

C156

SCD22U16V3ZY

C162

SCD22U16V3ZY

C164

SCD22U16V3ZY

C166

SCD22U16V3ZY

C168

SCD22U16V3ZY

0.22u x 10

1 1

A

B

C

D

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet of

DDR DECOUPLING

Bolsena

E

10 58Tuesday, December 28, 2004

SA

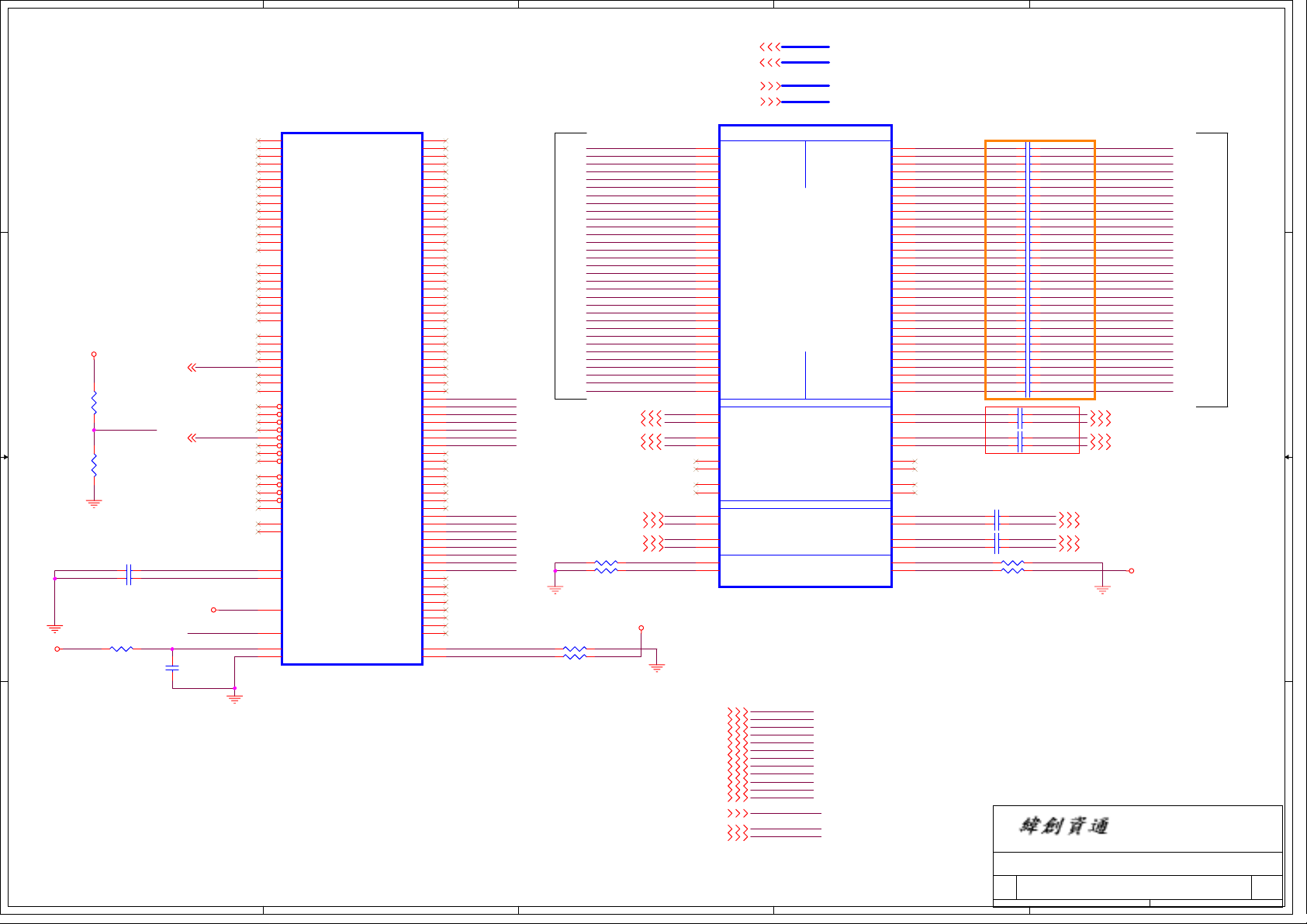

Page 11

A

4 4

B

C

D

E

CLAW HAMMER TO NB NB TO CLAW HAMMER

CPUCADOUT[15..0]4

CPUCADOUTJ[15..0]4

3 3

1D2V_S0

12

2 2

AROUND NB

C169

SCD1U16V

DY

12

C170

SCD1U16V

CPUHTTCLKOUT14

CPUHTTCLKOUTJ14

CPUHTTCLKOUT04

CPUHTTCLKOUTJ04

CPUHTTCTLOUT04

CPUHTTCTLOUTJ04

1D2V_HT0A_S0

1 2

1 2

CPUCADOUT15

CPUCADOUTJ15

CPUCADOUT14

CPUCADOUTJ14

CPUCADOUT13

CPUCADOUTJ13

CPUCADOUT12

CPUCADOUTJ12

CPUCADOUT11

CPUCADOUTJ11

CPUCADOUT10

CPUCADOUTJ10

CPUCADOUT9

CPUCADOUTJ9

CPUCADOUT8

CPUCADOUTJ8

CPUCADOUT7

CPUCADOUTJ7

CPUCADOUT6

CPUCADOUTJ6

CPUCADOUT5

CPUCADOUTJ5

CPUCADOUT4

CPUCADOUTJ4

CPUCADOUT3

CPUCADOUTJ3

CPUCADOUT2

CPUCADOUTJ2

CPUCADOUT1

CPUCADOUTJ1

CPUCADOUT0

CPUCADOUTJ0

CPUHTTCLKOUT1

CPUHTTCLKOUTJ1

CPUHTTCLKOUT0

CPUHTTCLKOUTJ0

CPUHTTCTLOUT0

CPUHTTCTLOUTJ0

R64

49D9R2F

R65

49D9R2F

HT_RXCALN

HT_RXCALP

W25

W24

AA25

AA24

AB26

AA26

AC25

AC24

AD26

AC26

W30

AB29

AA29

AC29

AC28

W26

W29

W28

T26

R26

U25

U24

V26

U26

R29

R28

T30

R30

T28

T29

V29

U29

Y30

Y28

Y29

Y26

P29

N29

D27

E27

U4A

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALN

HT_RXCALP

RS480M-U

PART 1OF6

HYPER TRANSPORT CPU I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

R24

R25

N26

P26

N24

N25

L26

M26

J26

K26

J24

J25

G26

H26

G24

G25

L30

M30

L28

L29

J29

K29

H30

H29

E29

E28

D30

E30

D28

D29

B29

C29

L24

L25

F29

G29

M29

M28

B28

A28

NB0CADOUT15

NB0CADOUTJ15

NB0CADOUT14

NB0CADOUTJ14

NB0CADOUT13

NB0CADOUTJ13

NB0CADOUT12

NB0CADOUTJ12

NB0CADOUT11

NB0CADOUTJ11

NB0CADOUT10

NB0CADOUTJ10

NB0CADOUT9

NB0CADOUTJ9

NB0CADOUT8

NB0CADOUTJ8

NB0CADOUT7

NB0CADOUTJ7

NB0CADOUT6

NB0CADOUTJ6

NB0CADOUT5

NB0CADOUTJ5

NB0CADOUT4

NB0CADOUTJ4

NB0CADOUT3

NB0CADOUTJ3

NB0CADOUT2

NB0CADOUTJ2

NB0CADOUT1

NB0CADOUTJ1

NB0CADOUT0

NB0CADOUTJ0

NB0HTTCLKOUT1

NB0HTTCLKOUTJ1

NB0HTTCLKOUT0

NB0HTTCLKOUTJ0

NB0HTTCTLOUT

NB0HTTCTLOUTJ

HT_TXCALP

HT_TXCALN

1 2

NB0CADOUT[15..0] 4

NB0CADOUTJ[15..0] 4

NB0HTTCLKOUT1 4

NB0HTTCLKOUTJ 1 4

NB0HTTCLKOUT0 4

NB0HTTCLKOUTJ 0 4

NB0HTTCTLOUT 4

NB0HTTCTLOUTJ 4

R66

100R2F

1 1

A

B

C

D

<Variant Name>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet

ATI-RS480M (1 of 4) HT

Bolsena

11 58Tuesday, December 28, 2004

E

of

SA

Page 12

A

B

C

D

E

PEG_TXP[15..0]49

PEG_TXN[15..0]49

PEG_RXP[15..0]49

PEG_RXN[15..0]49

D8

D7

D5

D4

E4

F4

G5

G4

H4

H5

H6

G1

G2

K5

K4

M4

N5

N4

P4

R4

P5

P6

P2

R2

T5

T4

U4

V4

W1

W2

AE1

AE2

AB2

AC2

AB5

AB4

Y4

AA4

AG1

AH1

AC5

AC6

AH3

AJ3

DVO_MDA5215

DVO_MDA4915

DVO_MDA5015

DVO_MDA5115

DVO_MDA3915

DVO_MDA4815

DVO_MDA3815

DVO_MDA3715

DVO_MDA3615

DVO_MDA3515

DVO_MDA3415

DVO_MDA3315

DVO_MDA5315

DVO_MDA5415

DVO_MDA5515

U4B

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

J4

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

L4

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P/SB_RX2P

GPP_RX0N/SB_RX2N

GPP_RX1P/SB_RX3P

GPP_RX1N/SB_RX3N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

PCE_ISET

PCE_TXISET

RS480M-U

PART 2 OF 6

GPP_TX0P/SB_TX2P

GPP_TX0N/SB_TX2N

GPP_TX1P/SB_TX3P

GPP_TX1N/SB_TX3N

PCIE I/F TO VIDEO

PCIE I/F TO SLOT