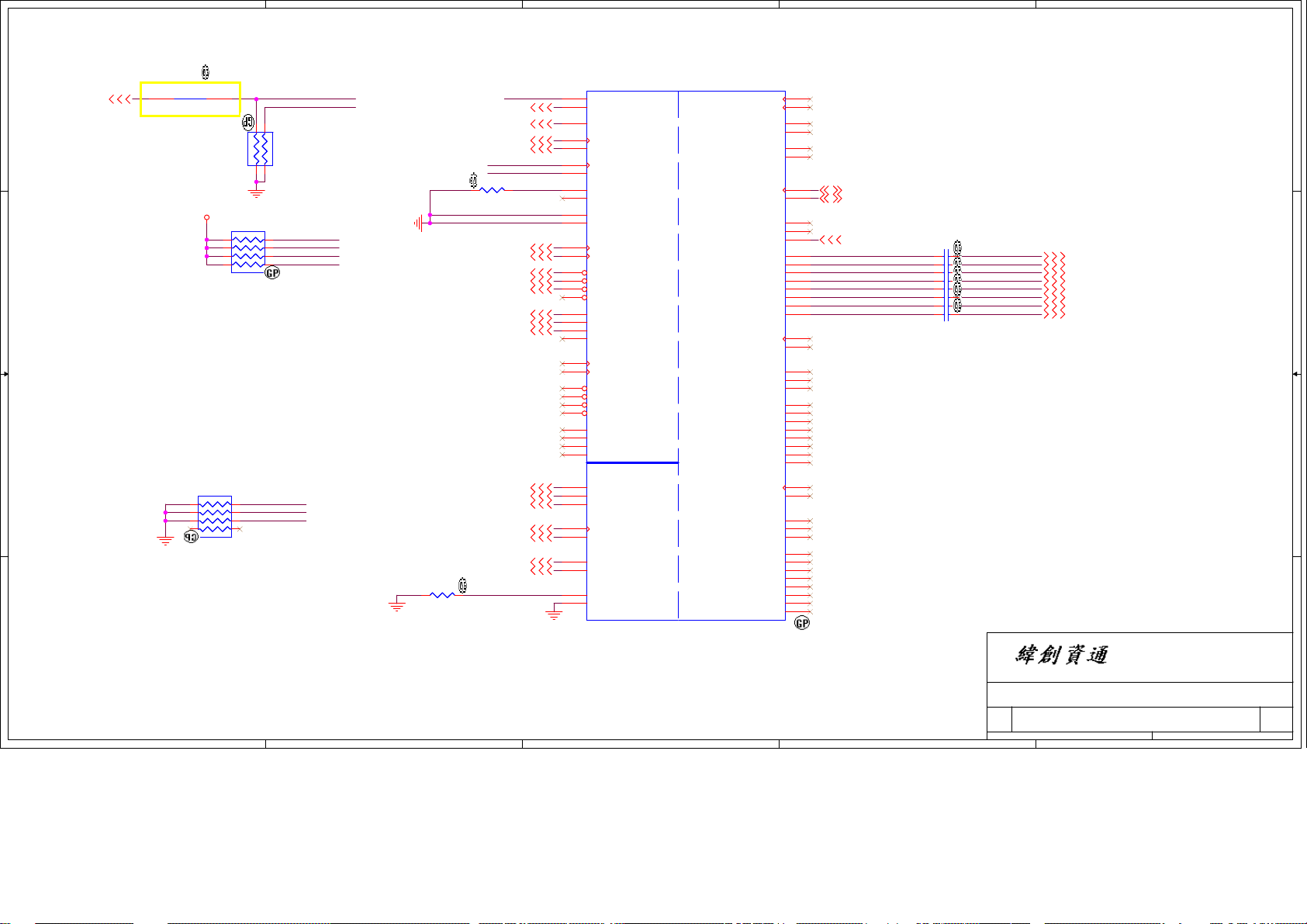

Acer aspire 1430, Aspire 1830, Aspire 1830t Schematics

5

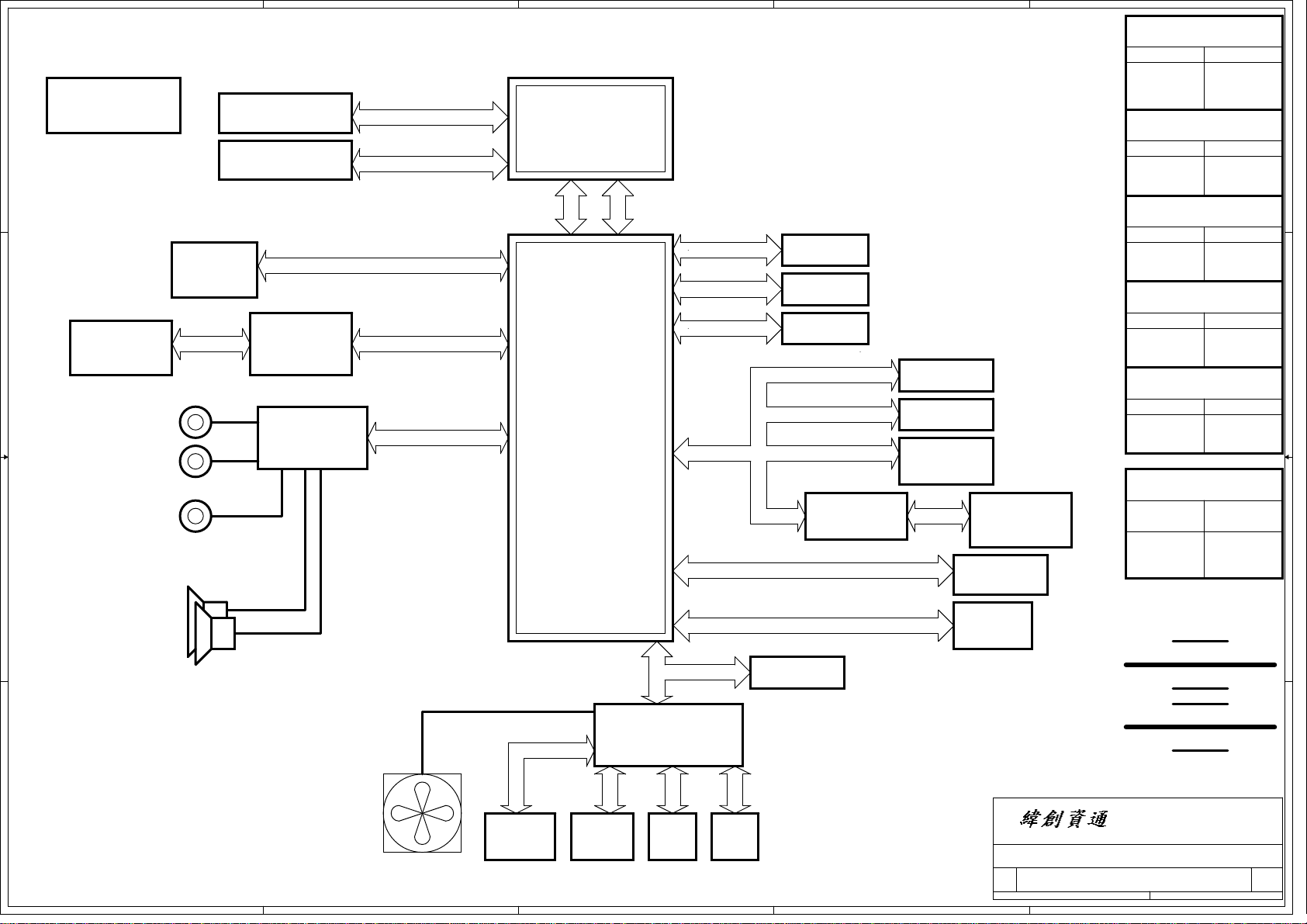

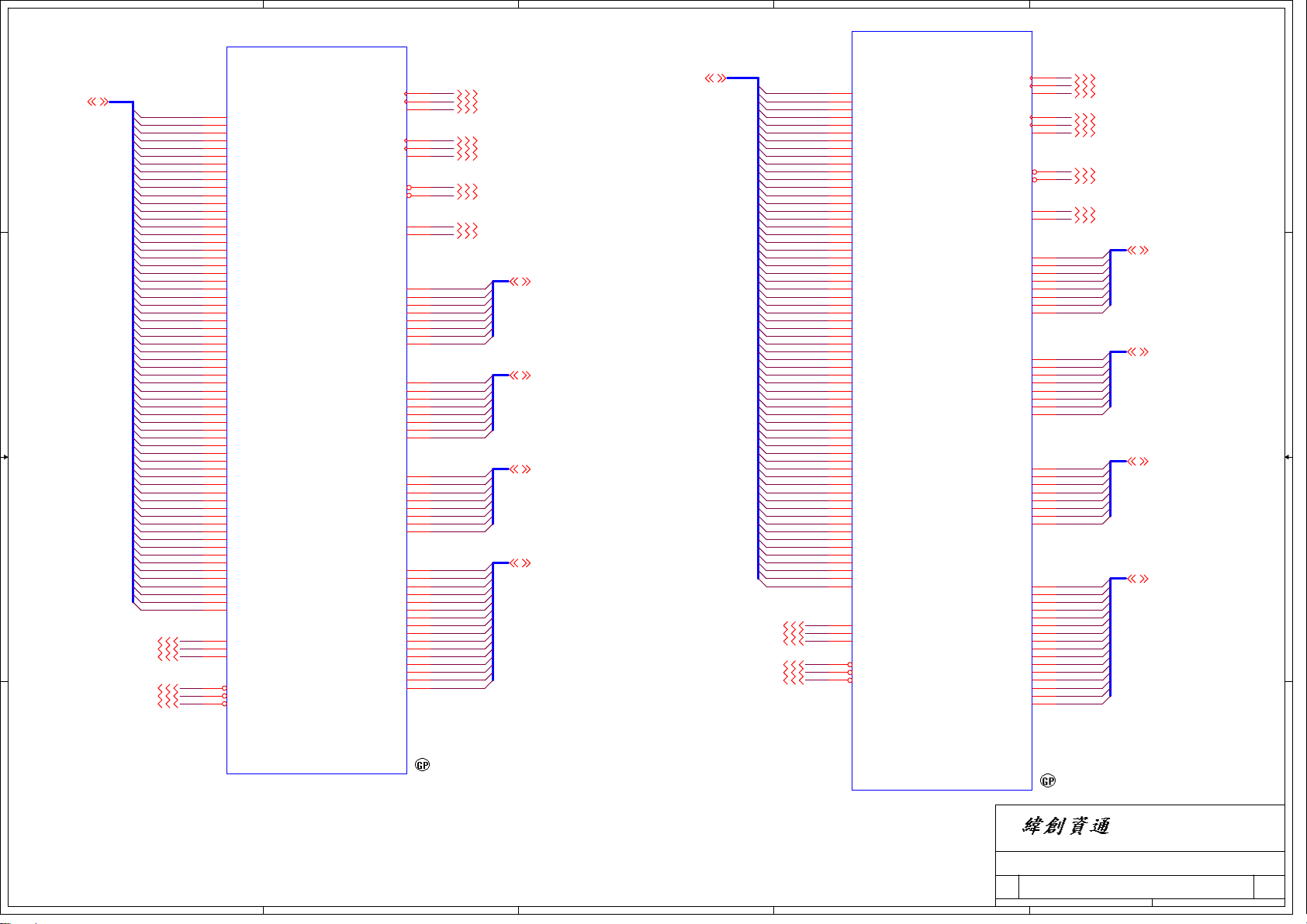

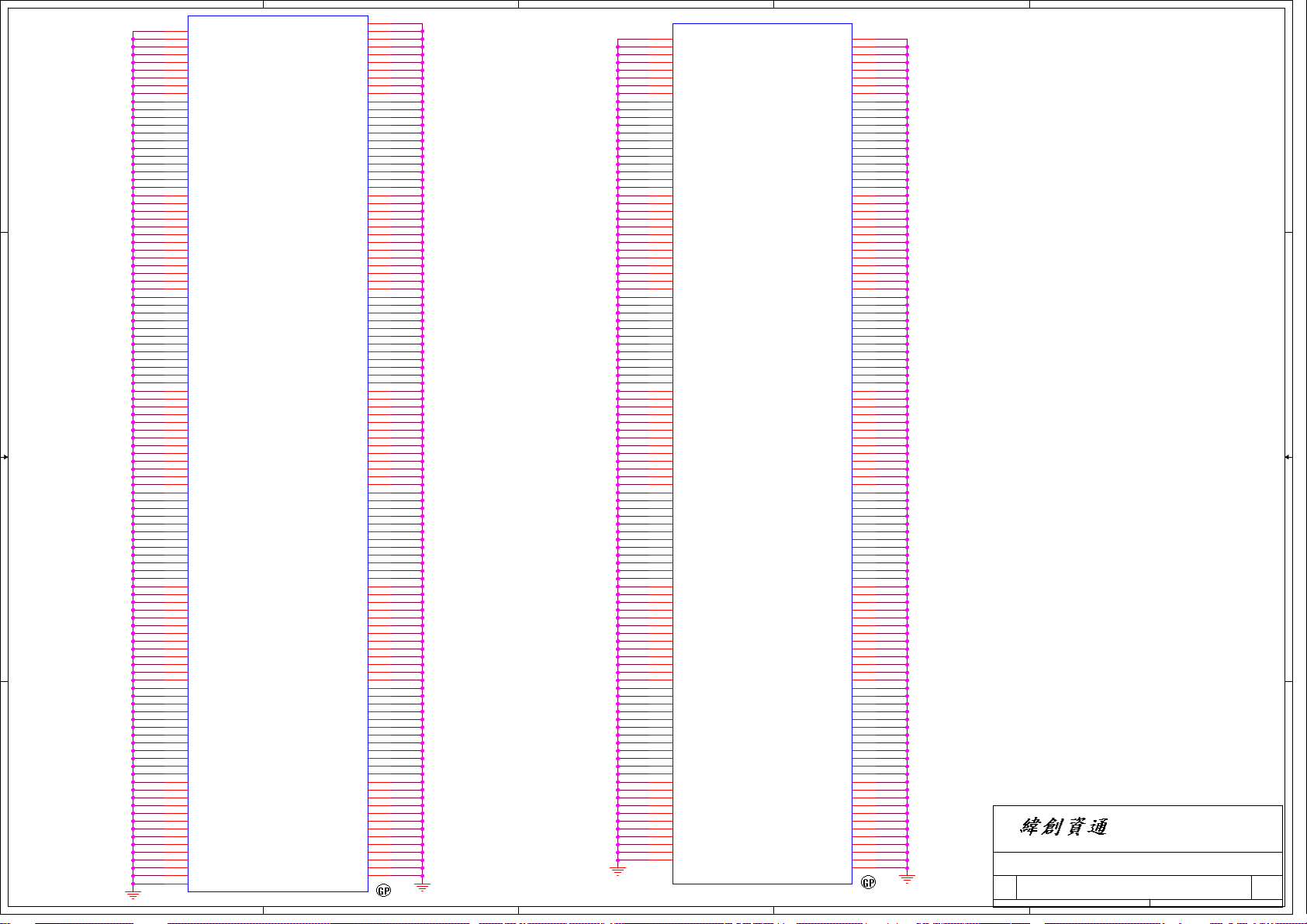

JV10-CS Block Diagram

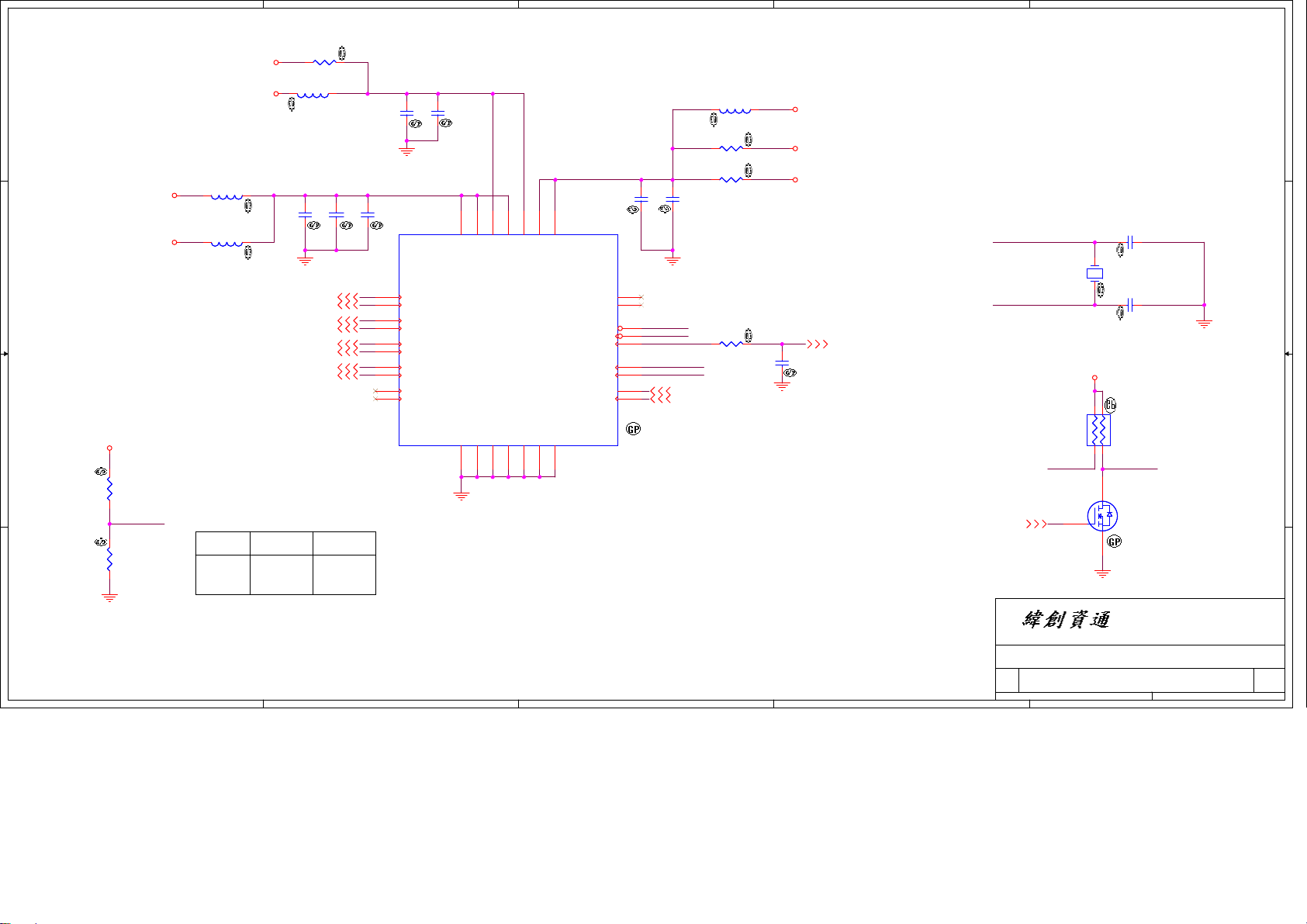

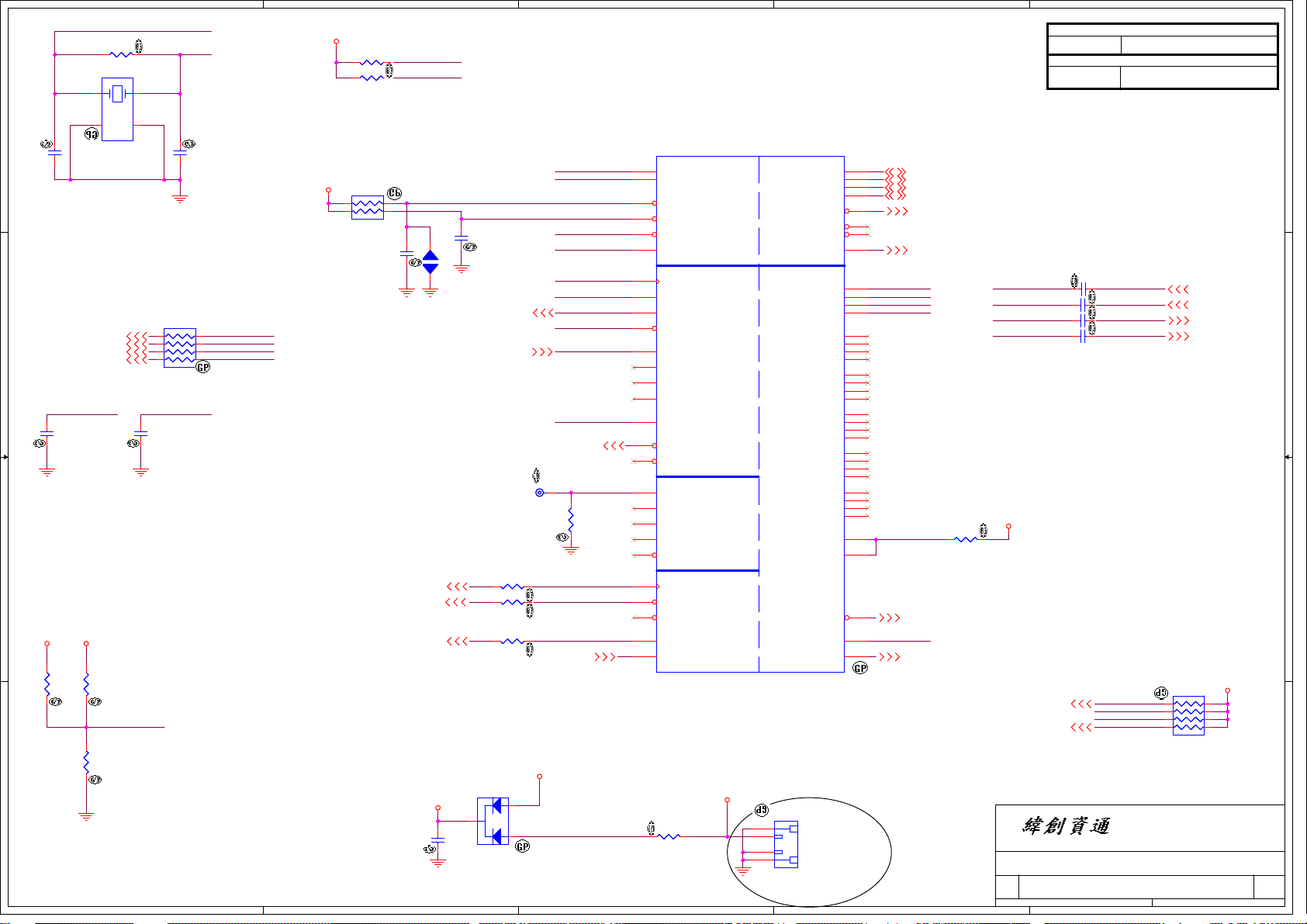

Clock Generator

D D

ICS9LRS3197AKLFT

3

DDRIII

800/1066/1333

DDRIII

800/1066/1333

Slot 0

Slot 1

21

22

4

DDRIII Channel A

DDRIII Channel B

FDIx8

Intel CPU

SFF

4,5,..,10,11

3

DMIx4

2

Project code:91.4GS01.001

PCB P/N :48.4GS01.0SA

REVISION :09918-1

1

SYSTEM DC/DC

RT8223

INPUTS

DCBATOUT

SYSTEM DC/DC

RT8209E

INPUTS

DCBATOUT

OUTPUTS

SYSTEM DC/DC

OUTPUTS

5V_S5

3D3V_S5

1D5V_S3

42

43

RT8209B

Mini-Card

WLAN & 3G

C C

RJ45

CONN

35

32 31

MIC IN

33

Giga LAN

AR8151

HD AUDIO

CODEC

23

INT MIC

35

LINE OUT

B B

ALC271X

PCIE+USB 2.0

PCIE

AZALIA

34

INTEL

PCH

14 USB 2.0/1.1 ports

(10/100/1000Mb)ETHERNET

High Definition Audio

6 SATA ports

8 PCIE ports

ACPI 1.1

LPC I/F

PCI/PCI BRIDGE

RGB CRT

LVDS 2CH

Digital Display

USB 2.0

SATA

CRT

LCD

WXGA+

HDMI

24

23

25

Card Reader

RTS5138

WEBCAM

BLUETOOTH

USB x 3

30

23

38

29,38

SD/MMC

MS/MS Pro/xD

SATA HDD

31

28

INPUTS

DCBATOUT

SYSTEM DC/DC

INPUTS

5V_S5

CPU DC/DC

INPUTS

DCBATOUT

INTERSIL CHARGER

INPUTS

DCBATOUT

OUTPUTS

1D05V_S0

RT9026

OUTPUTS

DDR_VREF_S3

TPS51611

OUTPUTS

VCC_CORE

ISL88731A

OUTPUTS

44

43

41

BT+

45

Flash ROM

4MB

37

JV10 CS

JV10 CS

JV10 CS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

TOP

Power

S

S

GND

BOTTOM

Block Diagram

Block Diagram

Block Diagram

JV10-CS

JV10-CS

JV10-CS

2CH SPEAKER

35

12,13,...,19,20

LPC Bus

SPI

LPC debug

37

KBC

SPI

A A

Flash ROM

36

128KB

26

CPU FAN

5

4

Thermal

Sensor

G795

NPCE781B

26

3

Touch

PAD

36

Int.

38

KB

2

PCB STACKUP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

150Friday, January 22, 2010

150Friday, January 22, 2010

150Friday, January 22, 2010

1

-1

-1

-1

5

4

3

2

1

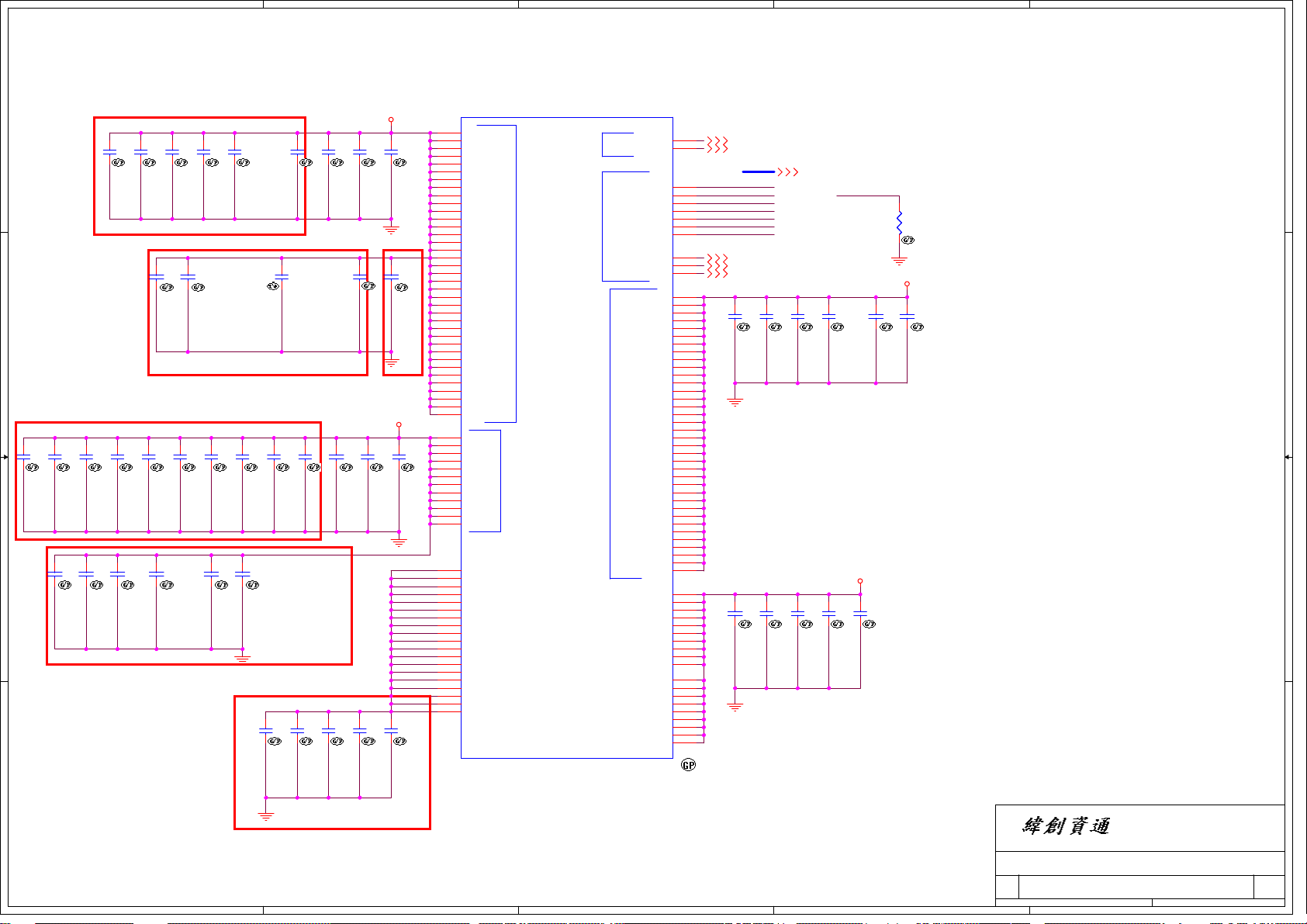

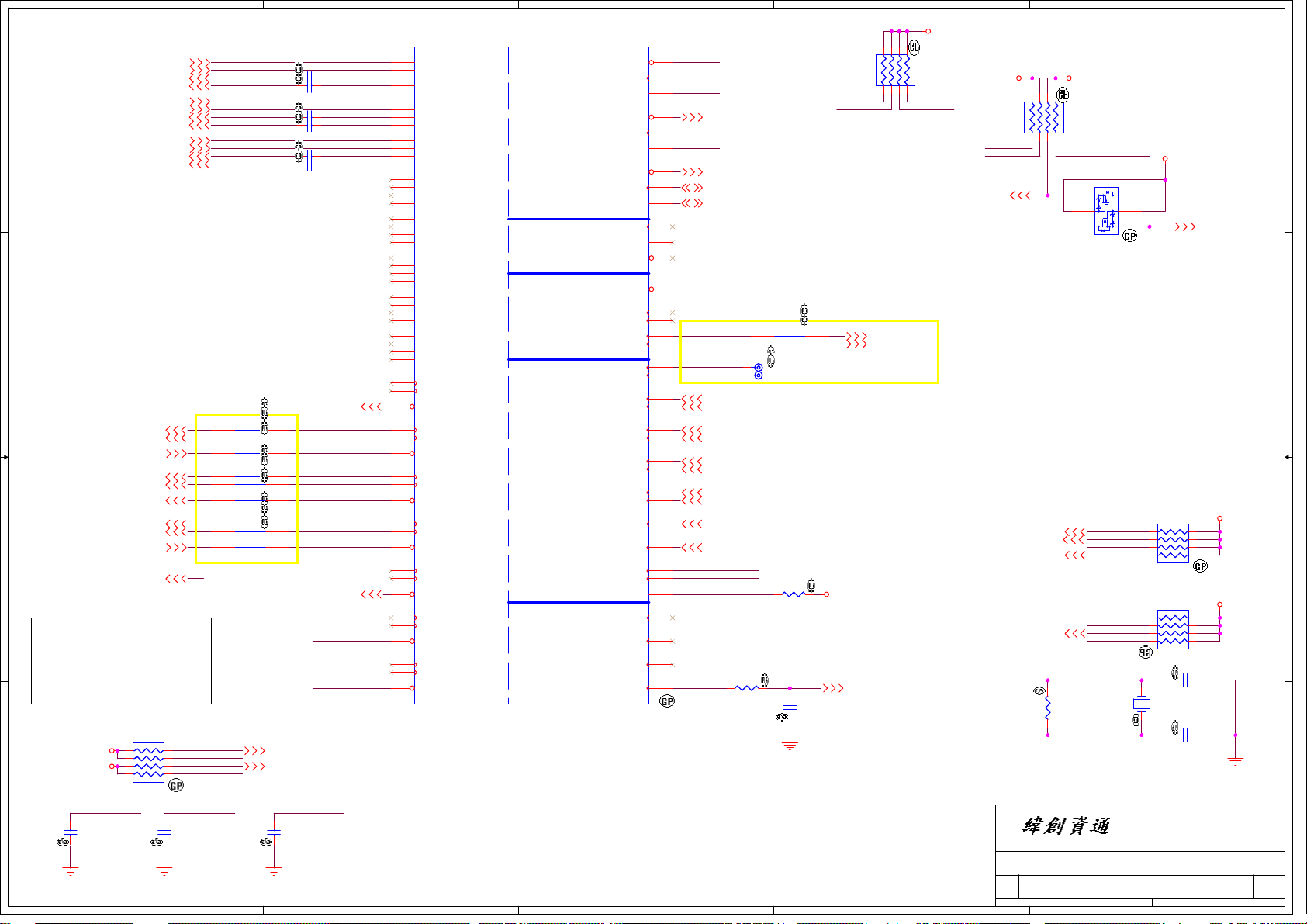

PCH

Strapping

Name Schematics Notes

SPKR

D D

C C

B B

INIT3_3V#

GNT3#/

GPIO55

INTVRMEN

GNT0#,

GNT1#

GNT2#/

GPIO53

GPIO33

SPI_MOSI

NV_ALE

NC_CLE

HAD_DOCK_EN#

/GPIO[33]

HDA_SDO

HDA_SYNC

GPIO15

GPIO8

GPIO27

Reboot option at power-up

Internal weak Pull-down.

Default Mode:

Connect to Vcc3_3 with 8.2-kΩ

No Reboot Mode with TCO Disabled:

- 10-kΩ weak pull-up resistor.

Weak internal pull-down. Do not pull high.

Internal pull-up.

Default Mode:

(Connect to ground with 4.7-kΩ weak

Low (0) = Top Block Swap Mode

pull-down resistor).

High (1) = Integrated VRM is enabled

Low (0) = Integrated VRM is disabled

Left both GNT0# and GNT1# floating. No pull up

Default (SPI):

required.

Connect GNT1# to ground with 1-kΩ pull-down

Boot from PCI:

resistor. Leave GNT0# Floating.

Connect both GNT0# and GNT1# to ground with 1-kΩ

Boot from LPC:

pull-down resistor.

Default - Internal pull-up.

= Configures DMI for ESI compatible operation (for servers

Low (0)

only. Not for mobile/desktops).

Do not pull low.

Default:

Connect to ground with 1-kΩ

Disable ME in Manufacturing Mode:

pull-down resistor.

Connect to Vcc3_3 with 8.2-kΩ weak pull-up resistor.

Enable iTPM:

Left floating, no pull-down required.

Disable iTPM:

Connect to Vcc3_3 with 8.2-kΩ weak pull-up

Enable Danbury:

resistor.

Connect to ground with 4.7-kΩ weak pull-down

Disable Danbury:

resistor.

Weak internal pull-up. Do not pull low.

Flash Descriptor Security will be overridden.

Low (0):

Flash Descriptor Security will be in effect.

High (1) :

Weak internal pull-down. Do not pull high.

Weak internal pull-down. Do not pull high.

Weak internal pull-down. Do not pull high.

Weak internal pull-up. Do not pull low.

Default = Do not connect (floating)

High(1) = Enables the internal VccVRM to have a clean supply for

analog rails. No need to use on-board filter circuit.

Low (0) = Disables the VccVRM. Need to use on-board filter

circuits for analog rails.

Processor Strapping

Pin Name

CFG[4]

CFG[3]

CFG[0]

CFG[7]

Strap Description Configuration (Default value for each bit is

DisplayPort

Presence

PCI-Express Static

Lane Reversal

PCI-Express

Configuration

Select

Reserved Temporarily used

for early

Clarksfield

samples.

1 unless specified otherwise)

Disabled - No Physical Display Port attached to

1:Embedded

Embedded DisplayPort.

Enabled - An external Display Port device is

0:

connected to the Embedded Display Port.

Normal Operation.

1:

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

0:

Single PCI-Express Graphics

1:

Bifurcation enabled

0:

-

Clarksfield (only for early samples pre-ES1)

Connect to GND with 3.01K Ohm/5% resistor

Only temporary for early CFD samples

Note:

(rPGA/BGA) [For details please refer to the WW33

MoW and sighting report].

For a common motherboard design (for AUB and CFD),

the pull-down resistor should be used. Does not

impact AUB functionality.

Power Sequence

U32

1D5V_S3PM_SLP_S4# ALL_PWRGD

RT8209E

U40

1D05V_S0 VTT_PWRGD

RT9025

Default

Value

1

1

1

0

U13

KBC IMVP_VR_EN

NPCE781

USB Table

PCIE Routing

LANE1

LANE2

A A

LAN

MiniCard1

5

Pair

Device

USB3

0

1

USB2

NC

2

MINICARD1

3

4 WECAM

5

NC

6

NC

7

NC

89NC

USB1(HS)

NC

10

11

Blue Tooth

1213MINIC2

Cardreader

4

U77

CPU Core PWM

TPS51161

3

PCH1C

CORE_PWRGDIMVP_VR_EN

PCH

IBEXPEAK

H_PWRGD

CPU1

CPU

AUBURNDALE

PLT_RST#

ALL DEVICE

JV10 CS

JV10 CS

JV10 CS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Table of Content

Table of Content

Table of Content

JV10-CS

JV10-CS

JV10-CS

250Friday, January 22, 2010

250Friday, January 22, 2010

250Friday, January 22, 2010

1

-1

-1

-1

5

R96

將來

RFL1~4

料號申請中

68.00373.001

D D

EC 修正MGB1005G601EBP

1D5V_S0

3D3V_S0

R96

Do Not Stuff

Do Not Stuff

1 2

DY

DY

RFL1

RFL1

MGB1005G601FBP-GP

MGB1005G601FBP-GP

12

-1

-1

Do Not Stuff

Do Not Stuff

3D3V_S0

-1

MGB1005G601FBP-GP

MGB1005G601FBP-GP

1D5V_S0

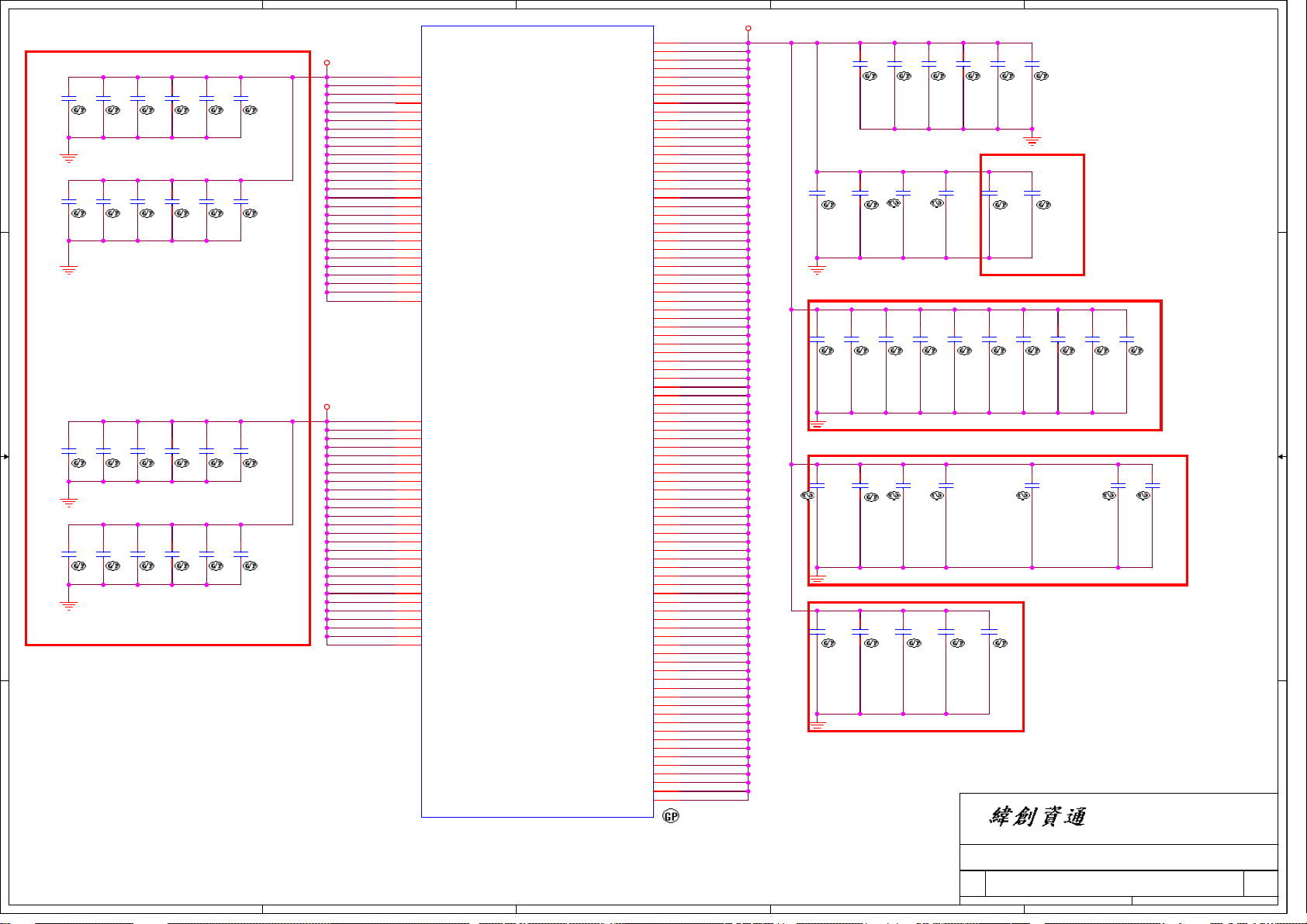

CLK Low Power

C C

CLK Low Power

96 MHz

100 MHz

133-MHz

B B

A A

1D05V_S0

DY

DY

1 2

1 2

R120

R120

Do Not Stuff

Do Not Stuff

FSC

R118

R118

2K2R2J-2-GP

2K2R2J-2-GP

5

RFL3

RFL3

1 2

CLK Normal

CLK Normal

RFL4

RFL4

1 2

PCH

DMI100 MHz

SATA

CLK_CPU_BCLK#13

CPU

FSC 0 1

SPEED

CLK_CPU_BCLK13

133MHz

(Default)

12

12

C239

C239

C227

C227

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DREFCLK#13

DREFCLK13

CLK_DMI#13

CLK_DMI13

CLK_SATA#13

CLK_SATA13

100MHz

4

3D3V_CK505

12

12

C231

C231

C241

C241

SC1U10V2ZY-GP

SC1U10V2ZY-GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_CK505_IO

3D3V_CK505_1

12

C492

C492

Do Not Stuff

Do Not Stuff

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

4

DOT96C_LPR

3

DOT96T_LPR

14

SRCC1_LPR

13

SRCT1_LPR

11

SATAC_LPR

10

SATAT_LPR

22

CPUC0_LPR

23

CPUT0_LPR

19

CPUC1_LPR

20

CPUT1_LPR

U20

U20

ICS9LRS3197AKLFT-GP-U

ICS9LRS3197AKLFT-GP-U

71.93197.003

71.93197.003

2nd = 71.08595.B03

2nd = 71.08595.B03

CLK Lower Power ICS:71.93197.B03,SILEGO:71.08595.003

CLK Lower Power ICS:71.93197.B03,SILEGO:71.08595.003

4

24

VDDCPU_3_3

GND

33

17

VDDSRC_3_3

GNDREF

26

29

VDDREF_3_3

GNDCPU

21

1

VDDDOT96MHZ_3_3

GNDSRC

12

5

VDD_27MHZ

GNDDOT96MHZ

2

15

18

VDDSRC_IO

VDDCPU_IO

27MHZ_NONSS

27MHZ_SS

CPU_STOP#

CLKPWRGD/PD#_3_3

REF_3L/FSLC_3_3

SDATA_3_3

SCLK_3_3

GND27MHZ8GNDSATA

9

X1

X2

3

12

6

7

CPU_STOP#

16

CLK_EN

25

FSC

30

GEN_XTAL_IN

28

GEN_XTAL_OUT

27

31

32

3

-1

R323

R323

Do Not Stuff

Do Not Stuff

R104

R104

Do Not Stuff

Do Not Stuff

12

C230

C230

C224

C224

SC1U10V2ZY-GP

SC1U10V2ZY-GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

PCH_SMBDATA 13,21,22

PCH_SMBCLK 13,21,22

RFL2

RFL2

MGB1005G601FBP-GP

MGB1005G601FBP-GP

12

1 2

DY

DY

1 2

DY

DY

R123

R123

1 2

33R2J-2-GP

33R2J-2-GP

2

1

Normal Pin 15,18----3.3V/1.05V

Low Power Pin 15,18---1.5V/1.05V

Normal Pin 1,17,24---3.3V/1.05V

1D05V_S0

1D5V_S0

3D3V_S0

Low Power Pin 1,17,24---1.5V/1.05V

SAm

JV50上1D05V

上

3D3V

JV70

14.31818M HZ

CL=20pF±0.2pF

GEN_XTAL_IN

X2

X2

X-14D31818M-50GP

X-14D31818M-50GP

82.30005.A51

82.30005.A51

2nd = 82.30005.C51

2nd = 82.30005.C51

GEN_XTAL_OUT

RFC1

RFC1

SC12P50V2JN-3GP

SC12P50V2JN-3GP

CLK_ICH14 13

12

3G

3G

14.318 MHz

2

CPU_STOP#

VR_CLKEN#41

JV10 CS

JV10 CS

JV10 CS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet

C245

C245

SC12P50V2JN-3GP

SC12P50V2JN-3GP

12

12

12

C244

C244

SC12P50V2JN-3GP

SC12P50V2JN-3GP

3D3V_S0

4

RN31

RN31

SRN10KJ-5-GP

SRN10KJ-5-GP

1

2 3

CLK_EN

Q18

Q18

2N7002-11-GP

2N7002-11-GP

G

S D

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Clock Generator

Clock Generator

Clock Generator

JV10-CS

JV10-CS

JV10-CS

1

-1

-1

of

350Friday, January 22, 2010

350Friday, January 22, 2010

350Friday, January 22, 2010

-1

5

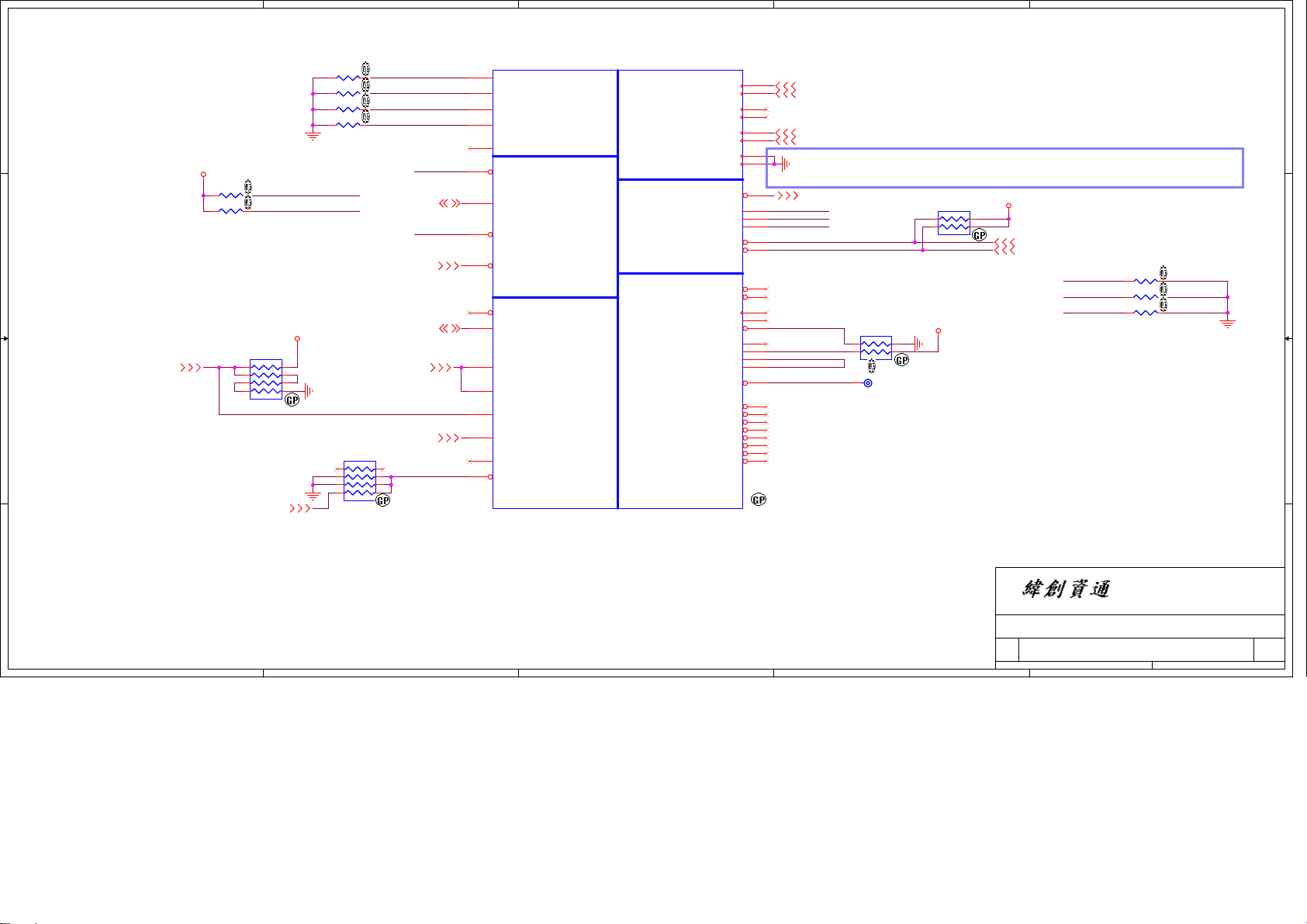

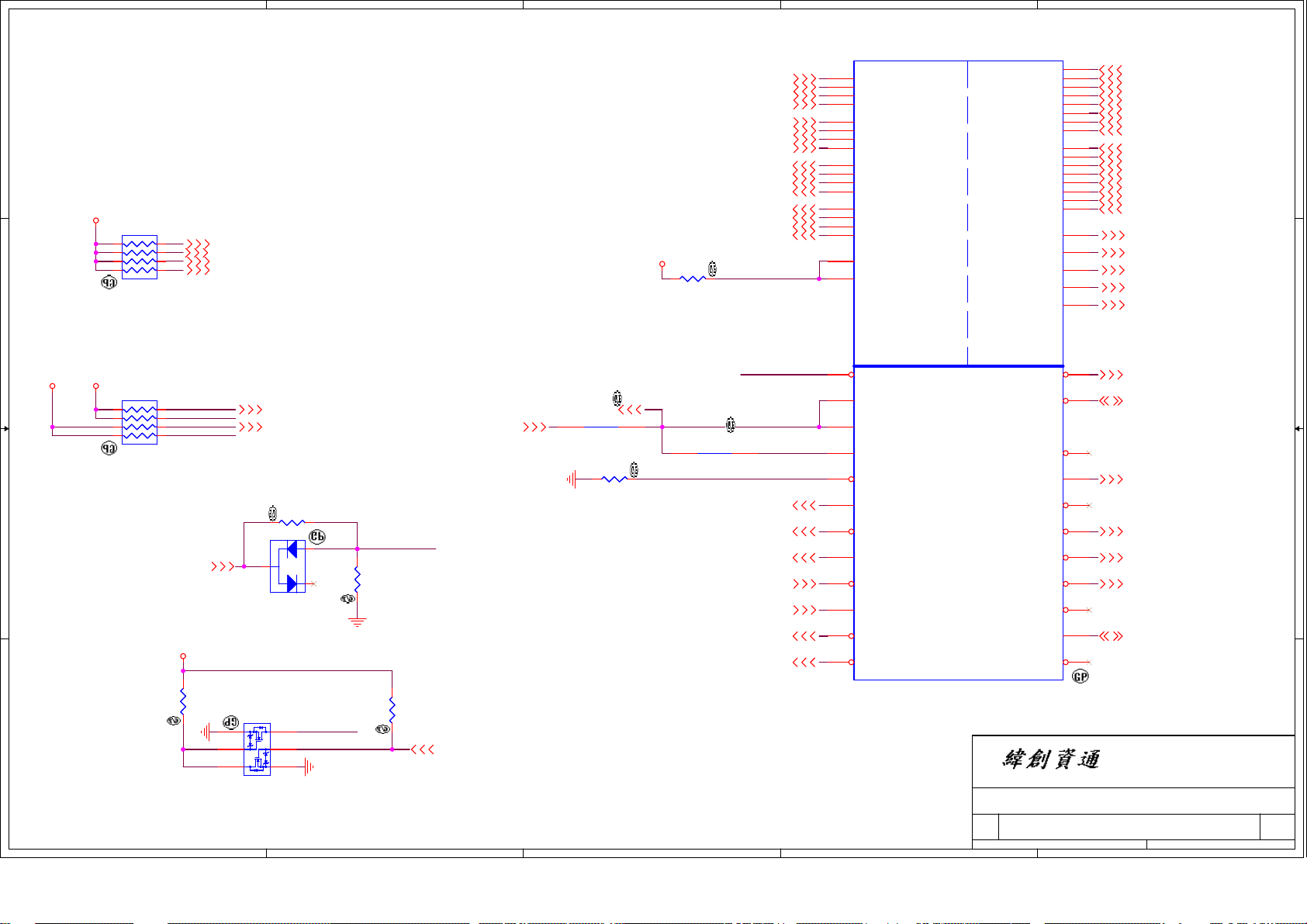

DMI_TXN014

DMI_TXN114

DMI_TXN214

DMI_TXN314

D D

C C

B B

A A

5

DMI_TXP014

DMI_TXP114

DMI_TXP214

DMI_TXP314

DMI_RXN014

DMI_RXN114

DMI_RXN214

DMI_RXN314

DMI_RXP014

DMI_RXP114

DMI_RXP214

DMI_RXP314

FDI_TXN014

FDI_TXN114

FDI_TXN214

FDI_TXN314

FDI_TXN414

FDI_TXN514

FDI_TXN614

FDI_TXN714

FDI_TXP014

FDI_TXP114

FDI_TXP214

FDI_TXP314

FDI_TXP414

FDI_TXP514

FDI_TXP614

FDI_TXP714

FDI_FSYNC014

FDI_FSYNC114

FDI_INT14

FDI_LSYNC014

FDI_LSYNC114

4

CPU1A

CPU1A

F7

DMI_RX#0

J8

DMI_RX#1

K8

DMI_RX#2

J4

DMI_RX#3

F9

DMI_RX0

J6

DMI_RX1

K9

DMI_RX2

J2

DMI_RX3

H17

DMI_TX#0

K15

DMI_TX#1

J13

DMI_TX#2

F10

DMI_TX#3

G17

DMI_TX0

M15

DMI_TX1

G13

DMI_TX2

J11

DMI_TX3

L2

FDI_TX#0

N7

FDI_TX#1

M4

FDI_TX#2

P1

FDI_TX#3

N10

FDI_TX#4

R7

FDI_TX#5

U7

FDI_TX#6

W8

FDI_TX#7

K1

FDI_TX0

N5

FDI_TX1

N2

FDI_TX2

R2

FDI_TX3

N9

FDI_TX4

R8

FDI_TX5

U6

FDI_TX6

W10

FDI_TX7

AC7

FDI_FSYNC0

AC9

FDI_FSYNC1

AB5

FDI_INT

AA1

FDI_LSYNC0

AB2

FDI_LSYNC1

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

4

DMI

DMI

Intel(R) FDI

Intel(R) FDI

3

1 OF 10

1 OF 10

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

3

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

B12

A13

D12

B11

G40

G38

H34

P34

G28

H25

H24

D29

B26

D26

B23

D22

A20

D19

A17

B14

F40

J38

G34

M34

J28

G25

K24

B28

A27

B25

A24

B21

B19

B18

B16

D15

N40

L38

M32

D40

A38

G32

B33

B35

L30

A31

B32

L28

N26

M24

G21

J20

L40

N38

N32

B39

B37

H32

A34

D36

J30

B30

D33

N28

M25

N24

F21

L20

PEG_IRCOMP_R

EXP_RBIAS

2

1 2

1 2

JV10 CS

JV10 CS

JV10 CS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

2

1

R232

R232

49D9R2F-GP

49D9R2F-GP

R229

R229

750R2F-GP

750R2F-GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU SFF 1 of 8(DMI/FDI/PEG)

CPU SFF 1 of 8(DMI/FDI/PEG)

CPU SFF 1 of 8(DMI/FDI/PEG)

JV10-CS

JV10-CS

JV10-CS

450Friday, January 22, 2010

450Friday, January 22, 2010

450Friday, January 22, 2010

of

of

of

1

-1

-1

-1

5

1 2

1D5V_S3

8

7

6

1 2

1 2

1 2

H_CATERR#

PROCHOT#

1

2

3

4 5

RN60

RN60

SRN1K5J-1-GP

SRN1K5J-1-GP

D D

1D05V_S0

R257

1 2

1 2

C C

PM_DRAM_PWRGD14

B B

R257

49D9R2F-GP

49D9R2F-GP

R256

R256

68R2-GP

68R2-GP

RN61

RN61

SRN1KJ-10-GP-U

SRN1KJ-10-GP-U

1

2

3

4 5

PLT_RST#16,31,33,36,37,39,49

4

R254

R254

20R2F-GP

20R2F-GP

R255

R255

20R2F-GP

20R2F-GP

R253

R253

49D9R2F-GP

49D9R2F-GP

R73

R73

49D9R2F-GP

49D9R2F-GP

PM_THRMTRIP-A#17,39

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_CATERR#

H_PECI17

PROCHOT#

H_PM_SYNC14

H_PWRGD17,49

From PCH

H_VTTPWRGD44

8

PLT_RST#_R

7

6

CPU1B

CPU1B

AD71

COMP3

AC70

COMP2

AD69

COMP1

AE66

COMP0

M71

PROC_DETECT

N61

CATERR#

N19

PECI

N67

PROCHOT#

N17

THERMTRIP#

N70

RESET_OBS#

M17

PM_SYNC

AM7

VCCPWRGOOD_1

Y67

VCCPWRGOOD_0

AM5

SM_DRAMPWROK

H15

VTTPWRGOOD

Y70

TAPPWRGOOD

G3

RSTIN#

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

3

2 OF 10

2 OF 10

Misc

Misc

BCLK_ITP#

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

Clocks

Clocks

Thermal

Thermal

DDR3

DDR3

Power Management

Power Management

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PM_EXT_TS#0

PM_EXT_TS#1

Misc

Misc

JTAG & MBP

JTAG & MBP

BCLK

BCLK#

BCLK_ITP

PEG_CLK

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

TDI_M

TDO_M

DBR#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

AK7

AK8

K71

J70

L21

J21

Y2

W4

BJ12

BV33

BP39

BV40

AV66

AV64

U71

U69

T67

N65

P69

T69

TDI

T71

P71

T70

W71

J69

J67

J62

K65

K62

J64

K69

M69

2

BCLK_CPU_P 17

BCLK_CPU_N 17

CLK_EXP_P_R 13

CLK_EXP_N_R 13

If supports integrated graphics but without Embedded DisplayPort(eDP), these pins can

also be connected to GND directly.

DDR3_DRAMRST# 21,22

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

XDP_TRST#

XDP_TDO

XDP_TDI_TDO_M

XDP_DBRESET#

RN64

RN64

SRN56J-4-GP

SRN56J-4-GP

1

2 3

1

RN26

RN26

SRN10KJ-5-GP

SRN10KJ-5-GP

1

2 3

1D05V_S0

4

TP24 Do Not StuffTP24 Do Not Stuff

4

1D05V_S0

PM_EXTTS#0_R 21

PM_EXTTS#1_R 22

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

1

Refer JV50 CP

R245 100R2F-L1-GP-UR245 100R2F-L1-GP-U

1 2

R246 24D9R2F-L-GPR246 24D9R2F-L-GP

1 2

R247 130R2F-1-GPR247 130R2F-1-GP

1 2

SB

JV10 CS

JV10 CS

JV10 CS

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

CPU SFF 2 of 8(CLK/Thermal)

CPU SFF 2 of 8(CLK/Thermal)

CPU SFF 2 of 8(CLK/Thermal)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

JV10-CS

JV10-CS

JV10-CS

550Friday, January 22, 2010

550Friday, January 22, 2010

550Friday, January 22, 2010

1

-1

-1

of

-1

5

CPU1C

CPU1C

4

3 OF 10

3 OF 10

3

CPU1D

CPU1D

2

4 OF 10

4 OF 10

1

BM34

SA_CK0

M_A_DQ[63..0]21

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS021

M_A_BS121

M_A_BS221

M_A_CAS#21

M_A_RAS#21

M_A_WE#21

AT8

AT6

BB5

BB9

AV7

AV6

BE6

BE8

BF11

BE11

BK5

BH13

BF9

BF6

BK7

BN8

BN11

BN9

BG17

BK15

BK9

BG15

BH17

BK17

BN20

BN17

BK25

BH25

BJ20

BH21

BG24

BG25

BJ40

BM43

BF47

BF48

BN40

BH43

BN44

BN47

BN48

BN51

BH53

BJ55

BH48

BJ48

BM53

BN55

BF55

BN57

BN65

BJ61

BF57

BJ57

BK64

BK61

BJ63

BF64

BB64

BB66

BJ66

BF65

AY64

BC70

BT38

BH38

BF21

BK43

BL38

BF38

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK#0

SA_CKE0

SA_CK1

SA_CK#1

SA_CKE1

SA_CS#0

SA_CS#1

SA_ODT0

SA_ODT1

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

BP35

BF20

BK36

BH36

BK24

BH40

BJ47

BF43

BL47

BB10

BJ10

BM15

BN24

BG44

BG53

BN62

BH59

AY5

BJ7

BN13

BL21

BH44

BK51

BP58

BE62

AY7

BJ5

BL13

BN21

BK44

BH51

BM60

BE64

BT36

BP33

BV36

BG34

BG32

BN32

BK32

BJ30

BN30

BF28

BH34

BH30

BJ28

BF40

BN28

BN25

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 21

M_CLK_DDR#0 21

M_CKE0 21

M_CLK_DDR1 21

M_CLK_DDR#1 21

M_CKE1 21

M_CS#0 21

M_CS#1 21

M_ODT0 21

M_ODT1 21

M_A_DM[7..0] 21

M_A_DQS#[7..0] 21

M_A_DQS[7..0] 21

M_A_A[15..0] 21

M_B_DQ[63..0]22

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS022

M_B_BS122

M_B_BS222

M_B_CAS#22

M_B_RAS#22

M_B_WE#22

BA2

AW2

BD1

BE4

AY1

BC2

BF2

BH2

BG4

BG1

BR6

BR8

BK2

BU9

BV10

BR10

BT12

BT15

BV15

BV12

BP12

BV17

BU16

BP15

BU19

BV22

BT22

BP19

BV19

BV20

BT20

BT48

BV48

BV50

BP49

BT47

BV52

BV54

BT54

BP53

BU53

BT59

BT57

BP56

BT55

BU60

BV59

BV61

BP60

BR66

BR64

BR62

BT61

BN68

BL69

BJ71

BF70

BG71

BC67

BK70

BK67

BD71

BD69

BV43

BV41

BV24

BU46

BT40

BT41

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

BJ4

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_BS0

SB_BS1

SB_BS2

SB_CAS#

SB_RAS#

SB_WE#

SB_CK0

SB_CK#0

SB_CKE0

SB_CK1

SB_CK#1

SB_CKE1

SB_CS#0

SB_CS#1

SB_ODT0

SB_ODT1

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

BU33

BV34

BT26

BV38

BU39

BT24

BP46

BT43

BV45

BU49

BB4

BL4

BT13

BP22

BV47

BV57

BU65

BF67

BE2

BM3

BU12

BT19

BT52

BV55

BU63

BG69

BD4

BN4

BV13

BT17

BT50

BU56

BV62

BJ69

BT34

BP30

BV29

BU30

BV31

BT33

BT31

BP26

BV27

BT27

BU42

BU26

BT29

BT45

BV26

BU23

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_CLK_DDR2 22

M_CLK_DDR#2 22

M_CKE2 22

M_CLK_DDR3 22

M_CLK_DDR#3 22

M_CKE3 22

M_CS#2 22

M_CS#3 22

M_ODT2 22

M_ODT3 22

M_B_DM[7..0] 22

M_B_DQS#[7..0] 22

M_B_DQS[7..0] 22

M_B_A[15..0] 22

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

A A

5

4

3

AUBURNDALE-1-GP-U3-NF

2

JV10 CS

JV10 CS

JV10 CS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU SFF 3 of 8(DDR)

CPU SFF 3 of 8(DDR)

CPU SFF 3 of 8(DDR)

JV10-CS

JV10-CS

JV10-CS

650Friday, January 22, 2010

650Friday, January 22, 2010

650Friday, January 22, 2010

1

-1

-1

-1

5

4

3

2

1

1-k? pull-up to VTT and 1-k? pull-down to GND for POC.

1D05V_VTT

D D

C C

B B

Please note that the VTT Rail

CPU_Core_VID[6..0]41

VCC_CORE

RN25

RN25

SRN100J-3-GP

SRN100J-3-GP

1

2 3

4

1D5V_S3

1 2

L5

L5

IND-1UH-2-GP

IND-1UH-2-GP

Values are Auburndale

CPU_Core_VID0

CPU_Core_VID1

CPU_Core_VID2

CPU_Core_VID3

CPU_Core_VID4

CPU_Core_VID5

CPU_Core_VID6

PM_DPRSLPVR41

IMVP_IMON41

VCC_SENSE41

VSS_SENSE41

VTT_SENSE44

PSI#41

TP25

TP25

Do Not Stuff

Do Not Stuff

1D8V_S0

VDDQ_CK

12

C145

C145

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

VTT=1.05V; Clarksfield

VTT=1.1V

SB

1

C109

C109

F68

A61

D61

D62

A62

B63

D64

D66

AN1

F66

A41

F64

F63

N13

R12

W39

W37

U37

R39

R37

BB14

BB12

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

CPU1F

CPU1F

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VTT_SELECT1

PROC_DPRSLPVR

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

1.8V

VCCPLL

VCCPLL

VCCPLL

VCCPLL

VCCPLL

VDDQ_CK1

VDDQ_CK2

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

1.8V

SENSE LINESCPU VIDS

SENSE LINESCPU VIDS

1.1V RAIL POWER

1.1V RAIL POWER

POWER

POWER

6 OF 10

6 OF 10

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

SAM JV50 JV70 接到CPU Core PSI#check list

AW14

AW12

AU60

AU59

AU12

AR60

AR59

AR12

AN60

AN59

AN35

AN33

AN17

AN15

AN14

AN12

AM10

AL60

AL59

AL17

AL15

AL14

AL12

AK35

AK33

AF39

AF37

AF35

AF33

AF32

AF30

AD39

BF60

BF59

BD60

BD59

BB60

BB59

AY60

AW60

AW35

AW33

AD37

AD35

AD33

AD32

AD30

W35

W33

W32

W30

W28

W26

W24

W23

U35

U33

U32

U30

U28

U26

U24

U23

R35

R33

R32

R30

R28

R26

R24

R23

AY10

AN9

1D05V_S0

12

C405

C405

12

C180

C180

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C117

C117

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C182

C182

C181

C181

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C137

C137

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C185

C185

JV10 CS

JV10 CS

JV10 CS

12

C131

C131

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C141

C141

C134

C134

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

5

4

3

2

CPU SFF 4 of 8(POWER/VTT)

CPU SFF 4 of 8(POWER/VTT)

CPU SFF 4 of 8(POWER/VTT)

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

JV10-CS

JV10-CS

JV10-CS

of

of

of

750Friday, January 22, 2010

750Friday, January 22, 2010

750Friday, January 22, 2010

1

-1

-1

-1

5

4

3

2

1

-1

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

DY

DY

C488

C488

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C441

C441

Do Not Stuff

Do Not Stuff

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C450

C450

12

C458

C458

modify C441

12

C437

C437

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C451

C451

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C459

C459

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C187

C187

12

C452

C452

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C491

C491

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

VCC_GFXCORE

12

12

C122

C122

C121

C121

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C128

C128

C125

C125

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SB

12

12

C114

C443

C443

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

12

C132

C132

C453

C453

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C188

C188

C189

C189

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C114

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

1D05V_S0

12

12

C110

C110

C108

C108

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

VCAP2

12

12

C190

C190

C191

C191

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

AN32

AN30

AN28

AN26

AN24

AN23

AN21

AN19

AL32

AL30

AL28

AL26

AL24

AL23

AL21

AL19

AK14

AK12

AJ10

AH14

AH12

AF28

AF26

AF24

AF23

AF21

AF19

AF17

AF15

AF14

AD28

AD26

AD24

AD23

AD21

AD19

AD17

W21

W19

U21

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

U19

U17

U15

U14

U12

R21

R19

R17

R15

AK62

AK60

AK59

AH60

AH59

AF60

AF59

AD60

AD59

AB60

AB59

AA60

AA59

W60

W59

U60

U59

R60

R59

CPU1G

CPU1G

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

VCAP2

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

GRAPHICS

GRAPHICS

PEG & DMI

PEG & DMI

POWER

POWER

SENSE

SENSE

GRAPHICS VIDs

GRAPHICS VIDs

7 OF 10

7 OF 10

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

AF12

AF10

AF71

AG67

AG70

AH71

AN71

AM67

AM70

AH69

AL71

AL69

BU40

BU35

BU28

BN38

BM25

BL30

BJ38

BH32

BH28

BG43

BF16

BF15

BD35

BD33

BD32

BD30

BD28

BD26

BD24

BD23

BD21

BD19

BD17

BD15

BB35

BB33

BB32

BB30

BB28

BB26

BB24

BB23

BB21

BB19

BB17

BB15

AW32

AW30

AW28

AW26

AW24

AW23

AW21

AW19

AW17

AW15

AD15

AD14

AD12

AB12

AA12

W17

W15

W14

W12

VAXG_SENSE

VSSAXG_SENSE

LINES

LINES

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

VTT0_DDR

VTT0_DDR

VTT0_DDR

VTT0_DDR

VTT0_DDR

VTT0_DDR

VTT0_DDR

VTT0_DDR

VTT0_DDR

VTT0_DDR

VCC_AXG_SENSE 46

VSS_AXG_SENSE 46

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

GFX_VR_EN 46

GFX_DPRSLPVR 46

GFX_IMON 46

12

12

C123

C123

C115

C115

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C120

C120

C107

C107

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

GFX_VID[6..0] 46

12

C127

C127

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C116

C116

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

GFX_VR_EN

12

C133

C133

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

1D05V_S0

12

C124

C124

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

R203

R203

4K7R2J-2-GP

4K7R2J-2-GP

1D5V_S3

12

12

C136

C136

C126

C126

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C135

C135

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

D D

-1

modify C487 C491 C443

C C

SB

12

12

C438

C438

12

C439

C439

C440

C440

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C487

C487

Do Not Stuff

Do Not Stuff

DY

DY

SB

12

C444

C444

SB

B B

12

12

C446

C446

C445

C445

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C454

C454

C455

C455

Do Not Stuff

Do Not Stuff

DY

DY

-1

modify C457 C454

12

12

C447

C447

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C456

C456

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C448

C448

C449

C449

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C457

C457

Do Not Stuff

Do Not Stuff

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

A A

Do not dummy these CAPs

5

4

3

2

JV10 CS

JV10 CS

JV10 CS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU SFF 5 of 8(PWR/DDR/GFX/)

CPU SFF 5 of 8(PWR/DDR/GFX/)

CPU SFF 5 of 8(PWR/DDR/GFX/)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

JV10-CS

JV10-CS

JV10-CS

1

850Friday, January 22, 2010

850Friday, January 22, 2010

850Friday, January 22, 2010

-1

-1

-1

5

VCAP0

12

12

12

12

12

C176

C176

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C174

C174

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C177

C177

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C172

C172

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C165

C165

C163

C163

C164

12

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C162

C162

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C164

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C178

C178

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C173

C173

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

D D

12

12

C166

C166

C179

C179

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

Sam

C C

Processor package decoupling DO NOT connect to any power rail

VCAP1

12

12

12

C149

C149

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C144

C144

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C158

C158

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C147

C147

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C155

C155

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C142

C142

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

B B

A A

12

12

C153

C153

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C143

C143

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

5

C151

C151

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C156

C156

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C148

C148

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C157

C157

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

4

CPU1H

CPU1H

BD55

VCAP0

BD51

VCAP0

BD48

VCAP0

BB55

VCAP0

BB51

VCAP0

BB48

VCAP0

AY57

VCAP0

AY53

VCAP0

AY50

VCAP0

AW57

VCAP0

AW53

VCAP0

AW50

VCAP0

AU55

VCAP0

AU51

VCAP0

AU48

VCAP0

AR55

VCAP0

AR51

VCAP0

AR48

VCAP0

AN57

VCAP0

AN53

VCAP0

AN50

VCAP0

AL57

VCAP0

AL53

VCAP0

AL50

VCAP0

AK57

VCAP0

AK53

VCAP0

AK50

VCAP0

BD44

VCAP1

BD41

VCAP1

BD37

VCAP1

BB44

VCAP1

BB41

VCAP1

BB37

VCAP1

AY46

VCAP1

AY42

VCAP1

AY39

VCAP1

AW46

VCAP1

AW42

VCAP1

AW39

VCAP1

AU44

VCAP1

AU41

VCAP1

AU37

VCAP1

AR44

VCAP1

AR41

VCAP1

AR37

VCAP1

AN46

VCAP1

AN42

VCAP1

AN39

VCAP1

AL46

VCAP1

AL42

VCAP1

AL39

VCAP1

AK46

VCAP1

AK42

VCAP1

AK39

VCAP1

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

4

POWER

POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

3

8 OF 10

8 OF 10

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

3

AF57

AF55

AF53

AF51

AF50

AF48

AF46

AF44

AF42

AF41

AD55

AD51

AD48

AD44

AD41

AB55

AB51

AB48

AB44

AB41

AA55

AA51

AA48

AA44

AA41

W55

W51

W48

W44

W41

U55

U51

U48

U44

U41

R55

R51

R48

R44

R41

P60

N55

N51

N48

N44

N42

M60

M51

M44

L55

K60

K51

K44

J55

H60

H51

H44

G60

G55

G51

G44

F55

E60

E57

E53

E50

E46

E42

D59

D57

D55

D54

D52

D50

D48

D47

D45

D43

B60

B56

B53

B49

B46

B42

A57

A54

A50

A47

A43

VCC_CORE

DY

DY

12

12

12

12

C186

C186

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C463

C463

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C473

C473

Do Not Stuff

Do Not Stuff

C482

C482

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C175

C175

12

C169

C169

C464

C464

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C474

C474

12

C483

C483

2

12

C161

C161

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

DY

DY

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C465

C465

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

2

12

Do Not Stuff

Do Not Stuff

C146

C146

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C466

C466

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C475

C475

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C484

C484

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

1

-1

12

12

C152

C152

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

DY

DY

C154

C154

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C160

C160

Do Not Stuff

Do Not Stuff

12

DY

DY

C168

C168

C150

C150

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

Do Not Stuff

Do Not Stuff

DY

DY

12

C140

C140

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C167

C167

Do Not Stuff

Do Not Stuff

modify C160 C161

-1

modify C167 C168

SB

12

12

12

12

12

C467

C467

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C468

C468

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C469

C469

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C470

C470

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C471

C471

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C472

C472

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SB

12

C476

C476

Do Not Stuff

Do Not Stuff

DY

DY

12

C485

C485

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

JV10 CS

JV10 CS

JV10 CS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

12

C478

C478

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

-1

SB

12

C486

C486

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

CPU SFF 6 of 8(CPUCORE)

CPU SFF 6 of 8(CPUCORE)

CPU SFF 6 of 8(CPUCORE)

modify C477 C479 C476 C473

12

12

C480

C480

C481

C481

Do Not Stuff

Do Not Stuff

SC10U10V5ZY-1GP

DY

DY

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

JV10-CS

JV10-CS

JV10-CS

SC10U10V5ZY-1GP

950Friday, January 22, 2010

950Friday, January 22, 2010

950Friday, January 22, 2010

of

of

1

of

-1

-1

-1

5

CPU1E

CPU1E

5 OF 10

5 OF 10

RSVD#W66

RSVD#W64

4

W66

W64

3

2

1

D D

CFG0

CFG3

C C

B B

A A

AL4

CFG0

AM2

CFG1

AK1

CFG2

AK2

CFG3

AK4

CFG4

AJ2

CFG5

AT2

CFG6

AG7

CFG7

AF4

CFG8

AG2

CFG9

AH1

CFG10

AC2

CFG11

AC4

CFG12

AE2

CFG13

AD1

CFG14

AF8

CFG15

AF6

CFG16

AB7

CFG17

AU1

RSVD_TP0

T4

RSVD#T4

T2

RSVD#T2

U1

RSVD#U1

V2

RSVD#V2

AV71

RSVD#AV71

AW70

RSVD#AW70

AY69

RSVD#AY69

BB69

RSVD#BB69

D8

RSVD#D8

B7

RSVD#B7

A10

RSVD#A10

B9

RSVD#B9

C5

RSVD_NCTF#C5

A6

RSVD_NCTF#A6

E3

RSVD_NCTF#E3

F1

RSVD_NCTF#F1

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

5

RESERVED

RESERVED

NCTF_DC_TEST#BV71

NCTF_DC_TEST#BV69

NCTF_DC_TEST#BV68

NCTF_DC_TEST#BT71

NCTF_DC_TEST#BR71

NCTF TEST PIN:

A5,A68,A69,A71,C3,C71,E1,E71,BR1,BR71,

NCTF TEST PIN:

A5,A68,A69,A71,C3,C71,E1,E71,BR1,BR71,

BT1,BT71,BV1,BV3,BV5,BV68,BV69,BV71

BT1,BT71,BV1,BV3,BV5,BV68,BV69,BV71

RSVD#AC69

RSVD#AC71

RSVD#AA71

RSVD#AA69

RSVD#R66

RSVD#R64

RSVD_NCTF#BT5

RSDV_NCTF#BR5

RSDV_NCTF#BV6

RSDV_NCTF#BV8

RSVD#AV69

RSVD#AK71

RSVD#AN69

RSVD#AP66

RSVD#AH66

RSVD#AK66

RSVD#AR71

RSVD#AM66

RSVD#AK69

RSVD#AU71

RSVD#AT70

RSVD#AR69

RSVD#AU69

RSVD#AT67

RSVD_TP2

RSVD_TP1

RSVD#AV4

RSVD#AU2

RSVD#BE69

RSVD#BE71

NCTF_DC_TEST#BV5

NCTF_DC_TEST#BV3

NCTF_DC_TEST#BV1

DC_TEST_BT69

DC_TEST_BT3

NCTF_DC_TEST#BT1

NCTF_DC_TEST#BR1

NCTF_DC_TEST#E71

NCTF_DC_TEST#E1

NCTF_DC_TEST#C71

DC_TEST_C69

NCTF_DC_TEST#C3

NCTF_DC_TEST#A71

NCTF_DC_TEST#A69

NCTF_DC_TEST#A68

NCTF_DC_TEST#A5

AC69

AC71

AA71

AA69

R66

R64

BT5

BR5

BV6

BV8

AV69

AK71

AN69

AP66

AH66

AK66

AR71

AM66

AK69

AU71

AT70

AR69

AU69

AT67

AP2

AN7

AV4

AU2

BE69

BE71

TP27

1

1

1

1

TP27

Do Not Stuff

Do Not Stuff

TP20

TP20

Do Not Stuff

Do Not Stuff

TP21

TP21

Do Not Stuff

Do Not Stuff

TP26

TP26

Do Not Stuff

Do Not Stuff

3

BV71

BV69

BV68

BV5

BV3

BV1

BT71

BT69

BT3

BT1

BR71

BR1

E71

E1

C71

C69

C3

A71

A69

A68

A5

4

CFG0

CFG3

DY

DY

DY

DY

12

12

R216

R216

Do Not Stuff

Do Not Stuff

R217

R217

Do Not Stuff

Do Not Stuff

PCI-Express Configuration Select

CFG0

1:Single PEG

0:Bifurcation enabled

CFG3 - PCI-Express Static Lane Reversal

CFG3

1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

JV10 CS

JV10 CS

JV10 CS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

CPU SFF 7 of 8(RESERVED)

CPU SFF 7 of 8(RESERVED)

CPU SFF 7 of 8(RESERVED)

JV10-CS

JV10-CS

JV10-CS

2

10 50Friday, January 22, 2010

10 50Friday, January 22, 2010

10 50Friday, January 22, 2010

of

of

of

1

-1

-1

-1

5

D D

C C

B B

A A

5

CPU1I

CPU1I

BU62

VSS

BU58

VSS

BU55

VSS

BU51

VSS

BU48

VSS

BU44

VSS

BU37

VSS

BU32

VSS

BU25

VSS

BU21

VSS

BU18

VSS

BU14

VSS

BU11

VSS

BU7

VSS

BP42

VSS

BN64

VSS

BN6

VSS

BM70

VSS

BM51

VSS

BM44

VSS

BM32

VSS

BM24

VSS

BM17

VSS

BL57

VSS

BL55

VSS

BL48

VSS

BL40

VSS

BL28

VSS

BL20

VSS

BK63

VSS

BK60

VSS

BK53

VSS

BK34

VSS

BK10

VSS

BJ64

VSS

BJ21

VSS

BJ9

VSS

BJ1

VSS

BH70

VSS

BH57

VSS

BH55

VSS

BH47

VSS

BH24

VSS

BH20

VSS

BH15

VSS

BG51

VSS

BG36

VSS

BF62

VSS

BF30

VSS

BF13

VSS

BF8

VSS

BE70

VSS

BE65

VSS

BE9

VSS

BE1

VSS

BD57

VSS

BD53

VSS

BD50

VSS

BD46

VSS

BD42

VSS

BD39

VSS

BD14

VSS

BB71

VSS

BB62

VSS

BB57

VSS

BB53

VSS

BB50

VSS

BB46

VSS

BB42

VSS

BB39

VSS

BB7

VSS

BB1

VSS

BA70

VSS

AY71

VSS

AY66

VSS

AY62

VSS

AY59

VSS

AY55

VSS

AY51

VSS

AY48

VSS

AR42

VSS

AR39

VSS

AR35

VSS

AR33

VSS

AR32

VSS

AR30

VSS

AR28

VSS

AR26

VSS

AR24

VSS

AR23

VSS

AR21

VSS

AR19

VSS

AR17

VSS

AR15

VSS

AR14

VSS

AR4

VSS

AR1

VSS

AP70

VSS

AP64

VSS

AN62

VSS

AN55

VSS

AY44

VSS

AY41

VSS

AY37

VSS

AY35

VSS

AY33

VSS

AY32

VSS

AY30

VSS

AY28

VSS

AY26

VSS

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

VSS

VSS

9 OF 10

9 OF 10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AY24

AY23

AY21

AY19

AY17

AY15

AY14

AY12

AY8

AY4

AW67

AW62

AW59

AW55

AW51

AW48

AW44

AW41

AW37

AV9

AV1

AU70

AU62

AU57

AU53

AU50

AU46

AU42

AU39

AU35

AU33

AU32

AU30

AU28

AU26

AU24

AU23

AU21

AU19

AU17

AU15

AU14

AU4

AT64

AT10

AR62

AR57

AR53

AR50

AR46

AN51

AN48

AN44

AN41

AN37

AN5

AN4

AM64

AM8

AL62

AL55

AL51

AL48

AL44

AL41

AL37

AL35

AL33

AL1

AK70

AK64

AK55

AK51

AK48

AK44

AK41

AK37

AK32

AK30

AK28

AK26

AK24

AK23

AK21

AK19

AK17

AK15

AJ70

AH62

AH57

AH55

BV66

BV64

BT68

BR69

BR68

BR3

BN71

BN1

BL71

BL1

R14

H71

F71

E69

E68

A66

A64

E5

C68

4

4

3

CPU1J

CPU1J

AH53

VSS

AH51

VSS

AH50

VSS

AH48

VSS

AH46

VSS

AH44

VSS

AH42

VSS

AH41

VSS

AH39

VSS

AH37

VSS

AH35

VSS

AH33

VSS

AH32

VSS

AH30

VSS

AH28

VSS

AH26

VSS

AH24

VSS

AH23

VSS

AH21

VSS

AH19

VSS

AH17

VSS

AH15

VSS

AH4

VSS

AG64

VSS

AG9

VSS

AG6

VSS

AF69

VSS

AF62

VSS

AF1

VSS

AE70

VSS

AE64

VSS

AD62

VSS

AD57

VSS

AD53

VSS

AD50

VSS

AD46

VSS

AD42

VSS

AD4

VSS

AC67

VSS

AC64

VSS

AC10

VSS

AC5

VSS

AC1

VSS

AB70

VSS

AB62

VSS

AB57

VSS

AB53

VSS

AB50

VSS

AB46

VSS

AB42

VSS

AB39

VSS

AB37

VSS

AB35

VSS

AB33

VSS

AB32

VSS

AB30

VSS

AB28

VSS

AB26

VSS

AB24

VSS

AB23

VSS

AB21

VSS

AB19

VSS

AB17

VSS

AB15

VSS

AB14

VSS

AB9

VSS

AA66

VSS

AA64

VSS

AA62

VSS

AA57

VSS

AA53

VSS

AA50

VSS

AA46

VSS

AA42

VSS

AA39

VSS

AA37

VSS

AA35

VSS

AA33

VSS

AA32

VSS

AA30

VSS

AA28

VSS

AA26

VSS

AA24

VSS

AA23

VSS

AA21

VSS

AA19

VSS

F20

VSS

F4

VSS

E37

VSS

E33

VSS

E30

VSS

E16

VSS

E12

VSS

D41

VSS

D38

VSS

D34

VSS

D31

VSS

D27

VSS

D24

VSS

D20

VSS

D17

VSS

D13

VSS

D10

VSS

D6

VSS

B65

VSS

B40

VSS

AUBURNDALE-1-GP-U3-NF

AUBURNDALE-1-GP-U3-NF

3

VSS

VSS

10 OF 10

10 OF 10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A40

A36

A33

A29

A26

A22

A19

A15

A12

A8

B62

B58

B55

B51

B48

B44

A59

A55

A52

A48

A45

AA17

AA15

AA14

AA4

W69

W62

W57

W53

W50

W46

W42

W6

W1

V70

U64

U62

U57

U53

U50

U46

U42

U39

U9

U4

T1

R70

R62

R57

R53

R50

R46

R42

R5

P4

N63

N57

N53

N50

N46

N30

N21

N15

M53

M42

M36

M1

L70

L57

L48

L47

L13

K64

K53

K43

K36

K34

K32

K25

K17

K11

K6

K4

J65

J57

J48

J47

J40

J9

H53

H43

H36

H1

G70

G57

G53

G48

G47

G43

G30

G24

G20

G15

F61

F48

F47

F28

2

JV10 CS

JV10 CS

JV10 CS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

2

Date: Sheet

CPU SFF 8 of 8(VSS)

CPU SFF 8 of 8(VSS)

CPU SFF 8 of 8(VSS)

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

JV10-CS

JV10-CS

JV10-CS

11 50Friday, January 22, 2010

11 50Friday, January 22, 2010

11 50Friday, January 22, 2010

of

of

1

of

-1

-1

-1

5

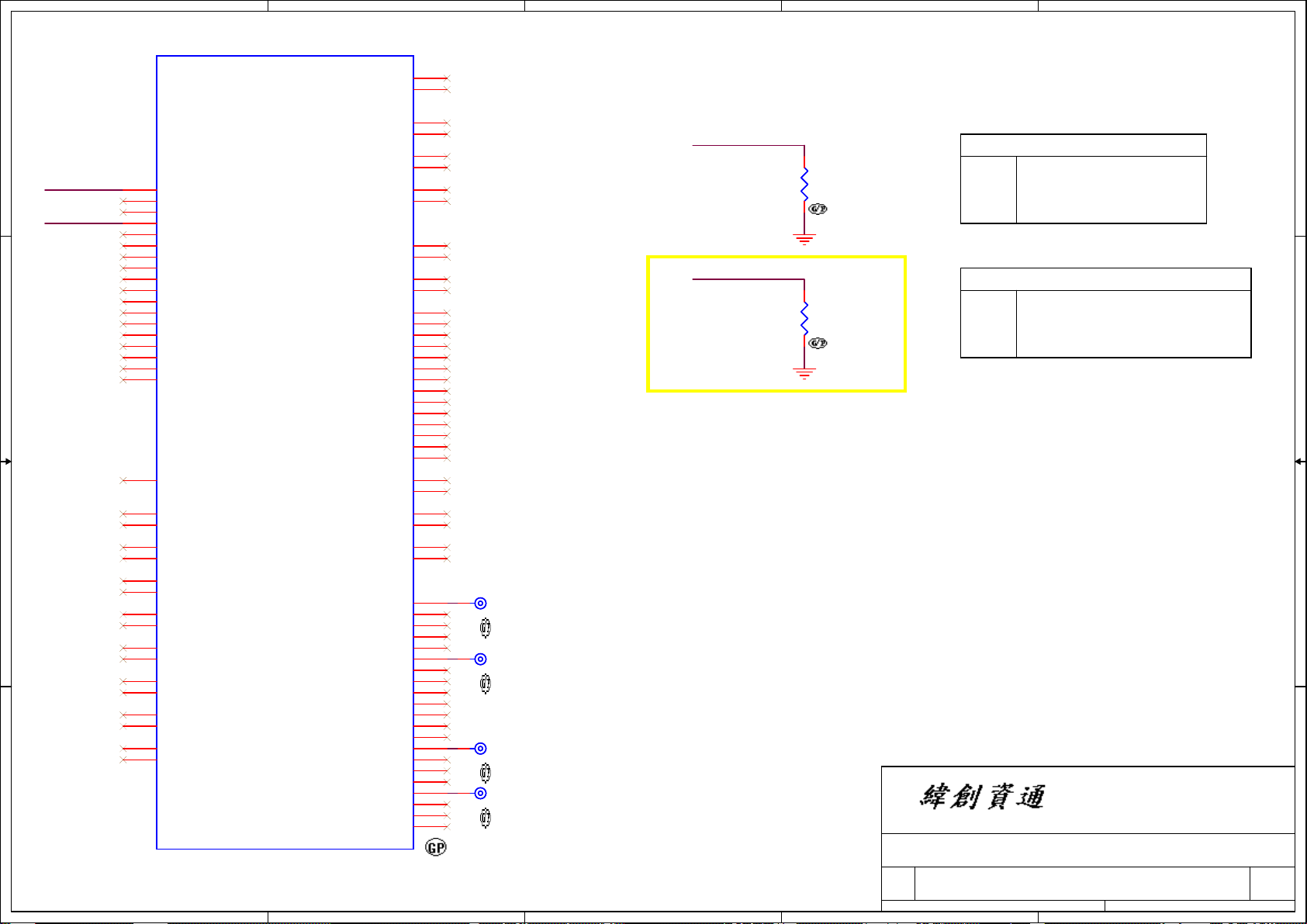

RTC_X1

DY

DY

5

1

23

12

EC14

EC14

Do Not Stuff

Do Not Stuff

RTC_X2

1 2

RN45

RN45

SRN33J-7-GP

SRN33J-7-GP

1

2

3

4 5

C307

C307

SC5P50V2CN-2GP

SC5P50V2CN-2GP

SB

8

7

6

ACZ_RST#

ACZ_BIT_CLK

ACZ_SYNC

ACZ_SDATAOUT

1 2

R168

R168

10MR2J-L-GP

10MR2J-L-GP

4

D D

X3

X3

C304

C304

X-32D768KHZ-34GPU

X-32D768KHZ-34GPU

SC5P50V2CN-2GP

SC5P50V2CN-2GP

82.30001.661

82.30001.661

1 2

2ND = 82.30001.B21

2ND = 82.30001.B21

ACZ_RST#_AUDIO34

ACZ_BITCLK_AUDIO34

C C

ACZ_SYNC_AUDIO34

ACZ_SDATAOUT_AUDIO34

ACZ_BIT_CLK PCH_SPI_CLK

12

EC11

EC11

Do Not Stuff

Do Not Stuff

DY

DY

B B

1D5V_S01D8V_S0

12

R151

R151

Do Not Stuff

Do Not Stuff

DY

DY

DY

DY

DY

DY

A A

If reserve 1.5/1.8V option for VCCVRM.Not Power plan change only.

Please refer figure2.HDA_SYNC will be strap to define VCCVRM is 1.5 or 1.8V source.

Means need have Pull high/low resistor to option,

P/H voltage base on HAD Link is 1.5V or 3.3V(Figure 3).

-1

12

R152

R152

Do Not Stuff

Do Not Stuff

ACZ_SYNC

12

R150

R150

Do Not Stuff

Do Not Stuff

RTC_AUX_S5

RTC_AUX_S5

2 3

1

SPI_CS0#, SPI_MISO, SPI_MOSI, SPI_CLK:

No series resistor required if routing length is 1.5"-6.5"

4

R163

R163

330KR2F-L-GP

330KR2F-L-GP

1 2

1 2

R164

R164

1MR2J-1-GP

1MR2J-1-GP

RN40

RN40

SRN20KJ-GP-U

SRN20KJ-GP-U

C296

C296

4

SC1U10V3KX-3GP

SC1U10V3KX-3GP

INTVRMEN

SM_INTRUDER#

21

12

G80

G80

Do Not Stuff

Do Not Stuff

12

C297

C297

SC1U10V3KX-3GP

SC1U10V3KX-3GP

ACZ_SPKR34

ACZ_SDATAIN034

When unused all JTAG pins may be NC

-1

PCH_SPI_CLK37

PCH_SPI_CS#037

PCH_SPI_MOSI37

RTC_AUX_S5

12

4

1 2

R305 0R2J-2-GPR305 0R2J-2-GP

1 2

R306 0R2J-2-GPR306 0R2J-2-GP

1 2

R307 0R2J-2-GPR307 0R2J-2-GP

3

C381

C381

SC1U16V3ZY-GP

SC1U16V3ZY-GP

D26

D26

BAS40CW-GP

BAS40CW-GP

83.00040.E81

83.00040.E81

2nd = 83.00040.M81

2nd = 83.00040.M81

ME_UNLOCK#36

TP14Do Not Stuff TP14Do Not Stuff

R292

R292

51R2F-2-GP

51R2F-2-GP

SPI_MOSO_R37

3D3V_AUX_S5

2

1

RTC_X1

RTC_X2

ICH_RTCRST#

SRTCRST#

SM_INTRUDER#

INTVRMEN

ACZ_BIT_CLK

ACZ_SYNC

ACZ_RST#

ACZ_SDATAOUT

PCH_JTAG_TCK

1

12

SB

SPI_CLK_R

SPI_CS#0_R

SPI_MOSI_R

B13

D13

C14

D17

A16

A14

A30

D29

C30

G30

E32

B29

H32

BA2

AV3

AY3

AY1

AV1

F30

F32

J30

RTC CONN

RTC_BAT_1

3

PCH1A

PCH1A

RTCX1

RTCX2

RTCRST#

SRTCRST#

INTRUDER#

INTVRMEN

HDA_BCLK

HDA_SYNC

P1

SPKR

HDA_RST#

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_SDIN3

HDA_SDO

HDA_DOCK_EN#/GPIO33

HDA_DOCK_RST#/GPIO13

M3

JTAG_TCK

K3

JTAG_TMS

K1

JTAG_TDI

J2

JTAG_TDO

J4

TRST#

SPI_CLK

SPI_CS0#

SPI_CS1#

SPI_MOSI

SPI_MISO

IBEXPEAK-M-GP-NF

IBEXPEAK-M-GP-NF

12

R233

R233

1KR2J-1-GP

1KR2J-1-GP

3

1 OF 10

1 OF 10

FWH0/LAD0

FWH1/LAD1

FWH2/LAD2

FWH3/LAD3

FWH4/LFRAME#

LDRQ0#

LDRQ1#/GPIO23

LPC

LPC

RTCIHDA

RTCIHDA

SPI JTAG

SPI JTAG

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA

SATA

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATALED#

SATA0GP/GPIO21

SATA1GP/GPIO19

SERIRQ

23.25218.001

Pin define

RTC_BAT

4

2

2nd = 20.F1035.002

2nd = 20.F1035.002

20.F0772.002

20.F0772.002

ACES-CON2-11-GP

ACES-CON2-11-GP

1

RTC2

RTC2

3

2

D33

B33

C32

A32