Acer Egret, Aspire 1360, Aspire 1362, Aspire 1363, Aspire 1520 Schematic

...

A

B

C

D

E

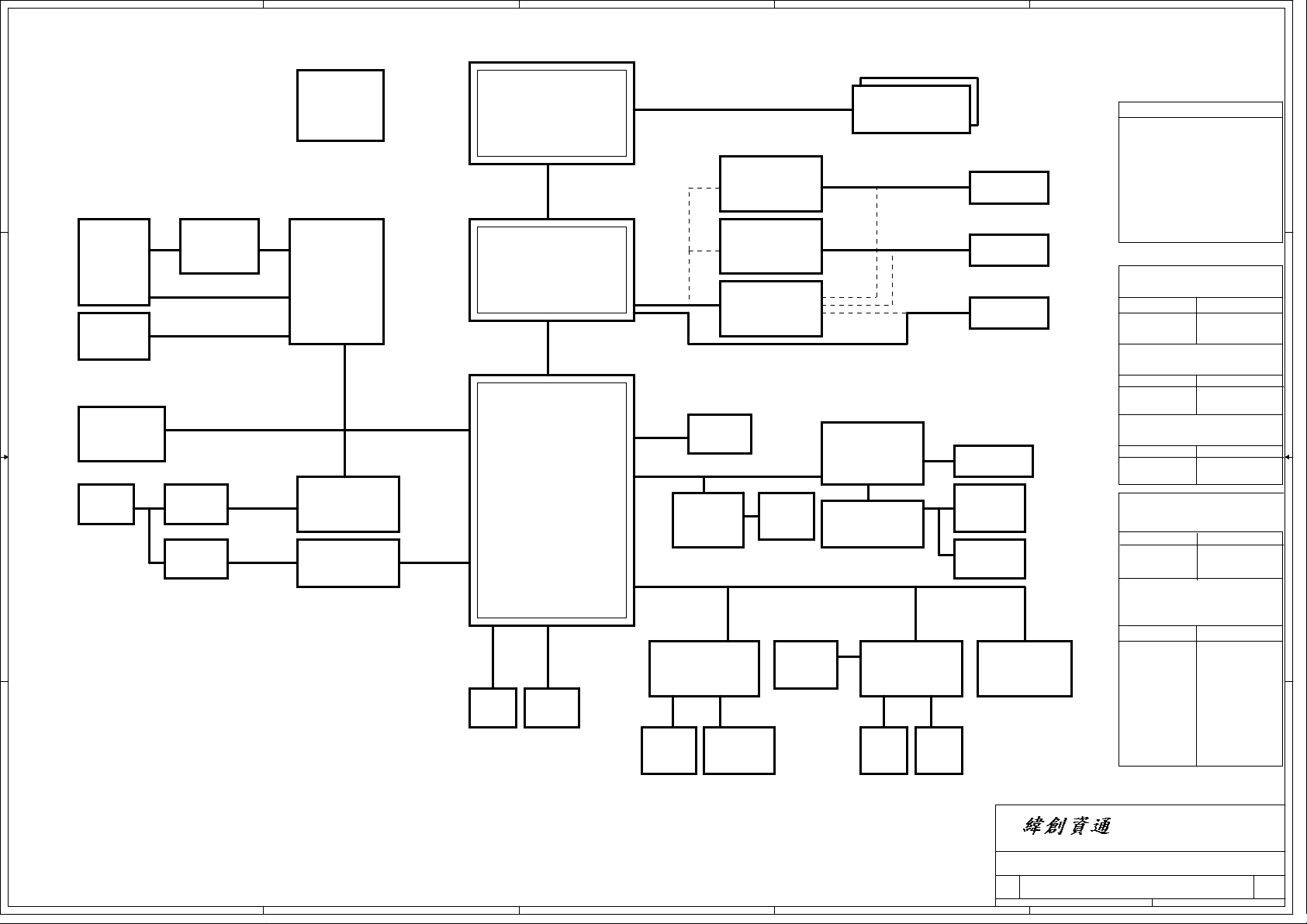

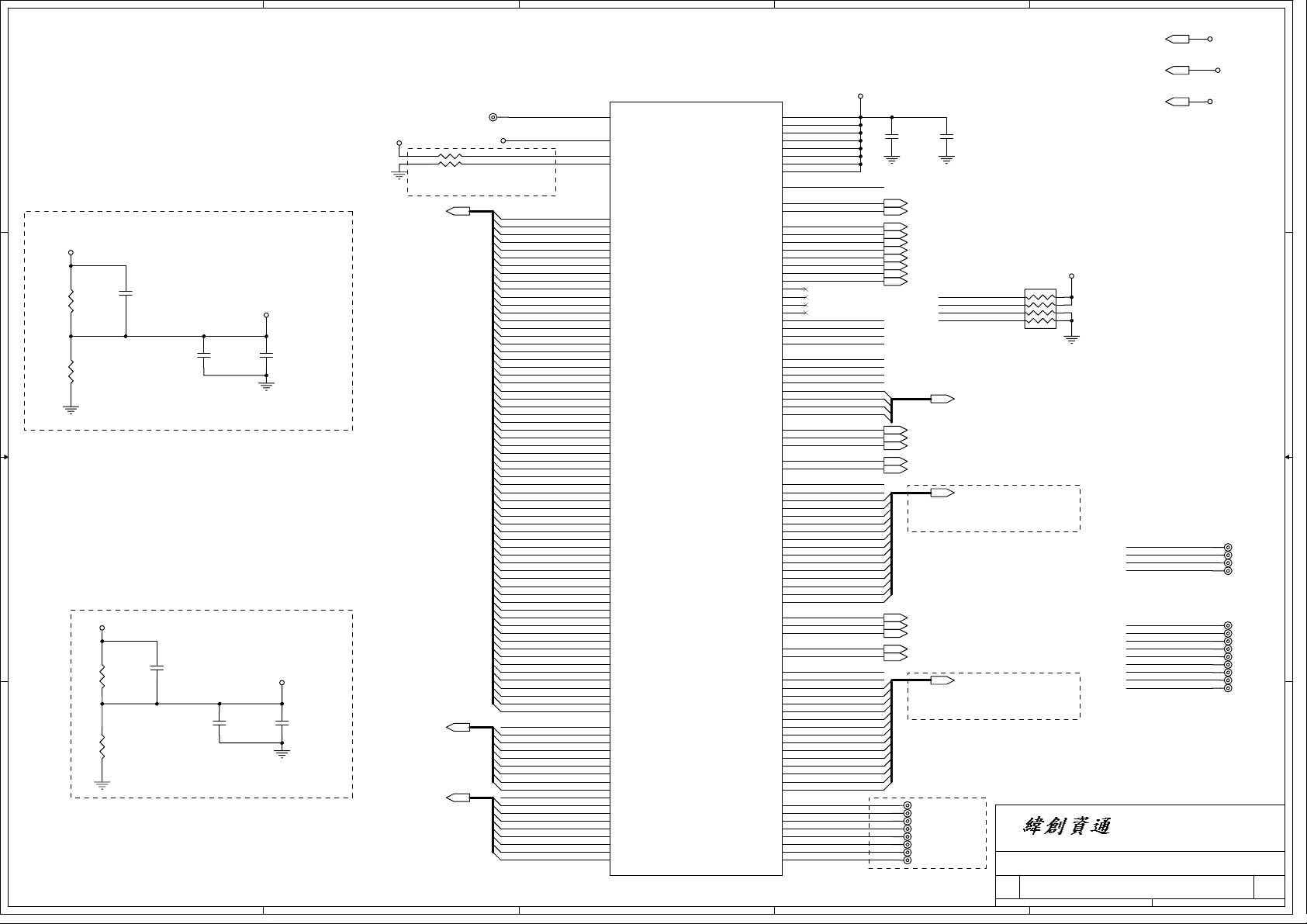

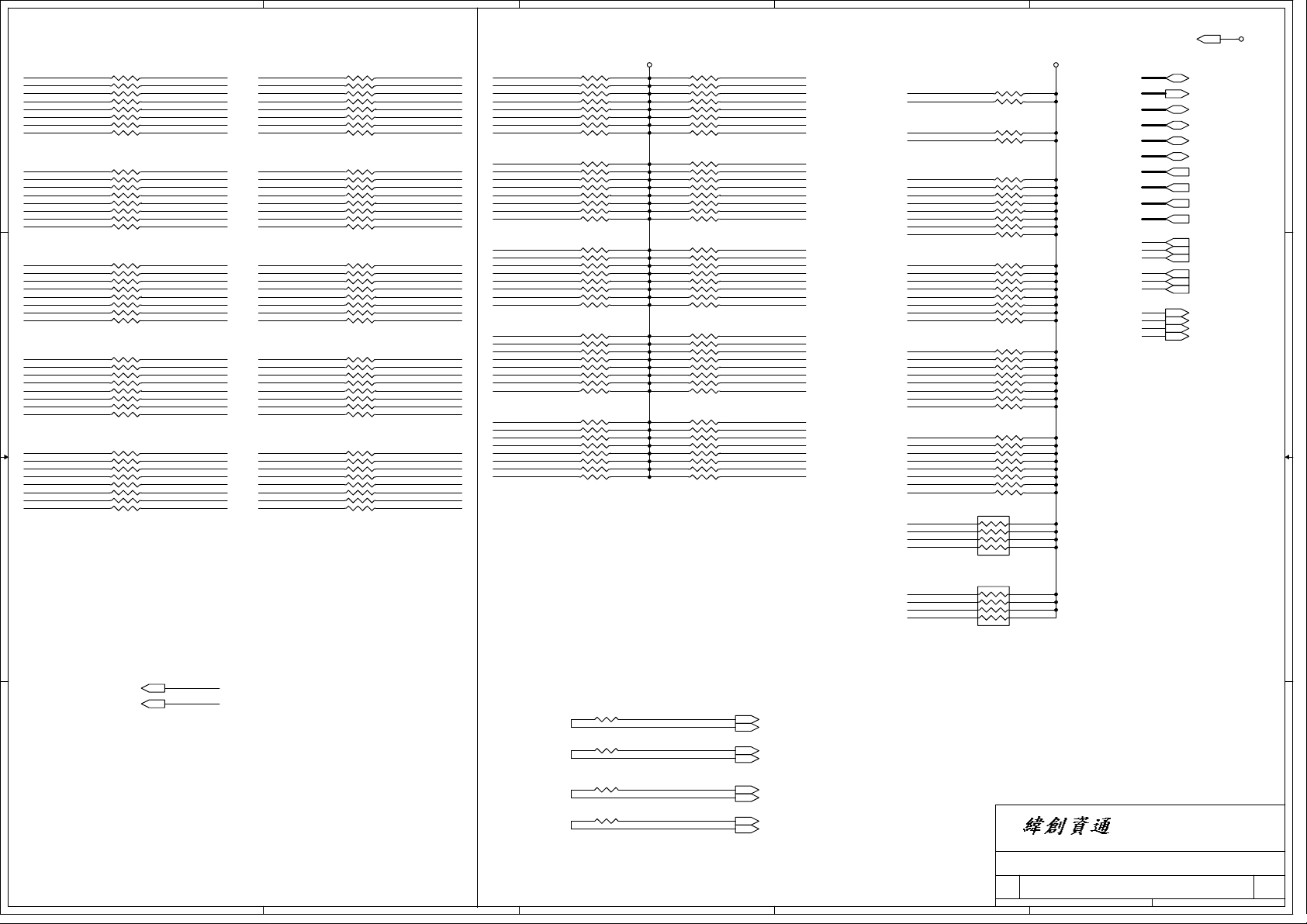

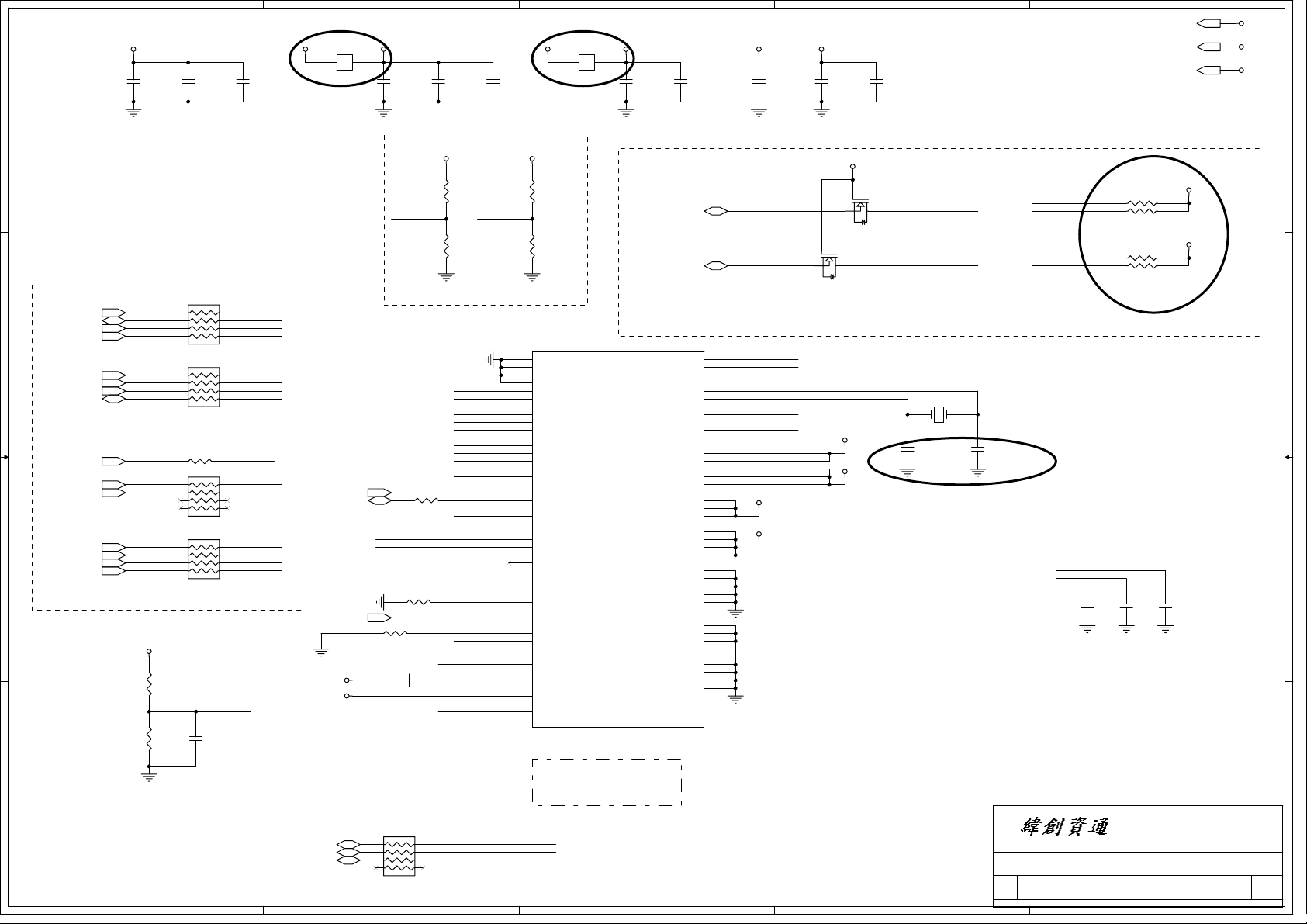

EGRET Block Diagram

200-PIN DDR SODIMM

CLK GEN

ICS

4 4

PCMCIA

SLOT

Support

TypeII

27

PWR SW

TPS2224AP

27

PCMCIA I/F

1394

3 3

Conn

27

Mini-PCI

ICS950405

TI

PCI 7420

2* Slot Cardbus

1* 1394

25,26

3

PCI Bus / 33MHz

802.11a/b/g

30

RJ45

29

TXFM

TXFM

2 2

1000Mb

29

10/100Mb

29

PCI GIGA LAN

Realtek

RTL8110SBL

LAN PHY

VIA VT6103L

28

29

AMD CPU

Claw Hammer K8

HyperTransport

6.4GB/S 16b/8b

VIA

K8N800

AGTL+ CPU I/F + UMA

8 bit V-LINK

66MHZ 8x/4x/2x

VIA

VT8235CE

ACPI 2.0

PCI

MII

ATA 133

PIDE

HDD

23

SIDE

DVD/

CD-RW

23

4,5,6,7

11,12,13

6xUSB 2.0

6-CH

AC97 2.2

LPC I/F

19,20,21

AGP 8x

NS SIO

PC87392

port

DDR 333/400

LVDS Transmitter

USB x 4

AC LINK

MODEM

MDC Card

FIRParallel

TFDU6101E

37

TV Encoder

VIA VT1623M

VIA VT1631

Graphic CONN.

AGP 8X

24

RJ11

CONN

29

LPC Bus / 33MHz

Thermal

& Fan

G791

36

36

14

15

16

AC'97 CODEC

VT1612A

OP AMP

APA2020

22

DDR x2

Touch

Pad

8,9,10

SVIDEO/COMP

LVDS

RGB CRT

31

3224

KBC

M38859

Int.

KB

34 34

TVOUT

LCD

CRT

Line In

MIC In

Line Out

(SPDIF)

Int. SPKR

SST-49LF040

32

32

32

FWH

17

18

17

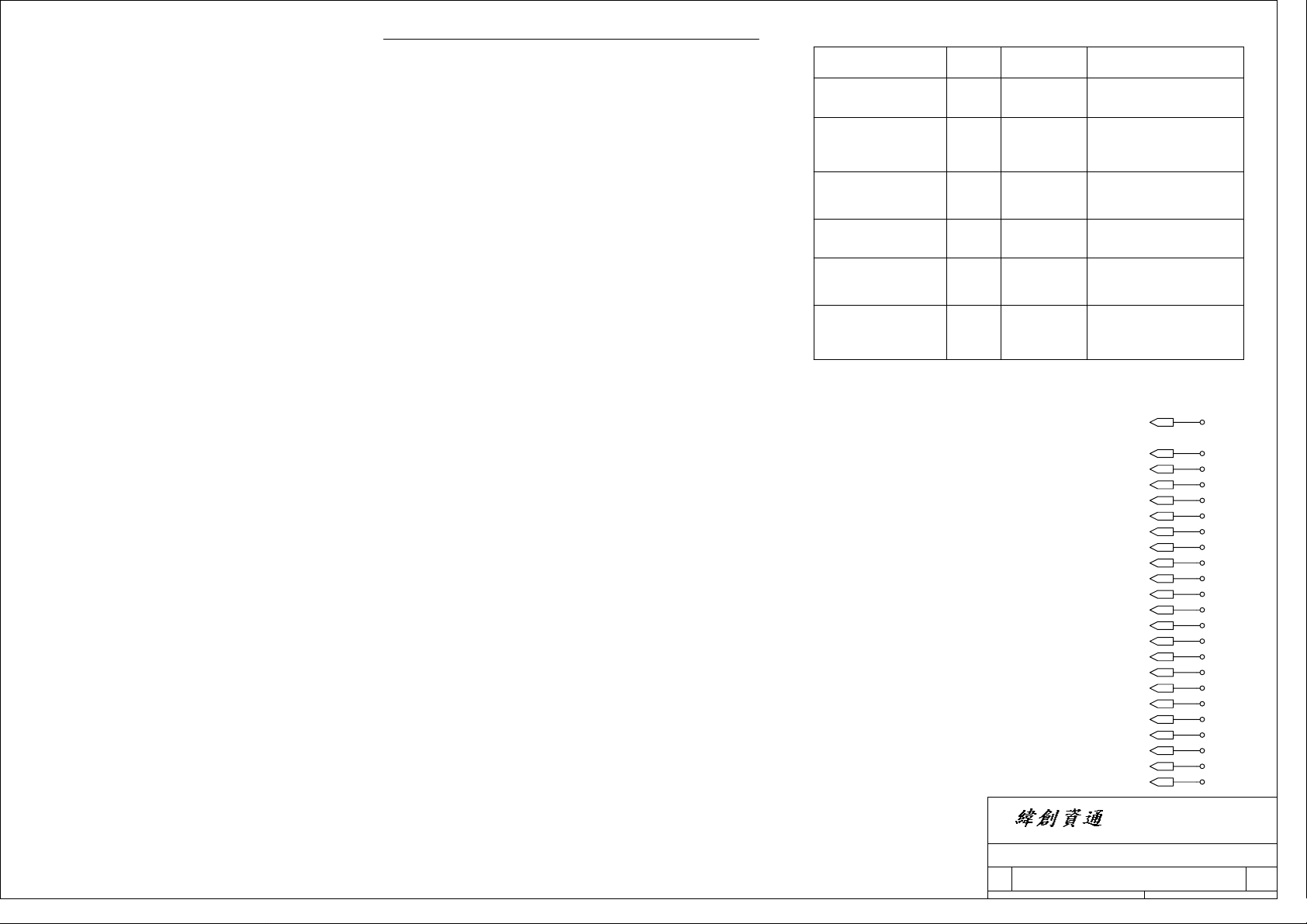

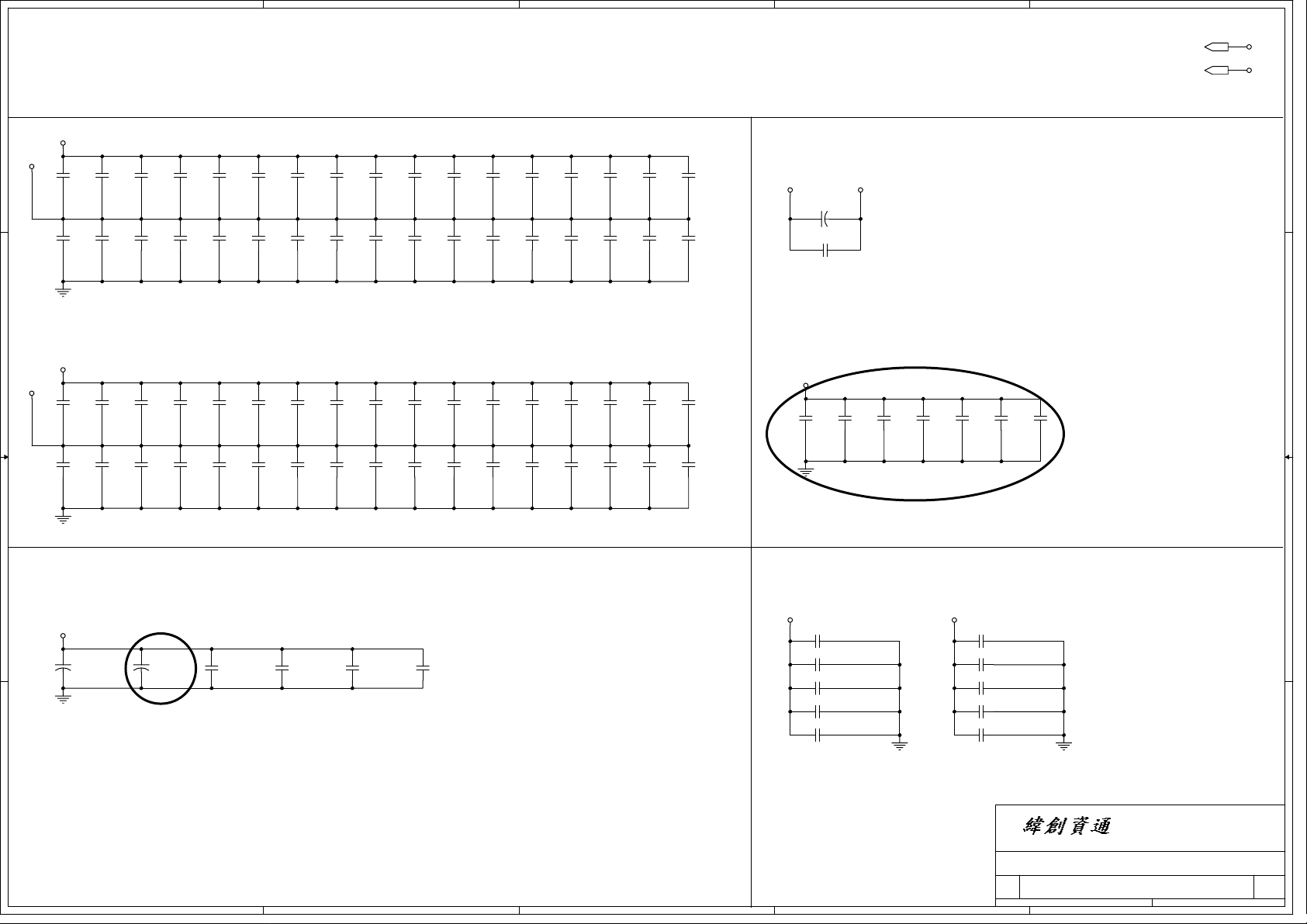

PCB Layer Stackup

L1: Signal 1

L2: GND

L3: Signal 2

L4: Signal 3

L5: VCC

L6: Signal 4

Battery Charger

MAX1645BEEI

INPUTS

AD+

BAT+

OUTPUTS

DCBATOUT

SYSTEM DC/DC

MAX1999

INPUT

DCBATOUT

OUTPUT

5V_S5 ,

3D3V_S5

SYSTEM DC/DC

INPUT

DCBATOUT

2D5V_S3

TPS5110

OUTPUT

2D5V_S3

1D5V_S0

CPU V_CORE

ISL6559CR

INPUT

DCBATOUT

SYSTEM POWER

FDD6035AL/FDS9412-U

FDS9412-U/SI4892DY/LP2951ACM

APL5508-18VC/APL5308-25AC

INPUT

5V_S3

3D3V_S5

3533

3D3V_S3

3D3V_S0

DCBATOUT

OUTPUT

VCC_CORE_S0

OUTPUT

2D5V_S5

5V_S0

3D3V_S3

3D3V_S0

3D3V_LAN_S3

1D8V_S0

+5V_AUX_S5

+5V_UP_S5

2D5V_S0

46

43

44

41,42

44,45

1 1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

A

B

C

D

Date: Sheet of

Block Diagram

EGRET

E

150Friday, July 23 , 2004

SC

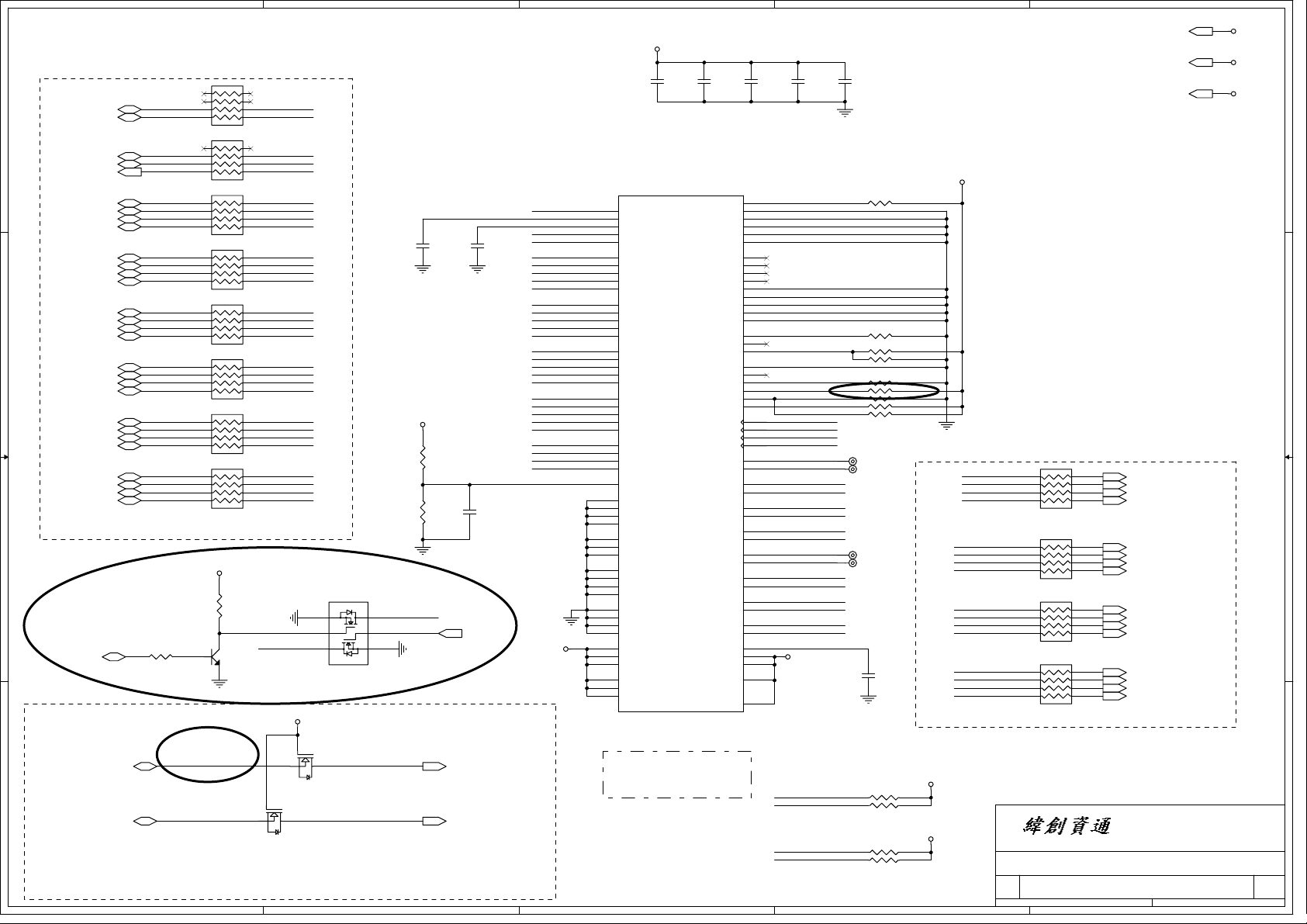

EGRET REVISION HISTORY

PCI RESOURCE TABLE

VGA & AGP

PCI7420-CardBus A

PCI7420-CardBus B

PCI7420-IEEE1394A

Mini-PCI

Giga LAN

RTL8110SBL

IDSEL

PCI IRQDEVICE REQ# / GNT#

P_INTA#

AD22

P_INTB#

P_REQ#1/P_GNT#1

AD22 P_INTC# P_REQ#1/P_GNT#1

P_INTD#

P_REQ#1/P_GNT#1AD22

AD21 P_INTF# P_REQ#0/P_GNT#0

AD23 P_INTG#

P_REQ#2/P_GNT#2

VREF_DDR_MEM5,8

1D2V_HT0A_S04,11,13,39,45

1D2V_HT0B_S04,6

1D25V_S35,6,7,9,10,39,45

1D5V_S012,13,14,15,16,44,50

2D5V_S06,12,14,15,1 6,19,20,21,38,39,50

2D5V_S35,6,7,8,10,38,39,44,45,50

2D5V_S520,21,39

3D3V_S03,6,8,11,12,13,14,15,16,17,18,19,20,21,24,25,26,27,28,30,31,32,33,34,35,36,38,41,47,49,50

3D3V_S318,33,34,38,50

3D3V_S513,18,19,20 ,2 1 ,22,24,28,29,33,38,43,49,50

5V_S016,17,18,19,20,21,22,23,24,27,30,31,32,33,34,37,38,39,41,42,47,48,49,50

5V_S521,38,39,43,44,45,46,48,49

+5V_AUX_S519,21,22,34,38,39,45,46,49

+5V_UP_S518,48,50

DCBATOUT16,18,38,41,43,44,45,46,47,50

VCC_CORE_S07,41,42

AD+46,47

BT+46,47

DCBATOUT_ISL41,42

3D3V_LAN_S524,28,29

VCC_ASKT_S025,27

VPP_ASKT_S027

VREF_DDR_MEM

1D2V_HT0A_S0

1D2V_HT0B_S0

1D25V_S3

1D5V_S0

2D5V_S0

2D5V_S3

2D5V_S5

3D3V_S0

3D3V_S3

3D3V_S5

5V_S0

5V_S5

+5V_AUX_S5

+5V_UP_S5

DCBATOUT

VCC_CORE_S0

AD+

BT+

DCBATOUT_ISL

3D3V_LAN_S5

VCC_ASKT_S0

VPP_ASKT_S0

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

Date: Sheet

REVISION HISTORY

A3

EGRET

of

250Friday, July 23 , 2004

SC

A

B

C

D

E

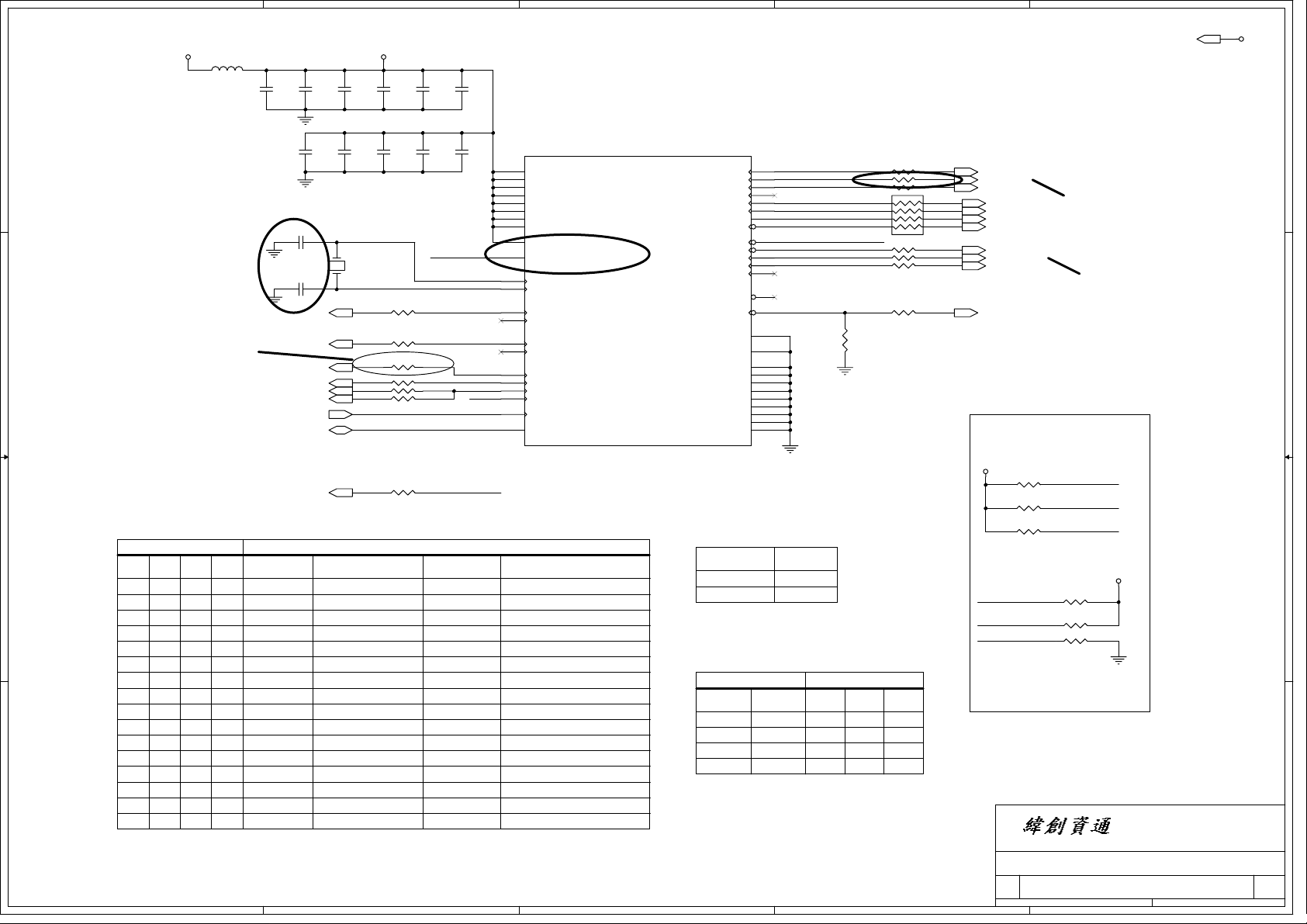

3D3V_S0

L9 BLM21A121S

1 2

4 4

SC10U10V6ZY-U

12

12

C156

12

C593

SCD1U

C599

SCD1U

SC

C154

By KDS suggested change

From 78.33034.1B1

To 78.12034.1B1

3 3

GUICLK Damping only

Stuff for K8N800 UMA

1 2

SC12P

C155

1 2

SC12P

CPUCLK6

CPUCLK#6

APICCLKSB21

SIO_OSC20

CLK14_SIO36

SMBC_SB8,21

SMBD_SB8,21

CLK48_USB19

GUICLK12

3D3V_CLK_S0

3D3V_CLK_S0

12

C592

SCD1U

12

C595

SCD1U

12

X3

XTAL-14D318M-2

R86 DY-22R3

R88 22R3

R109 22R3

R110 22R3

R111 22R3

12

12

C594

SCD1U

12

12

C596

SCD1U

XI_CLK

XO_CLK

R108 15R3F

1 2

R112 15R3F

1 2

1 2

1 2

1 2

1 2

1 2

12

C645

SCD1U

12

C597

SCD1U

CLK_PD#

CPUCLK#_CY

ZZ.22034.151

C646

SCD1U

C598

SCD1U

FS0

FS1

FS2

FS3

FS3

FS0~FS2 Hav e internal Pull-up resistor

FS3 Have internal Pull-down resistor

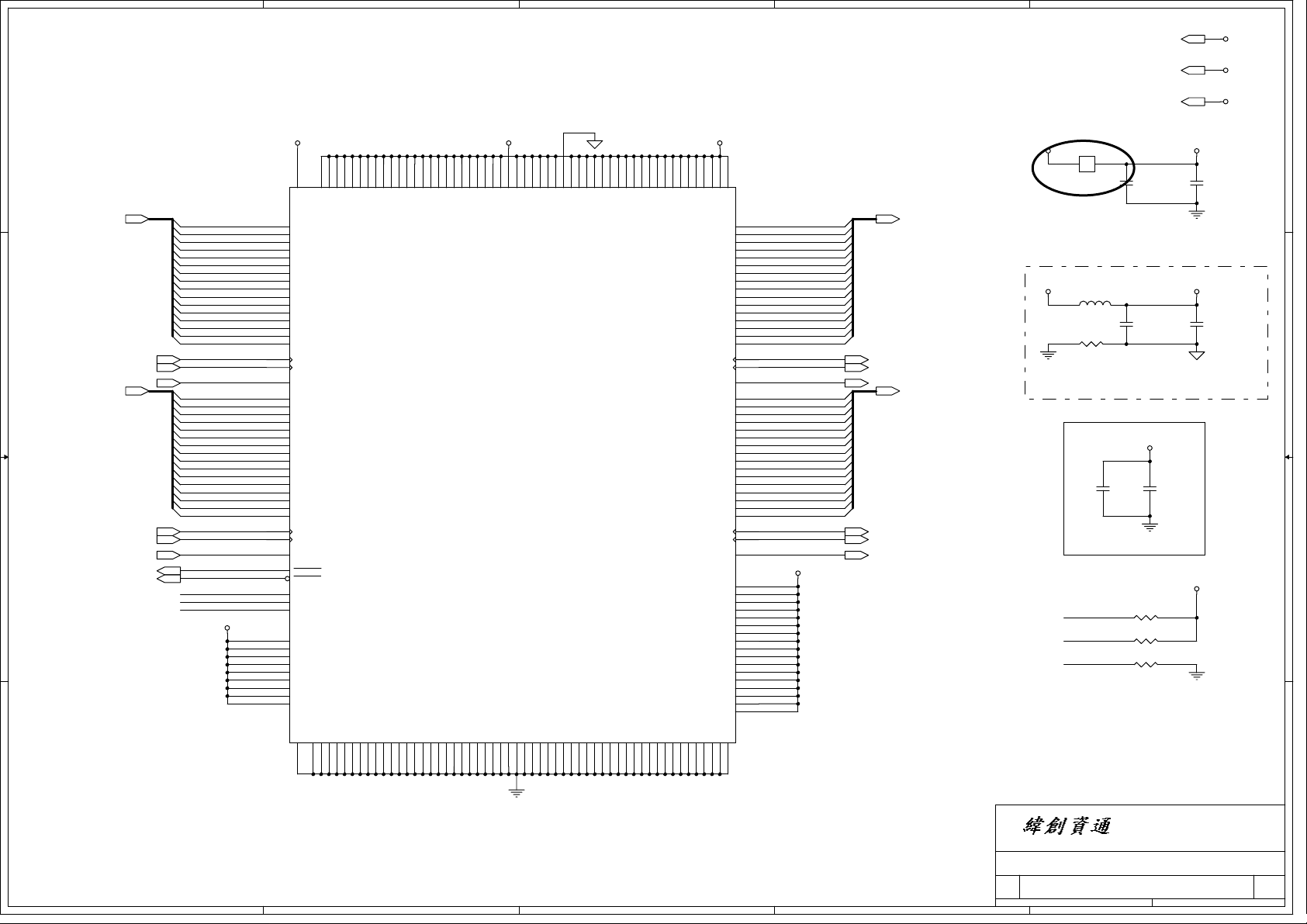

U15

2

VDD

9

VDD

16

VDD

19

VDD

29

VDD

35

VDD

38

VDD

46

VDD

43

32

3

4

41

37

40

36

1

48

45

31

25

26

VDDA

VDDF

XIN

XOUT

CPUT0

CPUT1

CPUC0

CPUC1

FS0/REF0

FS1/REF1

FS2/REF2

USB/FS3

SCLK

SDATA

ICS950405

Library Issue

Pin32: PD#

HT66_0/PCIHT66SEL0#

PCI33_8_HT66_1/PCIHT66SEL1#

PCI33_0

PCI33_1

PCI33_2

PCI33_3

PCI33_4

PCI33_5

PCI33_6

PCI33_7

PCI33_9_HT66_2

PCI33_11_HT66_3

PCI33_10

SRESET#/PD#

24_48MHZ/SEL#

VSSF

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

13

14

17

18

21

22

23

24

6

7

8

11

12

44

28

33

42

5

10

15

20

27

30

34

39

47

PCICLK0

PCICLK1

PCICLK2

PCICLK4

PCICLK5

PCICLK6

PCICLK7

CLK33_HT66SEL#0

CLK33_HT66SEL#1

PCI33_HT66_2

PCI33_HT66_3

CLK_24_48SEL#CPUCLK_CY

SB

R105 22R3

1 2

R107 22R3

1 2

R126

1 2

22R3

RN13

4 5

3

SRN22-1

2

1

R101 22R3

1 2

R106 22R3

1 2

R102 22R3

1 2

R127 22R3

1 2

12

R128

10KR3

63.22034.151

6

7

8

CLK33_CARDBUS 25

CLK33_LAN 28

CLK33_MINI 30

CLK33_KBC 33

CLK33_SIO 36

CLK33_LPCROM 35

CLK33_SB 21

CLK66_NB 12

CLK66_VGA 16

CLK66_VCLK 21

CLK48_CARDBUS 25

3D3V_CLK_S0

R85 10KR3

1 2

R87 10KR3

1 2

R114 10KR3

1 2

CLK33_LAN Damping only

Stuff for RTL8110SB

CLK66_VGA Damping only

Stuff for K8N800 Discrete

FS0

FS1

FS2

3D3V_S06,8,11,12,13,14,15,16,17,18,19,20,21,24,25,26,27,28,30,31,32,33,34,35,36,38,41,47,49,50

3D3V_S0

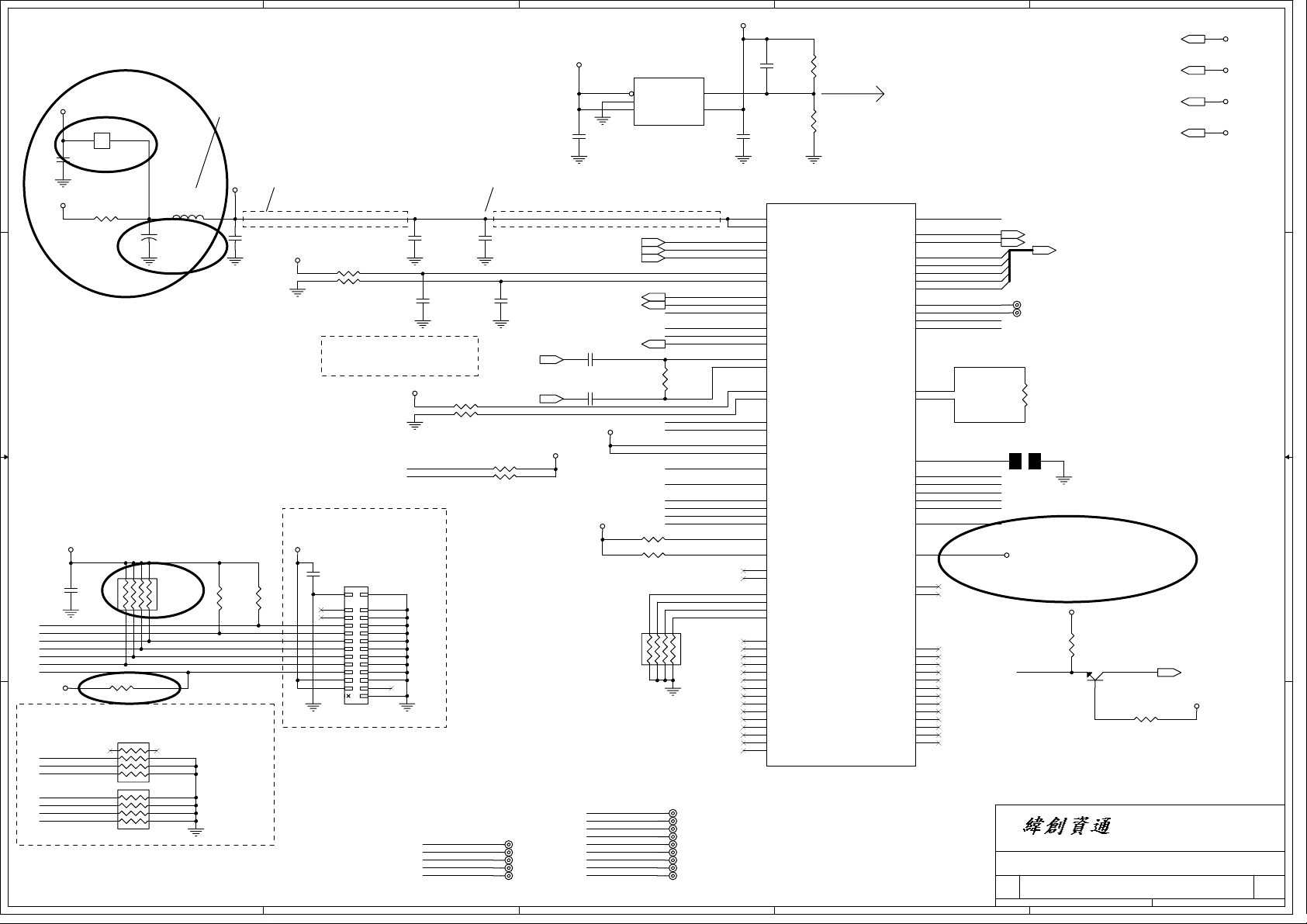

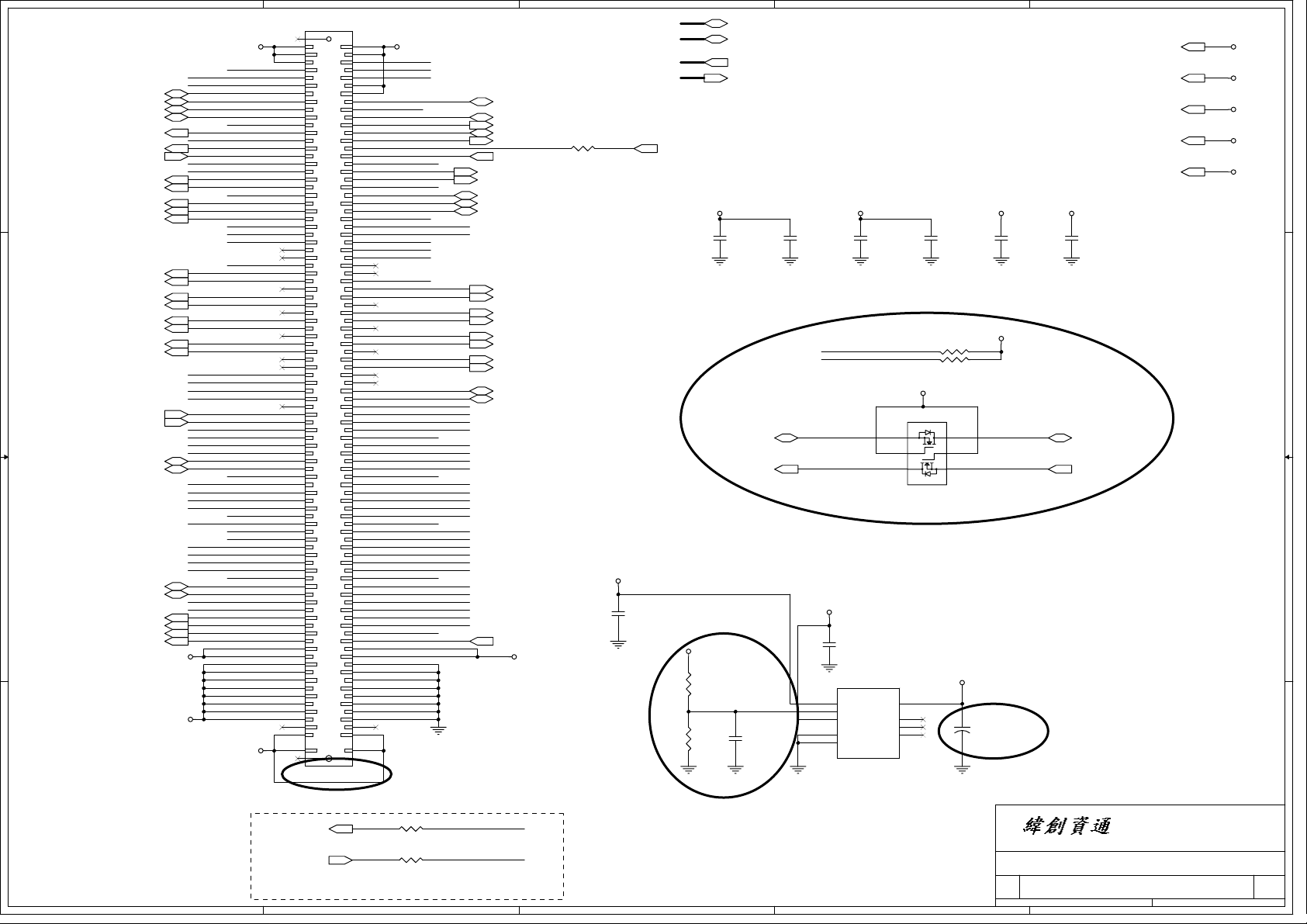

Clock Generator OutputInput Configuration

FS1

2 2

FS2 FS0FS3

0

0

001

0

0

011

0

0

010

101

0

001

*

1 1

1

1

1

1

1

1

1

A

0

001

0

0

10

0

1

00

1

1

1111

00

010

011

11

10

11

10

0

CPU (MHz)

100.90

133.90

168.00

202.00

100.20

133.50

166.70

200.40

150.00

180.00

210.00

240.00

270.00

233.33

266.67

300.00

PCI33_HT66 (MHz)

PCI33 (MHz)

67.27 33.63

66.95

67.20

67.33

66.80

66.75

66.68

66.80

33.48

33.60

33.67

33.40

33.38

33.34

33.40

60.00 30.00

60.00

70.00

60.00

67.50

66.67

66.67

75.00

30.00

35.00

30.00

33.75

33.33

33.33

37.50

B

All output Tri-state

Normal Hammer operation

C

24_48 SEL# 24_48MHz

0

*

1

PCIHT66 SEL [1:0]#

SEL1SEL0

0

0

*

10

11

48MHz

24MHz

0

1

PCI33_HT66[3:0]

PIN7

PIN8 PIN11

HT66 HT66

HT66HT66

PCI33 PCI33HT66

PCI33

HT66

PCI33PCI33PCI33

D

3D3V_CLK_S0

CLK_PD#

CLK33_HT66SEL#1

CLK33_HT66SEL#0

Title

Size Document Number Rev

A3

Date: Sheet

R113 10KR3

1 2

1 2

R103 10KR3

1 2

R104 10KR3

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

CLKGEN_ICS 9 50405

EGRET

350Friday, July 23 , 2004

E

of

SC

A

B

C

D

E

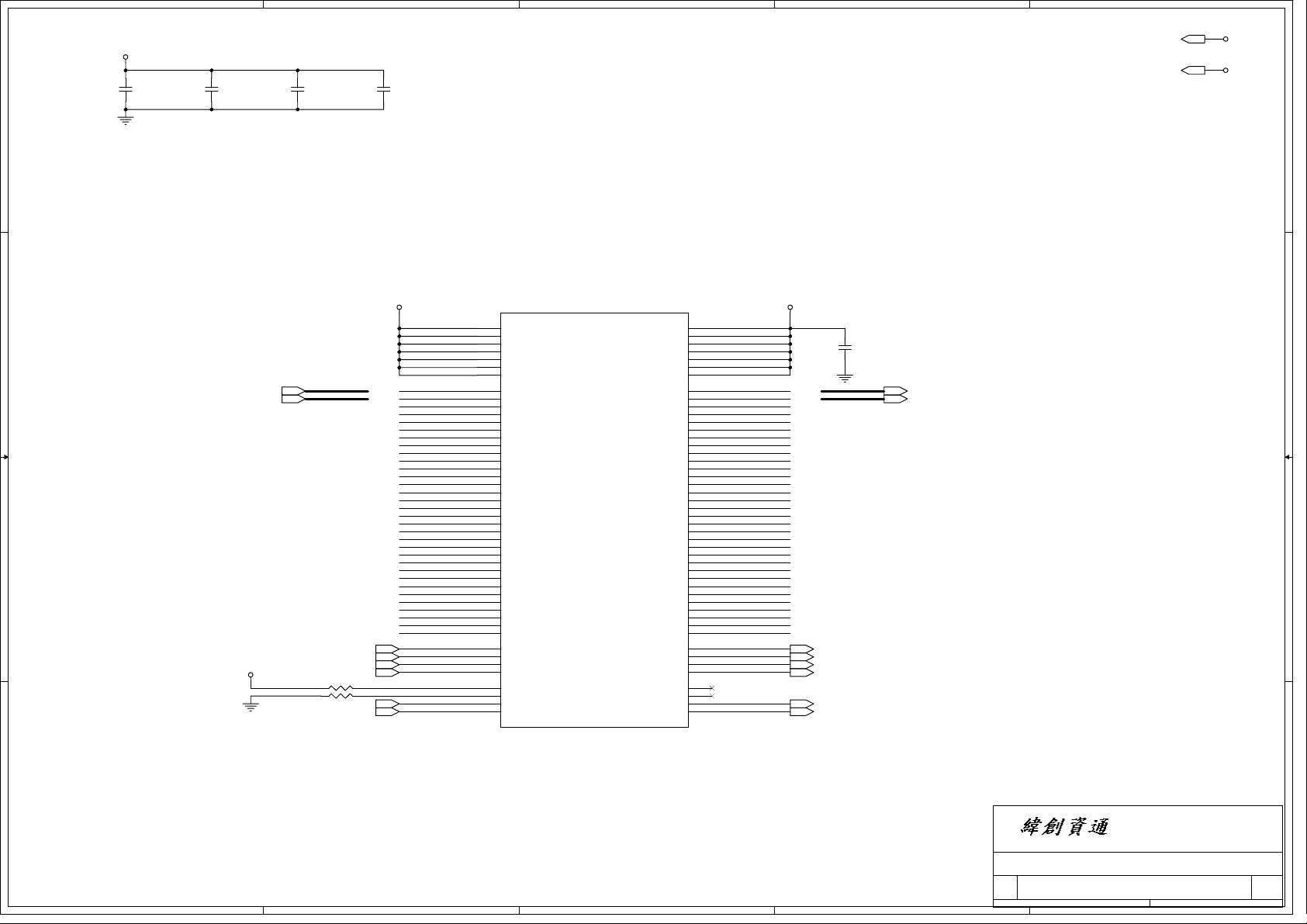

1D2V_HT0A_S0

12

C105

SCD22U16V3ZY

4 4

3 3

12

C107

SCD22U16V3ZY

NB0CADOUT[15..0]11

NB0CADOUTJ[15..0]11

12

C106

SCD22U16V3ZY

Used SideB Power Plane

2 2

NB0HTTCLKOUT111

NB0HTTCLKOUTJ 111

1D2V_HT0B_S0

NB0HTTCLKOUT011

NB0HTTCLKOUTJ 011

R289 49D9R3F

1 2

R290 49D9R3F

1 2

NB0HTTCTLOUT11

NB0HTTCTLOUTJ11

12

C109

SCD22U16V3ZY

HTT for CPU sideA

Transmit power

and NB sideA Receive

power

1D2V_HT0A_S0

NB0CADOUT15

NB0CADOUTJ15

NB0CADOUT14

NB0CADOUTJ14

NB0CADOUT13

NB0CADOUTJ13

NB0CADOUT12

NB0CADOUTJ12

NB0CADOUT11

NB0CADOUTJ11

NB0CADOUT10

NB0CADOUTJ10

NB0CADOUT9

NB0CADOUTJ9

NB0CADOUT8

NB0CADOUTJ8

NB0CADOUT7

NB0CADOUTJ7

NB0CADOUT6

NB0CADOUTJ6

NB0CADOUT5

NB0CADOUTJ5

NB0CADOUT4

NB0CADOUTJ4

NB0CADOUT3

NB0CADOUTJ3

NB0CADOUT2

NB0CADOUTJ2

NB0CADOUT1

NB0CADOUTJ1

NB0CADOUT0

NB0CADOUTJ0

NB0HTTCLKOUT1

NB0HTTCLKOUTJ1

NB0HTTCLKOUT0

NB0HTTCLKOUTJ0

CPUHTTCTLIN1

CPUHTTCTLINJ1

NB0HTTCTLOUT

NB0HTTCTLOUTJ

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

U11A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

HTT for CPU sideB

Receive power

and NB sideA

Transmit power

1D2V_HT0B_S0

CPUCADOUT15

CPUCADOUTJ15

CPUCADOUT14

CPUCADOUTJ14

CPUCADOUT13

CPUCADOUTJ13

CPUCADOUT12

CPUCADOUTJ12

CPUCADOUT11

CPUCADOUTJ11

CPUCADOUT10

CPUCADOUTJ10

CPUCADOUT9

CPUCADOUTJ9

CPUCADOUT8

CPUCADOUTJ8

CPUCADOUT7

CPUCADOUTJ7

CPUCADOUT6

CPUCADOUTJ6

CPUCADOUT5

CPUCADOUTJ5

CPUCADOUT4

CPUCADOUTJ4

CPUCADOUT3

CPUCADOUTJ3

CPUCADOUT2

CPUCADOUTJ2

CPUCADOUT1

CPUCADOUTJ1

CPUCADOUT0

CPUCADOUTJ0

CPUHTTCLKOUT1

CPUHTTCLKOUTJ1

CPUHTTCLKOUT0

CPUHTTCLKOUTJ0

CPUHTTCTLOUT0

CPUHTTCTLOUTJ0

LAYOUT: Place bypass cap on topside of board near

C469

SC4D7U10V5ZY

HTT power pins that are not connected directly to

downstream HTT device, but connected internally to

other HTT power pins.

CPUCADOUT[15..0] 11

CPUCADOUTJ[15..0] 11

Used SideA Power Plane

CPUHTTCLKOUT1 11

CPUHTTCLKOUTJ1 11

CPUHTTCLKOUT0 11

CPUHTTCLKOUTJ0 11

CPUHTTCTLOUT0 11

CPUHTTCTLOUTJ0 11

1D2V_HT0A_S011,13,39,45

1D2V_HT0B_S06

1D2V_HT0A_S0

1D2V_HT0B_S0

BGA754-SKT-U

62.10030.041

By ME requset U11 P/N:

1 1

A

B

Main 62.10030.041

Second 62.10053.191

Third 62.10053.201

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

C

D

Date: Sheet

CPU(1/4)_HyperTransport I/F

EGRET

450Friday, July 23 , 2004

E

of

SC

A

B

C

D

E

VREF_DDR_MEM8

2D5V_S36,7,8,10,38,39,44,45,50

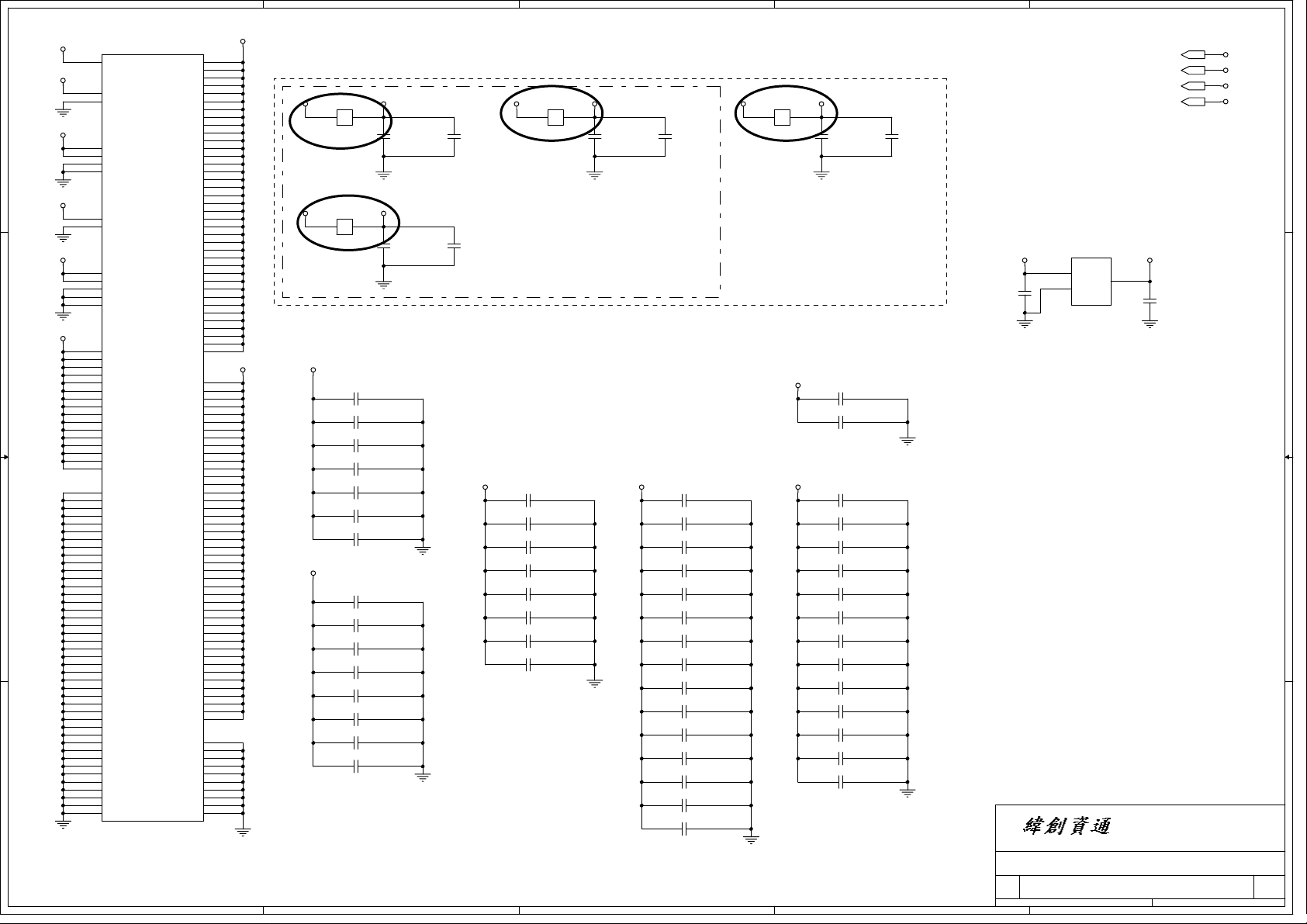

U11B

TP42

4 4

VREF_DDR_MEM

2D5V_S3

VREF_DDR_CLAW

R319 34D8R3F-1

1 2

R318 34D8R3F-1

1 2

AMD suggested change

to 34.8 ohm

M_DATA[63..0]9

NOTE: Test wi th p assive probes only.

2D5V_S3

3 3

NOTE: Install to bypass op-amp

R207

100R3

R206

100R3

12

C302

SCD1U

12

12

12

C300

SCD1U

VREF_DDR_MEM

12

C332

SC1000P50V3KX

78.10224.2B1

LAYOUT: Lo cate close to DI MMs.

NOTE: Remove to bypass op-amp

2 2

VREF_DDR_CLAW

2D5V_S3

12

12

1 1

12

R328

100R3

R329

100R3

C577

SCD1U

12

C579

SCD1U

VREF_DDR_CLAW

LAYOUT: Locate close to CPU .

A

12

C580

SC1000P50V3KX

78.10224.2B1

M_ADM[7..0]9

M_DQS[7..0]9

B

DDRVTT_SENSE

MEMZN

MEMZP

M_DATA63

M_DATA62

M_DATA61

M_DATA60

M_DATA59

M_DATA58

M_DATA57

M_DATA56

M_DATA55

M_DATA54

M_DATA53

M_DATA52

M_DATA51

M_DATA50

M_DATA49

M_DATA48

M_DATA47

M_DATA46

M_DATA45

M_DATA44

M_DATA43

M_DATA42

M_DATA41

M_DATA40

M_DATA39

M_DATA38

M_DATA37

M_DATA36

M_DATA35

M_DATA34

M_DATA33

M_DATA32

M_DATA31

M_DATA30

M_DATA29

M_DATA28

M_DATA27

M_DATA26

M_DATA25

M_DATA24

M_DATA23

M_DATA22

M_DATA21

M_DATA20

M_DATA19

M_DATA18

M_DATA17

M_DATA16

M_DATA15

M_DATA14

M_DATA13

M_DATA12

M_DATA11

M_DATA10

M_DATA9

M_DATA8

M_DATA7

M_DATA6

M_DATA5

M_DATA4

M_DATA3

M_DATA2

M_DATA1

M_DATA0

M_ADM8

M_ADM7

M_ADM6

M_ADM5

M_ADM4

M_ADM3

M_ADM2

M_ADM1

M_ADM0

M_DQS8

M_DQS7

M_DQS6

M_DQS5

M_DQS4

M_DQS3

M_DQS2

M_DQS1

M_DQS0

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

D17

VTT_A

A18

VTT_A

B17

VTT_A

C17

VTT_A

AF16

VTT_B

AG16

VTT_B

AH16

VTT_B

AJ17

VTT_B

MEMCKEA

MEMCKEB

NC_E13

NC_C12

NC_E14

NC_D12

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

BGA754-SKT-U

MEMRESET_L

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

C

1D25V_S3

MEMRESET#

M_CKE#0

M_CKE#1

M_CLK7

M_CLK#7

M_CLK6

M_CLK#6

M_CLK5

M_CLK#5

M_CLK4

M_CLK#4

M_CLK1

M_CLK#1

M_CLK0

M_CLK#0

M_CS#7

M_CS#6

M_CS#5

M_CS#4

M_CS#3

M_CS#2

M_CS#1

M_CS#0

M_ARAS#

M_ACAS#

M_AWE#

M_ABS#1

M_ABS#0

RSVD_M_AA15

RSVD_M_AA14

M_AA13

M_AA12

M_AA11

M_AA10

M_AA9

M_AA8

M_AA7

M_AA6

M_AA5

M_AA4

M_AA3

M_AA2

M_AA1

M_AA0

M_BRAS#

M_BCAS#

M_BWE#

M_BBS#1

M_BBS#0

RSVD_M_BA15

RSVD_M_BA14

M_BA13

M_BA12

M_BA11

M_BA10

M_BA9

M_BA8

M_BA7

M_BA6

M_BA5

M_BA4

M_BA3

M_BA2

M_BA1

M_BA0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

12

C578

SCD1U

For REGISTED DIMM Only

UNBUFFER DIMM NC

12

C177

SC1000P50V3KX

78.10224.2B1

M_CKE#0 8,9

M_CKE#1 8,9

M_CLK7 8,9

M_CLK#7 8,9

M_CLK6 8,9

M_CLK#6 8,9

M_CLK5 8,9

M_CLK#5 8,9

M_CLK4 8,9

M_CLK#4 8,9

M_ARAS# 8,9

M_ACAS# 8,9

M_AWE# 8,9

M_ABS#1 8,9

M_ABS#0 8,9

M_BRAS# 8,9

M_BCAS# 8,9

M_BWE# 8,9

M_BBS#1 8,9

M_BBS#0 8,9

D

M_CLK#1

M_CLK#0

M_CLK1

M_CLK0

M_CS#[3..0] 8,9

M_AA[13..0] 8,9

AMD suggested M_AA13

connect to DIMM pin123

M_BA[13..0] 8,9

AMD suggested M_BA13

connect to DIMM pin123

TP53

TP5

TP54

TP11

TP6

TP8

TP10

TP12

Title

Size Document Number Rev

A3

Date: Sheet of

1D25V_S36,7,9,10,39,45

2D5V_S3

1

8

2

7

3

6

45

RN95

SRN10K-2

MEMZN

MEMZP

M_DQS8

M_ADM8

MEMRESET#

M_CS#7

M_CS#6

M_CS#5

M_CS#4

RSVD_M_AA15

RSVD_M_AA14

RSVD_M_BA15

RSVD_M_BA14

NOT SUPPORT ECC CHECK

AMD suggested remove

PULL-HI resistor.

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

CPU(2/4)_DDR

EGRET

E

550Friday, July 23 , 2004

VREF_DDR_MEM

2D5V_S3

1D25V_S3

TP35

TP34

TP9

TP7

TP51

TP48

TP47

TP50

TP49

TP40

TP37

TP39

TP38

SC

A

2D5V_VDDA_S0

2D5V_S0

4 4

12

2D5V_CPUA_S0

SC

R499

1 2

GAP-CLOSE-PWR

C472

SC10U10V6ZY-U

R500

1 2

DY-0R3-U

ZZ.R0004.151

2D5V_CPUR_S0

L23 0R5J

1 2

12

TC6

ST100U4VBM-1

80.10716.321

SB

KEMET,NT:5.7, B2 size

ST100U4VBM-1 (80.10716.321)

3 3

Iripple=1.1A,ESR=70mohm

SANYO, NT$:6.1

Iripple=1.1A,ESR=70mohm

3.5/2.8/2.0

77.21071.031

HDT Connectors

2D5V_S0

2 2

1 1

12

C437

SCD1U

DBREQJ

DBRDY

TCK

TMS

TDI

TRST_L

TDO

R277 680R3

2D5V_S3

CHANGE FROM 1KR3 TO 680R2 FOR AMD

CHECK LIST

NC_AG17

NC_AJ18

NC_D18

NC_B19

NC_C19

NC_D20

NC_C21

1 2

RN88 SRN680-U

1

2

3

4 5

RN9 SRN680-U

1

2

3

4 5

123

SB

678

RN76

SRN680-U

4 5

8

7

6

8

7

6

A

Need to check which should be used

Change

L270H

2D5V_VDDA_S0

LAYOUT: Rou te tr ace 50 mils wide and

500 to 750 mils long between these

caps.

C470

SC4D7U10V5ZY

78.47593.411

1D2V_HT0B_S0

SC

Add HDT connector

for AMD suggested

2D5V_S0

12

12

R276

R275

680R3

680R3

SB

R292 44D2R3F

1 2

R291 44D2R3F

1 2

AMD suggest voltege

from 2D5V_S0 to 2D5V_S3

differentially im pedance 100

12

C438

DY-SCD1U

1

3

5

7

9

11

13

15

17

19

21

23

DY-SMC-CONN26A-FP

ZZ.F0357.025

B

3D3V_S0

12

C442

DY-SC1U10V3ZY

LAYOUT: Route VDDA trace approx.

50 mils wid e (use 2x25 mil traces to

exit ball field) and 500 mils long.

12

C499

SCD22U16V3ZY

12

1 2

1 2

CPUCLK#3

R308 680R3

1 2

R309 680R3

1 2

C467

SC1000P50V3KX

78.10224.2B1

CPUCLK3

2D5V_S0

HTT_CPU_STOP#21

VDDIOSENSE44

1 2

C500 SC3900P50V3KX

C501 SC3900P50V3KX

1 2

1D25V_S3

2D5V_S0

CN5

64.44R25.551

2D5V_S3

2

4

6

8

10

12

14

16

18

20

22

24

26

12

C471

SC3300P50V3KX

12

C468

SC1000P50V3KX

78.10224.2B1

R310 820R3

R311 820R3

RST_CPU#

ALL_PWROK

Validation Test Points

LAYOUT: Place close to the CPU.

NC_C15

NC_AE23

NC_AF23

NC_AF22

NC_AF21

B

TP36

TP24

TP25

TP26

TP27

RST_CPU#

CLKIN

CLKIN#

CORE_SENSE

VDDIOFB

VDDIOFBJ

VDDIOSENSE

NC_AE24

NC_AF24

C

Iomax=120mA

U42

1

SHDN#

2

GND

3

IN

DY-G913C-U

RST_CPU#19

ALL_PWROK12,19,21,39

COREFB41

COREFB#41

R80 680R3

1 2

R79 680R3

1 2

123

C

ALL_PWROK

L0_REF1

L0_REF0

COREFB

COREFB#

CORE_SENSE

VDDIOFB

VDDIOFBJ

VDDIOSENSE

CLKIN

12

R307

169R3F

CLKIN#

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_AE23

NC_AF23

NC_AF22

NC_AF21

678

4 5

TP30

TP32

TP33

TP28

TP43

TP44

TP41

TP29

TP31

SET

OUT

RN80

SRN680-U

2D5V_CPUA_S0

2D5V_VDDA_VREF

5

4

NC_C18

NC_A19

12

C441

DY-SC22P

12

C440

DY-SC1U10V3ZY

U11C

AH25

VDDA1

AJ25

VDDA2

AF20

RESET_L

AE18

PWROK

AJ27

LDTSTOP_L

AF27

L0_REF1

AE26

L0_REF0

A23

COREFB_H

A24

COREFB_L

B23

CORE_SENSE

AE12

VDDIOFB_H

AF12

VDDIOFB_L

AE11

VDDIO_SENSE

AJ21

CLKIN_H

AH21

CLKIN_L

AJ23

NC_AJ23

AH23

NC_AH23

AE24

NC_AE24

AF24

NC_AF24

C16

VTT_A

AG15

VTT_B

AH17

DBRDY

C15

NC_C15

E20

TMS

E17

TCK

B21

TRST_L

A21

TDI

C18

NC_C18

A19

NC_A19

A28

KEY1

AJ28

KEY0

AE23

NC_AE23

AF23

NC_AF23

AF22

NC_AF22

AF21

NC_AF21

C1

NC_C1

J3

NC_J3

R3

NC_R3

AA2

NC_AA2

D3

NC_D3

AG2

NC_AG2

B18

NC_B18

AH1

NC_AH1

AE21

NC_AE21

C20

NC_C20

AG4

NC_AG4

C6

NC_C6

AG6

NC_AG6

AE9

NC_AE9

AG9

NC_AG9

BGA754-SKT-U

12

R278

DY-20KR3F

12

R279

DY-20KR3F

D

R1

Vout = 1.25*(1+ R1/R2)

R2

THERMTRIP#

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

A20

A26

A27

AG13

AF14

AG14

AF15

AE15

AG18

AH18

AG17

AJ18

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

DBREQJ

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

THERMTRIP_L

FBCLKOUT_H

FBCLKOUT_L

Connect to VDDIO for AMD suggest.

D22

NC_D22

C22

NC_C22

B13

NC_B13

B7

NC_B7

C3

NC_C3

K1

NC_K1

R2

NC_R2

AA3

NC_AA3

F3

NC_F3

C23

NC_C23

AG7

NC_AG7

AE22

NC_AE22

C24

NC_C24

A25

NC_A25

C9

NC_C9

D

E

1D25V_S35,7,9,10,39,45

2D5V_S012,14,15,16,19,20,21,38,39,50

2D5V_S35,7,8,10,38,39,44,45,50

1D2V_HT0B_S04

THERMDP 22

THERMDN 22

VID[4..0] 41

TP45

TP46

LAYOUT: Route FBCLKOUT_H/L

FBCLKOUT

FBCLKOUTJ

differentially i mpedance 80

12

R323

80D6R3F-U

R322 DU MMY- R 3

1 2

2D5V_S3

SB

2D5V_S0

12

R193

680R3

THERMTRIP#

THERMTRIPJ Level shift to VT8235

EM_OFF PIN near VT8235

Title

Size Document Number Rev

A3

Date: Sheet of

CPU(3/4)_Control & Debug

2

1

EGRET

3

Q20

MMBT3904-U1

R194 1KR3

NS3

1 2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

CPU_THERMTRIP# 38

2D5V_S0

650Friday, July 23 , 2004

E

1D25V_S3

2D5V_S0

2D5V_S3

1D2V_HT0B_S0

SC

U11E

Y17

VSS

K17

VSS

H17

VSS

F17

VSS

E18

VSS

AJ26

VSS

AE29

VSS

AC16

VSS

AA16

VSS

J16

VSS

G16

VSS

E16

VSS

AH14

4 4

3 3

2 2

1 1

AD15

AB15

K15

E15

D16

AE14

AC14

AA14

G14

AF17

AD13

AB13

Y13

K13

H13

F13

AH12

AC12

AA12

G12

B12

AD11

AB11

Y11

K11

H11

F11

AH10

AC10

W10

U10

R10

N10

G10

B10

AD9

AH8

AC8

AD7

AB7

AH6

AC6

AA6

AH4

AH2

AD2

AB2

C29

AH28

AF28

AC28

W28

R28

J14

L10

J10

Y9

V9

T9

P9

M9

K9

H9

F9

W8

U8

R8

N8

L8

J8

G8

B8

V7

T7

P7

M7

K7

H7

F7

U6

R6

N6

L6

J6

G6

B6

B4

Y2

V2

T2

P2

M2

K2

H2

F2

L28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

BGA754-SKT-U

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A

VCC_CORE_S0 2D5V_S3

N20

L20

J20

AF19

AD19

AB19

Y19

K19

H19

F19

D19

AC18

AA18

G18

B16

AD17

AB17

H15

F15

G28

D28

B28

C27

AH26

AF26

AD26

Y26

T26

M26

H26

D26

B26

C25

B25

AJ24

AG24

AC24

AA24

W24

U24

R24

N24

J24

G24

E24

AG23

AD23

AB23

Y23

V23

T23

P23

K23

H23

F23

D23

AJ22

AH22

AG22

AC22

AA22

AG29

U22

R22

N22

L22

J22

G22

E22

B22

AG21

AD21

Y21

V21

T21

P21

M21

K21

H21

F21

D21

AJ20

AG20

AE20

AC20

AA20

W20

U20

R20

G20

J18

AE16

Y15

B14

J12

AA10

AB9

AA8

Y7

W6

AF2

D2

AG27

AG25

L24

M23

W22

AB21

AH20

B2

A

AC15

H18

B20

E21

H22

H24

F26

V10

G13

K14

Y14

AB14

G15

AA15

H16

K16

Y16

AB16

G17

AA17

AC17

AE17

F18

K18

Y18

AB18

AD18

AG19

E19

G19

AC19

AA19

F20

H20

K20

M20

P20

T20

V20

Y20

AB20

AD20

G21

N21

R21

U21

W21

AA21

AC21

F22

K22

M22

P22

T22

V22

Y22

AB22

AD22

E23

G23

N23

R23

U23

W23

AA23

AC23

B24

D24

F24

K24

M24

P24

T24

V24

Y24

AB24

AD24

AH24

AE25

K26

P26

V26

L7

J23

N7

L9

J15

J17

J19

J21

L21

L23

U11D

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

BGA754-SKT-U

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

B

VCC_CORE_S0

B

VCC_CORE_S0

12

C525

DY-SC6D8P50V2DC

0402

VCC_CORE_S0

12

C130

VCC_CORE_S0

1 2

C528

DY-SCD22U16V3ZY

0.22u x 4

2D5V_S3

12

C194

SCD22U16V3ZY

1D25V_S3

12

C535

SCD22U16V3ZY

0.22u x 2

EMI

12

C672

DY-SC6D8P50V2DC

C

LAYOUT: Place in uPGA socket cavity.

0.22u x 6

12

12

12

12

12

C132

C138

C137

C131

SCD22U16V3ZY

SCD22U16V3ZY

SCD22U16V3ZY

SCD22U16V3ZY

SCD22U16V3ZY

C139

SCD22U16V3ZY

LAYOUT: Place on backside of processor.

12

12

C530

DY-SCD22U16V3ZY

C531

SC10U10V5ZY

SC10U10V5ZY

1 2

1 2

1 2

C527

C533

C532

DY-SCD22U16V3ZY

DY-SCD22U16V3ZY

10u x 2

2D5V_S3

12

12

C198

C200

SCD22U16V3ZY

SCD22U16V3ZY

12

12

C196

SCD22U16V3ZY

12

C195

C626

SCD22U16V3ZY

SCD22U16V3ZY

C178

10u x 1 4.7u x 6

1D25V_S3

12

C534

SCD22U16V3ZY

C128

SC4D7U10V5ZY

SC4D7U10V5ZY

C129

4.7u x 2

VCC_CORE_S0

1000p x 3

12

12

C108

DY-SC1000P50V3KX

LAYOUT: Place 1000pF capacitors

between VRM & CPU.

C

12

C682

C660

DY-SC1000P50V3KX

DY-SC1000P50V3KX

C133

12

10u x 4

12

SC10U10V5ZY

C625

SC10U10V5ZY

C136

SC4D7U10V5ZY

12

SC10U10V5ZY

C526

C134

12

SC4D7U10V5ZY

SC10U10V5ZY

C257

C135

D

12

SC4D7U10V5ZY

D

SC10U10V5ZY

C254

SC4D7U10V5ZY

E

1D25V_S35,6,9,10,39,45

2D5V_S35,6,8,10,38,39,44,45,50

VCC_CORE_S041,42

C250

C253

78.47593.411

SC4D7U10V5ZY

SC4D7U10V5ZY

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet of

CPU(4/4)_Power

EGRET

E

1D25V_S3

2D5V_S3

VCC_CORE_S0

SC

750Friday, July 23 , 2004

A

M_AA0

M_AA1

M_AA2

M_AA3

M_AA4

M_AA6

M_AA5

M_AA7

M_AA8

M_AA9

M_AA10

M_AA11

M_ARAS#5,9

M_ACAS#5,9

M_AWE#5,9

TP65

TP15

TP64

C276

SCD1U

M_AA12

M_ABS#0

M_ABS#1

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_AA13

12

A

DM1_RESET#

DM1_A13

DM1_BA2

3D3V_S0

4 4

3 3

2 2

1 1

VREF_DDR_MEM VREF_DDR_MEM

Layout trace 20 mil Layout trace 20 mil

DM1

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

201

GND

DDR-SODIMM-N-U1

/CS0

/CS1

CKE0

CKE1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

NORMAL TYPE

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

62.10017.191

B

M_BRAS#5,9

M_BCAS#5,9

M_BWE#5,9

TP23

TP69

TP22

C299

SCD1U

M_BA0

M_BA1

M_BA2

M_BA3

M_BA4

M_BA6

M_BA5

M_BA7

M_BA8

M_BA9

M_BA10

M_BA11

M_BA12

M_BBS#0

M_BBS#1

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

DM2_RESET#

DM2_A13

DM2_BA2

M_BA13

M_BRAS#

M_BCAS#

M_BWE#

12

3D3V_S0

121

122

M_CKE#0

96

95

M_DQS_R0

11

M_DQS_R1

25

M_DQS_R2

47

M_DQS_R3

61

M_DQS_R4

133

M_DQS_R5 M_DQS_R5

147

M_DQS_R6

169

M_DQS_R7

183

77

M_ADM_R0

12

M_ADM_R1

26

M_ADM_R2

48

M_ADM_R3

62

134

M_ADM_R5 M_ADM_R5

148

M_ADM_R6

170

M_ADM_R7

184

78

35

37

160

158

DDR_CLK0

89

DDR_CLK#0

91

SMBC_SB

195

SMBD_SB

193

194

196

198

9

10

21

22

33

34

36

45

46

57

58

69

70

81

82

92

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

202

B

M_CS#0 5,9

M_CS#1 5,9

M_CKE#0 5,9

M_ADM#0

M_ADM#1

M_ADM#2

M_ADM#3

M_ADM#4

M_ADM#5

M_ADM#6

M_ADM#7

M_CLK5 5,9

M_CLK#5 5,9

M_CLK7 5,9

2D5V_S3

NOT SUPPORT ECC CHECK

ALi suggested pull-low

C

DM2

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

202

GND

DDR-SODIMM-R-U2

62.10017.201

C

/CS0

/CS1

CKE0

CKE1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

REVERSE TYPE

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

121

122

96

95

11

25

47

61

133

147

169

183

77

12

26

48

62

134

148

170

184

78

35

37

160

158

89

91

195

193

194

196

198

9

10

21

22

33

34

36

45

46

57

58

69

70

81

82

92

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

201

M_CS#2 5,9

M_CKE#1

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R6

M_DQS_R7

M_ADM_R0

M_ADM_R1

M_ADM_R2

M_ADM_R3

M_ADM_R4M_ADM_R4

M_ADM_R6

M_ADM_R7

DDR_CLK1

DDR_CLK#1

DM2_SA0

M_CS#3 5,9

M_CKE#1 5,9

M_ADM#0

M_ADM#1

M_ADM#2

M_ADM#3

M_ADM#4

M_ADM#5

M_ADM#6

M_ADM#7

M_CLK4 5,9

M_CLK#4 5,9

M_CLK6 5,9

M_CLK#6 5,9M_CLK#7 5,9

SMBC_SB 3,21

SMBD_SB 3,21

2D5V_S3

1 2

R204 4K7R3

By ME requset DM1 P/N:

Main 62.10017.191

Second 62.10017.381

By ME requset DM2 P/N:

Main 62.10017.201

Second 62.10017.371

Third 62.10017.701

D

M_ADM_R[7..0] 9

M_DATA_R_[63..0] 9

M_DQS_R[7..0] 9

M_AA[13..0] 5,9

M_ABS#[1..0] 5,9

M_BA[13..0] 5,9

M_BBS#[1..0] 5,9

3D3V_S0

DDR_CLK#1

DDR_CLK#0

DDR_CLK1

DDR_CLK0

8

7

6

RN39

SRN10K-2

VREF_DDR_MEM5

2D5V_S3

1

2

3

45

E

VREF_DDR_MEM

3D3V_S03,6,11,12,13,14,15,16,17,18,19,20,21,24,25,26,27,28,30,31,32,33,34,35,36,38,41,47,49,50

2D5V_S35,6,7,10,38,39,44,45,50

3D3V_S0

2D5V_S3

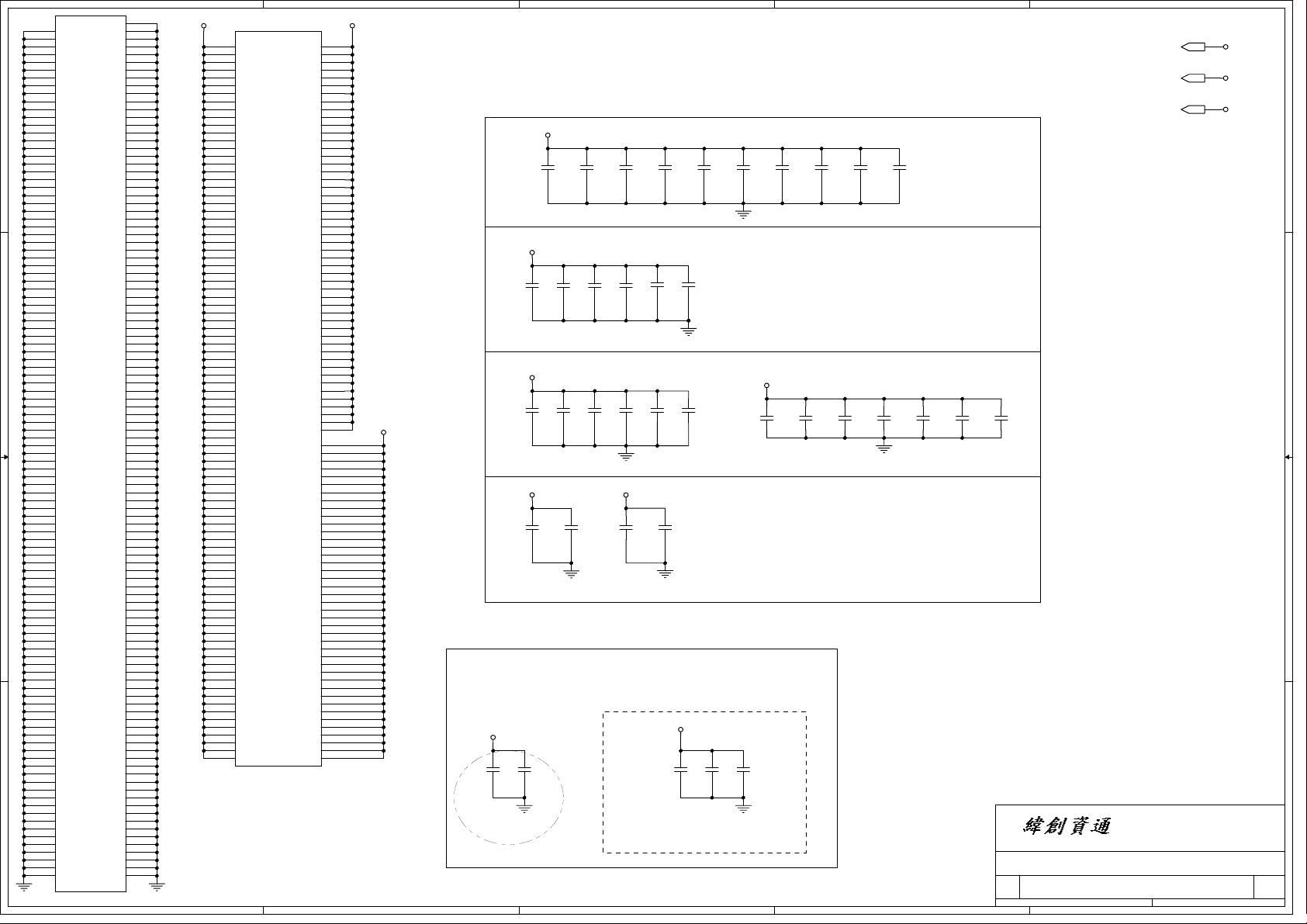

AMD K8

ClawHummar

MD63

DDR SOCKET PLACEMENT

TOP VIEW PERSPECTIVE DRAWING

DM1

Pin 199

Pin 200 Pin 2

DM2(Reverse)

Title

Size Document Number Rev

A3

D

Date: Sheet of

DDR SO-DIMM SKT

SMA11

Pin 200

Pin 199

EGRET

SMA10

SMA0

SMA14

SMA12

MD0

Pin 2

Pin 1

Pin 1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

850Friday, July 23 , 2004

E

SC

A

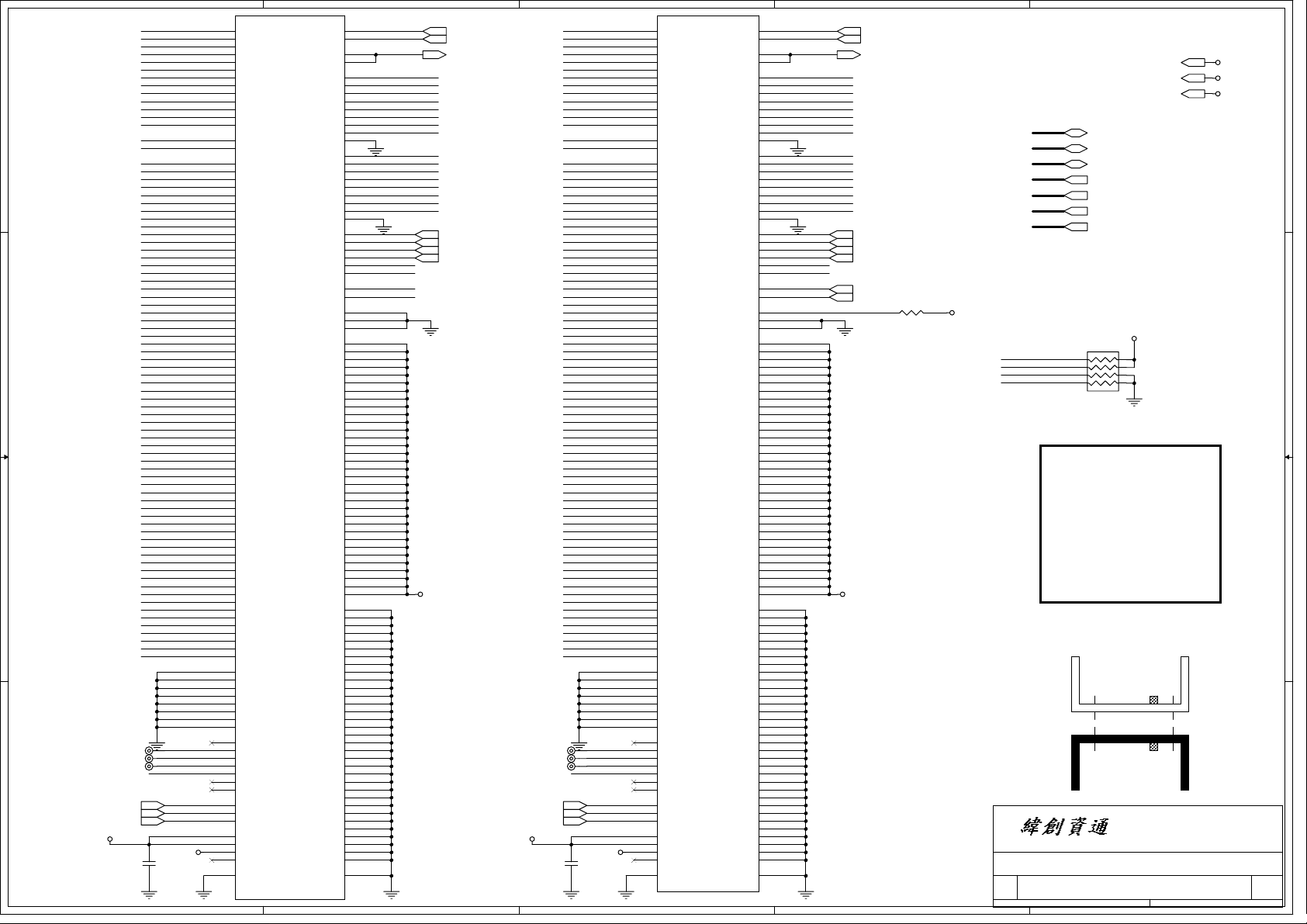

SERIES DAMPING PARALLEL TERMINATION

PLACE RNs CLOSE TO FIRST DM ( DM1 ), < 0.75"

STRICT EQUAL LENGTH LIMITATION WITH DQS,

CB PINS

M_DATA4

M_ADM0

M_DATA6

M_DATA7

M_DATA13

M_DATA12

4 4

M_ADM1

M_DATA1

M_DATA0

M_DQS0

M_DATA2

M_DATA3

M_DATA8

M_DATA9

M_DQS1

M_DATA14

M_DATA15

M_DATA21

M_DATA20

M_ADM2

M_DATA23

M_DATA22

M_DATA25 M_DATA_R_25

3 3

M_DATA11

M_DATA10

M_DATA17

M_DATA16

M_DQS2 M_DQS_R2

M_DATA19 M_DATA_R_19

M_DATA18

M_DATA24

M_DATA29

M_DATA28

M_ADM3

M_DATA26

M_DATA27

M_DATA30 M_DATA_R_30

M_DATA31

2 2

RN23

1

2

3

4

5

6

7

8 9

SRN10J-3

RN44

1

2

3

4

5

6

7

8 9

SRN10J-3

RN22

1

2

3

4

5

6

7

8 9

SRN10J-3

RN42

1

2

3

4

5

6

7

8 9

SRN10J-3

RN21

1

2

3

4

5

6

7

8 9

SRN10J-3

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

M_DATA_R_4

M_DATA_R_5M_DATA5

M_ADM_R0

M_DATA_R_6

M_DATA_R_7

M_DATA_R_13

M_DATA_R_12

M_ADM_R1

M_DATA_R_1

M_DATA_R_0

M_DQS_R0

M_DATA_R_2

M_DATA_R_3

M_DATA_R_8

M_DATA_R_9

M_DQS_R1

M_DATA_R_14

M_DATA_R_15

M_DATA_R_21

M_DATA_R_20

M_ADM_R2

M_DATA_R_23

M_DATA_R_22

M_DATA_R_11

M_DATA_R_10

M_DATA_R_17

M_DATA_R_16

M_DATA_R_18

M_DATA_R_24

M_DATA_R_29

M_DATA_R_28

M_DQS_R3M_DQS3

M_ADM_R3

M_DATA_R_26

M_DATA_R_27

M_DATA_R_31

M_DATA34

M_DATA32

M_DQS4

M_DATA33

M_DATA36

M_DATA37

M_ADM4

M_DATA39

M_DATA35

M_DATA41

M_DATA40

M_DQS5

M_DATA42

M_DATA43

M_DATA49

M_DATA48

M_DATA38

M_DATA45

M_DATA44

M_ADM5

M_DATA47

M_DATA46

M_DATA53

M_DATA52

M_DQS6

M_DATA50

M_DATA51

M_DATA56

M_DATA57

M_DQS7

M_DATA58

M_DATA59

M_ADM6

M_DATA54

M_DATA55

M_DATA61

M_DATA60

M_ADM7

M_DATA62

M_DATA63

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

RN20

SRN10J-3

RN32

SRN10J-3

RN19

SRN10J-3

RN29

SRN10J-3

RN18

SRN10J-3

B

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

M_DATA_R_34

M_DATA_R_32

M_DQS_R4

M_DATA_R_33

M_DATA_R_36

M_DATA_R_37

M_ADM_R4

M_DATA_R_39

M_DATA_R_35

M_DATA_R_41

M_DATA_R_40

M_DQS_R5

M_DATA_R_42

M_DATA_R_43

M_DATA_R_49

M_DATA_R_48

M_DATA_R_38

M_DATA_R_45

M_DATA_R_44

M_ADM_R5

M_DATA_R_47

M_DATA_R_46

M_DATA_R_53

M_DATA_R_52

M_DQS_R6

M_DATA_R_50

M_DATA_R_51

M_DATA_R_56

M_DATA_R_57

M_DQS_R7

M_DATA_R_58

M_DATA_R_59

M_ADM_R6

M_DATA_R_54

M_DATA_R_55

M_DATA_R_61

M_DATA_R_60

M_ADM_R7

M_DATA_R_62

M_DATA_R_63

M_ADM_R1

M_DATA_R_13

M_DATA_R_12

M_DATA_R_6

M_DATA_R_7

M_ADM_R0

M_DATA_R_5

M_DATA_R_4

M_DATA_R_1

M_DATA_R_0

M_DQS_R0

M_DATA_R_2

M_DATA_R_3

M_DATA_R_8

M_DATA_R_9

M_DQS_R1

M_DATA_R_25

M_DATA_R_22

M_DATA_R_23

M_ADM_R2

M_DATA_R_20

M_DATA_R_21

M_DATA_R_14

M_DATA_R_15

M_DATA_R_11

M_DATA_R_10

M_DATA_R_16

M_DATA_R_17

M_DQS_R2

M_DATA_R_19

M_DATA_R_18

M_DATA_R_24

M_DATA_R_30

M_DATA_R_31

M_DATA_R_26

M_DATA_R_27

M_ADM_R3

M_DQS_R3

M_DATA_R_29

M_DATA_R_28

RN45

1

2

3

4

5

6

7

8 9

SRN68J-1

RN65

1

2

3

4

5

6

7

8 9

SRN68J-1

RN43

1

2

3

4

5

6

7

8 9

SRN68J-1

RN64

1

2

3

4

5

6

7

8 9

SRN68J-1

RN41

1

2

3

4

5

6

7

8 9

SRN68J-1

C

PULL HIGH STUBS < 0.8", PLACE RPs CLOSE TO SECOND DM ( DM2 )

1D25V_S3 1D25V_S3

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

RN33

1

2

3

4

5

6

7

8 9

SRN68J-1

RN61

1

2

3

4

5

6

7

8 9

SRN68J-1

RN31

1

2

3

4

5

6

7

8 9

SRN68J-1

RN60

1

2

3

4

5

6

7

8 9

SRN68J-1

RN30

1

2

3

4

5

6

7

8 9

SRN68J-1

NO EQUAL LENGTH LIMITATION

M_DATA_R_36

16

M_DATA_R_32

15

M_DATA_R_37

14

M_DATA_R_33

13

M_ADM_R4

12

M_DQS_R4

11

M_DATA_R_38

10

M_DATA_R_39

M_DATA_R_48

16

M_DATA_R_49

15

M_DATA_R_43

14

M_DATA_R_42

13

M_DQS_R5

12

M_DATA_R_41

11

M_DATA_R_40

10

M_DATA_R_34

M_DATA_R_35

16

M_DATA_R_46

15

M_DATA_R_47

14

M_ADM_R5

13

M_DATA_R_44

12

M_DATA_R_45

11

M_DATA_R_53

10

M_DATA_R_52

M_DATA_R_59

16

M_DATA_R_58

15

M_DQS_R7

14

M_DATA_R_57

13

M_DATA_R_56

12

M_DATA_R_51

11

M_DATA_R_50

10

M_DQS_R6

M_DATA_R_55

16

M_DATA_R_54

15

M_ADM_R6

14

M_DATA_R_60

13

M_DATA_R_61

12

M_ADM_R7

11

M_DATA_R_63

10

M_DATA_R_62

D

M_CKE#1

M_BA12

M_CKE#0

M_AA12

M_AA11

M_AA9

M_AA7

M_AA5

M_AA4

M_AA8

M_AA6

M_AA3

M_CS#3

M_BA13

M_CS#2

M_BRAS#

M_BBS#1

M_BCAS#

M_BA0

M_BA2

M_AA1

M_AA10

M_AA2

M_AA0

M_ABS#1

M_ARAS#

M_AWE#

M_ABS#0

M_BA7

M_BA3

M_BA6

M_BA9

M_BA10

M_BA1

M_BBS#0

M_BWE#

M_BA5

M_BA8

M_BA11

M_BA4

M_AA13

M_CS#0

M_CS#1

M_ACAS#

RN63

2

1 4

SRN47J

RN40

2

1 4

SRN47J

RN37

1

2

3

4

5

6

7

8 9

SRN47J-1-U

RN36

1

2

3

4

5

6

7

8 9

SRN47J-1-U

RN35

1

2

3

4

5

6

7

8 9

SRN47J-1-U

RN62

1

2

3

4

5

6

7

8 9

SRN47J-1-U

RN38

1

2

3

4 5

SRN47-1

RN34

1

2

3

4 5

SRN47-1

3

3

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

8

7

6

8

7

6

E

1D25V_S35,6,7,10,39,45

1D25V_S3

M_ADM_R[7..0] 8

M_ADM[7..0] 5

M_DATA[63..0] 5

M_DATA_R_[63..0] 8

M_DQS[7..0] 5

M_DQS_R[7..0] 8

M_AA[13..0] 5,8

M_ABS#[1..0] 5,8

M_BA[13..0] 5,8

M_BBS#[1..0] 5,8

M_AWE# 5,8

M_ACAS# 5,8

M_ARAS# 5,8

M_BWE# 5,8

M_BCAS# 5,8

M_BRAS# 5,8

M_CS#0 5,8

M_CS#1 5,8

M_CS#2 5,8

M_CS#3 5,8

PLACE BETWEEN DM1, DM2

M_CKE#05,8

M_CKE#15,8

05/10

Remove the damping resistor for AMD suggest.

1 1

M_CKE#0

M_CKE#1

A

B

CLOSE TO FIRST DM ( DM 2 ) < 0.2", TO SECOND DM ( DM1 ) < 1.1"

EQUAL LENGTH LIMITATION WITH SCK/SCK#

R171 121R3F

1 2

R239 121R3F

1 2

R205 121R3F

1 2

R240 121R3F

1 2

M_CLK7

M_CLK#7

M_CLK6

M_CLK#6

M_CLK5

M_CLK#5

M_CLK4

M_CLK#4

C

M_CLK7 5,8

M_CLK#7 5,8

M_CLK6 5,8

M_CLK#6 5,8

M_CLK5 5,8

M_CLK#5 5,8

M_CLK4 5,8

M_CLK#4 5,8

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

D

Date: Sheet of

DDR DAMPING & TERMINATION

EGRET

950Friday, July 23 , 2004

E

SC

A

B

C

D

E

2D5V_S35,6,7,8,38,39,44,45,50

1D25V_S35,6,7,9,39,45

4 4

2D5V_S3

1D25V_S3

3 3

1D25V_S3

12

12

2D5V_S3

12

12

C269

SCD1U

C249

SCD1U

C367

SCD1U

C366

SCD1U

12

12

C347

C349

SCD1U

DY-SCD1U

12

12

C346

C348

SCD1U

DY-SCD1U

12

12

C328

C369

SCD1U

DY-SCD1U

12

12

C327

C368

SCD1U

LAYOUT:Place altemating caps to GND and 2D5_S3

12

12

12

12

12

12

C351

SCD1U

C350

SCD1U

C330

SCD1U

C329

SCD1U

12

12

C319

DY-SCD1U

12

12

C318

DY-SCD1U

12

12

C301

DY-SCD1U

12

12

C370

C353

SCD1U

C352

SCD1U

C258

SCD1U

C303

SCD1U

12

12

12

C355

SCD1U

C354

SCD1U

C214

SCD1U

C259

SCD1U

12

C296

C357

SCD1U

DY-SCD1U

12

12

C297

C356

SCD1U

DY-SCD1U

12

12

C197

C316

SCD1U

DY-SCD1U

12

12

C230

C199

SCD1U

12

12

12

12

C322

SCD1U

C358

SCD1U

C288

SCD1U

C315

SCD1U

12

12

C359

C361

SCD1U

DY-SCD1U

12

12

C323

C360

SCD1U

DY-SCD1U

12

12

C324

SCD1U

C325

SCD1U

12

C293

DY-SCD1U

12

C291

DY-SCD1U

12

12

C292

SCD1U

C294

SCD1U

12

12

C363

SCD1U

C362

SCD1U

12

C365

DY-SCD1U

12

C364

DY-SCD1U

LAYOUT:Locate close to CPU socket.

2D5V_S3 1D25V_S3

TC16

1 2

DY-SE220U2VDM-6

C659

1 2

SC22U10V6ZY-U

SB

12

C268

DY-SCD1U

12

C287

12

12

C227

SCD1U

C267

SCD1U

12

12

C333

SCD1U

C226

SCD1U

12

12

12

12

C371

SCD1U

C251

SCD1U

12

C213

DY-SCD1U

12

C193

C252

C256

SCD1U

DY-SCD1U

12

12

C229

C334

SCD1U

1D25V_S3

12

C804

12

C805

DY-SCD1U

DY-SCD1U

12

12

C806

C807

DY-SCD1U

DY-SCD1U

12

C809

12

C810

DY-SCD1U

DY-SCD1U

12

C808

DY-SCD1U

2D5V_S3

1D25V_S3

DY-SCD1U

2 2

DY-SCD1U

DY-SCD1U

DY-SCD1U

DY-SCD1U

DY-SCD1U

LAYOUT:Place close to Power Pin of DDR socket.

LAYOUT:Place at end of the DIMMs

1D25V_S3

12

1 1

SC

TC23

DY-ST100U4VBM

12

TC24

ST100U4VBM-1

80.10716.321

KEMET,NT:5.7, B2 size

ST100U4VBM-1 (80.10716.321)

Iripple=1.1A,ESR=70mohm

SANYO, NT$:6.1

Iripple=1.1A,ESR=70mohm

3.5/2.8/2.0

77.21071.031

A

12

C786

SC22U10V6ZY-U

12

C787

SC22U10V6ZY-U

12

C795

SC22U10V6ZY-U

B

12

C796

SC22U10V6ZY-U

C

2D5V_S3 2D5V_S3

C271

SCD22U16V3ZY

1 2

C289

DY-SCD22U16V3ZY

1 2

C298

DY-SCD22U16V3ZY

1 2

C290

SCD22U16V3ZY

1 2

C321

SCD22U16V3ZY

1 2

0.22u x 10

D

C273

SCD22U16V3ZY

1 2

C274

DY-SCD22U16V3ZY

1 2

C295

DY-SCD22U16V3ZY

1 2

C320

SCD22U16V3ZY

1 2

C326

SCD22U16V3ZY

1 2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet of

DDR DECOUPLING

EGRET

E

10 50Friday, July 23 , 2004

SC

A

B

C

D

E

3D3V_S03,6,8,12,13,14,15,16,17,18,19,20,21,24,25,26,27,28,30,31,32,33,34,35,36,38,41,47,49,50

1D2V_HT0A_S04,13,39,45

2D5V_S06,12,14,15,1 6,19,20,21,38,39,50

4 4

CLAW HAMMER TO NB

CPUCADOUT[15..0]4

3 3

2 2

CPUHTTCLKOUT04

CPUHTTCLKOUT14

CPUHTTCTLOUT04

CPUCADOUTJ[15..0]4

CPUHTTCLKOUTJ14

CPUHTTCTLOUTJ04

LDTRST#21

LDTSTP#21

CPUCADOUT0

CPUCADOUT1

CPUCADOUT2

CPUCADOUT3

CPUCADOUT4

CPUCADOUT5

CPUCADOUT6

CPUCADOUT7

CPUCADOUT8

CPUCADOUT9

CPUCADOUT10

CPUCADOUT11

CPUCADOUT12

CPUCADOUT13

CPUCADOUT14

CPUCADOUT15

CPUHTTCLKOUT0

CPUHTTCLKOUT1

CPUHTTCTLOUT0

CPUCADOUTJ0

CPUCADOUTJ1

CPUCADOUTJ2

CPUCADOUTJ3

CPUCADOUTJ4

CPUCADOUTJ5

CPUCADOUTJ6

CPUCADOUTJ7

CPUCADOUTJ8

CPUCADOUTJ9

CPUCADOUTJ10

CPUCADOUTJ11

CPUCADOUTJ12

CPUCADOUTJ13

CPUCADOUTJ14

CPUCADOUTJ15

CPUHTTCLKOUTJ0

CPUHTTCLKOUTJ1

CPUHTTCTLOUTJ0

LDTRST#

LDTSTP#

RPCOMP

RNCOMP

RTCOMP

1D2V_HT0A_S0

3D3VA_HT_S0

C22

AVDD2

T26

RCADP0

P24

RCADP1

P26

RCADP2

M24

RCADP3

K24

RCADP4

K26

RCADP5

H24

RCADP6

H26

RCADP7

R24

RCADP8

R22

RCADP9

N24

RCADP10

N22

RCADP11

L22

RCADP12

J24

RCADP13

J22

RCADP14

G24

RCADP15

M26

RCLKP0

L24

RCLKP1

F24

RCTLP

R26

RCADN0

P25

RCADN1

N26

RCADN2

M25

RCADN3

K25

RCADN4

J26

RCADN5

H25

RCADN6

G26

RCADN7

R23

RCADN8

P22

RCADN9

N23

RCADN10

M22

RCADN11

K22

RCADN12

J23

RCADN13

H22

RCADN14

G23

RCADN15

L26

RCLKN0

L23

RCLKN1

F25

RCTLN

B11

LDTRST

A12

LDTSTP

D25

RPCOMP

D26

RNCOMP

C26

RTCOMP

U24

VLDT

U25

VLDT

U26

VLDT

V21

VLDT

V22

VLDT

V23

VLDT

V24

VLDT

V25

VLDT

V26

VLDT

AGND2

C21

A10

VLDT

VSSA8VSS

VSS

A23

A24

A25

VLDT

VSSB8VSS

B13

AGND2

A26

B10

B23

B24

B25

B26

C10

C11

C23

C24

C25

D10

D11

D22

D23

D24

E10

E11

E21

E22

E23

E24

F10

F11

F15

F16

F19

F20

F21

F22

F23

G21

G22

H21

VLDT

VLDT

VLDTA9VLDT

VLDT

VLDT

VLDT

VLDT

VLDTB9VLDT

VLDT

VLDT

VLDT

VLDT

VLDTC9VLDT

VLDT

VLDT

VLDT

VLDT

VLDTD9VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDTE9VLDT

VLDT