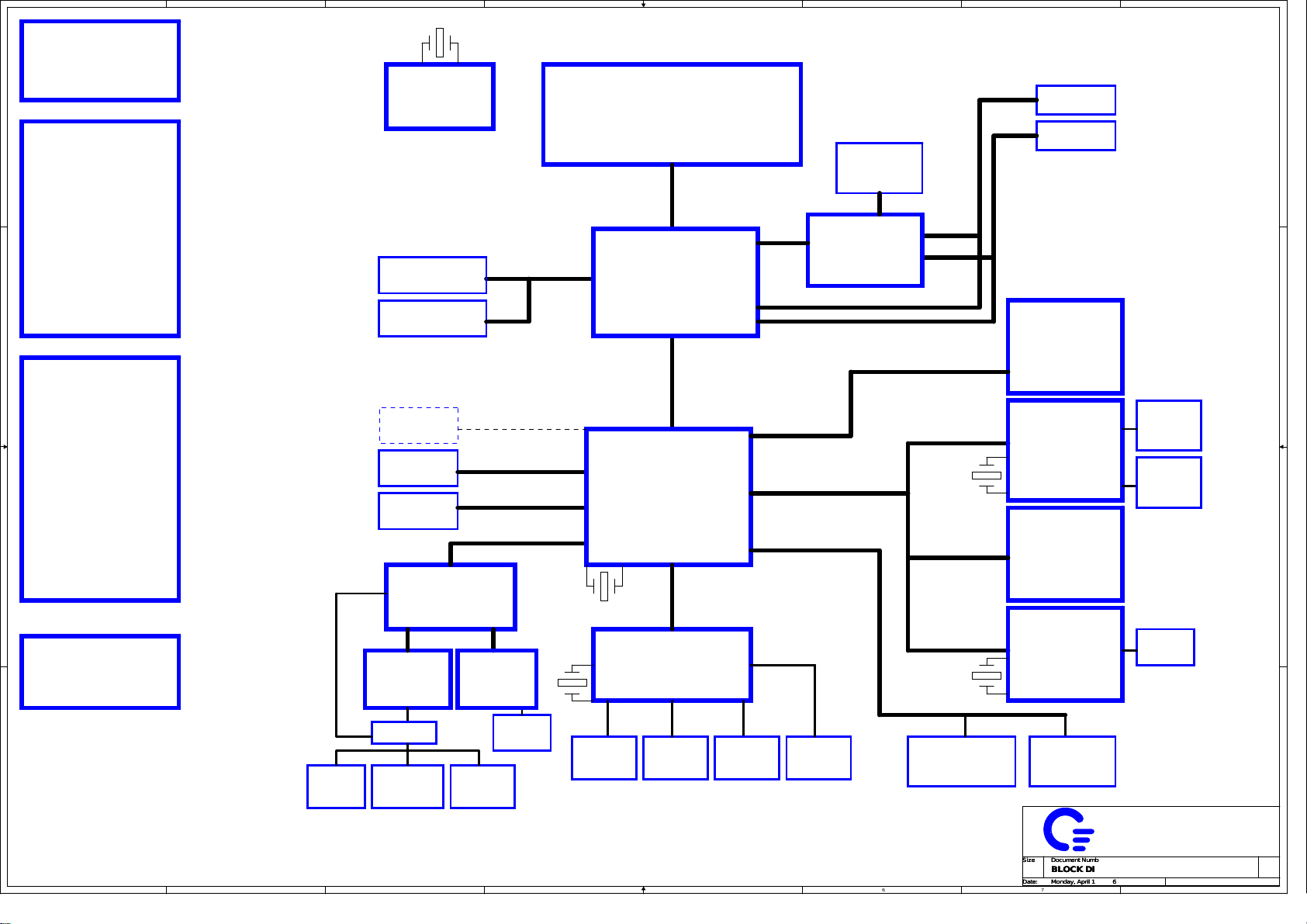

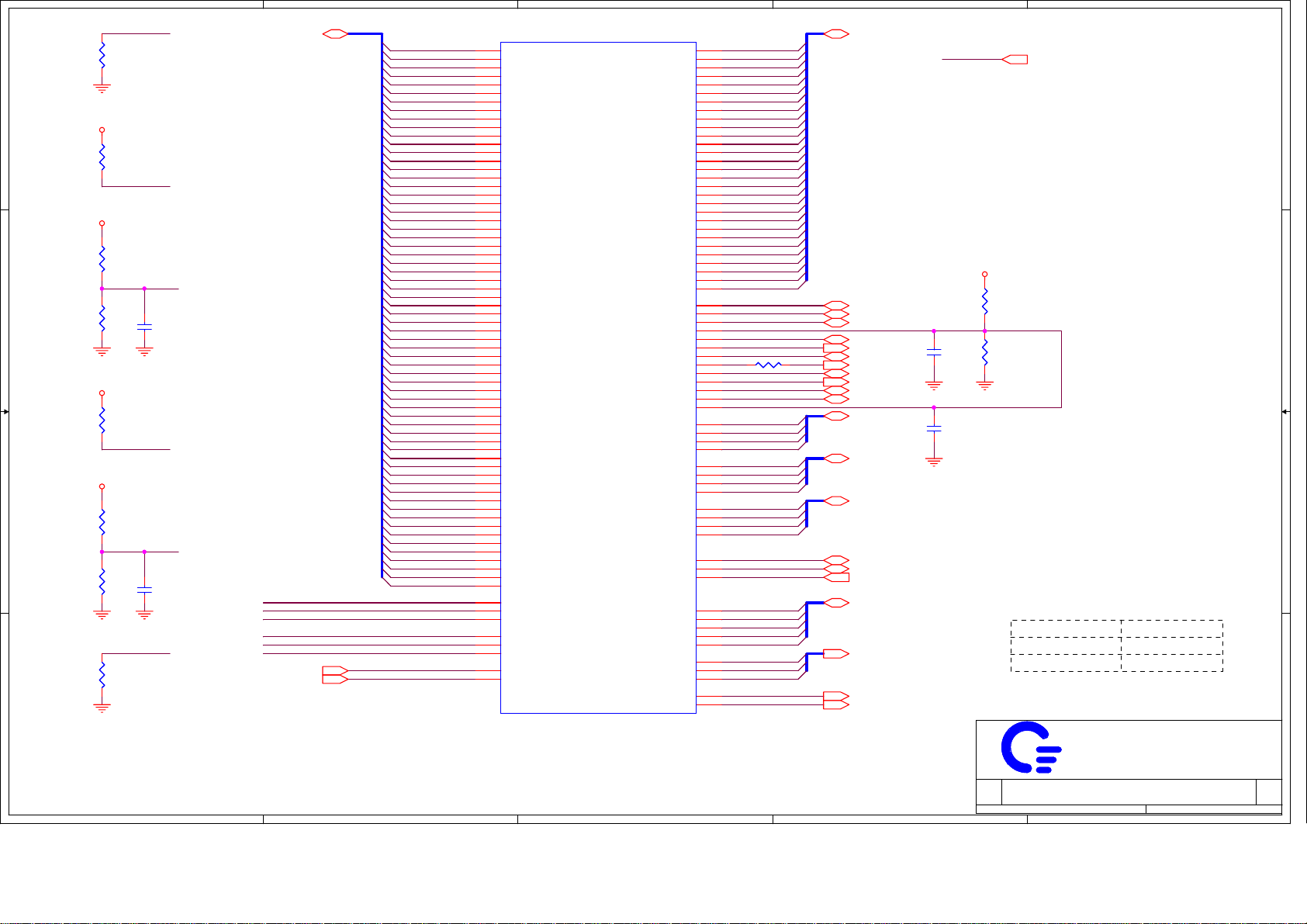

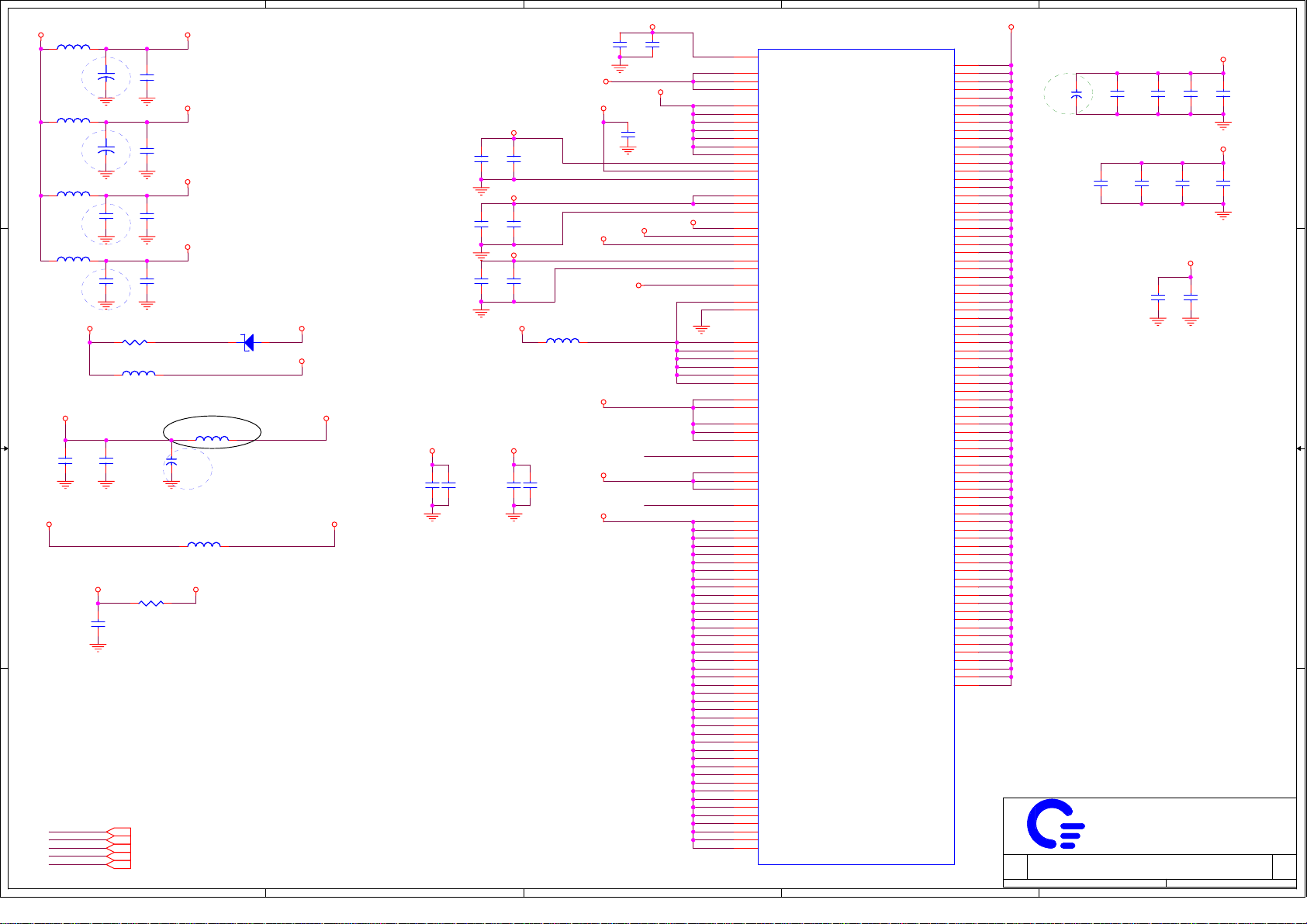

Acer TM4220, AS5600 Schematics

1

www.kythuatvitinh.com

Digitally signed by dd

DN: cn=dd, o=dd, ou=dd,

email=dddd@yahoo.com,

c=US

Date: 2009.11.29 17:25:45

+07'00'

2

3

4

5

6

7

8

CPU CORE

SENTECH

SC451ITSTR

A A

Page:32

CLOCK GEN

ICS954310BG

SYSTEM 3V/5V

MAXIM

MAX1999

+3VPCU

+3V_S5

+3VSUS

+3V

+5VPCU

+5VSUS

+5V

+15V

B B

Page:33

DDR-II SODIMM1

Page: 12

DDR-II SODIMM2

Page: 12

+1.8VSUS

+1.8V

+0.9VSUS

+0.9V

SATA HDD

Page: 23

+1.5V

+1.05V

+2.5V

Page:34

PATA HDD

Page: 23

IDE-ODD

Page: 23

+1.2V

VGA_CORE

C C

Page:36

AUDIO CODEC

ALC883 (ALC260)

BATTERY CHARGER

MAXIM

MAX8724

Page:35 Page: 25

MAX9755

Page: 29

Page:4

Realtek

X'TAL

14.318MHZ

Page: 28

MODEMAMP

Page: 28

DDR-II

ATA 66/100

ATA 66/100

HD Audio

ZB2

Yonah/Merom

INTEL Mobile_479 CPU

CALISTOGA-GM

Page: 5, 6 , 7, 8, 9, 10

X'TAL

32.768KHZ

X'TAL

32.768K

HOST BUS 533/667 MHz

1466 FCBGA

DMI I/F

ICH7-M

652 BGA

Page: 13,14,15,16

LPC 33MHZ

KBC

NS PC97551/541V

Page: 30

Page:2, 3

PCIE

PCI-E BUS

PCI BUS 33MHZ

USB 2.0

VRAM x4

DDR2

16Mx16

32Mx16

ATi

M52P

/M52PG

/M54P

UMA(option)

Page: 17,

18,19, 20

RGB

LVDS

X'TAL

25M

OSC

48MHZ

CRT

Page: 22

LVDS

Page: 22

MINI-Card slot

Wireless LAN

Page: 24

TI PCI7412

AD25

REQ0#

GNT0#

INTE#

INTF#

INTG#

Page: 26

MINI-PCI

Wireless LAN

AD19

REQ2# / GNT2#

INTC# , INTD#

Page: 24

REALTEK

RTL8100CL

AD16

REQ1#

GNT1#

INTB#

TYPE II

SLOT

Page: 26

6 IN 1

Cardreader

Page: 27

RJ45

Page: 25

Connector

D D

SPEAKER LINE OUTMIC IN

1

2

3

RJ11

Page: 25

Page: 29Page: 29 Page: 29

Touchpad

Page: 29

4

Keyboard

Page: 31

FLASH

Page: 30

5

FAN

Page: 31

SYSTEM

USB PORT *3

Page:24

6

Bluetooth

USB

interface

Page:24

PROJECT : ZB2

PROJECT : ZB2

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet

Date: Sheet

Date: Sheet

7

Quanta Computer Inc.

137Monday, April 10, 2006

137Monday, April 10, 2006

137Monday, April 10, 2006

of

of

of

8

1A

1A

1A

5

www.kythuatvitinh.com

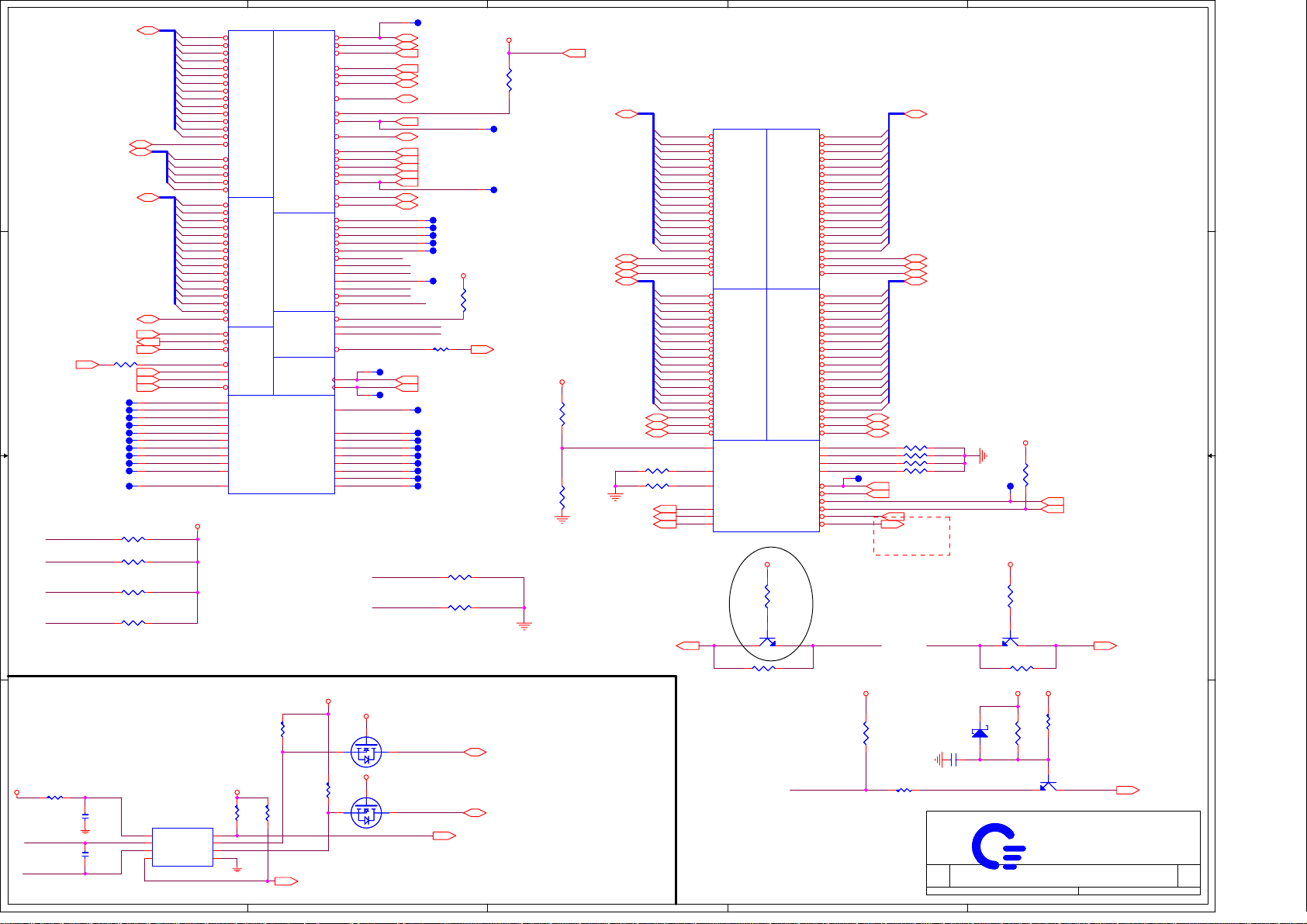

U29A

H_A#[16:3][5]

D D

H_ADSTB0#[5]

H_REQ#[4:0][5]

H_A#[31:17][5]

H_ADSTB1#[5]

H_A20M#[13]

C C

H_STPCLK#[13]

XDP_DBRESET#

XDP_TMS

B B

XDP_TDI

XDP_BPM#5

H_FERR#[13]

H_IGNNE#[13]

R131 0_4R131 0_4

H_INTR[13]

H_NMI[13]

H_SMI#[13]

T105T105

T103T103

T102T102

T104T104

T109T109

T108T108

T107T107

T106T106

T111T111 R12427.4/F_6 R12427.4/F_6

T38T38

T138T138

R186 *54.9/F_4R186 *54.9/F_4

R133 39.2/F_4R133 39.2/F_4

R132 150_4R132 150_4

R134 54.9/F_4R134 54.9/F_4

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_STPCLK_R#

TP_A32#

TP_A33#

TP_A34#

TP_A35#

TP_A36#

TP_A37#

TP_A38#

TP_A39#

TP_APM0#

TP_APM1#

TP_HFPLL

U29A

H_A#3

J4

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

+1.05V

XDP_TCK PD 27.4/1%

XDP_TRST PD 680ohm /5%

XDP_TDI PU 150ohm /1.05V

XDP_TMS PU 39.2/1%

ADDR GROUP 0

ADDR GROUP 0

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]#

RSVD[02]#

RSVD[03]#

RSVD[04]#

RSVD[05]#

RSVD[06]#

RSVD[07]#

RSVD[08]#

RSVD[09]#

RSVD[10]#

RSVD[11]#

PZ47903-2741-01

PZ47903-2741-01

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

CONTROL

CONTROL

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

PROCHOT

THERMDA

THERMDC

THERMTRIP#

THERMH CLK

THERMH CLK

BCLK[0]

BCLK[1]

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RESERVED

RESERVED

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

H/W MONITOR

R213

R213

10K_4

10K_4

SLAVE ADDRESS: 98

R209

To FAN

R209

10K_4

10K_4

MAX6648_OV# [31]

+3V +3V

R212 47_6R212 47_6

A A

THERMDC

THERMDA

10 mil trace /

10 mil space

15 MIL

3V_THM

C260

C260

.1U/10V_4

.1U/10V_4

C261

C261

2200P_4

2200P_4

5

U8

1

VCC

3

DXN

2

DXP

-OVT4GND

G781U8G781

-ALT

SMDATA

SMCLK

R215

R215

10K_4

10K_4

6

7

8

5

R438

R438

*10K_4

*10K_4

KBSMDAT

KBSMCLK

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

+3V

1

1

4

H_RS#0

H_RS#1

H_RS#2

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_PROCHOT_R#

THERMDA

THERMDC

THERMTRIP#_PWR

T131T131

T130T130

TP_EXTBREF

TP_SPARE0

TP_SPARE1

TP_SPARE2

TP_SPARE3

TP_SPARE4

TP_SPARE5

TP_SPARE6

TP_SPARE7

XDP_TCK

XDP_TRST#

+3V

2

Q20

Q20

3

2N7002

2N7002

+3V

2

Q21

Q21

3

2N7002

2N7002

4

T22T22

H_ADS# [5]

H_BNR# [5]

H_BPRI# [5]

H_DEFER# [5]

H_DRDY# [5]

H_DBSY# [5]

H_BREQ#0 [5]

H_INIT# [13]

H_LOCK# [5]

H_CPURST# [5]

H_RS#0 [5]

H_RS#1 [5]

H_RS#2 [5]

H_TRDY# [5]

H_HIT# [5]

H_HITM# [5]

T18T18

T19T19

T99T99

T14T14

T100T100

T101T101

R241 *0_4R241 *0_4

CLK_CPU_BCLK [4]

CLK_CPU_BCLK# [4]

T58T58

T25T25

T40T40

T39T39

T110T110

T98T98

T52T52

T51T51

T137T137

R136 27.4/F_4R136 27.4/F_4

R135 680_4R135 680_4

CPU_MBDATA

CPU_MBCLK

To SB

+1.05V

T129T129

T16T16

XDP PU_R < 0.2"

+1.05V

R194

R194

68_4

68_4

PM_THRMTRIP# [7,13]

Close CPU

CPU_MBDATA [30]

CPU_MBCLK [30]

THERM_ALERT# [15]

R190

R190

56.2/F_4

56.2/F_4

+1.05V

R205

R205

1K/F_4

1K/F_4

R206

R206

2K/F_6

2K/F_6

+1.05V [3,4,5,8,9,13,16,33,34]

H_D#[15:0][5]

H_DSTBN#0[5]

H_DSTBP#0[5]

H_DINV#0[5]

H_D#[31:16][5]

+1.05V

20/15mils

3

Near to MCH <500mils

H_D#0

E22

H_D#1

F24

H_D#2

E26

H_D#3

H22

H_D#4

F23

H_D#5

G25

H_D#6

E25

H_D#7

E23

H_D#8

K24

H_D#9

G24

H_D#10

H_D#11

H_D#12

H26

H_D#13

F26

H_D#14

K22

H_D#15

H25

H23

G22

H_D#16

N22

H_D#17

K25

H_D#18

P26

H_D#19

R23

H_D#20

L25

H_D#21

L22

H_D#22

L23

H_D#23

M23

H_D#24

P25

H_D#25

P22

H_D#26

P23

H_D#27

T24

H_D#28

R24

H_D#29

L26

H_D#30

T25

H_D#31

N24

*1K/F_4

*1K/F_4

51/F_4

51/F_4

M24

N25

M26

AD26

C26

D25

C21

B22

B23

H_DSTBN#1[5]

H_DSTBP#1[5]

H_DINV#1[5]

CPU_BSEL0[4]

CPU_BSEL1[4]

CPU_BSEL2[4]

H_GTLREF

R446

R446

R445

R445

To EC

3

U29B

U29B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

J24

D[10

J23

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

J26

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

PZ47903-2741-01

PZ47903-2741-01

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

DATA GRP 2

DATA GRP 2

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DATA GRP 3

DATA GRP 3

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

MISC

MISC

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

PWRGOOD

R526

R526

330_6

330_6

2

Q27 MMBT3904Q27 MMBT3904

13

R196 *0_4R196 *0_4

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DPWR#

SLP#

PSI#

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

H_D#32

AA23

REV_2A/12-13 Add

THERMTRIP#_PWR

2

27.4/F_6

27.4/F_6

R245 330_4R245 330_4

2

H_DSTBN#3 [5]

H_DSTBP#3 [5]

H_DINV#3 [5]

R12554.9/F_4 R12554.9/F_4

ICH_DPRSTP# [13,32]

H_DPSLP# [13]

H_CPUSLP# [5,13]

PSI# [32]

TO VRD

R419

R419

56_4

56_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

H_D#[47:32] [5]

H_DSTBN#2 [5]

H_DSTBP#2 [5]

H_DINV#2 [5]

H_D#[63:48] [5]

Close CPU

R208

R208

R20754.9/F_4 R20754.9/F_4

XDP_DBRESET#H_PROCHOT_R#

C274

C274

*4.7U-10V_8

*4.7U-10V_8

CPU(1 OF 2 )

CPU(1 OF 2 )

CPU(1 OF 2 )

+1.05V

25/25mils

D2*CH500H-40 D2*CH500H-40

R129

R129

T136T136T21T21

*200/F_6

*200/F_6

H_PWRGD is CMOS driving by ICH

+1.05V+1.05V

R428

R428

*330_6

*330_6

2

Q17

Q17

1 3

*MMBT3904

*MMBT3904

R431 0_4R431 0_4

VCC_CORE+1.05V+1.05V

R243

R243

*330_4

*330_4

2

1 3

Q9 MMBT3904Q9 MMBT3904

PROJECT : ZB2

PROJECT : ZB2

Quanta Computer Inc.

Quanta Computer Inc.

H_DPWR# [5]

H_PWRGD [13]

R242

R242

330_4

330_4

1

CPU

SYS_RST# [15]H_PROCHOT#[30]

1999_SHT# [33]

2A

2A

2A

of

of

of

237Monday, April 10, 2006

237Monday, April 10, 2006

237Monday, April 10, 2006

1

5

www.kythuatvitinh.com

U29D

U29D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

D D

C C

B B

A A

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

P3

VSS[081]

PZ47903-2741-01

PZ47903-2741-01

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

+1.05V

VCC_CORE

+1.5V

VCC_CORE

5

4

+1.05V [2,4,5,8,9,13,16,33,34]

VCC_CORE [2,32]

+1.5V [7,9,14,16,24,28,33,34]

C237

C237

10U-6.3V_8

10U-6.3V_8

C213

C213

10U-6.3V_8

10U-6.3V_8

C185

C185

10U-6.3V_8

10U-6.3V_8

C220

C220

10U-6.3V_8

10U-6.3V_8

C263

C263

10U-6.3V_8

10U-6.3V_8

C613

C613

10U-6.3V_8

10U-6.3V_8

C608

C608

10U-6.3V_8

10U-6.3V_8

C624

C624

10U-6.3V_8

10U-6.3V_8

C189

C189

10U-6.3V_8

10U-6.3V_8

C217

C217

10U-6.3V_8

10U-6.3V_8

C191

C191

10U-6.3V_8

10U-6.3V_8

C236

C236

10U-6.3V_8

10U-6.3V_8

C264

C264

10U-6.3V_8

10U-6.3V_8

C612

C612

10U-6.3V_8

10U-6.3V_8

C609

C609

10U-6.3V_8

10U-6.3V_8

C623

C623

10U-6.3V_8

10U-6.3V_8

C193

C193

10U-6.3V_8

10U-6.3V_8

C230

C230

10U-6.3V_8

10U-6.3V_8

C197

C197

10U-6.3V_8

10U-6.3V_8

C244

C244

10U-6.3V_8

10U-6.3V_8

C265

C265

10U-6.3V_8

10U-6.3V_8

C611

C611

10U-6.3V_8

10U-6.3V_8

C626

C626

10U-6.3V_8

10U-6.3V_8

C621

C621

10U-6.3V_8

10U-6.3V_8

C199

C199

10U-6.3V_8

10U-6.3V_8

C238

C238

10U-6.3V_8

10U-6.3V_8

C214

C214

10U-6.3V_8

10U-6.3V_8

C262

C262

10U-6.3V_8

10U-6.3V_8

C266

C266

10U-6.3V_8

10U-6.3V_8

C610

C610

10U-6.3V_8

10U-6.3V_8

C625

C625

10U-6.3V_8

10U-6.3V_8

C622

C622

10U-6.3V_8

10U-6.3V_8

change to 0805

REV_3A/02-09 Change to 10U

4

3

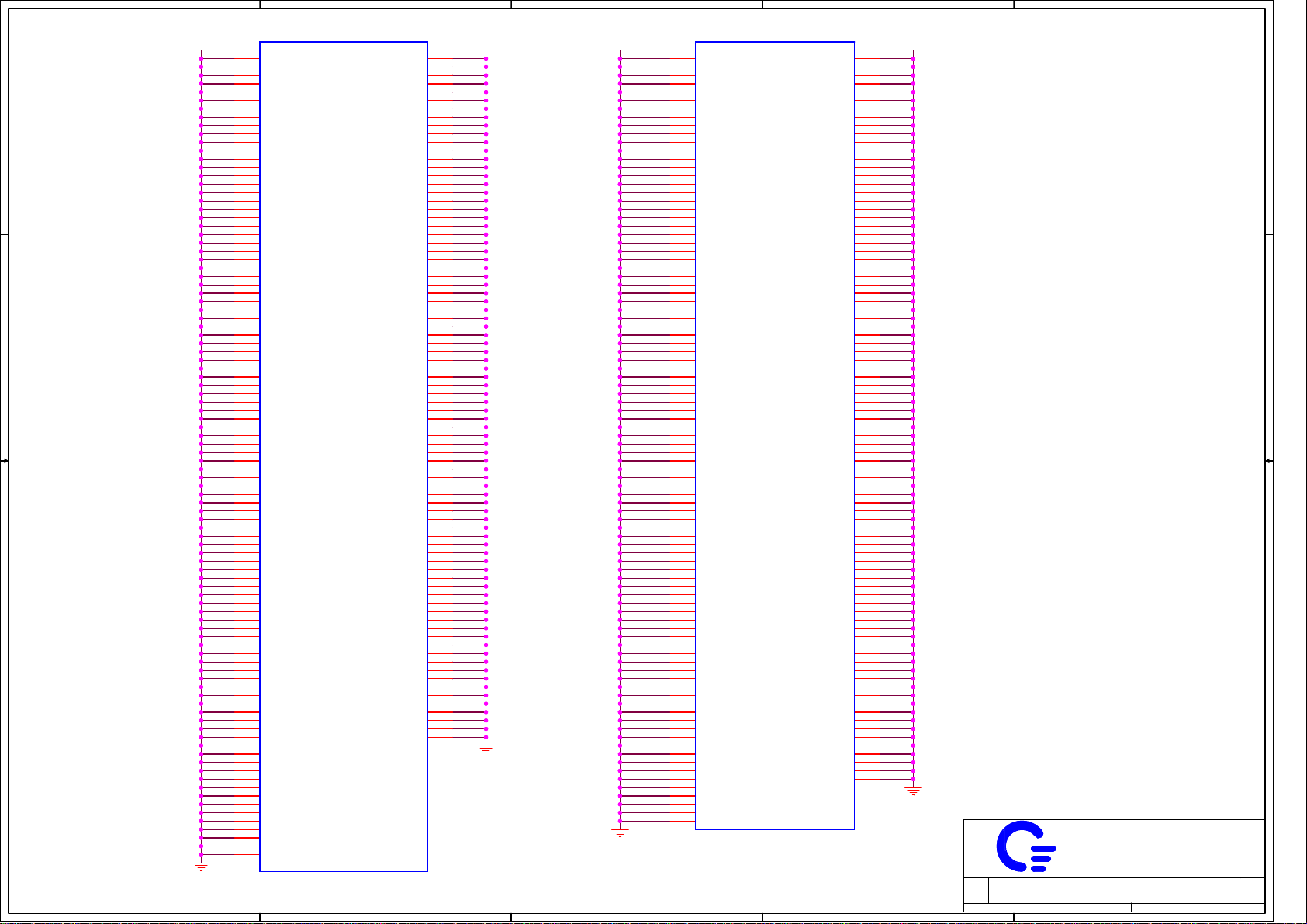

U29C

U29C

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

PZ47903-2741-01

PZ47903-2741-01

3

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

2

VCC_COREVCC_CORE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

+1.05V

+1.05V

R162 100/F_4R162 100/F_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

VCC_CORE

REV_3A/02-09 Change to 10U

C186

C186

.1U/10V_4

.1U/10V_4

C144

C144

330U-2.5V_7343

330U-2.5V_7343

+

+

CPU(2 OF 2 )

CPU(2 OF 2 )

CPU(2 OF 2 )

2

C216

C200

C200

10U-6.3V_8

10U-6.3V_8

C187

C187

.1U/10V_4

.1U/10V_4

C211

C211

10U-6.3V_8

10U-6.3V_8

+1.5V

C216

10U-6.3V_8

10U-6.3V_8

reserve dummy cap--Allen

C243

C243

C242

C242

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

+1.5V

C637

C637

.01U/16V_4

.01U/16V_4

Close CPU B26

CPU_VID0 [32]

CPU_VID1 [32]

CPU_VID2 [32]

CPU_VID3 [32]

CPU_VID4 [32]

CPU_VID5 [32]

CPU_VID6 [32]

VCC_CORE

R164

R164

100/F_4

100/F_4

VCCSENSE [32]

VSSSENSE [32]

PROJECT : ZB2

PROJECT : ZB2

Quanta Computer Inc.

Quanta Computer Inc.

1

C225

C225

10U-6.3V_8

10U-6.3V_8

C149

C149

.1U/10V_4

.1U/10V_4

C639

C639

10U/X5R-6.3V_8

10U/X5R-6.3V_8

337Monday, April 10, 2006

337Monday, April 10, 2006

337Monday, April 10, 2006

of

of

of

1

CPU

C153

C153

.1U/10V_4

.1U/10V_4

3A

3A

3A

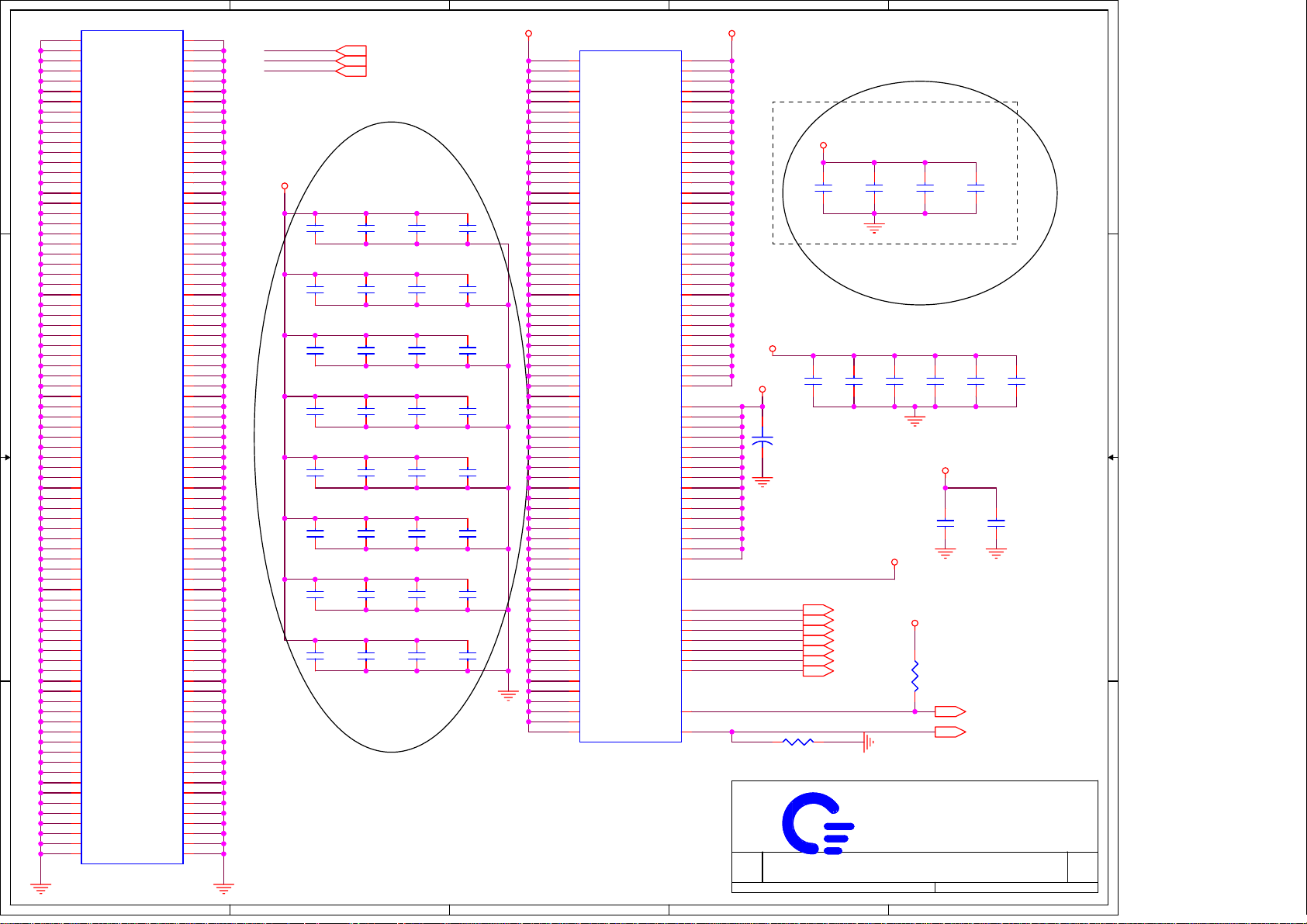

A

www.kythuatvitinh.com

B

C

D

E

Note : If Use Internal VGA Please NC "EV@xxx" Parts

C246

C246

*10P/50V_4

*10P/50V_4

2

4

2

4

4

2

2

4

4

2

4

2

4

2

4

2

4

2

437Monday, April 10, 2006

437Monday, April 10, 2006

437Monday, April 10, 2006

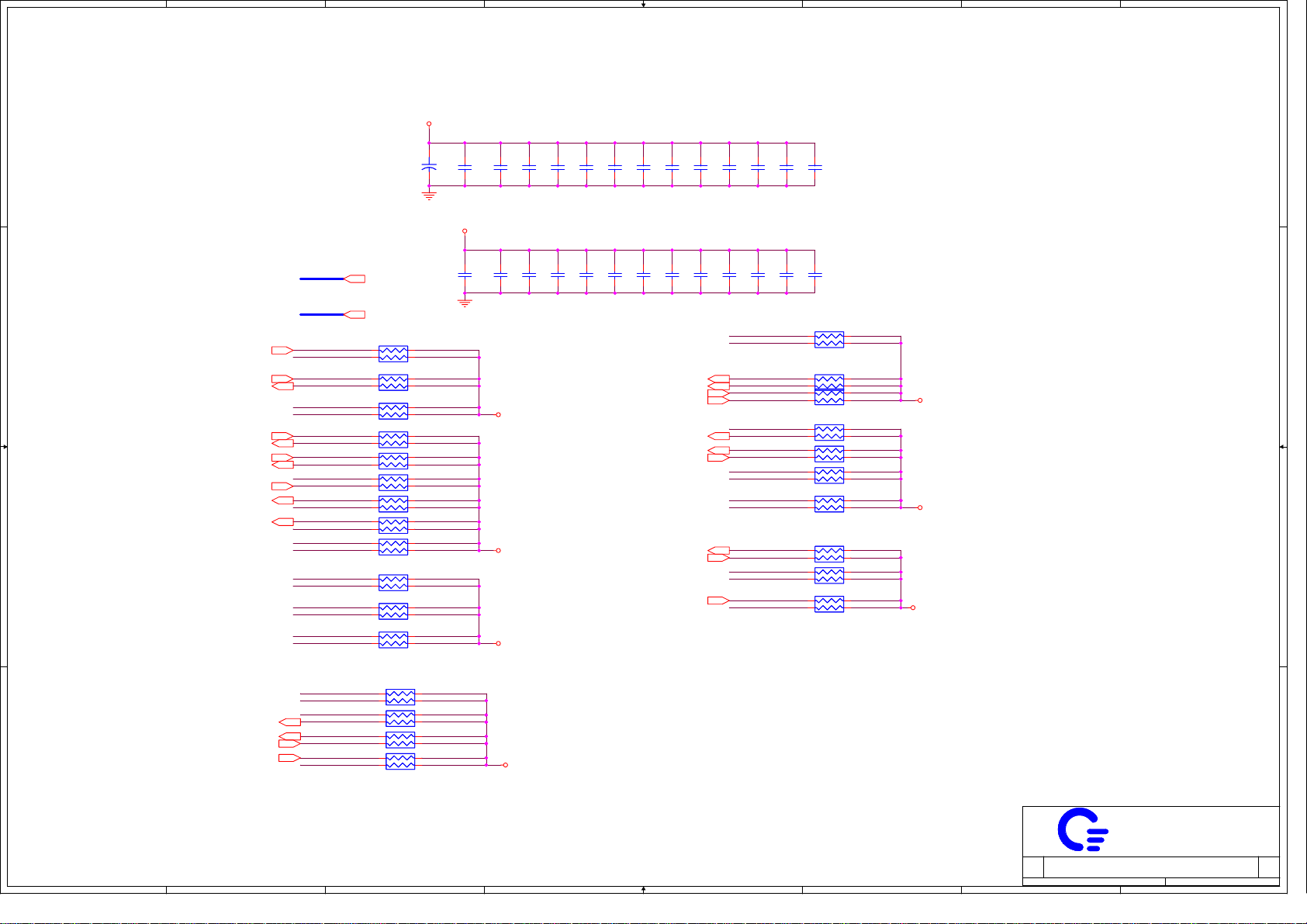

CLK

14M_ICH [15]

of

of

3B

3B

3B

Close to IC <500mils

REV_3B/03-14 Add

L21

L21

ACB2012L-120-T_8

ACB2012L-120-T_8

+3V

120 ohms@100Mhz

4 4

L22

L22

+3V

ACB2012L-120-T_8

ACB2012L-120-T_8

3 3

VR_PWRGD_CK410#[15,32]

VR_PWRGD_CK410_R#[15]

2 2

MINI_CLKREQ3#[24]

1 1

PDAT_SMB[15,24]

PCLK_SMB[15,24]

25 mils

VDD_SRC_CPU

C235

C235

C182

C182

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

R187 2.2/F_6R187 2.2/F_6

VDD_A

25 mils

VDD_PCI

R153 2.2/F_6R153 2.2/F_6

R189 1_6R189 1_6

REQ3 Latched Select

"0" : CLK Enable

"1" : CLK Disable

Control : PCIE 2,4

MINI_CLKREQ3#

PEREQ Control Pair

PEREQ1

PEREQ2

PEREQ3

PEREQ4

Q18

Q18

RHU002N06

RHU002N06

3

Q19

Q19

RHU002N06

RHU002N06

3

A

VDD_48

VDD_REF

R540 0_4R540 0_4

R541 *0_4R541 *0_4

PECLK Pair0, 6

PECLK Pair1, 8

PECLK Pair2, 4

PECLK Pair3, 5, 7

+3V

R430

R430

2

+3V

2

C179

C179

C233

C233

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

C247

C231

C231

.1U/10V_4

.1U/10V_4

C247

10U/10V_8

10U/10V_8

VR_PWRGD_CK410#_C

C724

C724

.1U/10V_4

.1U/10V_4

REV_3A/02-05 Add

C192

C192

C180

C180

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

C181

C181

.1U/10V_4

.1U/10V_4

C234

C234

.1U/10V_4

.1U/10V_4

VR_PWRGD_CK410#_C

REV_3A/02-09 Add

R169 10K_4R169 10K_4

R432

10K_4

10K_4

R432

10K_4

10K_4

SMBDT

1

1

SMBCK

C194

C194

10U/10V_8

10U/10V_8

C169

C169

10U/10V_8

10U/10V_8

C245

C245

10U/10V_8

10U/10V_8

+3V

C183

C183

10U/10V_8

10U/10V_8

VDD_A

U6

U6

X1

X2

Vtt_PwrGd#/PD

CPU_STOP#

PCI/PCIE_STOP#

SCLK

SDATA

FSA/USB_48MHz

FSB/TEST_MODE

REF1/FSLC/TEST_SEL

VDD_REF

VDDCPU

1

VDD_PCI_1

7

VDD_PCI_2

VDD_PCIE

VDDPCIE

VDD_PCIE

VDD_48

REQ3(PCIE)

REQ4(PCIE)

IREF

DOT96MHz

DOT96MHz#

PWRSAVE#

GND

13

53

R409 1K_4R409 1K_4

R418 1K_4R418 1K_4

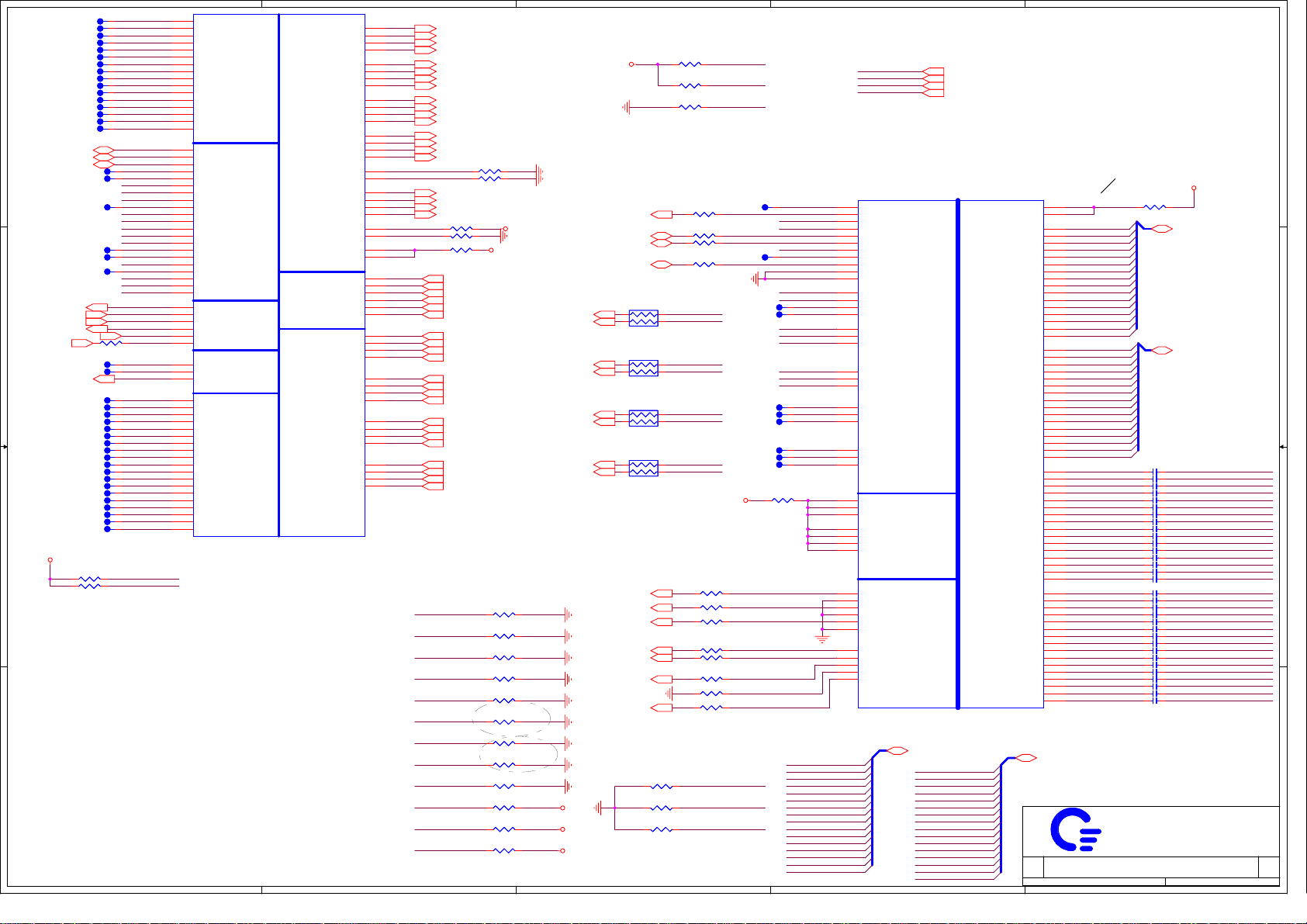

CK-410M

CK-410M

GND

GND_48

2

59

PM_STPCPU#[15]

PM_STPPCI#[15]

CLKUSB_48[15]

C627 27P_4C627 27P_4

CL=20pF

C629 27P_4C629 27P_4

VR_PWRGD_CK410#_C

PM_STPCPU#

PM_STPPCI#

DREFCLK

DREFCLK#

+1.05V

+1.05V

SMBCK

SMBDT

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

VDD_REF

VDD_SRC_CPU

VDD_PCI

VDD_SRC_CPU

VDD_48

MINI_CLKREQ3#

SMBCK[12]

SMBDT[12]

Iref=5mA,

Ioh=4*Iref

DREFCLK[7]

DREFCLK#[7]

BSEL strappings need to be set for 533MHz Moby Dick (Intel?915GM - Calistoga Interposer)

(if Calistoga is designed for 667MHz board).

CPU_BSEL0[2]

CPU_BSEL1[2]

+3V

R421 33_4R421 33_4

R182 475/F_6R182 475/F_6

RP18

RP18

1

3

33_4P2R_S

33_4P2R_S

R412 *56.2/F_4R412 *56.2/F_4

R410 0_4R410 0_4

R411 *1K_4R411 *1K_4

R413 *1K_4R413 *1K_4

R415 0_4R415 0_4

R424 *0_4R424 *0_4

CG_XIN

21

Y4

Y4

14.318MHZ

14.318MHZ

CG_XOUT

R420 *10K_4R420 *10K_4

CLKUSB_48_R

R414 4.7K_4R414 4.7K_4

R181 4.7K_4R181 4.7K_4

IREF

R_DOT96

2

R_DOT96#

4

T47T47

INTERNAL PULL HIGH

CLK_BSEL0

FSA

CLK_BSEL1

FSB

58

57

10

62

63

54

55

12

16

61

56

50

21

28

42

11

32

33

47

14

15

34

Stuff 0 ohm for 533MHz, NC for 667MHz

+1.05V

CPU_BSEL2[2] MCH_BSEL2 [7]

B

R179 *1K_4R179 *1K_4

R188 0_4R188 0_4

R183 *0_4R183 *0_4

CLK_BSEL2

FSC

R185 1K_4R185 1K_4

C

45

46

VDDA

CPUCLKC2/PCIEC8

27Mfix/LCD_SSCGT/PCIE0T

27SS/LCD_SSCGC/PCIE0C

selPCIEX0_LCD#/PCI5

GND

GND_PCI_26GND_SRC

GND_PCI_1

37

29

REF0

GNDA

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2/PCIET8

REQ1#/PCIET7

REQ2#/PCIEC7

PCIET6

PCIEC6

PCIET5

PCIEC5

PCIET4

PCIEC4

SATA_CKT

SATA_CKC

PCIET3

PCIEC3

PCIET2

PCIEC2

PCIET1

PCIEC1

PCICLK2/REQ_SEL

PCIF1/selLCD_27#

PCIF0/ITP_EN

ICS954310BGLF

ICS954310BGLF

MCH_BSEL0 [7]

MCH_BSEL1 [7]

Place these termination to close CK410M.

14M_REF

60

RHCLK_CPU

52

RHCLK_CPU#

51

RHCLK_MCH

49

RHCLK_MCH#

48

44

43

41

40

39

38

RSRC_MCH

36

RSRC_MCH#

35

30

31

RSRC_SATA

26

RSRC_SATA#

27

PECLK_VGA_R

24

PECLK_VGA_R#

25

R_CLK_PCIE_MINI

22

R_CLK_PCIE_MINI#

23

RSRC_ICH CLK_PCIE_ICH

19

RSRC_ICH#

20

R_DREFSSCLK

17

R_DREFSSCLK#

18

R_PCLK_SIO

5

R_PCLK_LAN

4

PCI4

R_PCLK_PCM

3

PCI3

PCLK_MINI_LPC

64

R_PCLK_ICH

9

R_PCLK_591

8

C162

C162

.1U/10V_4

.1U/10V_4

3

1

3

1

1

3

1

3

3

1

1

3

3

1

1

3

R177 *10K_4R177 *10K_4

R417 10K_4R417 10K_4

R416 10K_4R416 10K_4

+5V +1.8V

.1U/10V_4

.1U/10V_4

REV_02/11-21 Modify

FSC FSB FSA CPU SRC PCI

1 0 1 100 100 33

0 0 1 133 100 33

0 1 1 166 100 33

0 1 0 200 100 33

0 0 0 266 100 33

1 0 0 333 100 33

1 1 0 400 100 33

1 1 1 200 100 33

4

2

4

2

2

4

2

4

4

2

2

4

4

2

2

4

R159 10K_4R159 10K_4

R160 33_4R160 33_4

R161 33_4R161 33_4

R176 33_4R176 33_4

R423 33_4R423 33_4

R422 33_4R422 33_4

C630

C630

D

RP57

RP57

33_4P2R_S

33_4P2R_S

RP58

RP58

33_4P2R_S

33_4P2R_S

RP19

RP19

33_4P2R_S

33_4P2R_S

RP55

RP55

33_4P2R_S

33_4P2R_S

RP16

RP16

EV@33_4P2R_S

EV@33_4P2R_S

RP56

RP56

33_4P2R_S

33_4P2R_S

RP17

RP17

33_4P2R_S

33_4P2R_S

RP54

RP54

33_4P2R_S

33_4P2R_S

+3V

C601

C601

*10P/50V_4

*10P/50V_4

C600

C600

*10P/50V_4

*10P/50V_4

REV_3A/02-06 Modify

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_MINI

CLK_PCIE_MINI#

CLK_PCIE_ICH#

DREFSSCLK

DREFSSCLK#

C209

C209

*10P/50V_4

*10P/50V_4

Default

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet of

R180 22_4R180 22_4

C166

C166

*10P/50V_4

*10P/50V_4

C165

C165

*10P/50V_4

*10P/50V_4

CLK_CPU_BCLK#

CLK_CPU_BCLK

CLK_MCH_BCLK#

CLK_MCH_BCLK

CLK_PCIE_MINI#

CLK_PCIE_MINI

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_VGA

CLK_PCIE_VGA#

DREFSSCLK#

DREFSSCLK

DREFCLK

DREFCLK#

CLK_PCIE_SATA#

CLK_PCIE_SATA

Quanta Computer Inc.

Quanta Computer Inc.

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

CLK_CPU_BCLK [2]

CLK_CPU_BCLK# [2]

CLK_MCH_BCLK [5]

CLK_MCH_BCLK# [5]

CLK_PCIE_3GPLL [7]

CLK_PCIE_3GPLL# [7]

CLK_PCIE_SATA [13]

CLK_PCIE_SATA# [13]

CLK_PCIE_VGA [17]

CLK_PCIE_VGA# [17]

CLK_PCIE_MINI [24]

CLK_PCIE_MINI# [24]

CLK_PCIE_ICH [14]

CLK_PCIE_ICH# [14]

DREFSSCLK [7]

DREFSSCLK# [7]

PCLK_LAN [25]

PCLK_PCM [26]

PCLK_MINI [24]

PCLK_ICH [14]

PCLK_591 [30]

RP59 49.9_4P2R_SRP59 49.9_4P2R_S

1

3

RP60 49.9_4P2R_SRP60 49.9_4P2R_S

1

3

RP53 49.9_4P2R_SRP53 49.9_4P2R_S

3

1

RP20 49.9_4P2R_SRP20 49.9_4P2R_S

1

3

RP13 49.9_4P2R_SRP13 49.9_4P2R_S

3

1

RP15 EV@49.9_4P2R_SRP15 EV@49.9_4P2R_S

3

1

RP51 IV@49.9_4P2R_SRP51 IV@49.9_4P2R_S

3

1

RP14 49.9_4P2R_SRP14 49.9_4P2R_S

3

1

RP52 49.9_4P2R_SRP52 49.9_4P2R_S

3

1

PROJECT : ZB2

PROJECT : ZB2

E

5

www.kythuatvitinh.com

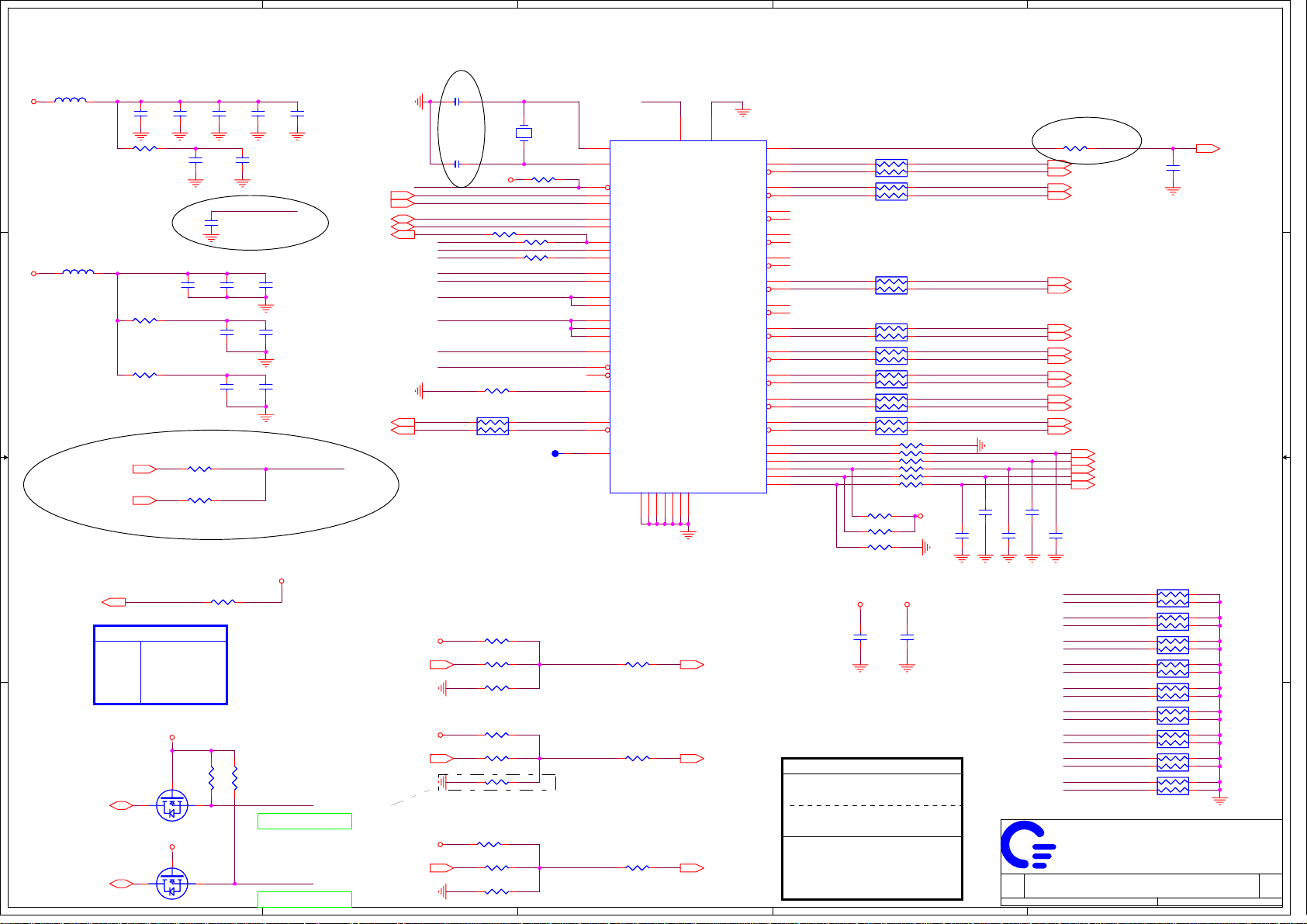

H_XRCOMP

R128

R128

24.9/F_4

24.9/F_4

D D

C C

B B

+1.05V

+1.05V

+1.05V

+1.05V

R140

R140

54.9/F_4

54.9/F_4

R122

R122

221/F_4

221/F_4

R123

R123

100/F_4

100/F_4

R165

R165

54.9/F_4

54.9/F_4

R167

R167

221/F_4

221/F_4

R170

R170

100/F_4

100/F_4

R172

R172

24.9/F_4

24.9/F_4

H_XSCOMP

H_XSWING

H_YSCOMP

H_YSWING

H_YRCOMP

15 mils/10mils

C143

C143

.1U/10V_4

.1U/10V_4

C196

C196

.1U/10V_4

.1U/10V_4

15 mils/10mils

A A

5

CLK_MCH_BCLK[4]

CLK_MCH_BCLK#[4]

H_D#[63:0][2]

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

Short Stub < 100mils

extract from same point

4

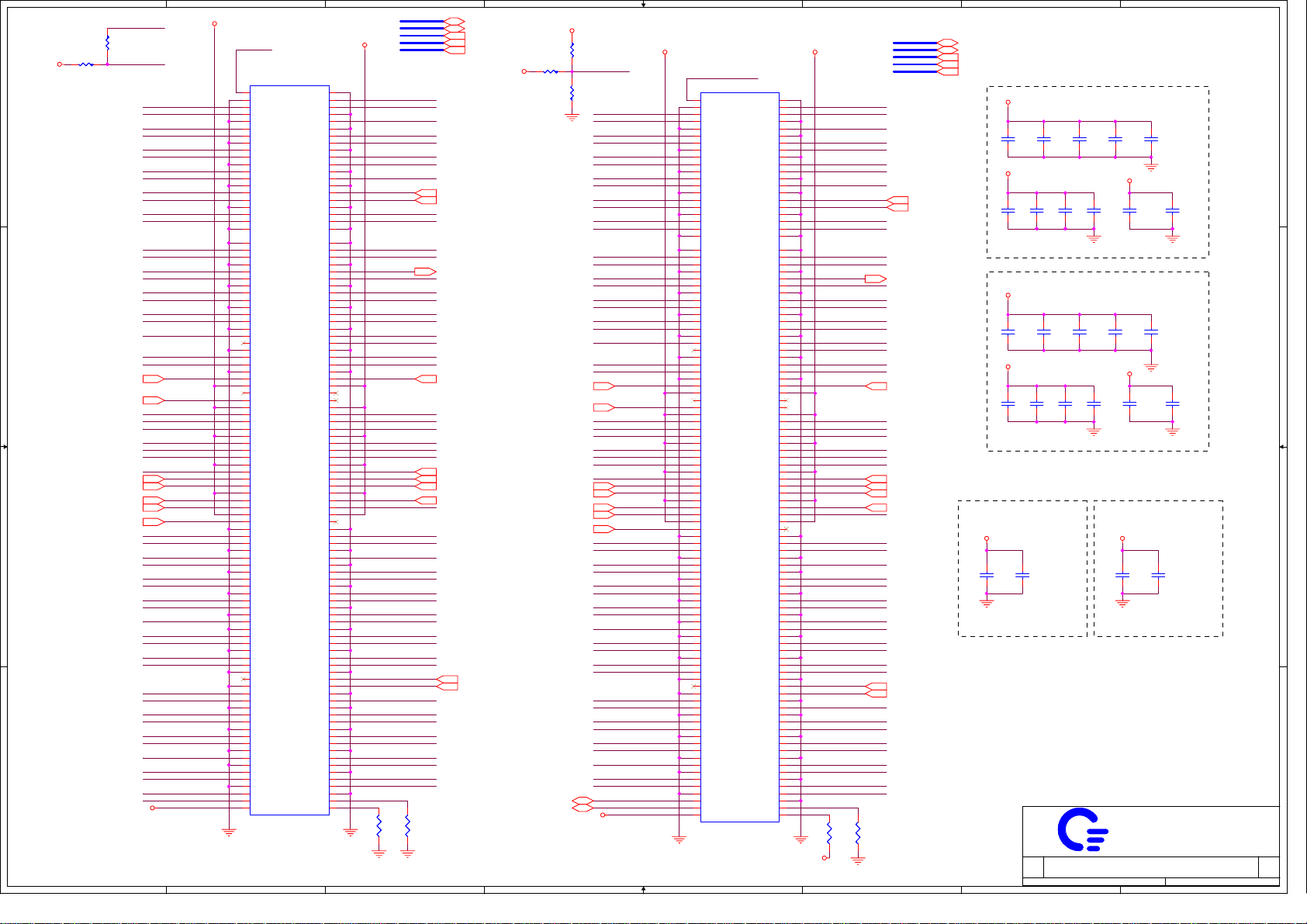

U28A

K11

T10

W11

U11

T11

AB7

AA9

Y10

AB8

AA4

AA7

AA2

AA6

AA10

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

AG2

AG1

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

G4

T3

U7

U9

W9

T1

T8

T4

W7

U5

T9

W6

T5

W4

W3

Y3

Y7

W5

W2

Y8

E1

E2

E4

Y1

U1

W1

U28A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

Calistoga

Calistoga

HOST

HOST

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

4

3

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

3

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

R402 0_4R402 0_4

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

2

H_A#[31:3] [2]

H_ADS# [2]

H_ADSTB0# [2]

H_ADSTB1# [2]

H_BNR# [2]

H_BPRI# [2]

H_BREQ#0 [2]

H_CPURST# [2]

H_DBSY# [2]

H_DEFER# [2]

H_DPWR# [2]

H_DRDY# [2]

H_DINV#[3:0] [2]

H_DSTBN#[3:0] [2]

H_DSTBP#[3:0] [2]

H_HIT# [2]

H_HITM# [2]

H_LOCK# [2]

H_REQ#[4:0] [2]

H_RS#[2:0] [2]

H_CPUSLP# [2,13]

H_TRDY# [2]

2

1

+1.05V

C164

C164

.1U/10V_4

.1U/10V_4

C167

C167

.1U/10V_4

.1U/10V_4

+1.05V

+1.05V [2,3,4,8,9,13,16,33,34]

R155

R155

100/F_4

100/F_4

R156

R156

200/F_4

200/F_4

H_VREF :10 mils/20 mils space

H_VREF

H_VREF

P/NCOMPONENTS

945GM

945PM

PROJECT : ZB2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GMCH HOST(1 OF 6 )

GMCH HOST(1 OF 6 )

GMCH HOST(1 OF 6 )

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT : ZB2

Quanta Computer Inc.

Quanta Computer Inc.

AJ009450T04

AJ009450T12

537Monday, April 10, 2006

537Monday, April 10, 2006

537Monday, April 10, 2006

1

CLG

of

of

of

1A

1A

1A

5

www.kythuatvitinh.com

4

3

2

1

CLG

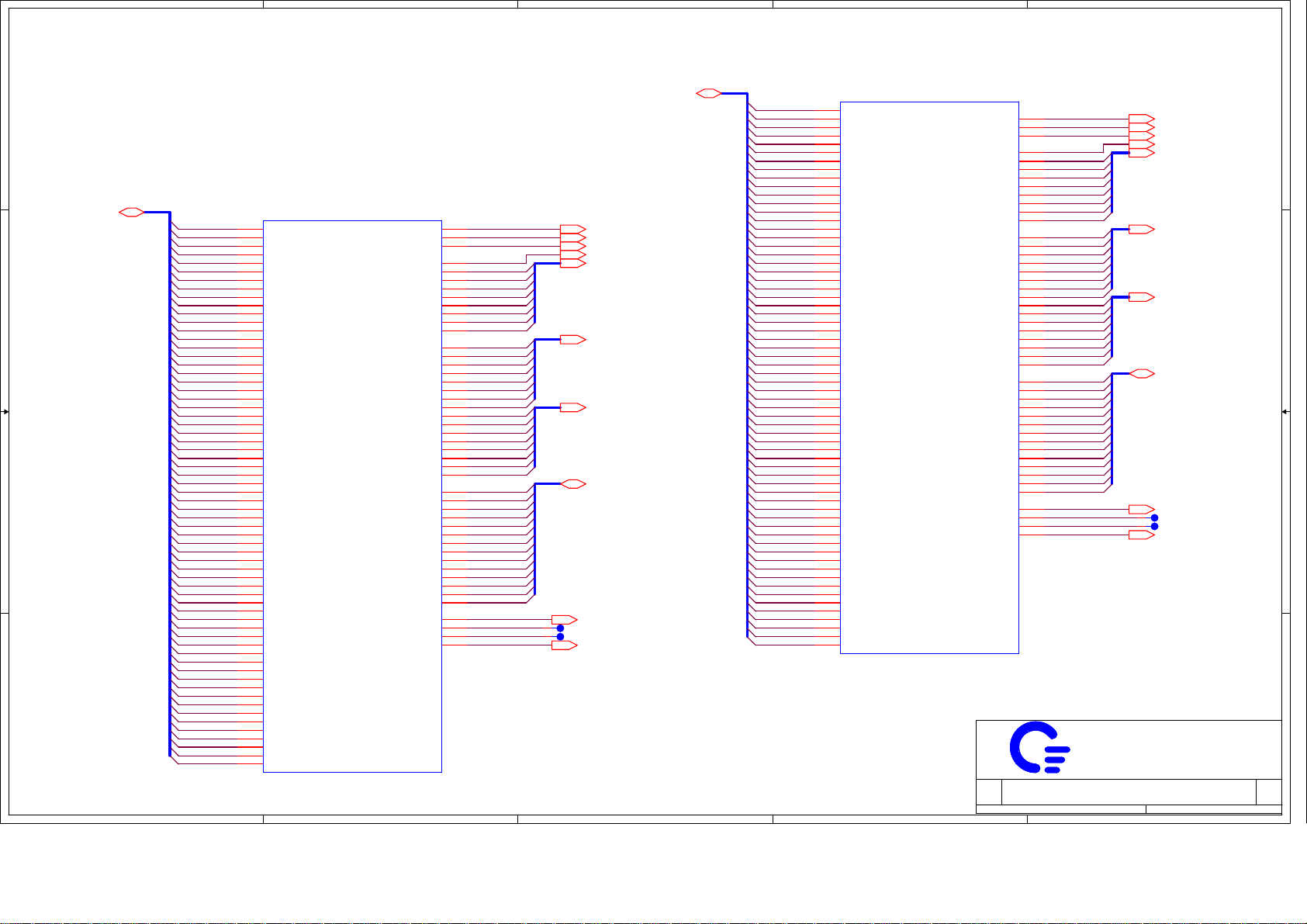

R_B_MD[0..63][12]

D D

R_A_MD[0..63][12]

C C

B B

A A

5

R_A_MD0

R_A_MD1

R_A_MD2

R_A_MD3

R_A_MD4

R_A_MD5

R_A_MD6

R_A_MD7

R_A_MD8

R_A_MD9

R_A_MD10

R_A_MD11

R_A_MD12

R_A_MD13

R_A_MD14

R_A_MD15

R_A_MD16

R_A_MD17

R_A_MD18

R_A_MD19

R_A_MD20

R_A_MD21

R_A_MD22

R_A_MD23

R_A_MD24

R_A_MD25

R_A_MD26

R_A_MD27

R_A_MD28

R_A_MD29

R_A_MD30

R_A_MD31

R_A_MD32

R_A_MD33

R_A_MD34

R_A_MD35

R_A_MD36

R_A_MD37

R_A_MD38

R_A_MD39

R_A_MD40

R_A_MD41

R_A_MD42

R_A_MD43

R_A_MD44

R_A_MD45

R_A_MD46

R_A_MD47

R_A_MD48

R_A_MD49

R_A_MD50

R_A_MD51

R_A_MD52

R_A_MD53

R_A_MD54

R_A_MD55

R_A_MD56

R_A_MD57

R_A_MD58

R_A_MD59

R_A_MD60

R_A_MD61

R_A_MD62

R_A_MD63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U28D

U28D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

Calistoga

Calistoga

R_A_BS0#

AU12

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

4

AV14

BA20

AY13

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

R_A_BS1#

R_A_BS2#

R_A_SCASA#

R_A_DM0

R_A_DM1

R_A_DM2

R_A_DM3

R_A_DM4

R_A_DM5

R_A_DM6

R_A_DM7

R_A_DQS0

R_A_DQS1

R_A_DQS2

R_A_DQS3

R_A_DQS4

R_A_DQS5

R_A_DQS6

R_A_DQS7

R_A_DQS#0

R_A_DQS#1

R_A_DQS#2

R_A_DQS#3

R_A_DQS#4

R_A_DQS#5

R_A_DQS#6

R_A_DQS#7

R_A_MA0

R_A_MA1

R_A_MA2

R_A_MA3

R_A_MA4

R_A_MA5

R_A_MA6

R_A_MA7

R_A_MA8

R_A_MA9

R_A_MA10

R_A_MA11

R_A_MA12

R_A_MA13

R_A_SRASA#

SA_RCVENIN#

SA_RCVENOUT#

R_A_BMWEA#

R_A_BS0# [11,12]

R_A_BS1# [11,12]

R_A_BS2# [11,12]

R_A_SCASA# [11,12]

R_A_DM[0..7] [12]

R_A_DQS[0..7] [12]

R_A_DQS#[0..7] [12]

R_A_MA[0..13] [11,12]

R_A_SRASA# [11,12]

T46T46

T45T45

R_A_BMWEA# [11,12]

3

R_B_MD0

R_B_MD1 R_B_BS0#

R_B_MD2

R_B_MD3

R_B_MD4

R_B_MD5

R_B_MD6

R_B_MD7

R_B_MD8

R_B_MD9

R_B_MD10

R_B_MD11

R_B_MD12

R_B_MD13

R_B_MD14

R_B_MD15

R_B_MD16

R_B_MD17

R_B_MD18

R_B_MD19

R_B_MD20

R_B_MD21

R_B_MD22

R_B_MD23

R_B_MD24

R_B_MD25

R_B_MD26

R_B_MD27

R_B_MD28

R_B_MD29

R_B_MD30

R_B_MD31

R_B_MD32

R_B_MD33

R_B_MD34

R_B_MD35

R_B_MD36

R_B_MD37

R_B_MD38

R_B_MD39

R_B_MD40

R_B_MD41

R_B_MD42

R_B_MD43

R_B_MD44

R_B_MD45

R_B_MD46

R_B_MD47

R_B_MD48

R_B_MD49

R_B_MD50

R_B_MD51

R_B_MD52

R_B_MD53

R_B_MD54

R_B_MD55

R_B_MD56

R_B_MD57

R_B_MD58

R_B_MD59

R_B_MD60

R_B_MD61

R_B_MD62

R_B_MD63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

U28E

U28E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

Calistoga

Calistoga

AT24

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

2

SB_WE#

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

R_B_BS1#

AV23

R_B_BS2#

AY28

R_B_SCASA#

AR24

R_B_DM0

AK36

R_B_DM1

AR38

R_B_DM2

AT36

R_B_DM3

BA31

R_B_DM4

AL17

R_B_DM5

AH8

R_B_DM6

BA5

R_B_DM7

AN4

R_B_DQS0

AM39

R_B_DQS1

AT39

R_B_DQS2

AU35

R_B_DQS3

AR29

R_B_DQS4

AR16

R_B_DQS5

AR10

R_B_DQS6

AR7

R_B_DQS7

AN5

R_B_DQS#0

AM40

R_B_DQS#1

AU39

R_B_DQS#2

AT35

R_B_DQS#3

AP29

R_B_DQS#4

AP16

R_B_DQS#5

AT10

R_B_DQS#6

AT7

R_B_DQS#7

AP5

R_B_MA0

AY23

R_B_MA1

AW24

R_B_MA2

AY24

R_B_MA3

AR28

R_B_MA4

AT27

R_B_MA5

AT28

R_B_MA6

AU27

R_B_MA7

AV28

R_B_MA8

AV27

R_B_MA9

AW27

R_B_MA10

AV24

R_B_MA11

BA27

R_B_MA12

AY27

R_B_MA13

AR23

R_B_SRASA#

AU23

SB_RCVENIN#

AK16

SB_RCVENOUT#

AK18

R_B_BMWEA#

AR27

PROJECT : ZB2

PROJECT : ZB2

Quanta Computer Inc.

Quanta Computer Inc.

GMCH DDR(2 OF 6 )

GMCH DDR(2 OF 6 )

GMCH DDR(2 OF 6 )

R_B_BS0# [11,12]

R_B_BS1# [11,12]

R_B_BS2# [11,12]

R_B_SCASA# [11,12]

R_B_DM[0..7] [12]

R_B_DQS[0..7] [12]

R_B_DQS#[0..7] [12]

R_B_MA[0..13] [11,12]

R_B_SRASA# [11,12]

T48T48

T49T49

R_B_BMWEA# [11,12]

of

of

of

637Monday, April 10, 2006

637Monday, April 10, 2006

637Monday, April 10, 2006

1

1A

1A

1A

5

www.kythuatvitinh.com

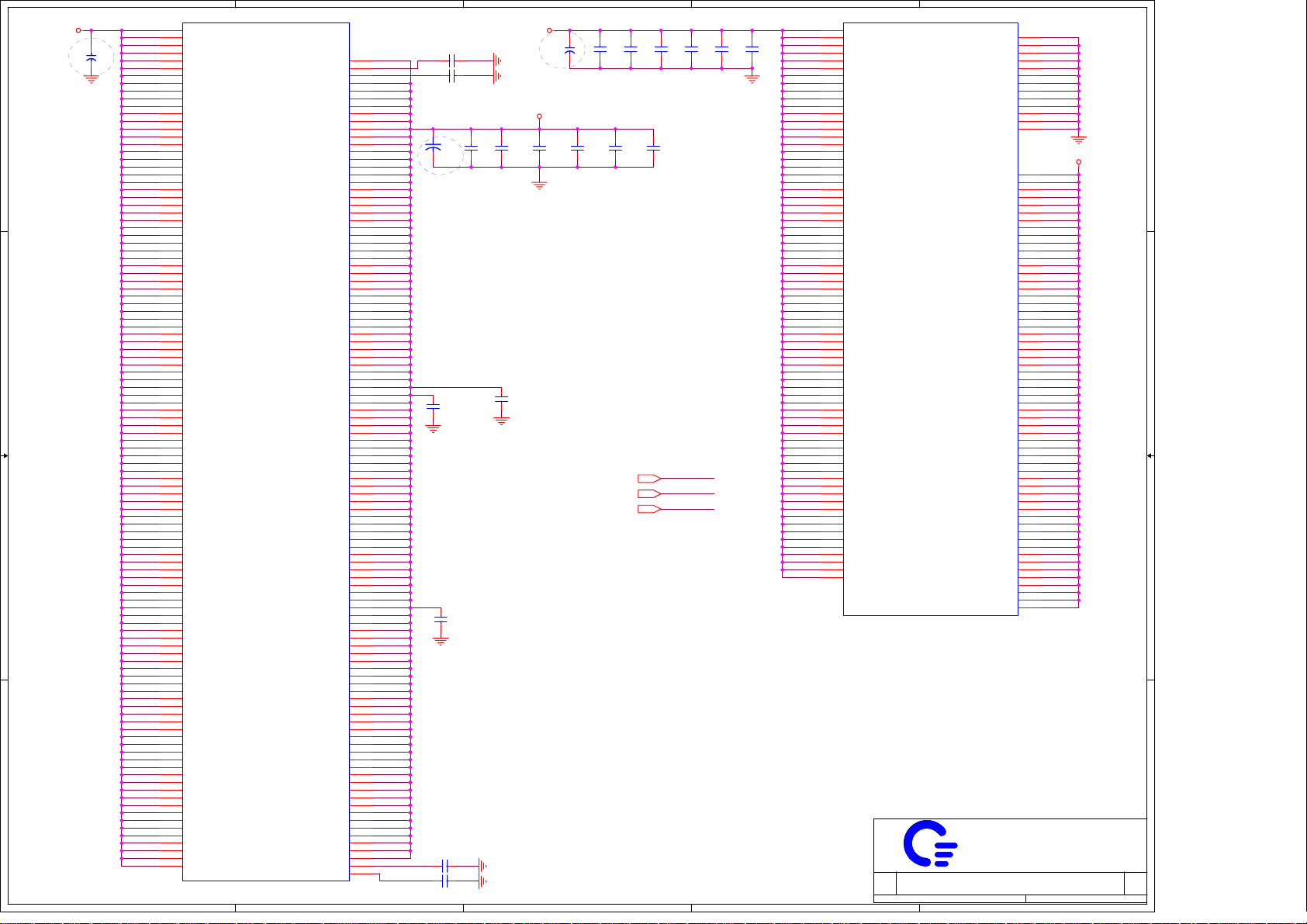

CLK_MCH_OE#

T29T29

MCH_RSVD_1

T42T42

MCH_RSVD_2

T41T41

MCH_RSVD_3

T124T124

MCH_RSVD_4

T123T123

MCH_RSVD_5

T44T44

MCH_RSVD_6

T43T43

MCH_RSVD_7

T30T30

MCH_RSVD_8

T35T35

TV_DCONSEL0

T36T36

TV_DCONSEL1

T33T33

MCH_RSVD_11

T116T116

MCH_RSVD_12

T121T121

MCH_RSVD_13

T120T120

MCH_RSVD_14

D D

CFG[17:3] Internal Pull-up

CFG[2:0]=011

FSB=667M

CFG[2:0]=001

FSB=533M

CFG[18,19] Internal

Pull-down

C C

PLT_RST-R#[14]

B B

T17T17

T127T127

MCH_BSEL0[4]

MCH_BSEL1[4]

MCH_BSEL2[4]

PM_BMBUSY#[15]

PM_EXTTS#0[12]

PM_EXTTS#1[12]

PM_THRMTRIP#[2,13]

IMVP_PWRGD[15,32]

MCH_ICH_SYNC[14]

T122T122

T128T128

T112T112

T135T135

T132T132

T134T134

T55T55

T56T56

T57T57

T115T115

T113T113

T50T50

T54T54

T133T133

T53T53

T126T126

T117T117

T114T114

T125T125

+3V

R130 10K/F_4R130 10K/F_4

R151 *10K/F_4R151 *10K/F_4

MCH_RSVD_15

T10T10

T24T24

T13T13

T11T11

T37T37

T9T9

R427 100/F_4R427 100/F_4

T32T32

T12T12

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

PM_EXTTS#0

PM_EXTTS#1

RST IN# MCH

TP_MCH_NC0

TP_MCH_NC1

TP_MCH_NC2

TP_MCH_NC3

TP_MCH_NC4

TP_MCH_NC5

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC8

TP_MCH_NC9

TP_MCH_NC10

TP_MCH_NC11

TP_MCH_NC12

TP_MCH_NC13

TP_MCH_NC14

TP_MCH_NC15

TP_MCH_NC16

TP_MCH_NC17

TP_MCH_NC18

PM_EXTTS#0

PM_EXTTS#1

AG11

AF11

AH33

AH34

BA41

BA40

BA39

AY41

AW41

AW1

U28B

U28B

H32

T32

R32

F3

F7

H7

J19

K30

J29

A41

A35

A34

D28

D27

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

J25

K27

J26

G28

F25

H26

G6

H28

H27

K28

D1

C41

C1

BA3

BA2

BA1

B41

B2

AY1

A40

A4

A39

A3

RSVD_0

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

LT_RESET#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

CFGRSVD

CFGRSVD

PM

PM

MISC

MISC

NC

NC

Calistoga

Calistoga

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

DDR MUXINGCLKDMI

DDR MUXINGCLKDMI

SM_VREF_0

SM_VREF_1

G_CLKIN#

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

G_CLKIN

CFG[17:3] Internal Pull-up

1.MCH_CFG_5 DMI Select : Low = DMI X2, High=DMIX4 (Default "1")

2.MCH_CFG_6 DDR : Low =Moby Dick, High= Calistoga (Default)

3.MCH_CFG_7 CPU Strap : Low=RSVD, High=Mobile CPU (Default "1")

4.MCH_CFG_9 PCI Exp Graphics Lane : Low =Reserved, High=Mobility (Default "1")

5.MCH_CFG_10 Host PLL VCC Select: Low=Reserved, High=Mobility

6.MCH_CFG_11: PSB 4x CLK ENABLE Low=Reserved, High=Calistoga

7.MCH_CFG_16 FSB Dynmic ODT: Low=Dynamic ODT Disabled,

High=Dynamic ODT Enabled. (Default "1")

A A

8.MCH_CFG_18 VCC Select : LOW=1.05V, High=1.5V (Default "0")

9.MCH_CFG_19 DMI Lane Reversal : 0=Normal operation

1=Reverse Lane (Default "0")

10.MCH_CFG_20 PCIE Backward interpoerability mode: Low= only

SDVO or PCIE x1 is operational (defaults) ,High=SDVO and

PCIE x1 are operation simultaneously via the PEG port.

5

4

AY35

AR1

AW7

AW40

AW35

AT1

AY7

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

M_OCDCOMP_0

AL20

M_OCDCOMP_1

AF10

BA13

BA12

AY20

AU21

M_RCOMP#

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

R197 80.6/F_4R197 80.6/F_4

M_RCOMP

R193 80.6/F_4R193 80.6/F_4

SMDDR_VREF_MCH

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

< 0.1" . 15mils/15mils space

use 1% R

GMCH Strap pin

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_16

MCH_CFG_18

CFG[18,19]

Internal

Pull-down

MCH_CFG_19

MCH_CFG_20

4

CLK_SDRAM0 [12]

CLK_SDRAM1 [12]

CLK_SDRAM3 [12]

CLK_SDRAM4 [12]

CLK_SDRAM0# [12]

CLK_SDRAM1# [12]

CLK_SDRAM3# [12]

CLK_SDRAM4# [12]

CKE0 [11,12]

CKE1 [11,12]

CKE2 [11,12]

CKE3 [11,12]

SM_CS0# [11,12]

SM_CS1# [11,12]

SM_CS2# [11,12]

SM_CS3# [11,12]

R184 *40.2/F_4R184 *40.2/F_4

R174 *40.2/F_4R174 *40.2/F_4

M_ODT0 [11,12]

M_ODT1 [11,12]

M_ODT2 [11,12]

M_ODT3 [11,12]

R195 0_6R195 0_6

CLK_PCIE_3GPLL# [4]

CLK_PCIE_3GPLL [4]

DREFCLK# [4]

DREFCLK [4]

DREFSSCLK# [4]

DREFSSCLK [4]

DMI_TXN0 [14]

DMI_TXN1 [14]

DMI_TXN2 [14]

DMI_TXN3 [14]

DMI_TXP0 [14]

DMI_TXP1 [14]

DMI_TXP2 [14]

DMI_TXP3 [14]

DMI_RXN0 [14]

DMI_RXN1 [14]

DMI_RXN2 [14]

DMI_RXN3 [14]

DMI_RXP0 [14]

DMI_RXP1 [14]

DMI_RXP2 [14]

DMI_RXP3 [14]

R121 *2.2K_4R121 *2.2K_4

R127 *2.2K_4R127 *2.2K_4

R126 *2.2K_4R126 *2.2K_4

R141 *2.2K_4R141 *2.2K_4

R138 *2.2K_4R138 *2.2K_4

R120 *2.2K_4R120 *2.2K_4

R145 *2.2K_4R145 *2.2K_4

R154 *2.2K_4R154 *2.2K_4

R142 *2.2K_4R142 *2.2K_4

R146 *1K/F_4R146 *1K/F_4

R149 *1K/F_4R149 *1K/F_4

R150 *1K/F_4R150 *1K/F_4

Layout as short as passable

NC from WW45

15mils/15mils

15mils/10mils

+1.8VSUS

+0.9VSUS

TXLCLKOUT-[19,22]

TXLCLKOUT+[19,22]

TXLOUT0-[19,22]

TXLOUT0+[19,22]

TXLOUT1-[19,22]

TXLOUT1+[19,22]

TXLOUT2-[19,22]

TXLOUT2+[19,22]

+3V

+3V

+3V

LCD_POWER_ON[19,22]

UMA@0_4P2R_S

UMA@0_4P2R_S

UMA@0_4P2R_S

UMA@0_4P2R_S

UMA@0_4P2R_S

UMA@0_4P2R_S

UMA@0_4P2R_S

UMA@0_4P2R_S

3

+3V

BLON[19,22]

EDIDCLK[17,22]

EDIDDATA[17,22]

RP3

RP3

4

2

RP5

RP5

4

2

RP6

RP6

4

2

RP9

RP9

4

2

VGA_BLU[17,22]

VGA_GRN[17,22]

VGA_RED[17,22]

DDCCLK[17,22]

DDCDAT[17,22]

HSYNC[17,20,22]

VSYNC[17,20,22]

R398 UMA@150_4R398 UMA@150_4

R401 UMA@150_4R401 UMA@150_4

R400 UMA@150_4R400 UMA@150_4

3

R147 10K/F_4R147 10K/F_4

R148 10K/F_4R148 10K/F_4

R139 1.5K/F_4R139 1.5K/F_4

R143 UMA@0_4R143 UMA@0_4

R48 UMA@0_4R48 UMA@0_4

R46 UMA@0_4R46 UMA@0_4

R68 UMA@0_4R68 UMA@0_4

TXLCLKOUT-_NB

3

TXLCLKOUT+_NB

1

TXLOUT0-_NB

3

TXLOUT0+_NB

1

TXLOUT1-_NB

3

TXLOUT1+_NB

1

TXLOUT2-_NB

3

TXLOUT2+_NB

1

R113 UMA@0_4R113 UMA@0_4

R110 UMA@0_4R110 UMA@0_4

R106 UMA@0_4R106 UMA@0_4

R90 UMA@0_4R90 UMA@0_4

R88 UMA@0_4R88 UMA@0_4

R100 UMA@0_4R100 UMA@0_4

R152 255/F_6R152 255/F_6

R97 UMA@0_4R97 UMA@0_4

L_CLKCTLA

L_CLKCTLB

L_IBG

T28T28

T26T26

+1.5V

R399 0_4R399 0_4

VGA_BLU_NB

VGA_GRN_NB

VGA_RED_NB

2

Note : If Use Internal VGA Please NC "UMA@xxx" Parts

BLON_NB

EDIDCLK_NB

EDIDDATA_NB

DISP_ON

TXLCLKOUT-_NB

TXLCLKOUT+_NB

T20T20

T15T15

T34T34

T119T119

T23T23

T27T27

T118T118

T31T31

VGA_BLU_NB

VGA_GRN_NB

VGA_RED_NB

DDCCLK_NB

DDCDAT_NB

HSYNC_NB

CRTIREF

VSYNC_NB

L_CLKCTLA

L_CLKCTLB

L_IBG

L_VBG

L_VREFH

L_VREFL

TXUCLKOUTTXUCLKOUT+

TXLOUT0-_NB

TXLOUT1-_NB

TXLOUT2-_NB

TXLOUT0+_NB

TXLOUT1+_NB

TXLOUT2+_NB

TXUOUT0TXUOUT1TXUOUT2-

TXUOUT0+

TXUOUT1+

TXUOUT2+

GMCHEXP_TXP0

GMCHEXP_TXP1

GMCHEXP_TXP2

GMCHEXP_TXP3

GMCHEXP_TXP4

GMCHEXP_TXP5

GMCHEXP_TXP6

GMCHEXP_TXP7

GMCHEXP_TXP8

GMCHEXP_TXP9

GMCHEXP_TXP10

GMCHEXP_TXP11

GMCHEXP_TXP12

GMCHEXP_TXP13

GMCHEXP_TXP14

GMCHEXP_TXP15

U28C

U28C

D32

J30

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

J20

B16

B18

B19

E23

D23

C22

B22

A21

B21

C26

C25

G23

J22

H23

Calistoga

Calistoga

+V1.5_PCIE

+3V

+0.9VSUS

+1.8VSUS

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CLKCTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

2

+V1.5_PCIE [9]

+3V [2,4,9,12,13,14,15,16,17,19,20,22,23,24,25,26,27,28,29,30,31,32,33,34,36]

+0.9VSUS [12,34]

+1.8VSUS [8,12,33,34]

20mils/20mils space

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

GMCHEXP_TXN[0..15] [17]

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GMCH DMI/VEDIO(3 OF 6 )

GMCH DMI/VEDIO(3 OF 6 )

GMCH DMI/VEDIO(3 OF 6 )

Date: Sheet

Date: Sheet

Date: Sheet

LVDS

LVDS

TV

TV

VGA

VGA

GMCHEXP_TXP[0..15] [17]

GMCHEXP_TXN0

GMCHEXP_TXN1

GMCHEXP_TXN2

GMCHEXP_TXN3

GMCHEXP_TXN4

GMCHEXP_TXN5

GMCHEXP_TXN6

GMCHEXP_TXN7

GMCHEXP_TXN8

GMCHEXP_TXN9

GMCHEXP_TXN10

GMCHEXP_TXN11

GMCHEXP_TXN12

GMCHEXP_TXN13

GMCHEXP_TXN14

GMCHEXP_TXN15

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

EXP_A_COMPX

GMCHEXP_RXN0

GMCHEXP_RXN1

GMCHEXP_RXN2

GMCHEXP_RXN3

GMCHEXP_RXN4

GMCHEXP_RXN5

GMCHEXP_RXN6

GMCHEXP_RXN7

GMCHEXP_RXN8

GMCHEXP_RXN9

GMCHEXP_RXN10

GMCHEXP_RXN11

GMCHEXP_RXN12

GMCHEXP_RXN13

GMCHEXP_RXN14

GMCHEXP_RXN15

GMCHEXP_RXP0

GMCHEXP_RXP1

GMCHEXP_RXP2

GMCHEXP_RXP3

GMCHEXP_RXP4

GMCHEXP_RXP5

GMCHEXP_RXP6

GMCHEXP_RXP7

GMCHEXP_RXP8

GMCHEXP_RXP9

GMCHEXP_RXP10

GMCHEXP_RXP11

GMCHEXP_RXP12

GMCHEXP_RXP13

GMCHEXP_RXP14

GMCHEXP_RXP15

CGMCHEXP_TXN0

CGMCHEXP_TXN1

CGMCHEXP_TXN2

CGMCHEXP_TXN3

CGMCHEXP_TXN4

CGMCHEXP_TXN5

CGMCHEXP_TXN6

CGMCHEXP_TXN7

CGMCHEXP_TXN8

CGMCHEXP_TXN9

CGMCHEXP_TXN10

CGMCHEXP_TXN11

CGMCHEXP_TXN12

CGMCHEXP_TXN13

CGMCHEXP_TXN14

CGMCHEXP_TXN15

CGMCHEXP_TXP0

CGMCHEXP_TXP1

CGMCHEXP_TXP2

CGMCHEXP_TXP3

CGMCHEXP_TXP4

CGMCHEXP_TXP5

CGMCHEXP_TXP6

CGMCHEXP_TXP7

CGMCHEXP_TXP8

CGMCHEXP_TXP9

CGMCHEXP_TXP10

CGMCHEXP_TXP11

CGMCHEXP_TXP12

CGMCHEXP_TXP13

CGMCHEXP_TXP14

CGMCHEXP_TXP15

1

CLG

+V1.5_PCIE

R137 24.9/F_4R137 24.9/F_4

GMCHEXP_RXN[0..15] [17]

GMCHEXP_RXP[0..15] [17]

UMA@.1U_4C155 UMA@.1U_4C155

UMA@.1U_4C587 UMA@.1U_4C587

UMA@.1U_4C159 UMA@.1U_4C159

UMA@.1U_4C593 UMA@.1U_4C593

UMA@.1U_4C163 UMA@.1U_4C163

UMA@.1U_4C597 UMA@.1U_4C597

UMA@.1U_4C170 UMA@.1U_4C170

UMA@.1U_4C599 UMA@.1U_4C599

UMA@.1U_4C184 UMA@.1U_4C184

UMA@.1U_4C603 UMA@.1U_4C603

UMA@.1U_4C190 UMA@.1U_4C190

UMA@.1U_4C606 UMA@.1U_4C606

UMA@.1U_4C198 UMA@.1U_4C198

UMA@.1U_4C614 UMA@.1U_4C614

UMA@.1U_4C210 UMA@.1U_4C210

UMA@.1U_4C619 UMA@.1U_4C619

UMA@.1U_4C150 UMA@.1U_4C150

UMA@.1U_4C586 UMA@.1U_4C586

UMA@.1U_4C156 UMA@.1U_4C156

UMA@.1U_4C588 UMA@.1U_4C588

UMA@.1U_4C161 UMA@.1U_4C161

UMA@.1U_4C596 UMA@.1U_4C596

UMA@.1U_4C168 UMA@.1U_4C168

UMA@.1U_4C598 UMA@.1U_4C598

UMA@.1U_4C178 UMA@.1U_4C178

UMA@.1U_4C602 UMA@.1U_4C602

UMA@.1U_4C188 UMA@.1U_4C188

UMA@.1U_4C604 UMA@.1U_4C604

UMA@.1U_4C195 UMA@.1U_4C195

UMA@.1U_4C607 UMA@.1U_4C607

UMA@.1U_4C201 UMA@.1U_4C201

UMA@.1U_4C617 UMA@.1U_4C617

0.1u Capacitors place at

first 1/3 of trace

PROJECT : ZB2

PROJECT : ZB2

Quanta Computer Inc.

Quanta Computer Inc.

1

GMCHEXP_TXN0

GMCHEXP_TXN1

GMCHEXP_TXN2

GMCHEXP_TXN3

GMCHEXP_TXN4

GMCHEXP_TXN5

GMCHEXP_TXN6

GMCHEXP_TXN7

GMCHEXP_TXN8

GMCHEXP_TXN9

GMCHEXP_TXN10

GMCHEXP_TXN11

GMCHEXP_TXN12

GMCHEXP_TXN13

GMCHEXP_TXN14

GMCHEXP_TXN15

GMCHEXP_TXP0

GMCHEXP_TXP1

GMCHEXP_TXP2

GMCHEXP_TXP3

GMCHEXP_TXP4

GMCHEXP_TXP5

GMCHEXP_TXP6

GMCHEXP_TXP7

GMCHEXP_TXP8

GMCHEXP_TXP9

GMCHEXP_TXP10

GMCHEXP_TXP11

GMCHEXP_TXP12

GMCHEXP_TXP13

GMCHEXP_TXP14

GMCHEXP_TXP15

737Monday, April 10, 2006

737Monday, April 10, 2006

737Monday, April 10, 2006

of

of

of

1A

1A

1A

5

www.kythuatvitinh.com

U28G

U28G

+1.05V +1.05V

+

+

C151

220U/2.5V_3528

220U/2.5V_3528

6/22 330U 7343 chagne to 220U 3528

package

D D

C C

B B

A A

C151

AA33

VCC_0

W33

VCC_1

P33

VCC_2

N33

VCC_3

L33

VCC_4

J33

VCC_5

AA32

VCC_6

Y32

VCC_7

W32

VCC_8

V32

VCC_9

P32

VCC_10

N32

VCC_11

M32

VCC_12

L32

VCC_13

J32

VCC_14

AA31

VCC_15

W31

VCC_16

V31

VCC_17

T31

VCC_18

R31

VCC_19

P31

VCC_20

N31

VCC_21

M31

VCC_22

AA30

VCC_23

Y30

VCC_24

W30

VCC_25

V30

VCC_26

U30

VCC_27

T30

VCC_28

R30

VCC_29

P30

VCC_30

N30

VCC_31

M30

VCC_32

L30

VCC_33

AA29

VCC_34

Y29

VCC_35

W29

VCC_36

V29

VCC_37

U29

VCC_38

R29

VCC_39

P29

VCC_40

M29

VCC_41

L29

VCC_42

AB28

VCC_43

AA28

VCC_44

Y28

VCC_45

V28

VCC_46

U28

VCC_47

T28

VCC_48

R28

VCC_49

P28

VCC_50

N28

VCC_51

M28

VCC_52

L28

VCC_53

P27

VCC_54

N27

VCC_55

M27

VCC_56

L27

VCC_57

P26

VCC_58

N26

VCC_59

L26

VCC_60

N25

VCC_61

M25

VCC_62

L25

VCC_63

P24

VCC_64

N24

VCC_65

M24

VCC_66

AB23

VCC_67

AA23

VCC_68

Y23

VCC_69

P23

VCC_70

N23

VCC_71

M23

VCC_72

L23

VCC_73

AC22

VCC_74

AB22

VCC_75

Y22

VCC_76

W22

VCC_77

P22

VCC_78

N22

VCC_79

M22

VCC_80

L22

VCC_81

AC21

VCC_82

AA21

VCC_83

W21

VCC_84

N21

VCC_85

M21

VCC_86

L21

VCC_87

AC20

VCC_88

AB20

VCC_89

Y20

VCC_90

W20

VCC_91

P20

VCC_92

N20

VCC_93

M20

VCC_94

L20

VCC_95

AB19

VCC_96

AA19

VCC_97

Y19

VCC_98

N19

VCC_99

M19

VCC_100

L19

VCC_101

N18

VCC_102

M18

VCC_103

L18

VCC_104

P17

VCC_105

N17

VCC_106

M17

VCC_107

N16

VCC_108

M16

VCC_109

L16

VCC_110

5

VCC

VCC

Calistoga

Calistoga

VCC_SM_100

VCC_SM_101

VCC_SM_102

VCC_SM_103

VCC_SM_104

VCC_SM_105

VCC_SM_106

VCC_SM_107

VCC_SM_0

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_SM_37

VCC_SM_38

VCC_SM_39

VCC_SM_40

VCC_SM_41

VCC_SM_42

VCC_SM_43

VCC_SM_44

VCC_SM_45

VCC_SM_46

VCC_SM_47

VCC_SM_48

VCC_SM_49

VCC_SM_50

VCC_SM_51

VCC_SM_52

VCC_SM_53

VCC_SM_54

VCC_SM_55

VCC_SM_56

VCC_SM_57

VCC_SM_58

VCC_SM_59

VCC_SM_60

VCC_SM_61

VCC_SM_62

VCC_SM_63

VCC_SM_64

VCC_SM_65

VCC_SM_66