Page 1

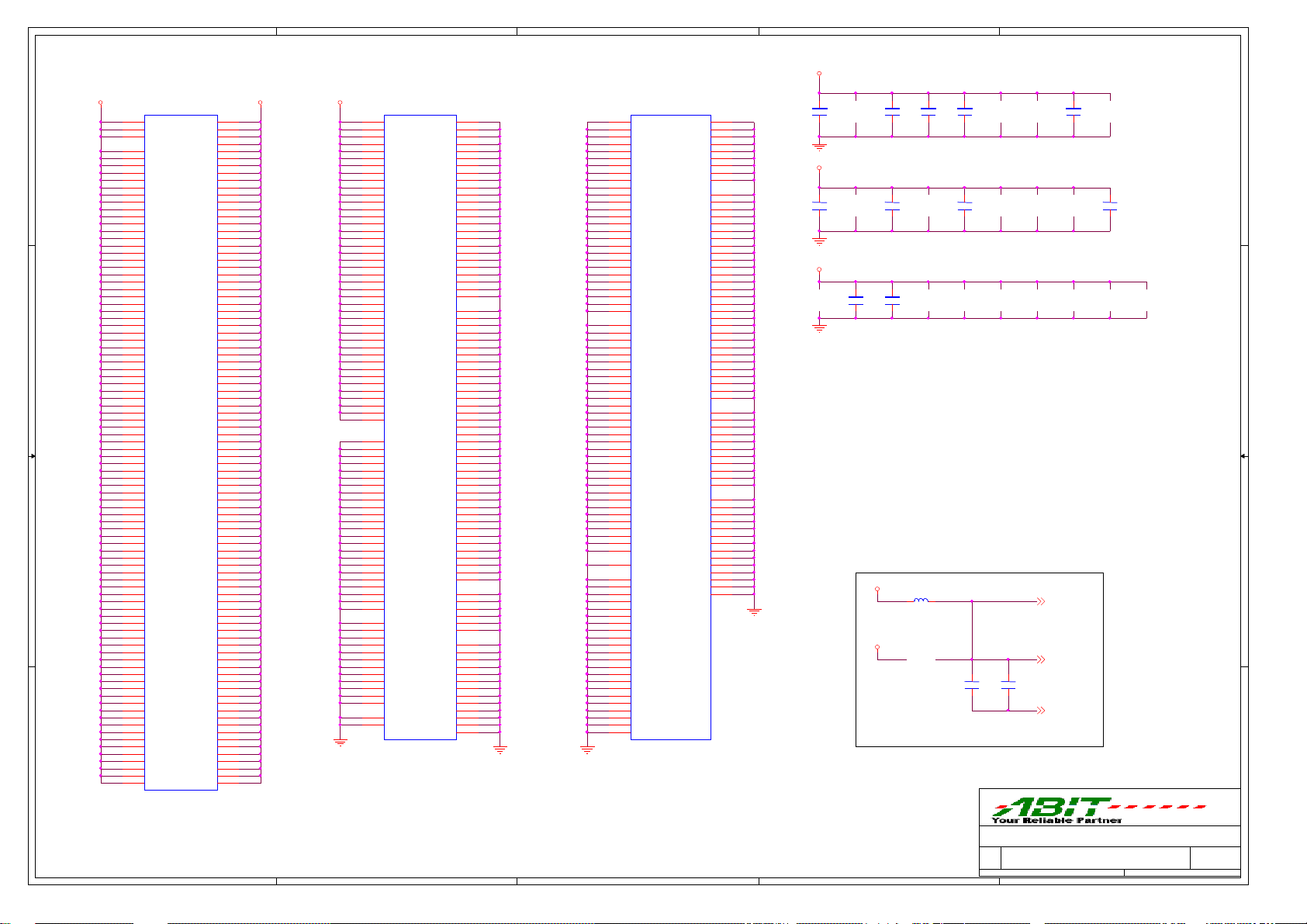

5

4

3

2

1

Version: 1.4

Intel APAC Lakeport CRB Schematic

D D

TITLE

COVER SHEET

BLOCK DIAGRAM & SETTINGS

CK410 CLOCK GEN. / BUFFER

P4-775 PART A , B

MCH-Lakeport part A & B & C

C C

DIMM1, 2, 3, 4 & TERMINATION

PCI EXPRESS X16 DISPLAY

VGA CONNECTOR

ICH7 PART A ,B & C

PCI EXPRESS X1 SLOT 1 & 2,SATA

PCI 1, 2, 3

LAN Part A & B

B B

ALC880 AUDIO CODEC & AUDIO LINE IN & OUT

LPC I/O, FDC, COM & LPT

KB, MS, FWH, SMB & AK2001

USB,FPIO & MISC.

V1.1

V1.1, V1.3

V1.1, V1.2, V1.3, V1.4

V1.1 ,V1.3

V1.1

V1.1, V1.2, V1.3

SHEETMODIFY

1

2

3

4, 5

6, 7, 8

9, 10, 11

12

13

14, 15, 16

17

18

19, 20

21, 22

23

24

25

ATX POWER & FAN

VCORE

OTHER DC-DC CONVERTER

V1.3

V1.1, V1.3

MECHANICAL

A A

5

4

3

26

27

28

29

30

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Lakeport CRB

Lakeport CRB

Lakeport CRB

1

1.4

1.4

1.4

1 30Wednesday, July 09, 2008

1 30Wednesday, July 09, 2008

1 30Wednesday, July 09, 2008

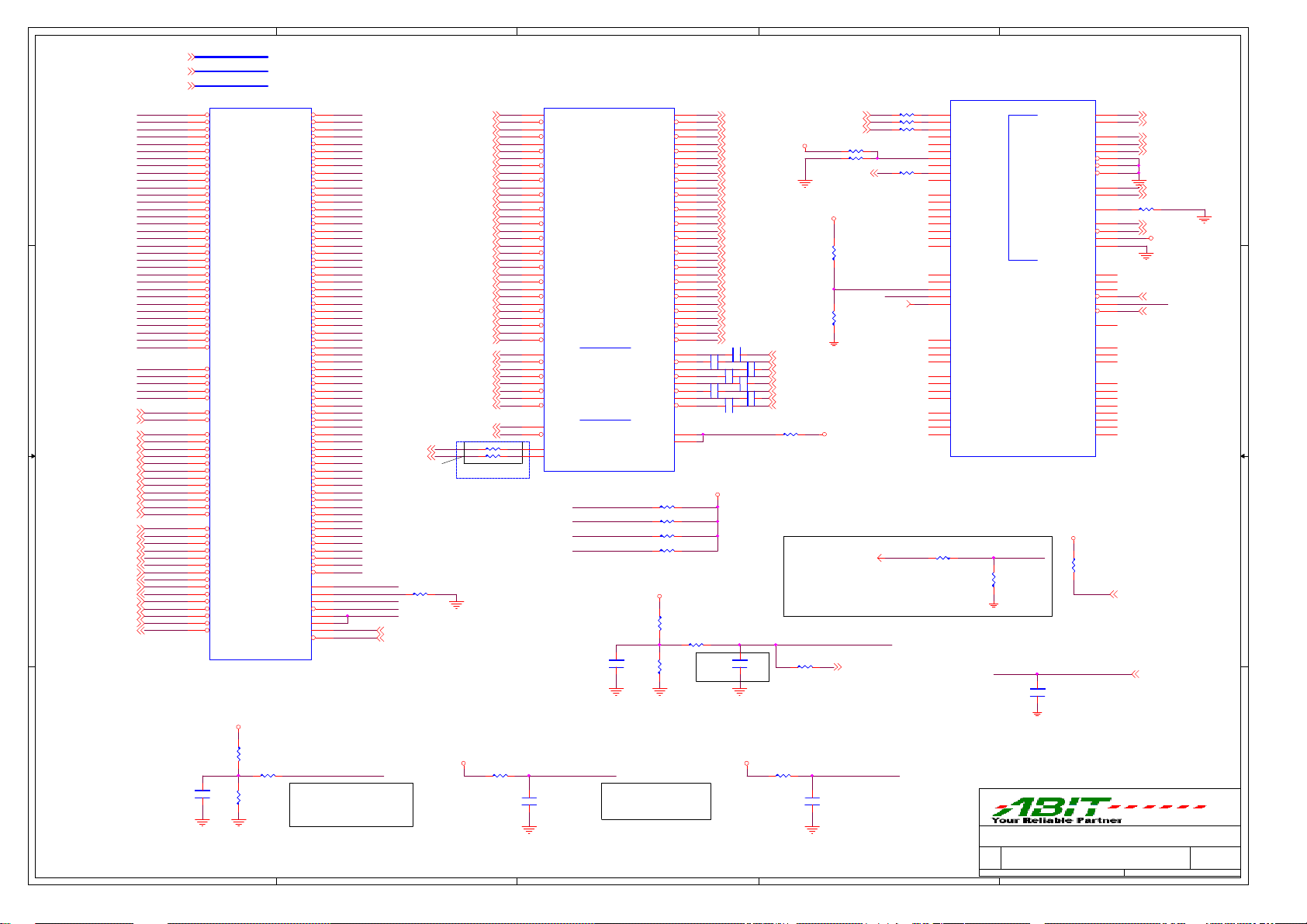

Page 2

5

4

3

2

1

PINNAME WELL USAGE I/O NOTE

ICH7 GPIO SETTING

D D

VRD

10.1

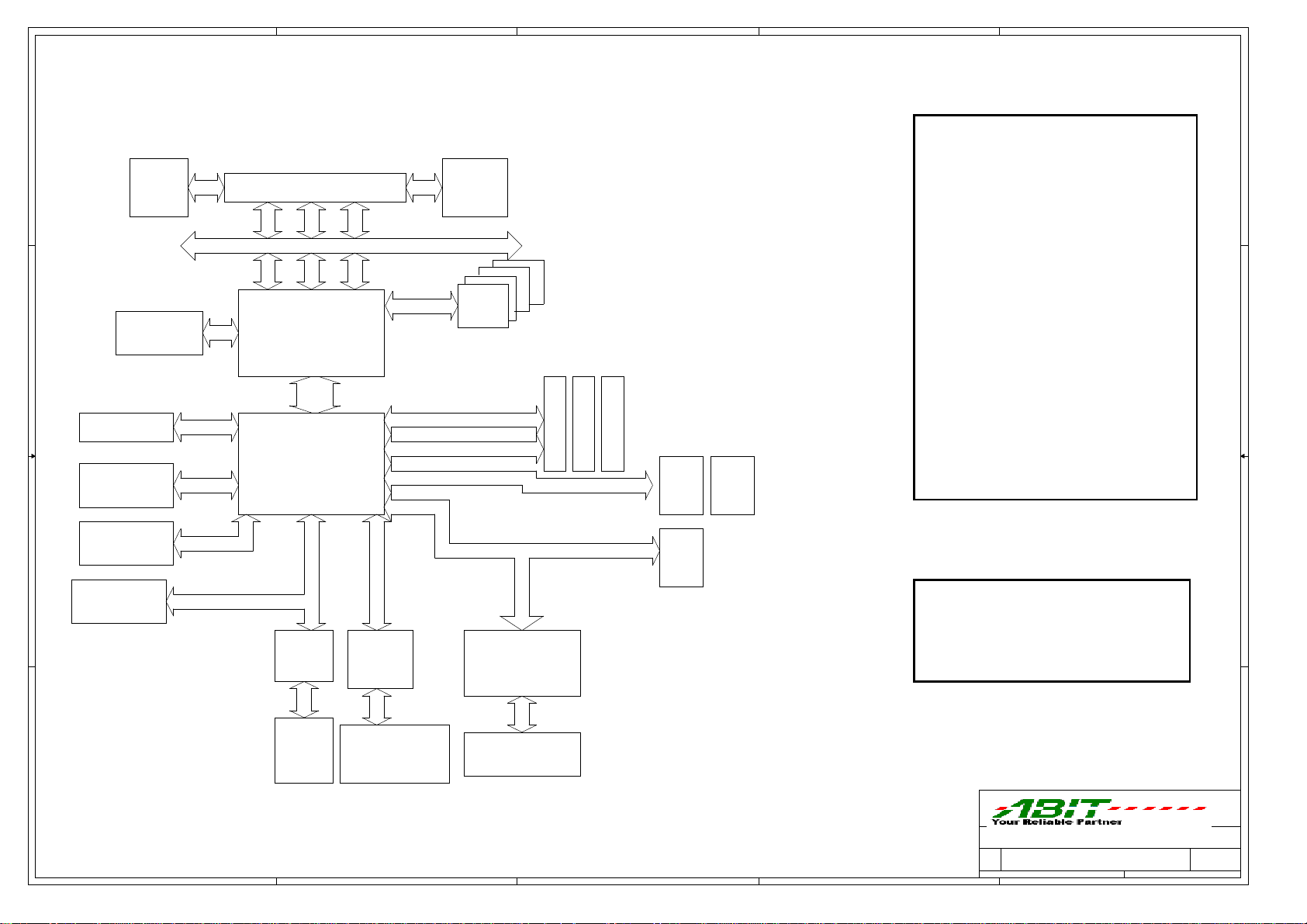

BLOCK DIAGRAM

775-PIN P4

CTRL

ADDR

AGTL+ BUS

ADDR

DATA

FSB 533/800/1066

DATA

CTRL

CK_410

4 DIMM

PCI CNTRL

DDR2

PCI-EX1

PCI CONN 2

PCI CONN 1

PCI CONN 3

PCI

EXPRESS

X1 CON

heard

NEW

CARD

X1 CON

EXPRESS

PCI

PCI EXPRESS X16

Connector (VGA)

C C

8.4G

IDE Primary

UDMA/100

MCH

Intel Lakeport

DMI

PCIE X4

2G/1G

PCI ADDR/DATA

ICH7

SATA 2

4PORT

USB PORT 1-8

USB 2.0

B B

SATA/3Gb

USB

PCI EXPRESS X1

GPI0 MAIN P_REQA I

GPI1 MAIN P_REQ5 I

GPI2 MAIN P_REQE I

GPI3 MAIN P_REQF I

GPI4 MAIN P_REQG I

GPI5 MAIN P_REQH I

GPI6 MAIN N/A I

GPI7 MAIN N/A I

GPI8 RESUME LPC_PME I

GPI9 RESUME 66DET I

GPI10 RESUME FWH_WP I

GPI11 RESUME SMB_ALERT I

GPI12 RESUME ACZ_DET I

GPI13 RESUME N/A I

GPI14 RESUME N/A I

GPI15 RESUME N/A I

GPO16 MAIN N/A O

GPO17 MAIN N/A O

GPO18 MAIN N/A O

GPO19 MAIN N/A O

GPO20 MAIN N/A O

GPO21 MAIN N/A O

GPO22 MAIN N/A OD

GPO23 MAIN LDQR1# O

GPO24 RESUME LAN_DISABLE I/O

GPO25 RESUME N/A I/O

GPO27 RESUME N/A I/O

GPO28 RESUME N/A I/O

GPO32 MAIN N/A I/O

GPO33 MAIN N/A I/O

GPO34 MAIN N/A I/O

PCI DEVICE SETTING

FirmWare Hub

A A

5

LPC

SIO

Floopy

KB/MS

HD AUDIO

ALC880D

7.1 Channel

S/P DIF IN

S/P DIF OUT

4

LAN

Intel 82573

82562EX/GX/GZ

RJ45

10/100/1000Mb

3

2

DEVICE PCI1 PCI2 PCI3

IRQ F G F

| G F E

| H E H

| E H G

ID 21 22 23

REQ/GNT 0 1 2

Title

Title

Title

BLOCK DIAGRAM & SETTING

BLOCK DIAGRAM & SETTING

BLOCK DIAGRAM & SETTING

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Lakeport CRB

Lakeport CRB

Lakeport CRB

1

1.4

1.4

1.4

2 30Wednesday, July 09, 2008

2 30Wednesday, July 09, 2008

2 30Wednesday, July 09, 2008

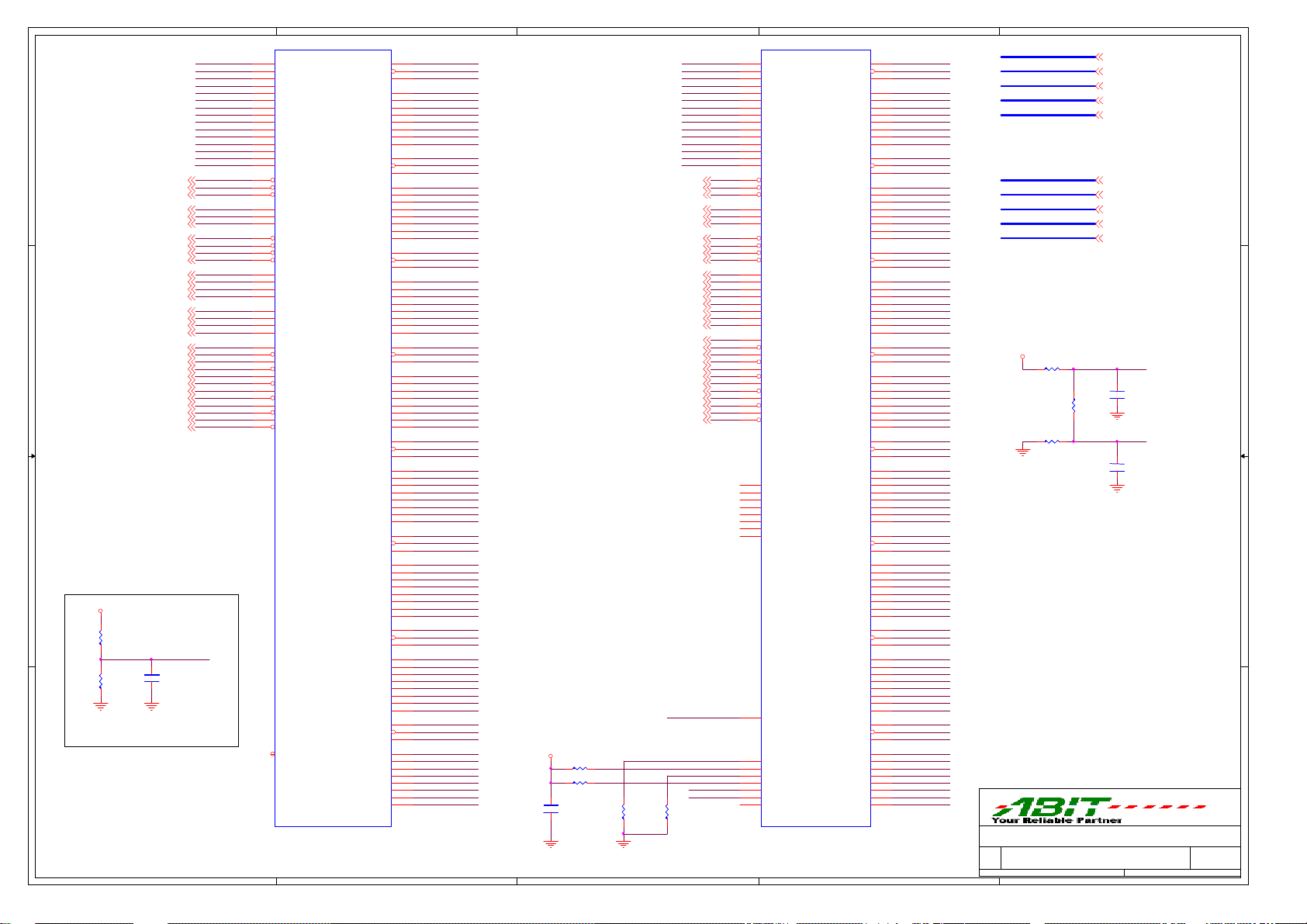

Page 3

5

VCC3

FB20

VCCP

0805

0805

FB20

30_OHM-0805

30_OHM-0805

L0805

L0805

C360

C360

4.7U

4.7U

0603

0603

10V

10V

Y5V

Y5V

10UF X1

0.1UF X7

R375

R375

220

220

C307

C307

0.1U

0.1U

16V

16V

Y5V

Y5V

0603

0603

C358

C358

20P

20P

50V

50V

NPO

NPO

0603

0603

0603

0603

C362

C362

1U

1U

Y5V

Y5V

16V

16V

C317

C317

0.1U

0.1U

16V

16V

Y5V

Y5V

C361

C361

0.1U

0.1U

Y5V

Y5V

16V

16V

VCC3_CLK

Q38

Q38

B

SOT23

SOT23

14.318MHZ

14.318MHZ

XTAL-49US

XTAL-49US

0603

0603

0603

0603

Y2

Y2

0603

0603

E C

49US

49US

C348

C348

0.1U

0.1U

16V

16V

Y5V

Y5V

C299

C299

0.1U

0.1U

Y5V

Y5V

16V

16V

R3881KR388

1K

TR-SOT23

TR-SOT23

C281

C281

0.1U

0.1U

0603

0603

16V

16V

Y5V

Y5V

PMBS3904

PMBS3904

SMBDATA9,10,12,15,17,18,19,23

SMBCLK9,10,12,15,17,18,19,23

CLK_X1

CLK_X2

C359

C359

20P

20P

0603

0603

50V

50V

NPO

NPO

VCC3_CLK

0603

0603

C201

C201

4.7U

4.7U

0805

0805

10V

10V

Y5V

Y5V

VCC3_CLK

C293

C293

0.1U

0.1U

16V

16V

Y5V

Y5V

0603

0603

VCC3_CLK

Q1

Q1

B

SOT23

SOT23

R5

X10KR5X10K

C185

C185

0.1U

0.1U

16V

16V

Y5V

Y5V

E C

VCC3_CLK

R21KR2

1K

PMBS3904

PMBS3904

TR-SOT23

TR-SOT23

R6

X10KR6X10K

VCC3_CLK

VTT_PG

R337

R337

X10K

X10K

D D

C C

B B

A A

4

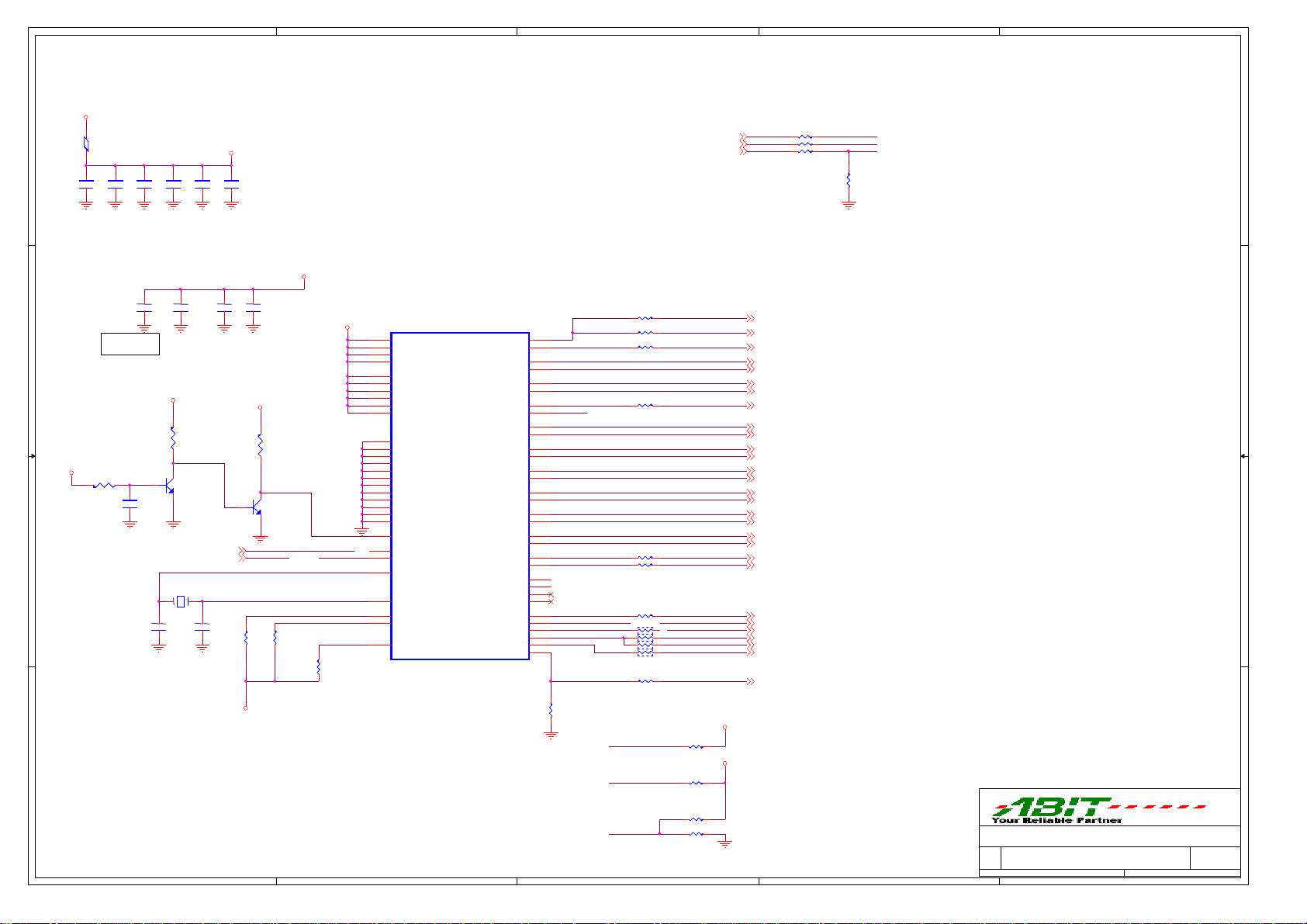

U34

U34

47

VDDCPU

44

VDDI/O

32

VDD_PCIEX

42

VDD_SRC

14

VDD48

3

VDD

5

VDDPCI

62

VDD25M_STB

61

VDDSATA_STB

53

VDDREF_STB

63

GND

50

GND

58

GND

56

GND

43

GNDA

2

GND

6

GND

17

GND

21

GND

26

GND

31

GND

37

GND

18

VTTPWGD/WOL_STOP#

52

SDATA

51

SCLK

55

X1

54

X2

7

**DOC_1

13

**DOC_0

1

**RLATCH

ICS9LPRS511

ICS9LPRS511

FSLC/REF0_2x

FSLA/USB_48MHz

CPUCLK0

CPUCLK0#

CPUCLK1

CPUCLK1#

25Mhz_0F_2x/Freerun*

**GSEL/24.576Mhz

PCIeT4

PCIeC4

PCIeT3

PCIeC3

PCIeT2

PCIeC2

SATACLKT

SATACLKC

PCIeT1

PCIeC1

PCIeT5

PCIeC5

96MHz_T/PCIeT0

96MHz_C/PCIeC0

PCIeT6

PCIeC6

PCIeT7

PCIeC7

SELRSET/RESET#/PCICLK3

PCICLK4

FSLB/PCICLK2_2x

PCICLK1_2x

PCICLK0

*SEL24_48#/24_48Mhz

57

15

49

48

46

45

64

4

29

30

27

28

24

25

60

59

22

23

34

33

19

20

36

35

39

38

12

11

10

9

8

16

FSC

FSA

R_H_MCH_P

R_H_MCH_N

R_H_CPU_P

R_H_CPU_N

Freerun

GSEL

R_PE_MCH_P

R_PE_MCH_N

R_PE_ICH_P

R_PE_ICH_N

R_PE_X16_P

R_PE_X16_N

R_SATA_P

R_SATA_N

R_PE_S1_P

R_PE_S1_N

R_PE_S2_P

R_PE_S2_N

R_DOT96_P

R_DOT96_N

SELRST

FSB

R306

R306

10K

10K

3

R38522/X R38522/X

R355 22R355 22

R342 22R342 22

R53033 R53033

R3830/X R3830/X

R3840/X R3840/X

1 8

2 7

3 6

4 5

R348 22R348 22

Freerun

GSEL

R51833 R51833

R370 X10KR370 X10K

R4 10KR4 10K

RN16-1 33-8P4RRN16-1 33-8P4R

RN16-2 33-8P4RRN16-2 33-8P4R

RN16-3 33-8P4RRN16-3 33-8P4R

RN16-4 33-8P4RRN16-4 33-8P4R

CPU_FSA4,6

CPU_FSB4,6

CPU_FSC4,6

VCC3_CLK

VCC3_CLK

R190 1KR190 1K

R186 1KR186 1K

R182 1KR182 1K

CK_14M_AC97 21

CK_14M_ICH 15

CK_48M_USB 14

CK_H_MCH_P 6

CK_H_MCH_N 6

CK_H_CPU_P 4

CK_H_CPU_N 4

PCIE_25M 19

CK_PE_MCH_P 6

CK_PE_MCH_N 6

CK_PE_ICH_P 14

CK_PE_ICH_N 14

CK_PE_X16_P 12

CK_PE_X16_N 12

CK_PE_SATA_P 14

CK_PE_SATA_N 14

CK_PE_S3_P 19

CK_PE_S3_N 19

CK_PE_S2_P 17

CK_PE_S2_N 17

CK_DOT96_P 6

CK_DOT96_N 6

CK_33M_ICH 14

CK_33M_S4 29

CK_33M_S2 18

CK_33M_S1 18

CK_33M_S3 18

CK_33M_SIO 23

CK_48M_SIO 23

FSA

FSB

FSC

2

R39

R39

10K

10K

1

SELRST

5

4

R33 10K/XR33 10K/X

R3 10KR3 10K

3

2

Title

Title

Title

CK505 CLOCK GEN. / BUFFER

CK505 CLOCK GEN. / BUFFER

CK505 CLOCK GEN. / BUFFER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Lakeport CRB

Lakeport CRB

Lakeport CRB

1

3 30Wednesday, July 09, 2008

3 30Wednesday, July 09, 2008

3 30Wednesday, July 09, 2008

1.4

1.4

1.4

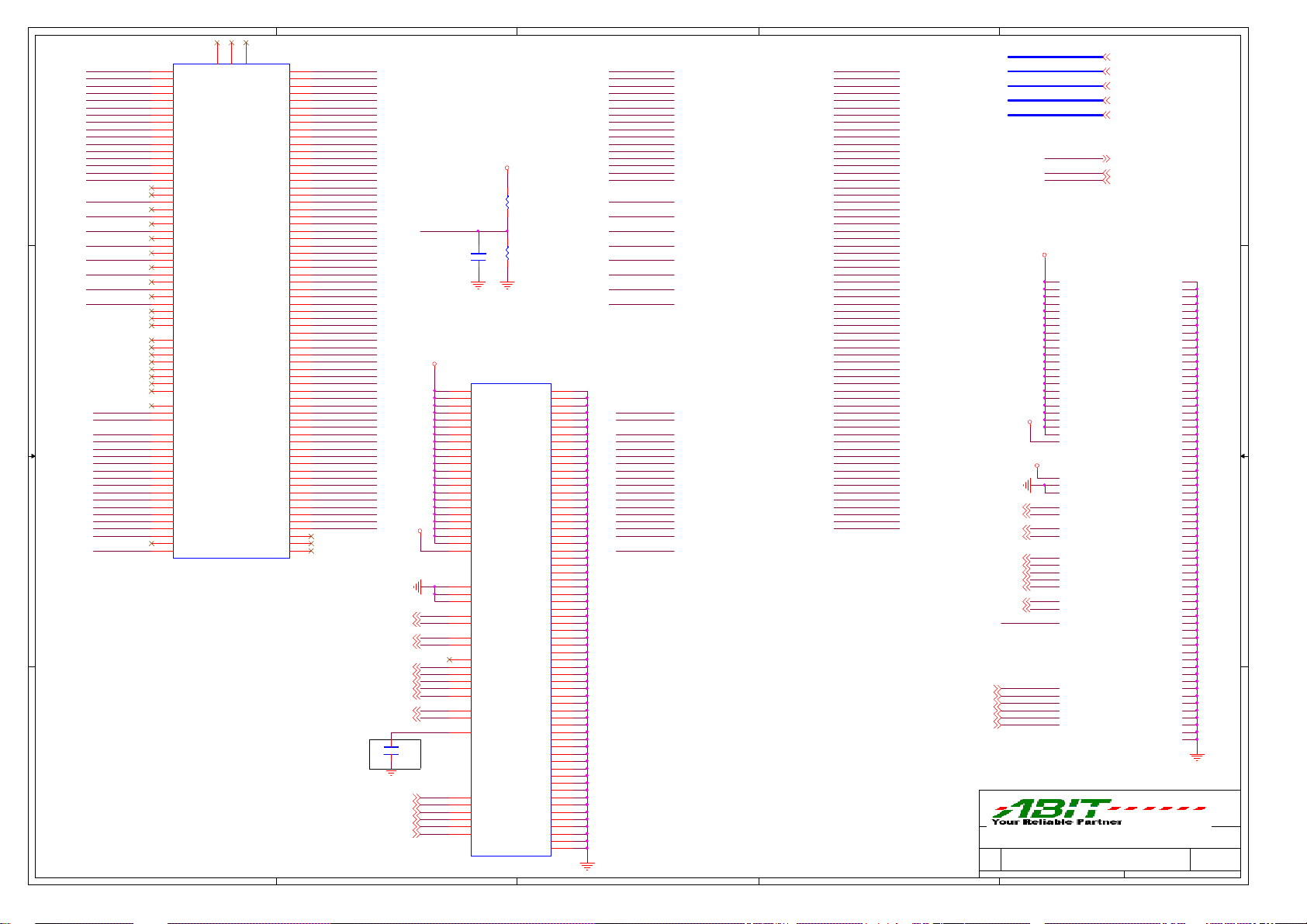

Page 4

5

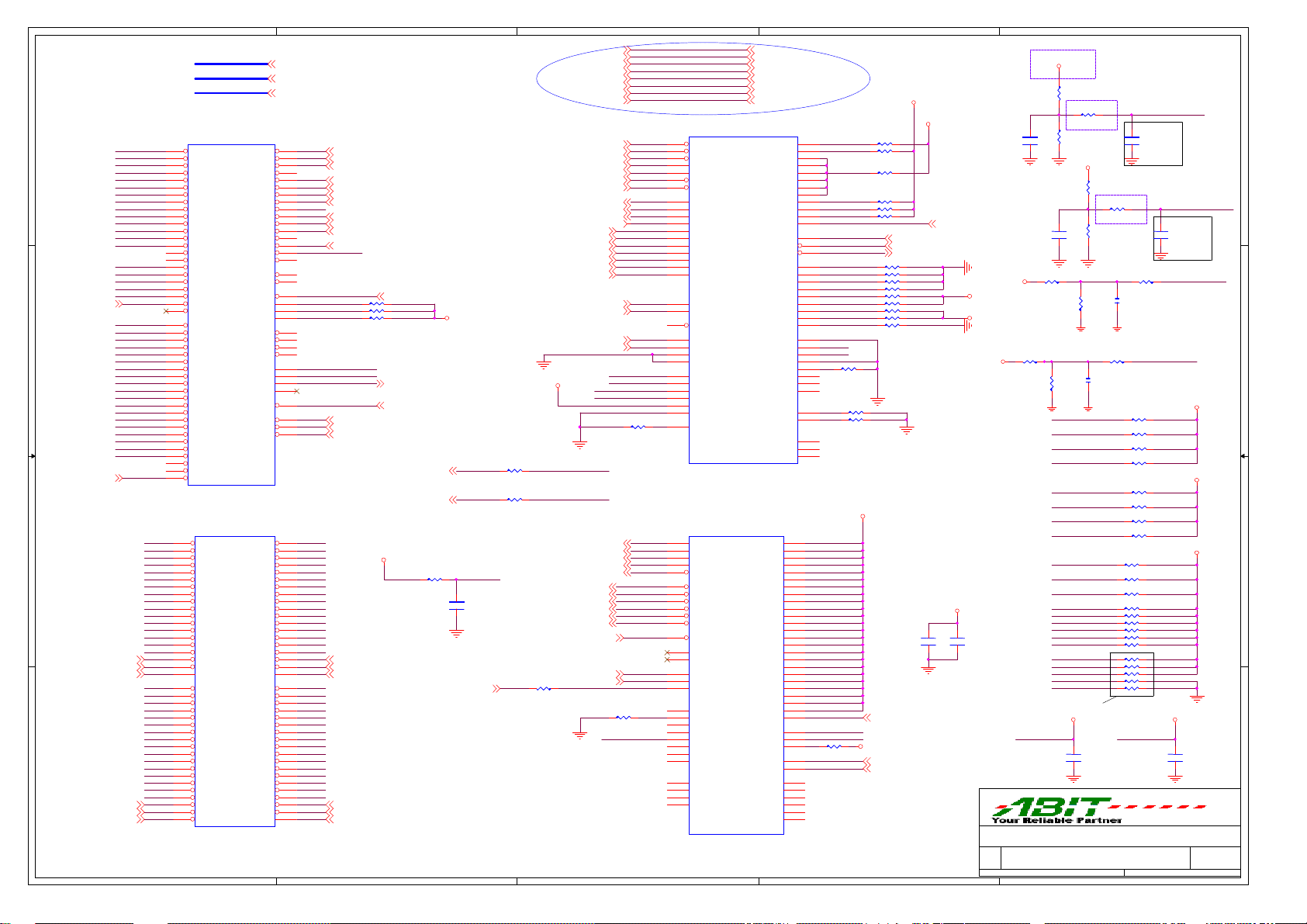

H_REQ[0..4]

H_A[3..35]

H_D[0..63]

SK1A

H_D0

H_D1

H_D2

H_D3

H_D4

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

5

SK1A

L5

A03*

P6

A04*

M5

A05*

L4

A06*

M4

A07*

R4

A08*

T5

A09*

U6

A10*

T4

A11*

U5

A12*

U4

A13*

V5

A14*

V4

A15*

W5

A16*

N4

RSVD0

P5

RSVD1

K4

REQ0*

J5

REQ1*

M6

REQ2*

K6

REQ3*

J6

REQ4*

R6

ADSTB0*

G5

PCREQ*

AB6

A17*

W6

A18*

Y6

A19*

Y4

A20*

AA4

A21*

AD6

A22*

AA5

A23*

AB5

A24*

AC5

A25*

AB4

A26*

AF5

A27*

AF4

A28*

AG6

A29*

AG4

A30*

AG5

A31*

AH4

A32*

AH5

A33*

AJ5

A34*

AJ6

A35*

AC4

RSVD2

AE4

RSVD3

AD5

ADSTB1*

LGA_775

LGA_775

SOCKET_LGA775_DIP

SOCKET_LGA775_DIP

SK1B

SK1B

B4

D00*

C5

D01*

A4

D02*

C6

D03*

A5

D04*

B6

D05*

B7

D06*

A7

D07*

A10

D08*

A11

D09*

B10

D10*

C11

D11*

D8

D12*

B12

D13*

C12

D14*

D11

D15*

A8

DBI0*

C8

DSTBN0*

B9

DSTBP0*

G9

D16*

F8

D17*

F9

D18*

E9

D19*

D7

D20*

E10

D21*

D10

D22*

F11

D23*

F12

D24*

D13

D25*

E13

D26*

G13

D27*

F14

D28*

G14

D29*

F15

D30*

G15

D31*

G11

DBI1*

G12

DSTBN1*

E12

DSTBP1*

LGA_775

LGA_775

SOCKET_LGA775_DIP

SOCKET_LGA775_DIP

GTLREF_SEL

D D

H_ADSTB06

C C

H_ADSTB16

B B

A A

H_A3

H_A4

H_A5

H_A6

H_A7

H_A8

H_A9

H_A10

H_A11

H_A12

H_A13

H_A14

H_A15

H_A16

H_REQ0

H_REQ1

H_REQ2

H_REQ3

H_REQ4

H_A17

H_A18

H_A19

H_A20

H_A21

H_A22

H_A23

H_A24

H_A25

H_A26

H_A27

H_A28

H_A29

H_A30

H_A31

H_A32

H_A33

H_A34

H_A35

H_DBI06

H_STBN06

H_STBP06

H_DBI16

H_STBN16

H_STBP16

ADS*

BNR*

HIT*

RSP*

BPRI*

DBSY*

DRDY*

HITM*

IERR*

INIT*

LOCK*

TRDY*

BINIT*

DEFER*

EDRDY*

MCERR*

AP0*

AP1*

BR0*

TESTHI08

TESTHI09

TESTHI10

DP0*

DP1*

DP2*

DP3*

GTLREF0

GTLREF1

GTLREF2

RESET*

RS0*

RS1*

RS2*

D32*

D33*

D34*

D35*

D36*

D37*

D38*

D39*

D40*

D41*

D42*

D43*

D44*

D45*

D46*

D47*

DBI2*

DSTBN2*

DSTBP2*

D48*

D49*

D50*

D51*

D52*

D53*

D54*

D55*

D56*

D57*

D58*

D59*

D60*

D61*

D62*

D63*

DBI3*

DSTBN3*

DSTBP3*

H_REQ[0..4] 6

H_A[3..35] 6

H_D[0..63] 6

D2

C2

D4

H4

G8

B2

C1

E4

H_IERR#

AB2

P3

C3

E3

AD3

G7

GTLREF2

F2

AB3

U2

U3

H_BREQ0#

F3

TESTHI8

G3

TESTHI9

G4

TESTHI10

H5

J16

H15

H16

J17

H1

H2

E24

H29

H_CPURST#

G23

B3

F5

A3

BLACK

BLACK

H_D32

G16

H_D33

E15

H_D34

E16

H_D35

G18

H_D36

G17

H_D37

F17

H_D38

F18

H_D39

E18

H_D40

E19

H_D41

F20

H_D42

E21

H_D43

F21

H_D44

G21

H_D45

E22

H_D46

D22

H_D47

G22

D19

G20

G19

H_D48

D20

H_D49

D17

H_D50

A14

H_D51

C15

H_D52

C14

H_D53

B15

H_D54

C18

H_D55

B16

H_D56

A17

H_D57

B18

H_D58

C21

H_D59

B21

H_D60

B19

H_D61

A19

H_D62

A22

H_D63

B22

C20

A16

C17

BLACK

BLACK

H_ADS# 6

H_BNR# 6

H_HIT# 6

H_BPRI# 6

H_DBSY# 6

H_DRDY# 6

H_HITM# 6

H_INIT# 14

H_LOCK# 6

H_TRDY# 6

H_DEFER# 6

CPU_GTLREF_0

CPU_GTLREF_1

H_RS0# 6

H_RS1# 6

H_RS2# 6

H_DBI2 6

H_STBN2 6

H_STBP2 6

H_DBI3 6

H_STBN3 6

H_STBP3 6

H_BREQ0# 6

R99 62R99 62

R104 62R104 62

R96 62R96 62

MCH_CPU_GTLREF 6

H_CPURST# 6

VCC15

4

VCCSENSE27

VSSSENSE27

4

R10 0

R10 0

SHORT

SHORT

C2

C2

1U

1U

16V

16V

Y5V

Y5V

VTT_OUT_LEFT

VCC_PLL

0603

0603

CPU_FSC3,6

UPDATE

R31 0R31 0

R30 0R30 0

VCCP

VCC_PKGSENSE

VSS_PKGSENSE

R360R36

0

CPUVID727

CPUVID627

CPUVID527

CPUVID427

CPUVID327

CPUVID227

CPUVID127

CPUVID027

H_SMI#14

H_A20M#14

H_FERR#14

H_INTR14

H_NMI14

H_IGNNE#14

H_STPCLK#14

H_VCCA5

H_VSSA5

H_VCCIOPLL5

VCC_PLL8

CPUVID027

CPUVID127

CPUVID227

CPUVID327

CPUVID427

CPUVID527

CPUVID627

CK_H_CPU_P3

CK_H_CPU_N3

THRMDA23,26

THRMDC23,26

VCC_PKGSENSE

VSS_PKGSENSE

TRST#

H_BPM0

H_BPM1

H_BPM2

H_BPM3

H_BPM4

H_BPM5

FP_RST#15,25

CPU_FSA3,6

CPU_FSB3,6

R48 X1KR48 X1K

H_FERR#

TP_VCCSENSE

TP_VSSSENSE

R20 51R20 51

TCK

TDI

TDO

TMS

H_BPM0

H_BPM1

H_BPM2

H_BPM3

H_BPM4

H_BPM5

CPU_FSCCC

GTLREF3

3

VCC_PLL

TCK

TDI

TDO

TMS

TRST#

3

SK1C

SK1C

P2

SMI*

K3

A20M*

R3

FREE*/PBE*

K1

LINT0

L1

LINT1

N2

IGNNE*

M3

STPCLK*

A23

VCCA

B23

VSSA

C23

VCCIOPLL

D23

VCC_PLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

VID6

F28

BLCK0

G28

BLCK1

AE8

SKTOCC*

AL1

THERMDA

AK1

THERMDC

AJ7

VSS277

AH7

VSS278

AN3

VCCSENSE

AN4

VSSSENSE

AN5

VCC_MB_REGULATION

AN6

VSS_MB_REGULATION

AL8

VCC

AL7

VSS279

F6

IMPSEL

LGA_775

LGA_775

SOCKET_LGA775_DIP

SOCKET_LGA775_DIP

SK1D

SK1D

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST*

AJ2

BPM0*

AJ1

BPM1*

AD2

BPM2*

AG2

BPM3*

AF2

BPM4*

AG3

BPM5*

AC2

DBR*

AK3

ITPCLKOUT0

AJ3

ITPCLKOUT1

G29

BSEL0

H30

BSEL1

G30

BSEL2

E7

RSVD15

N5

RSVD16

AE6

RSVD17

C9

RSVD18

G10

RSVD19

D16

RSVD20

A20

RSVD21

E23

RSVD22

1

H1

2

H2

3

H3

4

H4

LGA_775

LGA_775

SOCKET_LGA775_DIP

SOCKET_LGA775_DIP

IO_CPUVID7 23,27

IO_CPUVID6 23,27

IO_CPUVID5 23,27

IO_CPUVID4 23,27

IO_CPUVID3 23,27

IO_CPUVID2 23,27

IO_CPUVID1 23,27

IO_CPUVID0 23,27

TESTHI00

TESTHI01

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

TESTHI11

TESTHI12

TESTHI13

FORCEPH

PWRGOOD

PROCHOT*

THERMTRIP*

BOOTSELECT

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

VID_SELECT

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

COMP8

VSS280

VSS281

VSS282

VSS283

VSS284

RSVD12

RSVD13

RSVD14

MSID[1]

MSID[0]

LL_ID0

LL_ID1

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

AN7

AM7

F23

D14

E6

E5

D1

J3

BLACK

BLACK

F26

W3

F25

G25

G27

G26

G24

F24

P1

W2

L2

AK6

N1

AL2

M2

A13

T1

G2

R1

J2

T2

Y3

AE3

B13

AL3

CPU_U1

U1

CPU_G1

G1

E29

A24

F29

G6

AH2

V1

W1

Y1

V2

AA2

BLACK

BLACK

VTT_OUT_RIGHT

VTT_OUT_LEFT

R156 X1KR156 X1K

R146 62R146 62

TESTHI0

TESTHI1

R82 62R82 62

R155 62R155 62

TESTHI2_7

R93 62R93 62

TESTHI11

TESTHI12

R87 62R87 62

R95 62R95 62

TESTHI13

H_PWRGD

PROCHOT#

THRMTRIP#

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

COMP8

R79 X1KR79 X1K

R88 62R88 62

R86 62R86 62

VTT12

VCC3

2

VTT_OUT_LEFT

VTT12

H_PWRGD 15

PROCHOT#

THRMTRIP# 14

1%

R164 49.9_1%

1%

R164 49.9_1%

1%

R90 60.4_1%

1%

R90 60.4_1%

1%

R103 60.4_1%

1%

R103 60.4_1%

1%

R92 60.4_1%

1%

R92 60.4_1%

1%

R97 60.4_1%

1%

R97 60.4_1%

1%

R91 60.4_1%

1%

R91 60.4_1%

1%

R81 60.4-1%

1%

R81 60.4-1%

1%

R78 60.4-1%

1%

R78 60.4-1%

1%

R17 24.9_1%

1%

R17 24.9_1%

0603

0603

VR_RDY 27

VRD_SEL 27

CPUVID7 27

2

V1.3

H_FORCEPH

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

C40

C40

C42

C42

1U

1U

1U

1U

0603

0603

Y5V

Y5V

Y5V

Y5V

16V

16V

16V

16V

PLACE TCK/TDI/TMS

TERMINATION NEAR CPU

WITHIN 1.5" OF CPU.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

GTLREF VOLTAGE SHOULD BE 0.63 x VTT = 0.75V

VTT_OUT_RIGHT

R80

R80

124_1%

124_1%

1%

1%

R102 10R102 10

R85

0603

0603

C47

C47

1U

1U

16V

16V

Y5V

Y5V

R667 124/6/1/XR667 124/6/1/X

R85

210_1%

210_1%

1%

1%

VTT_OUT_RIGHT

0603

0603

R674

R674

210/6/1/X

210/6/1/X

PROCHOT#

CPU_FSA

CPU_FSB

CPU_FSCCC

CPU_U1

CPU_G1

H_BREQ0#

H_CPURST#

VRD_SEL

H_IERR#

H_FORCEPH

H_BPM0

H_BPM1

H_BPM2

H_BPM3

H_BPM4

H_BPM5

TDI

TDO

TMS

TCK

TRST#

0603

0603

Lakeport CRB

Lakeport CRB

Lakeport CRB

C43

C43

1U

1U

16V

16V

Y5V

Y5V

R671 124/6/1/XR671 124/6/1/X

VTT_OUT_RIGHT

P4-775 PART A

P4-775 PART A

P4-775 PART A

V1.2

0603

0603

R89

R89

124_1%

124_1%

1%

1%

R100 10R100 10

R84

R84

210_1%

210_1%

1%

1%

R668 10/6R668 10/6

R669

R669

C349

C349

210/6/1/X

210/6/1/X

1U/6/Y/10V/X

1U/6/Y/10V/X

R672 10/6R672 10/6

C354

C354

1U/6/Y/10V/X

1U/6/Y/10V/X

R178 130R178 130

R191 470R191 470

R187 470R187 470

R183 470R183 470

R19 51R19 51

R18 47R18 47

R105 62R105 62

R75 62R75 62

R47 1KR47 1K

R83 62R83 62

R69 X62R69 X62

R61 62R61 62

R62 62R62 62

R57 62R57 62

R71 62R71 62

R70 62R70 62

R67 62R67 62

R77 62R77 62

R74 62R74 62

R76 62R76 62

R73 62R73 62

R66 62R66 62

VTT_OUT_LEFT

C45

C45

X0.1U

X0.1U

16V

16V

Y5V

Y5V

1

CPU_GTLREF_0

Close

C59

C59

X220P

X220P

to PIN

16V

16V

H2

X7R

X7R

V1.2

0603

0603

GTLREF3

VTT_OUT_LEFTVTT_OUT_RIGHT

4 30Wednesday, July 09, 2008

4 30Wednesday, July 09, 2008

4 30Wednesday, July 09, 2008

CPU_GTLREF_1

C58

C58

X220P

X220P

16V

16V

X7R

X7R

GTLREF2

VTT_OUT_LEFT

VTT_OUT_RIGHT

C50

C50

X0.1U

X0.1U

0603

0603

16V

16V

Y5V

Y5V

Close

to PIN

H1

VTT12

1.4

1.4

1.4

Page 5

5

4

3

VCCP

2

1

VCCP VCCP VCCP

D D

C C

B B

A A

SK1E

SK1E

AG22

VCCP1

K29

VCCP2

AM26

VCCP3

AE12

VCCP5

AE11

VCCP6

W23

VCCP7

W24

VCCP8

W25

VCCP9

T25

VCCP10

Y28

VCCP11

AL18

VCCP12

AC25

VCCP13

W30

VCCP14

Y30

VCCP15

AN14

VCCP16

AD28

VCCP17

Y26

VCCP18

AC29

VCCP19

M29

VCCP20

U24

VCCP21

J23

VCCP22

AC27

VCCP23

AM18

VCCP24

AM19

VCCP25

AB8

VCCP26

AC26

VCCP27

J8

VCCP28

J28

VCCP29

T30

VCCP30

AM9

VCCP31

AF15

VCCP32

AC8

VCCP33

AE14

VCCP34

N23

VCCP35

W29

VCCP36

U29

VCCP37

AC24

VCCP38

AC23

VCCP39

Y23

VCCP40

AN26

VCCP41

AN25

VCCP42

AN11

VCCP43

AN18

VCCP44

Y27

VCCP45

Y25

VCCP46

AD24

VCCP47

AE23

VCCP48

AE22

VCCP49

AN19

VCCP50

V8

VCCP51

K8

VCCP52

AE21

VCCP53

AM30

VCCP54

AE19

VCCP55

AC30

VCCP56

AE15

VCCP57

M30

VCCP58

K27

VCCP59

M24

VCCP60

AN21

VCCP61

T8

VCCP62

AC28

VCCP63

N25

VCCP64

AE18

VCCP65

W26

VCCP66

AD25

VCCP67

M8

VCCP68

N30

VCCP69

AD26

VCCP70

AJ26

VCCP71

AM29

VCCP72

M25

VCCP73

M26

VCCP74

L8

VCCP75

U25

VCCP76

Y8

VCCP77

AJ12

VCCP78

AD27

VCCP79

U23

VCCP80

M23

VCCP81

AG29

VCCP82

N27

VCCP83

AM22

VCCP84

U28

VCCP85

K28

VCCP86

U8

VCCP87

AK18

VCCP88

AD8

VCCP89

K24

VCCP90

AH28

VCCP91

AH21

VCCP92

LGA_775

LGA_775

SOCKET_LGA775_DIP

SOCKET_LGA775_DIP

VCCP93

VCCP94

VCCP95

VCCP96

VCCP97

VCCP98

VCCP99

VCCP100

VCCP101

VCCP102

VCCP103

VCCP104

VCCP105

VCCP106

VCCP107

VCCP108

VCCP109

VCCP110

VCCP111

VCCP112

VCCP113

VCCP114

VCCP115

VCCP116

VCCP117

VCCP118

VCCP119

VCCP120

VCCP121

VCCP122

VCCP123

VCCP124

VCCP125

VCCP126

VCCP127

VCCP128

VCCP129

VCCP130

VCCP131

VCCP132

VCCP133

VCCP134

VCCP135

VCCP136

VCCP137

VCCP138

VCCP139

VCCP140

VCCP141

VCCP142

VCCP143

VCCP144

VCCP145

VCCP146

VCCP147

VCCP148

VCCP149

VCCP150

VCCP151

VCCP152

VCCP153

VCCP154

VCCP155

VCCP156

VCCP157

VCCP158

VCCP159

VCCP160

VCCP161

VCCP162

VCCP163

VCCP164

VCCP165

VCCP166

VCCP167

VCCP168

VCCP169

VCCP170

VCCP171

VCCP172

VCCP173

VCCP174

VCCP175

VCCP176

VCCP177

VCCP178

VCCP179

VCCP180

VCCP181

VCCP182

VCCP183

VCCP184

AK12

AH22

T29

AM14

AM25

AE9

Y29

AK25

AK19

AG15

J22

T24

AG21

AM21

J25

U30

AL21

AG25

AJ18

J19

AH30

J15

AG12

AJ22

J20

AH18

AH26

W27

AL25

AN8

AH14

U27

T23

R8

AK22

AN29

AG11

AK26

J10

AJ15

AG26

AN9

AH15

AF18

AL15

J26

J18

J21

AG27

AK15

AF11

AD23

AM15

AF8

AK21

AG30

AJ21

AM11

AL11

AJ11

K30

AL14

AN30

AH25

AL12

AJ9

AK11

AG14

N29

AL30

AJ25

AH9

J29

J11

K25

P8

K23

AL19

AM8

T26

N28

AH12

AL22

AN15

AJ8

U26

AJ19

T27

AK8

AN12

AG9

N26

BLACK

BLACK

SK1F

SK1F

AF9

VCCP185

AF22

VCCP186

AH11

VCCP187

AJ14

VCCP188

AH19

VCCP189

AH29

VCCP190

AH27

VCCP191

AG28

VCCP192

AL26

VCCP193

AM12

VCCP194

J24

VCCP195

J13

VCCP196

T28

VCCP197

W28

VCCP198

J12

VCCP199

J27

VCCP200

AG19

VCCP201

AL9

VCCP202

AD30

VCCP203

AF21

VCCP204

Y24

VCCP205

AK14

VCCP206

J9

VCCP207

M27

VCCP208

AF14

VCCP209

J30

VCCP210

AG18

VCCP211

AA8

VCCP212

AG8

VCCP213

AL29

VCCP214

AD29

VCCP215

W8

VCCP216

AH8

VCCP217

N24

VCCP218

AN22

VCCP219

J14

VCCP220

K26

VCCP221

AF19

VCCP222

N8

VCCP223

AF12

VCCP224

M28

VCCP225

AK9

VCCP226

C10

VSS1

D12

VSS2

Y2

VSS3

C24

VSS4

K2

VSS5

C22

VSS6

AN1

VSS7

B14

VSS8

K7

VSS9

AE16

VSS10

B11

VSS11

AL10

VSS12

AK23

VSS13

H12

VSS14

AF7

VSS15

AK7

VSS16

H7

VSS17

E14

VSS18

L28

VSS19

Y5

VSS20

E11

VSS21

AL16

VSS22

AL24

VSS23

AK13

VSS24

D21

VSS26

AL20

VSS27

D18

VSS28

AN2

VSS29

AK16

VSS30

AK20

VSS31

AM27

VSS32

AM1

VSS33

AL13

VSS34

AL17

VSS35

C19

VSS36

E28

VSS37

AK30

VSS39

D24

VSS40

LGA_775

LGA_775

SOCKET_LGA775_DIP

SOCKET_LGA775_DIP

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

AL23

A12

L25

J7

AE28

AE29

K5

J4

AE30

AN20

AF10

AE24

AM24

AN23

H9

H8

H13

AC6

AC7

AH6

C16

AM16

AE25

AE27

AJ28

F19

AH13

AD7

AH16

AK17

E17

AH17

AH20

AE5

AH23

AE7

AM13

AH24

AJ30

AJ10

AF3

AK5

AJ16

AF6

AK29

AJ17

F22

AH3

AK10

AM10

F16

AJ23

F13

AG7

F10

L26

AD4

H11

L24

L23

AM23

A15

AH10

B24

L3

H27

A21

AE2

AJ29

AK27

AK28

B20

AM20

H26

B17

H25

H24

AA3

AA7

H23

AA6

H10

BLACK

BLACK

SK1G

SK1G

H22

VSS126

H21

VSS127

H20

VSS128

H19

VSS129

H18

VSS130

AB7

VSS131

H17

VSS132

AJ24

VSS133

AM17

VSS134

AC3

VSS135

H14

VSS136

P28

VSS137

V6

VSS138

AK2

VSS139

P27

VSS140

P26

VSS141

AM28

VSS142

AJ13

VSS143

W4

VSS144

P25

VSS145

AJ20

VSS146

W7

VSS147

P23

VSS148

AG13

VSS149

AG16

VSS150

AG17

VSS151

C7

VSS152

L30

VSS154

L29

VSS155

D15

VSS156

AL27

VSS157

Y7

VSS158

L27

VSS159

AA29

VSS160

N6

VSS161

N7

VSS162

AA28

VSS163

AN13

VSS164

AA27

VSS165

AA26

VSS166

P4

VSS167

AA25

VSS168

AA24

VSS169

P7

VSS170

E26

VSS171

V30

VSS172

R2

VSS173

V29

VSS174

V28

VSS175

R5

VSS176

V27

VSS177

R7

VSS178

E20

VSS179

AN10

VSS180

V25

VSS181

T3

VSS182

V24

VSS183

V23

VSS184

T6

VSS185

E25

VSS187

R29

VSS189

R28

VSS190

R27

VSS191

R26

VSS192

R25

VSS193

U7

VSS194

R24

VSS195

R23

VSS196

P30

VSS197

V3

VSS198

P29

VSS199

AF16

VSS200

AE10

VSS201

AF13

VSS202

H6

VSS203

A18

VSS204

A2

VSS205

E2

VSS206

D9

VSS207

C4

VSS208

A6

VSS209

D6

VSS210

LGA_775

LGA_775

SOCKET_LGA775_DIP

SOCKET_LGA775_DIP

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

D5

A9

D3

B1

B5

B8

AJ4

AE26

AH1

V7

C13

AK24

AB30

L6

L7

AB29

M1

AB28

E8

AG20

AN17

AB27

AB26

AN16

M7

AB25

AB24

AB23

N3

AA30

F4

AG10

AE13

AF30

H28

F7

AF29

AF28

AF27

AF26

AF25

AN28

AN27

AF24

AF23

AG24

AF17

AN24

H3

P24

AE20

AE17

E27

T7

R30

AJ27

AB1

AM4

V26

AA23

AL28

AF20

AG23

BLACK

BLACK

1206

1206

VCCP

1206

1206

VCCP

C64

C64

10U

10U

X5R

X5R

16V-1206

16V-1206

C31

C31

10U

10U

X5R

X5R

16V-1206

16V-1206

1206

1206

1206

1206

C88

C88

10U

10U

1206

1206

1206

1206

X5R

X5R

16V-1206

16V-1206

VTT12

VTT12

CAD NOTE :

TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MIL

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

C69

C69

10U

10U

X5R

X5R

16V-1206

16V-1206

C104

C104

10U

10U

X5R

X5R

16V-1206

16V-1206

C61

C61

10U

10U

X5R

X5R

16V-1206

16V-1206

L7 10UH

L7 10UH

SHORT

SHORT

1206

1206

C74

C74

C73

C73

10U

10U

10U

10U

1206

1206

X5R

X5R

X5R

X5R

16V-1206

16V-1206

16V-1206

16V-1206

C32

C32

10U

10U

1206

1206

X5R

X5R

16V-1206

16V-1206

PLL SUPPLY FILTER

C55

C55

10U

10U

1206

1206

X5R

X5R

16V-1206

16V-1206

0805

0805

C14

C14

1U

1U

25V

25V

Y5V

Y5V

C70

C70

10U

10U

1206

1206

X5R

X5R

16V-1206

16V-1206

H_VCCIOPLL 4

H_VCCA 4

H_VSSA 4

1206

1206

C53

C53

10U

10U

X5R

X5R

16V-1206

16V-1206

Title

Title

Title

P4-775 PART B

P4-775 PART B

P4-775 PART B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Lakeport CRB

Lakeport CRB

Lakeport CRB

1

1.4

1.4

1.4

5 30Wednesday, July 09, 2008

5 30Wednesday, July 09, 2008

5 30Wednesday, July 09, 2008

Page 6

5

K42

N32

N34

M38

N37

M36

R34

N35

N38

U37

N39

R37

P42

R39

R38

U36

U33

R35

Y34

Y36

Y38

Y39

AA37

G43

M34

U34

M43

M40

G35

H33

G27

H27

G29

B38

D38

E33

W40

Y40

W41

T43

Y43

U42

AA42

W42

G39

U40

U41

AA41

U39

C31

J42

L39

J40

L37

L36

V36

V33

V35

V42

V38

F40

L35

L38

J37

L40

J33

V41

H_A[3..35]

H_D[0..63]

H_REQ[0..4]

U6B

U6B

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADSTB0#

HADSTB1#

HDSTBP0#

HDSTBN0#

HDINV0#

HDSTBP1#

HDSTBN1#

HDINV1#

HDSTBP2#

HDSTBN2#

HDINV2#

HDSTBP3#

HDSTBN3#

HDINV3#

HADS#

HTRDY#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HRS0#

HRS1#

HRS2#

HCPURST#

946GZ(PL)

946GZ(PL)

VTT12

U1MCH

U1MCH

FSB

FSB

HSWING

HRCOMP

HSCOMP

HSCOMP#

HDVREF

HACCVREF

1 OF 7

1 OF 7

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HCLKP

HCLKN

R40

P41

R41

N40

R42

M39

N41

N42

L41

J39

L42

J41

K41

G40

F41

F42

C42

D41

F38

G37

E42

E39

E37

C39

B39

G33

A37

F33

E35

K32

H32

B34

J31

F32

M31

E31

K31

G31

K29

F31

J29

F29

L27

K27

H26

L26

J26

M26

C33

C35

E41

B41

D42

C40

D35

B40

C38

D37

B33

D33

C34

B35

A32

D32

B25

D23

C25

D25

D24

B24

R32

U32

H_D0

H_D1

H_D2

H_D3

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

H_D32

H_D33

H_D34

H_D35

H_D36

H_D37

H_D38

H_D39

H_D40

H_D41

H_D42

H_D43

H_D44

H_D45

H_D46

H_D47

H_D48

H_D49

H_D50

H_D51

H_D52

H_D53

H_D54

H_D55

H_D56

H_D57

H_D58

H_D59

H_D60

H_D61

H_D62

H_D63

MCH_SWING

MCH_RCOMP

MCH_SCOMP

MCH_SCOMPB

MCH_GTLREF0

H_A[3..35]4

H_D[0..63]4

H_REQ[0..4]4

H_A3

H_A4

H_A5

H_A6

D D

C C

H_ADSTB04

H_ADSTB14

H_STBP04

H_STBN04

H_DBI04

H_STBP14

H_STBN14

H_DBI14

H_STBP24

H_STBN24

H_DBI24

H_STBP34

H_STBN34

H_DBI34

H_ADS#4

H_TRDY#4

H_DRDY#4

H_DEFER#4

B B

H_HITM#4

H_HIT#4

H_LOCK#4

H_BREQ0#4

H_BNR#4

H_BPRI#4

H_DBSY#4

H_RS0#4

H_RS1#4

H_RS2#4

H_CPURST#4

H_A7 H_D4

H_A8

H_A9

H_A10

H_A11

H_A12

H_A13

H_A14

H_A15

H_A16

H_A17

H_A18

H_A19

H_A20

H_A21

H_A22

H_A23

H_A24

H_A25

H_A26

H_A27

H_A28

H_A29

H_A30

H_A31

H_A32

H_A33

H_A34

H_A35

H_REQ0

H_REQ1

H_REQ2

H_REQ3

H_REQ4

4

GEXP_RXP_012

GEXP_RXN_012

GEXP_RXP_112

GEXP_RXN_112

GEXP_RXP_212

GEXP_RXN_212

GEXP_RXP_312

GEXP_RXN_312

GEXP_RXP_412

GEXP_RXN_412

GEXP_RXP_512

GEXP_RXN_512

GEXP_RXP_612

GEXP_RXN_612

GEXP_RXP_712

GEXP_RXN_712

GEXP_RXP_812

GEXP_RXN_812

GEXP_RXP_912

GEXP_RXN_912

GEXP_RXP_1012

GEXP_RXN_1012

GEXP_RXP_1112

GEXP_RXN_1112

GEXP_RXP_1212

GEXP_RXN_1212

GEXP_RXP_1312

GEXP_RXN_1312

GEXP_RXP_1412

GEXP_RXN_1412

GEXP_RXP_1512

GEXP_RXN_1512

DMI_TXP014

DMI_TXN014

DMI_TXP114

DMI_TXN114

DMI_TXP214

DMI_TXN214

DMI_TXP314

DMI_TXN314

CK_PE_MCH_P3

V1.3

CK_PE_MCH_N3

1%

1%

R548 220R548 220

R561 220R561 220

SDVO_DATA12

SDVO_CLK12

PLACED AS CLOSE

AS POSSIBLE TO THE GMCH

R200 16.5_1%

R200 16.5_1%

CK_H_MCH_P 3

CK_H_MCH_N 3

U6A

U6A

F15

EXP_RXP0

G15

EXP_RXN0*

K15

EXP_RXP1

J15

EXP_RXN1*

F12

EXP_RXP2

E12

EXP_RXN2*

J12

EXP_RXP3

H12

EXP_RXN3*

J11

EXP_RXP4

H11

EXP_RXN4*

F7

EXP_RXP5

E7

EXP_RXN5*

E5

EXP_RXP6

F6

EXP_RXN6*

C2

EXP_RXP7

D2

EXP_RXN7*

G6

EXP_RXP8

G5

EXP_RXN8*

L9

EXP_RXP9

L8

EXP_RXN9*

M8

EXP_RXP10

M9

EXP_RXN10*

M4

EXP_RXP11

L4

EXP_RXN11*

M5

EXP_RXP12

M6

EXP_RXN12*

R9

EXP_RXP13

R10

EXP_RXN13*

T4

EXP_RXP14

R4

EXP_RXN14*

R6

EXP_RXP15

R7

EXP_RXN15*

W2

DMI_RXP0

V1

DMI_RXN0*

Y8

DMI_RXP1

Y9

DMI_RXN1*

AA7

DMI_RXP2

AA6

DMI_RXN2*

AB3

DMI_RXP3

AA4

DMI_RXN3*

B12

GCLKP

B13

GCLKN*

G17

SDVO_CTRLDATA

E17

SDVO_CTRLCLK

946GZ(PL)

946GZ(PL)

3

U1MCH

U1MCH

D11

D12

B11

A10

C10

D9

B9

B7

D7

D6

B5

B6

B3

B4

F2

E2

F4

G4

J4

K3

L2

K1

N2

M2

P3

N4

R2

P1

U2

T2

V3

U4

V7

V6

W4

Y4

AC8

AC9

Y2

AA2

AC11

AC12

GEXP_TXP_0 12

GEXP_TXN_0 12

GEXP_TXP_1 12

GEXP_TXN_1 12

GEXP_TXP_2 12

GEXP_TXN_2 12

GEXP_TXP_3 12

GEXP_TXN_3 12

GEXP_TXP_4 12

GEXP_TXN_4 12

GEXP_TXP_5 12

GEXP_TXN_5 12

GEXP_TXP_6 12

GEXP_TXN_6 12

GEXP_TXP_7 12

GEXP_TXN_7 12

GEXP_TXP_8 12

GEXP_TXN_8 12

GEXP_TXP_9 12

GEXP_TXN_9 12

GEXP_TXP_10 12

GEXP_TXN_10 12

GEXP_TXP_11 12

GEXP_TXN_11 12

GEXP_TXP_12 12

GEXP_TXN_12 12

GEXP_TXP_13 12

GEXP_TXN_13 12

GEXP_TXP_14 12

GEXP_TXN_14 12

GEXP_TXP_15 12

GEXP_TXN_15 12

0603

0603

0603

0603

EXP_COMP

VCC1_25

Close to

pin D27

0603

0603

0603

0603

0603

0603

0603

0603

0603

0603

C157

C157

X220P

X220P

16V

16V

X7R

X7R

EXP_TXP0

EXP_TXN0*

EXP_TXP1

EXP_TXN1*

EXP_TXP2

EXP_TXN2*

EXP_TXP3

EXP_TXN3*

EXP_TXP4

EXP_TXN4*

EXP_TXP5

EXP_TXN5*

EXP_TXP6

EXP_TXN6*

EXP_TXP7

EXP_TXN7*

EXP_TXP8

EXP_TXN8*

EXP_TXP9

PCIE

PCIE

EXP_TXN9*

EXP_TXP10

EXP_TXN10*

EXP_TXP11

EXP_TXN11*

EXP_TXP12

EXP_TXN12*

EXP_TXP13

EXP_TXN13*

EXP_TXP14

EXP_TXN14*

EXP_TXP15

EXP_TXN15*

DMI_TXP0

DMI_TXN0*

DMI_TXP1

DMI_TXN1*

DMI_TXP2

DMI

DMI

DMI_TXN2*

DMI_TXP3

DMI_TXN3*

EXP_COMPO

EXP_COMPI

2 OF 7

2 OF 7

R119 4.7K/6R119 4.7K/6

DMI_TXP0

R120 4.7K/6R120 4.7K/6

DMI_TXP1

R121 4.7K/6R121 4.7K/6

DMI_TXP2

R122 4.7K/6R122 4.7K/6

DMI_TXP3

V1.1

GTLREF VOLTAGE SHOULD BE 0.63 x VTT = 0.75V

VTT12

R203

R203

124_1%

124_1%

1%

1%

R197 51R197 51

C160

C160

1%

1%

R199

R199

0.1U

0.1U

0603

0603

16V

16V

Y5V

Y5V

210_1%

210_1%

DMI_RXP0 14

DMI_RXN0 14

DMI_RXP1 14

0603

0603

DMI_RXN1 14

DMI_RXP2 14

DMI_RXN2 14

DMI_RXP3 14

0603

0603

DMI_RXN3 14

R243

R243

24.9_1%

24.9_1%

VCC1_25

R320

R320

1K/6/1

1K/6/1

R321

R321

392/6/1

392/6/1

1%

1%

R152 0R152 0

CPU_FSA3,4

CPU_FSB3,4

CPU_FSC3,4

R223 1KR223 1K

R221

R221

EXP_EN_HDR12

VCC1_25

0.352V

C501 0.1U 16VY5V

C501 0.1U 16VY5V

C502 0.1U 16VY5V

C502 0.1U 16VY5V

C504 0.1U 16VY5V

C504 0.1U 16VY5V

C505 0.1U 16VY5V

C505 0.1U 16VY5V

C506 0.1U 16VY5V

C506 0.1U 16VY5V

C508 0.1U 16VY5V

C508 0.1U 16VY5V

VCC1_25PCIEX

PLTRST#12,15,17,19,23

MCH_GTLREF0

MCH_CPU_GTLREF 4

2

R201 10KR201 10K

R206 10KR206 10K

R212 10KR212 10K

EXP_SLR

X1K

X1K

R217 0R217 0

-CL_RST

PWROK115,23

C503 0.1U 16VY5V

C503 0.1U 16VY5V

C507 0.1U 16VY5V

C507 0.1U 16VY5V

R322 1.65K/6/1R322 1.65K/6/1

G20

K20

F20

G18

E18

K17

H18

N17

N18

N15

M20

M18

AD12

AD13

AM5

AA12

AM15

AA10

AA9

AA11

Y12

U30

U31

R29

R30

U12

U11

R12

R13

J20

J18

J17

L17

L15

L18

U6E

U6E

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

RESERVED_24

EXP_SLR

RESERVED_25

EXP_EN

RESERVED

RESERVED_1

RESERVED_2

RESERVED_3

RESERVED_4

RESERVED_5

RESERVED_6

RESERVED_7

RESERVED_8

RESERVED_28

RESERVED_27

VREF2

V_1P25_PLTRST#

PWROK2

RESERVED_9

RESERVED_10

RESERVED_11

RESERVED_12

RESERVED_13

RESERVED_14

RESERVED_15

RESERVED_16

RESERVED_17

RESERVED_18

RESERVED_19

RESERVED_20

946GZ(PL)

946GZ(PL)

R323

R323

1K/6/1

1K/6/1

-CL_RST

M_PWOK

RESERVED_001

RESERVED_23

RESERVED_26

MISC VGA

MISC VGA

5 OF 7

5 OF 7

0603

0603

DDC_DATA

DREFCLKP

DREFCLKN

ICH_SYNC#

C18

C18

10P

10P

16V

16V

Y5V

Y5V

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREEN#

BLUE#

DDC_CLK

REFSET

VCC

VSS

RSTIN#

PWROK

TEST0

TEST1

TEST2

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

VCC3

1%

1%

NC

R8

R8

1K

1K

1

C15

D15

B18

C19

B20

C18

D19

D20

L13

M13

R220

R220

A20

C14

D13

L12

M11

F13

F17

A14

AM18

M_PWOK

AM17

J13

A42

BC43

BC1

A43

N20

BC42

BC2

BB43

BB1

B43

B42

B2

ICH_SYNC# 15

HSYNC 13

VSYNC 13

RED 13

GREEN 13

BLUE 13

DDC_DATA 13

DDC_CLK 13

1%

R0603

1%

R0603

1.3K_1%

1.3K_1%

CK_DOT96_P 3

CK_DOT96_N 3

VCC1_25

PLTRST# 12,15,17,19,23

ICH_SYNC# 15

PWROK1 15,23

PLEASE

CLOSE TO

MCH

R209

R209

301_1%

301_1%

1%

1%

A A

0603

0603

C162

C162

0.01U

0.01U

16V

16V

Y5V

Y5V

R205 49.9_1%R205 49.9_1%

R210

R210

1%

1%

100_1%

100_1%

MCH_SWING

CAD NOTE :

HD_SWING Voltage

routed 10 mils / 7mils

TRACE

0.22 x VTT

5

4

VTT12

R211

R211

49.9_1%

49.9_1%

VTT12

R11

1%

1%

0603

0603

MCH_SCOMP MCH_SCOMPB

C161

C161

X2.2P

X2.2P

50V

50V

X7R

X7R

PLEASE DRIVER

RESISTORS

NEAR VTT

3

R11

49.9_1%

49.9_1%

1%

1%

C3

C3

X2.2P

X2.2P

0603

0603

50V

50V

X7R

X7R

2

Title

Title

Title

MCH LAKEPORT PART A

MCH LAKEPORT PART A

MCH LAKEPORT PART A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Lakeport CRB

Lakeport CRB

Lakeport CRB

1

6 30Wednesday, July 09, 2008

6 30Wednesday, July 09, 2008

6 30Wednesday, July 09, 2008

1.4

1.4

1.4

Page 7

5

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_WE_A9,11

M_CAS_A9,11

M_RAS_A9,11

MCH_VREF

C197

C197

0.1U

0.1U

16V

16V

Y5V

Y5V

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14 M_MAA_B14

PLACE

0.1UF CAP

CLOSE TO

MCH

D D

M_SBA_A09,11

M_SBA_A19,11

M_SBA_A29,11

M_SCS_A09,11

M_SCS_A19,11

M_SCS_A2

M_SCS_A3

M_SCKE_A09,11

M_SCKE_A19,11

M_SCKE_A2

M_SCKE_A3

M_SODT_A09,11

M_SODT_A19,11

M_SODT_A2

M_SODT_A3

VCCDDR

1%

1%

1%

1%

CK_M_DDR_P_A09

CK_M_DDR_N_A09

CK_M_DDR_P_A19

CK_M_DDR_N_A19

CK_M_DDR_P_A29

CK_M_DDR_N_A29

CK_M_DDR_P_A3

CK_M_DDR_N_A3

CK_M_DDR_P_A4

CK_M_DDR_N_A4

CK_M_DDR_P_A5

CK_M_DDR_N_A5

0603

0603

CAD NOTES :

PLASE CLOSE TO MCH

5

C C

B B

R295

R295

1K-1%

1K-1%

R294

R294

1K-1%

1K-1%

A A

BA31

BB25

BA26

BA25

AY25

BA23

AY24

AY23

BB23

BA22

AY33

BB22

AW21

AY38

BA21

BB34

AY35

BB33

BA33

AW32

BB21

AW35

BA35

BA34

BB38

BC20

AY20

AY21

BA19

AY37

BA38

BB35

BA39

AU31

AR31

AP27

AN27

AV33

AW33

AP29

AP31

AM26

AM27

AT33

AU33

AN21

U6C

U6C

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SMA_A14

SWE_A#

SCAS_A#

SRAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A0#

SCS_A1#

RESERVED_11

RESERVED_12

SCKE_A0

SCKE_A1

RESERVED_9

RESERVED_10

SODT_A0

SODT_A1

RESERVED_2

RESERVED_1

SCLK_A0

SCLK_A0#

SCLK_A1

SCLK_A1#

SCLK_A2

SCLK_A2#

RESERVED_3

RESERVED_4

RESERVED_5

RESERVED_6

RESERVED_7

RESERVED_8

DDR_0

DDR_0

RESERVED

3 OF 7

3 OF 7

U1MCH

U1MCH

946GZ(PL)

946GZ(PL)

SDQS_A0

SDQS_A0#

SDM_A0

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDQS_A1

SDQS_A1#

SDM_A1

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQS_A2

SDQS_A2#

SDM_A2

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_A23

SDQS_A3

SDQS_A3#

SDM_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDQS_A4#

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDQS_A5#

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDQS_A6#

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDQS_A7#

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

4

AU4

AR3

AR2

AR5

AR4

AV3

AV2

AP3

AP2

AU1

AV4

BB3

BA4

BA2

AY2

AY3

BB5

AY6

AW2

AW3

BA5

BB4

BB9

BA9

AY9

AY7

BC7

AW11

AY11

BB6

BA6

BA10

BB10

AT20

AU18

AN18

AT18

AR18

AU21

AT21

AP17

AN17

AP20

AV20

AR41

AR40

AU43

AV42

AU40

AP42

AN39

AV40

AV41

AR42

AP41

AL41

AL40

AM43

AN41

AM39

AK42

AK41

AN40

AN42

AL42

AL39

AG42

AG41

AG40

AJ40

AH43

AF39

AE40

AJ42

AJ41

AF41

AF42

AC42

AC41

AC40

AD40

AD43

AB41

AA40

AE42

AE41

AC39

AB42

4

M_DQS_P_A0

M_DQS_N_A0

M_DQM_A0

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DQS_P_A1

M_DQS_N_A1

M_DQM_A1

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DQS_P_A2

M_DQS_N_A2

M_DQM_A2

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DQS_P_A3

M_DQS_N_A3

M_DQM_A3

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DQS_P_A4

M_DQS_N_A4

M_DQM_A4

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DQS_P_A5

M_DQS_N_A5

M_DQM_A5

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DQS_P_A6

M_DQS_N_A6

M_DQM_A6

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DQS_P_A7

M_DQS_N_A7

M_DQM_A7

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

VCCDDR

0603

0603

R285

R285

R287

R287

C223

C223

0.1U

0.1U

16V

16V

Y5V

Y5V

20_1%

20_1%

20_1%

20_1%

3

M_SCKE_B010,11

M_SCKE_B110,11

M_SCKE_B2

M_SCKE_B3

M_SODT_B010,11

M_SODT_B110,11

M_SODT_B2

M_SODT_B3

CK_M_DDR_P_B010

CK_M_DDR_N_B010

CK_M_DDR_P_B110

CK_M_DDR_N_B110

CK_M_DDR_P_B210

CK_M_DDR_N_B210

CK_M_DDR_P_B3

CK_M_DDR_N_B3

CK_M_DDR_P_B4

CK_M_DDR_N_B4

CK_M_DDR_P_B5

CK_M_DDR_N_B5

M_WE_B10,11

M_CAS_B10,11

M_RAS_B10,11

M_SBA_B010,11

M_SBA_B110,11

M_SBA_B210,11

M_SCS_B010,11

M_SCS_B110,11

M_SCS_B2

M_SCS_B3

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

BB17

AY17

BA17

BC16

AW15

BA15

BB15

BA14

AY15

BB14

AW18

BB13

BA13

AY29

AY13

BA27

AW29

AW26

AY19

BA18

BC12

BB27

BB30

AY27

AY31

AY12

AW12

BB11

BA11

BA29

BA30

BB29

BB31

AV31

AW31

AU27

AT27

AV32

AT32

AU29

AR29

AV29

AW27

AN33

AP32

SMA_B0

SMA_B1

SMA_B2

SMA_B3

SMA_B4

SMA_B5

SMA_B6

SMA_B7

SMA_B8

SMA_B9

SMA_B10

SMA_B11

SMA_B12

SMA_B13

SMA_B14

SWE_B#

SCAS_B#

SRAS_B#

SBS_B0

SBS_B1

SBS_B2

SCS_B0#

SCS_B1#

RESERVED_13

RESERVED_10

SCKE_B0

SCKE_B1

RESERVED_11

RESERVED_12

SODT_B0

SODT_B1

RESERVED_14

RESERVED_15

SCLK_B0

SCLK_B0#

SCLK_B1

SCLK_B1#

SCLK_B2

SCLK_B2#

RESERVED_16

RESERVED_17

RESERVED_18

RESERVED_19

RESERVED_20

RESERVED_21

U6D

U6D

U1MCH

U1MCH

SDQS_B0#

SDQS_B1#

SDQS_B2#

SDQS_B3#

SDQS_B4#

BB2

RESERVED_1

AW42

RESERVED_2

AN32

RESERVED_3

AM31

RESERVED_4

AG32

RESERVED_5

AF32

RESERVED_6

AP21

RESERVED_9

AA39

MCH_VREF

AM21

AM6

RESERVED_8

DDR_1

DDR_1

RESERVED_7

SVREF

SDQS_B5#

SDQS_B6#

SDQS_B7#

SMRCOMP0

AN2

1%

1%

1%

1%

1%

1%

R286

R286

20_1%

20_1%

3

1%

1%

SMRCOMPVOL

SMRCOMPVOH

R288

R288

20_1%

20_1%

SMRCOMP1

SMRCOMP2

SMRCOMP3

AN3

BB40

BA40

AM8

AM10

BB19

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

SMRCOMPVOL

SMRCOMPVOH

RESERVED

4 OF 7

4 OF 7

946GZ(PL)

946GZ(PL)

SDQS_B0

SDM_B0

SDQ_B0

SDQ_B1

SDQ_B2

SDQ_B3

SDQ_B4

SDQ_B5

SDQ_B6

SDQ_B7

SDQS_B1

SDM_B1

SDQ_B8

SDQ_B9

SDQ_B10

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_B14

SDQ_B15

SDQS_B2

SDM_B2

SDQ_B16

SDQ_B17

SDQ_B18

SDQ_B19

SDQ_B20

SDQ_B21

SDQ_B22

SDQ_B23

SDQS_B3

SDM_B3

SDQ_B24

SDQ_B25

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_B30

SDQ_B31

SDQS_B4

SDM_B4

SDQ_B32

SDQ_B33

SDQ_B34

SDQ_B35

SDQ_B36

SDQ_B37

SDQ_B38

SDQ_B39

SDQS_B5

SDM_B5

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQS_B6

SDM_B6

SDQ_B48

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQS_B7

SDM_B7

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

SDQ_B63

2

AV6

AU5

AR7

AN7

AN8

AW5

AW7

AN5

AN6

AN9

AU7

AR12

AP12

AW9

AT11

AU11

AP13

AR13

AR11

AU9

AV12

AU12

AP15

AR15

AW13

AU15

AV13

AU17

AT17

AU13

AM13

AV15

AW17

AT24

AU26

AP23

AV24

AT23

AT26

AP26

AU23

AW23

AR24

AN26

AW39

AU39

AU37

AW37

AV38

AN36

AN37

AU35

AR35

AN35

AR37

AL35

AL34

AM37

AM35

AM38

AJ34

AL38

AR39

AM34

AL37

AL32

AG35

AG36

AG39

AG38

AJ38

AF35

AF33

AJ37

AJ35

AG33

AF34

AC36

AC37

AD38

AD36

AC33

AA34

AA36

AD34

AF38

AC34

AA33

2

M_DQS_P_B0

M_DQS_N_B0

M_DQM_B0

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DQS_P_B1

M_DQS_N_B1

M_DQM_B1

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DQS_P_B2

M_DQS_N_B2

M_DQM_B2

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DQS_P_B3

M_DQS_N_B3

M_DQM_B3

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DQS_P_B4

M_DQS_N_B4

M_DQM_B4

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DQS_P_B5

M_DQS_N_B5

M_DQM_B5

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DQS_P_B6

M_DQS_N_B6

M_DQM_B6

M_DATA_B48

M_DATA_B49

M_DATA_B50

M_DATA_B51

M_DATA_B52

M_DATA_B53

M_DATA_B54

M_DATA_B55

M_DQS_P_B7

M_DQS_N_B7

M_DQM_B7

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

1

M_MAA_A[0..14]

M_DQS_P_A[0..7]

M_DQS_N_A[0..7]

M_DQM_A[0..7]

M_DATA_A[0..63]

M_MAA_B[0..14]

M_DQS_P_B[0..7]

M_DQS_N_B[0..7]

M_DQM_B[0..7]

M_DATA_B[0..63]

VCCDDR

R283

R283

1K-1%

1K-1%

R12

R12

3.01K-1%

3.01K-1%

R284

R284

1K-1%

1K-1%

Title

Title

Title

MCH LAKEPORT PART B

MCH LAKEPORT PART B

MCH LAKEPORT PART B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_MAA_A[0..14] 9,11

M_DQS_P_A[0..7] 9

M_DQS_N_A[0..7] 9

M_DQM_A[0..7] 9

M_DATA_A[0..63] 9

M_MAA_B[0..14] 10,11

M_DQS_P_B[0..7] 10

M_DQS_N_B[0..7] 10

M_DQM_B[0..7] 10

M_DATA_B[0..63] 10

SMRCOMPVOH

1%

1%

0603

0603

1%

1%

SMRCOMPVOL

1%

1%

0603

0603

Lakeport CRB

Lakeport CRB

Lakeport CRB

1

C196

C196

0.01U

0.01U

16V

16V

Y5V

Y5V

C11

C11

0.01U

0.01U

16V

16V

Y5V

Y5V

PLACE

0.1UF CAP

CLOSE TO

MCH

7 30Wednesday, July 09, 2008

7 30Wednesday, July 09, 2008

7 30Wednesday, July 09, 2008

1.4

1.4

1.4

Page 8

5

VCCDQ_CRT

VCCD_CRT

AD5

AD4

AD2

AD1

AC4

AC3

AC2

AE4

AE3

AE2

C17

B16

A16

C21

B21

D D

C C

B B

A A

D16

VSS_1

VCCA_EXP

VCCD_CRT

VCCDQ_CRT

VCC_EXP_16

VCCA_DAC_17

VCCA_DAC_18

6 OF 7

6 OF 7

VCC_SMCLK_3

VCC_SMCLK_4

VCC_SMCLK_5

RESERVED_1

RESERVED_2

AJ32

AL31

BA42

AY42

BB42

BA43

V_CKDDR

VCC1_25 VCC1_25PCIEX

R261 X0-SHORT

R261 X0-SHORT

L1206_S

L1206_S

SHORT

SHORT

VCC3

FB6

FB6

30_OHM-0805

30_OHM-0805

FB0805_S

FB0805_S

SHORT

SHORT

VCC1_25

VCC1_25

0603

0603

CAPS FOR SPECIFIC CORE MCH

VCCDDR

C221

C221

C156

C156

0.1U

0.1U

0.1U

0.1U

0603

0603

0603

0603

16V

16V

16V

16V

Y5V

Y5V

Y5V

Y5V

VCCDDR

C176

C176

0805

2.2UF

0805

2.2UF

Y5V

Y5V

16V-0805

16V-0805

MCH MEMORY DECOUPLING

VCC_EXP_10

VCC_EXP_11

VCC_EXP_12

VCC_EXP_13

VCC_EXP_14

VCC_EXP_15

VCC2_248

VCC2_249

VCC_SMCLK_1

VCC_SMCLK_2

AL29

AL27

BB41

0603

0603

PCI EXPRESS FILTER

EC29

EC29

+

+

100UF

100UF

25V

25V

ECD-6-2_5

ECD-6-2_5

C224

C224

0603

0603

0.1U

0.1U

16V

16V

Y5V

Y5V

0805

0805

VCC_EXP_9

VCC2_247

AL13

AK14

R13

R13

0/6

0/6

Y5V

Y5V

0603

0603

C198

C198

0.1U

0.1U

16V

16V

Y5V

Y5V

C147

C147

2.2UF

2.2UF

Y5V

Y5V

16V-0805

16V-0805

VCC_EXP_8

VCC2_246

VCC_EXP_7

VCC2_245

U27

C4

C4

0.1U16V

0.1U16V

C179

C179

0.1U

0.1U

16V

16V

Y5V

Y5V

VCC1_25PCIEX

AD8

AD7

AD6

VCC_EXP_4

VCC_EXP_5

VCC_EXP_6

VCC2_242

VCC2_243

VCC2_244

V30

V29

U29

0805

0805

0603

0603

0603

0603

C261

C261

10U

10U

0805

0805

10V

10V

Y5V

Y5V

C154

C154

0805

2.2UF

0805

2.2UF

Y5V

Y5V

16V-0805

16V-0805

AD10

AD9

VCC_EXP_3

VCC2_241

Y30

Y29

C205

C205

10U

10U

10V

10V

Y5V

Y5V

VCC3_DAC

C181

C181

0.01U

0.01U

16V

16V

Y5V

Y5V

C257

C257

0.1U

0.1U

16V

16V

Y5V

Y5V

VCC_EXP_2

VCC2_240

VCC3_DACVCC3_DAC

R140/6 R140/6

VCCDDR

BC39

BC34

BC30

BC26

BC22

BC18

BC14

BB39

BB37

BB32

BB28

BB26

BB24

BB20

BB18

BB16

BB12

AY32

AW24

AW20

AV26

AV18

AD11

VCCSM_1

VCCSM_2

VCCSM_3

VCCSM_4

VCCSM_5

VCCSM_6

VCCSM_7

VCCSM_8

VCCSM_9

VCCSM_10

VCCSM_11

VCCSM_12

VCCSM_13

VCCSM_14

VCCSM_15

VCCSM_16

VCCSM_17

VCCSM_18

VCCSM_19

VCCSM_20

VCCSM_21

VCCSM_22

VCC_EXP_1

VCC2_217

VCC2_218

VCC2_219

VCC2_220

VCC2_221

VCC2_222

VCC2_223

VCC2_224

VCC2_225

VCC2_226

VCC2_227

VCC2_228

VCC2_229

VCC2_230

VCC2_231

VCC2_232

VCC2_233

VCC2_234

VCC2_235

VCC2_236

VCC2_237

VCC2_238

VCC2_239

Y31

AK3

AK2

AK1

AJ13

AJ26

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AJ15

AJ14

AA30

AA29

C146

C146

0.1U

0.1U

0603

0603

16V

16V

Y5V

Y5V

VTT12

AA31

AC31

0805

0805

C158

C158

0805

10U

0805

10U

Y5V

Y5V

10V-0805

10V-0805

AK20

AK18

AK17

AK15

AD31

The plane must be split at the edge of the package

and be separate under the MCH

VCC1_25

C266

C266

C191

C191

10U

10U

10U

10U

0805

0805

6.3V

6.3V

Y5V

Y5V

Y5V

Y5V

10V-0805

10V-0805

C150

C150

0805

0805

0805

10U

0805

10U

Y5V

Y5V

10V-0805

10V-0805

R23

AK21

R24

VTT_45

VTT_46

VCC2_215

VCC2_216

AK23

C145

C145

10U

10U

Y5V

Y5V

10V-0805

10V-0805

4

VTT12

N26

N24

N23

M29

M24

M23

L24

L23

K24

K23

J24

J23

H24

H23

G26

G24

G23

F26

F24

F23

E29

E27

E26

E23

D29

D28

D27

C30

C29

C27

B30

B29

B28

B27

A30

A28

R27

R26

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_30

VTT_31

VTT_32

VTT_33

VTT_34

VTT_35

VTT_36

VTT_37

VTT_38

VTT_39

VTT_40

VTT_41

VTT_42

VTT_43

VTT_44

VCC2_177

VCC2_178

VCC2_179

VCC2_180

VCC2_181

VCC2_182

VCC2_183

VCC2_184

VCC2_185

VCC2_186

VCC2_187

VCC2_188

VCC2_189

VCC2_190

VCC2_191

VCC2_192

VCC2_193

VCC2_194

VCC2_195

VCC2_196

VCC2_197

VCC2_198

VCC2_199

VCC2_200

VCC2_201

VCC2_202

VCC2_203

VCC2_204

VCC2_205

VCC2_206

VCC2_207

VCC2_208

VCC2_209

VCC2_210

VCC2_211

VCC2_212

VCC2_213

VCC2_214

AL9

AL8

AL7

AL6

AL5

AL4

AL3

AL2

AK26