ZMD U631H64BSC45, U631H64BSC35, U631H64BSC25, U631H64SC25, U631H64BDK45 Datasheet

...

Features

p

High-performance CMOS nonvolatile static RAM 8192 x 8 bits

p

25, 35 and 45 ns Access Times

p

12, 20 and 25 ns Output Enable

Access Times

p

Software STORE Initiation

(STORE Cycle Time < 10 ms)

p

Automatic STORE Timing

p

105 STORE cycles to EEPROM

p

10 years data retention in

EEPROM

p

Automatic RECALL on Power Up

p

Software RECALL Initiation

(RECALL Cycle Time < 20 µs)

p

Unlimited RECALL cycles from

EEPROM

p

Unlimited Read and Write to

SRAM

p

Single 5 V ± 10 % Operation

p

Operating temperature ranges:

p

CECC 90000 Quality Standard

p

ESD characterization according

MIL STD 883C M3015.7-HBM

(classification see IC Code

Numbers)

0 to 70 °C

-40 to 85 °C

p

Packages:PDIP28 (300 mil)

SOP28 (330 mil)

Description

The U631H64 has two separate

modes of operation: SRAM mode

and nonvolatile mode. In SRAM

mode, the memory operates as an

ordinary static RAM. In nonvolatile

operation, data is transferred in

parallel from SRAM to EEPROM or

from EEPROM to SRAM. In this

mode SRAM functions are disabled.

The U631H64 is a fast static RAM

(25, 35, 45 ns), with a nonvolatile

electrically erasable PROM

(EEPROM) element incorporated

in each static memory cell. The

SRAM can be read and written an

unlimited number of times, while

independent nonvolatile data resides in EEPROM. Data transfers

from the SRAM to the EEPROM

(the STORE operation), or from the

EEPROM to the SRAM (the

RECALL operation) are initiated

through software sequences.

U631H64

SoftStore

The U631H64 combines the high

performance and ease of use of a

fast SRAM with nonvolatile data

integrity.

Once a STORE cycle is initiated,

further input or output are disabled

until the cycle is completed.

Because a sequence of addresses

is used for STORE initiation, it is

important that no other read or write

accesses intervene in the sequence

or the sequence will be aborted.

Internally, RECALL is a two step

procedure. First, the SRAM data is

cleared and second, the nonvolatile

information is transferred into the

SRAM cells.

The RECALL operation in no way

alters the data in the EEPROM

cells. The nonvolatile data can be

recalled an unlimited number of

times.

8K x 8 nvSRAM

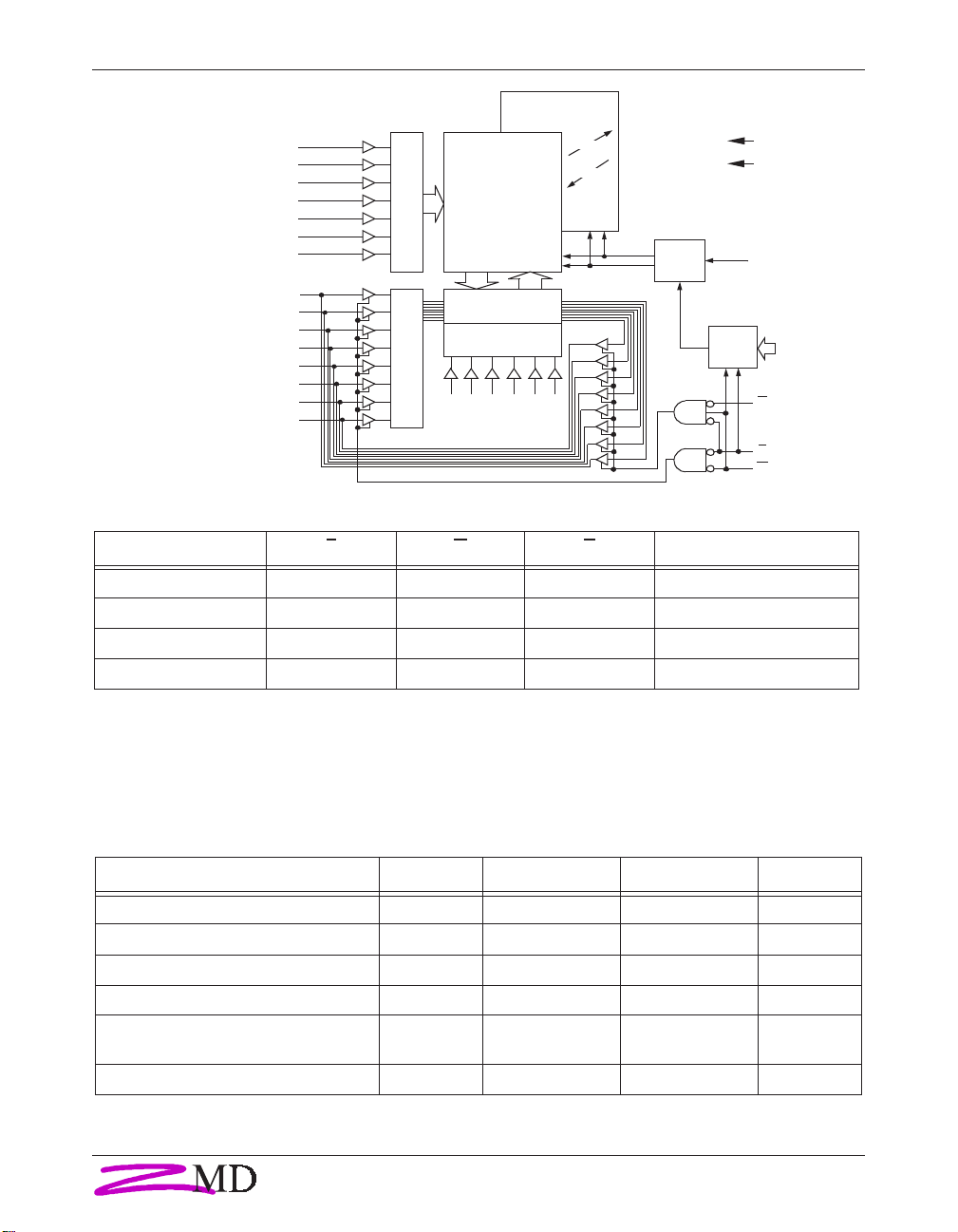

Pin Configuration Pin Description

PDIP

SOP

28

VCC

27

W

26

n.c.

25

A8

24

A9

23

A11

22

G

21

A10

20

E

19

DQ7

18

DQ6

17

DQ5

16

DQ4

15

DQ3

Signal Name Signal Description

A0 - A12 Address Inputs

DQ0 - DQ7 Data In/Out

E

G

W

VCC Power Supply Voltage

VSS Ground

1

1

n.c.

2

A12

3

A7

4

A6

5

A5

6

A4

7

A3

8

A2

9

A1

10

A0

11

DQ0

12

DQ1

13

DQ2

14

VSS

Top View

December 12, 1997

Chip Enable

Output Enable

Write Enable

U631H64

Block Diagram

A5

A6

A7

A8

A9

A11

A12

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

64 x 8 Columns

Row Decoder

Column Decoder

Input Buffers

A0 A1 A2 A3 A4A10

EEPROM Array

Array

128 Rows x

Column I/O

128 x (64 x 8)

STORE

RECALLSRAM

Store/

Recall

Control

Software

Detect

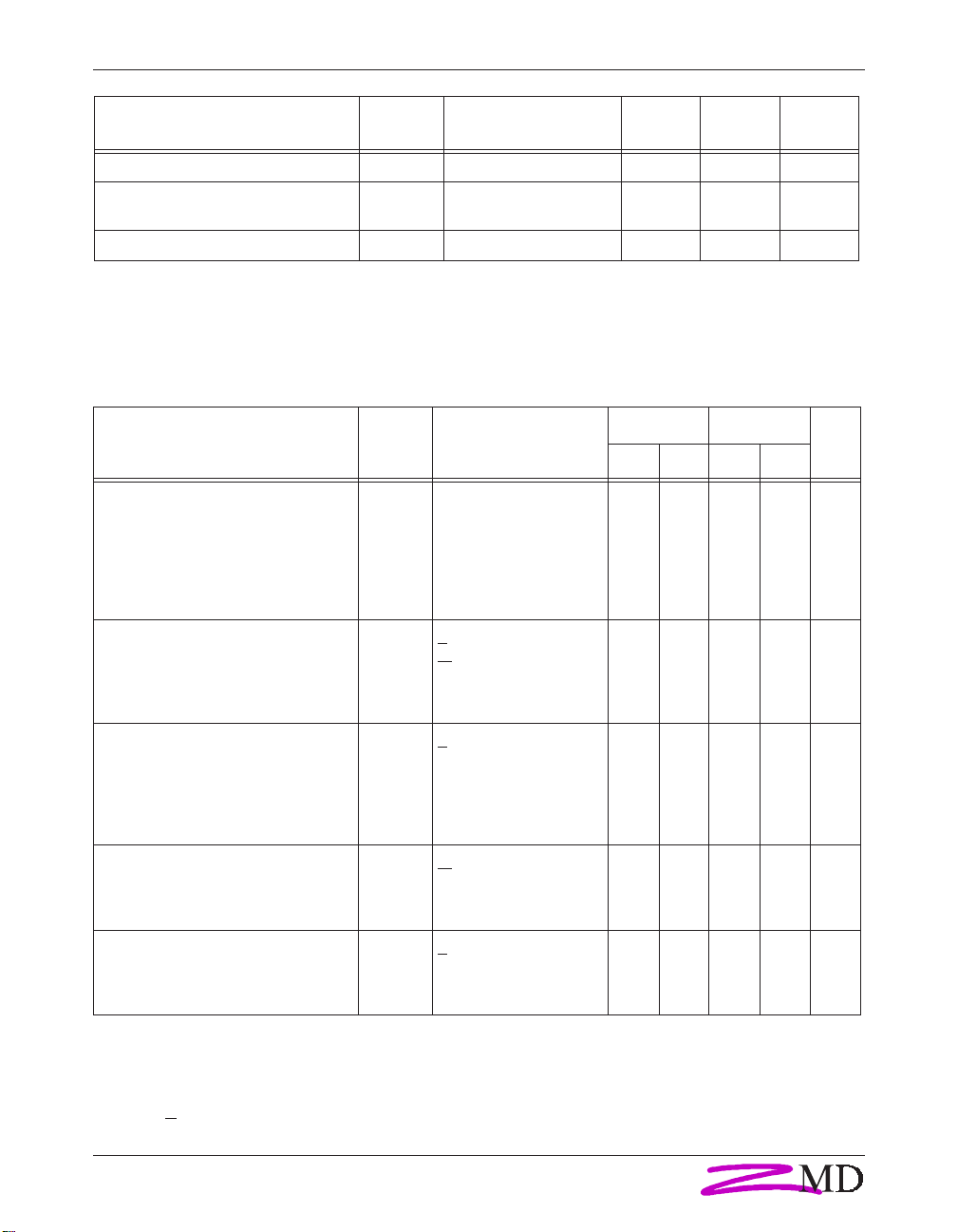

Truth Table for SRAM Operations

Operating Mode E W G DQ0 - DQ7

Standby/not selected H

**

Internal Read L H H High-Z

Read L H L Data Outputs Low-Z

Write L L

*

Data Inputs High-Z

*H or L

V

V

V

G

E

W

High-Z

CC

SS

CC

A0 - A12

Characteristics

All voltages are referenced to VSS = 0 V (ground).

All characteristics are valid in the power supply voltage range and in the operating temperature range specified.

Dynamic measurements are based on a rise and fall time of ≤ 5 ns, measured between 10 % and 90 % of V

input levels of V

with the exception of the t

Absolute Maximum Rating

Power Supply Voltage V

Input Voltage V

Output Voltage V

Power Dissipation P

Operating Temperature C-Type

Storage Temperature T

a:Stresses greater than those listed under „Absolute Maximum Ratings“ may cause permanent damage to the device. This is a stress

rating only, and functional operation of the device at condition above those indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

= 0 V and VIH = 3 V. The timing reference level of all input and output signals is 1.5 V,

IL

-times and ten-times, in which cases transition is measured ± 200 mV from steady-state voltage.

dis

a

K-Type

Symbol Min. Max. Unit

CC

I

O

D

T

a

stg

-0.5 7 V

-0.3 VCC+0.5 V

-0.3 VCC+0.5 V

0

-40

-65 150 °C

2

,as well as

I

1W

70

85

°C

°C

December 12, 1997

U631H64

Recommended Operation

Conditions

Power Supply Voltage V

Input Low Voltage V

Input High Voltage V

Symbol Conditions Min. Max. Unit

CC

-2 V at Pulse Width

IL

10 ns permitted

IH

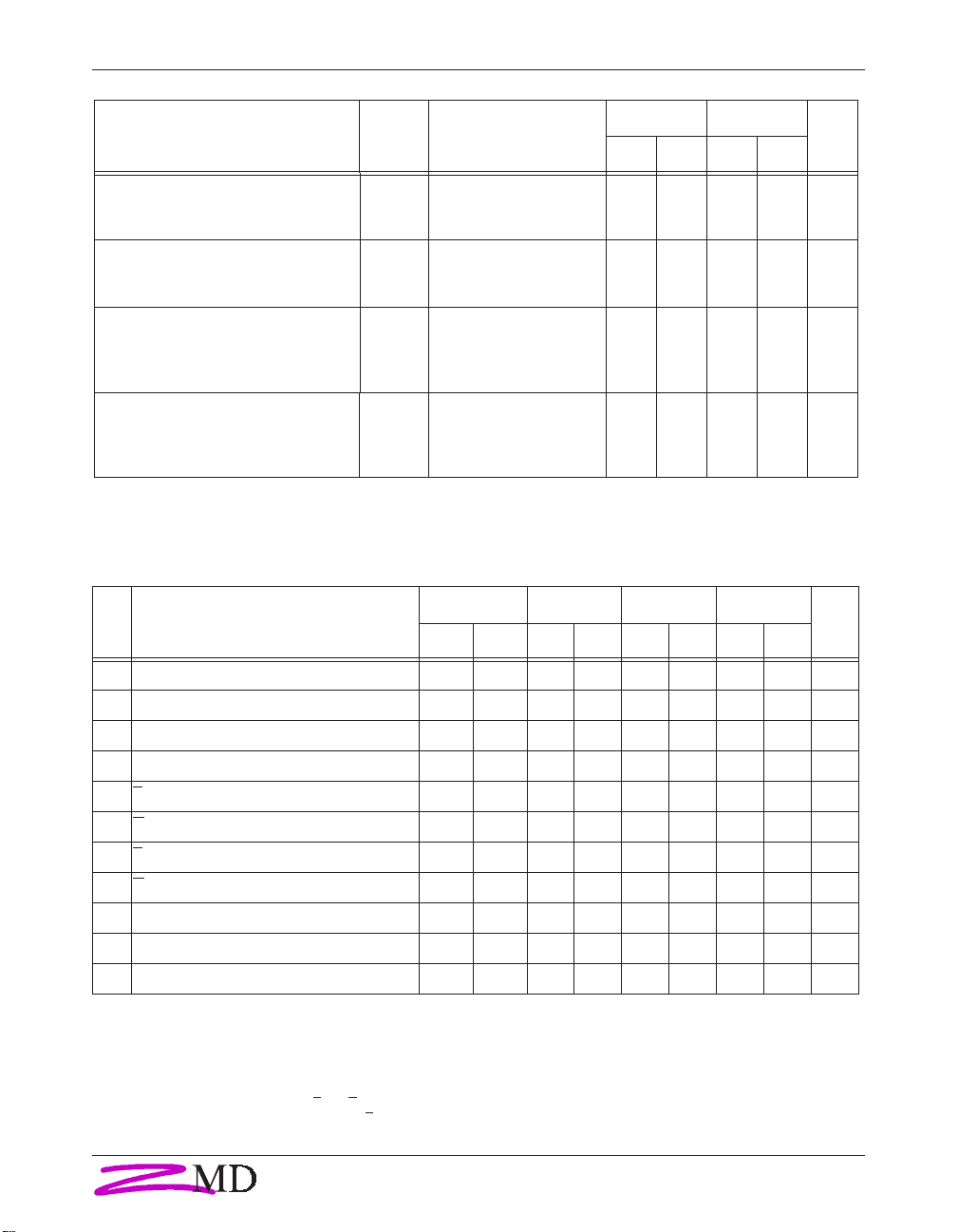

DC Characteristics Symbol Conditions

Operating Supply Current

Average Supply Current during

c

STORE

Standby Supply Current

(Cycling TTL Input Levels)

b

d

I

V

CC1

V

V

t

t

t

V

I

CC2

E

W

V

V

I

CC(SB)1VCC

E

= 5.5 V

CC

= 0.8 V

IL

= 2.2 V

IH

= 25 ns

c

= 35 ns

c

= 45 ns

c

= 5.5 V

CC

≥ V

-0.2 V

CC

≥ V

-0.2 V

CC

≤ 0.2 V

IL

≥ V

IH

CC

-0.2 V

= 5.5 V

≥ V

IH

4.5 5.5 V

-0.3 0.8 V

2.2 VCC+0.3 V

C-Type K-Type

Min. Max. Min. Max.

90

80

75

95

85

80

67mA

Unit

mA

mA

mA

t

= 25 ns

c

= 35 ns

t

c

= 45 ns

t

c

Average Supply Current

at t

= 200 ns

cR

(Cycling CMOS Input Levels)

Standby Supply Current

(Stable CMOS Input Levels)

b:I

and I

CC1

The current I

c:I

is the average current requird for the duration of the STORE cycle (STORE Cycle Time).

CC2

d: Bringing E

table. The current I

b

d

are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

CC3

is measured for WRITE/READ - ratio of 1/2.

CC1

≥ VIH will not produce standby current levels until any nonvolatile cycle in progress has timed out. See MODE SELECTION

is measured for WRITE/READ - ratio of 1/2.

CC(SB)1

I

CC(SB)

December 12, 1997

I

CC3

V

= 5.5 V

CC

≥ V

W

≤ 0.2 V

V

IL

≥ V

V

IH

V

= 5.5 V

CC

≥ V

E

≤ 0.2 V

V

IL

≥ V

V

IH

3

CC

CC

CC

CC

-0.2 V

-0.2 V

-0.2 V

-0.2 V

30

23

20

34

27

23

mA

mA

mA

15 15 mA

11mA

U631H64

DC Characteristics Symbol Conditions

Output High Voltage

Output Low Voltage

Output High Current

Output Low Current

Input Leakage Current

Output Leakage Current

High at Three-State- Output

Low at Three-State- Output

High

Low

V

V

I

I

OH

OL

I

OH

I

OL

I

IH

I

IL

OHZ

OLZ

V

CC

I

OH

I

OL

V

CC

V

OH

V

OL

V

CC

V

IH

V

IL

V

CC

V

OH

V

OL

= 4.5 V

=-4 mA

= 8 mA

= 4.5 V

= 2.4 V

= 0.4 V 8

= 5.5 V

= 5.5 V

= 0 V -1

= 5.5 V

= 5.5 V

= 0 V -1

SRAM MEMORY OPERATIONS

Switching Characteristics

No.

Read Cycle

1 Read Cycle Time

2 Address Access Time to Data Valid

f

g

3 Chip Enable Access Time to Data Valid t

4 Output Enable Access Time to Data Valid t

5E

HIGH to Output in High-Z

6G

HIGH to Output in High-Z

h

h

7E LOW to Output in Low-Z t

8G

LOW to Output in Low-Z t

9 Output Hold Time after Addr. Change

g

10Chip Enable to Power Activee t

11Chip Disable to Power Standby

d, e

Symbol 25 35 45

Alt.IECMin.Max.Min.Max.Min.Max.

t

AVAVtcR

t

AVQVta(A)

ELQVta(E)

GLQVta(G)

t

EHQZtdis(E)

t

GHQZtdis(G)

ELQXten(E)

GLQXten(G)

t

AXQXtv(A)

t

ELICCH

t

EHICCL

PU

t

PD

C-Type K-Type

Unit

Min. Max. Min. Max.

2.4

0.4

-4

1

1

2.4

-1

-1

8

0.4VV

-4 mA

mA

1 µA

µA

1 µA

µA

Unit

25 35 45 ns

25 35 45 ns

25 35 45 ns

12 20 25 ns

13 17 20 ns

13 17 20 ns

555ns

000ns

333ns

000ns

25 35 45 ns

e: Parameter guaranteed but not tested.

f: Device is continuously selected with E

g:Address valid prior to or at the same time with E

h:Measured ± 200 mV from steady state output voltage.

and G both LOW.

transition LOW.

4

December 12, 1997

Loading...

Loading...