ZLG AN05320101 User Manual

AN

05320101

V1.00

Date:

2007/06/24

www.embedtools.com

Appplication

Note

FIFO 应用笔记

产品应用笔记

文件信息

类别

关键词 FIFO、FULL、控制器

摘要 介绍如何使用 ProASIC3/E 三种 FIFO,包括内部结

构、时序波形以及简单的实例

内容

广州致远电子有限公司

AN05320101

广州致远电子有限公司

FIFO

应用笔记

©200

7

Guangzhou ZHIYUAN

Date:

2007/06/

24

V1.00

修订历史

版本 日期 原因

V1.00 2007/06/24

创建文档。

产品应用手册

Electronics CO., LTD.

i

AN05320101

广州致远电子有限公司

FIFO

应用笔记

©200

7

Guangzhou ZHIYUAN

Date:

2007/06/

24

V1.00

目 录

1. 适用范围......................................................................................................................................1

2. 概述..............................................................................................................................................2

3. FIFO 的特点.................................................................................................................................3

3.1 FIFO 内部结构...................................................................................................................3

3.2 FIFO 控制器的内部信号...................................................................................................4

3.3 时序波形图........................................................................................................................6

4. 三种 FIFO 应用实例 ...................................................................................................................8

4.1 应用场合............................................................................................................................8

4.2 同步的 FIFO(内嵌硬件控制器) .................................................................................. 8

4.3 软 FIFO 控制器(带存储单元) ...................................................................................12

4.4 软 FIFO 控制器(不带存储单元) ...............................................................................16

5. 特别注意事项............................................................................................................................19

5.1 存储模块的匹配..............................................................................................................19

5.2 FIFO 标志的匹配.............................................................................................................19

5.3 读写的数据宽度匹配......................................................................................................19

6. 总结............................................................................................................................................20

7. 参考资料....................................................................................................................................21

8. 免责声明....................................................................................................................................22

9. 销售与服务网络........................................................................................错误!未定义书签。

产品应用手册

Electronics CO., LTD.

ii

AN05320101

广州致远电子有限公司

FIFO

应用笔记

©200

7

Guangzhou ZHIYUAN

Date:

2007/06/24

V1.00

1. 适用范围

此应用笔记适用于 Actel Flash 结构的 ProASIC3/E 系列的 FPGA,适用 Libero 7.3 和

Libero 8.0 IDE 开发环境。

产品应用手册

Electronics CO., LTD.

1/26

AN05320101

广州致远电子有限公司

FIFO

应用笔记

©200

7

Guangzhou ZHIYUAN

Date:

2007/06/24

V1.00

2. 概述

随着设计需求地增加,对存储器的要求也越来越高,很多地设计都需要使用 FIFO,Actel

的 FPGA 在这方面有独特的设计,为了迎合不同的客户需求,Actel 设计了三种类型的 FIFO,

分别是:内嵌硬件 FIFO 控制器的同步 FIFO、带有存储单元的软控制器的 FIFO、不带存储

单元的软控制器的 FIFO,第一种不占用逻辑资源,和 RAM 一起使用;第二种控制器用逻

辑资源搭建,存储器用内部的 RAM;第三种是独立的控制器,用逻辑资源搭建,不带有存

储单元,但有读写信号和地址信号输出。下面将会介绍这些 FIFO 的使用。

产品应用手册

Electronics CO., LTD.

2/26

AN05320101

广州致远电子有限公司

FIFO

应用笔记

©200

7

Guangzhou ZHIYUAN

Date:

2007/06/24

V1.00

RW[2:0]

WW[2:0]

3. FIFO 的特点

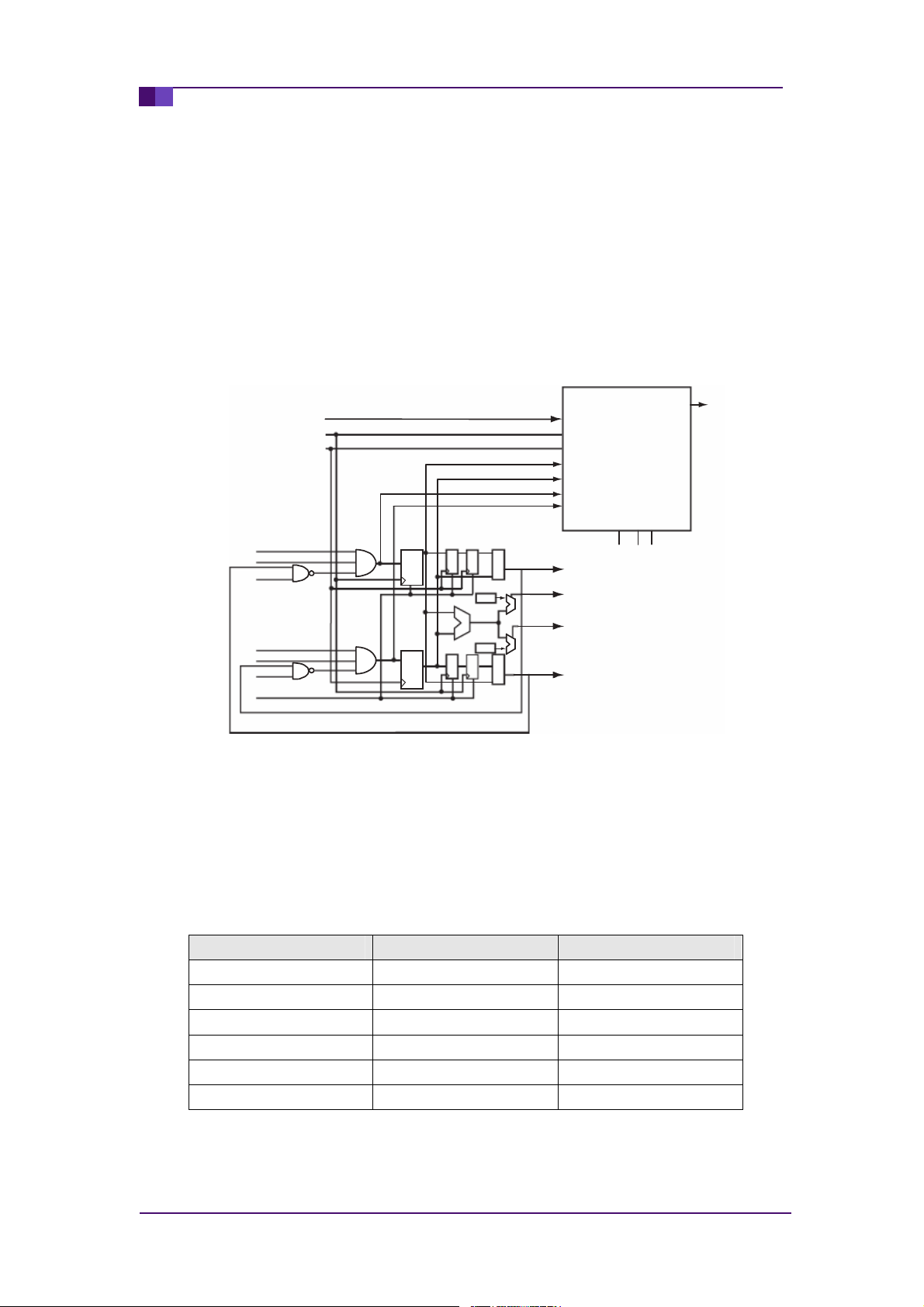

3.1 FIFO 内部结构

这里主要介绍内部带有硬件 FIFO 控制器的 FIFO 的结构,这是 Actel FPGA 的一大特点,

可以节省很多的资源,它和内部的 RAM 一起配合使用,每个 4K 的 RAM 块内部都带有 FIFO

控制器。当只作为 RAM 使用时,控制器被旁路;当用作 FIFO 使用时,控制器被使能,并

产生一些标志信号,例如:FULL、EMPTY、AFULL、AEMPTY 等,图 1 是带有控制器的

RAM 块的内部结构。

RD

RBLK

REN

ESTOP

WBLK

WEN

FSTOP

Reset

WD

RCLK

WCLK

FREN

FWEN

CNT 1

E

E

WD [17:0]

RCLK

WCLK

RADD [J:0]

WADD [J:0]

REN

WEN

=

AFVAL

AEVAL

SUB 1 2CNT 2

=

FULL

AFULL

AEMPTY

EMPTY

RD [17:0]

RAM

RPIPE

图 1 内嵌 FIFO 控制器的 RAM 块内部结构

FIFO 中的 RAM 块和一般的 RAM 的使用一样,只能是配置成 4,096×1,2048×2,1,024

×4,512×9,256×18 这 5 种模式,虽然软件里可以设置各种各样的宽度和深度比,但是

最终是用这几种模式中的一种来实现的,它是由控制器内部的 WW 和 RW 信号决定的,具

体见表 1 所示。

FIFO 的存储模块最高可以配置成 18 位的模式,所以在 FIFO 控制器的接口上预留有 18

位的数据接口,当使用的数据宽度达不到 18 位时,剩余的读写数据线必须接地。但是如果

产品应用手册

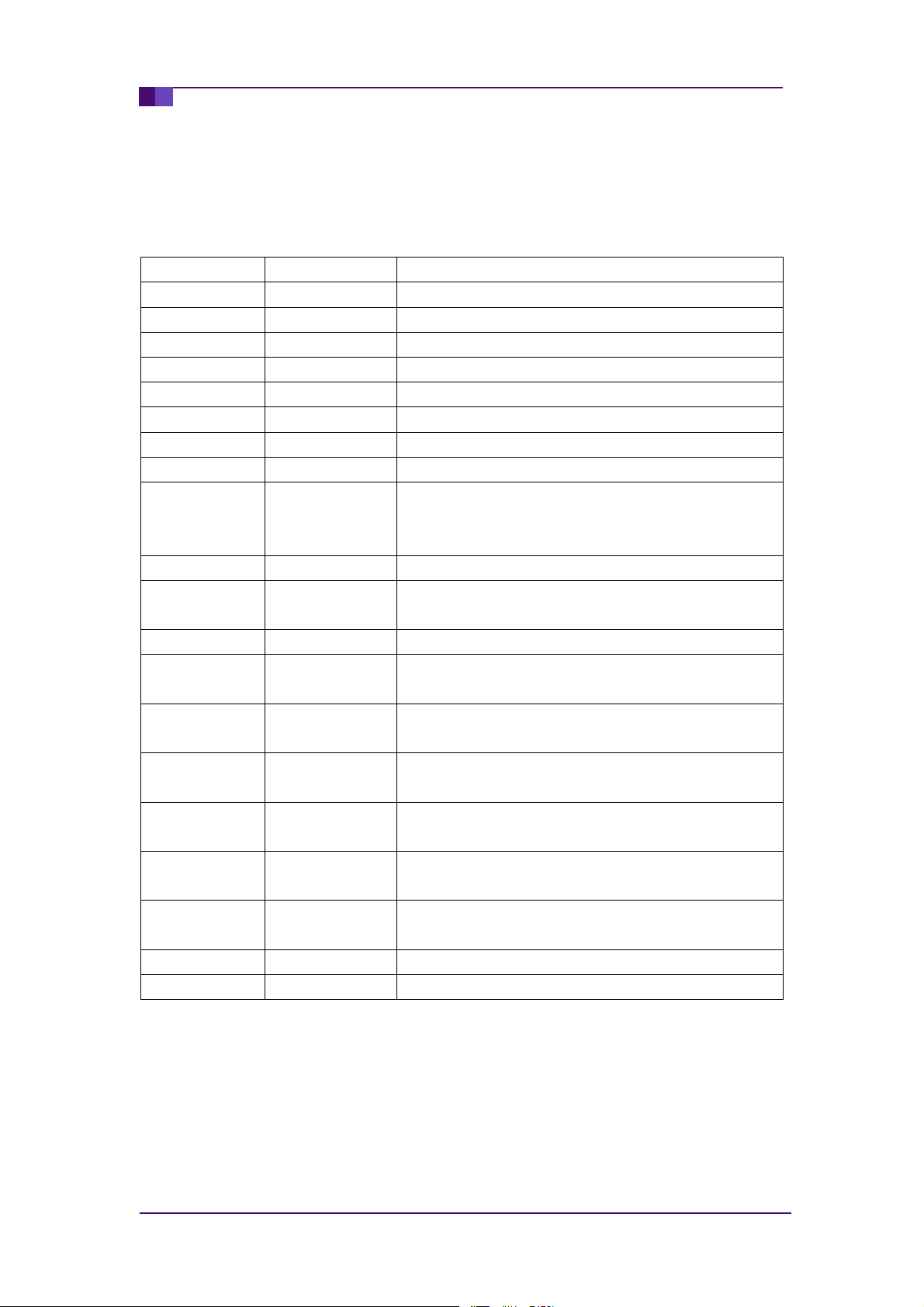

表 1 WW 和 RW 配置宽度深度比

WW2, WW1, WW0 RW2, RW1, RW0 DxW

000 000 4k×1

001 001 2k×2

010 010 1k×4

011 011 512×9

100 100 256×18

101, 110, 111 101, 110, 111 保留

Electronics CO., LTD.

3/26

AN05320101

广州致远电子有限公司

FIFO

应用笔记

©200

7

Guangzhou ZHIYUAN

Date:

2007/06/24

V1.00

是通过 SmartGen 软件生成的 FIFO,这些工作是 SmartGen 软件来自动完成;如果是直接例

化一个 FIFO,这些地方是我们必须手动设置,数据总线的使用情况如表 2 所示。

表 2 不同宽度深度比的数据信号的使用情况

DxW

4k×1 WD[17:1], RD[17:1]

2k×2 WD[17:2], RD[17:2]

1k×4 WD[17:4], RD[17:4]

512×9 WD[17:9], RD[17:9]

256×18 -

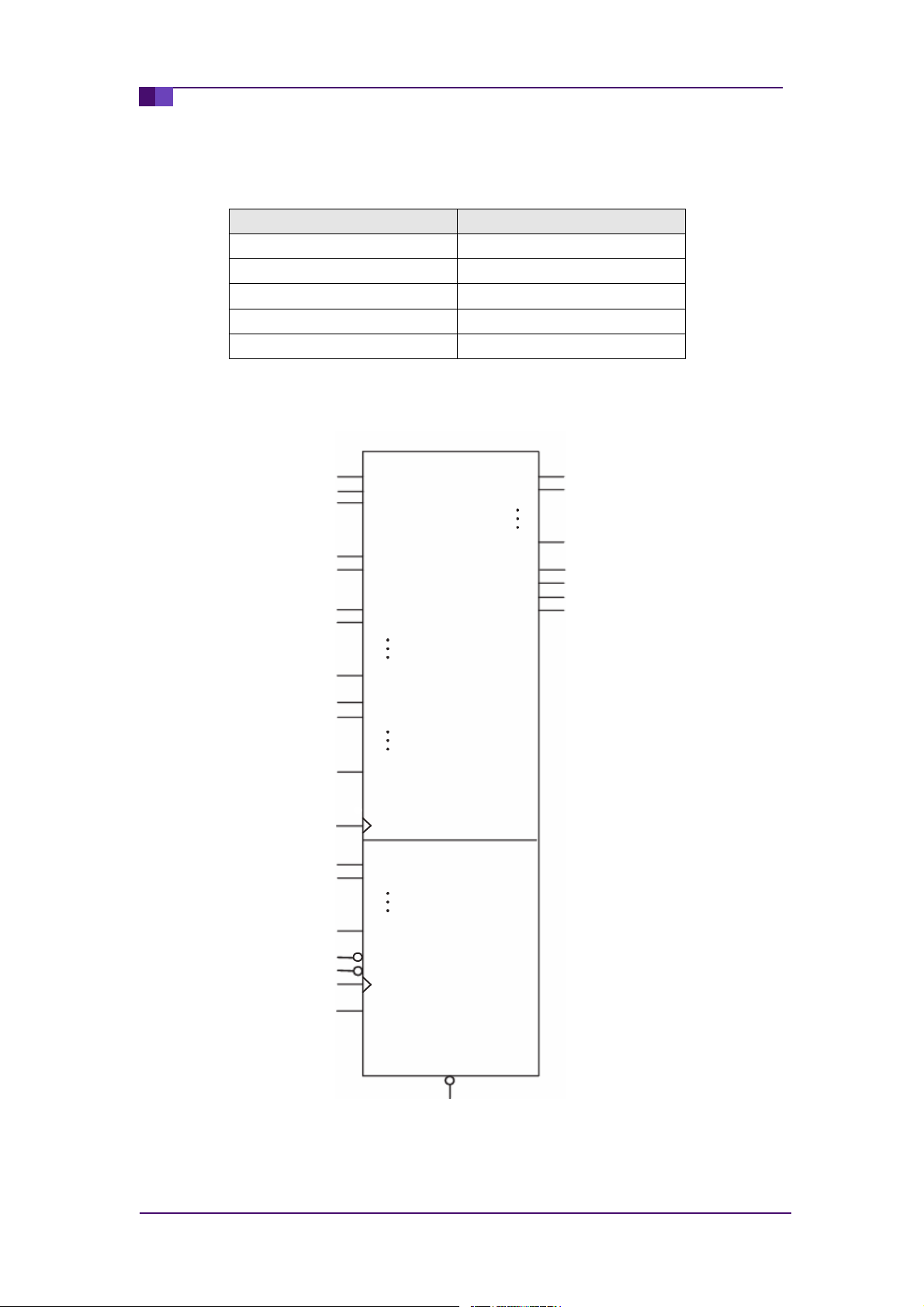

3.2 FIFO 控制器的内部信号

RW2

RW1

RW0

WW2

WW1

WW0

ESTOP

FSTOP

AEVAL11

AEVAL10

不使用的 WD/RD

FIFO4K18

RD17

RD16

RD0

FULL

AFULL

EMPTY

AEMPTY

AEVAL0

AFVAL11

AFVAL10

AFVAL0

REN

RBLK

RCLK

WD17

WD16

WD0

WEN

WBLK

WCLK

RPIPE

RESET

图 2 FIFO 控制器宏模块

产品应用手册

Electronics CO., LTD.

4/26

AN05320101

广州致远电子有限公司

FIFO

应用笔记

©200

7

Guangzhou ZHIYUAN

Date:

2007/06/24

V1.00

这是 FIFO 宏模块的内部接口信号,SmartGen 软件中的设置参数也是最终影响这些信号

来完成 FIFO 控制器的配置,我们在 SmartGen 软件生成时并不关心这些信号,但是用 HDL

例化的时候,我们必须非常的清楚这些信号的含义,如表 3 所示列出这些信号的含义,这

些信号的含义仅仅针对于内嵌硬件控制器的 FIFO 来说的,其他两种会有一定的区别。

表 3 FIFO 的控制信号

信号名称 I/O 类型 含义

WW[2:0] I 配置 FIFO 的写宽度和深度比,具体见表 1

RW[2:0] I 配置 FIFO 的读宽度和深度比,具体见表 1

WBLK I 写端口使能信号

RBLK I 读端口使能信号

WEN I 写使能信号,默认低有效,可以设置为高

REN I 读使能信号,默认低有效,可以设置为高

WCLK I 同步写数据时钟,可设置为上升或下降沿

RCLK I 同步读数据时钟,可设置为上升或下降沿

指定流水线的读,为低为非流水线的读,数据在一个时钟周

RPIPE I

RESET I 复位信号,低有效,将输出信号复位到零

WD I

RD O 输出数据总线,描述如上。

ESTOP I

FSTOP I

FULL O

EMPTY O

AFULL O

AEMPTY O

AFVAL I 指定近满标志的阀值,12 位可设置,可寻址 4096bits

AEVAL I 指定近空标志的阀值,12 位可设置,可寻址 4096bits

期内出现输出口上,高为流水线的读,数据出现在下个读时

钟周期上

输入数据总线,18 位宽,但当配置成不同模式的 RAM 块时,

这 18 位并非全部用到,不使用的信号必须接地

当 FIFO 为空时,该信号可以用来禁止读地址计数器继续计数

(高有效),否则读地址计数器将从零开始

当 FIFO 为满时,该信号可以来禁止写地址计数器继续计数(高

有效),否则写地址计数器将从零开始

当 FIFO 已满不能再写入数据时,该标志置高 ,保持两个时

钟周期时间,因为它需要和写地址进行比较

当 FIFO 已空不能再读取数据时,该标志置高,保持两个时钟

周期时间,因为它需要和读地址进行比较

近满标志,这和 AFVAL 的阀值有关,在写操作时,FIFO 存

放的数据到达了 AFVAL 设定的值时,该标志变成高电平

近空标志,这和 AEVAL 的阀值有关,在读操作时,FIFO 存

放的数据到达了 AEVAL 设定的值时,该标志变成高电平

产品应用手册

Electronics CO., LTD.

5/26

Loading...

Loading...