1

P

RELIMINARY

C

USTOMER

P

ROCUREMENT

S

PECIFICATION

FEATURES

ROM *

Device

Z87001 64 512 32 144-Pin QFP

Z87L01 64 512 32 144-Pin QFP

Note: *Maximum accessible external ROM

Transceiver/Controller Chip Optimized for Implement-

■

ation of 900 MHz Spread Spectrum Cordless Telephone

– Adaptive Frequency Hopping

– Transmit Power Control

– Error Control Signaling

– Handset Power Management

– Support of 32 kbps ADPCM Speech Coding for

(KWords)

High V oice Quality

RAM

(Words)

I/O

Lines

Package

Information

Z87001/Z87L01

ROM

C

■

■

■

■

LESS

ORDLESS

Transceiver Circuitry Provides Primary Cordless Phone

Communications Functions

– Digital Downconversion with Automatic Frequency

– FSK Demodulator

– FSK Modulator

– Symbol Synchronizer

– Time Division Duplex (TDD) Transmit and Receive

On-Chip A/D and D/A to Support 10.7 MHz IF Interface

Up to 64 Kw of External Program Memory Accessible by

the DSP Core

Bus Interface to Z87010 ADPCM Processor

S

PREAD

P

HONE

Control (AFC) Loop

Buffers

S

PECTRUM

C

ONTROLLER

1

■

DSP Core Acts as Phone Controller

– Zilog-Provided Embedded Transceiver Software to

Control Transceiver Operation and Base StationHandset Communications Protocol

– User-Modifiable Software Governs Telephone

Features

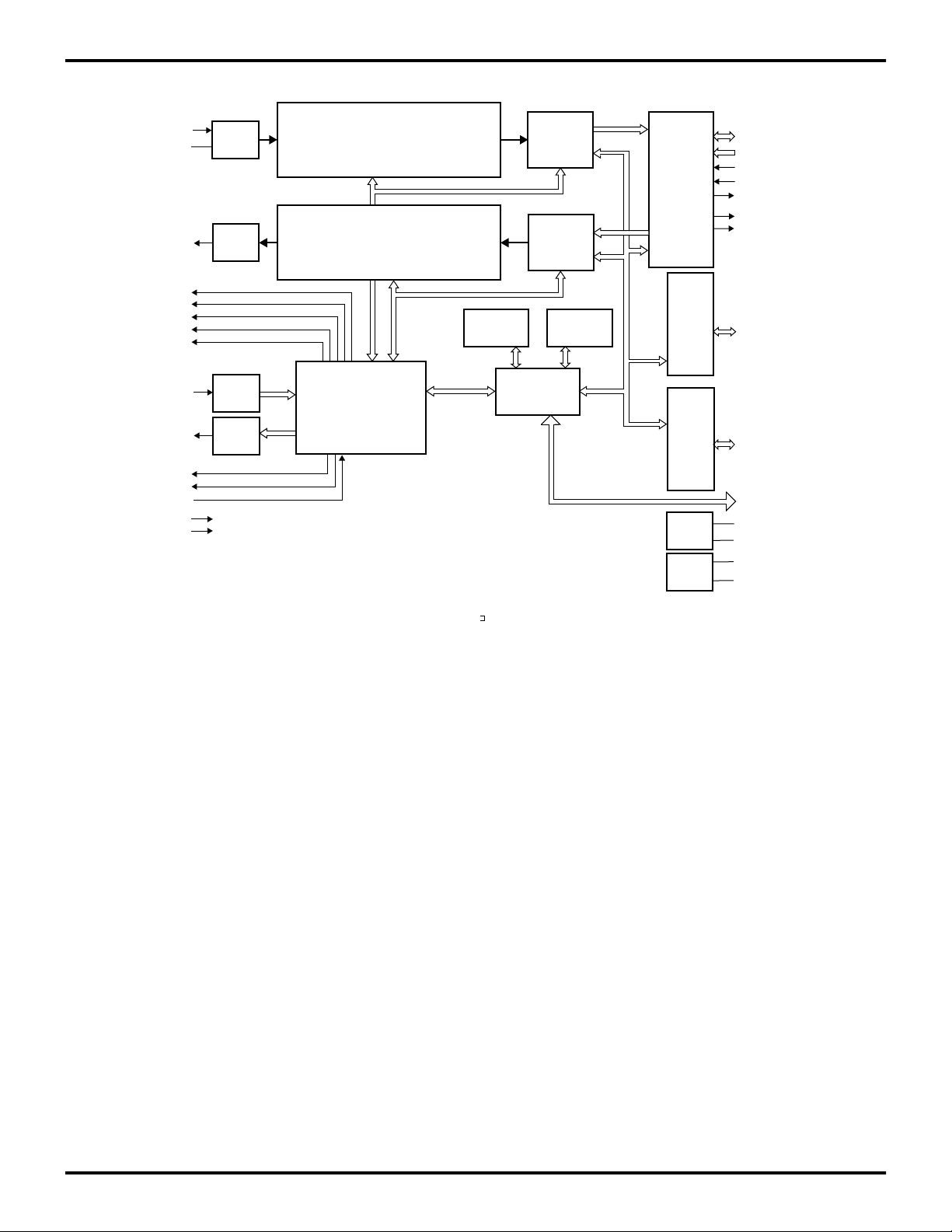

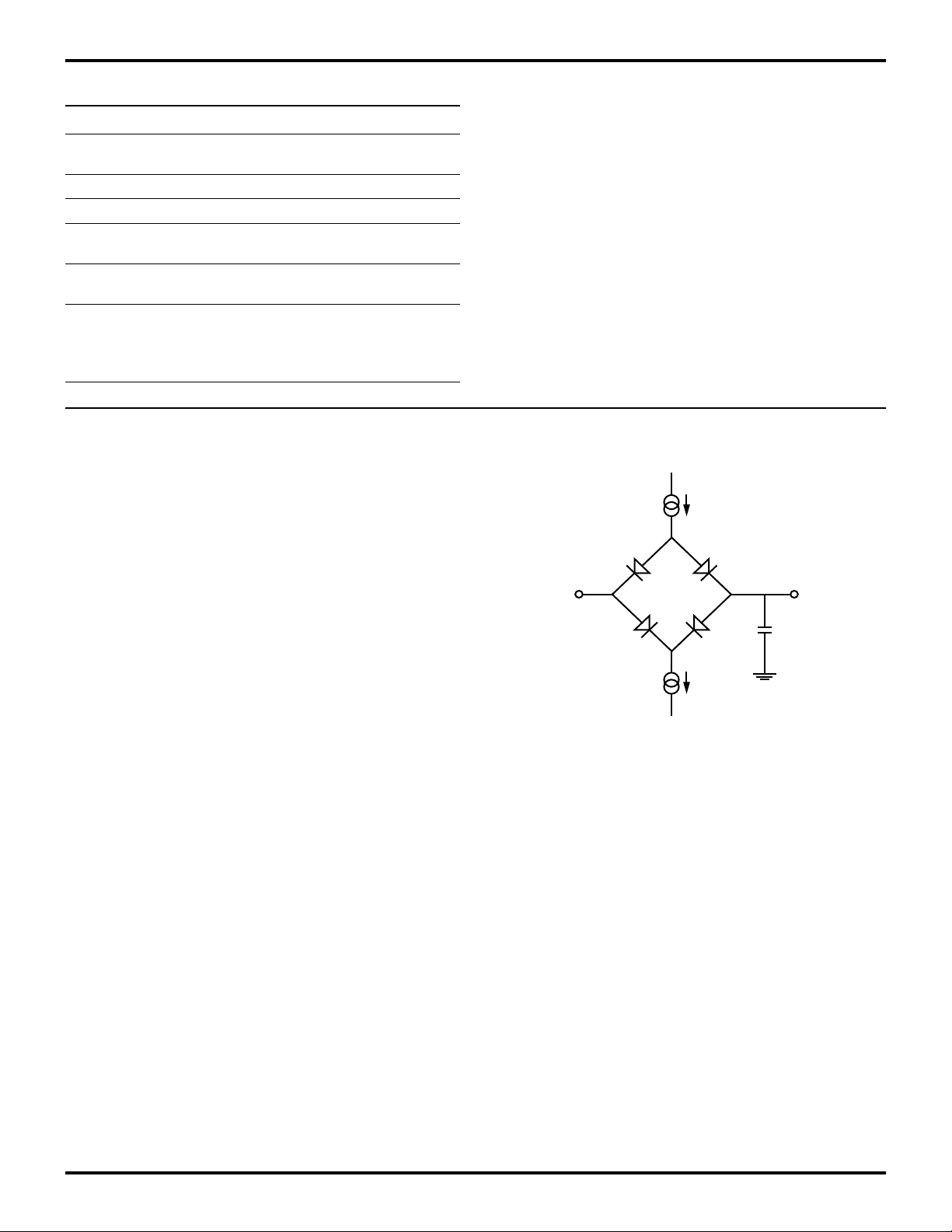

GENERAL DESCRIPTION

The Z87001 /Z87L01 FHSS Cordless Telephone Transceiver/Controller is expressly designed to implement a 900

MHz frequency hopping spread spectrum cordless telephone compliant with US FCC regulations for unlicensed

operation. The Z87001 and Z87L01 are distinct 5V and

3.3V versions, respectively, of the core device. For the

sake of brevity, all subsequent references to the Z87001 in

this document also apply to the Z87L01 unless specifically

noted.

The Z87001 is the ROMless version of the Z87000 Spread

Spectrum Controller IC. Specifically intended to facilitate

user specific software development, the Z87001 can access up to 64 kwords of external program ROM.

■

Static CMOS for Low Power Consumption

■

3.0V to 3.6V, -20 ° C to +70 ° C, Z87L01

4.5V to 5.5V, -20 ° C to +70 ° C, Z87001

■

16.384 MHz Base Clock

The Z87001 supports a specific cordless phone system

design that uses frequency hopping and digital modulation

to provide extended range, high voice quality, and low system costs.

The Z87001 uses a Zilog 16-bit fixed-point two’s complement static CMOS Digital Signal Processor core as the

phone and RF section controller. The Z87001’s DSP core

processor further supports control of the RF section’s frequency synthesizer for frequency hopping and the generation of the control messages needed to coordinate incorporation of the phone’s handset and base station. Additional

on-chip transceiver circuitry supports Frequency Shift Keying modulation/demodulation and multiplexing/demulti-

DS96WRL0800

P R E L I M I N A R Y

1

2

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

GENERAL DESCRIPTION (Continued)

plexing of the 32 kbps voice data and 4 kbps command

data between handset and base station. The Z87001 provides thirty-two I/O pins, including four wake-up inputs and

two CPU interrupt inputs. These programmable I/O pins allow a variety of user-determined phone features and board

layout configurations. Additionally, the pins may be used

so that phone features and interfaces are supported by an

Codec

Z87010

ADPCM

Processor

Telephone

Line

Interface

Z87001

Spread

Spectrum

Controller

RF Section

Base Station

Figure 1. System Block Diagram of a Z87001/Z87010 Based Phone

optional microcontroller rather than by the Z87001’s DSP

core.

In combination with an RF section designed according to

the system specifications, Zilog’s Z87010/Z87L10 ADPCM

Processor, a standard 8-bit PCM telephone codec and

minimal additional phone circuity, the Z87001 and its embedded software provide a total system solution.

Codec

RF Section

Z87001

Spread

Spectrum

Controller

Z87010

ADPCM

Processor

Handset

P R E L I M I N A R Y

DS96WRL0800

1

Z87001/Z87L01

Zilog ROMless Spread Spectrum Cordless Phone Controller

RX

VREF

TX

RXSW

TXSW

PAON

RFEON

SYLE

RSSI

PWLV

ANT0

ANT1

HBSW

RESETB

TEST

ADC

(1-bit)

DAC

(4-bit)

ADC

(8-bit)

DAC

(4-bit)

FSK Demodulator

(downconverter, limiter discriminator,

AFC, bit sync, frame sync, SNR

detector)

FSK Modulator

256 Word

Frame Counter(s),

Event Trigger ,

T/R Switch Ctrl,

Power On/Off Ctrl,

Antenna Select

RAM 0

Receive

Rate

Buffer

Transmit

Rate

Buffer

DSP Core

256 Word

RAM 1

Z87010

Interface

Port 0

Port 1

Analog

Power

Digital

Power

VXDATA[7..0]

VXADD[2..0]

VXSTRB

VXRWB

VXRDYB

CLKOUT

CODCLK

P0[15..0]

P1[15..0]

Addr[15..0]

Data[15..0]

AVDD

AGND

VDD

GND

Figure 2. Z87001 Functional Block Diagram

DS96WRL0800

P R E L I M I N A R Y

3

4

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

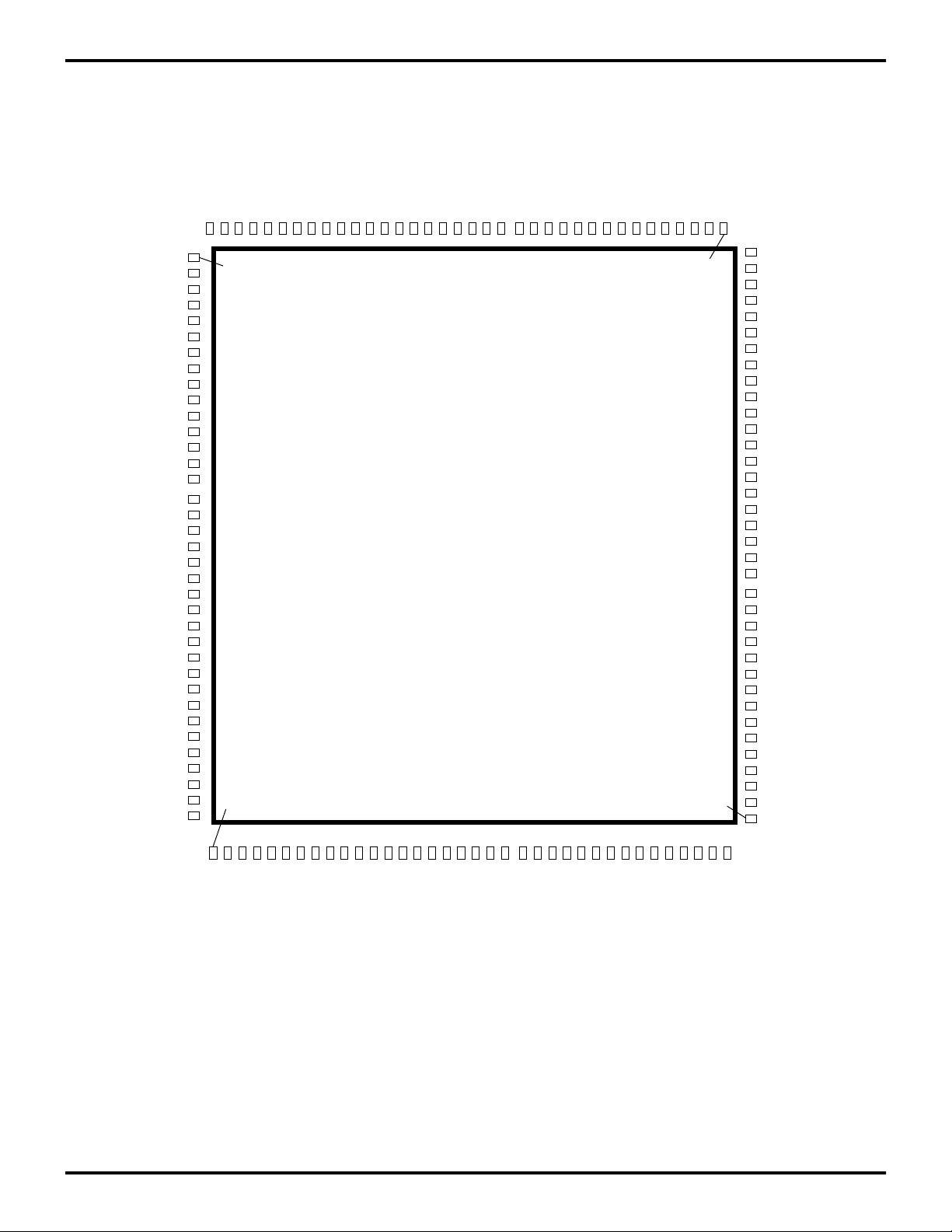

PIN DESCRIPTION

AGND

RX

AVDD

VREF

RFEON

addr12

P115

addr11

GND

addr10

P114

addr9

P113

addr8

P112

addr7

VDD

addr6

P111

addr5

P110

addr4

P19

addr3

GND

addr2

P18

addr1

P17

addr0

P16

idata15

VDD

idata14

P15

TX

RSSI

AVDD

1

37

PWLV

AGND

TXSW

RXSW

addr13

addr14

dspclk

PAON

SYLE

addr15

VDD

triadd

halt

MCLK

intenb

GND

Z87001

RESETB

irwb

CODCLK

iaddr1

iaddr0

VXADD1

VXADD0

VXADD2

VDD

iaddr3

iaddr2

trice

VXRWB

iaddr4

eib

VXSTRB

GND

VXRDYB

109

73

VXDATA0

data0

VXDATA1

data1

VXDATA2

data2

VDD

VXDATA3

data3

VXDATA4

data4

VXDATA5

data5

VXDATA6

VXDATA7

data6

CLKOUT

data7

HBSW

data8

GND

TEST

VDD

data9

ANT0

data10

ANT1

data11

P00

P01

data12

GND

data13

P02

data14

P03

P14

idata13

P13

idata12

P12

GND

idata11

P11

idata10

P10

idata9

P015

idata8

VDD

P014

P013

idata7

idata6

P012

idata5

P011

P010

GND

idata3

idata4

P09

Figure 3. 144 Pin QFP Pin Configuration

P R E L I M I N A R Y

P07

P08

idata2

P06

VDD

idata1

P05

data15

idata0

P04

DS96WRL0800

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

Table 1. 144 Pin QFP Pin Configuration

No Symbol Function Direction

1 TX Analog transmit IF signal Output

2,141 AGND Analog ground –

3 RX Analog receive IF signal Input

4,144 AV

5 VREF Analog reference voltage for RX signal –

6 RFEON RF on/off control Output

7,9,11,13,15,17,19,

21,23,25,27,29,31,

136,138,140

8,12,14,16,20,22,24,

28,30,32,36,37,39,

41,44,46

10,26,43,60,77,88,

109,128

18,34,51,68,86,102,

116,131

33,35,38,40,42,45,

47,49,52,54,56,59,

61,63,66,69

48,50,53,55,57,58,

62,64,65,67,70,72,

73,75,79,80

71,74,76,78,81,83,

85,89,91,93,96,98,

100,103,105,107

82,84 ANT[1..0] RF antenna diversity control Output

87 TEST Test mode select Input

90 HBSW Handset/base mode select Input

92 CLKOUT Clock, ADPCM processor (16.384 MHz) Output

94,95,97,99,101,

104,106,108

110 VXRDYB ADPCM processor ready Output

111 eib External register data strobe Output

112 VXSTRB ADPCM processor data strobe Input

113,117,119,121,

123

114 VXRWB ADPCM processor read/write control Input

115 trice ROMless mode select Input

118,120,122 VXADD[2..0] ADPCM processor address bus Input

124 CODCLK Clock to codec (2.048 MHz) Output

125 irwb External register read/write control Output

126 /RESETB Master reset Input

127 intenb Interrupt enable Input

VXDATA[7..0] ADPCM processor data bus Input

DD

addr[15..0] DSP core program address bus Output

P1[15..0] General-purpose I/O port 1 Input/Output

GND Digital ground –

V

DD

idata[15..0] DSP core internal data bus Output

P0[15..0] General-purpose I/O port 0 Input/Output

data[15..0] DSP core program data bus Input

iaddr[4..0] External register address bus Output

Analog power supply –

Digital power supply –

Z87001/Z87L01

DS96WRL0800

P R E L I M I N A R Y

5

6

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

PIN DESCRIPTION (Continued)

Table 1. 144 Pin QFP Pin Configuration

No Symbol Function Direction

129 halt Halt/ single step control Input

130 MCLK Master clock (16.384 MHz) Input

132 triadd Program address bus enable Input

133 PAON RF transmit enable Output

134 dspclk DSP core clock Output

135 SYLE RF synthesizer load enable Output

137 RXSW Demodulator “on” indication Output

139 TXSW RF receive enable Output

142 PWLV RF transmit power level Input

143 RSSI RF receive signal strength indicator Input

P R E L I M I N A R Y

DS96WRL0800

1

°

°

Z87001/Z87L01

Zilog ROMless Spread Spectrum Cordless Phone Controller

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Min Max Units

V

DD

, AV

DC Supply

DD

-0.5 7.0 V

Voltage(1)

V

V

T

IN

OUT

A

Input V oltage(2) -0.5 V

Output V oltage(3) -0.5 V

Operating

-20 +70

+ 0.5 V

DD

+ 0.5 V

DD

C

Temperature

T

STG

Storage

-65 +150

C

Temperature

Notes:

1. Voltage on all pins with respect to GND.

2. Voltage on all inputs WRT VDD

3. Voltage on all outputs WRT VDD

STANDARD TEST CONDITIONS

The electrical characteristics listed below apply for the following standard test conditions, unless otherwise noted.

All voltages are referenced to GND. Positive current flows

into the referenced pins. Standard test conditions are as

follows:

■

■

3.0V < V

4.5V < V

< 3.6V (Z87L01)

DD

< 5.5V (Z87001)

DD

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at

any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended period may

affect device reliability.

IoL

Threshold

Voltage

Output

Under

Test

GND = 0V

■

T

= -20 to +70 ° C

■

A

50pF

IoH

Figure 5. Test Load Diagram

DS96WRL0800

P R E L I M I N A R Y

7

8

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

RECOMMENDED OPERATING CONDITIONS

Table 3. 5V ± 0.5V Operation (Z87001)

Symbol Parameter Min Max Units

V

, AV

DD

DD

V

IH

V

IL

I

OH

I

OHICE

I

OL1

I

OL2

I

OLICE

T

A

Notes:

1. ICE pins are addr[15..0], iaddr[15..0], idata[15..0], eib and irwb

2. Maximum 3 pins total from P0[15..0] and P1[15..0]

Supply V oltage 4.5 5.5 V

Input High Voltage 2.0 V

+ 0.3 V

DD

Input Low Voltage GND -0.3 0.8 V

Output High Current -2.0 mA

Output High Current, ICE pins (1) -0.5 mA

Output Low Current 4.0 mA

Output Low Current, GPIO (limited usage, 2) 12.0 mA

Output Low Current, ICE pins (1) 0.5 mA

Operating Temperature -20 +70 °C

Table 4. 3.3V ± 0.3V Operation (Z87L01)

Symbol Parameter Min Max Units

V

DD

V

IH

V

IL

I

OH

I

OHICE

I

OL1

I

OL2

I

OLICE

T

A

Notes:

1. ICE pins are addr[15..0], iaddr[15..0], idata[15..0], eib and irwb

2. Maximum 3 pins total from P0[15..0] and P1[15..0]

Supply V oltage 3.0 3.6 V

Input High Voltage 0.7 V

DD

Input Low Voltage GND -0.3 0.1 V

VDD+0.3 V

DD

Output High Current -1.0 mA

Output High Current, ICE pins (1) -0.5 mA

Output Low Current 2.0 mA

Output Low Current, Ports (limited usage, 2) 6.0 mA

Output Low Current, ICE pins (1)) 0.5 mA

Operating Temperature -20 +70 °C

V

P R E L I M I N A R Y

DS96WRL0800

Z87001/Z87L01

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

DC ELECTRICAL CHARACTERISTICS

Conditions for DC characteristics are corresponding operating conditions, and standard test conditions, unless otherwise specified.

Table 5. 5V ± 0.5V Operation (Z87001)

Symbol Parameter Test Condition Min Max Units

V

OH

V

OHICE

V

OL1

V

OL2

V

OLICE

I

L

I

CC

I

CC2

Notes:

1. ICE pins are addr[15..0], iaddr[15..0], idata[15..0], eib and irwb

2. Maximum 3 pins total from P0[15..0] and P1[15..0]

3. 2.3 mA typical at 25°C, 5 volts.

Output High Voltage VDD min, IOH max 2.4 V

Output High Voltage, ICE pins (1) VDD min, I

Output Low Voltage VDD min, I

Output Low Voltage, GPIO (2) VDD min, I

Output Low Voltage, ICE pins (1) VDD min, I

Input Leakage VIN = 0V, V

max 2.4 V

OHICE

max 0.6 V

OL1

max 1.2 V

OL2

max 0.4 V

OLICE

DD

-2 2 µA

Supply Current 80 mA

Standby Mode Current (3) 4 mA

Table 6. 3.3V ± 0.3V Operation (Z87L01)

Symbol Parameter Test Condition Min Max Units

V

OH

V

OHICE

V

OL1

V

OL2

V

OLICE

I

L

I

CC

I

CC2

Notes:

1. ICE pins are addr[15..0], iaddr[15..0], idata[15..0], eib and irwb

2. Maximum 3 pins total from P0[15..0] and P1[15..0]

3. 1.6 mA typical at 25°C, 3.3 volts.

Output High Voltage VDD min, IOH max 1.6 V

Output High Voltage, ICE pins (1)VDD min, I

Output Low Voltage VDD min, I

Output Low Voltage, Ports(2) VDD min, I

Output Low Voltage, ICE pins (1) VDD min, I

Input Leakage VIN = 0V, V

max 1.6 V

OHICE

max 0.4 V

OL1

max 1.2 V

OL2

max 0.4 V

OLICE

DD

-2 2 µA

Supply Current 55 mA

Standby Mode Current(2) 1.4 mA

DS96WRL0800 P R E L I M I N A R Y 9

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

ANALOG CHARACTERISTICS

Table 7. 1-Bit ADC (Temperature: -20/+70°C)

Parameter Minimum Typical Maximum Units

Resolution - 1 - bit

Power dissipation 0.54

(70°c)

Power dissipation, Stop mode 0.06

(70°c)

Sample frequency - 8.192 - MHz

Sample window(1) 29 31 33 ns

Bandwidth - 60 - MHz

Supply Range(=AVDD)

Z87L01

Z87001

3.0

4.5

Acquisition time 2 3 8 ns

Settling time 8 10 18 ns

Conversion time 4 6 18 ns

Aperture delay 2 3 8.5 ns

Aperture uncertainty(2) - - 0.5 ns

Input voltage range (p-p) 800 1000 1200 mV

Reference voltage

Z87L01

Z87001

1.7 (AV

2.7 (AV

DD

DD

= 3V)

=4.5V)

1.9 (AV

Input resistance 10 18 25 KOhm

Input capacitance - 10 - pF

Notes:

Window of time while input signal is applied to sampling capacitor; see next figure.

Uncertainty in sampling time due to random variations such as thermal noise.

(40°c)

(40°c)

3.0 (AV

1.0

0.2

DD

DD

= 3.3V)

= 5V)

(-20°c)

(-20°c)

2.1 (AV

3.3 (AV

2.75

1.1

3.6

5.5

DD

DD

= 3.6V)

= 5.5V)

mW

mW

V

V

V

V

10 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

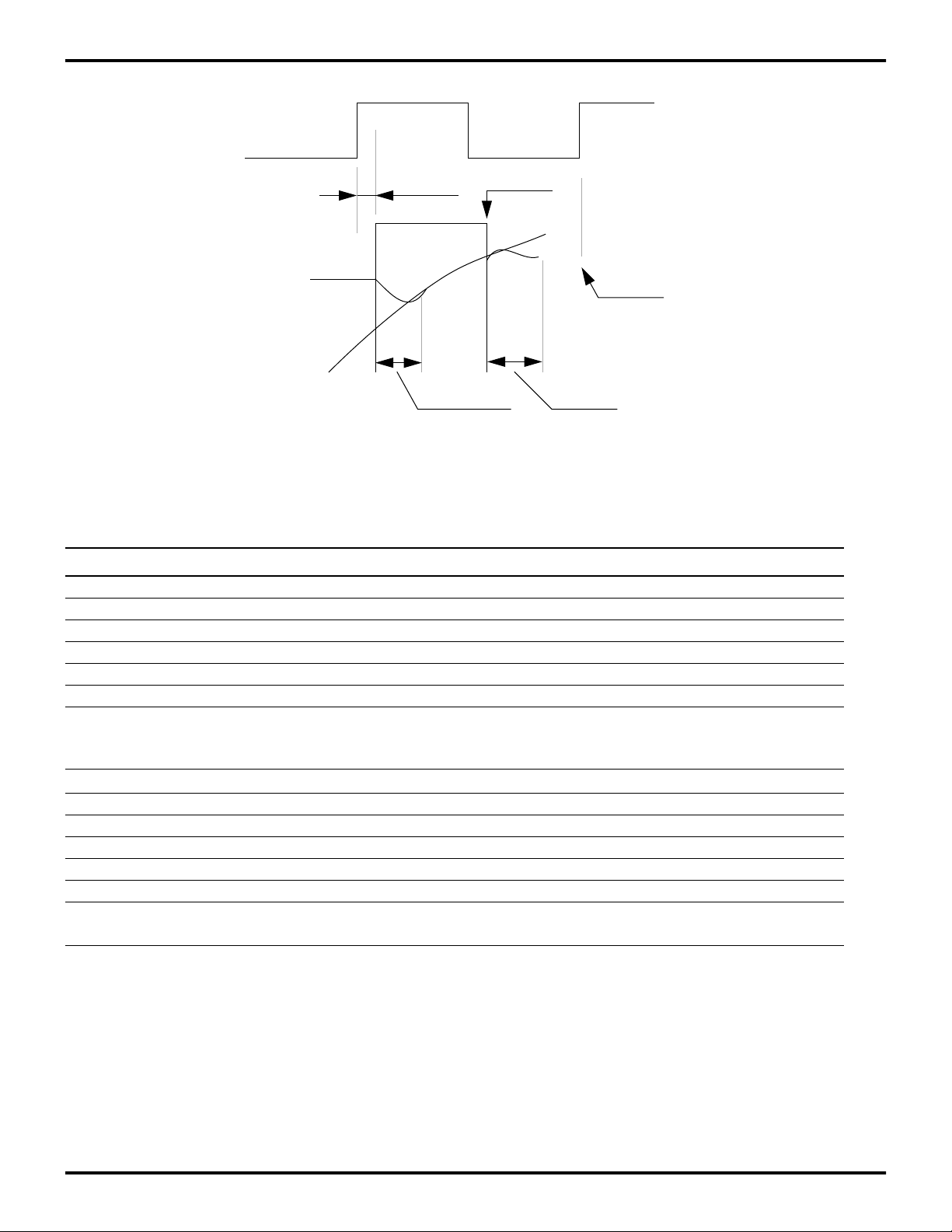

CLK (16.384MHz)

Aperture

Delay

SAMPLING

WINDOW

INPUT

SIGNAL

Sampling

Latched

Output

Acquisition

Time

Settling

Time

Conversion

+

Time (for

digital output)

Figure 6. 1-Bit ADC Definition of Terms

Table 8. 8-bit ADC (Temperature -20/+70°C)

Parameter Minimum Typical Maximum Units

Resolution - 6 - bit

Integral non-linearity - 0.5 1 LSB

Differential non-linearity - - 0.5 LSB

Power Dissipation (peak) 35 70 mW

Sample window 5 - 120 ns

Bandwidth - - 2 Msps

Supply Range (=AVDD)

Z87L01

Z87001

3.0

4.5

Input voltage range 0-AV

3.3

5.0

DD

3.6

5.5

V

V

V

Conversion time 0.5 - - µs

Aperture delay 2 3 8.5 ns

Aperture uncertainty - - 1 ns

Input resistance - 25 - Kohm

Input capacitance - 10 - pF

Notes:

1. 8-bit ADC only tested for 6-bit resolution.

DS96WRL0800 P R E L I M I N A R Y 11

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

Table 9. 4-bit DAC (Temperature: -20/+70°C)

Parameter Minimum Typical Maximum Units

Resolution - 4 - bit

Integral non-linearity - 0.25 0.5 LSB

Differential non-linearity - 0.25 1 LSB

Settling time (1/2 LSB) - - 22.5 ns

Zero error at 25°C-12mV

Conversion time (input change to output change) 14 19 76 ns

Power dissipation, 25 pF load 1.2

(70°c)

Power dissipation, 25 pF load, Stop mode 0.18

(70°c)

20

(40°c)

1.0

(40°c)

24.1

(-20°c)

1.1

(-20°c)

mW

mW

Conversion time (input change to output change) 14.5 19.1 75.8 ns

Rise time (full swing) 11 15 71 ns

Output slew rate 8 67 96 V/µs

Output voltage range - 0.2 AV

Supply Range (=AV

Z87L01

Z87001

DD

)

3.0

4.5

to 0.6A V

DD

3.3

5.0

DD

-V

3.6

5.5

V

V

Output load resistance 330 Ohm

Output load capacitance - 25 - pF

12 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

INPUT/OUTPUT PIN CHARACTERISTICS

All digital pins (all pins except VDD, AVDD, GND, AGND,

V

, RX, TX, RSSI and PWLV) have an internal capaci-

REF

tance of 5 pF.

The RX analog input pin has an input capacitance of 10

pF.

The RSSI analog input pin has an input capacitance of 10

pF.

AC ELECTRICAL CHARACTERISTICS

Clocks, Reset and RF Interface

Table 10. Clocks, Reset and RF Interface

No. Symbol Parameter Min Max Units

1 TpC MCLK input clock period (1) 61 61 ns

2 TwC MCLK input clock pulse width 20 40 ns

3 TrC, TfC MCLK input clock rise/fall time 15 ns

4 TrCC, TfCC CLKOUT output clock rise/fall time 2 6 ns

5 TrCO, TfCO CODCLK output clock rise/fall time 2 6 ns

6 TwR RESETB input low width 18 TpC

7 TrRF, TfRF RF output controls rise/fall time (2) 2 6 ns

Notes:

1. MCLK is 16.384 MHz ± 25 ppm

2. RF Controls are PAON, TXSW, RFEON, SYLE.

DS96WRL0800 P R E L I M I N A R Y 13

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

ADPCM Processor Interface

The Z87001 is a peripheral device for the ADPCM Processor. The interface from the Z87001 perspective is composed of an input address bus, a bidirectional data bus,

strobe and read/write input control signals and a

READ CYCLES refer to data transfers from the Z87001 to

the ADPCM Processor.

WRITE CYCLES refer to data transfers from the ADPCM

Processor to the Z87001.

ready/wait output control signal.

Table 11. Read Cycles

Signal Name Function Direction

VXADD[2..0] Address Bus ADPCM Proc. to Z87001

VXDATA[7..0] Data Bus Bidirectional

VXSTRB Strobe Control Signal ADPCM Proc. to Z87001

VXRWB Read/Write Control Signal ADPCM Proc. to Z87001

VXRDYB Ready Control Signal Z87001 to ADPCM Proc.

Table 12. Write Cycles

No. Symbol Parameter Min Max Units

8 TsAS Address, Read/Write setup time before Strobe falls 10 ns

9 ThSA Address, Read/Write hold time after Strobe rises 3 ns

10 TaDrS Data read access time after Strobe falls 30 (1) ns

11 ThDrS Data read hold time after Strobe rises 8.5 40 (2) ns

12 TwS Strobe pulse width 20

13 TsDwS Data write setup time before Strobe rises 10 ns

14 ThDwS Data write hold time after Strobe rises 3 ns

15 TaDrRY Data read valid before Ready falls 22 ns

16 TdSRY Strobe high after Ready falls 0 ns

Notes:

1. Requires wait state on ADPCM Processor read cycles

2. Requires no write cycle directly following read cycle on ADPCM Processor

14 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

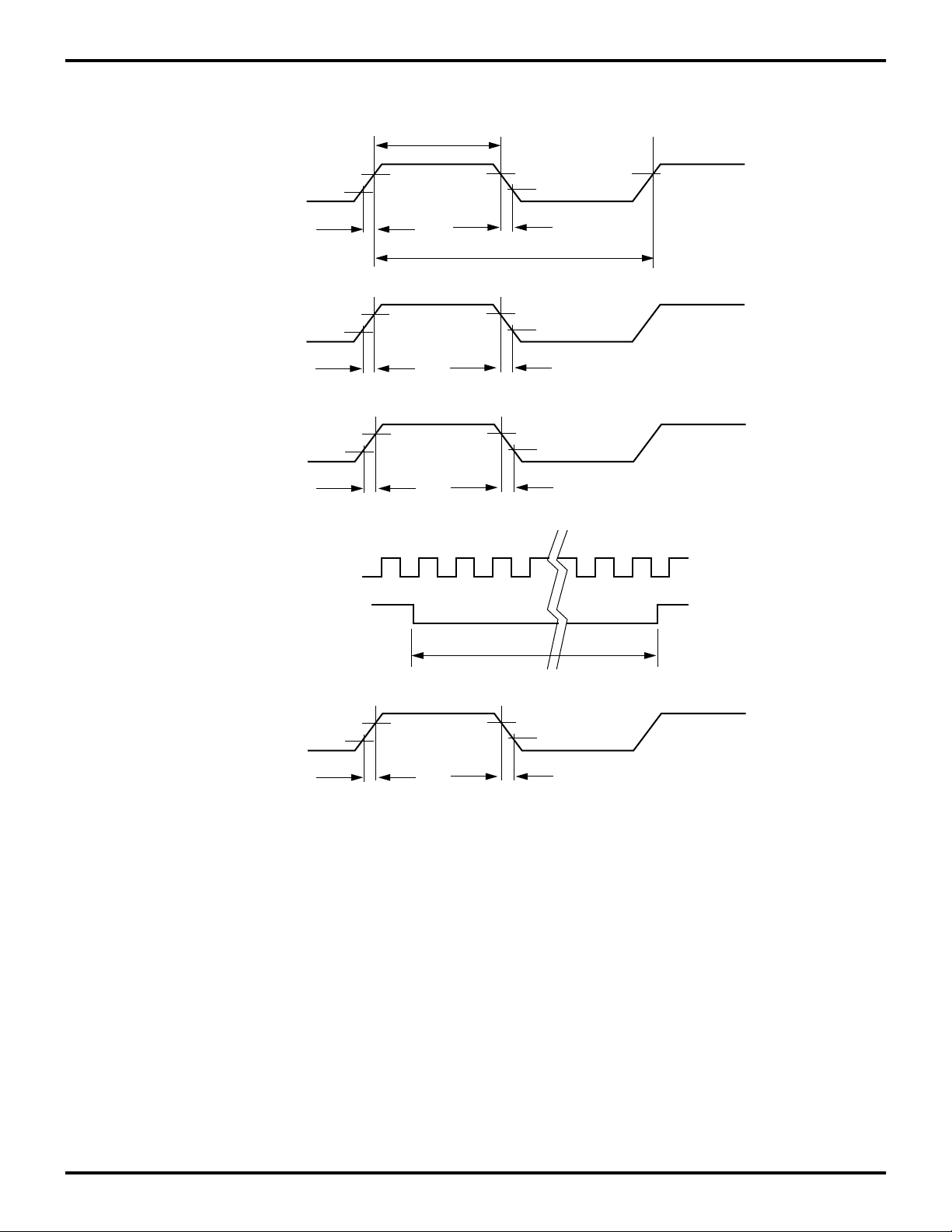

AC TIMING DIAGRAMS

TwC(2)

MCLK

TfC(3)TrC(3)

TpC (1)

CLKOUT

CODCLK

MCLK

RESETB

PAON

TXSW

RXSW

RFEON

SYLE

TrCC(4)

TrCO(5)

TrRF(7)

1

TfCC(4)

TfCO(5)

23

TwR(6)

TfRF(7)

418

16

17

Figure 7. Transceiver Output Signal

DS96WRL0800 P R E L I M I N A R Y 15

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

TsAS(8) ThSA(9)

VXADD

VXRWB

VXSTRB

ThDrS(11)TaDrS(10)

VXDA TA

VXRD YB

VXDATA Read Cycle

VXADD

VXRWB

VXSTRB

VXDATA

VXRDYB

TsAS(8) ThSA(9)

TwS(12)

ThDwS(14)

TsDwS(13)

VXDA TA Write Cycle

Figure 8. Read/Write Cycle TImings

16 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

TsAS(8) ThSA(9)

VXADD

VXRWB

VXSTRB

VXDATA

VXRDYB

ThDrS(11)

TaDrRY(15)

TdSRY(16)

VXDATA Read Cycle with Wait State

TsAS(8) ThSA(9)

VXADD

VXRWB

VXSTRB

VXDATA

VXRDYB

TwS(12)

ThDwS(14)

TsDwS(13)

TdSRY(16)

VXDATA Write Cycle with Wait State

Figure 9. Read/Write Cycle Timing with Wait StatE

DS96WRL0800 P R E L I M I N A R Y 17

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

PIN FUNCTIONS

V

Digital power supply.

DD.

GND. Digital ground.

AVDD. Analog power supply.

AGND. Analog ground.

V

(analog reference). This signal is the reference volt-

REF

age used by the high speed analog comparator to sample

the RX input signal.

RX (analog input). This is the RX IF receive signal from

the RF module, input to the analog comparator and FSK

demodulator. It is internally biased to the V

DC voltage.

REF

The IF signal from the RF module should be AC coupled

to the RX pin.

TX (analog output). This is the IF transmit signal to the RF

module, output from the FSK modulator and transmit 4-bit

D/A converter.

RXSW (output; active high or low programmable). This

pin reflects the programming of the demodulator turn-on

time.

TXSW (output; active high or low programmable). Con-

trol for the receive switch on the RF module. Active during

receive periods.

PAON (output; active high or low programmable). Control for the transmit switch on the RF module. Active during

transmit periods.

RFEON (output; active high or low programmable).

On/off control for the RF module. Active (on) during wake

periods. Inactive (off) during sleep periods on the handset.

CLKOUT (output). Clock output for external ADPCM processor.

CODCLK (output). Clock output for external voice codec.

/RESETB (input, active low). Reset signal.

VXADD[2..0] (input). Address bus controlled by external

ADPCM processor. The Z87001 acts as peripheral of the

Z87010 ADPCM processor.

VXDATA[7..0](input/output). Read/write data bus controlled by external Z87010 ADPCM processor.

VXSTRB (input). Data strobe signal for the VXDATA bus,

controlled by external Z87010.

VXRWB (input). Read/write control for the VXDATA bus,

controlled by external Z87010.

VXRDYB (output, active low). Ready control for the VXDATA bus. This signal is driven high (de-asserted) by the

Z87001 to insert wait states in the Z87010 ADPCM processor accesses.

TEST (input, active high). Main test mode control. Must be

set to GND.

HBSW (input with internal pull-up). Control for handset/base configuration. Must be driven high or not connected for handset, low for base.

P0[15..0] (input/output). General-purpose I/O port. Direction is bit-programmable. Pins P0[3..0],when configured in

input mode, can also be individually programmed as wakeup pins for the Z87001 (wake-up active low; signal internally debounced and synchronized to the bit clock).

RSSI (analog input). Receive signal strength indicator

from RF module, input to the RSSI 8-bit ADC.

PWLV (analog output). Power level control for RF module,

output from the transmit power 4-bit DAC.

SYLE (output). RF synthesizer load enable: latches new

frequency hopping control word of external RF synthesizer. Programmable polarity.

P1[15..0] (input/output).General-purpose I/O port. Direction is bit-programmable. Pins P114 and P115, when configured in input mode, also behave as individually

P0 0 WAKEUP0

P0 1 WAKEUP1

P0 2 WAKEUP2

P0 3 WAKEUP3

maskable interrupt pins for the core processor (positive

ANT[1..0] (output). Control for optional antenna diversity

edge-triggered).

on the RF module.

MCLK (input). Master clock input.

P1 14 INT0

P1 15 INT2

18 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

FUNCTIONAL DESCRIPTION

The functional partitioning of the Z87001 is shown in Figure 2. The chip consists of a receiver, a transmitter, and

several additional functional blocks.The receiver consists

of the following blocks:

■ Receive 1-bit ADC

■ Demodulator, including:

– IF Downconverter

– AFC (Automatic Frequency Control)

– Limiter-Discriminator

– Matched Filter

– Bit Synchronizer

– Bit Inversion

– Frame Synchronizer (unique word detector)

– SNR Detector

■ Receive Frame Timing Counter

■ Receive Buffer and Voice Interface

The Transmitter Consists of the Following Blocks:

■ Transmit Buffer and Voice Interface

■ Transmit Frame Timing Counter (used on base station

only)

■ Modulator, including:

– NCO

– Bit Inversion

■ Transmit 4-Bit DAC

In Addition, there are the following Shared Blocks.

■ Event Trigger Block, Controlling:

– Transmit/Receive Switch

– Power On/Off Switches (Modulator, Demodulator,

RF Module)

– Antenna Switch Control (used on Base Station

only for Antenna Diversity)

■ 4-Bit DAC for Setting Transmit Power Level

■ 8-Bit ADC for Sampling the Received Signal Strength

Indicator (RSSI)

■ DSP Core Processor

■ Two 16-Bit General-Purpose I/O Ports

■ Z87010 ADPCM Processor Interface

Basic Operation

The transmitter and receiver operate in time-division duplex (TDD): handset and base station transmit and receive

alternately. The TDD duty cycle lasts 4 ms and consists of

the following events:

■ At the beginning of the cycle, the frequency is changed

(hopping)

■ The base station transmits a frame of 144 bits while the

handset receives

BASE

HANDSET

HOP

Frequency

Hopping

guard time

■ The handset then transmits a frame of 148 bits while the

base receives.

4ms frame

144 bits

TX

TDD switching

guard time

RX TX

Figure 1. Basic Time Duplex Timing

148 bits

RX

19 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

Receive 1-Bit ADC

The incoming receive signal at the RX analog input pin is

sampled by a 1-bit analog-to-digital converter at 8.192

MHz.

The receive signal is FSK-modulated (Frequency Shift

Keying) with a carrier frequency of 10.7 MHz (Intermediate

Frequency, or IF). The instantaneous frequency varies between 10.7 MHz plus or minus 32.58 kHz. Since the data

rate is 93.09 kbps, there are 88 samples per data bit. This

oversampled data is further processed by the demodulator

to retrieve the baseband information.

The 1-bit converter is implemented with a fast comparator,

which determines whether the RX signal is larger or smaller than a reference signal (VREF). The Z87001 internally

generates the DC level of both VREF and RX input pins.

The received signal at 10.7 MHz should thus be AC coupled to the RX pin via a coupling capacitor. To ensure accurate operation of the converter, the user should also attach to the VREF pin a network whose impedance

matches the DC impedance seen by the RX pin.

Demodulator

The demodulator includes a two-stage IF downconverter

that brings the sampled receive signal to baseband.

The narrow-band 10.7 MHz receive signal, sampled at

8.192 MHz by the 1-bit ADC, provides a 2.508 MHz useful

image. The first local oscillator used to downconvert this IF

signal is obtained from a Numerically Controlled Oscillator

(NCO) internal to the Z87001, at the nominal frequency of

460 kHz. The resulting signal is thus at 2.048 MHz (= 2.508

MHz - 460 kHz). A second downconversion by a 2.048

MHz signal brings the receive signal to baseband.

The exact frequency of the 460 kHz NCO is slightly adjusted by the Automatic Frequency Control (AFC) loop for exact downconversion of the end signal to the zero frequency. The AFC circuit detects any DC component in the

output of the limiter-discriminator (see below) when receiving a known sequence of data (preamble). This DC component is called the “frequency bias”. The bias estimate

out of the AFC can be read by the DSP processor on every

frame and subsequently filtered. The processor then adds

or subtract this filtered bias to/from the NCO control word

to correct the NCO frequency output.

Rx signal

1-bit

ADC

SSB

460 kHz

+ bias

NCO AFC

2.048 MHz

Figure 2. Demodulator Block Diagram

The main element of the demodulator is its limiter-discriminator. The limiter-discriminator detects the frequency variations (ideally up to ± 32.58 kHz) and converts them to “0”

or “1” information bits. First, the data is processed through

low-pass filters to eliminate high frequency spurious components introduced by the 1-bit ADC. The resulting signal

is then differentiated and fed to a matched filter. In the

matched filter, an integrate-and-dump operation is performed to extract the digital information from its background noise.

The symbol clock is provided by the bit synchronizer. The

bit synchronizer circuit detects 0-to-1 and 1-to-0 transitions

SNR

Filter

Limiter-

Discriminator

Bit

Sync

Frame

Sync

Rx

Buffer

in the incoming data stream in order to synchronize a digital phase-lock loop (DPLL). The PLL output is the recovered bit clock, used to time the receiver on the base station, and both receiver and transmitter on the handset.

To ensure enough transitions in the voice data stream, a

pseudo-random bit inversion operation is performed on the

outgoing voice data. The inversion is then reversed on the

demodulated data.

Since the data is packed in frames sent alternately from

base and handset every 4 ms (TDD), additional synchronization means are necessary. This is realized in a frame

20 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

FUNCTIONAL DESCRIPTION (Continued)

synchronizer, based on detection of a “unique word” following the preamble.

The receiver also features a signal-to-noise ratio detector,

which allows the DSP software to detect noisy channels

and eliminate them from the frequency hopping cycle. The

SNR information is also used by the Z87001 software as a

measure the current range between handset and base station. This information allows the adaptive power control algorithm to provide sufficient output power to the RF transmitter.

Receive Frame Counter

The receive frame counter is responsible to keep track of

time within the frame. It is initialized by the frame synchronizer logic on detection of the unique word. It is then

clocked by the recovered bit clock from the bit synchronizer.

On the base station, the receive frame counter is used as

time base for the receiver. On the handset, it is used as

time base for both receiver and transmitter.

Receive Rate Buffer and Voice Interface

The voice signal is generated at the fixed rate of 32 kips by

the Z87010 processor, and transmitted/received in bursts

of 93.09 kips across the air. Data buffers in the transmitter

and receiver are thus necessary to absorb the rate differences over time. These buffers are called “rate buffers”.

They can store up to 144 data bits and are organized as an

array of 36 4-bit nibbles.

The receive rate buffer stores the received data from the

demodulator. Incoming bits are arranged in 4-bit nibbles

and transferred to successive locations of the rate buffer.

When the last location is reached, transfers resume from

the beginning (circular buffer). The system design guarantees that no buffer overrun nor enduring can occur.

The receive rate buffer can be read by the DSP core processor of the Z87001 or by the Z87010 chip. On the

Z87001 side, the buffer can be read as a random-access

memory: the processor writes the nibble address in an address register and reads the 4-bit data from a data register.

On the Z87010 side, a voice processor interface logic handles the addressing to automatically present the successive voice nibbles to the Z87010 in the order they were received.

Transmit Rate Buffer and Voice Interface

The transmit rate buffer stores the data to be modulated.

The data is sourced from the Z87010 or the Z87001 core

processor. As for the receive rate buffer, the Z87010 sees

a unique pipe to write to, while the Z87001 DSP core accesses the rate buffer as random-access memory. The

modulator reads from the rate buffer as from a circular

buffer.

Transmit Frame Timing Counter

On the handset, transmission does not start until the receiver has synchronized itself to the signal received from

the base station. The transmission timing is based on the

recovered clock. No additional counter is necessary.

On the base station, the situation is different. Transmission

timing is based on a local clock, while the reception’s timing is based on the clock recovered from the incoming received signal. Two counters, respectively clocked by local

and recovered clocks, are necessary to track the transmit

and receive signals.

Note that the receive clock on the base station tracks the

handset’s transmit clock, which is also the handset’s receive clock and tracks the transmit clock of the base station. As a result, receive and transmit clocks of the base

station have exactly the same frequency; only their phases

differ.

Modulator

The modulator consists of a numerically controlled oscillator (NCO) which generates an FSK (Frequency Shift Keying) signal at the carrier frequency of 2.508 MHz. The carrier frequency is shifted plus or minus 32.58 kHz for a “1”

or a “0” data bit. To facilitate conformance to FCC regulations, the transitions from “1” to “0” or vice-versa are

smoothed in order to decrease the amplitude of the side

lobes of the transmit signal. In practice, the jump from one

frequency to the next is performed in several smaller

steps.

The carrier frequency is adjustable by the DSP core processor in order to provide additional frequency adjustment

between base and handset. This is provided in case of a

frequency offset too large for possible correction by the

AFC.

The modulator also includes bit inversion logic as discussed in the receiver section.

21 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

Tx signal

4-bit DAC

Figure 3. Modulator Block Diagram

Transmit 4-Bit DAC

The transmit DAC clocks one new NCO value out of the

Z87001 every 8.192 MHz period. Only the 10.7 MHz alias

frequency component of the transmit signal (2.508 + 8.192

MHz image) is filtered, amplified and upconverted to the

900 MHz ISM band by the companion RF module.

Event Trigger Block

The event trigger block is responsible for scheduling the

different events happening at the bit and frame levels. The

event trigger block receives input from the frame counters

as well as the register interface of the DSP core processor.

The event trigger schedules the following events:

NCO

Tx Buffer

Spectral

Shaping

rectly controlled by the Z87001 software through an output

register.

8-Bit ADC for Sampling the Received Signal

Strength Indicator (RSSI)

RSSI information is typically generated from the last stage

of the RF receiver. The RSSI is sampled once per frame

by the 8-bit ADC and used by the Z87001 software to compute the necessary Transmit Power Level voltages.

DSP Core Processor

A DSP core processor constitutes the heart of the Z87001.

The DSP runs the application software which performs the

following functions:

■ Start of the 4 ms frame: a synthesizer load enable pulse

is issued on the SYLE pin

■ Power-up of the modulator section and transmission of

the frame on handset and base station

■ Use of the bit inversion as function of mode

■ Power-up of the demodulator section and reception of

the frame on handset and base station

■ Control of PAON and TXSW output pins, to be used as

TDD control signals for the T/R switch as well as the

transmitter and receiver chains on the RF module

■ Control of RFEON pin, to be used as general on/off

switch on the RF module

■ Control of the Z87001 sleep mode

4-Bit DAC for Setting Transmit Power Level

In order to save battery life, the Z87001 only transmits the

amount of RF power needed to reach the remote receiver

with a sufficient SNR margin. The on-board transmit power

4-bit DAC provides 4 different voltage levels to the power

amplifier in the RF module for that purpose. This DAC is di-

■ Register initialization

■ Implementation of high-level phone features; control of

phone user interface (keypad, Led, etc.)

■ Control of the Z87010 ADPCM Processor

■ Control of the phone line interface

■ Ring detection by DSP processing

■ Communication protocol between handset and base

station supporting voice and signalling channels

■ Control of the RF synthesizer and adaptive frequency

hopping algorithm

■ Control of the RF power and adaptive power algorithm

■ Control of the demodulator (bit synchronizer loop filter,

AFC bias estimate filtering)

■ Control of the modulator (carrier frequency) and

adaptive frequency alignment

■ Signalling between base and handset to support above

features

22 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

FUNCTIONAL DESCRIPTION (Continued)

The DSP core is characterized by an efficient hardware architecture that allows fast arithmetic operations such as

multiplication, addition, subtraction and multiply-accumulate of two 16-bit operands. Most instructions are executed

in one clock cycle.

The DSP core is operated at the internal speed of 8.192

MHz. It has an internal RAM memory of 512 16-bit words

divided in two banks. Six register pointers provide circular

buffering capabilities and dual operand fetching. Three

vectored interrupts are complemented by a six-level stack.

One interrupt is used by the transceiver, while the two remaining vectors are mapped into port P1. In the phone

system, one of these interrupts is customarily reserved for

the Z87010 ADPCM Processor. The other interrupt can be

used for custom purposes.

The Z87001 may access up to 64K 16 bit words of external

ROM including 4 words for interrupt and reset vectors. The

ROM is mapped at addresses 0000h to 3FFFh, as shown

in Figure 13.

3FFFh

3FFEh

3FFDh

3FFCh

3FFFh

Int. V ector 0

Int. V ector 1

Int. V ector 2

Reset Vector

■ Control of battery charging and detection of low battery

conditions

■ Implementation of additional features for customizing of

the phone

Z87010 Interface

In addition to providing clock signals to the Z87010 processor, the Z87001 interfaces to the Z87010 through two different paths:

■ A command/status interface

■ A data interface

The command/status interface consists of two dual-port

registers accessible by both Z87001 and Z87010 DSP

core processors. On the Z87001 side, the registers are

mapped into the DSP core processor’s register interface.

To allow access by the Z87010, the internal command/status registers can also be decoded on the pinto of the

Z87001. Arbitration logic resolves access contentions.

The data interface allows the Z87010 processor direct access to the Z87001’s receive and transmit rate buffers. The

rate buffers are decoded on the pin to of the Z87001, and

dedicated voice processor interface logic handles the addressing within the rate buffers.

64K

USER ROM

(EXTERNAL)

0000h

Figure 4. ROM Mapping

Two 16-Bit General-Purpose I/O Ports

Two 16-bit general-purpose I/O ports are directly accessible by the DSP core. These input and output pins are typically used for:

■ Implementation of the phone’s user interface (keypad,

LED, optional display, etc.)

■ Control of phone line interface (on/off hook, ring detect)

The physical interface between Z87001 and Z87010 consists of an 8-bit data bus, a 3-bit address bus and control

signals, as summarized in the following:

VXDATA[7.0] Data bus

VXADD[2.0] Address bus

VXSTRB Data Strobe

VXRWB Read/Write Control

VXRDYB Read Control

This bus is controlled by the Z87010. Although in the system the Z87010 is enslaved to the Z87001 master, at the

physical level the Z87001 acts as a peripheral of the

Z87010.

The mapping of the command status and data interfaces

from the Z87010 side is given below.

Interface

Transmit

Address

(VXADD [2.0])

1W----3210

Read

/Write

Data

(VXDATA[7.0])

rate buffer

Receive

1R----3210

rate buffer

Command 0 R 76543210

Status 0 W 76543210

23 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

OPERATION

Automatic Frequency Control Loop

(Receiver) and Modulator

AFC Loop

The AFC loop consists of a bias estimator block, which determines frequency offsets in the incoming signal, an

adder, to add this bias to the 460 kHz frequency control

word driving the NCO, and various interface points to the

DSP core processor. In particular, the DSP can read the

bias estimate data and substitute its own calculated bias

value to the NCO.

The bias estimator accumulates the discriminator output

values (image of instantaneous frequency) that exceed a

programmable threshold (BIAS_THRESHOLD). The processor can freeze the bias calculation any time by resetting the BIAS_ENABLE control bit.

Rx signal

460 kHz

+ bias

Second downconvertor,

Discriminator

The accumulated bias, available in BIAS_ERROR_DATA,

can be used directly to correct the NCO frequency. Alternately, the estimated bias can be read by the DSP, further

processed, and written to the CORE_BIAS_DATA field.

The DSP controls which value is used by setting the

USE_CORE_BIAS field. The selected value is added to

the 460 kHz signal which downconverts the receive IF signal.

The CORE_BIAS_DATA and BIAS_ERROR_DATA are

two’s complement numbers in units of 125 Hz.

In addition to correcting the difference in clock frequencies

on the receiver using the AFC loop, a Z87001-base system

can also modify the frequency of the remote transmit IF

signals. The software has access to this frequency through

the MOD_FREQ register fields.

Discriminator

Output

Bias estimator

“0”

Downconverter

NCO and bias

adder

Figure 5. AFC Loop and Processor Control

BIAS_ERROR_DATA

CORE_BIAS_DATA

USE_CORE_BIAS

BIAS_ENABLEBIAS_THRESHOLD

DSP Core

Processor

24 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

OPERATION (Continued)

Modulator Control

The MOD_FREQ fields specify the carrier center frequency (should be programmed to 2.508 MHz) and deviation for

the FSK signal (should be programmed to ± 32.58 kHz). In

addition, wave shaping is performed on bit transitions, in

order to satisfy FCC regulations. Up to four different intermediate deviation values are programmable for each of

the two FSK states. The MOD_FREQ fields are programmable in units of 62.5 Hz.

Table 1. AFC and Modulator Control Fields

Field Register Bank EXT

BIAS_THRESHOLD

BIAS_ENABLE

BIAS_ERROR_DATA

CORE_BIAS_DATA

Discriminator

Output

CONFIG1

SSPSTATE

BIAS_ERROR

CORE_BIAS

In-phase

Matched

Filter

3 EXT0

3 EXT2

2 EXT2

2 EXT4

Transition

Detection

Bit Synchronizer

The bit synchronizer circuit is an implementation of the

Data-Transition-Tracking Loop (DTTL), best described in

“Telecommunications Systems Engineering”, by W. Lindsey and M. Simon (Dover 1973; oh. 9 p. 442). Its operation

is summarized in the following block diagram.

Signed

Error

Mid-phase

Matched

Filter

Recovered

Bit clock

Error

Magnitude

Clock

Generator

Loop Filter

division

first order

“by 1”

“by 64”

Figure 6. Bit Synchronizer Loop and Processor Control

INT_SYM_ERR0

INT_SYM_ERR1

SECOND_ORDER

BSYNC_GAIN

DSP Core

Processor

25 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

The loop filter is controlled by the DSP core processor. The

DSP core can implement a first order loop by setting the

SECOND_ORDER field to zero. Typically, the

BSYNC_GAIN would then be set to “divide-by-1” operation

to provide a wide closed loop bandwidth and thus a quick

acquisition of the bit clock. When the bit clock is in phase

with the input data, the loop bandwidth can be narrowed to

maintain tracking of the receive clock with minimum impact

from signal noise. To reduce the loop bandwidth, the

BSYNC_GAIN can be set to “divide-by-64” the first order

gain, while the integrated tracking error (available to the

DSP in fields INT_SYM_ERR0 and INT_SYM_ERR1) can

be used by the DSP software to adjust the

SECOND_ORDER term.

The bit synchronizer relies on transitions in the received bit

stream to operate. The bit inversion logic guarantees

enough transitions for all transferred data.

At the handset, the bit synchronizer must track both frequency and phase of the receive signal’s data clock. At the

base, only the phase must be tracked. The frequency is inherently correct since the base is the source of the system’s data clock.

Table 2. Bit Synchronizer Control Fields

Field Register Bank EXT

BYSNC_GAIN SSPSTATE 3 EXT2

INT_SYM_ERR1 BIT_SYNC 1 EXT2

INT_SYM_ERR0 INT_SYM-ERR0 0 EXT6

SECOND_ORDER BIT_SYNC 1 EXT2

Frame Counters

The handset only has one frame counter, which times all

receive and transmit events. The base station has distinct

transmit and receive frame counters. When used in this

document without any explicit reference to either base or

handset, the terms “receive frame counter” and “transmit

frame counter” refer to both sides. For the handset, both

terms refer to the same unique counter.

The frame counters are clocked at the bit rate, or 93.09

kHz (2.048 MHz/22). Each count lasts one bit =

1000/93.09 = 10.74 µs.

Each frame lasts 4 ms, which corresponds to (372 + 8/22)

bits; the frame counters count from 0 to 371, with the last

count lasting a bad longer than the other ones; at the end

of count 371, the counters wrap around to 0.

The “hop” command pulse is asserted to pin SYLE during

count “0” of the frame counter (transmit frame counter on

the base station).

Frame Synchronizer, Timings and

RF Interface

The frame synchronizer tracks the received frames and resets the receive frame counter. The synchronization is performed by recognizing certain data patterns present in the

receive bit stream: a comparison is done on the fly between the data pattern and the incoming bit stream; when

the data match, the frame counter is reset.

Two possible 16-bit data patterns are pre-programmed in

the Z87001. One is named UW (Unique Word) and is used

in acquisition mode for first-time synchronization to an incoming signal. UW can also be used to track an acquired

signal. The second pattern is named SYNC_D and is used

to track the received data frames while voice is being

transferred. The transition from tracking UW to tracking

SYNC_D is controlled by the DSP processor through the

SYNC_SEARCH_WORD field.

UW Synchronization

When the Z87001 matches the UW, the receive frame

counter is reset to the value of UW_LOCATION. This value

is programmable by the DSP processor. On the handset,

where the receive frame counter is used to derive all timings, UW_LOCATION actually defines the guard time between the frequency hop command and the beginning of

data reception, which starts at FRAME_COUNTER =

(UW_LOCATION - 84) as shown in the next figure.

On the base station, data reception starts when the receive

frame counter equals (UW_LOCATION - 84), but this has

less significance since the hop pulse is synchronized with

the transmit frame counter and there is no fixed relationship between transmit and receive frame counters. On the

base station, the UW_LOCATION should be set to 301.

26 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

OPERATION (Continued)

UW_LOCATION-84

Handset

FRAME_COUNTER

012

SYLE timing

Receive data at RX pin

Figure 7. Frame Counter and UW_LOCATION on Handset

Two modes of search are programmable through the

SYNC_SEARCH_MODE field: “full search” and “window

search”. The full search is used by the handset when first

acquiring the signal from the base station. In full search,

the handset is in receive mode and continuously looks for

a match with the UW. When a match is found and the time

reference established (UW_LOCATION is set), the DSP

processor on the handset detects the synchronization (see

below), switches to Time Division Duplex mode (TDD) and

starts receiving and transmitting alternately. The search

mode should also be switched to “window search” by the

DSP software.

The window search mode only searches for a match in a

certain time window centered around the expected match

time. The window size is programmable by the DSP processor in the WINDOW_SIZE field. If the matching does

not occur at the expected time, due to so-called “bit slips”,

the receive frame counter timing is adjusted. Note: although the bit synchronizer is meant to keep track of time

and prevent bit slips when the phone is operating continuously in TDD mode, bit slips are still possible when the

handset is in standby mode, and only receives once in a

while (see description of sleep mode).

SYNC_D Synchronization

When the DSP processor switches the Z87001 operation

to voice mode, the frame synchronization parameters

should be modified by the DSP software to:

■ SYNC_SEARCH_MODE = window search

■ SYNC_SEARCH_WORD = SYNC_D pattern

In this mode, the receiver searches for the SYNC_D pattern in windows of the incoming data stream. The window

size is determined by the WINDOW_SIZE field.

The transition to voice mode proceeds in two steps,

through an intermediate mode. The mode is set by the

DSP processor by programming the

MULTIPLEX_SWITCH field. The three modes are:

■ SMUX: initial mode. This mode allows acquisition, AFC

operation, UW synchronization and signalling; ADPCM

Processor access disabled; bit inversion disabled.

■ STMUX: intermediate mode. This mode allows

SYNC_D frame synchronization and signalling; ADPCM

Processor access disabled; bit inversion enabled.

■ TMUX: voice mode. This mode allows voice

transmission, SYNC_D frame synchronization and

signalling; ADPCM Processor access enabled; bit

inversion enabled.

In order to detect synchronizations, the software has access to the SYNC_ACQ_IND status field. This field is set

by the Z87001 matching hardware every time a match is

detected within the right time window. The software must

reset the “IND” bit by setting the SYNC_ACQ_CLEAR

field.

In addition, the software can track the frame timing by

reading the frame counter value, available in the

FRAME_COUNTER field. On the base station, where two

frame counters are in use, this field returns the value of the

transmit frame counter.

Every time the frame counter wraps around to 0, a frame

start indicator bit is set (FRAME_START_IND status field).

The software must reset this “IND” bit by setting the

FRAME_START_CLEAR field. If the FS_INT_ENABLE bit

is set, frame starts also trigger interrupts to the DSP processor.

27 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

The following table summarizes the fields allowing control

of frame synchronization and basic frame timing.

Table 3. Frame Synchronizer Control Fields

Field Register Bank Ext

SYNC_SEARCH-MODE SSPSTATE

SYNC_SEARCH_WORD SSPSTATE

UW_LOCATION RX_CONTROL

WINDOW_SIZE CONFIG1

MULTIPLEX_SWITCH SSPSTATE

SYNC_ACQ_IND SSPSTATUS

SYNC_ACQ_CLEAR SSPSTATE

FRAME_COUNTER SSPSTATUS

FS_INT_ENABLE CONTROL

FRAME_START_IND SSPSTATUS

FRAME_START_CLEAR SSPSTATE

SYNC_SEARCH-MODE SSPSTATE

3 EXT2

3 EXT2

2 EXT1

3 EXT0

3 EXT2

3 EXT3

3 EXT2

3 EXT3

1 EXT6

3 EXT3

3 EXT2

3 EXT2

RF Interface

Several control fields are available in the Z87001 register

set to control the timing and polarity of the RF module interface signals.

A first field, RFEON_POLARITY, controls the polarity of

the RFEON pin. This pin should be used to control the

power of the RF module. It is asserted by the Z87001 when

the RF module is in use, and de-asserted in sleep mode.

The sleep mode is used by the handset to save battery life

when no phone call is in process (See “Sleep mode”, below).

The SYLE pin (Synthesizer Load Enable), which carries a

“load enable” pulse that tells an external RF synthesizer to

generate the next RF channel, is controlled by two fields.

The HOP_ENABLE field is a global enable signal for the

SYLE signals. The SYLE_POLARITY field defines the polarity of the SYLE pin. The system designer should ensure

that the leading edge of the SYLE pulse triggers channel

hopping.

In addition to the SYLE signal, the interface to the most RF

synthesizers includes two more input lines, “data” and

“clock”, for serial programming of the data values defining

the RF channel. In order to allow interfacing to various

popular synthesizers, the Z87001 does not have dedicated

clock and data lines with fixed timing. Instead, two general

I/O pins from ports P0 and P1 can be controlled in software

by the DSP core to realize any particular interface timing.

This flexibility is made possible by the high speed, singlecycle architecture of the DSP core.

The transmitter control includes a global enable signal for

all transmit functions: TX_ENABLE. The transmission start

is controlled by the MOD_PWR_ON field. On the base station, the value programmed in MOD_PWR_ON is referenced to the transmit frame counter.

Two additional fields, RFTX_PWR_ON and

RFTX_PWR_OFF, define the duty cycle of the PAON output pin. On the base station, these fields are referenced to

the transmit frame counter. The RFTX_POLARITY bit defines the polarity of the PAON pin. This pin can be used to

control the transmit section and power amplifier of the external RF module.

On the receive side, two fields define the internal timing of

the receiver. The start of reception is controlled by the

DEMOD_PWR_ON field. Stop of reception (and receiver

power down) is controlled by the DEMOD_PWR_OFF

field. On the base station, these fields are referenced to

the receive frame counter. The RXSW output pin follows

the timing defined by the DEMOD_PWR_ON and OFF

fields.

Two additional fields, RFRX_PWR_ON and

RFRX_PWR_OFF, define the duty cycle of the TXSW output pin. On the base station, these fields are referenced to

the TRANSMIT (!) frame counter. The RFRX_POLARITY

bit defines the polarity of the TXSW and RXSW pins. The

TXSW pin can be used to control the receive section of the

external RF module.

The various timing control registers reviewed in this paragraph should be programmed differently for handset and

base station. If the same ROM code is used on base and

handset, the software can determine which station it runs

on by reading the HAND_BASE_SEL bit, which reflects

the state of the HBSW pin.

28 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

OPERATION (Continued)

The following figure and table summarize the RF interface

control fields.

HBSW

DSP Core

Processor

TX_ENABLE

HAND_BASE_SEL

MOD_PWR_ON

Modulator

DEMOD_PWR_ON

DEMOD_PWR_OFF

Demodulator

Sleep Mode

Control

RFEON_POLARITY

HOP_ENABLE

SYLE_POLARITY

RFTX_PWR_ON

RFTX_PWR_OFF

RFTX_POLARITY

RFRX_PWR_ON

RFRX_PWR_OFF

RFRX_POLARITY

RFEON

SYLE

PAON

TX

TXSW

RXSW

RX,VREF

Figure 8. RF interface Control

Table 4. Timing and RF Interface Control Fields

Field Register Bank Ext

RFEON_POLARITY RX_PWR_CTRL 2 EXT6

HOP_ENABLE SSPSTATE 3 EXT2

SYLE_POLARITY CONFIG1 3 EXT0

TX_ENABLE SSPSTATE 3 EXT2

MOD_PWR_ON MOD_PWR_CTRL 2 EXT5

RFRX_PWR_ON/OFF RFRX_PWR_CTRL 0 EXT7

DEMOD_PWR_ON/OFF DEMOD_PWR_CTRL 2 EXT6

RFRX_POLARITY RFRX_PWR_CTRL 0 EXT7

RFTX_PWR_ON/OFF RFTX_PWR_CTRL 2 EXT7

RFTX_POLARITY RFTX_PWR_CTRL 2 EXT7

HAND_BASE_SEL SSP_STATUS 3 EXT3

29 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

Sleep Mode

To save the phone’s battery life on the handset, the

Z87001 can be operated in sleep mode while the phone is

not in use. The sleep mode is entered by software command. The sleep mode first needs to be enabled by setting

the SLEEP_WAKE field. Then a GO_TO_SLEEP command puts the processor to sleep by temporarily stopping

its clock. The sleep period can be set to last between 4 ms

and 1.02 s by programming the SLEEP_PERIOD field. In

sleep mode, the RFEON pin is de-asserted.

The processor comes out of sleep mode in one of two

ways. Either the sleep counter counts down to zero, or one

of the enabled pins from port P0 is asserted prior to normal

expiration of the counter. Four port pins (P0[0..4]) can be

individually enabled to provide the wake-up function by

setting the appropriate bits in P0_WAKE_ENABLE. Typically, these port pins are connected to the telephone keypad.

When the processor core wakes up, the software needs to

know how much time it was actually asleep, in order to restore synchronization to the base station’s hopping sequence. For that purpose, the current value of the sleep

counter is available to the processor in

SLEEP_REMAINING. A value of zero indicates normal expiration of the sleep counter.

In order to guarantee a good operation of the wake-up

pins, the wake-up signals are hardware-denounced by the

Z87001. Furthermore, these signals are internally synchronized to the bit clock. This ensures that the processor

has enough time (one bit time = 10.74 ms) to read a stable

value of the remaining sleep time and synchronize correctly to the base station’s hopping sequence.

Table 5. Sleep Mode Control Fields

Field Register Bank Ext

SLEEP_EAKE SSPSTATE

GO_TO_SLEEP SSPSTATE

SLEEP_PERIOD CONFIG2

SLEEP_REMAINING CONFIG2

P0_WAKEUP_ENABLE CONTROL

3 EXT2

3 EXT2

3 EXT1

3 EXT1

1 EXT6

ADPCM Processor Interface and Rate Buffers

The interface to the ADPCM Processor (Z87010) consists

of clock control, command/status interface and data interface. The data interface gives the ADPCM Processor access to the rate buffers.

Clock Interface

The Z87001 generates the Z87010 clock at 16.384 or

8.192 MHz, as set in VP_CLOCK. In addition, the clock

can be stopped and restarted with the VP_STOP_CLOCK

field in order to reduce power consumption (Note: a software handshaking between Z87001 and Z87010 is necessary before stopping and after restarting the clock).

In addition to providing the Z87010 main clock, the Z87001

generates a CODCLK signal which will be used by the codec and by the Z87010 to synchronize its data transfers

with the Z87001. On the base station, the CODCLK is simply obtained by dividing the 16.384 MHz input clock.

On the handset, the CODCLK is synchronized to the base

station’s CODCLK signal through the receive bit sync logic. This ensures that production and consumption of voice

data is happening at identical rates on handset and base,

eliminating buffer overrun and underrun situations.

Command/Status Interface

The Z87001 sends commands to the Z87010 through the

VP_COMMAND write-only field. It reads the Z87010 status in the VP_STATUS read-only field. Both fields are located at the same address in the Z87001 register interface. A communication protocol should be established in

software to ensure correct reception of all commands.

Dedicated hardware ensures data integrity when both

Z87001 and Z87010 simultaneously access the same register.

Table 6. ADPCM Processor Control Fields

Field Register Bank Ext

VP_CLOCK CONFIG1 3 EXT0

VP_STOP_CLCOCKS SSPSTATE 3 EXT2

VP_COMMAND VP_INOUT 2 EXT0

VP_STATUS VP_INOUT 2 EXT0

Data Interface and Rate Buffers

The digitized voice data is communicated between the

Z87001 and Z87010 through the rate buffers and ADPCM

Processor data interface. The transmit and receive rate

buffers each contain 36 4-bit nibbles.

To write to the transmit rate buffer, the Z87001 core processor must first set the nibble address in the

TX_BUF_ADDR register field, then write the nibble data

through TX_BUF_DATA. If the TX_AUTO_INCREMENT

bit is set, the address is automatically incriminated (modulo 51 = the number of nibbles in rate buffer + 15 additional

data words accessible through TX_BUF_DATA; for more

information, see Register Description) after each data

write. This allows the DSP core to write successive nibbles

without resetting the address each time.

30 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

OPERATION (Continued)

The operation of the receive rate buffer is identical. The

Z87001 core processor must set the nibble address in

RX_BUF_ADDR, then read the nibble from

RX_BUF_DATA. If the RX_AUTO_INCREMENT bit is set,

the read address is automatically incriminated (modulo 36

= number of nibbles in rate buffer) after each data read.

This allows the DSP core to read successive nibbles without resetting the address each time.

Through its register interface, the Z87001 also controls

which rate buffer addresses the Z87010 ADPCM Processor can access. The nibble addresses are contained in the

RX RATE BUFFER

Demodulator

Address

Decoder

TX_BUF_VP_ADDR and RX_BUF_VP_ADDR register

fields. After the Z87010 writes or reads a nibble to or from

transmit or receive rate buffer, the corresponding

“VP_ADDR” is automatically incriminated (modulo 36) to

the next accessible address. The locations of accessible

addresses are individually controlled by the Z87001 in the

three TX_RX_NIBBLE_MARKER register fields. A marker

bit equal to “1” enables the Z87010 to access the corresponding address; a bit equal to “0” causes the Z87010’s

read or write access to skip to the next nibble that has a

marker bit equal to “1”.

Z87001

RX_BUF_VP_ADDR

TX_RX_NIBBLE_

MARKER

TX_BUF_VP_ADDR

Modulator

RX_BUF_DATA

TX RATE BUFFER

ADPCM Proc.

Interface

TX_BUF_DATA

RX_BUF_ADDR

RX_AUTO_INCR.

TX_BUF_ADDR

TX_AUTO_INCR.

DSP Core

Processor

VP_COMMAND

VP_STATUS

Figure 9. Rate Buffers Access and ADPCM Processor Interface

Data

Addr

Ctrl

31 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

Table 7. Data and Control Access to Rate Buffers

Field Register Bank Next

RX_AUTO_INCREMENT RATE_BUF_ADDR 1 EXT0

RX_BUF_ADDR RATE_BUF_ADDR 1 EXT0

TX_AUTO_INCREMENT RATE_BUF_ADDR 1 EXT0

TX_BUF_ADDR RATE_BUF_ADDR 1 EXT0

RX_BUF_DATA RATE_BUF_DATA 1 EXT0

TX_BUF_DATA RATE_BUF_ADDR 1 EXT1

TX_BUF_DATA RATE_BUF_DATA 1 EXT1

RX_BUF_VP_ADDR RATE_BUF_DATA 1 EXT1

TX_BUF_VP_ADDR RATE_BUF_DATA 1 EXT1

TX_RX_NIBBLE_MARKER RATE_BUF_DATA 1 EXT1

ADDITIONAL FEATURES

Power Control

The Z87001 features several means of measuring and

controlling power levels. One input pin (RSSI) connects an

external “receive signal strength indicator” to a half flash 8bit ADC in the Z87001. This ADC is sampled once per

frame during the receive portion of the TDD cycle. The

RSSI value can be accessed in software in the

RSSI_DATA register field. With external multiplexing, the

8-bit ADC can be used for additional purposes.

The RSSI data is used by the software to implement adaptive power control. In order to determine whether the RSSI

information is made of signal or noise, the Z87001 includes

logic to measure the signal-to-noise ratio (SNR) of the receive signal. This SNR value is available at the end of every frame in the SNR_ESTIMATE register field. It is also

used by the adaptive frequency hopping algorithm to determine and avoid the noisy channels.

Finally, a 4-bit DAC (resistive ladder) is provided to control

RF power output level. The DAC is under software control

through register field TX_PWR_DAC_DATA.

Table 8. Power Control

General-Purpose I/O Ports

The Z87001 includes two general-purpose input/output

ports, P0 and P1, of 16 bit each. The direction of each bit

is independently programmable by setting the register

fields DIRECTION0 and DIRECTION1. Then, the software

can access the input and output values by accessing

DATA0 and DATA1.

Two pins of port P1 (pins 14 and 15), when configured in

input mode, also behave as interrupt pins for the core processor. The software can enable or disable each interrupt

by setting the INTERRUPT_0_ENABLE and

INTERRUPT_2_ENABLE fields. The interrupts are positive edge-triggered.

Pin

Number

P1 14 INT0 3FFFh

P1 15 INT2 3FFDh

Table 9. General-Purpose I/O Ports

Interrupt

Number

DSP Interrupt

Vector

Field Register Bank Ext

RSSI_DATA RSSI 2 EXT3

SNR_ESTIMATE RX_CONTROL 2 EXT1

TX_PWR_DAC_DATA CONTROL 1 EXT6

RSSI_DATA RSSI 2 EXT3

SNR_ESTIMATE RX_CONTROL 2 EXT3

DIRECTION0 GPI00DIR 3

DATA0 GPI00DATA 3

DIRECTION1 GPI0IDIR 3

DATA1 GPI0IDATA 3

INTERRUPT_0_ENABLE CONTROL 1

INTERRUPT_1_ENABLE CONTROL 1

Field Register Bank Ext

EXT4

EXT5

EXT6

EXT7

EXT6

EXT6

Four pins of port P0 (pins 0 to 3), when configured in input

mode, can also be individually programmed as wake-up

pins for the Z87001 (See “Sleep mode”, above).

32 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

REGISTER DESCRIPTION

The Z87001 DSP core processor has four banks of eight

registers mapped in the core processor’s “external register” space, as summarized in the following table.

Table 10. Register Summary

BANK ADDRESS REGISTER READ DESCRIPTION WRITE DESCRIPTION TABLE #

Bank 3 EXT0 CONFIG1 Clock Dividers, Use Core Bias,

SYLE polarity, search window

size, Bias Threshold

EXT1 CONFIG2 Remaining Sleep time ANT0/1 control, Sleep Period Table 26

EXT2 SSPSTATE Stop VP clock, Absent gain, Bias Enable, Tx Enable, Sync

Search control, Hop Enable, Frame Start control, Multiplex

control, Sleep mode control

EXT3 SSPSTATUS Frame Counter, Handset/Base,

Sync Search control, Frame

Start control

EXT4 GPIO0DIR General-Purpose I/O port 0 direction control Table 29

EXT5 GPIO0DATA General-Purpose I/O port 0 data Table 30

EXT6 GPIO1DIR General-Purpose I/O port 1 direction control Table 31

EXT7 GPIO1DATA General-Purpose I/O port 1 data Table 32

Bank 2 EXT0 VP_INOUT ADPCM Processor Status ADPCM Processor Command Table 33

EXT1 RX_CONTROL SNR estimate UW location Table 34

EXT2 BIAS_ERROR FCW value Table 35

EXT3 RSSI 8-bit ADC data (RSSI) Table 36

EXT4 CORE_BIAS Core Bias data Table 37

EXT5 MOD_PWR_CTRL MOD_PWR control Table 38

EXT6 DEMOD_PWR_CTRL RXSW, RFEON pin control Table 39

EXT7 RFTX_PWR_CTRL PAON pin control Table 40

Bank 1 EXT0 RATE_BUF_ADDR Rate Buffer address Table 41

EXT1 RATE_BUF_DATA Re Rate Buffer data Tx Rate Buffer data, control

data

EXT2 BIT_SYNC Bit Sync monitoring Bit Sync control Table 43

EXT3 RESERVED Table 44

EXT4 RESERVED Table 44

EXT5 RESERVED Table 44

EXT6 CONTROL INT, WAKEUP pin control, 4-bit DAC data (PWLV) Table 45

EXT7 RESERVED Table 46

Bank 0 EXT0 RESERVED Table 47

EXT1 RESERVED Table 47

EXT2 RESERVED Table 47

EXT3 RESERVED Table 47

EXT4 RESERVED Table 47

EXT5 RESERVED Table 47

EXT6 INT_SYM_ERR0 Bit Sync monitoring Table 47

EXT7 RFRX_PWR_CTRL TXSW, RXSW pin control Table 49

Table 25

Table 27

Table 28

Table 42

DS96WRL0800 P R E L I M I N A R Y 33

Z87001/Z87L01

ROMless Spread Spectrum Cordless Phone Controller Zilog

REGISTER DESCRIPTION (Continued)

The bank is selectable in software by writing to the core’s

status register (see Table 24). Once a bank is selected,

Table 11. Bank Switching

Bank Status Register Bank Function

Bank 0 xxxx xxxx x00x xxxx b Test point access, TDD switching control

Bank 1 xxxx xxxx x01x xxxx b Rate buffer access, miscellaneous

Bank 2 xxxx xxxx x10x xxxx b ADPCM processor interface, RF interface, etc.

Bank 3 xxxx xxxx x11x xxxx b Configuration, status, general-purpose port data and direction

each of the eight external registers (EXT0 through EXT7)

can be accessed by a single-cycle software instruction.

Bank 3 Registers

Table 12. Bank 3 Registers

Config 1

Field

RESERVED f--------------- R

VP_CLOCK -e--------------

USE_CORE_BIAS --d-------------

SYLE_POLARITY ---c------------

WINDOW_SIZE ----ba98--------

BIAS_THRESHOLD-------76543210

Notes:

1. VP_CLOCK. Internally synchronized to avoid glitches. Changes to this bit take effect immediately.

2. SYLE_POLARITY. Changes to this bit take effect immediately.

3. BIAS_THRESHOLD. The bias threshold must be coded as a negative value

(opposite of the threshold value) coded in 2’s complement. The nominal value for the

threshold is -46 (=D3h). Internally, this value is sign-extended to 13 bits.

Bank 3

Bit Position

EXT0

R/W Data Description

Returns 0

W

R

W0*

R

W0

R

W 0000

0001

•••

1111

R

W XXh

Must be set to 1

Controls CLKOUT output pin (clock for ADPCM Processor).

Returns 0

0

CLOCKOUT=16.384 MHz

1

CLOCKOUT = 8.192

Controls which bias value is used by the downconverter’s

NCO as part of the automatic frequency control loop (AFC)

Returns 0

Uses BIAS_ERROR_DATA value from AFC hardware

1

Uses CORE_BIAS_DATA value from DSP core

Controls the polarity of the SYLE output pin (hop pulse)

Returns 0

SYLE is a positive pulse

1

SYLE is a negative pulse

Defines the search window size (in bits) for windo wed search

mode (for Unique Word or SYNC_D words).

Returns 0

Window size=1

Window size =3 (1±1)

Window size = 31 (1± 15)

Bias estimator threshold value

Returns 0

Sets the bias value

34 P R E L I M I N A R Y DS96WRL0800

Z87001/Z87L01

1

Zilog ROMless Spread Spectrum Cordless Phone Controller

Table 13. Bank 3 Register EXT1

Config 2

Field

ANTENNA_SW_DEFEAT f---------------

ANTENNA_SW_OFFSET -edcba98--------