Zetex ZXCD1000EQ16TA, ZXCD1000EQ16TC Datasheet

DESCRIPTION

The ZXCD1000 provides complete control and

modulation functions at the heart of a high efficiency

high performance Class D switching audio amplifier

solution. In combination with Zetex HDMOS MOSFET

devices, the ZXCD1000 provides a high performance

audio amplifier with all the inherent benefits of Class D.

The ZXCD1000solution uses proprietarycircuit design

to realise the true benefits of Class D without the

traditional drawback of poor distortion performance.

The combination of circuit design, magnetic

component choice and layout are essential to realising

these benefits.

FEATURES

•

>90% efficiency

•

4 / 8 Ω drive capability

•

Noise Floor -115dB for solution

•

Flat response 20Hz - 20kHz

•

High gate drive capability ( 2200pF)

•

Very low THD + N 0.2% typical full 90% power, full

band ( for the solution)

•

Complete absence of crossover artifacts

•

OSC output available for sync in multi-channel

applications

•

Available in a 16 pin exposed pad QSOP package

APPLICATIONS

•

DVD Players

•

Automotive audio systems

•

Home Theatre

•

Multimedia

•

Wireless speakers

•

Portable audio

•

Sub woofer systems

•

Public Address system

The ZXCD1000 reference designs give output powers

up to 100W rms with typical open loop (no feedback)

distortion of less than 0.2% THD + N over the entire

audio frequency range at 90% full output power. This

gives an extremely linear system. The addition of a

minimum amount of feedback (10dB) further reduces

distortion figures to give < 0.1 % THD + N typical at

1kHz.

From an acoustic point of view, even more important

than the figures above, is that the residual distortion is

almost totally free of any crossover artifacts. This

allows the ZXCD1000 to be used in true hi-fi

applications. This lack of crossover distortion, sets the

ZXCD1000 solutions quite apart from most other

presently available low cost solutions, which ingeneral

suffer from severe crossover distortion problems.

ZXCD1000

ISSUE 2 - APRIL 2002

1

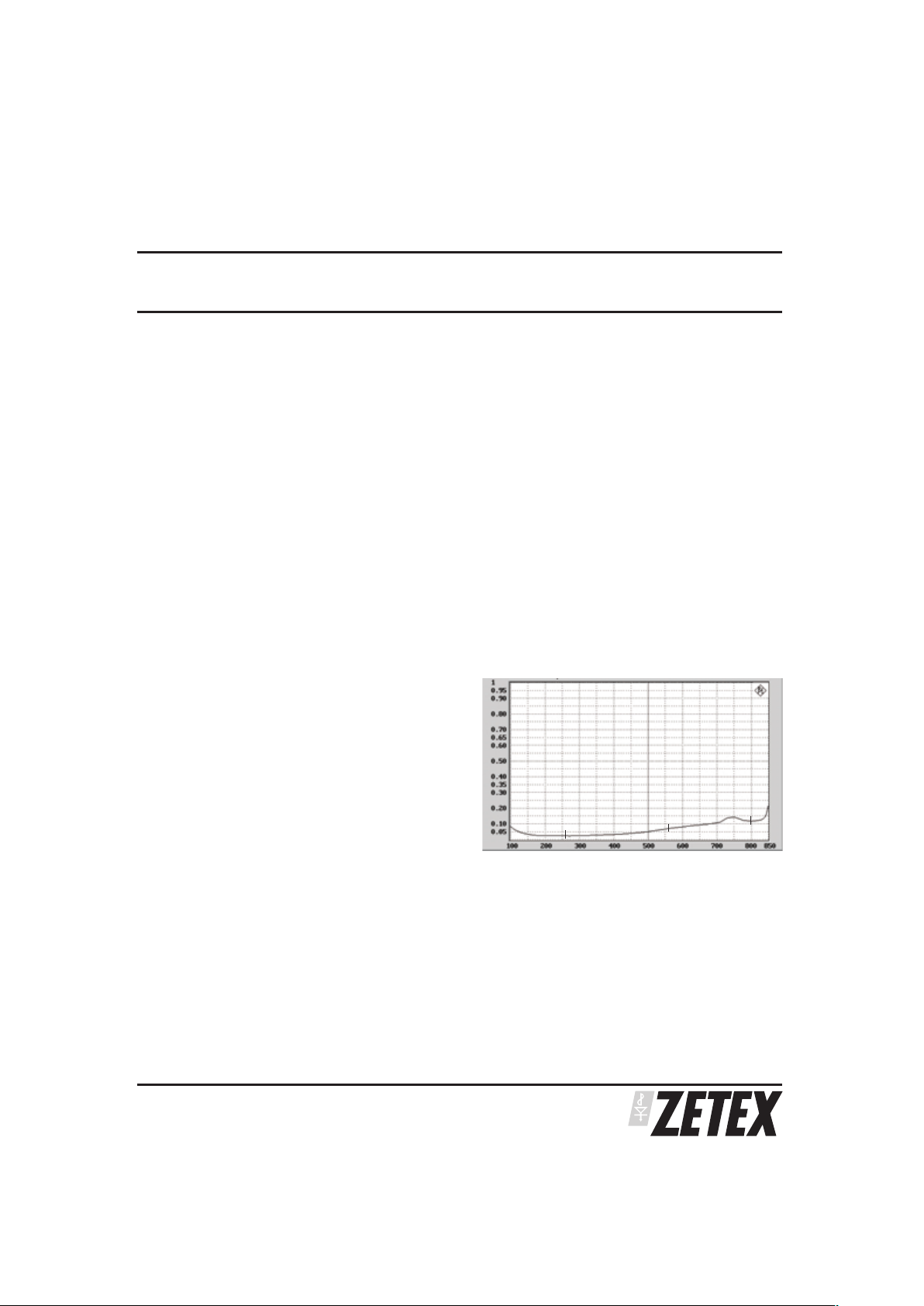

HIGH FIDELITY CLASS D AUDIO AMPLIFIER SOLUTION

Output Power

1W

5W

10W

THD + N (%)

Distortion v Power

8Ω open loop at 1kHz.

The plot shows Distortion v Power into an 8Ω load at

1kHz. This plot clearly demonstrates the unequalled

performance of theZetex solution. Typical distortionof

0.05% at 1Wcanbe seen with betterthan0.15% at 10W.

Truly world class performance.

ISSUE 2 - APRIL 2002

ABSOLUTE MAXIMUM RATINGS

Terminal Voltage with respect to G

ND

V

CC

20V

Power Dissipation 1W

Package Thermal Resistance (⍜ja)54⬚C/W

Operating Temperature Range -40⬚C to 70⬚C

Maximum Junction Temperature 125⬚C

Storage Temperature Range -50°C to 85⬚C

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.

These are stress ratings only, and functional operation of the device at these or any other conditions beyond

those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum

conditions for extended periods may affect device reliability.

ZXCD1000

2

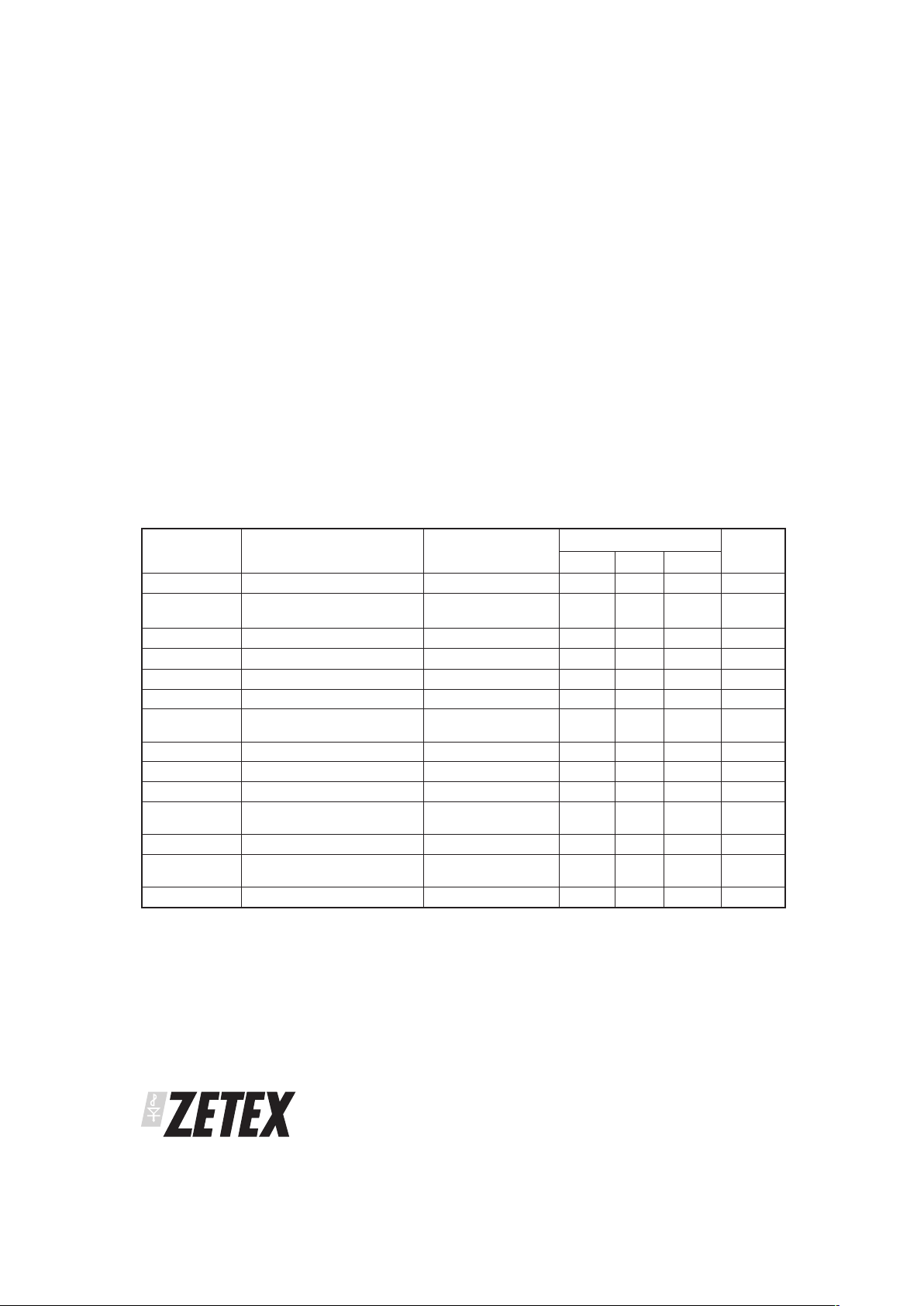

SYMBOL PARAMETER CONDITIONS

LIMITS UNITS

MIN TYP MAX

V

CC

Operating Voltage Range 12 16 18 V

I

ss

Operating Quiescent

Current

V

CC

= 12V

V

CC

= 18V, 16V

45

50

mA

mA

F

osc

Switching Frequency

C

osc

= 330pF

150 200 250 kHz

F

osc(tol)

Frequency Tolerance

C

osc

= 330pF

+/-25 %

Vol OutA/B Low level output voltage No load 100 mV

Voh OutA/B High level output voltage No load 7.5 V

T

Drive

Output Drive Capability

(OUTA/BRise/Fall)

Load Capacitance

= 2200pF

50 ns

5V5tol Internal Rail Tolerance 1µF Decoupling 5.23 5.5 5.77 V

9VA/Btol Internal Rail Tolerance 1µF Decoupling 8.32 8.75 9.18 V

Audio A / B Input Impedence 1.35k 1.8k 2.3k ⍀

Triangle

A/B

Input Impedence 1.35k 1.8k 2.3k ⍀

Audio A / B Bias Level 2.95 3.1 3.25 V

Triangle

A/B

Bias Level 2.95 3.1 3.25 V

Osc A / B Amplitude 0.89 1.05 1.2 V

ELECTRICAL CHARACTERISTICS

TEST CONDITIONS (unless otherwise stated) VCC= 16V, TA= 25⬚C

ZXCD1000

ISSUE 2 - APRIL 2002

3

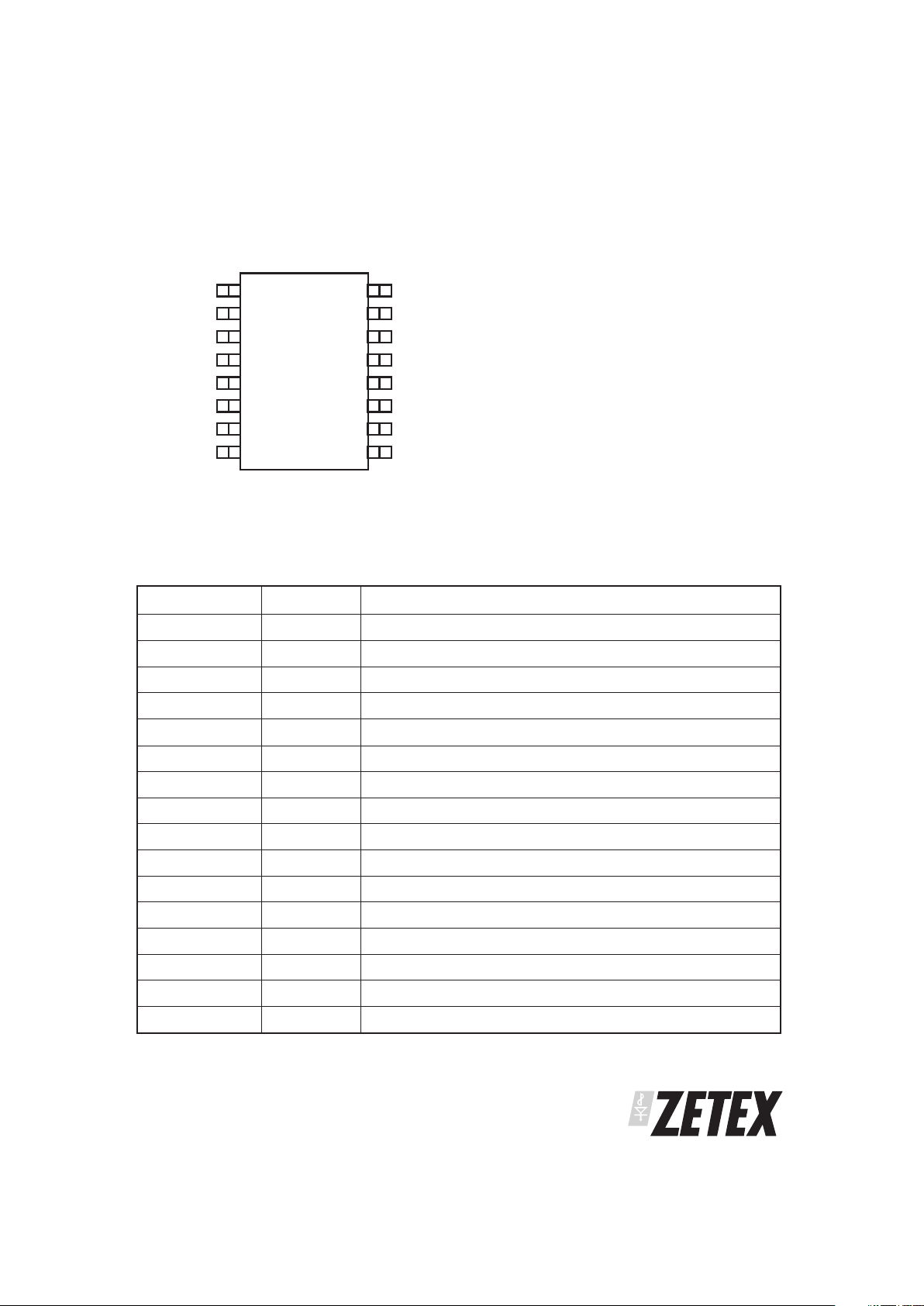

Audio A

Triangle A

Osc A

Dist

Cosc

Osc B

Triangle B

Audio B Gnd

Out B

Gnd2

9VB

VCC

9VA

Out A

5V5

1

2

3

4

5

6

7

89

10

11

12

13

14

15

16

Figure 1

Pin Connection Diagram

Pin number

Pin Name Pin Description

1 Audio A Audio Input for Channel A

2 Triangle A Triangle Input for Channel A

3 Osc A Triangle Output

4 Dist No connection

5

C

osc

External timing capacitor node (to set the switching frequency)

6 Osc B Triangle Output (for slave ZXCD1000 in stereo application)

7 Triangle B Triangle Input for Channel B

8 Audio B Audio Input for Channel B

9 Gnd Small Signal GND

10 OUT B Channel B PWM Output to drive external Bridge MOSFETs

11 Gnd2 Power GND (for Output Drivers)

12 9VB Internal Supply Rail (Decouple with 1µF Cap)

13 VCC Input Supply Pin (Max = 18V)

14 9VA Internal Supply Rail (Decouple with 1µF Cap).

15 OUT A Channel A PWM Output to drive external Bridge MOSFETs

16 5V5 Internal Supply Rail (Decouple with 1µF Cap)

Pin Description

ISSUE 2 - APRIL 2002

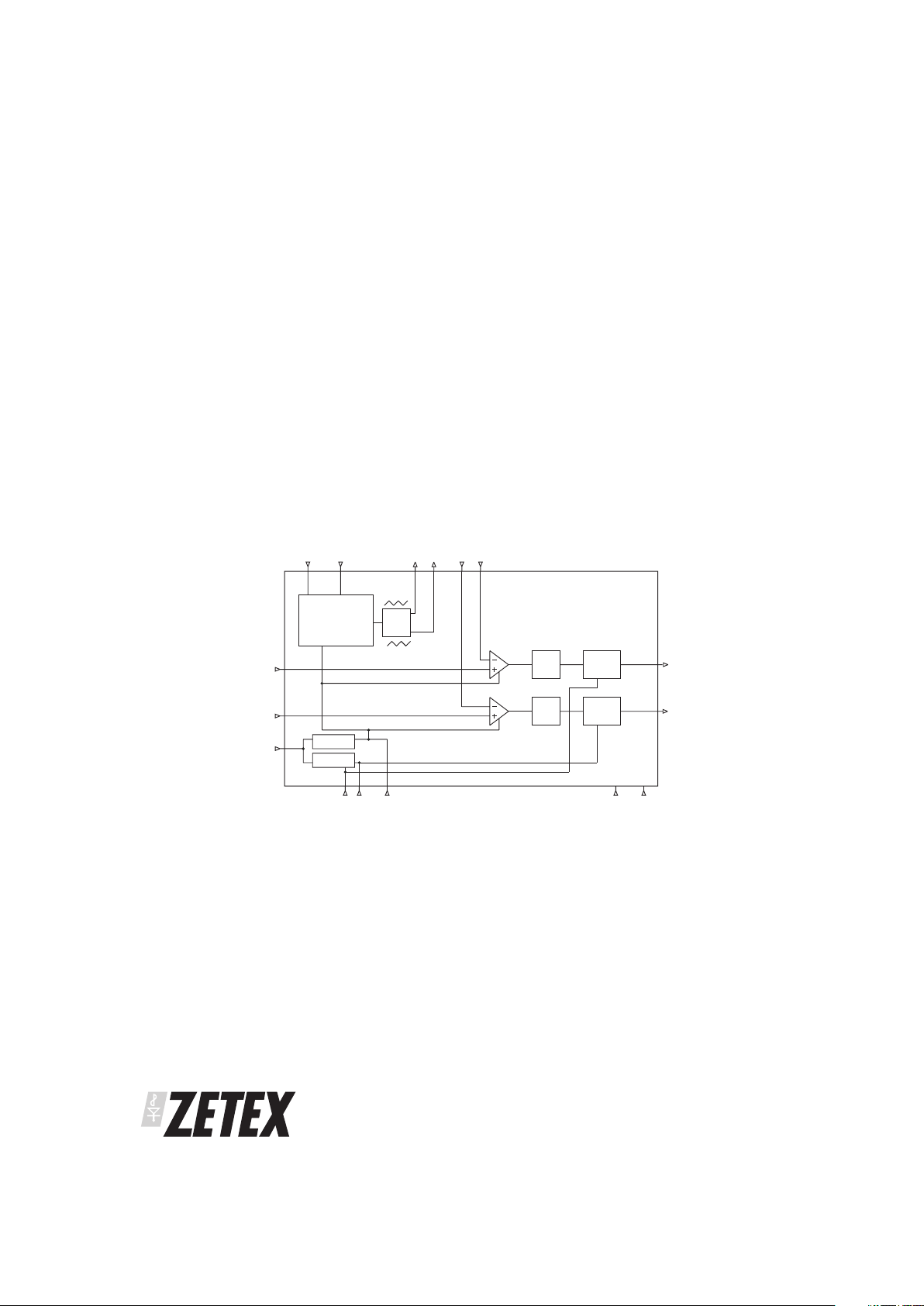

ZXCD1000 Class D controller IC

A functional block diagram of the ZXCD1000 is shown

in Figure 2. The on chip series regulators drop the

external VCCsupply (12V-18V) to the approximate 9V

(9VA/9VB) and 5.5V (5V5) supplies required by the

internal circuitry.

A triangular waveform is generated on chip and is

brought out at the OscA and OscB outputs. The

frequency of this is set (to ~200kHz) by an external

capacitor (C

osc

) and on chip resistor. The triangular

waveform mustbe externallyAC coupled back into the

ZXCD1000 at the TriangleA and TriangleB inputs.

AC coupling ensures symmetrical operation resulting

in minimal system DC offsets. TriangleA is connected

to one of the inputs of a comparator and TriangleB is

connected to oneof the inputs ofasecond comparator.

The other inputs of these two comparators are

connected tothe AudioA andAudioB inputs, which are

anti-phase signals externally derived from the audio

input. The triangular wave is an order higher in

frequency than the audio input (max 20kHz). The

outputs of the comparators toggle every time the

TriangleA/B and the (relatively slow) AudioA/B signals

cross.

ZXCD1000

4

Oscillator & Ramp

Generator

Internal 5V5

Internal 9V

PWM

Comp A

PWM

Comp B

PreDriver

PreDriver

O/P

Driver

O/P

Driver

Audio A

Audio B

V

CC

Cosc

Out A

Out B

5V5

9VB

9VA

Triangle B

Triangle A

Osc B

Osc A

Dist

Gnd

Gnd2

1

2345 67

8

9

10

1112

13

14

15

16

Osc

Buffers

Figure 2.

Functional Block Diagram

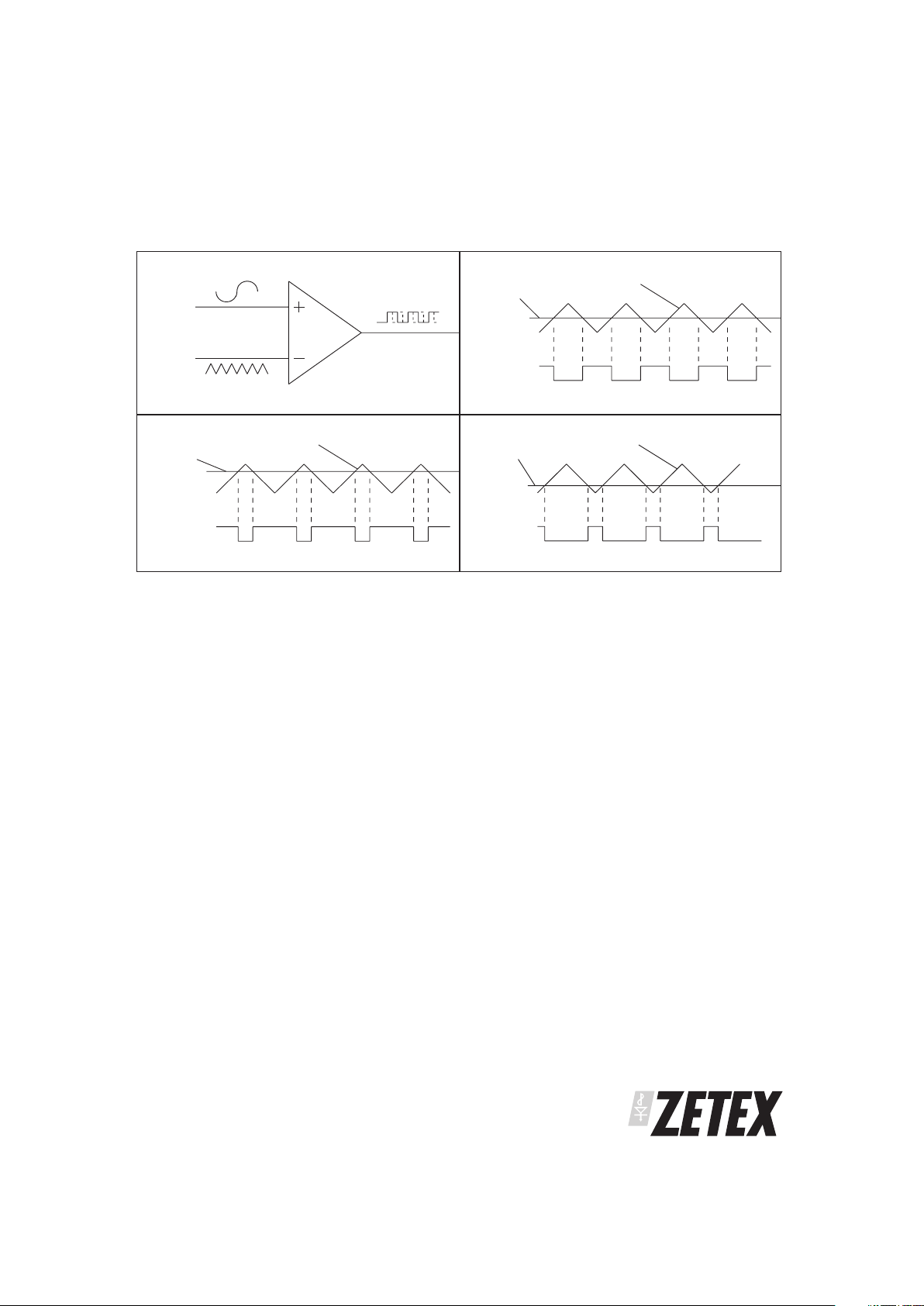

With no audio input signal applied, the AudioA/B

inputs are biased at the mid-point of the triangular

wave, and the duty cycle at the output of the

comparators is nominally 50%. As the AudioA/Bsignal

ascends towards the peak level, the crossing points

with the (higher frequency) triangular wave also

ascend. The comparator monitoring these signals

exhibits acorresponding increase in output duty cycle.

Similarly, as the AudioA/B signal descends, the duty

cycle is correspondingly reduced. Thus the audio input

Pulse Width Modulates the comparator outputs. This

principle is illustrated in Figures 3a, b, c and d. The

comparator outputs are buffered and used to drive the

OutA and OutBoutputs.Theseinturn drive the speaker

load (withthe audio information containedin the PWM

signal) via the off chip output bridge and single stage

L-C filter network.

The ramp amplitude is approximately 1V. The AudioA,

AudioB, TriangleA and TriangleB inputs are internally

biased to a DC voltage of approximately VCC/5. The

mid - point DC level of the OscA and OscB triangular

outputs is around 2V. The triangular wave at the Cosc

pin traverses between about 2.7Vand 3.8V and the dist

pin exhibits a roughly square wave from about 1.4V to

2V. (The above voltages may vary in practice and are

included for guidance only).

ZXCD1000

ISSUE 2 - APRIL 2002

5

Audio A/B

Triangle A/B

PWM Comparator

O/P

Audio A/B

Triangle A/B

Comparator O/P

(Duty Cycle = 50%)

O/P

Audio A/B

Triangle A/B

Comparator O/P

(Duty Cycle = 75%)

Audio A/B

Triangle A/B

Comparator O/P

(Duty Cycle = 25%)

Figure 3b.

Figure 3a.

Figures 3a,3b,3c and 3d

The audio input Pulse Width Modulates the comparator output.

Figure 3c. Figure 3d.

Loading...

Loading...