2000 C-Li ne Projecti on TV

,Q

Zp94 & ZP95

7 HFKQLFDO7UDLQLQJ0DQXDO

3URGXFW2YHUYLHZ

&KDVVLV'HVFULSWLRQV

)DFWRU\6HWXS

&RQYHUJHQFH

&LUFXLW7URXEOH6KRRWLQJ

3ULQ WHG

C

86$

=HQLWK(OHFW URQLFV&RUSRUDWLRQ

ZENITH ELECTRONICS CO R PORAT I O N

201 JAMES RECORD ROAD HUNTSVILLE, AL. 35824

CONTENTS

Safety Information ........................................................................................................ 1

General Information ........................................................................................................ 5

Service Menus ........................................................................................................ 8

Convergence Setup ........................................................................................................ 15

Circuit Descriptions ........................................................................................................ 28

Troubleshooting ........................................................................................................ 90

PRODUCT SAFETY SERVICING GUIDELINES FOR AUDIO-VIDEO PRODUCTS

9

IMPORTANT SAFETY NOTICE

This manual was prepaired for use only by proporly trained audio-visual service

technicians.

When servicing this product, under no circumstances should the original design be

modified or altered without permission from Zenith Electronics Corporation. All

components should be replaced only with types identical to those in the original

circuit and their physical location, wiring and lead dress must conform to original

layout upon completion of repairs.

Special components are also used to prevent x-radiation, shock and fire hazard. These

components are indicated by the letter x included in their component designators

and are required to maintain safe performance. No deviations are allowed without

prior approval by Zenith Electronics Corporation.

Circuit diagrams may occasionally differ from the actual circuit used. This way,

implementation of the latest safety and performance improvement changes into the

set is not delayed until the new service literature is printed.

Caution: Do not attempt to modify this product in any way. Never perform

customized installations without manufacturers approval. Unauthorized modifications

will not only void the warranty, but may lead to property damage or user injury.

Service work should be performed only after you are thoroughly familiar with these

safety checks and servicing guidelines.

Graphic symbols

The exclamation point within an equilateral triangle is intended

to alert the service personnel to important safety information in

the service literature.

The lightning flash with arrowhead symbol within an equilateral

triangle is intended to alert the service personnel to the presence

of noninsulated dangerous voltage that may be of sufficient

magnitude to constitute a risk of electric shock.

The pictorial representation of a fuse and its rating within an

equilateral triangle is intended to convey to the service

personnel the following fuse replacement caution notice:

CAUTION: FOR CONTINUED PROTECTION AGAINST RISK OF

$

SERVICE INFORMATION

While servicing, use an isolation transformer for protection from AC line shock.

After the original service problem has been corrected, make a check of the following:

FIRE AND SHOCK HAZARD

1. Be sure that all components are positioned to avoid a possibility of

2. Verify that all protective devices such as insulators, barriers, covers,

3. Soldering must be inspected to discover possible cold solder joints,

4. Check for physical evidence of damage or deterioration to parts and

5. No lead or component should touch a receiving tube or a resistor rated at

6. After re-assembly of the set, always perform an AC leakage test on all

FIRE, REPLACE ALL FUSES WITH THE SAME TYPE AND

RATING AS MARKED NEAR EACH FUSE.

adjacent component shorts. This is especially important on items transported

to and from the repair shop.

shields, strain reliefs, power supply cords, and other hardware have been

reinstalled per the original design. Be sure that the safety purpose of the

`polarized line plug has not been defeated.

solder splashes, or sharp solder points. Be certain to remove all loose

foreign particles.

components, for frayed leads or damaged insulation (including the AC

cord), and replace if necessary.

1 watt or more. Lead tension around protruding metal surfaces must be

avoided.

exposed metallic parts of the cabinet (the channel selector knobs, antenna

terminals, handle and screws) to be sure that set is safe to operate without

danger of electrical shock. DO NOT USE A LINE ISOLATION

TRANSFORMER DURING THIS TEST. Use an AC voltmeter having 5000

ohms per volt or more sensitivity in the following manner: Connect a 1500

ohm, 10 watt resistor, paralleled by a .15 mfd 150V AC type capacitor between

a known good earth ground (water pipe, conduit, etc.) and the exposed metallic

parts, one at a time. Measure the AC voltage across the combination of 1500

ohm resistor and .15 mfd capacitor. Reverse the AC plug by using a nonpolarized adaptor and repeat AC voltage measurements for each exposed

metallic part. Voltage measured must not exceed 0.75 volts RMS. This

corresponds to 0.5 milliamp AC. Any value exceeding this limit constitutes

a potential shock hazard and must be corrected immediately.

PRODUCT SAFETY

A.C. VOLTMETER

Good earth ground

0.15uf

such as a water

pipe, conduit, etc.

1500 Ohm

10 Watt

X-RADIATION

1. Be sure procedures and instructions to all service personnel cover the subject of

x-radiation. The only potential source of x-rays in current TV receivers is the

picture tube. However, this tube does not emit x-rays when the HV is at the

factory-specified level. The proper value is given in the applicable schematic.

Operation at higher voltages may cause a failure of the picture tube or highvoltage supply and, under certain circumstances, may produce radiation in excess

of desirable levels.

2. Only factory-specified CRT anode connectors must be used.

3. It is essential that the service personnel have available an accurate and

reliable high-voltage meter.

4. When the high-voltage circuitry is operating properly, there is no possibility

of an x-radiation problem. Every time a color chassis is serviced, the

brightness should be run up and down while monitoring the high voltage

with a meter, to be certain that the high voltage does not exceed the

specified value and that it is regulating correctly.

5. When troubleshooting and making test measurements in a product with a

problem of excessively high voltage, avoid being unnecessarily close to

the picture tube and the high voltage power supply. Do not operate the

product longer than necessary to locate the cause of excessive voltage.

6. Refer to HV, B+, and shutdown adjustment procedures described in the

appropriate schematics and diagrams (where used).

IMPLOSION

1. All direct view picture tubes are equipped with an integral implosion

protection system; take care to avoid damage during installation.

2. Use only the recommended factory replacement tubes.

TIPS ON PROPER INSTALLATION

1. Never install any receiver in a closed-in recess, cubbyhole, or closely

fitting shelf space over, or close to, a heat duct, or in the path of heated

air flow.

2. Avoid conditions of high humidity such as: outdoor patio installations

where dew is a factor, near steam radiators where steam leakage is a factor,

etc.

3. Avoid placement where draperies may obstruct venting. The customer

should also avoid the use of decorative scarves or other coverings that

might obstruct ventilation.

4. Wall- and shelf-mounted installations using a commercial mounting kit

must follow the factory-approved mounting instructions. A product mounted

to a shelf or platform must retain its original feet (or the equivalent

thickness in spacers) to provide adequate air flow across the bottom. Bolts

or screws used for fasteners must not touch any parts or wiring.

Perform leakage tests on customized installations.

5. Caution customers against mounting a product on a sloping shelf or in a

tilted position, unless the receiver is properly secured.

6. A product on a roll-about cart should be stable in its mounting to the cart.

Caution the customer on the hazards of trying to roll a cart with small

casters across thresholds or deep pile carpets.

7. Caution customers against using a cart or stand that has not been listed

by Underwriters Laboratories, Inc. for use with its specific model of

television receiver or generically approved for use with TVs of

the same or larger screen size.

8. Caution customers against using extension cords. Explain that a forest of

extensions, sprouting from a single outlet, can lead to disastrous

consequences to home and family.

Place this probe

on each exposed

metal part

1

PRODUCT SAFTEY

CHASSIS HIGH VOLTAGE ADJUSTMENT

PROCEDURE

1. Connect High Voltage meter to FBT High

Voltage output. Connect Ground of High Voltage

meter to CRT Ground or FBT Ground.

2. Check that the High Voltage adjustment VR

(RH44) is set to its mechanical center on the

Deflection PWB. This VR is located just behind

the Flyback transformer as viewed from the

Front of the set. (See diagram below)

3. Receive an NTSC generator signal. (Picture

should be stationary for this adjustment.

4. Video Controls should be set to Factor Settings.

5. Adjust the High Voltage to the following specifications by turning RH44 slowly.

6. Lock Paint the control. If available.

TH01

Checking Procedure :

1. Check that the picture is turned off and the

horizontal deflection circuit stops operation.

After Checking:

1. Unplug set and Remove Jig. Allow set to remain

in the off condition for at least 15 seconds.

2. Apply AC and confirm the set returns to normal

operation.

CH30

+50V Pulse

DH24

RH54

RH55

Add JIG to check Hi

Volt Limit Ci r c uit

JIG = 1k ohm 1/8W

DH31

FBT

RH44

High Voltage ADJ.

CHASSIS HIGH VOLTAGE LIMITER

CHECK

Check Preparation:

1. The set can face any direction.

2. Receive the Cross-Hatch Signal

3. VIDEO CONTROLS: Brightness to Maxi-

mum.

4. SCREEN FORMAT: Should be PROGRES-

SIVE mode.

5. Attach the JIG (1k ohm 1/8W resistor) to both

ends of DH31 as shown in the diagram below.

(See Diagram)

CHASSIS FLYBACK PROTECTION

CIRCUIT CHECK

Check Preparation:

1. The set can face any direction.

2. Receive the Cross-Hatch Signal

3. VIDEO CONTROLS: Factory Preset.

4. SCREEN FORMAT: Should be PROGRES-

SIVE mode.

5. Attach a 100 K ohm 1/16W ~ 1/8W resistor

between QP02 base and Gnd. (SD4 connector

Pin 4) and check operation.

After Checking:

1. Unplug set and Remove Jig. Allow set to remain

in the off condition for at least 15 seconds.

2. Apply AC and confirm the set returns to normal

operation.

2

CHASSIS SWEEP LOSS DETECTION

CIRCUIT CHECK

Check Preparation:

Check Number (1):

1. The set can face any direction.

2 Receive the Cross-Hatch Signal

3. VIDEO CONTROLS: Factory Preset.

4. SCREEN FORMAT: Should be PRO-

GRESSIVE mode.

5. Attach the JIG (A) (100 ohm 1/8W resistor) to

right hand side of RN01 and to Ground as

shown in the diagram below.

Check Number (2):

1. The set can face any direction.

2. Receive the Cross-Hatch Signal

3. VIDEO CONTROLS: Factory Preset.

4. SCREEN FORMAT: Should be PRO-

GRESSIVE mode.

5. Attach the JIG (B) (100 ohm 1/8W resistor) to

right hand side of RN11 and to Ground as

shown in the diagram below.

PRODUCT SAFETY

Checking Procedure :

1. Check that the picture is turned off in either

check.

After Checking:

1. Remove Jig after each check.

2. Confirm the set returns to normal operation.

&1 &1

3

PRODUCT SAFTEY

$

+9&DEOH

'()/(&7,21

3 : %

)%7

&211(&725

Perform the following when the

HV connector (anode connector) is removed or inserted for

CPT replacement, etc.

12'(

7$%

326,7,21

),*%

)O\EDFN

3. Remove the connector slowly by pulling it away

from the case.

+9&DEOH

%RRW$VVHPEO\

/(667+$1PP

)O\EDFN

386+

386+

),*$

During Removal

1. Roll out silicon cover from FBTs contact

area slowly.

2. While turning the connector about 90 degrees following the arrow (0 position). Push the

connector slightly toward the case. (Fig. A)

4

During Insertion

1. Please refer to direction for insertion as

shown in Fig. B (L position). Insert connector

until CLICK sound is heard.

2. Make sure the connector is pressed right in,

so that it has a good contact with the spring.

3. Confirm the contact by pulling the connector

slightly. (Dont pull hard because it may damage

the connector).

4. Cover the high voltage output by carefully

pushing silicon boot onto it. (Dont turn the

connector).

Note: Make sure the silicon boot is covering the

high voltage output.

GENERAL INFORMATION

SPECIFICATIONS FOR IQB-94/95 SERIES MODELS

Model:

Cathode-Ray

Tu be :

Power Input

Power

Consumption:

Antenna

Impedence:

Receiving

Channel:

Interm ediate

Freque ncy:

Video Input:

Video O utput:

IQC50H94/95 IQC60H94/95

R = P 16LFM00RFA(LU)

G = P16LFM00HHA(LU) Max Output - 2 4 Watt

B = P 16LFM00BMB(EU)

120 Volt AC, 6OHz

224/232 Watts - Maximum

192/206 Watts Operating

75ohm Unbalanced

VFH / UHF / CAT V

BAND

VHF 2-13

UHF 14-69 Height 52 60 1/2

EXT. Mid (A-5)~(A-1),4+ Width 43 1/2 51 1/2

CATV Mid A~I Depth 23 1/2 26 1/2

CATV Super J~W Weight 190 308

CAT V Hyper (W+1) (W+28) Power Supply P.W.B. C.P.T. (B) P.W.B

Picture I-F Carrier 45.75 MHz VM P.W.B C.P.T . (G) P.W.B.

Sound I-F Carrier 41.25 MHz Surround P.W.B C.P.T . (R) P.W.B.

Color Sub Carrier 42.17 MHz Signal P.W.B. Power/Deflection P.W.B.

1 Volt p-p, 75 Ohm Audio Out P.W.B. Control P.W.B.

1 Volt p-p, 75 Ohm (Y) 2H P.W.B Terminal P.W.B

07. Volt p - p , 7 5 Ohm, ( Cb, Cr) Sensor Dist P.W .B. Sub Deflectio n P. W.B.

1 Volt p-p, 75 Ohm

CH (12cm) Round

Audio Input:

Stereo Audio Output:

Audio O utput P ower:

Anode Vo ltage:

Brightness

Ful l W hi te 50"

Brig htnes s Max 60"

Speakers:

Dimension:

Circuit Board

Assemblies:

Size

470 mVrms, 47 k Ohm

470 mVrms, 1 k Ohm

Front- 12 Watt at 10% distortion, 8 Ohm Imp.

30.0 +

1.5kv (1.25 + 0.2ma)

ZP94 ZP95

130 130

100 100

2 woofers - 5 Inch

50" Series Models

60" Series Models

5

GENERAL INFORMATION

General Information

In 2000 Zenith will introduce a new C line of

Digital Ready Projection TVs. This new line will

help move Zenith forward with its goal to be the

Digital Leader in consumer electronic products and

reaffirm its continued commitment to supply

innovative and high quality products to our

customers. In this manual we will discuss the new

features and designs incorporated in the new

chassis line and newly designed cabinets in an

effort to enable our ASCs to offer better service

to our customers in the event that they require

service on their Zenith product.

The new C line ZP chassis family will be broken

down into service modules as follows: Power/

Deflection P.W.B., Main Chassis (Signal P.W.B.),

Signal Sub. P.W.B., VM P.W.B. Jack Pack and SP

Matrix (Audio) P.W.B. module. The new

Projection TV line will continue to be supported

to the modular level, which means that the repairs

to these units will be done by properly diagnosing

a defective module and replacing it. Since the

Projection TV line will be supported to the

modular level there will be no need to get prior

approval from Tech Support for defective module

replacement.

Remote Access

When using the MBR for customer menus, it must

be placed in the TV mode (by pressing the TV

button at the top). The customer menu is a bar of

ICONS at the top of the customer menu display.

By pressing the menu key you can select which

menu to use. Use of the Up/Down small arrows

allows the sub menu or feature item to be selected.

To adjust or change a feature selection you use the

Left/Right small arrows. Pressing the enter key

usually allows you to exit the customer menu.

<<

figure 1>>

Video Performance

Mechanical features include a Delta 78 lens

system, single piece Fresnel screen with special

cut of the front and back to add in distortion

reduction when moving from one viewing position

to another. The screen also incorporates vertical

black strip matrixing which gives an increased

contrast ratio. Finally the set comes with the tinted

screen protector already installed to prevent

damage to the screen. (scratches and cracks)

Electrical Features include a 3 line comb filter for

processing incoming signals to provide fine detail

images. Auto skin tone circuitry automatically

maintains natural skin tones. Black level

enhancement, white level, and peak white level

compression circuitry maintains black/white

contrast ratio and peak luminance level for detail

in both light and dark video areas. All these features

work together to provide a resolution level of 1000

lines on the ZP94/95 series.

MBR3475Z

924-10068

6

GENERAL INFORMATION

9

$

$

SOURCE

SOURCE

MENU

EXIT

TV / VIDEO

Source Selector

R

AUDIO

TO HI-FI

L

-VOLUME+

65

To

Converter

ANT A

ANT B

-CHANNEL+

POWER

65

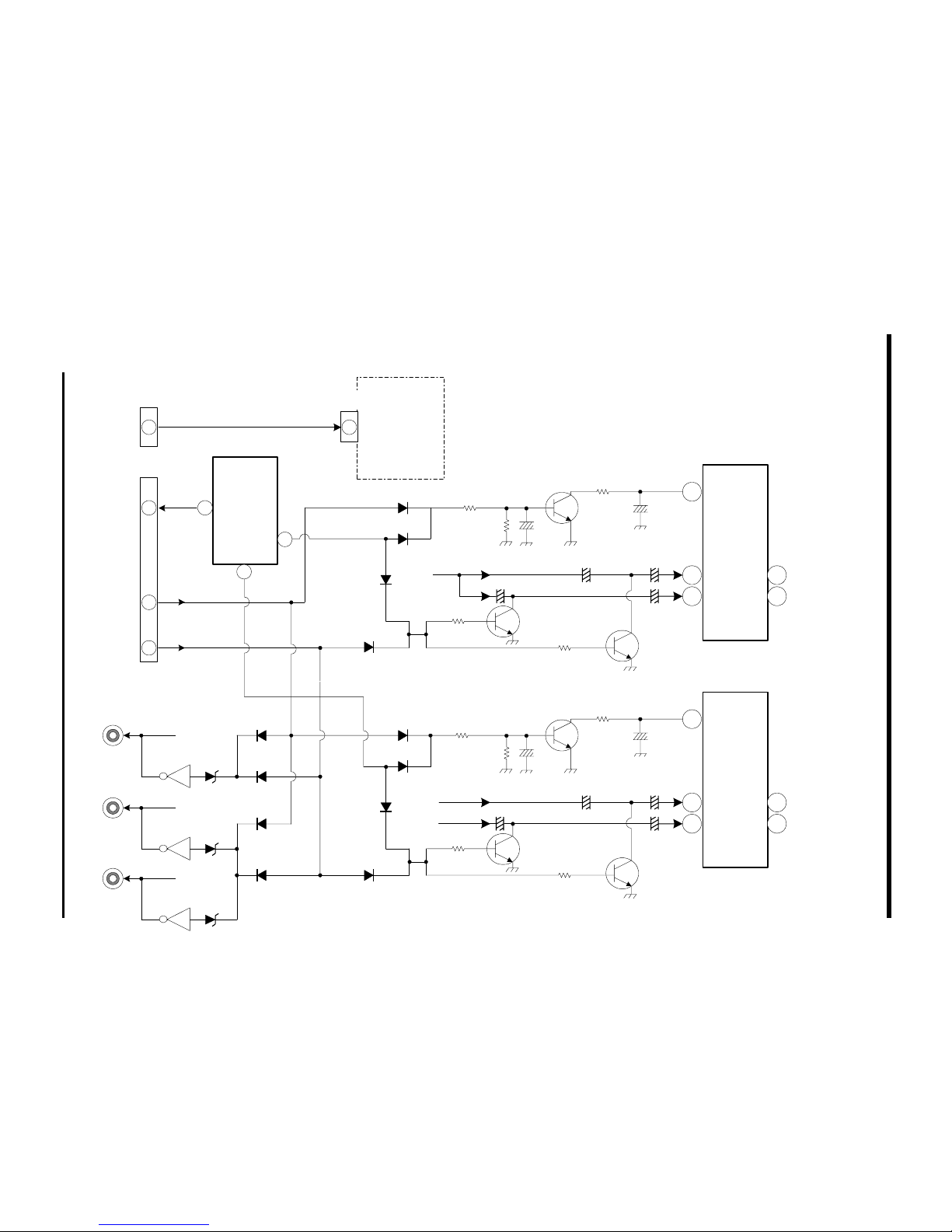

<<figure 2. Control Panel>>

S-VIDEO

VIDEO

(MONO)

AUDIO

INPUT 1

R

S-VIDEO

VIDEO

Y

(MONO)

P

BCB

L

PRC

R

AUDIO

INPUT 2

L

R

P

PRC

DIGITAL

SETUP

DIGITAL CONVERGENCE

SETS ONLY

S-VIDEO

VIDEO

Y

(MONO)

BCB

R

R

AUDIO

MONITOR

OUT

69,'(2

,'(2

/()7

8',2

5,*+7

8',2

<<figure 3 Rear Connection Panel>>

7

SERVICE MENUS

Service Menu Access

To access the service menu on the ZP94/95 series;

1. Press and hold the SOURCE button on the user control panel at the front of the set.

2. While holding the SOURCE button, press the POWER button on the user control panel at the front of

the set to activate the service menu.

3. Receive signal on main picture.

4. Check the service menu items according to the following tables, using the up and down buttons on

Remote Control.

5. Press MENU key to exit service menu adjustment mode.

NOTE:

1. If there is a different value than shown in table above, for fixed data, adjust it using buttons (only

in this case).

2. When exchanging microprocessor and TV is turned on for first time, it requires initialization of

VIDEO CHROMA ADJ on P1 to P6.

8

SERVICE MENUS

ITEM S ETTING

P01 ZP94/95

ADJUST MODE Ve r sion 704

SUB BRT 3C-C3 Sub Brightness

SERVI CE 0 SERVICE

DEF RESET 0

V/P RESET 0

3DYC RESET 0

FLEX RESET 0

DSP RESET 0

CCD RESET 0

FACT RESET 0 Resets Memory

MEMORY INITIAL 0 Resets Memory

P02 ZP94/95

ADJUST MODE

TA1300 31.5khz M 315

H POSI 40 00-7F Horizontal Position

FLEX CONT

VD POS 3F 00-7F Vertical Position

UPD64081

DYGA 09 00-0F Y Motion Detection Gain

DCGA 06 00-0F Chroma Motion Detection Gain

VAPGA 00 00-07 Vertical Aperture Co ntrole Gain

VAPIN 00 00- 1F Vertical Aperture Controle Invert

YHCOR 00 00- 01 Y Outp ut High Frequency Coring

P02 ZP94/95

ADJUST MODE

RANGE DESCRIPTION

*Non-Adjustable Data

TA1300 33.75kh z M 3375

H POSI 40 00-7F Horizontal Position

FLEX CONT

VD POS 3F 00-7F Vertical Position

UPD64081

DYGA 09 00-0F Y Motion Detection Gain

DCGA 06 00-0F Chroma Motion Detection Gain

VAPGA 00 00-07 Vertical Aperture Co ntrole Gain

VAPIN 00 00- 1F Vertical Aperture Controle Invert

YHCOR 00 00- 01 Y Outp ut High Frequency Coring

P03 ZP94/95

ADJUST MODE

TA1270-M

TINT (TV) 3C 00-7F Main NTSC Tint

TOFFO (TV) 00 00-07 Main NTSC TOF fO Peak Frequency Switch

TOFQ (TV) 00 0 0- 07 Main NTSC TOFQ Switch

SUB CNT 0F 00-1F Main NTSC Contrast

SUB CL 1B 00-1F Main NTSC Color

P03 ZP94/95

ADJUST MODE

TA1270-S

TINT (TV) 3C 00-7F Main NTSC Tint

TOFFO (TV) 00 00-07 Main NTSC TOF fO Peak Frequency Switch

TOFQ (TV) 00 0 0- 07 Main NTSC TOFQ Switch

SUB CNT 0F 00-1F Main NTSC Contrast

SUB CLR 1B 00-1F Mai n NT SC Color

9

SERVICE MENUS

ITEM S ETTIN G

P04 ZP94/95

FLEX CONT NTSC

39 HHPF1 00 00-01 Characteristic Switch 0 = Low Frequency, 1 = High Frequency

41 V-CRG 00 00-03 Vertical Enhance Coring

42 H-CRG 00 00-03 Horizontal Enhance Coring

43 V-ENH 00 00-03 Vertical Enhance

44 H-ENH 00 00-03 Horizontal Enhance

96 YVHENH 0B 00-1F Y Vertical & Horizontal Enhance Gain

100 CVHENH 12 00-1F Color Vertical & Horizontal Enhance Gain

P04 ZP94/95

FLEX CONT ATSC (480i, 480p, 1080i, 720p)

39 HHPF1 00 00-01 Characteristic Switch 0 = Low Frequency, 1 = High Frequency

41 V-CRG 00 00-03 Vertical Enhance Coring

42 H-CRG 00 00-03 Horizontal Enhance Coring

43 V-ENH 00 00-03 Vertical Enhance

44 H-ENH 00 00-03 Horizontal Enhance

96 YVHENH (720p 00 (10) 00 -1F Y Vertical & Horizontal Enhance Gain

100 CVHENH 12 00-1F Color Vertical & Horizontal Enhance Gain

P05 ZP94/95

FLEX CONT NTSC

71 YV-ENH 00 00-0F Y Vertical Enhance Gain

79 CV-ENH 00 00- 0F Color Vertical Enhance Gain

87 YH-ENH 07 0 0-0F Y Hor izontal En hance Gain

94 CH-ENH 0F 00-0F Color Horizontal Enhance Gain

66 YV-DSB 00 00-03 Y Vertical Dynamic Shoot Balance Gain

75 CV-DSB 00 00-03 Color Vertical Dynamic Shoot Balance Gain

82 YH-DSB 00 00-03 Y Ho rizontal Dynamic Shoot Balance Gain

90 CH-DSB 00 00-03 Color Horizontal Dynamic Shoot Balance Gain

69 YV-CLP 00 00-0F Y Vertical Enhance Clip Offset

84 YH-CLP 00 00-0F Y Hor izontal Enhance Clip Of fset

P05 ZP94/95

FLEX CONT ATSC (480i, 480p, 1080i, 720p)

71 YV-ENH 00 00-0F Y Vertical Enhance Gain

79 CV-ENH 00 00- 0F Color Vertical Enhance Gain

87 YH-ENH (1080i 07 (00) 00- 0F Y Horizontal Enhance Gain

94 CH-ENH 0F 00-0F Color Horizontal Enhance Gain

66 YV-DSB 00 00-03 Y Vertical Dynamic Shoot Balance Gain

75 CV-DSB 00 00-03 Color Vertical Dynamic Shoot Balance Gain

82 YH-DSB 00 00-03 Y Ho rizontal Dynamic Shoot Balance Gain

90 CH-DSB 00 00-03 Color Horizontal Dynamic Shoot Balance Gain

69 YV-CLP 00 00-0F Y Vertical Enhance Clip Offset

84 YH-CLP 00 00-0F Y Hor izontal Enhance Clip Of fset

P06 ZP94/95

FLEX CONT NTSC

97 YV-NLP 00 00-3 F Y Vertical Nonline ar Peak ing

98 YH-NLP 0 A 00-3F Y Ho rizon tal No nlinear Peaking

101 Y-LMT FF 0 0-FF Y Amplitude Limit

83 YH-FRQ 00 0 0-03 Y Horizo nt a l HPF P e a k Frequency Switch

91 CH-FRQ 02 00-03 Color Horizontal HPF Peak Frequency Switch

70 YV-LTI 00 00-01 Y Vertical Enhance Clip 0 = Enhance, 1 = LTI

78 CV-CTI 00 00-01 Color Vertical Enhance Clip 0 = CTI, 1 = Enhance

86 YH-LTI 01 00-01 Y Horizontal Enhance Clip 0 = Enhance, 1 = LTI

93 CH-CT I 01 0 0-01 Color Horizontal Enhance Clip 0 = CTI, 1 = Enhance

RANGE DE SCRIPTI ON

*Non-Adjustable Data

10

SERVICE MENUS

ITEM S ETTIN G

P06 ZP94/95

FLEX CONT ATSC (480 i, 480p, 1080i, 720p)

97 YV-NLP 00 00-3F Y Vertical Nonlinear Peaking

98 YH-NLP 0A 00-3F Y Horizontal Nonlinear Peaking

101 Y-LMT FF 00-FF Y Amplitude Limit

83 YH-FRQ 00 00-03 Y Horizontal HPF Peak Frequency Switch

91 CH-FRQ 02 00-03 Color Horizontal HPF Peak Frequency Switch

70 YV-LTI 00 00-01 Y Vertical Enhance Clip 0 = Enhance, 1 = LTI

78 CV-CTI 00 00-01 Color Vertical Enhance Clip 0 = CTI, 1 = Enhance

86 YH-LTI 01 00-01 Y Horizontal Enhance Clip 0 = Enhance, 1 = LTI

93 CH-CTI 01 00-01 Color Horizontal Enhance Clip 0 = CTI, 1 = Enhance

P07 ZP94/95

FLEX CONT NTSC

69 YVDSBC 00 0 0- 07 Y Vertical Dynamic Shoot Balance Coring Amplitude

77 CVDSBC 00 00-07 Color Vertical Dynamic Shoo t Balance Coring Amplitude

85 YHDSBC 00 00-07 Y Horizontal Dynamic Shoot Balance Coring Amplitude

92 CHDSBC 00 00-07 Color Horizontal Dynamic Shoot Balance Coring Amplitude

95 Y-CRG 00 00- 07 Y Coring Amplitude

99 C-CRG 00 00 -07 Color Cor in g Amplitude

64 YNR-IN 04 00-07 YNR Input L e vel Gain

73 CNR-IN 04 00-07 CNR Input Level Gain

80 YNRPAS 00 00-07 YNR Passage Level Limit

88 CNRPAS 02 00-07 CNR Passage Level Limit

P07 ZP94/95

FLEX CONT ATSC (480i, 480p, 1080i, 720p)

69 YVDSBC 00 0 0- 07 Y Vertical Dynamic Shoot Balance Coring Amplitude

77 CVDSBC 00 00-07 Color Vertical Dynamic Shoo t Balance Coring Amplitude

85 YHDSBC 00 00-07 Y Horizontal Dynamic Shoot Balance Coring Amplitude

92 CHDSBC 00 00-07 Color Horizontal Dynamic Shoot Balance Coring Amplitude

95 Y-CRG 00 00- 07 Y Coring Amplitude

99 C-CRG 00 00 -07 Color Cor in g Amplitude

64 YNR-IN 04 00-07 YNR Input L e vel Gain

73 CNR-IN 04 00-07 CNR Input Level Gain

80 YNRPAS 00 00-07 YNR Passage Level Limit

88 CNRPAS 02 00-07 CNR Passage Level Limit

P08 ZP94/95

FLEX CONT NTSC/ATSC (480i, 480p, 1080i, 720p)

65 YNRRDC 00 0 0-07 YNR Reducing Gain

74 CNRRDC 00 00-07 CNR Reducing Gain

67 YNR-DC 00 0 0-03 YNR DC Shif t

76 CNR-DC 00 00-03 Color DC Shift

81 YNR-O 00 00-0 7 YNR 0 Po int

89 CNR-O 00 00- 0F CNR 0 Point

45 CB-BLK 07 00-0F CB Blanking Level Offset

46 CR-BLK 07 00-0F CR Blanking Level Offset

27 FRMBRT* 60 00-7F Y Frame Bright

102 CLPOUT 7F 00-FF Clamp Output Offset

P09 ZP94/95

FLEX CONT NTSC/ATSC

10 MPLL-S 0F 00-1F Main PLL Vertical Mask Pulse Start Position Offset

17 SPLL-S 0F 00-1F Sub PLL Vertical Mask Pulse Start Position Offset

12 MPLL-E 0F 00-1 F Main PLL Vertical Mask Pulse End Po sition Offset

19 SPLL-E 0F 00-1F Sub PLL Vertical Mask Pulse End Position Offset

11 M VW-PH 05 00-07 Ma in Vertical Wr ite I nput Horizont a l Phase Adjustment

18 SVW-PH 05 00-07 Sub Ve rti cal Write In put Horizontal Phase Adjust ment

14 MHS-HP 0F 00-1F Main Horizontal Sync Horizontal Phase Offset

21 SHS-HP 0F 00-1F Sub Horizonyal Sync Horizontal Phase Offset

13 MY-CLP 03 00-07 Main Y Clamp Refrence Offset

20 SY-CLP 03 00-07 Sub Y Clamp Refrence Offset

RANGE DE SCRIPTI ON

*Non-Adjustable Data

11

SERVICE MENUS

ITEM S ETTING

P10 ZP94/95

FLEX CONT NTSC/ATSC (480i, 480p, 1080i, 720p)

23 V-POS 3F 00-3F Wide Vertical Position

24 V-SIZ 7F 0 0-FF Wid e Vert ical Size

50 HD-POS 3F 00-7F HD Position Offset

48 VBLK-T 7F 00-FF Vertical Blanking Top P osition Offset

49 VBLK-B 7F 00-FF Vertical Blanking Bottom Position Offset

51 HBLK-R 7F 00-FF Horizontal Blanking Right Position Offset

52 HBLK-L 7F 00-FF Horizontal Blanking Left Position Offset

40 READ F 10 0 0- 3F A/D Converter Clock Sampling Phase

P11 ZP94/95

FLEX CONT NTSC/ATSC (480i, 480p, 1080i, 720p)

35 FRMT OP -2 07 00-0F Frame Top Po sition Offset (2Pix)

FRMTOP-L* 07 00-0F Frame Top Po sition Offset (Letter)

36 FRMBTM-2 07 00-0F Frame Bottom Po sition Offset (2Pix)

FRMBTM-L* 07 00- 0 F Frame Bottom Position Offset (Letter)

37 FRMRGT 07 00-0F Frame Right Position Offset

38 FRMLFT 07 00- 0 F Frame Left Position Offset

59 BS-TOP 07 00-0F Black Strech Sto p Pulse Top Position Offset

60 BS-BTM 07 00-0F Black Strech Stop Pulse Bott om Position Offset

61 BS-RGT 07 00-0F Black Strech Stop Pulse Right Position Offset

62 BS-LFT 07 00-0F Black Strech Sto p Pulse Left Position Of fset

P12 ZP94/95

FLEX CONT

120 TV/CINE 01 00-01 TV Cinema Detection

121 T /C DET 07 00- 0F TV Cinema Detection Vertical Gate Area Start Position

122 T /C UNL 01 00-07 TV Cinema Detection Unlock Prot ection Count

123 T /C LCK 03 00-0F TV Cinema Detection Lock Protection Count

126 T/C ARE 05 00-FF TV Cinema Detection Motion Area Border Volume Offset

127 T/C CBR 07 00-0F TV Cinema Detection Color 2 Bit Border Volume Offset

128 T/C YBR 07 00-0F TV Cinema Detection Y 2 Bit Border Volume

P13 ZP94/95

TA1298 NTSC

SHARP 0C 00-1F Sharpness (Center Adjustment )

APACON 06 00 -07 APACON Peak fO

YNR 00 00-03 YNR

P13 ZP94/95

TA1298 4 80I

SHARP 0A 00-1F Sharpness (Center Adjustment)

APACON 06 00 -07 APACON Peak fO

YNR 00 00-03 YNR

P13 ZP94/95

TA1298 480P

SHARP 0A 00-1F Sharpness (Center Adjustment)

APACON 06 00 -07 APACON Peak fO

YNR 00 00-03 YNR

P13 ZP94/95

TA1298 1080I

SHARP 07 0 0- 1F Sharpness (Center Adjustment )

APACON 05 00 -07 APACON Peak fO

YNR 00 00-03 YNR

P13 ZP94/95

TA1298 720P

SHARP 0A 00-1F Sharpness (Center Adjustment)

APACON 06 00 -07 APACON Peak fO

YNR 00 00-03 YNR

RANGE DESCRIPTION

*Non-Adjustable Data

12

SERVICE MENUS

ITEM S ETTIN G

P14 ZP94/95

TA1298 NTSC

COLOR 40 00-7F Color (Center Adjustment)

T INT 45 00-7 F Tint (Center Adjustment)

R-Y PH 02 00-03 R-Y Phase

R/B GA 01 00-03 R/B Gain

G-Y PH 00 00-03 G-Y Phase

G/B GA 00 00-0 3 G/B Gain

COLOR SYST EM 0 0 00 -07 COLOR SYST EM

P14 ZP94/95

TA1298 SDTV

COLOR 4F 00-7F Color (Center Adjustment)

T INT 3B 00-7F Tint (Center Adjustment)

R-Y PH 02 00-03 R-Y Phase

R/B GA 02 00-03 R/B Gain

G-Y PH 01 00-03 G-Y Phase

G/B GA 00 00-0 3 G/B Gain

COLOR SYST EM 0 1 00 -07 COLOR SYST EM

P14 ZP94/95

TA1298 HDTV

COLOR 40 00-7F Color (Center Adjustment)

T INT 43 00-7 F Tint (Center Adjustment)

R-Y PH 00 00-03 R-Y Phase

R/B GA 02 00-03 R/B Gain

G-Y PH 02 00-03 G-Y Phase

G/B GA 00 00-0 3 G/B Gain

COLOR SYST EM 0 1 00 -07 COLOR SYST EM

P15 ZP94/95

TA1298

RGB BRT 50 0 0-7F RGB Brightness

RGB CNT 5 0 00 -7F RGB Contrast

G D RV (W) 3 9 00- 7 F Green Drive (WAR M)

B DRV (W) 2D 00-7F Blue Drive (WARM)

SUB CLR 10 00-1F Sub Col or (Demodulato r)

SUB CNT 1F 00-1F Main NTSC Contrast

VSM PH 05 00- 07 VM Ph ase

VSM GA 0 0 00-0 3 VM Gain

OS ACL 01 00 -01 OSD Auto Cont r ast Limiter Switch

RGB ACL 0 0 00 -01 RGB Auto Contrast Limi t er Swit ch

P16 ZP94/95

TA1298

CLR G 00 00 -03 Color G Corection P iont

CLT 00 00-01 Color Limiter Level

YOUT G 00 0 0- 01 Y G (After Contrast) Switch

YG PNT 00 00-01 Y G Point

S TRK 00 00-03 Sharpness T racking

RGBG 00 00-01 RGB Switch

DC PNT 00 00-07 DC Restoration Point

DC RAT 00 0 0-07 DC Restoration Rate

DC LMT 00 0 0- 03 DC Restorat ion Limit Point

RANGE DE SCRIPTI ON

*Non-Adjustable Data

13

SERVICE MENUS

ITEM S ETTING

P17 ZP94/95

TA1298

BSP 03 00-07 Black Strech Point

APL /BS 00 00 -03 APL / Black Strech Po int

B COR 01 00- 01 Black Level Correction

B GA 00 00-01 Black Strech Gain

B DET 00 00-01 Black Detect Level

DABL P N 00 00-07 Dynamic ABL Detection Point

DABL GA 07 0 0-07 Dynamic ABL Gain

ABL PN 0 7 00-07 ABL Detection Point

A BL GA 05 0 0-07 AB L Gain

P18 ZP94/95

V CHIP RAT ING

POLLING 0F 00-0F 0

TIMEOUT 05 00-0F 0

ST AT US 02 0 0-0F 0

AFC/CLOCK TEST

RANGE DESCRIPTION

*Non-Adjustable Data

SERVICE ADJUSTMENT PROCEDURE ORDER

The following is the suggested order for adjustment procedures.

ZP 94/95 SERVICE ADJUSTMENT ORDER “PREHEAT BEFORE BEGINNING”

Order Adjustment Item Scre en Format Signal DCU Da ta

Pre HEAT N/A NTSC N/A

1 Cut Off Progressive NTSC

2 Pre Focus Lens and Static Progressive NTSC

3 DCU Phase Data Setting Progressive NTSC

4 DCU Phase Data Setting HD 2.14H

5 Horz. Position Adj. (Coarse) Progressive NTSC

6 Horz. Position Adj. (Coarse) HD 2.14H

7 Raster Tilt Progressi ve NTSC CLEAR

8 Beam Ali gnment Progressi ve NTS C

9 Raster Position Progressive NTSC CLEAR

Horz. Size Ad just Progressive NTSC CLEAR

10

Horz. Size Adjust HD 2.14 CLEAR

11 Vertical Size Adjust Progress ive NTSC CLEAR

12 Beam Form Progressive NTSC

13 Lens Focus Adjust Progressive NTSC

14 Static Focus Adjust Progressive NTSC

15 Blue Defocus Progressive NTSC

16 White Balance Adjustment Progres sive NTSC

1 7 Sub Bright ness Adjustment Progressive NTSC Color Bar

1 8 Horz. Position Adjustment Progressive NTSC

1 9 Horz. Position Adjustment HD 2.14H

2 0 Converge nce Alignment Progressive NTSC

21 C onver gence Al ignment HD 2.14H

I t is necessary to follow the order when per forming an alignment on the ZP 94/95 chassis.

14

CLEAR to star t

CONVERGENCE

MEMORY INITIALIZATION PROCEDURE

WARNING: This should only be done in extreme

cases. I2C Data will be reset as well. Be sure

and write down all data values before

continuing.

1. Disconnect Power to Television.

2. Remove the Back Cover.

3. Remove the two screws holding the Main chassis

to the Cabinet if necessary.

4. Disconnect wiring harness clips to free up the

chassis if necessary.

5. Reconnect Power to the Television and turn the

set ON.

6. Locate PP1 and add a jumper between pins 1

and 2 of the PP1 connector.

7. Hold jumper in place for 5 seconds. (A beep will

NOT be heard).

8. Remove the jumper.

9. Confirm EEPROM reset, Input source is now set

to Air and not to Cable 1 or 2. No Child Lock,

and only channels 2 through 13 are in memory.

10.Reassemble Chassis and reinstall PTV back. Set

is now ready to operate.

NOTE: All customers' Auto Programming and

Set-Ups are returned to factory settings.

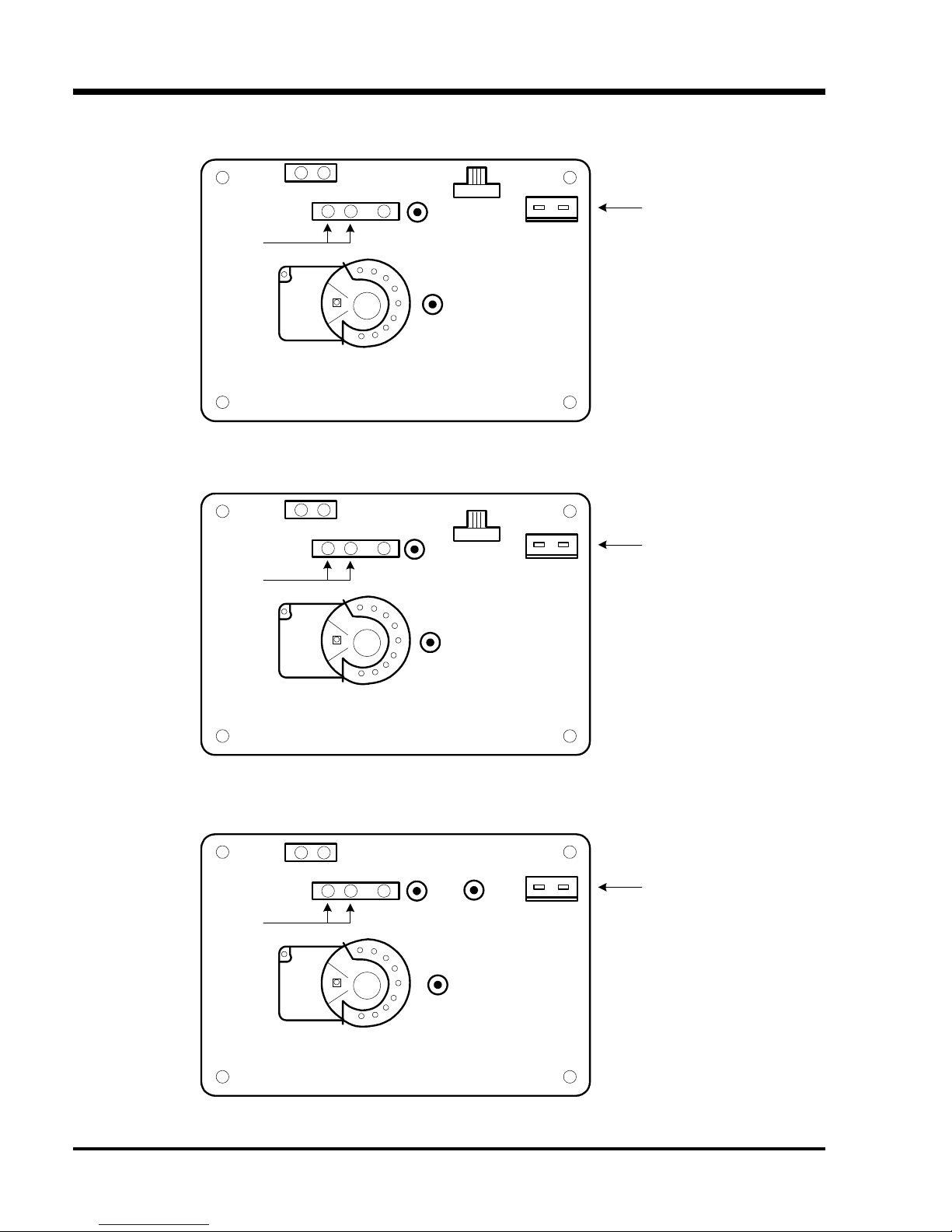

Pre HEAT

PRESET EACH ADJUSTMENT VR TO CONDI-

TION AS SHOWN:

A) Before Pre Heat Run.

1. Red and Green Drive VR on the CRT PWB. (Not

on Blue CRT).

a

2. SCREEN VR ON FOCUS PACK.

6&5((1 95

Pre Set fully counter clockwise.

3. Focus VR on focus pack

)2&86 95

Pre Set fully clockwise.

CUT OFF

ADJUSTMENT PREPARATION:

A) Pre Heat Run should be finished.

ADJUSTMENT PROCEDURE:

1. Go to I2C ADJ Mode. Press and hold the

Source key on the front panel and then POWER

ON to access I2C adjustment mode.

2. Choose SERVICE item [2] of I2C ADJ. Mode.

(Select CURSOR RIGHT (right arrow key).

3. Screen VR should be turned clockwise gradually

and set so that retrace lines begin to appear.

4. Return to normal mode by using the left arrow key.

5. Adjust focus VRs so that focus is even all around

the screen.

PRE-FOCUS ADJUSTMENT

Adjustment preparation

1. The set can face in any direction: west, east,

north or south.

'5,9( 95

Pre set between the 12 oclock and 2 oclock

position.

2. Receive the cross-hatch pattern signal.

CONTRAST : 60-70%

BRIGHTNESS : 50%

3. The electrical focus adjustment should have been

completed.

4. The centering DY inclination should have been

adjusted.

15

CONVERGENCE

$

12

$

Adjustment procedure

1. Loosen the fixing screw on the lens cylinder so

that the lens cylinder can be turned. (Be careful

not to loosen too much. If the screw is loosened too much, rattling when tightening becomes

greater and the focus may drift). After completing

steps (5), (6), and (7) below, tighten the fixing

screws for each lens with a torque of 12~17 Kgf

cm.

2. Apply covers to 2 of R, G, and B lenses, and

project a single color on the screen and adjust in

sequence.(The adjustment order of R, G, and B is

only an example.)

3. For each of the R, G, and B lenses, observe the

color aberration generated on the outer circumference of the cross-hatch bright line at the center

section (3 pitches vertically and horizontally from

the center.)

4. If the lens adjustment knob is turned clockwise,

viewed from the front, the color aberration

changes as follows.

/

6/,*+7<%/8(&+520$7,&$%(55$7,21

Set Size Pitch between L1 & L2

50" 3.0 cross-hatch pitches

55" 3.0 cross-hatch pitches

60" 3.0 cross-hatch pitches

25

/

&2/25

5('

&+520$7,&

%(55$7,21

6. In case of R lens, set to the position where the

chromatic aberration changes from red to crimson. As shown below, observe the vertical bright

line at the center and set to the position where the

crimson chromatic aberration slightly appears

inside and red outside (reference value: 1~3mm)

within the cross-hatch pitches specified in next

Lens Change of color aberration

R Lens Red Crimson

G Lens Blue Red

B Lens Purple Green

5. In case of G lens, set to the point where the

chromatic aberration switches from blue to red.

If the chromatic aberration appearing all over the

screen is not the same, observe the vertical bright

line at the center of the screen and set to the

position where red chromatic aberration slightly

appears inside and blue outside (reference value:

1~3mm) within the cross-hatch pitches specified

in next table. When the red chromatic aberration

appearing at both sides of the bright line is not

equal, observe the side with larger chromatic

aberration when adjusting.

/

5('

&+520$7,&

table.

6/,*+7<&5,0621

&+520$7,&

Set Size Pitch between L

50" 3.0 cross-hatch pitches

55" 3.0 cross-hatch pitches

60" 3.0 cross-hatch pitches

$%(55$7,21

%(55$7,21

7. In case of B lens, set to the position where the

chromatic aberration changes from purple to

green. As shown below, observe the vertical

bright line at the center and set to the position

where green chromatic aberration slightly appears

inside and purple outside (reference value:

1~3mm) within the cross-hatch pitches specified

in next table.

16

/

3853/(&+520$7,&

$%(55$7,21

Set Size Pitch between L

50" 3.0 cross-hatch pitches

55" 3.0 cross-hatch pitches

60" 3.0 cross-hatch pitches

6/,*+7<*5((1

&+520$7,&

$%(55$7,21

NOTES:

1. Fixing screw 2. Color aberration

),;,1*6&5(:

&2/25

$%(55$7,21

/(16

CONVERGENCE

Adjustment procedure

PROGRESSIVE MODE

1. Receive any NTSC signal (Set is in Progressive

mode)

2. Push SERVICE ONLY SW on Deflection

PWB (Enter to DCU ADJ. Mode)

3. Push (?) key on R/C. (Green cross hatch is

displayed). Then push (QUIT) key on R/C.

(Character pattern is displayed. This is the

PHASE setting mode)

4. Set PH-H phase data as shown below using (4)

and (6) key.

5. Set PH-V phase data as shown below using (2)

and (5) key.

6. Set CR-H phase data as shown below using (<)

and (>) key.

7. Set CR-V phase data as shown below using (up)

and (down) arrow keys.

8. Push (?) key on R/C to exit from the PHASE

mode.

9. Push (-)* key on R/C 2 time to write the phase

data to the E2PROM.

10.When Green dots are displayed, push (MUTE)

key to return to DCU ADJ. mode.

11. Push SERIVCE ONLY SW to return to RF

or VIDEO mode.

&5266+$7&+

3. Since the G light is very important for picture

quality and performance, pay special attention

in its adjustment.

NOTE: Be careful not to touch the lens with

your fingers when adjusting.

4. For red, setting to the center between red and

crimson is optimum.

5. For blue, setting to the center between purple

and green is optimum.

DCU PHASE DATA SETTINGS

Adjustment Preparation

1. Cut off adjustment should be finished

2. VIDEO CONTROL: Factory Preset Condition

HD MODE

12. Receive any HD signla (Set is in HD Mode)

13. Repeat (2)~(11) procedure again.

PROGRESSIVE MODE

PHASE MODE: PHASE MODE:

PH-H: BB

PH-V: OC

CR-H: 4C

CR-V: 00

HD MODE

PH-H: BB

PH-V: O7

CR-H: 4C

CR-V: 0C

CHASSIS HORIZ PHASE (COARSE) ADJUSTMENT

Adjustment Preparation:

1) Cut Off, DCU Phase adjustments should be finished.

2) Video Control: Brightness 90%, Contrast Max.

17

CONVERGENCE

Adjustment Procedure

PROGRESSIVE MODE

1) Receive any NTSC crosshair signal.

2) Screen Format is PROGRESSIVE.

3) Press the SERVICE ONLY switch on the de-

flection PWB and display the Digital Convergence

Crosshatch pattern.

4) Mark the center of the Digital Convergence Cross-

hatch Pattern with finger and press the SERVICE

ONLY switch to return to normal mode.

5) Enter the I2C Bus alignment menu and select Item

[12] H POSI and adjust the data so that the cen-

ter of Video matches the location of the Digital

Crosshatch pattern noted in step {4}.

6) Exit from the I2C Menu.

HD Mode Adjustment

1) Receive any 2.14H signal.

2) Screen Format is HD.

RASTER INCLINATION ADJUSTMENT

(DEFLECTION YOKE)

Adjustment preparation

1. The set can face any direction.

2. Input the single cross test signal.

3. Set video conditions to factory reset.

4. The lens focus adjustment should have been

completed, screen format should be progressive.

5. The electric focus should have been coarse

adjusted.

6. The digital convergence RAM should be cleared

(uncorrected state). With the TV set off, press

and hold the service switch located on the Power/

Deflection PWB and then press the power

button.

7. Start adjustment 20 minutes or more after TV is

turned on.

3) Press the SERVICE ONLY switch on the de-

flection PWB and display the Digital Convergence

Crosshatch pattern.

4) Mark the center of the Digital Convergence Cross-

hatch Pattern with finger and press the SERVICE

ONLY switch to return to normal mode.

5) Enter the I2C Bus alignment menu and select Item

[12] H POSI and adjust the data so that the cen-

ter of Video matches the location of the Digital

Crosshatch pattern noted in step {4}.

6) Exit from the I2C Menu.

%()25(

$&7,9(

9,'(2

&(17(5

)520

67(3

7+(186(180%(5.(<6720$7&+,17(51$/

&5266+$7&+ &(17(572$&7,9(9,'(2&(17(5

$)7(5

86(&85625

.(<672029(

'277('/,1(6

%(7:((1%(17

/,1(6),567

Adjustment procedure

1. Apply covers to the R and B lenses and project

only green light or short 2P plug on R & B.

2. Turn the G deflection yoke and adjust the vertical

raster inclination.

3. Then, remove the cover of R or B lens and

project red or blue light together on the screen.

4. Turn the deflection yoke of R or B and set so that

the inclination of R or B with respect to the green

light is as shown below on the top and bottom

sides.

5. After raster inclination adjustment, fixing screw of

DY should be screwed with 12+2kg-cm torque.

(PP

(

*UHHQ

(

5HGRU

%OXH

18

(

&URVVKDWFK*UHHQ

CONVERGENCE

Notes:

1. If internal cross-hatch does not appear after

clearing RAM data, press service switch again,

on POWER/DEFLECTION PWB.

2. To restore old RAM data, turn TV off and on.

BEAM ALIGNMENT

Adjustment preparation

1. Adjust at least 30 minutes after turning on power

switch.

2. Raster inclination, centering, horizontal and

vertical amplitudes, and optical focus adjustment

should be completed.

3. Set video conditions, Brightness to 90% and

Contrast MAX.

4. Receive cross-hatch signals. (Use of internal

cross-hatch signals allowed.) Raster Tilt should

be finished.

5. Screen format should be Progressive.

Adjustment procedure

1. Green (G) tube beam alignment adjustment.

Short-circuit 2P subminiature connector plug pins

of Red (R) and Blue (B) on the CPT boards and

project only Green (G) tube.

2. Put Green (G) tube beam alignment magnet to the

cancel state as shown below.

6. If image position does not shift when Green (G)

static focus (Focus Pack) is turned. Green (G)

beam alignment has been completed.

7. If image position shifts when Green (G) static

focus (Focus Pack) is turned, repeat (2)-(6).

8. Conduct beam alignment for Red (R) focus:

Focus Pack UFPK, Blue (B) focus: Focus Pack

UFPK.

9. Upon completion of adjustment, fix beam alignment magnets with white paint.

VERT & HORIZ PICTURE POSITION

ADJUSTMENT

Adjustment preparation

1. Select signal on main picture.

2. Video settings have to be at normal condition.

Adjustment procedure

1. Press the SOURCE and POWER button on

Control Panel at same time to access VIDEO

CHROMA ADJUST mode.

2. Select H POSI and V POSI using 56 buttons.

3. Adjust the H POSI (HORIZONTAL) and

VPOSI (VERTICAL) position using 34 buttons.

4. Press MENU button to exit VIDEO CHROMA

ADJUST mode.

5. Select single PINP mode and move the sub

picture, using the MOVE button. Distance

between PINP and edge of screen should be

equal when moved. If it is not, repeat (1) ~ (5).

3. Turn the Green (G) static focus (Focus Pack)

counterclockwise all the way and make sure of

position of cross-hatch center on screen. (Halo

state.)

4. Turn the Green (G) static focus (Focus Pack)

clockwise all the way. (Blooming state.)

5. Turn two magnets forming alignment magnet in

any desired direction and move cross-hatch

center to position found in (3).

NOTE: For ZP94/95 Models check the position

of MULTI PINP mode. Check the right edge

of the sub pictures for MV-4 to make sure there

is no separation between the MULTI PINP and

the edge of the screen.

HORIZONTAL SIZE

· Digital Convergence RAM should be cleared. With

Power Off, press and hold the Service Only

Switch on the Deflection PWB, then press Power.

Adjustment Prerparation

1. The set can face east or west

19

CONVERGENCE

2. Set video conditions to factory preset.

3. The electric focus should have been coarse adjusted.

4. Start adjustment 20 minutes or more after TV is

turned on.

Adjustment Procedure

PROGRESSIVE MODE

1. Receive any NTSC signal.

2. Press the SERVICE ONLY SW on DEFLECTION PWB.

3. Locate the horizontal size VR (R683). Adjustable

the horizotal size to the table below.

HD MODE

1. Input 1080i (fH=33.75kHz) component signal to

VIDEO 1 or 2.

2. Press the SERVICE ONLY SW on DEFLEC-

TION PWB.

3. Locate the horizontal size VR (R686). Adjustable

the horizotal size to the following table.

Adjustment Prerparation

1. The set can face east or west

2. Set video conditions to factory preset.

3. The electric focus should have been coarse adjusted.

4. Start adjustment 20 minutes or more after TV is

turned on.

Adjustment Procedure

PROGRESSIVE MODE

1. Receive any NTSC signal.

2. Press the SERVICE ONLY SW on DEFLECTION PWB.

3. Locate the vertical size VR (R630). Adjustable the

vertical size according to the table below.

Size O

50" 670mm

60" 775mm

Adjust Vertical Size until the size matches the chart

below.

Size Progressive Mode HD Mode

50" 1050mm 1050mm

60" 1200mm 1200mm

Adjust Horizontal Size until the size matches the

chart below.

O

VERTICAL SIZE

· Digital Convergence RAM should be cleared.

With Power Off, press and hold the Service Only

Switch on the Deflection PWB, then press Power.

O

BEAM FORM

Adjustment preparation

1. The beam alignment should have been completed.

2. The raster inclination, centering, horizontal/

vertical amplitude and optical focus adjustments

should have been completed.

3. Set video conditions to Brightness to 90 %

andContrast to MAX.

4. Input the dot signal.

Adjustment procedure

1. Green CRT beam shape adjustment. Shortcircuit 2P sub-mini connectors on Red and Blue

CRT P.W.B.s to project only the Green beam.

20

CONVERGENCE

2. Turn the green static focus fully clockwise.

(Blooming.)

3. Make the dot at the screen center a true circle

using the 4-pole magnet as shown below.

4. Also adjust the Red and Blue CRT beam shapes

according to the steps (1) to (3).

5. After the adjustment has been completed, return

R,G and B static VRs to the just focus point.

3576XUIDFH6LGH

3ROH%HDP

$OLJQPHQW

=HUR)LHOG

6SDFHU1R

$GMXVWPHQW

D

E

7UXH&LUFOH'HJUHHDE

6SHFLILFDWLRQ

0DJQHW

3ROH%HDP

$OLJQPHQW

0DJQHW

),;,1*6&5(:

/(16

8. Rotate the cylinder back and forth to obtain the

best focus point, while observing the Cross-Hatch.

(Observe the center of the screen).

Hint: Located just below the screen are the two

wooden panels. Remove the panels to allow

access to the focus rings on the Lenses.

9. After completing optical focus, tighten the fixing

screws for each lens.

10. When adjusting the Green Optical focus, be very

careful. Green is the most dominant of the color

guns and any error will be easily seen.

LENS FOCUS ADJUSTMENT

Preparation for adjustment

1. Receive the Cross-hatch pattern signal.

2. The electrical focus adjustment should have been

completed.

3. Deflection Yoke tilt should have been adjusted.

4. Brightness = 50%

5. Contrast = 60% to 70%

Adjustment procedure

6. Short the 2 pin sub-miniature connector on the

CRT P.W.B. TS, to produce only the color being

adjusted and adjust one at a time. (The adjustment order of R, G and B is just an example.)

7. (See Figure below) Loosen the fixing screw on

the lens assembly so that the lens cylinder can be

turned. (Be careful not to loosen the screw too

much, as this may cause movement of the lens

cylinder when tightening.)

11. Repeat Electrical Focus if necessary.

STATIC FOCUS ADJUSTMENT

Adjustment preparation

1. The lens focus should be finished.

2. Set video conditions to Contrast to MAX and

birightness to 50%.

3. Receive the cross-hatch pattern signal.

4. Apply covers to the lenses of colors other than

the color to be adjusted and project a single

color.

Adjustment procedure

1. Red (R), Green (G) and Blue (B) static focus

adjustment. Vary the static focus VR(focus pack

UFPK) and make the center of the cross-hatch

pattern clearest.

2. Observe the corners of the picture and check that

the focus does not get conspicuously worse.

21

CONVERGENCE

(

2%6(59,1*

&251(52)7+(3,&785(

2%6(59,1*32,176

32,1762)7+

BLUE DEFOCUS ADJUSTMENT

Adjustment preparation

1. Optical and electrical focus adjustment should

have been completed.

2. The convergence adjustment should have been

completed.

3. Set Video conditions to factory reset.

Adjustment procedure

1. Input a Crosshatch Signal to VIDEO input.

2. Short-circuit 2P sub-mini connectors on the red

and green CPT P.W.B.s to display only the blue

beam.

3. Turn the B Focus VR(Focus Pack) fully clockwise.

4. Adjust BLUE defocus according to the following

specifications. 1mm on each side equaling 2mm

total

See figure Below.

Blue Defocus “Sticking Out”

6FUHHQ 95

5* %

)RFXV 95

5* %

)2&86 3$&.

WHITE BALANCE ADJUSTMENT

1. Screen adjustment

2. High brightness white balance

3. Low brightness balance

Screen Adjustment VRs Drive Adjustment VRs

Red: on Focus Pack Red: R873 on CPT P.W.B.

Green: on Focus Pack Green: R842 on CPT P.W.B.

Blue: on Focus Pack

Adjustment VRs:

Screen adjustment VRs on Focus Block

Drive adjustment VRs on CRT P.W.B.

Red Drive = R829R

Green Drive = R879G

Preparation for adjustment

1. Start adjustment 20 minutes or more after the

power is turned on.

2. Turn the brightness and black level OSD to

minimum by remote control.

3. Receive a tuner signal, (any channel, B/W would

be best).

4. Set the drive adjustment VRs (Red R829R and

Green R879G) to their mechanical centers.

Cent er of Blue crosshatch li ne

22

Adjustment procedure

1. Go to I2C ADJ. Mode. (With power ON, press

DTV/SAT and Cursor Down buttons at the

same time. Service Menu is displayed.)

2. Choose SERVICE item Number [2] of I2C

ADJ. Mode. (Select ON by Cursor Right and

the Vertical will collapses).

3. Gradually turn the screen adjustment VRs (red,

green, blue) clockwise and set them where the

red, green and blue lines are equal and just

barely visible.

CONVERGENCE

4. Return Service item on I2C ADJ to Off by

Cursor Right. Number [2].

Adjust the Sub Brightness Number [1]

2

SUBBRT using I

C Bus alignment procedure so

only the slightest white portions of the raster can

be seen.

5. Input a gray scale signal into any Video input

and select that input using the INPUT button on

the remote or front control panel.

6. Turn the Brightness and Contrast OSD all the

way up.

7. Make the whites as white as possible using the

drive adjustment VRs (Red R829 and Green

R879).

8. Set the Brightness and Contrast to minimum.

(10800 Kelvin)

9. Adjust the low brightness areas to black and

white, using screen adjustment VRs (red, green,

blue).

10. Check the high brightness whites again. If not

OK, repeat steps 6 through 9.

11. Press the MENU key on remote to Exit

Service Menu.

sure that the other conditions are center.

Directly observe the screen by eye without

using a mirror.

Fade to black

18 HORIZONTAL POSITION (FINE)

Adjustment Preparation:

1. Video Control: Brightness 90%, Contrast Max.

Adjustment Procedure

PROGRESSIVE MODE:

1. Receive any NTSC crosshatch signal.

2. Screen Format is PROGRESSIVE

SUB BRIGHTNESS ADJUSTMENT

Adjustment preparation

1. Start adjustment 20 minutes or more after the

power is turned ON. Receive the color bar

signal.

2. Set the contrast and color controls to minimum.

Adjustment procedure

1. Go to Sub Brightness adjustement in VIDEO

CHROMA ADJUST mode (press Source and

Power button on Control panel at the same time),

using 56 buttons and then 4 button.

2. Then adjust Sub Brightness using 34 buttons to

increase or decrease the value, according to

figure. (Visually adjust).

3. After adjustment, press MENU button to exit

VIDEO CHROMA ADJUST mode. (Data is

stored in memory).

NOTE: When selecting SUB-BRIGHTNESS

mode, the microprocessor sets the CONTRAST

and COLOR to MIN. automatically, but make

3. Enter the I2C Bus alignment menu and select Item

[12] HPOSI

4. Adjust the data so that the Left and Right hand

side are equal.

5. Press the MENU button to exit from the Ser-

vice Menu.

HD Mode Adjustment:

1. Receive any 2.14H 33.75kHZ signal.

2. Display Format is HD mode.

3. Enter the I2C Bus alignment menu and select Item

[12] HPOSI

4. Adjust the data using the left and right cursor keys

and balance the Left and Right hand side.

5. Press the MENU button to exit from the Ser-

vice Menu.

DIGITAL CONVERGENCE ADJUSTMENT

Adjustment preparation

1. Receive an RF or video signal.

2. Set controls to factory preset.

3. Install jig screen on the set.

23

CONVERGENCE

4. Note the center of the video pattern displayed.

This is necessary to match dotted lines (adjustment point viewed) and actual point that is

adjusted and displayed by the video signal.

5. Press the service only switch (on POWER/

DEFLECTION PWB). The pattern displayed is

now the digital convergence mode.

6. When performing a complete digital convergence

adjustment CLEAR DATA in RAM. See 2.6 (1)(7).

7. To clear data turn TV set off. Press and hold the

service switch and then press POWER on.

Press the MENU button to see all colors if the

center cross is other than White.

3. Press the Cursor Keys to match the selected color

to the green at the geometric center of the screen.

4. Press the RECALL, 0, or SOURCE buttons to

select the next color to be adjusted.

0= Red / Green (Yellow)

SOURCE= Green / Blue (Cyan)

DISPLAY= Green Only

5. Press Freeze button to exit the Raster Phase Mode.

(The two lines disappear)

6. Press SKO1 to exit Convergence Service Mode.

$'-8670(1732,17

NOTE: If only minor adjustments to conver-

gence are needed, the jig screen is not necessary. Use digital data stored in memory and

one color as a reference(red,green or blue).

DO NOT CLEAR DATA and WRITE to

ROM memory.

Advanced convergence Adjustment Procedure

WARNING: Advanced Convergence Adjustment

Procedure is to be performed only when

replacement of the Small Signal Main

Module or one or more the the CRTs is

replaced.

RASTER CENTERING

1. Press the service button SKO1 to enter the

Convergence setup mode.

2. Press the FREEZE button to enter the Raster

Phase Adjustment Mode. Two additional lines

appear, one near the top, and one near the bottom

of the screen.

24

CONVERGENCE 3X3

Green 3x3 Mode Alignment

1. Start with power off, press the service button SKO1

and hold, then press the front panel POWER button

at the same time. Set should come on with misaligned convergence.

Note: Mis-aligned convergence will appear, DO

NOT ACTIVATE ROM WRITE (MOVE

button twice). If you do so, you will save this

un-adjusted convergence data.

2. Press DISPLAY button 5 times to access 3x3

Mode.

3. Press the MENU key to project the RED +

GREEN cross- hatch colors only. Then press

DISPLAY to project the GREEN only.

4. Use the 2,4,5, and 6 keys (up, left, down, and right,

respectively) to select the adjustment point. Start

at center adjustment point, then move to top and

bottom, then left and right, and finally the corners.

G-Only Screen

6WDUWLQJ$GMXVWPHQW3RLQW

/RFDWLRQ

,QWHUVHFWLRQRI

%OLQNLQJ&XUVRU

5.Press the CURSOR KEYS at the selected

adjustment point to match the GREEN horizontal

and vertical lines to the Screen Jig lines.

(Call Zenith Parts @ 1-800-3-ZENITH to order

the Screen Jig)

/LQHVV\PPHWULFDOO\DOLJQHGDWWKH

$GMXVWPHQW3RLQWV

Red and Blue 3x3 Mode Alignment

6. Press the 0 key to project the RED + GREEN

internal cross-hatch colors.

&XUVRUEOLQNV

VHOHFWHGFRORU

Internal cross-hatch is Yellow when the Red and

Green lines match, and Cyan when the Blue and

Green Match

7.Press the CURSOR KEYS at the selected

adjustment point to match the RED horizontal/

vertical lines to the Green cross-hatch lines.

8. Press the SOURCE key to select the BLUE +

GREEN cross-hatch colors. Perform step 7 for

the BLUE.

9. Press the MENU button to display all 3 colors.

10. In order to Save settings (WRITE to ROM),

press the MOVE key 2 times. When the data is

stored Green dot will appear on the screen. Press

MOVE once to continue with 7x5 adjustment

mode.

CONVERGENCE 7X5

Green 7X5 Mode Alignment

1. Press the 0 button 5 times to enter the 7X5

Adjustment Mode.

2. Press the MENU button and then the DISPLAY

button again to project the Green color only.

CONVERGENCE

G-Only Screen

3. Use the 2,4,5, and 6 keys (up, left, down, and right,

respectively) to select the adjustment point. Start

at center adjustment point, then move to top and

bottom, then left and right, and finally the corners.

4.Press the CURSOR KEYS at the selected

adjustment point to match the GREEN horizontal

and vertical lines to the Screen Jig lines.

Red 7X5 Mode Alignment

5. Press the 0 key to select the RED + GREEN

internal cross-hatch signal.

6. Repeat steps 3 and 4 for the Red 7X5 adjustment.

Blue 7X5 Mode Alignment

7. Press the SOURCE key to select the BLUE +

GREEN colors.

8. Repeat steps 3 and 4 for the Blue 7X5 mode

adjustments.

9. In order to Save settings (WRITE to ROM), press

the MOVE key 2 times. When the data is stored

Green dot will appear on the screen. Press MOVE

once to continue with 13x9 adjustment mode.

5HG$OLJQPHQW

Yellow Cros s-h atch

%OXH$OLJQPHQW

Magenta Cross-hatch

CONVERGENCE 13X9

Green 13X9 Mode Alignment

1. Press the SOURCE button 5 times to enter the

13X9 Mode.

2. Press the MENU button and then the DISPLAY

button again to project the GREEN only.

3. Use the 2,4,5, and 6 keys (up, left, down, and right,

respectively) to select the adjustment point. Start

at center adjustment point, then move to top and

bottom, then left and right, and finally the corners.

25

CONVERGENCE

4.Press the CURSOR KEYS at the selected

adjustment point to match the GREEN horizontal

and vertical lines to the Screen Jig lines.

Red 13X9 Mode Alignment

5. Press the 0 key to select the RED + GREEN

internal cross-hatch signals.

6. Repeat steps 3 and 4 for the Red 13X9 mode

adjustments.

Red Alignment

Yellow Cross-hatch

Blue Alignment

Magenta Cross-hatch

Blue 13X9 Mode Alignment

7. Press the SOURCE key to select the BLUE +

GREEN colors.

8. Repeat steps 3 and 4 for the Blue 13X9 mode

adjustment.

9. In order to Save settings (WRITE to ROM), press

the MOVE key 2 times. When the data is stored

Green dot will appear on the screen. Hit MOVE

to continue.

When complete, press the service mode button SKO1

to exit the Convergence setup mode.

26

DIGITAL CONVERGENCE REMOTE CONTROL

PHASE

BLUE

(13X9 ADJUSTMENT)

CONVERGENCE

AUXILLIARY

CURSOR UP

CURSOR LEFT

CURSOR DOWN

RED

(7X5 ADJUSTMENT)

REMOVE COLOR

INITIALIZE

CURSOR RIGHT

ROM WRITE

GREEN

(3X3 AD JUST MEN T)

ADJUSTMENT

CROSSHATCH /

VIDEO MODE

RASTER

POSITION

ROM READ

MBR3475Z

924-10092

27

CIRCUIT DESCRIPTION

Sub-Power Supply Circuit Description

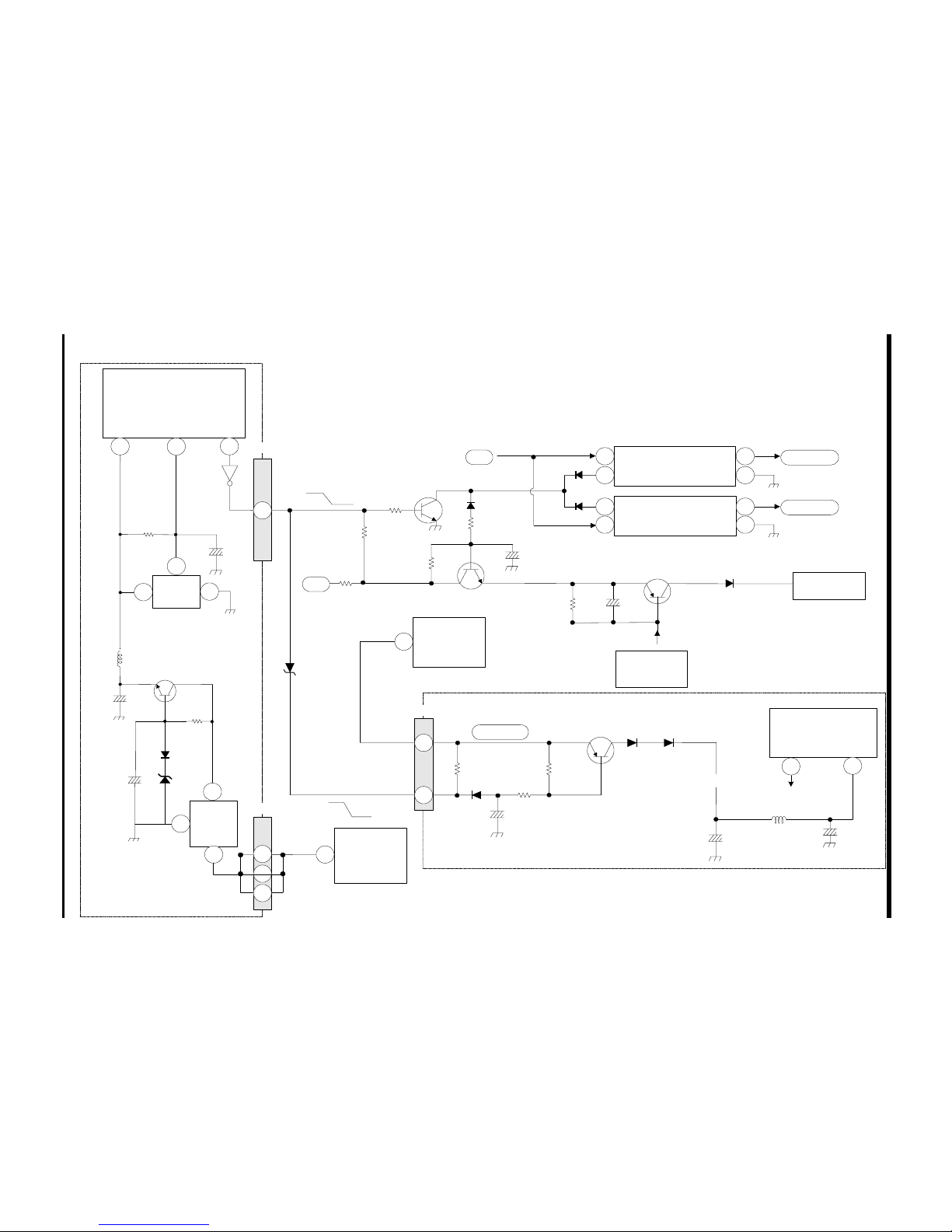

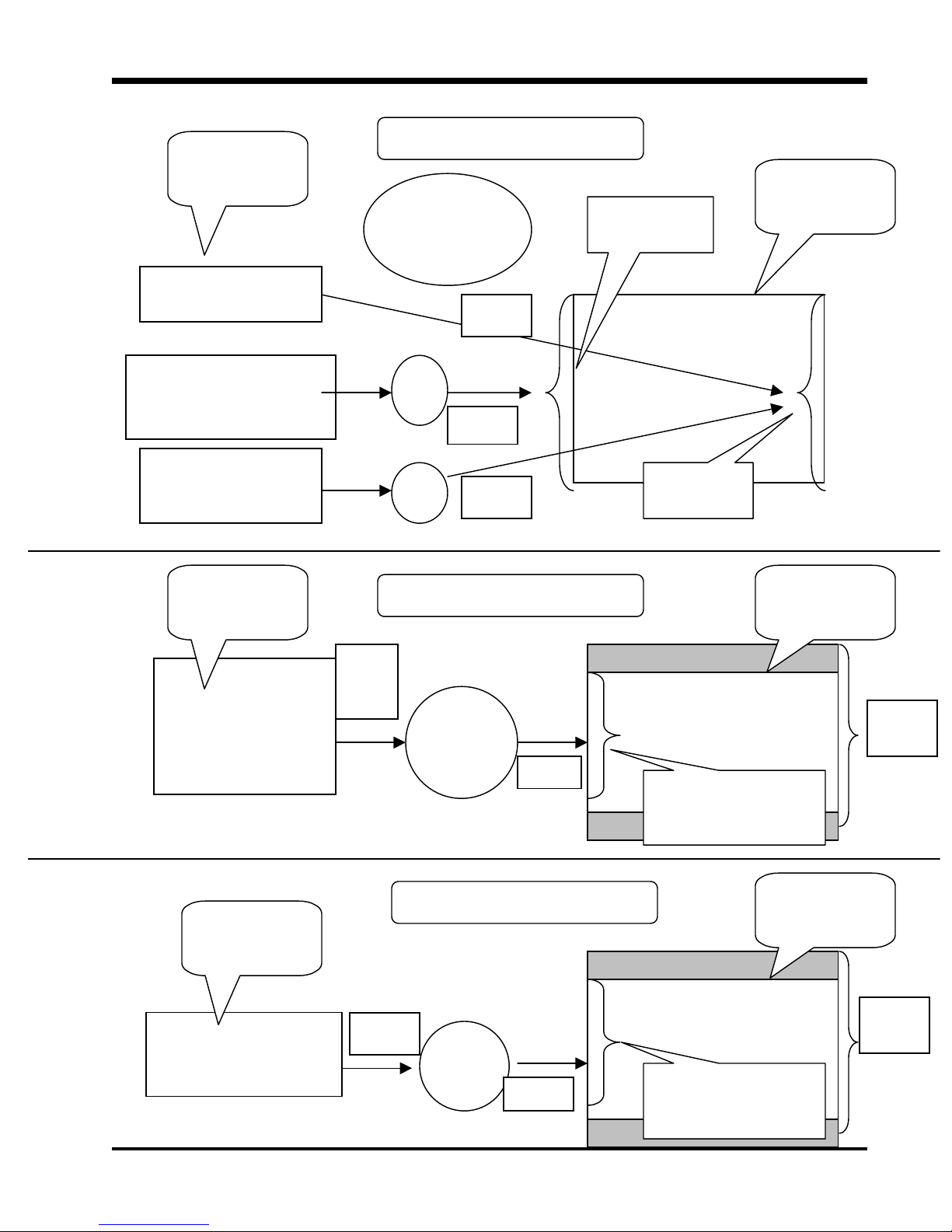

Figure 1 is a simplified diagram of the main Power Supply used in the ZP94/95 series Projection Television

Chassis. The primary control element of the power supply is I901 (the Switching Regulator IC), in conjunction with switching transformer T901. These two components, along with the supporting circuitry, comprise

a closed loop regulation system. Unlike previous Pulse Width Modulated (PWM) Switch Mode Zenith

power supplies, the regulation system in the this chassis utilizes Frequency Control Modulation with an

operational frequency of 85KHZ to 100KHZ, corresponding to full load and no load conditions, respectively. Primary regulation is provided by Q902, I902 and Q910, regulating the switching frequency at pin (3)

of I901 via pin 1, the regulation input to the IC.

B+ Generation for the Sub Power Supply Driver IC (see figure2)

Vcc for the Driver IC is first generated by the AC input. This voltage is called Start-Up Voltage. I901

requires 21V DC to operate normal. However, it will begin operation at 14.5V DC on pin (4) of I901.

When AC is applied, AC is routed through the main fuse F901 (a 5 Amp fuse), then through the Line filters

L901, 902, 903 and 904 to prevent any internal high frequency radiation for radiating back into the AC

power line. After passing the line filters it arrives at the bridge rectifier D901 where it is converted to Raw

150V DC voltage to be supplied to the power supply switching transformer T901 pin (1). However, one leg

of the AC is routed to a half wave rectifier D902 where it is rectified, routed through R905 and R906 (both

a 5.6K ohm resistor), filtered by C907, clamped by a 30V Zener D904 and made available to pin (4) of

I901 as start up voltage. The Red LED D903 is illuminated by this power supply. When this voltage reaches

14.4Vdc, the internal Regulator of I901 is turned on and begins the operation of I901. When the power

supply begins to operate by turning on and off the internal Switch MOSFET, the Raw 150V DC routed

through T901 (in on pin 1 and out on pin 2), is connected to pin (3) of I901 which is the Drain. The Source

of the internal Switch MOSFET is routed out of pin (2) through three low ohm resistors to hot ground. This

on and off action causes the transformer to saturate building up the magnet field. When the internal Switch

MOSFET turns off, the magnet field collapses and the EMF is coupled over to the secondary windings, as

well as the drive windings. The drive windings at pin (8 and 9) produce a run voltage pulse which is rectified

by D905, filtered by C908 then routed through R908, clamped by D904 and now becomes run voltage

(22V) for I901.

AC

4

I901

Switch

Mode

IC Reg

Raw 150V

T901

Switch Mode

3Drain

1

Q910

Buffer

Q914

SCR

Transformer

I902

Opti-Coupler

I903

Opti-Coupler

Q902

Buffer

Q905

SCR

28V

Shutdown

Input

<Figure 1>

28

29

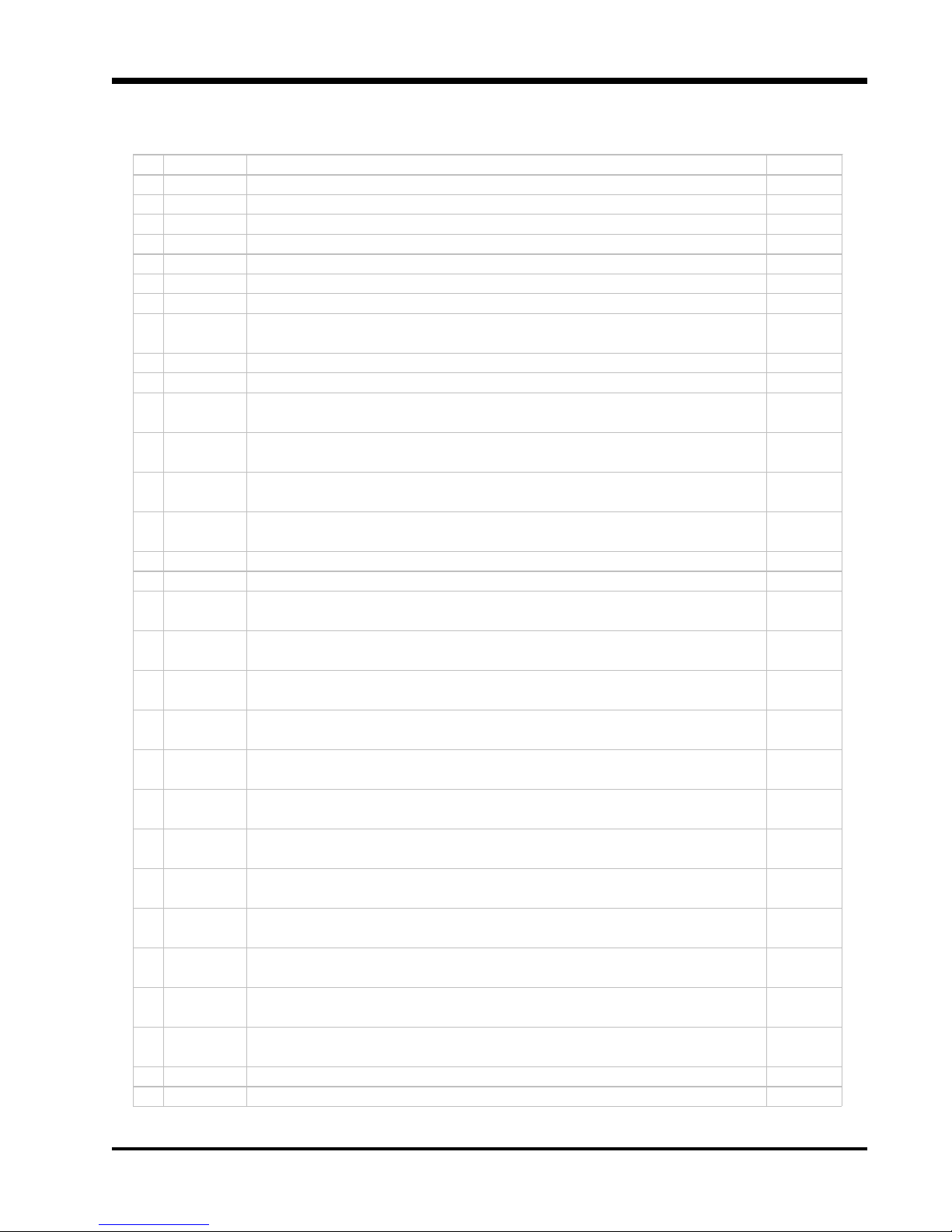

CIRCUIT DESCRIPTION

T901

Switch Mode

Transformer

SBY+7

PQS2

+

2

9

V

+29 to

Audio

Circuit

PQU1

Common-Action

Shutdown

Input

AC

I902

Opti-

Coupler

OCP

I903

Opti-

Coupler

CAS

1

3

Drain

I901

Switch

Mode

IC

Protect

Regulate

4

+28V

+35V

17

14

11

2

8

S903

Relay

S902

Relay

SW+35

PQS1

D912

G

D927

G

I905

I906

I907

SBY+11

PQD2 &

PQS1

SW+5

PQS2

I908

SW+12

PQD2

D949

G

D931

G

S901

AC Relay

To Main Power

Supply PQD1

Q905

Q901

D902

D903

R

5

Gnd

Vin

ZP94/95 SERIES CHASSIS STBY POWER SUPPLYCIRCUIT

Q902

Q910

<Figure 2>

CIRCUIT DESCRIPTION

Three primary voltages are developed that are needed to sustain run, maintain regulation, and support the

Shutdown Circuitry. They are Run Voltage generated from pin (8 and 9) of T901, +28V used for regulation,

and STBY +11V, respectively. The STBY represents always on; designating a supply that is active

when the unit is connected to AC power. The Power Supply utilizes a Shutdown circuit that can trigger

Q905 from 16 input sources. (6 of these are not operational in Stand by mode). I903 is activated by Q905,

applying gate voltage to Q901, which grounds out the Vcc at pin (4) of I901, disabling the power supply.

Audio Front 29V Regulator SW+29V Indicated by D912

The Audio Front 29V supply is generated from pin (17) of T901. This output is protected by E992, rectified by D910 and filtered by C918. This supply is routed to the Rear Audio Output IC IC01. This voltage is

what illuminates the Green Visual Trouble Shooting LED, D912.

Audio Rear and Center 29V Regulator SW+29V Indicated by D913

The Audio 29V supply is generated from pin (16) of T901. This output is protected by E993, rectified by

D911 and filtered by C917. This supply is routed to the Rear Audio Output IC IS16 and Center Audio

Output IC IC15. This voltage is what illuminates the Green Visual Trouble Shooting LED, D913.

STBY+11V Regulator I906 Indicated by D949

The STBY+11V supply is generated from pin (11) of T901. This output is rectified by D918 and filtered by

C928. This supply is routed to the Stand By +11 Regulator I906 pin (1). This voltage is what illuminates the

Green Visual Trouble Shooting LED, D949. The use of the power supply creating the SBY+11V supply

eliminates the need for a Stand-By transformer. The following explanation will describe the Turning ON and

OFF of the projection television.

STBY+7V Regulator I905 Indicated by D927

The STBY+7V supply is generated from pin (11) of T901. This output is rectified by D918 and filtered by

C928. This supply is routed to the Stand By +7 Regulator I905 pin (1). This voltage is what illuminates the

Green Visual Trouble Shooting LED, D927.

Power Supply Frequency of Operation during Run

The sub power supply in the ZP94/95 chassis works very similar to the previous models. This power supply

runs at 50% efficiency when the AC is applied with the set OFF. When the Horizontal deflection is in

operation, the power supply frequency fluctuates in accordance to current demands. The normal operational

range for the power supply is between 80 kHz to 100 kHz. The lower the frequency, the higher the current

supplied to the load. During Stand-By, it operates at 200KHz.

Power Supply Operational Frequency during Stand-By:

When the Horizontal deflection is defeated, the power supply no longer has a deflection load. The three

resistors connected to the source of the internal Switch MOSFET inside I901 via pin (2) detect this low

current demand. Pin (1) of I901 is the over current detection pin, however it is also the current demandsensing pin. When the current demand is low due to horizontal defeat, pin (1) will be less than 1.4V and the

internal frequency will switch to 200Khz. This is caused by the Quasi Resonant circuit operation. This

reduction of power supply frequency will move the frequency above the Bell of the power supply transformer and all secondary voltages will reduce to approximately 1/2 of their normal voltage. Due to the fact

that the power supply is still operating at 1/2 voltage output, the Green LEDs used for visual trouble sensing

will reduce in intensity, however they will remain lit, with the exception of the SW+12V and SW+5V

regulator. Which are turned off in Stand By.

30

CIRCUIT DESCRIPTION

Sw+9v and Sw+5v Regulator Operation in Stand-By:

Both of these ICs as well as the STY+11V and the STY+7V regulator ICs are DC to DC converters just

like last year. This is because of the wide range of input voltages from Stand-By to Normal operation of the

Power Supply. The SW+12V regulator (I908) and the SW+5V regulator (I907) are shut off during StandBy mode. Q002 and Q903 accomplish this. When the High for the power On/Off pin (53) of the Microprocessor is inverted by the relay driver Q002, and routed through the PQS1 connector pin (8). This is

detected by Q903, and its collector will go low. This will pull pin (5) of I907 and I908 low, turning off the

two DC to DC converters.

Some Shut-Down Detection Circuits Shut Off During Stand-By:

During Stand-By, all of the secondary voltages are reduced to approximately 50% of their normal voltage,

except the STBY voltages. This could cause a potential problem with the Short Detection circuits for

shutdown. To avoid accidental shut down, Q903 also controls the activity of Q908 and Q909. During

Stand-By, Q903 is turned on. This allows the Base of Q908 to be pulled through D945. This action turns

off Q908. When Q908 is off, it doesnt supply emitter voltage to the collector of Q909. The base of Q909

is connected to 6 Low Detection in-puts, (See the Sub Power Supply Shut Down Circuit explanation and

diagram for further details). When the power supply operates at 50%, the Short Detection circuit could

activate. By turning off Q909, no accidental shut down operation can occur.

ZP94/95 Chassis Has 4 Green and 1 Red LED On Sub Power Supply PWB.

This chassis utilizes 4 Green LEDs in the power supply cold side and a Red LED in the HOT side. The

power supply operates it two different modes, Standby and Projection on mode.

ZP94/95X CHASSIS L.E.D. (VISUAL TROUBLE DETEC TION) DIODES

SUB POWER SUPPLY PWB 4 GREEN L.E.D.s and 1 RED L.E.D.

4

3

1.9V

Sw

+5V

R936

D931

G

Vcc

I903

I903 Shutdown

Photocoupler

16 Shut Down

Inpu ts

1

2

Q905

Shutdown

SCR

Start Up

R905 R906

Osc B+

D903 is a RED L.E.D.

Off = No I901 B+

Blinking = Shutdown

R907

D903

R

Audio

Ft. 29V

Stby

+11V

D912

G

ALL GREE N L.E.D.s

24.2V

4

I901 Driver/

Output IC

100% Dead Time &

IC B+ Dete ctio n

Q901

Shutdown

SCR

R933

D949

G

Stby +7V

R930

D927

G

Run

24.2V

R908

31

CIRCUIT DESCRIPTION

Standby Mode:

4 Green LEDs and the Red LED are lit in the standby mode with the AC applied and the TV OFF;

· D903 Indicating Vcc applied to the Power Supply Driver IC Color RED

· Audio Front 29V Regulator SW+29V indicated by D912 Color GREEN

· Audio Rear and Center 29V Regulator SW+29V indicated by D913 Color GREEN

· STBY+11V Regulator I906 indicated by D949 Color GREEN

· STBY+7V Regulator I905 indicated by D927 Color GREEN

Power On Mode:

When the Power is turned ON, the other LED lights and the Red LED remains lit as well;

· D903 Indicating Vcc applied to the Power Supply Driver IC Color RED

· SW+5V Regulator I907 indicated by D931

LED USAGE:

The Visual LEDs are very useful in Trouble Shooting. Without removing the back cover, some diagnostics

can be made. By observing the operation of the Red and Green LEDs, the technician can determine if the

Sub Power Supply is running or not. The following will examine each LED and how they are lit.

D903 Indicating Vcc applied to the Power Supply Driver IC Color RED

This LED indicates any of four different scenarios,

1. Is there B+ (Vcc) available to the Sub Power Supply Driver IC? LED will be ON