Page 1

H/Z-IOO

COMPUTER

SERVICE

DATA

MANUALj

ADDITIONAL

AND

UPDATE

MATERIAL

DIRECTIONS:

REPLACE the following pages with the accompanying

updated pages:

Pages 3-21 through 3-28,

Pages 3-67/3-68,

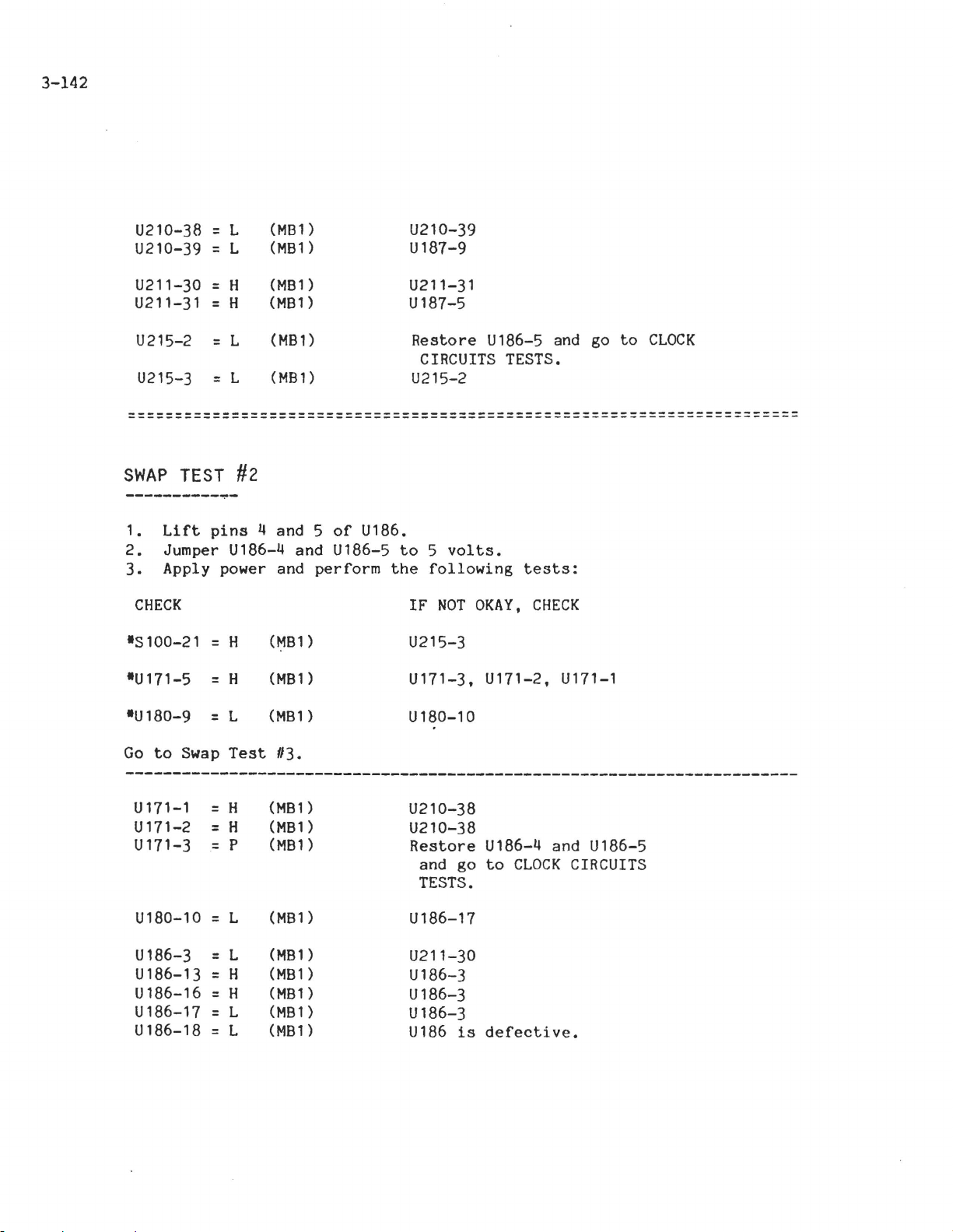

Pages 3-141 through 3-144,

ADD

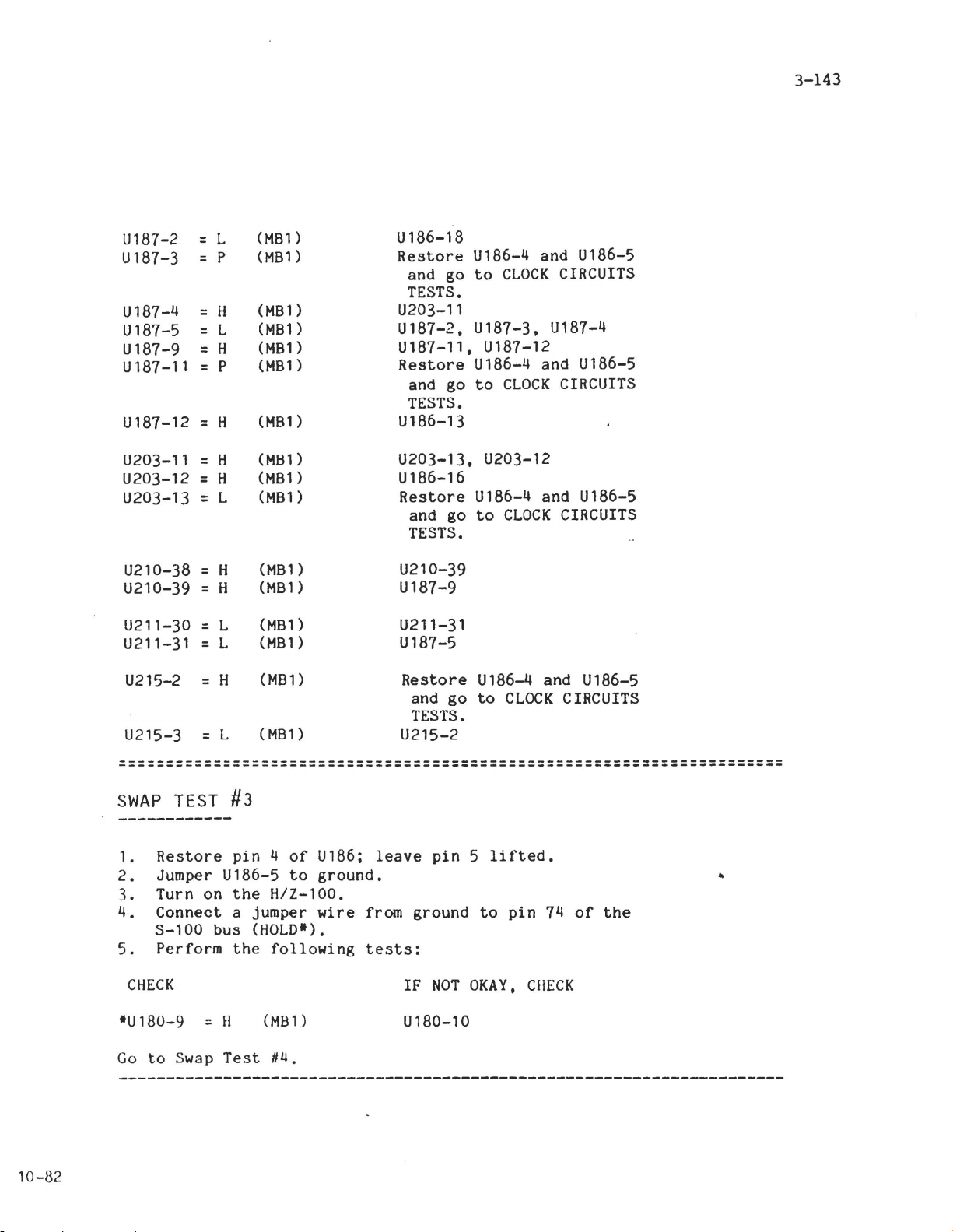

Part

CHANGE

First

and

H-207

the following:

Page

two

pages

Drives.

II

to Section 5. This

Floppy Disk

2-99,

Part

Parts

number

of

in

Section 5, Disk

is

Controller

Required,

the

programming

new

Board.

Controller

data

plug

for

...

the

..................

.........

.....,...

...................

:-

..

:-:-:-:-:-:-:

. .

. ..... ...

..

UPDATE

10/82

:

, .

::::}U:U~

..................

from:

Page

Part

from:

the Motherboard schematics

schematic

HE

969-18

3-159, Connectors

number

HE

432-363 to

revision

of

to:

the

sheet)

HE

and

4-pin

HE

432-1168.

Sockets,

right-angle

434-363.

(refer

.

connector

to the enclosed

...

/

Page 2

Page 3

2-99

INITIAL

SETUP

INTRODUCTION

The

H/Z-100

requires

However,

very

assembled

build

These

over

every

few

the

extender

a

Ie

PARTS

Qty.

2

1

4

20

ft.

20

1

2

1

29"

REQUIRED

Description

40-pin

34-pin

Small

#18

Large

10-pin

10-hole

Programming

is

only

about

due

to

test

and

following

x 46"

while

alligator

jumper

stranded

spring

easy

points

operating.

the

ribbon

ribbon

adapter

socket

to

15

the

extender

cables

surface.

unit

wire

wire

connector

plug

disassemble;

minutes

way

that

allow

is

cable

cable

clips

construction

plug

shell

to

the

unit

you

To

cables.

you

This

operating.

w/connectors

w/connectors

for

remove

can

get

to

permits

even

is

packaged,

reach

around

spread

an

all-in-one

the

motherboard.

while

this,

you

Part

HE

HE

HE

HE

HE

HE

HE

HE-432-1168

the

out

the

to

easily

No.

134-1108

134-1025

260-16

344-155

432-753

432-788

432-1061

there

you

unit

are

unit

H/Z-100

is

should

reach

10-82

Page 4

Page 5

3-21

TEST,

by-t"ti'e"wait-for

23

waits

MN/MX,

pinplaces

by

of

1s

RESET,

The

8088

(program

below

This

is

and

to

READY,

signal

is

CPU

brings

memory

Pin

is

low,

in

the

the

used

interrupts

are

the

line

pull

the

the

8088.

ready

goes

or

an

Pin

H/Z-100.

pin

for

Pin

set

counter)

top

is

ed

low.

clock

Pin

from

to

into

it

high.

I/O

23

Test

execution

idle

state.

33

Minimum/Maximum:

the

8088

functions

larger

21

Reset:

are

or

cleared,

end

of

asserted

ASchmitt

circuits

22

the

addressed

transfer

a

wait

dev

ices.

test"

continues,

in

When

change.

systems

disabled,

points

the

Ready:

This

Input:

software

the

placed

Goes

to

1

when

retimes

data.

state

allows

This

otherwise

minimun

in

the

Usually,

and

multi-processing

high

certain

and

the

the

memory

megabyte

the

RESET

tr

igger

it

This

is

memory

When

until

using

input

instruction.

the

Logic

mode,

maximum

to

instruction

range

shapesthis

before

an

or

this

the

the

the

reset

registers

address

(FFFFOH).

line

acknowledgement

I/O

line

addressed

the

8088

is

examined

processor

one

on

mode

mode,

maximlDll

systems.

the

16

at

applying

port

is

low,

with

If

pin

this

used

some

mode

8088.

in

the

pointer

bytes

U236-11

signal

it

that

it

the

device

slow

10-82

The

READY

one

on

8088

to

This

the

processor

eLK,

for

is

clock

Pin

provide

signal

15-MHz

optimized

the

signal

U236-4.

to

19

timing

crystal

active

swap

is

ensure

8088

comes

timing

processor,

port

generated

U236

correct

Clock

to

the

from

at

as

when

synchronizes

set

Input.

8088.

U236-8

Y103.

inside

886

this

to

the

provide

U205-9

this

up

and

Five-megahertz

which

Duty

line

cycle

8088.

also

system

places

signal

hold

derives

When

times.

is

about

goes

timing.

a

with

it

the

to

logic

the

clock

from

33i

8088

the

Page 6

3-22

r--------------------------:~

1111.

......

-----------=

~-----'~~,....,U.,.,2~OJ

....

'<.ItI-L-D._('7'(I

D11H

lS'"

44J''''

.......

L IIl4Cll.O

MOL'·

~----~II.I>

..

IlEF·

IW"

ISWAP

"'01""*-+"'l

PORTI

Sllf~IHT

IML

51lL

••\.........

+-F~

"'-h;,q-~"

+--tt!.)~A:-;-L';.;;JT;--tI!P

P

•

""'04.

~---,P--st

PROCESSOR

SWAP

PORT

(MBl)

Page 7

3-23

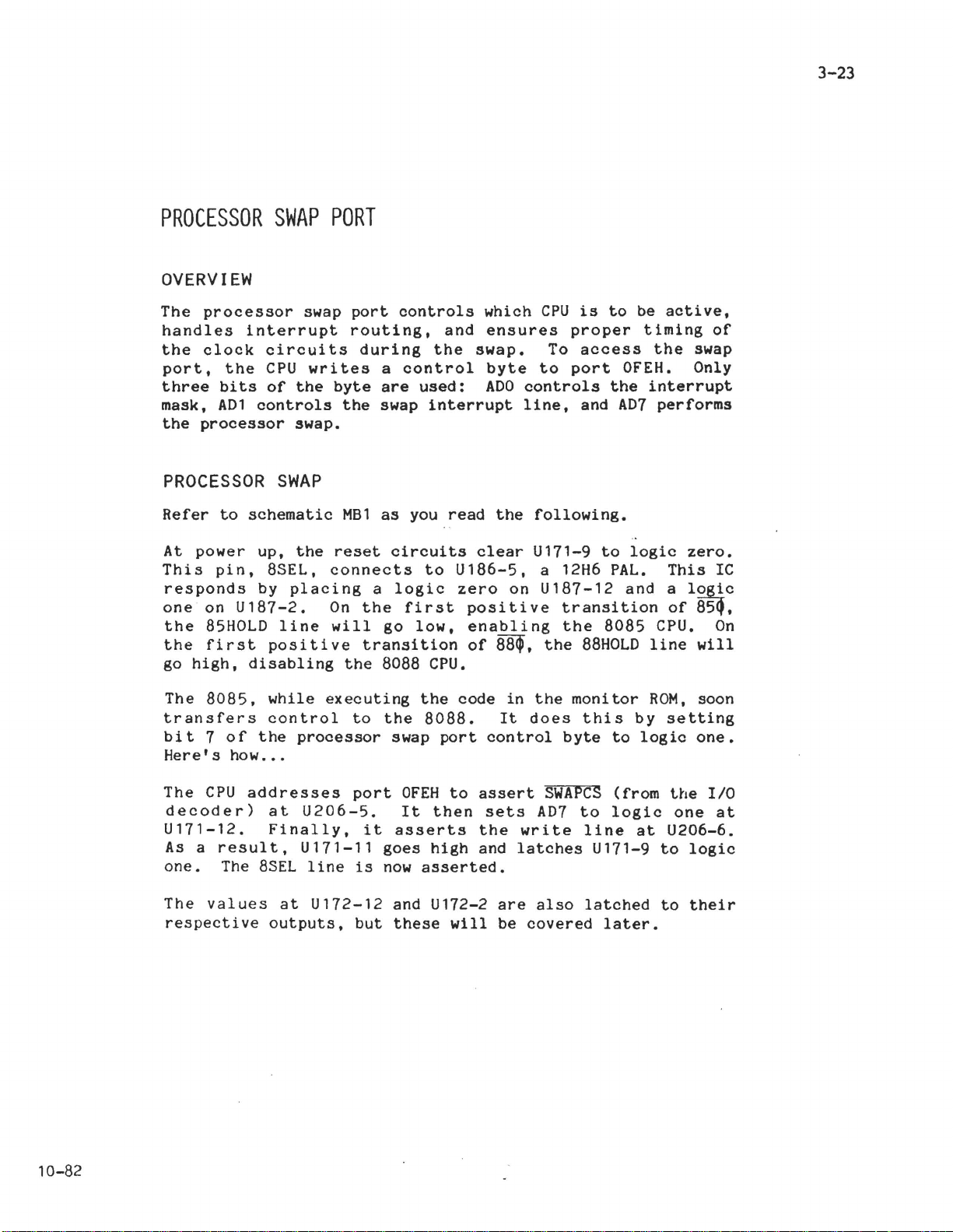

PROCESSOR

SWAP

OVERVIEW

The

processor

handles

the

port,

three

mask,

the

interrupt

clock

the

bits

ADl

processor

PROCESSOR

Refer

At

This

responds

one

the

the

go

to

power

pin,

on

85HOLD

first

high,

schematic

U181-2.

disabling

swap

circuits

CPU

writes

of

the

controls

swap.

SWAP

up,

the

8SEL,

by

placing

line

positive

PORT

port

routing,

during

a

byte

reset

connects

On

will

are

the

swap

MBl

as

a

the

go

transition

the

8088

controls

the

control

used:

interrupt

you

circuits

to

logic

first

low,

cpu.

which

and

swap.

read

clear

U186-5,

zero

positive

enabling

of

ensures

byte

ADO

controls

line,

the

on

~,

CPU

is

proper

To

access

to

port

and

following.

U171-9

a 12H6

U181-12

the

to

transition

the

88HOLD

to

OFEH.

the

AD7

logic

PAL.

and

8085

be

active,

timing

the

interrupt

performs

This

a

of

CPU.

line

of

swap

Only

zero.

IC

l~c

85~,

On

will

The

8085,

transfers

bit

7

of

Here's

The

CPU

decoder)

U111-12.

As

a

result,

one.

The

respective

The

values

while

control

the

how

.•.

addresses

at

Finally,

8SEL

outputs,

executing

processor

U206-5.

Ul11-11

line

at

U172-12

to

the

swap

port

it

goes

is

now

and U172-2

but

these

the

8088.

OFEH

It

then

asserts

high

asserted.

code

port

to

will

in

It

control

assert

sets

the

and

are

be

the

does

SWAPCS

AD7

write

latches

also

covered

monitor

this

byte

to

line

U171-9

latched

to

(from

logic

later.

ROM,

by

logic

at

soon

setting

one.

the

one

U206-6.

to

logic

to

their

1/0

at

10-82

Page 8

3-24

The

8SEL

logic

to

change

The

HOLD.

S-100

to

disable

CPUs

the

happens.

turn,

The

control

respond

8088

board

one.

bus

raises

of

line.

U186-18

to

line

takes

both

at

U186

that

the

now

logic

at

control

the

by

returning

U186-3

asserts

the

S-100

generated

H/Z-100.

logic

to

change

one.

U185-11

8085

and

the

pHLOA

one.

of

and

the

the

causes

to

asserts

the

the

their

8085

HAK

line

line

HOLD·

U186-13

logic

H/Z-100.

8088

hold-acknowledge

zero.

whenever a

This

through

at

U171-2.

at

pin

to

logic

request

17.

one

to

change

and

U186-16

board

causes

U187. Both

can

signals;

When

This,

at

U180-9.

now

on

to

the

U186

this

in

take

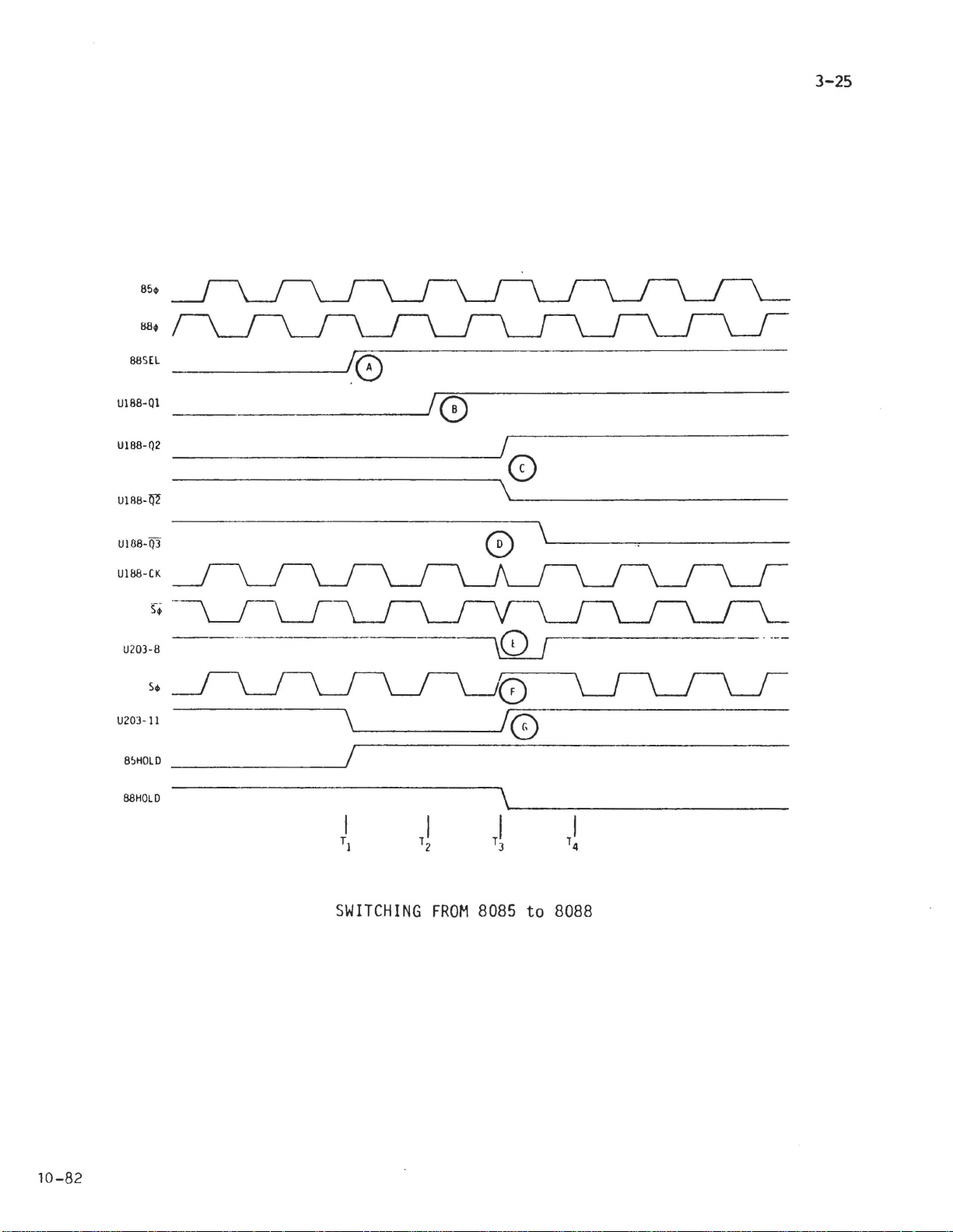

SWAP

The 88SEL

This

system

to

is

The

clocks;

these

from

clock

circuits.

TIMING

circuit

the

no

longer

8085

clocks

one

clock

other.

line,

line

and

the

clock

also

is

designed

line

It

active

the

8088

8085 from

are

stable.

to

S~.

which

goes

when

also

when

run

Y101

another

to

to

the

H/Z-100

ensures

the

other

on

and

they

can

can

U188-4,

suppress

that

separate

the

aren't

cause

upset

a

switches

the

CPU

is

8088 from Y103.

a

the

quad

any

CPU

enabled.

crystal-controlled

in

glitch

D-type

glitches

being

phase.

on

timing

from one

Switching

the

in

latch.

on

the

CPU

disabled

Although

system

other

Page 9

3-25

10-82

SWITCHING

FROM

8085

to

8088

Page 10

3-26

To

see

spike,

how

refer

U188 and

to

the

its

associated

waveforms on

the

circuits

previous

block

page.

this

The two

8085

inverters

the

through

U225B

At

logic

The

U188-2,

The

shown

gate

the

two

immediately

waveforms

Up

OR

Q2

since

same,

This

until

and

active

to

time

next

next

at

88~

clocks

until

gate,

and

forces

one

the

at

Q3

Q2

causing

time

top

waveforms

8088

the

clock

T1,

clock

clock

C.

U203B. At

clock

illustration.

this

has

went

CPUs.

U200-2

processor,

inverter

U188.

the

as

shown

pulse

Q1

output

pulse

This

to

are

nearly

returns

time,

been

of

U188

low

U203-8

the

T4

(waveform

8088

system

These

and

U200-14.

to

at

at

at

causes

tri-states

the

the

~

to

the

logic

have

at

time

are

the

are

then

is

l80-degrees

output

to

F).

form

selected;

A

on

U188-9

B.

same

line.

zero,

one.

been

T3,

go

clock

U200-1

the

to

respective

present

Assuming

Sl.

waveforms

latches

the

Q2

U200

time,

Since,

causing

of

U203-8,

This

in

opposite

both

logic

output

is

low

It

also

the

output

through

Q2

goes

in

out

of

the

is

inputs

zero

at

U225-3

clocks

at

that

and

couples

88SEL

this

the

this

phase,

spike

another

because

states.

to

for

the

inputs

the

8085

85'

couples

through

line

illustration.

logic

to

exclusive-DR

low

example,

U203C

(waveform

goes

one

latch

to

the

at

D

exclusiveits

However,

are

to

logic

couple

in

inputs

the

of

is

to

into

high,

the

clock

the

the

E).

one

Page 11

At

time

causes

gate

8088

As

U188

completely

To

illustration.

at

signal.

mentioned

perform

see

T4,

the

U225A

how

the

01

output

to

earlier,

is

disabled

this

first

pass

to

positive-going

of

the

the

ensure

before

is

done,

U188

system

other

that

again

the

to

edge

go

clock,

function

the

other

refer

high.

CPU

of

being

CPU

to

the

This

which

that

is

the

8088

disabled

activated.

clock

opens

is

now

88SEL

waveforms

3-27

the

the

and

is

Once

8085

which

exclusive-OR

inputs

to

Both

hold-acknowledge

the

17

At

logic

preset

zero

state.

Al

This

the

line

manufacturer.

8088

preset

8085

which

time

so

NDEF

again,

to

is

are

CPUs

one,

states.

at

at

last

that

is

the

coupled

both

respond

to

drives

T3,

U187-2

thi

IC

(8088)

can

active.

now

thus

s

assume

8088.

gate

the

HOLD

pin

the

the

into

time,

connects

be

For

that

At

to

is

the

same

latches

by

going

signals

4

through

S-100

Q2

line

releasing

The

next

U187-5,

U

188-7

line.

used

the

the

timeT1,

U203-11.

Q2

state,

at

into

to

U171.

pHLDA

goes

the

88l

removing

goes

to

pin

This

for

any

H/Z-100,

H/Z-100

the

The

line

U203-11

U187.

a

U186;

line

low

latches

clock

high

21

of

line

function

this

is

switching

from

HOLD

the

This

at

and

pulse

is

88SEL

other

U180-9.

the

to

the

a

line

line

U188.

goes

stat~

8088

asserts

U203-11

at

U187

latches

8088

drive

S-100

"not-to-be-defined"

by

asserts

input

to

to

from

U215-3

the

from

goes

of

Since

logic

and

pin

HAK

returns

from

the

the

bus

to

computer

when

the

high,

this

both

zero

sending

3

and

at

pin

their

logic

hold

high.

form

the

to

10-82

Page 12

3-28

INTERRUPT

The

interrupt

are

sent

is

set

processor

8085

is

ac

swap

the

8088

8088

Immediately

processor.

are

logic

U225-1

inverts

So

all

U189A.

The

8SEL

U1898

the

8085

and

5SEL

to

or

gets

t i

ve.

port

is

regardless

O.

shown

the

interrupts

non-maskable

line.

and

hands

will

MASK

mask

the

cleared

swap

all

interrupt

the

will

active.

after

Control

one.

resulting

U189C.

go low.

circuits

currently

port.

in

terrupt

disable

of

the

These

near

are

through

which

the

control

by

If

all

mask

reset.

lines

the

logic

sent

is

AND

ensure

active

setting

set.

requests.

request

the

8085

interrupt

bit.

the

5SEL

two

lines

8085

zero

to

U189D.

the

gates

to

the

that

CPU.

or

clearing

and

the

If

cleared.

is

blocked.

and

enable

requests

Here's

8085

at

U171-8 and

connect

IC

on

the

to

enable

the

8085;

complement

to

the

8088

CPU.

interrupt

The mask

bit

8085

hoW

CPU

is

the

are

it's

is

MSKatU112-6

to

schematic.

U189A

maskable

of

5SEL.

8088.

8SEL

requests

bit.

0

of

active,

and

the

However.

8088.

sent

will

to

done

.••

the

active

U225-9 and

U220-2

and

U189D.

through

disables

Later.

go

MSK.

the

the

8085

the

If

the

when

high

If.

while

zero.

interrupt

if

an

NMI,

U156-6

The

NMINT

port.

As

a

H/Z-100 swaps

When

and

U189C. U189A

logic

the

routed

U220-2

interrupt

The

result,

the

zero

R:rK

to

the

request

line

8088

bit

the

8085

disables

will

other

U155-8

to

CPU

at

at

BOB8

is

from

request

go

high

connects

input

the

is

and

U225-9.

U?25-10.

processor.

selected.

U189A

both

to

is

goes

8088

processor

active.

U189D

So,

and

the

should

assert

to

U155-9

the

low

no

all

the

MSK

U189D.

8085 and

occur.

the

MSK

line

to

assert

as

8SEL

are

disabled

matter

interrupt

line

the

either

NMINT

in

the

which

the

described

is

high

what

is

set

This

8088.

line.

processor

is

8SEL

to

enable

because

the

requests

to

logic

blocks

However.

standard

swap

also

line.

previously.

high.

U1898

5SEL

setting

will

the

or

The

is

of

be

Page 13

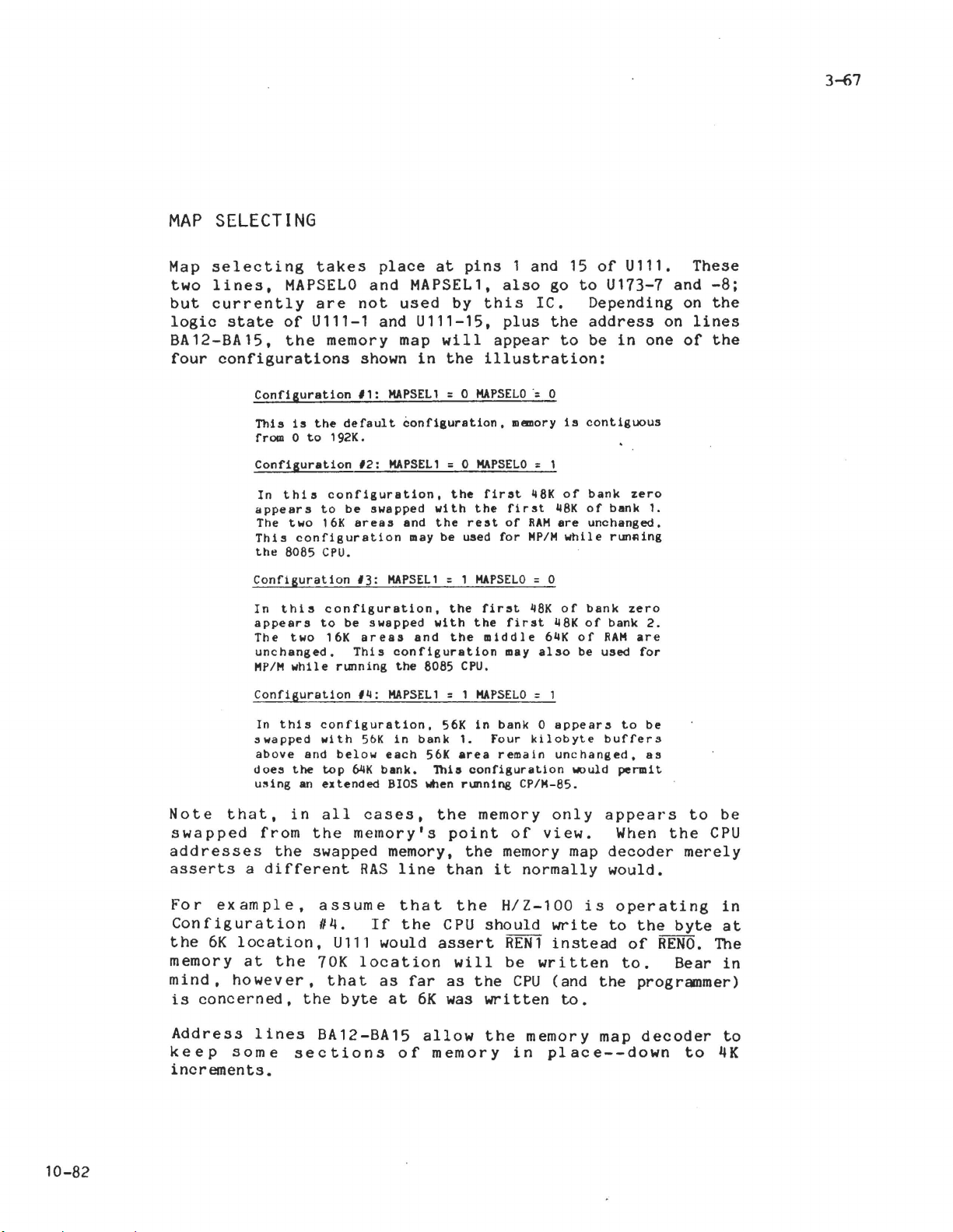

3-67

MAP

Map

but

SELECTING

selecting

two

lines,

currently

logic

state

BA12-BA15,

four

configurations

Configuration

In

appears

The

HP/H

takes

MAPSELO

are

of

U111-1 and

the

Confisuration

This

is

from0to

Confisuration

In

appears

The

This

the

unchanged.

the

this

to

two

configuration

8085

this

to

two

while

place

and

not

used

memory map

shown

11:

HAPSEL

default

192K.

configuration,

be

16K

areas

CPU.

configuration,

be

16K

This

running

confisuration,

12: HAPSELl = 0

swapped

and

13:

HAPSELl

swapped

areas

configuration

the

at

pins

MAPSEL1,

by

U111-15,

will

in

the

1 = 0

HAPSELO-=0

the

with

the

the

with

8085

= 1

the

the

rest

HAPSELO

the

CPU.

maybeused

and

1 and 15

also

this

IC.

plus

appear

illustration:

memory

HAPSELO

first

for

first

of

= 1

48K

RAH

HP/H

= 0

first

first

middle

alay

48K

64K

also

go

the

to

48K

are

of

48K

to

is

of

while

of

be

of

U111.

U173-7

Depending

address

be

in

one

contiguous

bank

zero

of

bank

runfling

zero

bank

RAH

1-

2.

are

for

unchanged.

bank

of

used

on

and

on

of

These

-8;

the

lines

the

Confisuration

In

swapped

above

does

using

Note

swapped

that,

from

addresses

asserts

For

a

example,

Configuration

the

6K

location,

memory

mind,

is

Address

keep

at

however,

concerned,

lines

some

increments.

this

configuration,

and

the

an

in

the

the

swapped memory,

different

assume

114.

the

70K

the

BA12-BA15

sections

14: HAPSELl = 1

with

5t>K

below

top

64K

extended

all

bank.

cases,

memory's

RAS

If

U111

would

location

that

as

byte

in

bank

each

56K

This

BIOS when

line

that

the

far

at

6K

allow

of

memory

56K

1.

area

configuration

running

the

point

the

than

the

CPU

assert

will

as

was

HAPSELO

in

= 1

bank0appears

four

kilobyte

remain

CP/H-85.

memory

of

memory

it

normally

H/Z-100

should

REN1

be

the

CPU

wri

tten

the

memory map

in

unchanged,

only

buffers

would

appears

view.

map

decoder

would.

is

write

to

instead

written

(and

the

to.

place--down

to

be

as

permit

When

the

operating

the

byte

of

RENO.

to.

Bear

programmer)

decoder

to

be

CPU

merely

in

at

The

in

to

to

4K

10-82

Page 14

w

Cl'l

CD

I

A~

/4.7

m>

m>

I

21{>~

U1Bl

LS'244

" p

14

12

3 P

& P

P

p

111

r

19

BA0

P

P ,

~~7

/

r.p!I_7:

~~'!'1

..

7·1~·

.'"3

n

--------

256'1.4

PROM

U179

_

10

82.~129

5

Af

,

1

4

100E:C

.3

2.

,

1~

A"7

"lolll4·1JI

C[1

iJ

12./

~

~

'1

'"

_1(21/

I"'"

.q/

..,-

03

CE2

~'4

P

P

P

P

P

P

P

P

P

P

P

P

p

BA~.

5A1

P

p.

BA2

-

BA3

HI1

-~

H •

P4

~

P 1

P 2

PJ

P,s.

Pl~

P

13

U159

(,1

G2A

G28

LS1H

~d·'n

1 A

,

B

3 c

U157

...

Gl

A

!>

~~'39

"43";U-

G2

A

8

"

l-I

1~

101

...\4.1

.13.

H

P

12

I""

11

~

1""1'

H

V

t!.

I""

p

1/

,..,

..

H

4/

p

5

,/

P

p

7

~2/

~

,..,

11/

H_

,_/

p-

~

...

q

~

T~RSTATCS

MEMCTRl,.CS

l"I1·ADCS

~WAPCS

D5~5EL

!Z39AC.~

~2S9AC.S'"

KEY8DSH

,"~ZIC5

8,5~CS

EPCl ACS

EPCl BCS

I/O

PORT

DECODER

CMB2)

I

I/O

PORT

DECODER

810SEL

r

Page 15

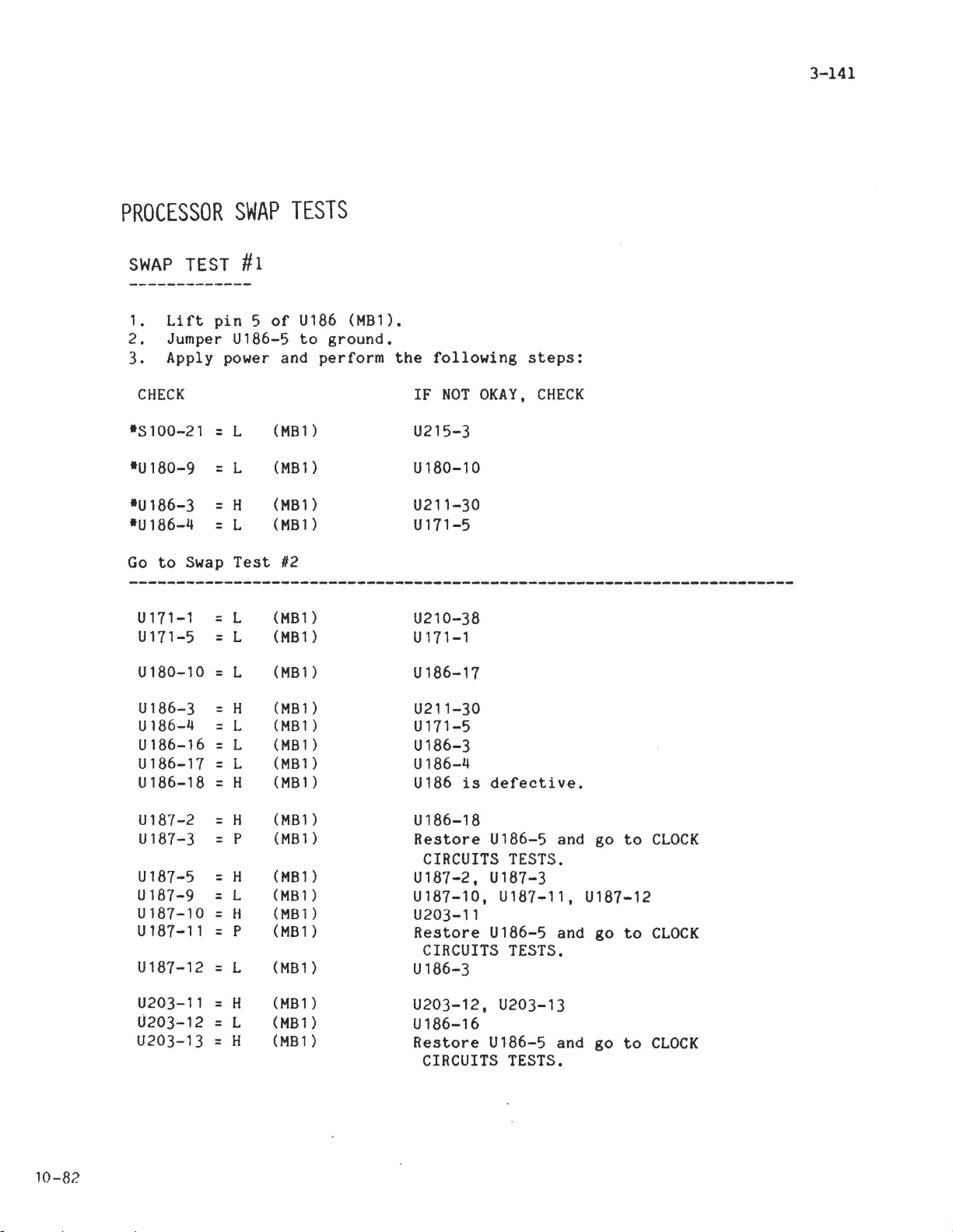

3-141

PROCESSOR

SWAP

1.

2.

3.

CHECK

·S100-21

·U180-9

·U186-3

·U186-4

Go

U17l-l

U171-5

TEST

Lift

Jumper U186-5

Apply power and

to

Swap

SWAP

#1

pin5of

= L

L

=

H

=

= L

Test

::

L

= L

TESTS

U186

to

ground.

perform

(MS1)

(MS1)

(MS1)

(MS1)

#2

(MS1)

(MS1)

(MS1).

the

IF

U215-3

UlaO-l0

U2l1-30

U17l-5

U2l0-38

U171-1

following

NOT

OKAY,

steps:

CHECK

U180-10

U186-3

U186-4

U186-l6

U186-17

U186-l8

U187-2

U187-3

U187-5

U187-9

U187-l0

U187-ll

U187-l2

U203-1l

U203-12

U203-13

::

=

::

=

=

=

::

=

=

= L

::

::

= L

::

::

::

(MS1)

L

(MS1)

H

(MS

L

L

L

H

H

p

H

H

P

H

L

H

1)

(MS

1)

(MS1)

(MS1)

(MS1)

(MS1)

(MB

1)

(MS

1)

(MS1)

(MS1)

(MS1)

(MS1)

(MS1)

(MS

1)

U186-17

U2ll-30

U171-5

U186-3

U186-4

U186

U186-l8

Restore

U187-2. U187-3

U187-10,

U203-l1

Restore

U186-3

U203-l2,

U186-l6

Restore

is

CIRCUITS

CIRCUITS

CIRCUITS

defective.

U186-5 and go

TESTS.

U187-ll,

U186-5 and

TESTS.

U203-l3

U186-5 and

TESTS.

to

U187-12

to

go

to

go

CLOCK

CLOCK

CLOCK

10-82

Page 16

3-142

L

H

H

L

L

#2

(MB1)

(MS

1)

(MS1)

(MS1)

(MS

1)

(MS

1)

4 and 5

(MS1)

(MS1)

of

U186.

perform

U210-38

U210-39

U211-30

U211-31

U215-2

U215-3

-----------------------------------------------------------------------

-----------------------------------------------------------------------

SWAP

1.

Lift

2.

Jumper U186-4 and U186-5

3.

Apply power and

CHECK

.S

100-21 = H

·U

171-5 = H

=L

=

=

=

=

=

TEST

pins

U210-39

U187-9

U211-31

U187-5

Restore

CIRCUITS

U215-2

to

5

the

following

IF

NOT

U215-3

U171-3, U171-2, U171-1

volts.

OKAY,

U186-5

TESTS.

tests:

and

CHECK

go

to

CLOCK

·U180-9

Go

to

Swap

U171-1 = H

U171-2

U171-3

U180-10=L

U186-3

U186-13

U186-16

U186-17=L

U186-18

= L

Test

= H

= p

L

=

H

=

H

=

L

=

(MS1)

#3.

(MS1)

(MSl

(MS1)

(MS1)

(MS

1)

(MS

1)

(MS1)

(MS

1)

(MS1)

U180-10

U210-38

)

U210-38

Restore

and go

TESTS.

U186-17

U211-30

U186-3

U186-3

U186-3

U186

is

U186-4 and U186-5

to

CLOCK

defective.

CIRCUITS

Page 17

3-143

U187-2

U187-3

U187-4

U187-5

U187-9

U187-11

U187-12

U203-11

U203-12

U203-13

U210-38

U210-39

U211-30

U211-31

U215-2

U215-3

=

=

=

=

=

=

=

=

=

=

=

=

=

=

=

= L

(MB1)

L

p

(MB1)

(MB1)

H

(MB1

(MB1)

(MB1)

(MB1

(MB1)

(MB1)

(MB1)

(MB1)

(MB1)

(MB1)

(MB1)

(MB1

(MB1)

)

)

)

L

H

P

H

H

H

L

H

H

L

L

H

U186-18

go

go

U186-4

to

CLOCK

U186-4

to

CLOCK

U203-12

U186-4

to

CLOCK

U186-4

to

CLOCK

Restore

and go

TESTS.

U203-11

U187-2_ U187-3_

U187-11_ U187-12

Restore

and

TESTS.

U186-13

U203-13_

U186-16

Restore

and

TESTS.

U210-39

U181-9

U211-31

U187-5

Restore

and go

TESTS.

U215-2

and U186-5

CIRCUITS

U187-4

and U186-5

CIRCUITS

and U186-5

CIRCUITS

and

U186-5

CIRCUITS

10-82

======================================================================

SWAP

1.

2.

3.

4.

5.

·U180-9

Go

TEST

Restore

Jumper U186-5

Turn on

Connect

S-100

Perform

CHECK

= H

to

Swap

#3

pin4of

to

the

H/Z-100.

a jumper

bus (HOLD·).

the

following

(MB

1)

Test

#4.

U186;

ground.

wire

from ground

tests:

leave

IF

U180-10

pin

NOT

5

lifted.

to

pin

OKAY_

74

CHECK

of

..

the

Page 18

3-144

U180-10 = H

U186-13

U186-16

U

186-17

tNOTE:

=H

= H

= H

Before

pins

check

(MB1)

(MB1)

(MBl

(MB1)

replacing

6 and

for

)

15.

ground

and

U186-17

U186

U186

U186-13. U186-18

U186.

between

at

pins

is

is

check

pins

2.

defective.

defective.t

the

continuity

7 and

8.

9.

10.

t

between

14.

Also

11. 12. and

19.

===============;======================================================

SWAP

1.

2.

.U180-9

Remove

Connect

CHECK

TEST

=H

#4

the

the

jumper

jumper from

(MB1)

between

ground

pin

IF

U180-10

5

NOT

to

and

pin

+5

volts.

OKAY.

5.

CHECK

End

of

tests.

U180-10 =H

U186-13

U

186-17

U186-18

tNOTE.

= H

= H

=H

Before

pins

check

(MB1)

(MB1)

(MB1)

(MB1)

replacing

6 and

for

15,

ground

and

U180-17

U186

U186-13. U186-18

U186

U186.

between

at

pins

is

is

check

pins

2.

defective.

defective.

the

continuity

7 and

8,

9,

t

t

14.

10. 11,

between

Also

12,

and

19.

Page 19

PARTS

C!

~~

?CJ

LIST

1~,..

:':5:':

:Tl~'i

HEATH

Part

';0.

c:

;lCe

Com?

IT

~Io.

DESCRIP710:/

HEAT"

Part

:/0.

CIRCUIT

Compo

OESCRl?i!C~

~O.

HEl,iH

Part

No.

INTEGRATED

U

170

U171

U172

UI73

U174

U175

U176

U

177

U178

U179

U180

U181

Ul82

u183

U184

u185

U186

U187

U188

U189

U190

U191

U192

U193

U194

U195

U196

U197

U198

U199

U200

U201

U202

U203

U204

U205

U206

U207

U208

U209

.......

0

I

CO

N

CIRCUITS

74ALS1020

74ALS74

7"ALS74

HAL14L4

74LS32

74L510

74L5174

74LS240

74LS244

825129

74LS367

74LS244

74L514

7"LS02

74LS156

74L514

HA1.12H6

74ALS74

74LS175

741.S08

2764

ROI1

4.000

HHz

74L5169

'!4U367

7417

74L5240

74L5373

741.Sfl3

74LS373

741.S156

74LS368

74L5125

74A1.S74

74LS86

8741A

74S74

74ALS02

74LS14

8259A

825~A

(CONTINUED)

PROM

oscillator

I

HE

443-1081

HE

443-1051

HE

443-1051

HE

444-130

HE

443-875

HE

443-797

HE

443-879

HE

443-754

HE

443-791

HE

444-101

HE

443-857

HE

443-791

HE

443-872

HE

443-779

HE

443-1036

HE

443-872

HE

444-128

HE

443-1051

HE

443-752

HE

443-780

HE

444-87

HE

150-132

HE

443-1054

HE

443-857

HE

443-72

HE

443-754

HE

443-837

HE

443-837

HE

443-837

HE

443-1036

HE

443-1024

HE

443-811

HE

443-1051

HE

443-891

HE

444-141

HE

443-900

HE

443-1045

HE

443-872

HE

443-1012

HE

443-1012 Wire. bare

INTEGRATED

U210

U211

U212

U213

U214

U215

U216

U217

U218

U219

U220

U221

U222

U223

U224

U225

U226

U227

U228

U229

U230

U231

U232

U233

U234

U235

U236

U237

U238

U239

U240

U24'

U242

U243

U244

U245

U246

U247

U248

- -

CIRCUITS

8085A

8088

74LS273

74LS373

74LS244

74L5125

74ALS28

74LS244

96LS02

74ALS74

74LS04

74L532

74L500

74L5244

74ALS28

74AL537

74S288'

74LS373

781.12

791.12

75189

75452

555

timer

74ALS74

74ALS74

74ALS10

8284A

74LS125

74ALS74

74LS244

4.9152

74L5244

2661-2

2661-2

74LS244

75188

75189

75189

75188

(CONTINUED)

PROM

.12V

regulator

-12V

regulator

MHz

oscillator

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

443-1010

443-1009

443-805

443-837

443-791

443-811

443-1048

443-791

443-1040

443-1051

443-755

443-875

443-728

443-791

443-1048

443-1049

444-105

443-837

442-644

442-646

443-795

443-74

442-53

443-1051

443-1051

443-1047

443-1011

443-811

443-1051

443-791

150-133

443-791

443-1061

443-1061

443-791

443-794

443-795

443-795

443-794

I

I

CRYSTALS

YI01

YI02

Y103

CONNECTORS-SOCKETS

HARDWARE

HISCELLANEOUS

0101

0102

0103

0104

SW101

Xl01

10.000

6.000

15.000

8-pinICsocket

14-pinICsocket

16-pinICsocket

18-pinICsocket

20-pinICsocket

24-pinICsocket

28-pinICsocket

40-pinICsocket

2-pin

3-pin

4-pin

9-pin

10-pin connector

20-pin

25-pin

25-pinHright-angle

40-pin

Jumper

S-10D

14

14

4-40 x

4-40 x

PC

Wire, blue wirewrap

IN5817

IN4149

1N4149

1N4149

8-section

Audio

I I

MHz

crystal

MHz

crystal

MHz

crystal

connector

connector

right-angle

right-angle

connector

connector

Fright-angle

connector

connector

connector

board edge connector

lockwasher

nut

5/16"

hex

5/16"

phillips-head

board

black

diode

diode

diode

diode

slide

transducer

HE

404-645

HE

404-647

HE

404-644

HE

434-230

HE

434-298

HE

434-299

HE

434-310

HE

434-311

HE

434-307

HE

434-310

HE

434-253

HE

432-1171

HE

connector HE-434-363

molex

"0"

"0"

"0"

spacerHE255-757

screw

switch

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

HE

432-1102

432-1202

432-903

432-1227

432-1195

432-1194

432-1062

432-1041

432-1193

254-9

252-15

250-1469

85-2653-1

340-8

344-189

57-507

56-56

56-56

56-56

60-621

473-29

w

I

t-'

lJ1

\.0

Page 20

Page 21

::::::::::::::::::::::::::;:;:::;::::::::::::::::::.

":;:::::::::::::::;'

.........

.li

.:->:-:-:.:-:-:-:

DISK

PART

I -

CONTROLLER

AND

H/Z-207

DRIVES

II

.........

·........

. ..... .

·.

.........

.........

· .

·........

· .... ....

..................

........

·.. . . ....

·.... ....

-:-:-:.:-:-:-:-:-:

.........

· .

.....

....

·........

·.. .. . . . .

.........

·. .. .... .

........

' .

..................

..................

.'';-:'>:-:-:':-'

· ........

.........

.........

· .

..................

INTRODUCTION

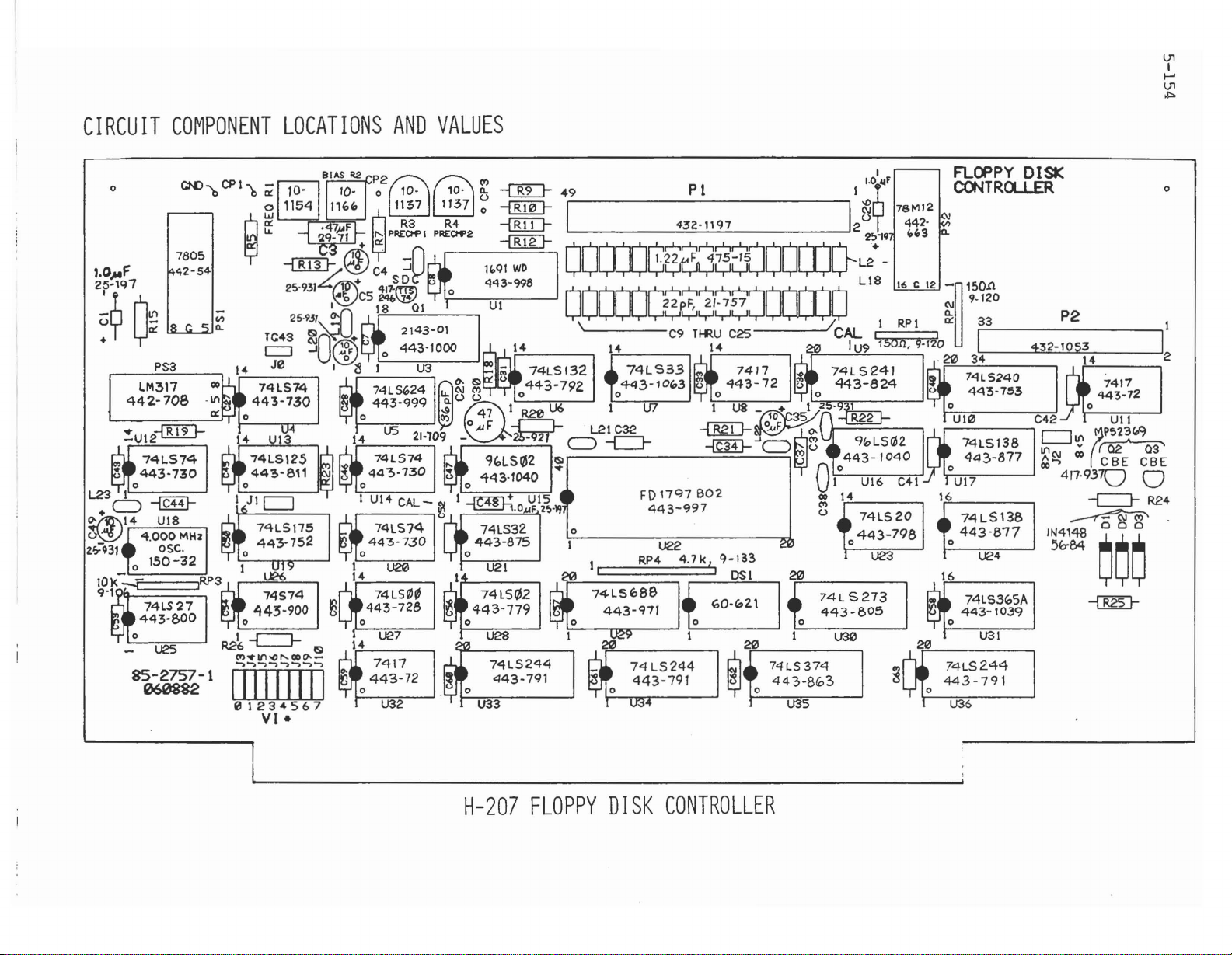

CIRCUIT

DESCRIPTION

DISASSEMBLY

VISUAL

CHECKS

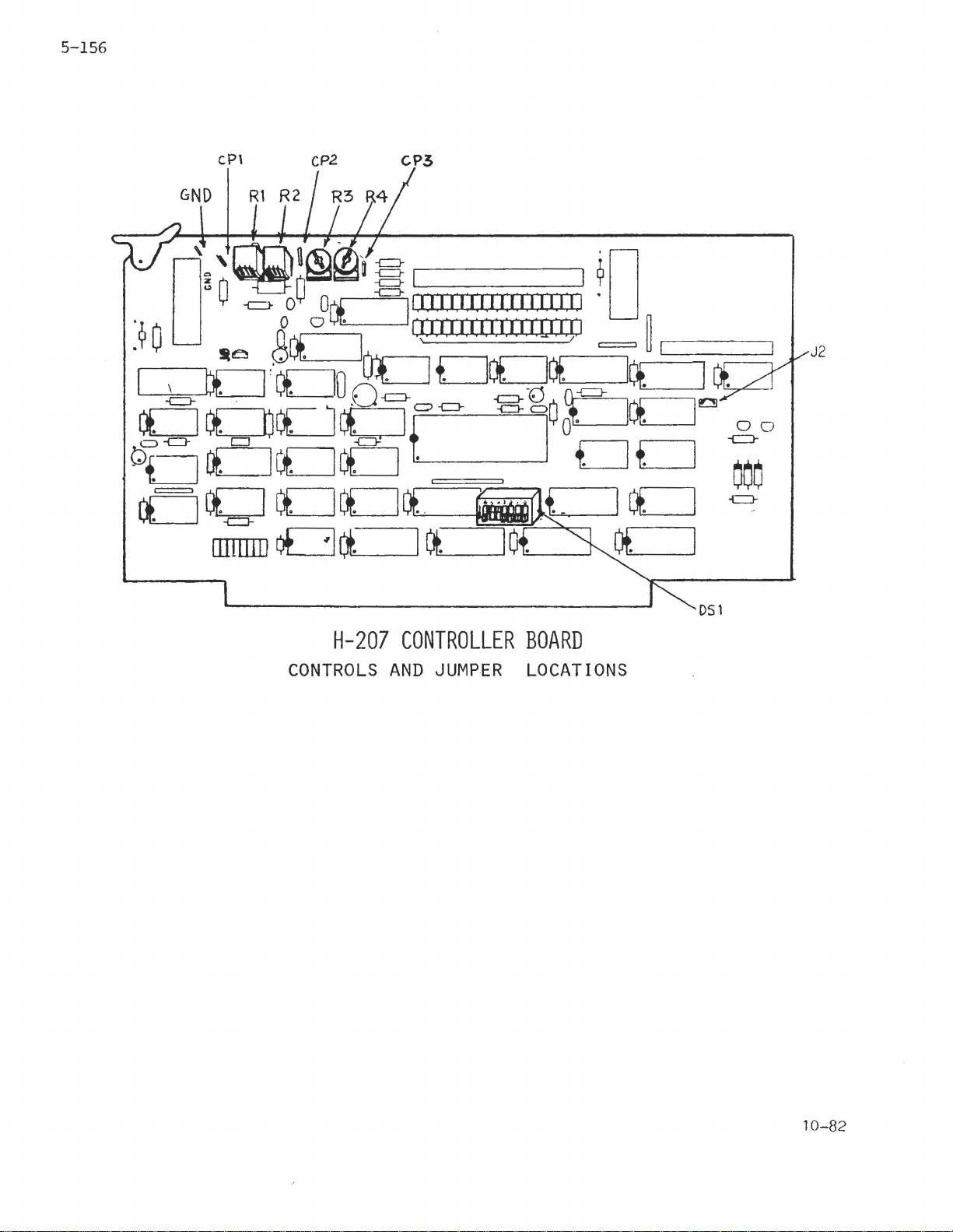

ADJUSTMENTS

TROUBLESHOOTING

PARTS

CIRCUIT

48

PARTII-

TPI

LIST

BOARD

DISK

H-207

X-RAY

DRIVE

DATA

INTRODUCTION

SPECIFICATIONS

VIEW

5-1

5-5

5-25

5-29

5-35

5-39

5-49

5-53

5-57

5-111

5-115

..................

..................

. .. .... ..

· .

.......

..

:

~:):

~;

~:~;

~:~:~;

..........

·.. ......

.... . . . ..

><?::::)

...................

......

· .

..........

·. . . .....

..........

..................

.

OPERATION

(CONTINUED)

5-119

/

Page 22

Page 23

CIRCUIT

DESCRIPTION

5-125

DISASSEMBLY

VISUAL

ADJUSTMENTS

TROUBLESHOOTING

PARTS

CIRCUIT

CALIBRATION

CHECKS

LISTS

BOARD

X-RAY

BOARD

VIEW

SCHEMATIC

5-145

5-151

5-155

5-165

5-177

5-181

5-185

Page 24

Page 25

PART

INTRODUCTION

I

/

Page 26

Page 27

PART

INTRODUCTION

II

/

Page 28

Page 29

The

H-207

as

an

intelligent

drives.

multi-drive

and from

The

H-207

disk

controller

controlled

board

into

This

while

the

takes

the

type

the

work

is

a

floppy

The

system

the

disk

operates

by

the

commands from

necessary

of

system

disk

of

controller

controlling

interface

H-207

drives.

board

master

disk

selects

and

as

a

contains

signals

allows

the

controller

between

properly

slave

CPU.

the

required

the

board

disk

the

handles

processor.

its

own

Thus,

master

master

processor

drives.

board.

the

correct

processor

the

CPU

to

control

CPU

CPU

data

and

to

It

and

drive

This

disk

converts

do

actually

functions

the

transfer

means

which

controller

the

drives.

other

disk

in

the

them

tasks

does

5-113

a

to

is

The

H-207

and

of

drive

present

to

three.

The

H-207

State,

four

is

8"

used

Heath

can

Polled

controller

so

ft-sectored

the

board

Because

card,

the

controller

selectable

Shugart

it

IEEE

can

the

can

Standard.

board

addressing,

compatible

precompensation.

The

in

formation

familiarize

the

H-207.

troubleshoot

level.

versatile.

disk

and

Company

be

I/O,

board

disk

be

jumpered

H-207

be

installed

provided

you

with

Using

the

drives.

the

software

operated

or

Interrupt.

to

formats.

is

a IEEE

Additional

acceptable

software

8"

the

this

disk

information,

controller

It

User

density

in

support

to

operate

in

other

interface,

in

this

operation

can

limits

three

By

696

to

software

of

using

other

section

support

the

up

media.

the

different

This

almost

the

at

speeds

Standard

makes

of

features

computers

controllable

and

of

and

troubleshooting

you

board

to

to

four

selects

number

modes;

allows

all

Wait

State

up

S-100

computers

that

formatting,

adjustable

the

manual

will

the

5-1/4"

the

type

However,

of

drives

Wait

the

disk

available

mode,

to

6

MHz.

compatible

using

make

are:

user

will

be

able

component

the

of

to

10-82

Page 30

Page 31

SPECIFICATIONS

."

'.~

."

.... .

/

Page 32

Page 33

5-117

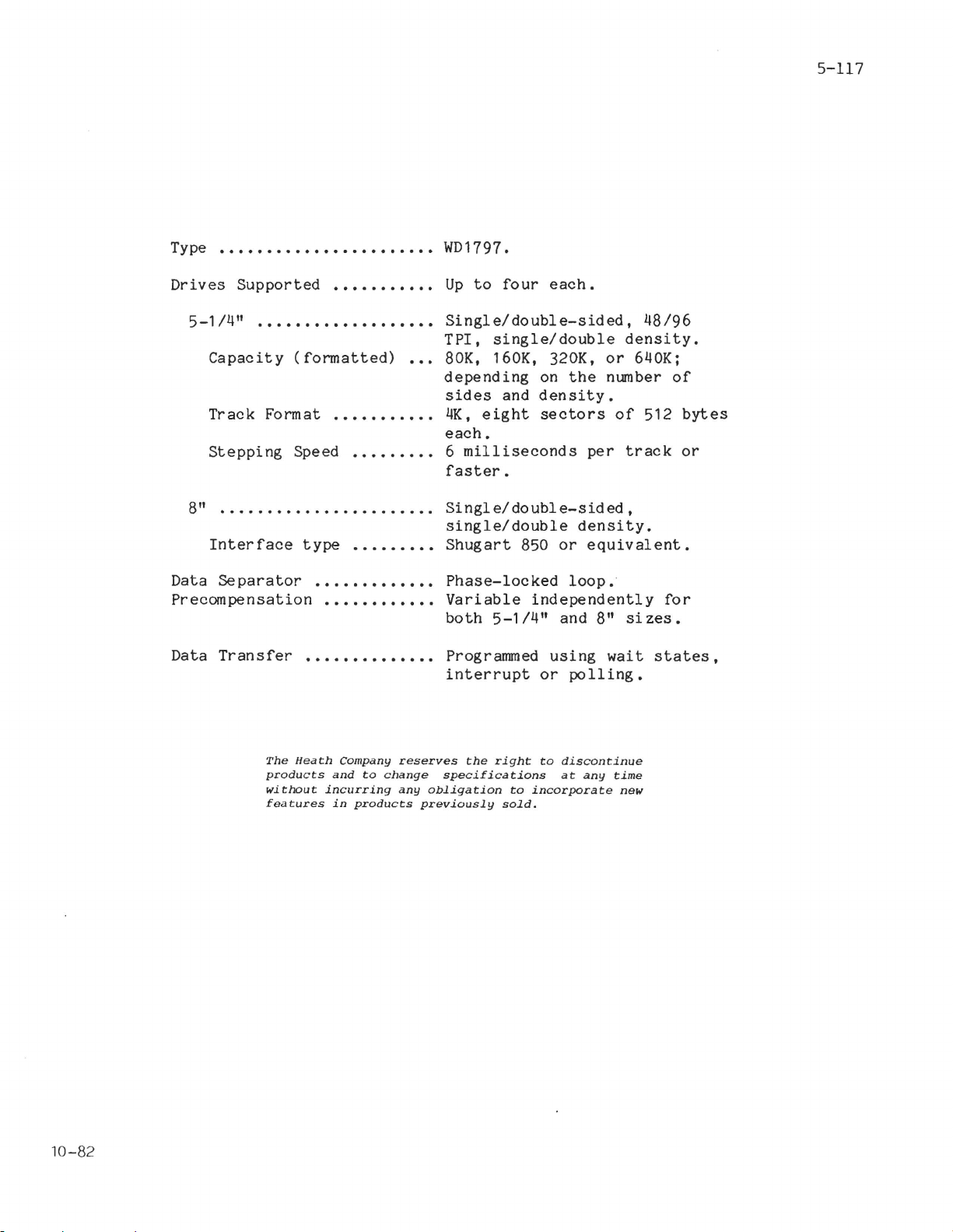

Type

Drives

••.••..•.••••..••••..••

Supported

5-1/4"

.•.••.•.••.••.•••••

Capacity

Track

Format

Stepping

8"

......•••..•..•...•....

Interface

Data

Separator

Precompensation

Data

Transfer

•••...•••.•

(formatted)

.•••.••.•..

Speed

type

•••••••••

......•••

.•....•••••••

.....•.••••.

•.••••.•••••••

WD

1

797

.

Up

to

four

Single/double-sided,

TPI,

•••

80K, 160K, 320K,

single/double

depending

sides

4K,

and

eight

each.

6

milliseconds

faster.

Single/double-sided,

single/double

Shugart

850

Phase-locked

Variable

both

5-1/4"

Programmed

interrupt

each.

density.

or

on

the

number

density.

sectors

per

of

track

density.

or

equivalent.

loop.

independently

and 8"

using

or

polling.

sizes.

wait

48/96

640K;

512

for

states,

of

bytes

or

10-82

The

Heath

products

without

features

Company

and

to

incurring

in

products

reserves

change

any

specifications

obligation

previously

the

right

sold.

to

incorporate

to

discontinue

at

any

time

new

Page 34

Page 35

OPERATION

INTRODUCTION

CLOCK

INTERRUPT

SLIDE

OUTPUT

5"

8"

SPEED

JUMPERS

SWITCH

CONNECTORS

Disk

Disk

(DS1)

Drive Connector

Drive Connector

5-121

5-121

5-122

5-122

5-124

5-124

5-124

./

Page 36

5-120

N

J

Page 37

INTRODUCTION

To

permitthe

computers,

incorporated

permit

environment

t h r e e ma

selection

switch,

for

configuring

the

location

DS1.

ina

a

in

of

H-207

number

into

rea

interrupt

the

which

s 0 f

Refer

of

the

to

of

design

the

the

concern:

jumpers

to

jumpers

operate

jumpers

of

controller

H-207

the

pictorial

and

in

is

and

many

and

the

board.

board

installed.

c10 c k s

the

setting

on

the

slide

different

a

slide

for

pee

the

switch

These

the

There

d j

urn

of

adjacent

switch.

types

devices

computer

per

i ng ,

the

slide

page

5-121

of

are

are

CLOCK

The

wi

J1

(See

to

than

installed

host

th

is

is

illustration

operate

3

SPEED

jumpered

MHz.

Jl

For

the

speed

bealtered.

on

jumper

Refer

al

at

the

to

teration.

bottom

from

computer

determined

by

in

computers

This

in

a

H/Z-100.

FOIL

I

,

O:':D 0

H-207

or

to

slower

This

of

the

the

illustration

CUT

FOILONBOTTOMOFBOARD

clock

by

a

foil

below.)

jumpering

JUMPER

operate

than

is

accomplished

the

circuit

middle

speed

the

that

Jl

or

in

3

hole

that

jumpering

run

on

This

set

for

jumpering

haveaCPU

is

for

CPU

a

computer

MHz,

board

of

below

the

at

the

bottom

normal

H/Z-IOO

clock speeds

the

by

J1

Computer

that

jumpering

cutting

and

installing

to

when

the

H-207

J1.

of

enables

clock

when

the

operation

faster

has

the

rightmost

performing

will

As

received,

the

the

speed

than 3

a

CPU

of

foil

a 1"

operate

board.

H-207

faster

H-207

MHz.

clock

J1

jumper

hole.

is

must

wire

this

10-82

Jl

Jl

setting

clock speed.

for3MHzorslower

CPU

Page 38

5-122

INTERRUPT

The

Vectored

on

the

The

data

holes

center

interrupt

line.

7.

from

No

is

when

interrupt

determined

J3

IRQ.

When

the

jumpers

used

the

JUMPERS

Interrupt

lower

request

through

row

of

lines

from

jumpered,

1797

are

in

a

HlZ-100.

H-207

protocol.

by

the

VI

VECTOR

(No

H/Z-100

INTERRUPT

jumpers are

operation.)

JUMPER

installed

left-hand

line.

J10

holes

VIO

the

these

controller

installed

is

customer's

LOCATIONS

for

jumper

corner

ORQ.

shown

numerically

through

1797

installed

The

in

is

locations

to

in

These

configuration

computer

locations.

of

the

from

VI7.

connected

these

jumper

0 0 0 0 0

0

0 0

the

the

correspond

the

S-100

in

computers

0

1797

illustration

The

route

locations

locations

documentation.

0 0 0

0 0 0

VI.

controller

is

connected

with

interrupt

to

holes

IRQ

interrupt

when

are

that

of

the

0

0

0

are

located

below.

the

request

0

through

and/or

the

only

require

jumpers

0 0

0

0

0

0

board.

The

S-100

ORQ

lines.

H-207

used

....

VI0-VIl

to

is

SLIDE

OSl,

and

sections

llH

OFF

an

the

I l 6 5

(l)

(0)

\

"------_-I

SWITCH

8-section

condition

of

I

<DSl)

OS1are

PORT

ADOllESSING

slide

of

defined

~

switch,

bits

-,

as

I

3 and 4

NOT

USED

3 2 I

o 1 2 3 4 5 6

determines

of

follows:

PRECOMP.

the

TPI

the

status

0.\

Configured foranH/Z-IOO

with48TPI. 5-1/4" Drives

port

port.

7-IRQ

address

The

Computer

~~~B8~~~

'.n

AT

0

DSI

I

Page 39

DSI

5-123

HEATH

Section

0

1

2

3-4-5-6-7

SOFTWARE

The

H-207

addresses.

1797

The

BOH.

registers,

H/Z-100

A map

DEFINED

Definition

This

bit

the

TPI

disk

drive.

o =

118

1

= 96

This

bit

whether

onoroff.

o = precomp

1 = precomp

Not

used.

Port

addressing.

occupies

The

three

computer

of

the

determines

of

the

TPI.

TPI.

determines

precomp

off.

on.

a

block

the

control

series

I/O

port

5-1/11"

3-4-5-6-7

is

of

low-order

place

is

Section

0

1

2

eight

bits

latch,

the

shown

contiguous

in

or

H-207

below.

niti

Status

Status

Not

Port

used.

DEFINED

on

port

port

addressing

HARDWARE

Defi

I/O

this

block

the

status

at

port

address

bit

bit

Leave

port

select

port.

ll.

3.

at

(HSB).

O.

10-82

ADDR.

dip

the

is

(Binary)

switch

bits

swi

shown

The

equi

for

dip

val

the

I/O

SSSSSOOO·

SSSSSOOO

SSSSS001

SSSSS010

SSSSS011

SSSSS100

SSSSS101

• S

switch

ent

of

HIZ-100

SSSSSXXX**=10110XXX=Port

** X = 1797

register,

control

bit

are

tches.

below.

JlEAD

•

•

•

•

•

simply

latch,

WRITE

•

•

•

•

•

For

BO

PORT

DESIGNATION

1797

1797

Command

1797 Track

1797

Sector

1797 Data

Control

-Status

defined

exqrnple,

- B7.

or

status

Status

Latch

Port

Register

Register

Register

Register

from

the

Register

the

port

port.

binary

address

Page 40

5-124

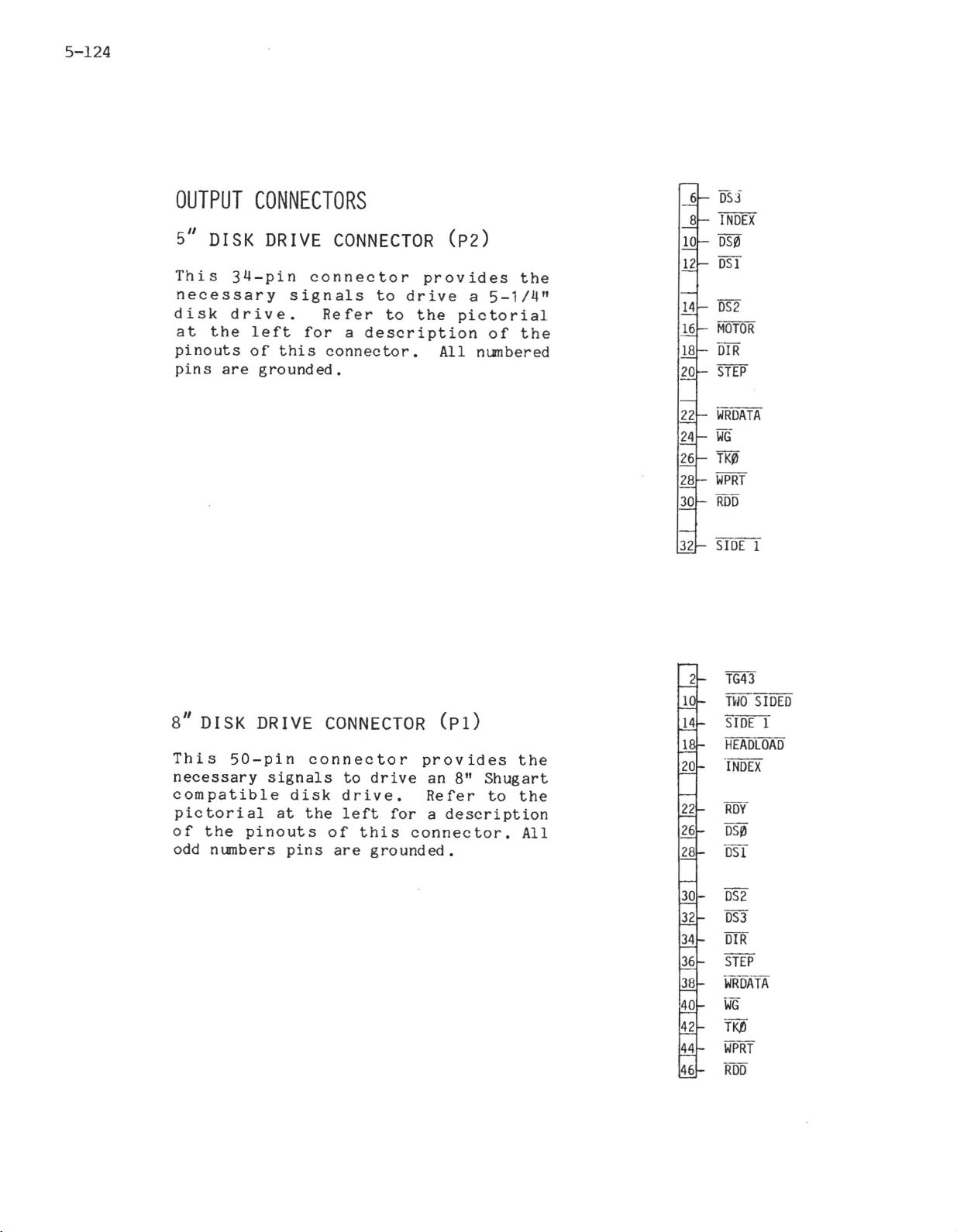

OUTPUT

5"

DISK

This

CONNECTORS

DRIVE

34-pin

necessary

disk

at

pinouts

pins

the

are

drive.

left

of

grounded.

connector

signals

for

this

CONNECTOR

to

drive

Refer

connector.

to

a

description

the

(P2)

provides

a

pictorial

All

numbered

the

5-1/4"

of

the

6

8

10

12

14

16

18

20

22

24

26

28

30

OS)

INDEX

DS0

DST

DS2

MOTOR

D1R

STEP

WRDATA

WG

TK~

WPRT

ROD

8"

DISK

This

DRIVE

50-pin

necessary

compatible

pic

tori

al

of

the

pinouts

odd numbers

connector

signals

disk

at

the

pins

CONNECTOR

provides

to

drive.

left

of

are

drive

this

grounded.

an 8"

Refer

for

a

connector.

(PI)

Shugart

to

description

the

the

All

32

22

26

28

30

32

34

36

38

40

42

44

46

SIDE

1

TG43

HiO

SIDED

SIDE

1

HEADlOAD

-INDEX

ROY

DS~

DS[

DS2

OS3

DIR

STEP

WRDATA

WG

T~

WPRT

ROD

Page 41

CIRCUIT

..

DESCRIPTION

1<:

BLOCK

DETAILED

DIAGRAM

S-100

Data

Data

CIRCUIT

Bus

In

Out

DESCRIPTION

DESCRIPTION

Interface

Address Lines

Control Lines

Vector

Ready

Interrupt

Line

Lines

RESETCIRCUITS

Power-Up/Reset

Power-Up

Write Protection

CPU/Controller Logic

Read

Status Latch

Read

Status Register of

Write Control Latch

(U31)

(U30)

Write Control Register in the

Data

ROY

Read/Write Operations 5-134

Delay

Interrupts

CONTROLLER/DISK-DRIVE

Data

Shaping 5-136

Data

Separation

Head

1797

8"

5"

CALIBRATION

H-207

Load

Timing

Drive

Drive

FLOPPY

Timi

ng

Interface

Interface

CIRCUIT

DISK

LOGIC

Precompensation

and

BOARD

CONTROLLER

1797

(U22)

1797

BOARD

(U22)

DEFINITIONS

5-127

5-128

5-128

5-128

5-128

5-128

5-128

5-129

5-129

5-129

5-129

5-130

5-130

5-130

5-131

5-132

5-133

5-135

5-135

5-136

5-136

5-138

5-139

5-139

5-139

5-140

5-141

"

,",

.

'.

..

::

.

" .

/

Page 42

~

l.I

~

~

~

~

~

~

c;

~

~

~

c;

~

~

~

V'

~

/

~

~

'/

~

~

~

~

~

'/

~

~

~

/

~

~

~

~

'/

V

~

'/

~

'/

~

~

~

~

~

'/

~

'/

~

~

~

~

'/

~

u.J

L>

<C

U-

0:::::

u.J

t-

z:

-

U)

::::>

.~

C>

C>

rl

U)

I

./

"

./

...........

~

~

~

~

~

~

/:

~

~

~

~

'/

"

~

~

~

~

,~

/~

~

~

~

~I

/"

STATUS

PORT

~

CONTROL

LATCH

IT»

./

"

./

"-

./

"'-

/

\

~

~

.......

.".

~

~

~

V

~

~

1797

FLOPPY

DISK

CONTROLLER

~

~

~

~

~

~

~

/

~

/

V )

~-

"

./

...........

~

~

~

~

u.J

~

L>

'/

<C

U-

~

0:::::

~

.......

u.J

,

""

......

......

.........

~~

/

\

~

.~

SEPARATION

~

~

~

,

PRECOMPEN-

/

~

SATION

'/

~

~

V1

/

\

DATA

AND

WRITE

./

"

'v

"''/

......

......

......

.......

~

~

~

~

~

~

~

~

~

~

~

'/

~

~

~

~

~

~

/'

~

~

/

~

/

~

~

~

t-

:z:

-

:::

00

u.J

<.J

<C

u..

0:::::

w

t-

z:

-

:::

Ll't

H-207

BLOCK

DIAGRAM

10-82

Page 43

5-127

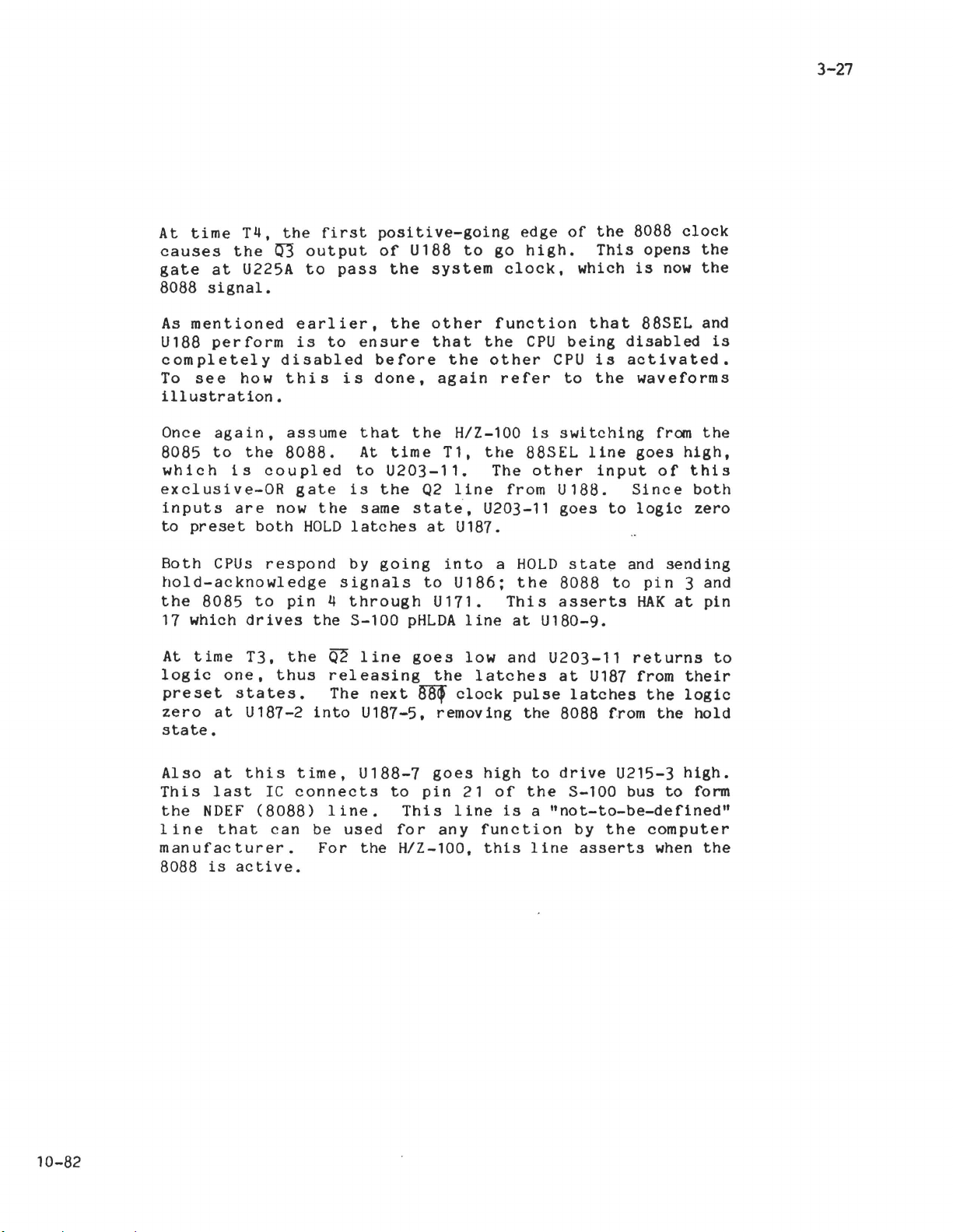

BLOCK

Refer

The

major

control

separation

drive

The

octal

miscellaneous

interface

The

the

includes

disk,

The

as

the

The 1797

on

the

read

DIAGRAM

to

the

H-207

sections:

latch,

interfaces.

bus

interface

tri-state

status

status

and

control

DRIVE

selection

the

diskette.

formation

data

DESCRIPTION

H-207

Floppy

&

the

H-207

port

of

track

if

precompensation

latch

SELECT,

and mode

controller

is

controlled

the

write

enabling

the

density,

of

block

Disk

the

latch,

is

5"

written

diagram

controller

bus

interface,

1797

precompensation

is

to

a

disk

accepts

FASTEP,

That

floppy

made

an

the

S-100

read-only

drives

number

of

the

controls

is,

data,

by

the

up

address

circuitry.

is

commands

and

drives.

the

1797.

as

you

board

disk

of

two

bus

in

device

and

the

of

recording

being

to

others

the

placement

movement

and

read

the

controller,

circuits,

octal

comparator,

the

used.

the

that

the

the

consists

status

bus

These

H/Z-100.

that

controller.

disk

have

of

of

the

separation

following.

of

port,

the

and

the

buffers,

and

components

tells

sides

the

drives

to

do

information

drive

seven

data

some

This

to

such

with

head,

of

the

two

an

CPU

the

the

10-82

The

data

control

di

sket

clock

data

The

circuitry.

during

8"

interface.

separation

how

te

.

signal

and

It

the

5.25"

Up

and

the

data

does

during

double-density

drive

to

thisby

read

interfaces

four

write

is

read

se

operations

drives

precompensation

to

or

parati

write

can

ng

operations.

include

be

and

connected

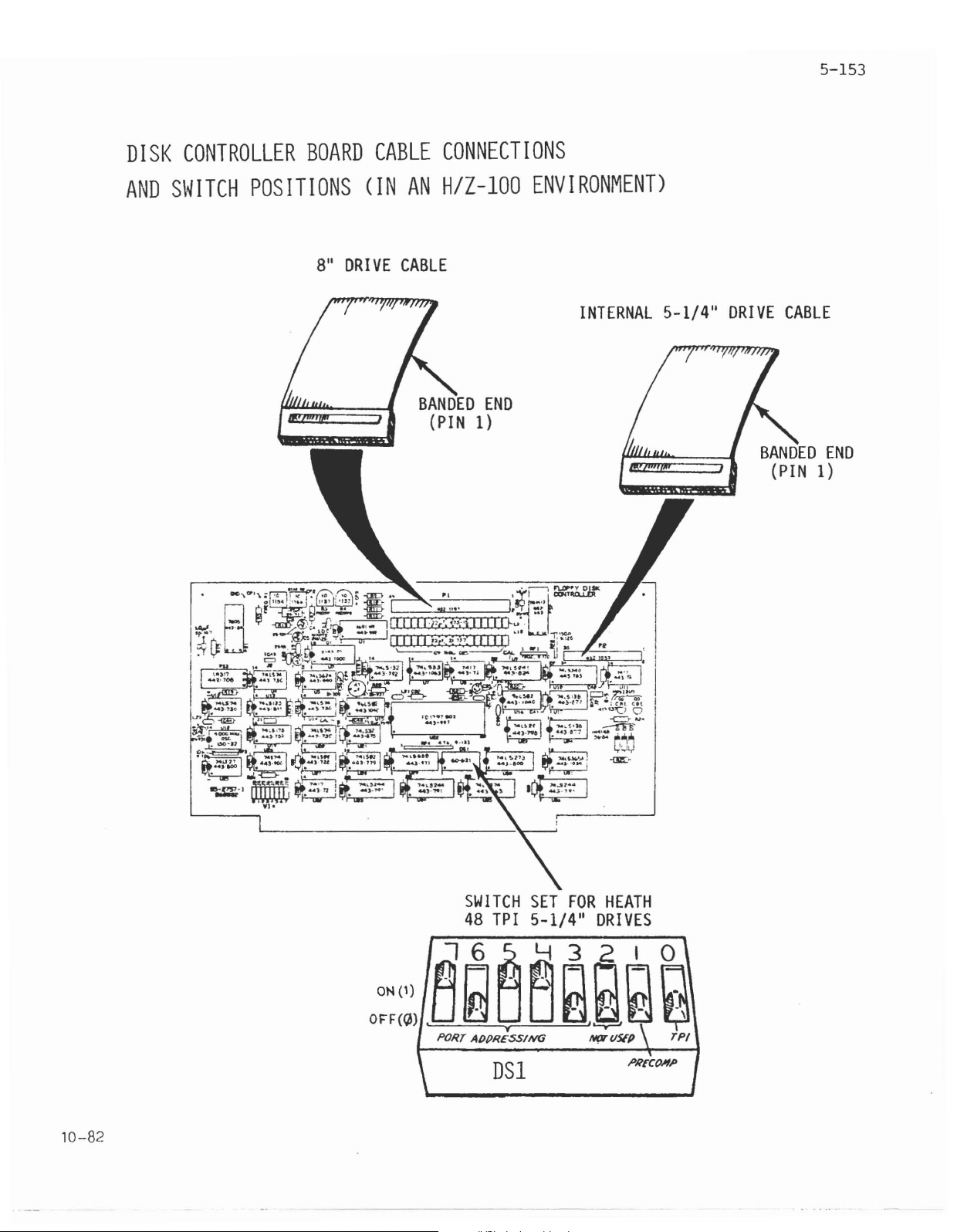

circuitry

written

the

data

precompensating

buffers

from

from

and

to

the

the

filter

each

Page 44

5-128

DETAILED

S-100

The

S-100

696-standard

in

the

lines.

DATA

Data

through

bus

the

is

bus

DATA

Data

through

interface

U35.

not

The

da

latched

through

latches

into

interface.

status

buffered

by

out

present

tri-state

tab

CIRCUIT

BUS

IN

means

OUT

The

INTERFACE

Bus

appendices

the

signal

1

from

pins

plug.

latch

us

sot

in

U35

pin

an

asserted

atch

from

of

long

DESCRIPTION

Interface

S-100

35, 36,

1 when

Bus. See

of

this

bus

(out

lines

These

the

U36, a 741$244

the

is

latch

hat

on

pins

or

from

board's.

bus

38, 39,

This

used

enough

holds

the

every

the

sOUT

91-95

from

(into

data

because

for

1797

write

ALE

(Status

is

the

manual

the

and

are

the

internal

buffer.

the

40,

is

the

the

can

(Address

compatible

S-100

for

controller

signal

used

1797

data

cycle.

in

controller.

controller

88,

latched

data

1797

on

read

Out)

data

89,

signal

with

specification

definitions

board)

lines

read

and

by

on

to

the

it.

The

Latch

receive

41-43

operations

bus

to

board)

90

tri-state

the

S-100

board's

Va

1 i d dat a

latch

Enable)

via

any

travels

The

the

travels

on

the

properly.

internal

is

enabled

U20.

IEEE

sheets

of

the

on

the

from

data

S-100

bus

latch

bus

signal

is

is

ADDRESS

The

address

29,

30,

They

are

CONTROL

The

control

pins

face.

24,

These

LINES

lines

31,

79,

buffered

LINES

lines

25,

45. 46,

lines

from

and

by

from

are

the

80

the

the

and

buffered

bus

through

74LS244

S-100

75

enter

83

chip,

bus

through

by U33.

the

of

U34.

enter

78

board

the

the

of

bus

board

the

through

interface.

through

bus

pins

inter-

Page 45

5-129

VECTOR

The

at

pins

driven

READY

The

interface.

this

operations

operation.

RESET

INTERRUPT

vector

by U32.

4

through

interrupt

LINE

ready

line

line,

It

to

to

CIRCUITS

is

put

POWER-UP/RESET

On

power

to

the

control

U26

the

board.

flip-flops

up,

H-207

latch,

the

board

drivert

give

CPU

the

in

LINES

lines

11

of

RDY,

.

a known

enters

the

the

sends

This

write

from

the

by U32. The

CPU

controller

RESET*

pI

precompensation

state

bus

through

in

aces

the

interface.

a

wait

the

before

bus

pin

controller

state

time

through

1797

enter

72

during

to

the

controller,

control,

the

CPU

the

They

of

board

finish

S-100

board

may

the

bus

uses

some

the

bus

the

and

the

accesses

be

10-82

In

the

03H,

register

After

restore

o

and

is

found.

The

to

clear

The

the

sheets)

Finally,

an

RDY

·of

the

U27-11.

1797,

the

sector

(Not

the

reset

command. The

sends

See

reset

reset

phase

line

all

state

four

.

the

(ready)

qualification

the

Ready

an

the

of

U26

reset

register

bit)

line

interrupt

1797 IC

connects

the

outputs.

of

the

(¢4)

Q-outputs

signal

line

to

goes

drive

to

phase

input

to

needed

sets

to

01H,

logic

high,

read/write

to

the

data

sheets

pin1of

lock

equal

are

made

the

CPU

for

the

and

zero.

the

computer

for

the

loop

to

0

(see

equal

and

read/write

command

bit

7

1797

head

once

more

control

control,

the

to

1;

pin

5

enabling

register

of

the

executes

seeks

the

details.

latch,

U1,

1691

pin

provides

at

status

the

track

track

U30,

makes

IC

data

9

sends

part

through

Page 46

5-130

POWER-UP

On

power

until

could

any

disks

To

protect

1797

These

remain

4

are

whenever

is

volts.

biased

WRITE

up,

the

power

generate

that

the

coupled

transistors

cut

off

When

near

WG

is

the

a

may

disk,

until

the

asserted.

CPU/CONTROLLER

Reading

of

information:

signals,

read

and

and

writing

and

control

control

signals

PROTECTION

TTL

circuits

supply

write

be

to

their

voltage

command

installed.

the

the

5"

are

biased

the

power

supply

operating

WG

and

reaches

LOGIC

in

the

H-207

data

which

signals.

can

only

will

(write

8"

supply

can

rises

in

drives

by

board

be

Status

be

be

at

the

gate)

R25,

voltage

this

region

read

written.

an

undefined

above 4

drives

output

through

D3-D1,

value,

and

involves

or

written,

signals

is

will

volts.

and

Q3

and

at

Q2

three

can

state

This

damage

from

and

R24

or

above

and

conduct

types

status

only

the

Q2.

to

Q3

be

READ

Assume a

sources

port

To