Z-Communications PCA0198A Technical data

q

查询PCA0198A供应商

9939 Via Pasar • San Diego, CA 92126

TEL (858) 621-2700 FAX (858) 621-2722

PCA0198A

PHASE LOCKED LOOP

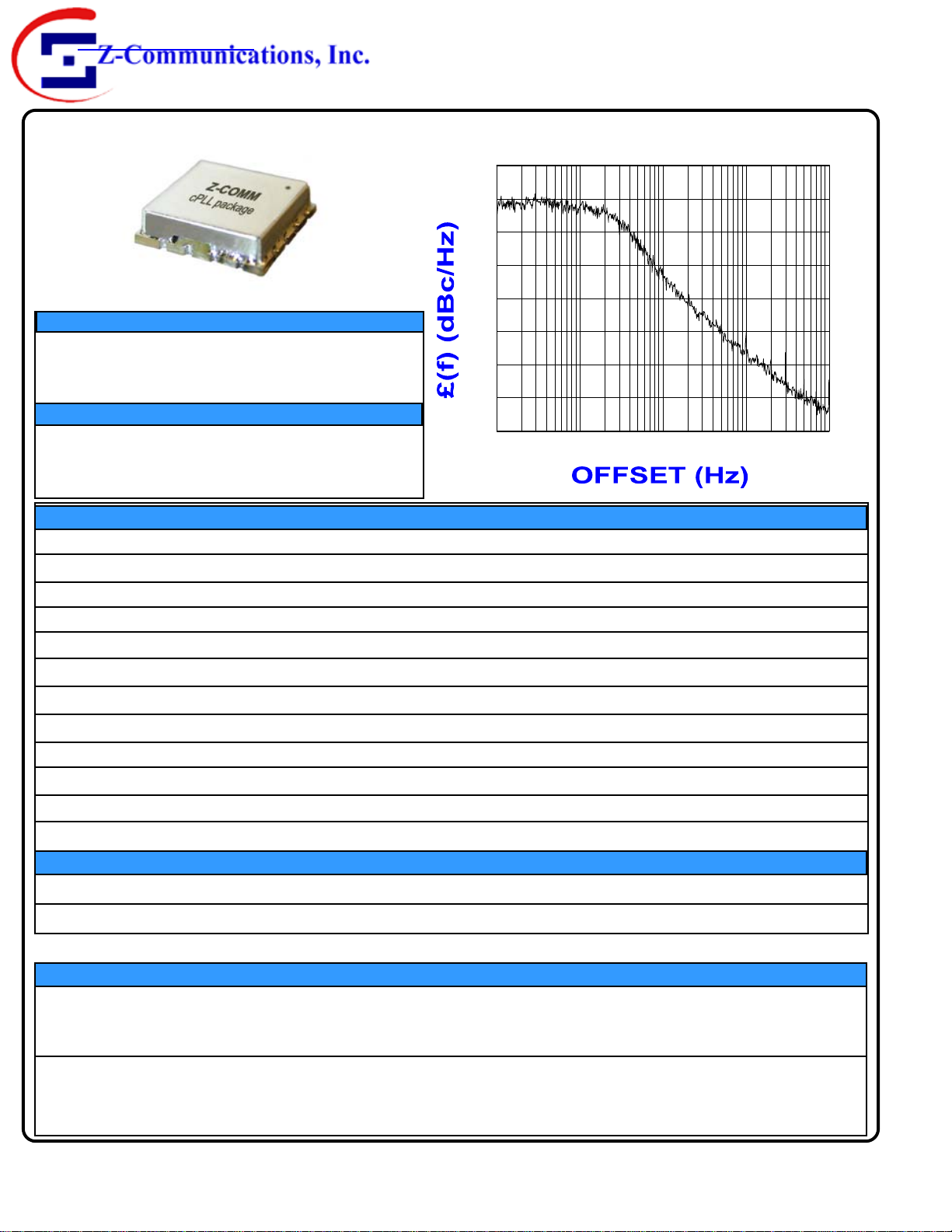

PHASE NOISE (1 Hz BW, typical)

-70

-80

-90

-100

-110

Rev

A1

FEATURES

• Frequency Range:

•

Step Size:

•

- Style Package

cPLL

198

100

-

199

KHz

MHz

APPLICATIONS

•

Telecommunications

Satellite

•

Telemetry

•

PERFORMANCE SPECIFICATIONS

Frequency Range

Phase Noise @ 10 kHz offset (1 Hz BW, typ.)

Harmonic Suppression (2nd, typ.)

Sideband Spurs (typ.)

Power Output

Load Impedance

Step Size

Charge Pump Output Current

Switching Speed (typ., adjacent channel)

Startup Lock Time (typ.)

Operating Temperature Range

Package Style

-120

-130

-140

-150

100 1000 10000 100000 1000000

VALUE UNITS

198

-

-104

-10

-70

199

MHz

dBc/Hz

dBc

dBc

0±2 dBm

50

100

2500

1.5

1.0

-40 to 85

Ω

KHz

µΑ

mSec

mSec

°C

cPLL

POWER SUPPLY REQUIREMENTS

Supply Voltage (Vcc, nom.)

Supply Current (Icc, typ.)

All specifications are typical unless otherwise noted and subject to change without notice.

APPLICATION NOTES

• AN-107 : How to Solder Z-COMM VCOs / PLLs

• AN-200 : Mounting and Grounding of Z-COMM PLLs

• AN-201 : PLL Fundamentals AN-202 : PLL Functional Description

NOTES:

Reference Oscillator Signal: 5 MHz<f

Fre

uency Synthesizer: Analog Devices - ADF4001

© Z-Communications, Inc.

<100 MHz

osc

Page 1

5

45

Vdc

mA

All rights reserved

LOW COST - HIGH PERFORMANCE

PHASE LOCKED LOOP

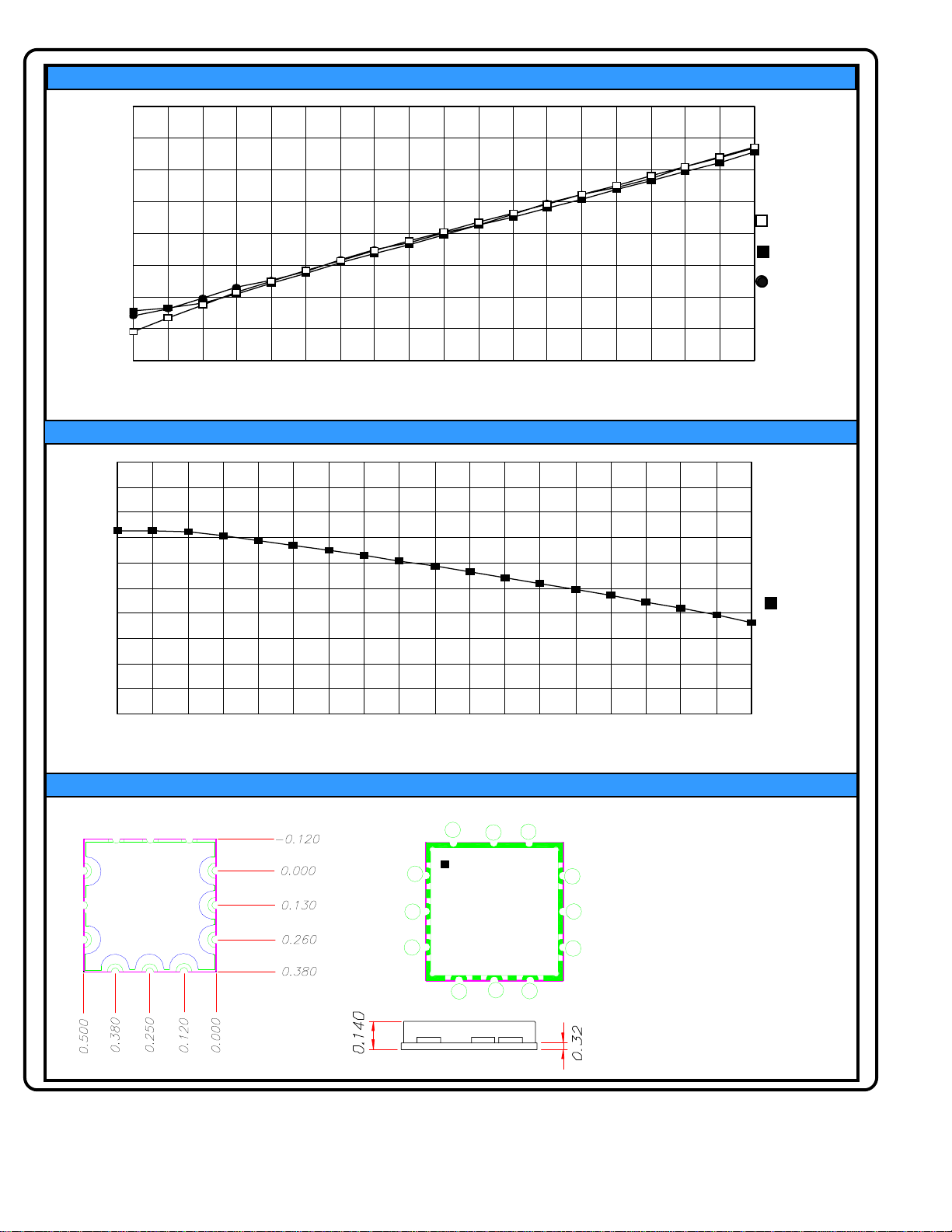

230

220

210

200

190

180

170

160

FREQUENCY (MHz)

150

00.511.522.533.544.5

5

4

3

2

1

0

-1

-2

-3

-4

OUTPUT POWER (dBm)

-5

166 168 174 181 187 193 198 204 209 216

VCO TUNING CURVE, typ.

TUNING VOLTAGE (Vdc)

VCO POWER CURVE, typ.

FREQUENCY (MHz)

PCA0198A

PAGE 2

°c

85

°c

25

°c

-40

°c

25

Bottom

View

© Z-Communications, Inc.

PHYSICAL DIMENSIONS

Top View

12

11

10

1

2

Z-COMM

PCAXXXXX

3

4

SIDE VIEW

Page 2

W/O #

5

6

1. The insi de radius of all 14 half holes at the perim eter of the board

are plated to provide a surface f or the attachment of th e P LL Module

to the motherboard. 5 pads are for grounding, 8 pads are for signal

interface.

9

8

7

2. The sur f ace of the shield is tin-plated and may be soldered to.

The shield's base metal is brass.

3.The ground plane on the bottom side is ground and attaches t o a

ground track on the top side of the board as well as to the shield.

4. Unless otherwise n oted all dimensions are in inches.

5.Unless otherwise noted all tolerances are as f ollows:

.xxx = ± .010

P1 RF OUTPUT

P2 REFERENCE OSCILLATOR INPUT

P3 CLOCK

P4 DATA

P5 LOAD ENABLE

P6 LOCK DETECT

P7 VCC

P8 GROUND

P9 NO CONNECTION

P10-12 GROUND

Printed in the U.S.A.