Page 1

PDP TELEVISION

PH-42R6

Canada

Page 2

CONTENTS

Safety precautions………………………………………………………………………..…

Alignment instructions …………………………….…….……………………………….…

Working principle analysis of the unit……………………………….………….………….

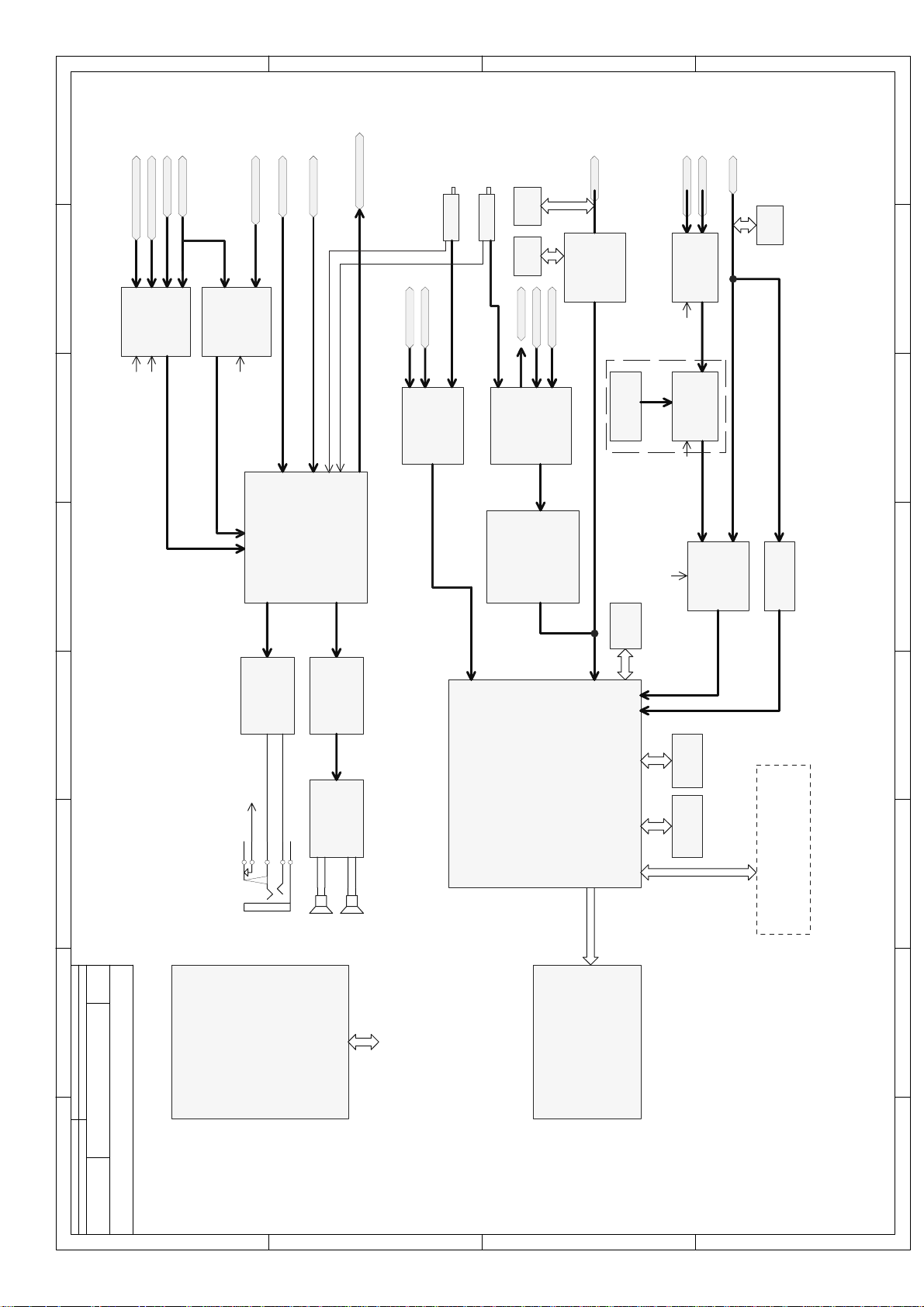

Block diagram…………………………………..………………………………….…………

IC block diagram………………………………………………………………………..……

Wiring diagram ……………………………………………………………..……………...

Troubleshooting………………………………………………………………………..……

Schematic diagram …………………………………………………………………………

APPENDIX-A: Main assembly list

APPENDIX-B: Exploded view

1

3

6

7

8

17

18

24

Page 3

Note: This maintenance manual is intended only for the reference of the maintenance people.

Please pay attention to the following points before carrying out the maintenance work.

Safety precautions

Please read the “Points for attention for the Maintenance & Repair of PDP” and “Criterion for

Identifying the Defects on Screen” as below, before inspecting and adjusting the TV set.

1. “Points for attention for the Maintenance & Repair of PDP”

To avoid possible danger, damage or jeopardy to health and to prevent PDP screen from new

damage, the maintenance people must read the following carefully. If they ignore the following

warnings, there will be deathful risks:

1.1 Screens vary from one model to another and therefore not interchangeable. Be sure to use the

same type of screen in the replacement.

1.2 The operation voltage is approximately 350V for PDP module (including screen, driving circuit,

logic circuit and power module). If you want to conduct maintenance work on PDP module when the

set is in normal operation or just after the power is off, you must take proper measures to avoid

electric shock and never have direct contact or touch with the circuitry of the working module or

metal parts. That’s because within a short time relatively high voltage still remains on the capacitor

of the driving part even after the power is off. Make sure to begin relevant maintenance operation at

least one minute after the power is off.

1.3 Don’t apply on the module any power supply that is higher than the specification. If the power

supply used deviates from the value given in the specification, there might be a possibility of leading

to fire or damage to the module.

1.4 Never have operation or mounting work under unsuitable environment such as areas in the

vicinity of water – bathroom, laundry, water chute of kitchen – sources of fire, heat-radiation parts or

direct exposure to sunlight. Otherwise there will be kickbacks.

1.5 In case foreign substances such as water, liquid, metal slices or others fall into the module

carelessly power must be cut off immediately. Keep the module as it is and do not move anything on

the module. Otherwise it might be possible to contact the high voltage or cause shock short circuit

so that it may lead to fire or electric shock.

1.6 If there is smoke, abnormal smell or sound from the module, please cut the power off

immediately. Likewise in case the screen doesn’t work when the power is on or during the operation,

please also cut off the power at once. No more operation in this case.

1.7 Do not remove or plug its connection wire when the module is in operation or right after the

power is off. That’s because there remains a relatively high voltage on the capacitor of the driving

circuit. If there is a need to remove or plug in the connection wire, please wait at least one minute

after the power is off.

1.8 Considering the module has a glass faceplate, please avoid extrusion by external force lest it

should cause glass breakage that may get people injured. Two people are needed in cooperation to

move this module lest contingency takes place.

1.9 The complete TV set is designed on the basis of full consideration of thermal dissipation by

convection, with the round hole on the top for heat emission. To avoid overheat, please do not have

any covering on the hole during normal operation and never put it in the place where the space is

narrow and in bad ventilation.

1.10 There is quite a number of circuits in PDP that are integrated ones. Please be on guard against

1

Page 4

static electricity. During maintenance operation be sure to cover yourself with anti-static bag and

before operation make sure to have it sufficiently grounded.

1.11 There are a big number of connection wires distributed around the screen. Please take care

not to touch or scuff them during maintenance or removing the screen, because once they are

damaged the screen will fail to work and it’s not possible to repair it.

1.12 Connector for the circuit board of the screen part is relatively fine and delicate. Please take

care in the replacement operation lest it should get damaged.

1.13 Special care must be taken during transportation and handling because strenuous vibration

could lead to screen glass breakage or damage on the driving circuitry. Be sure to use a strong

outer case to pack it up before transportation or handling.

1.14 Please put it for storage in an environment in which the conditions are under control so as to

prevent the temperature and humidity from exceeding the scope stipulated in the specification. For

prolonged storage please cover it with anti-moisture bag and have them piled and stored in one

place. The environmental conditions are tabulated as below:

Temperature Scope for operation 0~50centigrade

Scope for storage -15~60centigrade

Humidity Scope for operation 20%~80%

Scope for storage 20%~80%

1.15 If a fixed picture is displayed for a long time, difference in its brightness and color may occur

compared with movable pictures. But it doesn’t show any problem and the reason is that there is

reduced density of fluorescent powder in the former. On the other hand, even if changes take place

in the picture, it can keep its brightness for a period of time (several minutes). It’s a feature inherent

with plasma and it’s not abnormal. However please try as much as possible to avoid showing a still

picture of high brightness for a long time during operation.

1.16 As a digitalized display devise, this module is provided with error diffusion technology and the

gray scale and false enhancement of contour can be displayed by reusing of sub-field. As compared

with cathode ray tube, it can be found in the moving picture that at the brim of the face of a person

there are some wrong colors.

1.17 During the display of graph (indicating the gradual change in brightness horizontally or

vertically) resulting from gray scale test it can be found that the brightness for the two adjacent

levels is uneven. This is caused by the reuse of sub-field, the display of load rectification and the

electrolysis.

1.18 The screen front plate is of glass. Please make sure that the screen has been put in place

during erection. If it is not in place before the erection begins it may lead to screen crack or

breakage.

1.19 Make sure the screw used in the mounting of the screen is of the original specs lest it should

cause damage to the screen due to mismatch. Special care should be taken not to use too long or

too big screw.

1.20 Care must be taken to guard against dust during assembling or dismantling, especially to avoid

dirt from falling in between the screen and the glass lest it should harm the receiving and viewing

effect.

1.21 There is piece of insulator stuck on the rear chassis corresponding to the power supply board.

It is used to isolate the cool part from the hot part. Please take care to keep it intact lest it should

2

Page 5

become a potential safety trouble.

1.22 In addition to plasma screen, the glass is a part of high value. It has such functions as

anti-radiation, adjustment of color temperature etc. Please handle it carefully.

Alignment instructions

1. Test equipment

VG-848 (Signal generator)

CA100 (White balancer)

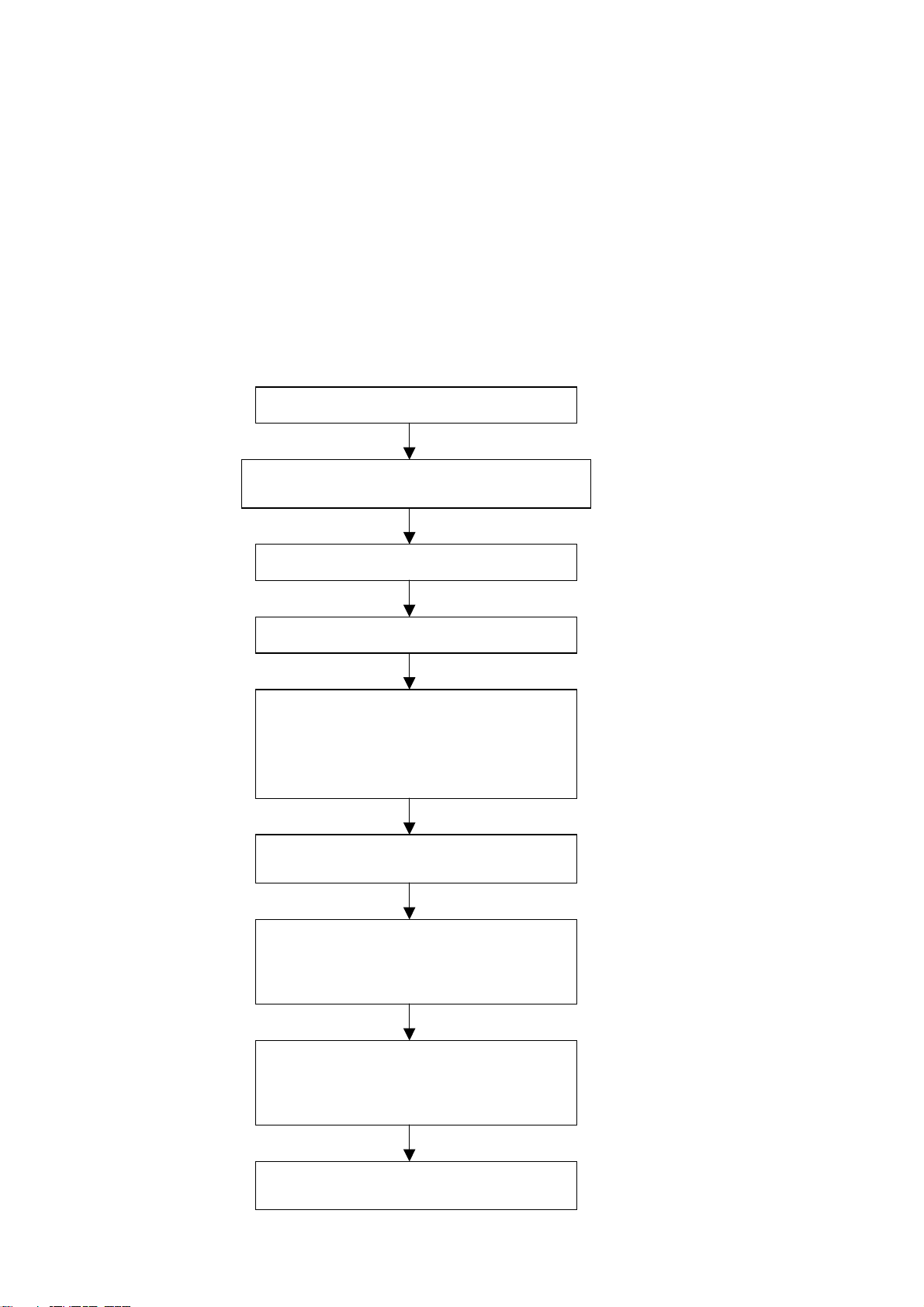

2. The alignment flow chart (see below figure)

Production of CPU board and analog board on the line.

Check DDC, HDCP KEY and FLASH

Check CPU board and analog board

Combined test for general assembly

Connect to central signal source; check if various

TV functions (station skipping, modulate quantity

control etc), check if the output of earphone and

speaker are normal.

Input AV/S signal and HDTV signal; check various

functions under AV/S terminal

Input VGA signal and check if display is normal in

the state of PC and various functions (analog

quantity control, line/field center etc.)

Input HDMI signal and check if display is normal in

the state of HDMI and various functions (sound

and analog quantity control).

Preset ex-factory

3

Page 6

Check accessories and then packing

Fig-1 adjustment flow-chart

3. The unit adjustment

Connect all the boards according the wiring diagram, turn on the power and check if the display is

normal.

3.1 The method of entering factory menu

Enter factory menu method: press the INPUT→ 2→ 5→8→0 buttons one by one on the remote

control to factory menu. Press the MENU button to select item. Press the DISPLAY button to exit the

factory menu.

3.2 EEPROM initialization and back light adjustment

Enter the firs page of factory menu, adjust item OPTION-1 to 9, OPTION-2 to 5, select the

EEPROM initial after, press the VOL+ button, then display the DOING, still the DOING disappear

and turn off the unit.

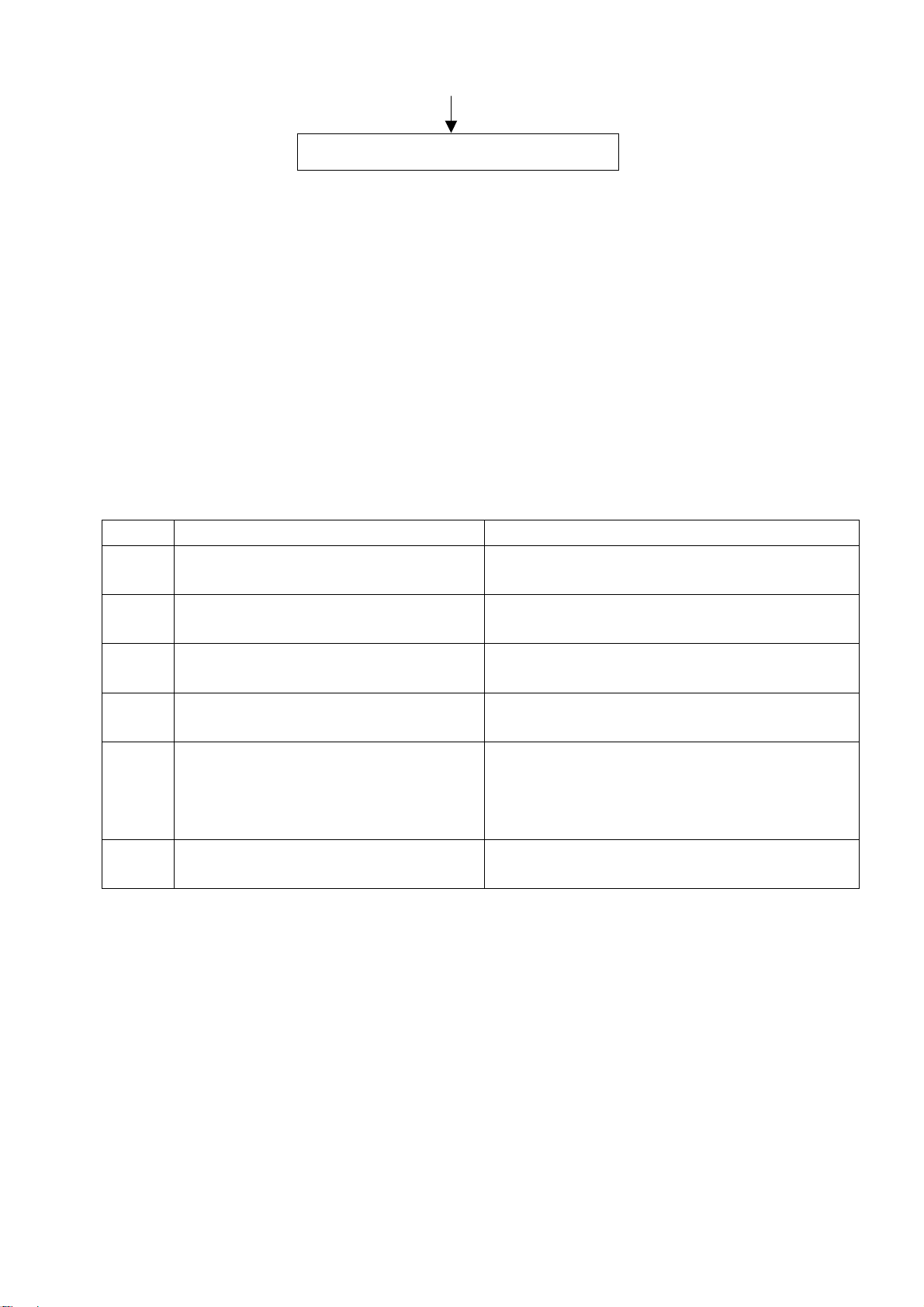

Note: option-1 and option-2 function as follows:

Option-1 Option-2

Bit6 0: normal TV mode

1: hotel TV mode

Bit5 0: TV/AV multi-system

1: TV/AV NTSC system

Bit4 0:fast search station

1:slow search station

Bit3 0: no memory function after power off for 10s

1: memory function after power off for 10s

Bit2,1 00: STANDBY

01: turn on

10: memory function of turn on

Bit0 0: without LOGO

1: With LOGO

3.3 HDMI channel adjustment

Input the VG-848 TIME854(800X600/60Hz) and PATTERN920 8-LEVEL gray signal, enter the

factory menu2(white balance adjustment menu), adjust the second step and the seventh step.

Adjust R-OFFSET, G-OFFSET and B-OFFSET item, still the second step color coordinate to (285,

293). Adjust R-GAIN, G-GAIN and B-GAIN item, still the seventh step color coordinate to (285, 293).

Repeat adjustment R-OFFSET, G-OFFSET and B-OFFSET item and R-GAIN, G-GAIN and B-GAIN

item, still two step gray to (285, 293).

Note: R-OFFSET, G-OFFSET and B-OFFSET values must be an item value to 128 at least; R-GAIN,

G-GAIN and B-GAIN values must be an item value to 255 at least.

3.4 VGA channel adjustment

3.4.1 mode pre-set

Input the VGA signal of VG-848 (PATTERN 980:1 dot ON/OFF), select the TIME877 (720x400/70Hz)

0:close HDMI hot-plug function

1:open HDMI hot-plug function

0:only have the first two pages of factory menu

1:all pages of factory menu

0:have GAMMA correction

1:no GAMMA correction

0:no signal noise wave of TV

1:no signal blue screen of TV

00:complexion correction (OFF)

01: complexion correction (WEAK)

10: complexion correction (MIDDLE)

11: complexion correction (STRONG)

0: Video and Graphic channel white balance no share

1: Video and Graphic channel white balance share

4

Page 7

signal, press auto-adjust button to all screen or adjust PC settings menu to auto correction.

Separate auto adjust for TIME885 (640x480/60Hz) and TIME854 (800x600/60Hz).

3.4.2 VGA channel auto color adjustment

Input the VG-848 TIME854(800x600/60Hz) and PATTERN920(GRAY 8 STEP(H)), enter the factory

menu1, select the AUTO COLOR after, press the VOL+ button to select AUTO COLOR.

3.5 HDTV channel adjustment

Input the VG-848 TIME972(1080i/60Hz) and PATTERN976(64 GRAY & Color), enter the factory

menu1, select the AUTO COLOR after, press the VOL+ button to select AUTO COLOR.

4. Performance check

4.1 TV function

Input center source signal to RF-TV terminal, check if the channel is leak for auto searching.

4.2 AV/S and HDTV terminal

Input AV/S and HDTV signal, check if the signal is normal.

4.3 VGA terminal

Input 640 x 480 @60Hz VGA format signal, check if the signal is normal.

4.4 HDMI terminal

Separate input HDMI and DVI signal; check the picture and sound is normal, check if the HDCP

function is normal.

4.5 check the sound channel

Check the speaker and headphone of each channel.

4.6 ex-factory setting

Enter the first page of factory menu, select the factory out after, press the VOL+ button to display

“doing”, then “doing” disappear while it can auto ex-factory setting.

5

Page 8

Working principle analysis of the unit

The RF1 via integrative tuner TUNER1 after, the FBAS VIDEO1 and SIF1 is generated. Video

signal of VIDEO1, AV1/S, AV2 sent to N7(TVP5160) as the main picture signal. The signal via N7

switch selection after, one way is AV OUT; another way sent 8-bit ITU-R656 format signal to N10

(FLI2310) non-interlaced processing, then sent 24bit YUV signal to main processing control chip

N15 (GM1501/1601).

The RF2 via integrative tuner TUNER2 after, the FBAS VIDEO2 and SIF2 is generated. Video

signal of VIDEO2,AV1/S,AV2 sent N8 (TVP5147) to decode as sub-picture signal. The signal via N8

decode after, it sent 8-bit ITU-R656 format signal to main processing control chip N15

(GM1501/1601).

Two ways YPBPR signal via HDTV switch N39(PI5V330) selection after, it sent to RGB switch

device N4(PI5V330) switch selection with RGB signal from VGA interface, then it sent to

GM1501/1601.

The HDMI via receiver N34(MST3383MB) processing after, it output RGB signal of 24bit to

GM1501/1601.

They sent to GM1501/1601 picture processing, therein YPBPB or RGB to A/D conversion after, it

and other three signal are switched selection and digital display processing, it include OSD,

GAMMA correction, brightness and contrast processing, then LVDS conversion to PDP panel

display.

The SIF1 of tuner1, SIF2 of tuner2 and audio signal of AV1/S, AV2 separate sent to audio processor

NA3(MSP3420).

The HDMI via chip N34(MST3383MB) decode to digital audio, after N26(CS4334) D/A conversion, it

audio and the audio signal of VGA/DVI sent to N44(HEF4052) switch selection, then sent to

MSP3420.

The audio of two YPBPR and VGA via switch conversion N42(HEF4052) to MSP3420 too.

The stereo of the SIF1 and SIF2 with other four ways audio switch conversion selection to volume

control and audio processing. One way output right/left channel audio of main-picture, the signal

sent SRS processing NA5 (M62494) to SRS sound stereo processing. It via sound amplifier

NA6(MP7722) to speaker; one way output right/left channel audio of sub-picture, it sent to earphone,

another way is AV OUT R/L output.

The work of whole unit is controlled by MCU, which includes GM1501/1601.

6

Page 9

A

Block diagarm

B

C

D

1 2 3 4 5 6 78

L/R_VGA

L/R_YPbPr1

L/R_YPbPr2

N42

YUV_SW

TC4052

YUV/USB

L/R_USB

Audio Switch

N44

TC4052

L/R_HDMI

L/R_AV1

L/R_AV2

Audio Switch

VGA/HDMI_SW

SIF

ANA_IN1

SC2_L/R

SC1_L/R

ANA_IN2

Audio Processor

MSP3420G

SC3_L/R

SC4_L/R

SC2_OUT

NA3

DACM_L/R

AUDIO OUT

HDMI

EDID

24C02

Tuner 1

Tuner 2

HDCP KEY

24C04

AV IN 1

AV IN 1

AV IN 2

AV IN 2

V OUT

MST3383

N34

HDMI RX

N39

YPbPr 2

CBT3257C

VGA

YPbPr 1

EDID

24C02

HDTV Switch

YUV_SW

OPTION

Media Player

N7

N10

TVP5160

FLI2310

Video Decoder

Deinterlacer

(USB)

Video Decoder

TVP5147

N8

SC1_OUT

CBT3257C

YUV/USB

YUV/VGA

HDTV Switch

Y Pb/Cb Pr/Cr

CBT3257C

RGB Switch

R G B

Hs Vs

SN74AHC14

N4

TDA7053AT

Head Phone

AMP

HP_SW

NA7

M62494FP

NA5SRS

Audio AMP

MP7722

NA5

NA6

N15

GM1601/GM1501

EEPROM

LCD TV Controller

Y Pb/Cb Pr/Cr

R G B

Hs Vs

Frash/ROM

Power_ON,IR,KeyA,KeyB,Led1,Led2

Mute,HP_SW,VGA_CAB,DVI_CAB

YUV/VGA,YUV_SW,YUV/USB

Frame Buffer

DDR

Title

SizeA3Date: 19-May-2006

File: G:\ \..\PH42R6BLOCK.Sch

Number

邱杰的文件 Drawn By:

PH42R6 BLOCK DIAGRAM

Power Supply

Power_ON,+5V_STB,VCC,VBL

PANEL

7654321

Sheet of

Revision

Ver 1.0

yyc

A

B

C

D

8

7

Page 10

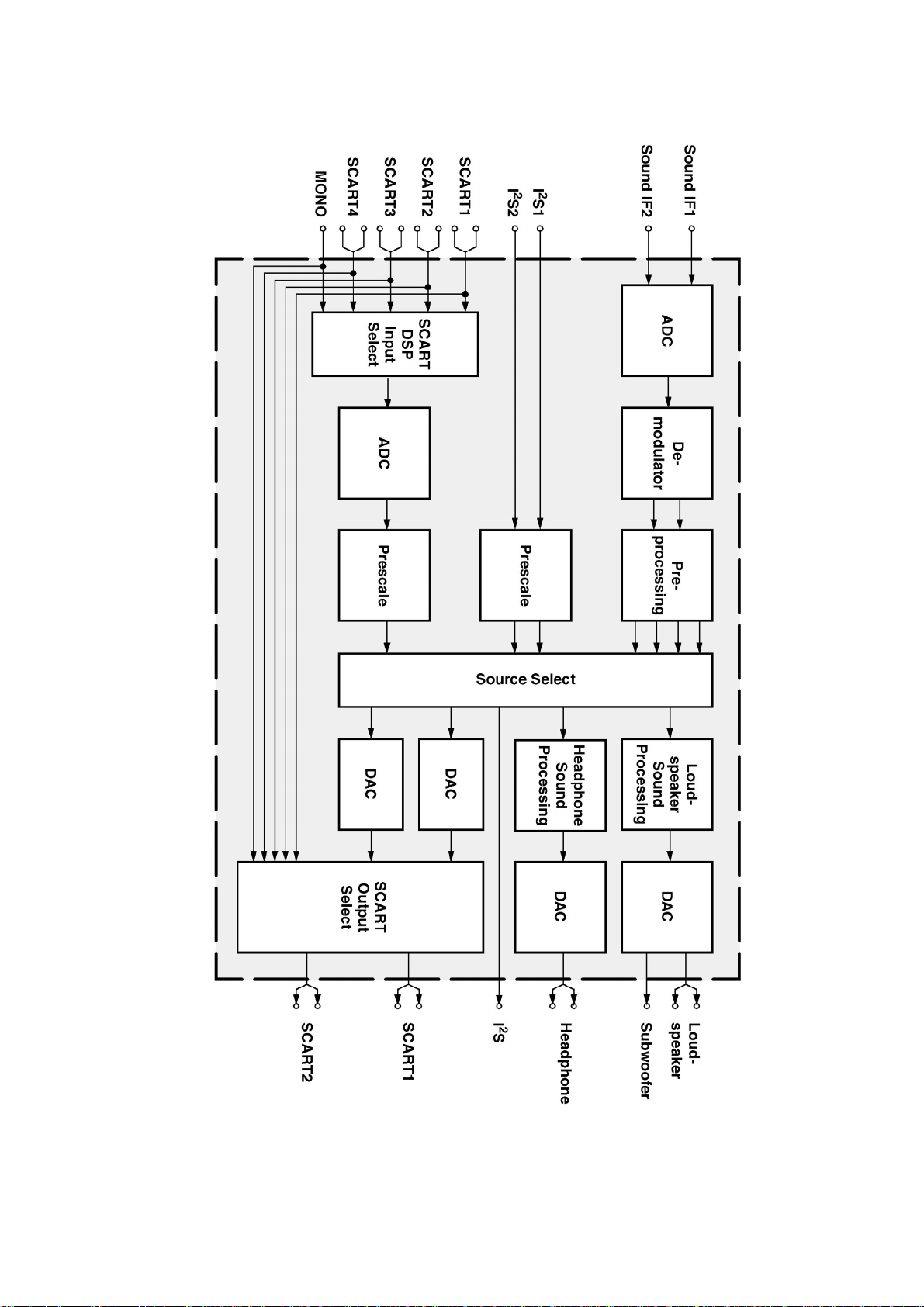

IC block diagram

1.MSP3420

The MSP 34x0G family of single-chip Multistandard Sound Processors covers the sound

processing of all analog TV-Standards worldwide, as well as the NICAM digital sound standards.

The full TV sound processing, starting with analog sound IF signal-in, down to processed analog

AF-out, is performed on a single chip. Figure 1–1 shows a simplified functional block diagram of the

MSP 34x0G.

This new generation of TV sound processing ICs now includes versions for processing the

multichannel television sound (MTS) signal conforming to the standard recommended by the

Broadcast Television Systems Committee (BTSC). The DBX noise reduction, or alternatively,

Micronas Noise Reduction (MNR) is performed alignment free.

Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the FM Stereo

Radio standard.

Current ICs have to perform adjustment procedures in order to achieve good stereo separation for

BTSC and EIA-J. The MSP 34x0G has optimum stereo performance without any adjustments.

All MSP 34xxG versions are pin compatible to the MSP 34xxD. Only minor modifications are

necessary to adapt a MSP34xxD controlling software to the MSP 34xxG. The MSP 34x0G further

simplifies controlling software. Standard selection requires a single I2C transmission only.

The MSP 34x0G has built-in automatic functions: The IC is able to detect the actual sound standard

automatically (Automatic Standard Detection). Furthermore, pilot levels and identification signals

can be evaluated internally with subsequent switching between mono/ stereo/bilingual; no I2C

interaction is necessary (Automatic Sound Selection).

The MSP 34x0G can handle very high FM deviations even in conjunction with NICAM processing.

This is especially important for the introduction of NICAM in China.

The ICs are produced in submicron CMOS technology. The MSP 34x0G is available in the following

packages: PLCC68 (not intended for new design), PSDIP64, PSDIP52, PQFP80, and PLQFP64.

8

Page 11

Fig. 1–1: Simplified functional block diagram of the MSP 34x0G

9

Page 12

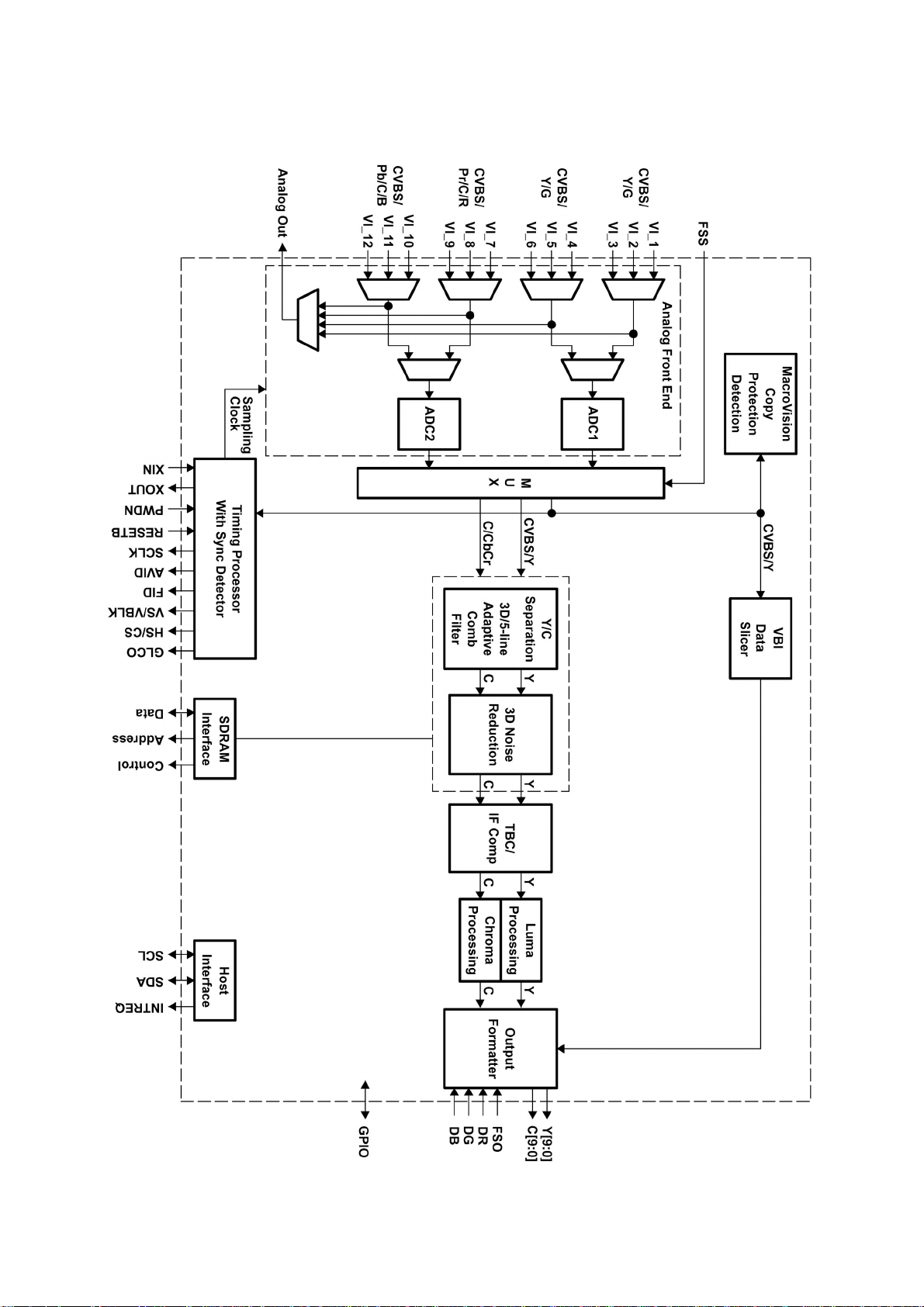

2. TVP5160

The TVP5160 device is a high quality; digital video decoder that digitizes and decodes all popular

baseband analog video formats into digital component video. The TVP5160 decoder supports the

A/D conversion of component YPbPr and RGB (SCART) signals, as well as the A/D conversion and

decoding of NTSC, PAL, and SECAM composite and S-Video into component YCbCr. Additionally,

component progressive signals can be digitized. The chip includes two 11-bit, 60-MSPS, A/D

converters (ADCs). Prior to each ADC, each analog channel contains an analog circuit, which

clamps the input to a reference voltage and applies a programmable gain and offset. A total of 12

video input terminals can be configured to a combination of YPbPr, RGB, CVBS,and S-Video video

inputs.

Progressive component signals are sampled at 2x clock frequency (54 MHz) and are then

decimated to the 1x rate. In SCART mode the component inputs and the CVBS inputs are sampled

at 54 MHz alternately, then decimated to the 1x rate. Composite or S-Video signals are sampled at

4x the ITU-R BT.601 clock frequency (54 MHz), line-locked for correct pixel alignment, and are then

decimated to the 1x rate. CVBS decoding utilizes advanced 3D Y/C filtering and 2-dimensional

complementary 5-line adaptive comb filtering for both the luma and chroma data paths to reduce

both cross-luma and cross-chroma artifacts. 3D Y/C color separation may be used on both PAL and

NTSC video signals. A chroma trap filter is also available. On CVBS and Y/C inputs, the user can

control video characteristics such as hue, contrast, brightness, and saturation via an I2C host port

interface. Furthermore, luma peaking with programmable gain is included, as well as a patented

color transient improvement (CTI) circuit. Attenuation at higher frequencies or asymmetrical color

subcarrier sidebands are compensated using the IF compensation block. Frame adaptive noise

reduction may be applied to reduce temporal noise on CVBS, S-Video, or component inputs.

3D noise reduction and 3D Y/C separation may be used at the same time or independently.

The TVP5160 decoder utilizes Texas Instruments’ patented technology for locking to weak, noisy,

or unstable signals and can auto-detect between broadcast quality and VCR-style (nonstandard)

video sources.

The TVP5160 decoder generates synchronization, blanking, field, active video window, horizontal

and vertical syncs, clock, genlock (for downstream video encoder synchronization), host CPU

interrupt and programmable logic I/O signals, in addition to digital video outputs.

The TVP5160 decoder includes methods for advanced vertical blanking interval (VBI) data retrieval.

The VBI data processor (VDP) slices and performs error checking on teletext, closed caption, and

other VBI data. A built-in FIFO stores up to 11 lines of teletext data, and, with proper host port

synchronization, full-screen teletext retrieval is possible. The TVP5160 decoder can pass through

the output formatter 2x sampled raw Luma data for host-based VBI processing.

Digital RGB overlay can be synchronously switched with any video input, with all signals being

oversampled at 4x the pixel rate.

10

Page 13

INTERNAL BLOCK DIAGRAM:

11

Page 14

3. MP7722

The MP7722 is a stereo 20W Class D Audio Amplifier. It utilizes a single ended output structure

capable of delivering 2x20W into 4Ω speakers. MPS Class D Audio Amplifiers exhibit the high

fidelity of a Class A/B amplifier at efficiencies greater than 90%. The circuit is based on the MPS’

proprietary variable frequency topology that delivers low distortion, fast response time and operates

on a single power supply.

TYPICAL APPLICATION

:

12

Page 15

4. MST3383MB

The MST3383MB integrates the HDMI compliant receiver for enabling advanced digital display

devices such as digital TVs, plasma displays, LCD TVs and projectors to receive and display.

Compliant with the HDMI 1.0 specification, the MST3383MB enables consumer electronic devices

to receive uncompressed, high quality, digital audio and video HD content over a single, low-cost

HDMI cable. The MST3383MB is available in a 128-pin PQFP package.

FUNCTIONAL DESCRIPTION

DVI/HDMI Interface

The MST3383MB integrates an HDMI compliant receiver and enables a high quality and secure

delivery of digital video and audio. The HDMI link input supports up to 170 MHz pixel rate. With the

HDMI input and signal detection, the MST3383MB provides a high-performance solution for up to

1080p for video and 1600x1200 (UXGA) for monitor applications. The MST3383MB’s HDMI

receiver is fully backward compatible to DVI 1.0 and HDCP 1.0.

MCU Interface

The MST3383MB provides 2-wire serial bus for interfacing with an MCU. It detects active inputs for

both on-line and off-line operations. During on-line operation, the MST3383MB also provides

polarity and period count information of active input’s DE signals. The MCU can easily adjust the

input mode and switch to active input properly.

Color Space Conversion

The MST3383MB supports all general color space conversions such as RGB to YUV or RGB to

YCbCr using parameters programmable by 2-wire serial bus.

Digital Video Output Formatting

The MST3383MB can output digital data in the following configurations:

. 24-bit 4:4:4 YCbCr/RGB output formats

. 16-bit 4:2:2 YCbCr output formats (ITU.601)

. 8-bit 4:2:2 YCbCr output formats (ITU.656)

. Channel swap

. MSB/LSB swap

Audio Stream S/PDIF port output is supported to enable PCM, Dolby Digital, DTS with sample rates

of 32~48 kHz and a sample size of 16~24 bits.

Audio Serial bus is supported to enable 2-channel PCM audio with sample rates of 32~192 kHz and

a sample size of 16~24 bits.

13

Page 16

5.GM1601/GM1501

The gm1601H is a dual channel graphics and video processing IC for Liquid Crystal Display (LCD)

monitors and televisions incorporating Picture in Picture, up to WUXGA output resolutions. The

gm1601H provides all key IC functions required for image capture, processing and display timing

control. On-chip functions include a high-speed triple-ADC and PLL, Ultra-Reliable DVI® receiver,

high quality zoom and shrink scaling engines, Motion Adaptive De-Interlacing (MADI), Low Angle

Diagonal Interpolation (LADI), an on-screen display (OSD) controller, a 100MHz on-chip X186

micro-controller (OCM), and a selectable double wide TTL or dual channel LVDS transmitter for

interface to displays. With all these functions integrated onto a single device, the gm1601H

eliminates the need for several system components, simplifying the design and reducing the cost of

high-end multimedia LCD monitors and televisions while maintaining a high degree of flexibility and

quality. The gm1601H is available in two silicon revisions – “BD” and “CF”. GM1601H-CF is a

backwards-compatible addition that incorporates some functional and quality improvements.

Applliicattiions

Multi-media LCD monitors up to WUXGA resolutions

LCD, PDP and Rear Projection TV at WXGA, UXGA, WUXGA and HD(720P & 1080P)

resolutions

GM1601H Systtem Desiign Examplle

Figure 2 below shows a typical high-resolution multi-media LCD monitor/TV system based on the

gm1601H. Designs based on the gm1601H have reduced system cost, simplified hardware and

firmware design and increased reliability because only a minimal number of components are

required in the system.

Figure 2. gm1601H System Design Example

14

Page 17

6. FLI2310

The FLI230x and FLI2310 are highly integrated digital video format converters for DTV and DVD

applications using patented deinterlacing and post processing algorithms from Faroudja

Laboratories, coupled with highly flexible scaling, a wide variety of aspect ratio conversions, and

other special video enhancing features to produce the highest quality image.

6.1 Inputs

Input all industry standard and non-standard video resolutions, including 480i (NTSC), 576i

(PAL/SECAM), 480p, 720p, 1080i, and VGA to XGA

Digital input, 8-bit Y/Cr/Cb (ITU-R BT656), 8-bit Y/Pr/Pb, 16-bit Y Cr/Cb (ITU-R BT601), 24-bit

RGB, YCrCb, YPrPb

Input pixel rate up to 75MHz maximum

6.2 Outputs

Output resolutions include 480p, 576i, 576p, 720p, 1080i, 1080p, and VGA to SXGA

Interlaced or Progressive output

In the FLI230x, the output can be either analog YUV/RGB (through the integrated 10-bit DAC),

or digital 24-bit RGB, YCrCb, YPrPb (4:4:4), or digital 16/20-bit Y Cr/Cb (4:2:2)

The FLI2301 can provide 525P/625P Macrovision compliant analog output

In the FLI2310, digital output of 24-bit RGB, YCrCb, YPrPb (4:4:4), or 16/20-bit Y Cr/Cb (4:2:2)

are available

Output pixel rate up to 150 MHz maximum

6.3 Formats

Input color manipulation matrix supports all color spaces: RGB, YPrPb, 4:4:4 YCrCb, 4:2:2

YCr/Cb, ITU-R BT656, ITU-R BT601

Output supports analog RGB, YPrPb, and YCrCb in the FLI230x; and digital RGB, YPrPb, 4:4:4

YCrCb and 4:2:2 YCr/Cb in FLI230x/FLI2310

6.4 Frame Rate Conversion

Tearless Frame Rate Conversion 50/60/72/75/100/120 Hz

6.5 Front End Processing

Motion Adaptive Noise Reduction – Improves picture quality for off-air material.

Cross Color Suppressor (CCS) - Removes cross color artifacts in composite video signals due

to poor Y/C separation in standard 2-D video decoders, eliminating the need for expensive 3-D

video decoders.

6.6 Deinterlacing

Per-pixel Motion Adaptive Deinterlacing

Patented FilmMode Processing - Used for proper de-interlacing of 3:2 and 2:2 pulldown

material.

Edit Correction - Film content is continuously monitored for any break in sequence caused by

“bad edits” and quickly compensates for the most effective reduction in artifacts.

DCDi™ - Video is analyzed on a single pixel granularity to detect presence or absence of

angled lines and edges, which are then processed to produce a smooth and natural looking

image without visible artifacts or “jaggies”.

6.7 Scaling

High Quality Fully Programmable Two Dimensional Scaler

Aspect Ratio Conversion for “Anamorphic” or “Panoramic” (non-linear)

Display 4:3 images on 16:9 displays and vice versa, including Letterbox to Fullscreen, Pillarbox,

15

Page 18

and Subtitle Display Modes

6.8 TrueLife™ Enhancer

Two dimensional, non-linear, luma and chroma video enhancer brings out details in the picture,

producing a more life-like image.

6.9 Memory

32-bit wide SDRAM (i.e. one 2M x 32-bit, or two 1M x 16-bit) controller, up to 166 MHz operation, for

external SDRAM

INTERNAL BLOCK DIAGRAM:

7. TVP5147

Functional Block Diagram

16

Page 19

A

B

Wiring diagram

1 2 3 4 56

TO KEYBOARD

C

D

TO PANEL

KEY BOARD

6 PIN

X6

6 PIN

X10

X7

12 PIN

X502X510

X29 X13 X28

12 PIN

X508

X509 X507 X504

POWER BOARD

11 PIN

LVDS

X15

8 PIN

10 PIN

AC IN

XA5

XA7

XA9

XA12 XA11

667-PS42R6-53667-PS42R6-56

File: C:\Documents and Settings\..\PH42R6.Sch Drawn By:

Number

Sheet of

Revision

TO SPEAKER

Title

SizeBDate: 18-May-2006

54321

6

A

B

C

D

17

Page 20

Troubleshooting charts

p

k

n

p

p

1. No raster, no picture and no sound:

Check if power indication is light?

yes no

normal

Turn on the power again and chec

the power supply

JI

EEPROM

abnormal

Normal abnormal

Check X29,

rewrite the

software

Check the supply

power D3.3V, 12V

abnormal

abnormal normal

Set the power to self turn-o

mode then check

Power board

roblem

No raster, no picture and no sound

Turn off the

ower and then

turn on

Rewrite the software

again and check

Check 5V-STBY

abnormal normal

Power board

roblem

18

Page 21

2. With sound but no picture:

d

yes no

no yes

Check if the white

balance of the factory

menu is normal?

normal

abnormal

Check each level

Normal abnormal

circuit following the

input signal channel

Normal abnormal

Check if no image for all

other channels

Refer to checking

program4

yes no

Reset the EEPROM

With sound but no picture

Display LOGO?

Check if the

X13 is signal

Check LVDS wire

Panel

damaged

Reconnect the LVDS

wire

If the panel lights or produce

high voltage when turn on the

TV

Power boar

damaged

19

Page 22

3. With picture but no sound.

n

r

t

d

V

p

N

N

p

p

N

y

y

With picture but no sound

If there is output from sound power amplification board

no

yes

check if input signal in sound power

amplification board

Sound box damaged

yes no

Sound power amp. or other peripheral circuit have

problem. Check power supply, if SHUTDOWN pi

control is normal and if output short circuited or othe

problems that cause protection to work.

Measure if the sound input of the

present channel is normal

no yes

MSP3420 or other peripheral

circuit have problem

Check different levels of circui

following input audio signal

4. A certain channel is abnormal

1) AV no picture

Check if X7 has signal input

yes no

Check if N7 has clock signal output an

ITU-R 656 is normal?

There is problem from A

socket to X7 channel

no

es

7 or other peripheral

circuit have problem

Check if N10 FLI2310

out

ut is normal

no

es

10 FLI2310 or other

eripheral circuit have

roblem

15 or other peripheral

circuit have problem

20

Page 23

2) No picture in YPRPB

N

t

N

t

N

t

N

y

y

y

t

N

r

p

p

t

N

r

p

N

r

p

t

y

y

y

Check ifN39 has input signal.

es

no

Check if the outpu

of N4 is normal?

no

4 or the peripheral circui

have problem.

Check if the input of N4 is

normal?

no

es

15 or the peripheral

circuit have problem.

es

39 has problem

4 or the peripheral circui

have problem

3) TV no picture

.

Check if N7 has clock signal outpu

and ITU-R 656 is normal?

7 and othe

eripheral circuit have

roblem.

10 FLI2310 and othe

eripheral circuit have

Check if X7 have input signal?

es no

Check TUNA01 of

supply power and

other peripheral circui

es no

Check if N10 FLI2310

output is normal?

esno

15 and othe

eripheral circui

21

Page 24

5. Abnormal picture :

Peculiar color, which may be caused by the following phenomena:

A certain differential wire pair of LVDS (RX0+/-,RX1+/-,RX2+/-,RX3+/-) of X13 is abnormal,

which may lead to lack of color (it’s not a complete loss of color);

Abnormal picture vertically or horizontally (bar like): Abnormal in complete line extending all the

way from up downward on the screen of stand definition TV set; abnormal vertically on half

screen of high definition TV set. They may be caused by the damage of the address BUFFER

module that directly corresponds to its position, or may be caused by the damage of the

connection wire that directly corresponds to the position of the screen. The horizontal bar like

abnormality is also related to the Y driving circuit that corresponds directly to its position. To

judge these phenomena, It’s possible to check it by setting the screen to the status of self

check as explained above

No brightness in the square block area: Normally it’s caused by the damage of the address

BUFFER module that directly corresponds to its position, or may be caused by the damage of

the connection wire that directly corresponds to the position of the screen. To judge these

phenomena, It’s possible to check it by setting the screen to the state of self check as

explained above.

Diagnosis for panel and service

1. The screen is not bright:

a. Check to see if the power supply plug from the power filter board to the power supply board is well

inserted into the socket. If not, plug it in.

b. Check if the fuse on the power supply board is blown up. If yes, replace it for a good one.

c. Remove our main board and the video processing board, unplug P4, P2, short circuit the pin 8 of P2 to

the ground, testing signal itself of the logic board set the on, switch the power on and see if the screen is

lit. If the screen can give a normal and completely white field signal, then the problem lies in our main

board or video processing board, which will be dealt with separately.

d. If the screen is not lit, then first replace the power supply board to see if the problem is solved.

e. If the problem remains after the power supply board is replaced, then the problem lies in the screen.

Replace the entire screen for treatment.

2. There appears on the screen a line or several unlit lines.

Check if the socket between Y driving board and Y BUFFER is plugged well. If not, plug it well. If yes

22

Page 25

then replace Y BUFFER (upper, lower) in respect to the upper, lower part of the dark line on the screen.

3. There appear on the screen one or several horizontal lines that are much brighter

than the remaining horizontal lines at the edge:

Check if the socket between Y driving board and Y BUFFER is plugged well. If not, plug it well. If yes

then replace Y BUFFER (upper, lower) in respect to the upper , lower part of the dark line on the screen.

4. There appear on the screen one vertical unlit line or a vertical entirely unlit block

a. If it’s one vertical unlit line, then COF has problem.

b. If it’s a vertical entirely unlit block, then first check if the connection socket between COF and logic

BUFFER has problem. If not, check if the connection socket between the logic BUFFER and the logic

board is normal. If yes, replace the logic BUFFER. Finally, if the problem still remains when the

replacement is over, then replace the logic board.

5. There appears on the screen a mono color signal and one or several vertical bright

lines of other colors:

a. If it’s a vertical bright line of other colors, then the problem lies with COF or the screen.

b. If it’s an entire vertical block of other colors, then first check to see if the connection socket

between COF and logic BUFFER has problem. If no problem, check if the connection

socket between the logic BUFFER and the logic board is normal. If it’s normal, then replace

the logic BUFFER. If the problem still remains after the replacement, then replace the logic

board. Finally if the problem is still there, then the problem lies with COF.

6. There appear on the screen abnormal bright spots or blocks that are different from

what’s described above:

a. Check if the connection socket between COF and logic BUFFER board has been well plugged.

b. Replace the logic BUFFER board. If it’s not solved then replace logic board. If the problem still

remains, then it’s the problem with COF.

23

Page 26

Power board

Page 27

Power board

power board

Page 28

XA5

1

2

3

4

5

6

XA3

CKX5-2K-2

C

GND-D

Y

XA2

AV3-14WKD

Y

W

R

XA1

AV3-14WKD

Y

W

R

XA4

AV3-14WKD

Y

W

R

GND-D

100n

100n

1

3456789

2

XA7

GND-D GND-D GND-D GND-D GND-D GND-D

TJC10-12A

AL

R_HD

L_HD

68uH

+5V_V

LA48

CA11

220u

16V

+5V_V

68uH

LA45

CA3

16V

220u

SCL

SDA

CA4

100n

CA1

LA43

2

1

BT

VCC3

BT

AGC

1

2

LA44

CA2

100n

16V

220u

GND-D

GND-D

GND-D

RA3

100

RA1

100

3

5

6

4

7

AS

SDA

SCL

VCC1

VCC15SDA

3

CA5

CA6

GND-D

AFC

TUNA1

TUNA2

AFC

AS

SCL

6

4

7

RA2

RA4

100

100

SCL

SDA

68uH

LA46

PACDN045YB6

34

2

100n

CA7

1

GND-D

LA1

STBL2012-501

LA2

STBL2012-501

LA3

STBL2012-501

JS-6AM/134-A2

JS-6AM/134

+5V_V

NA1

CA8

100n

RA5

100K

GND-D

RA6

100K

GND-D

RA7

100K

GND-D GND-D

TV1

CA12

100n

RA8

75

GND-D

11

12

13

14

SIF

VCC2

AUDIO

VIDEO

VIDEO

VCC2

SIF

AUDIO

11

12

13

14

75

RA12

CA13

100n

10n

CA15

CA14

220u

16V

LA47

68uH

+5V_V

STBL2012-501

STBL2012-501

STBL2012-501

470u

CA16

10u

16V

CA18

16V

CA17

10u

16V

5

6

GND-D

STBL2012-501

STBL2012-501

STBL2012-501

STBL2012-501

STBL2012-501

100n

CA19

GND-D

5

GND-D

6

NA2

PACDN045YB6

34

2

1

RA9

75

RA10

1K

1n

CA9

GND-D

RA11

1K

1n

CA10

LA12

LA11

LA10

LA7

LA9

LA5

LA6

LA8

+9V

BC847AW

BC847AW

VA1

RA13

VA2

RA14

GND-D

GND-D

GND-D

1n

CA20

GND-DGND-D

1n

CA21

GND-D GND-D

1n

CA22

GND-D GND-D

1n

CA23

GND-D GND-D

RA15

470

1K

GND-D

RA16

470

1K

GND-D

RA17

RA18

RA19

75

75

75

RA24

1K

100K

RA20

RA25

1K

RA21

100K

RA26

1K

100K

RA22

RA27

1K

RA23

100K

LOUT

LOUT

ROUT

ROUT

SIF1

TV_MONO

SIF2

SV_DET

Y/AV1

VOUT

L_HD

TV1

SIF1

SIF2

GND-D

SRS_STE

SRS_MONO

TV2

C

AV2

SRS_STE

SRS_MONO

L1

R1

MUTE

L2

R2

CA24

ALARAR

R_HD

+5V_A

10u

16V

TXD

1K

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

RA33

100

RA34

100

VCC

2

TXD

100

CA36

63NC64

NC

AVSUP

AVSUP

ANA_IN1+

ANA_IN-

ANA_IN2+

TESTEN

XTAL_IN

XTAL_OUT

TP

AUD_CL_OUT

NC

NC

D_CTR_I/O_1

D_CTR_I/O_0

ADR_SEL

STANDBYQ

1NC2

2K

RA35

CA32

GND-D

100n

RA36

3.9K

CA33

10n

RA37

100

RA38

100

CA38

100n

1

XA6

+5V_RS232

8

R2IN

RA32

R2OUT10T2IN11T1IN12R1OUT13R1IN14T1OUT15GND16Vcc

9

CA34

47p

CA35

47p

XA8

68uH

LA16

CA30

CA31

47u

1.5n

470p

16V

GND-D

RA28

100

CA27

51p

CA28

51p

RA29

100

CA29

GND-D

51p

CA25

18p

GND-D

GA1

CA26

18.432MHz

18p

+5V_A

GND-D

RA30

10K

LA17

68uH

SCL

SDA

RXD

GND

3

4

RXD

RA31

C

TV_MONO

CA47

470n

CA46

CA37

100n

59

60

61

AVSS62AVSS

SCART_5_R/MONO

I2C_CL3I2C_DA4I2S-CL5I2S_WS6I2S_DA_OUT7I2S_DA_IN18ADR_DA9ADR_WS10ADR_CL11DVSUP12DVSUP13DVSUP14DVSS15DVSS16DVSS17I2S_DA_IN218NC19NC

CA48

CA41

10u

16V

CA42

4.7n

CA43

220n

CA44

100n

GND-D

CA45

100n

GND-D

100n

CA40

100n

CA39

6V-7

T2OUT

RA39

12345

RXD

11

7906-9F

678

CA50

470n

58

VREFTOP

SCART_5_L

47u

16V

20

19

18

17

16

15

14

13

12

11

CA49

C1-4C2+5C2-

100

100

TXD

9

Y/AV1

R2

470n

57

SC1_IN_R

CA54

REF OUT

REF IN

L+R

BPF

HPF

LPF

PS

GND

SRS STEREO

SRS MONO

100n

2V+3

+5V_RS232

RA40

10

CA51

100n

CA53

1.5n

C1+

CA55

16V

22u

L2

56

AV2

470n

55

SC1_IN_L

NA5

M62494FP

CA52

100n

1

MAX3232CSE

CA56

ASG

SRS PR

SRS NR

SRS NL

NA4

R1

470n

54

SC2_IN_R

MSP3420

(ADDR:80H)

CA57

RIN

LIN

SRS A

ROUT

LOUT

Vcc

Mute

TV1

L1

470n

CA58

52

53

SC2_IN_L

NA3

470p

1

2

3

4

5

6

7

8

9

10

+5V_RS232

VOUT

AR

470n

CA60

51

ASG

CA59

101112

AL

CA61

50

SC3_IN_R

220p

CA67

470p

TV2

470n

49

ASG

SC3_IN_L

GND-D

CA66

18n

CA68

470p

CA64

100n

GND-D

DA1

LL4148

CA65

CA62

2.2u

R_HD

470n

48

2.2u

CA63

+5V

SC4_IN_R

50V

50V

L_HD

LL4148

DA2

CA70

470n

46NC47

SC4_IN_L

LA49

68uH

CA69

100u

16V

RA41

10K

RA43

RA78

0

820n

10K

20NC21

CA71

3K

RA42

35V

CA73

GND-D

+5V_A

50V

CA74

3.3u

AHVSS44AHVSS45AGNDC

RESETQ22NC23NC24DACA-R

RA45

100

RESET#

0

RA47

10n

CA72

RA44

1.5K

+9V

DA3

LL4148

VA4

BC857AW

10K

RA46

47u

VA3

BC847AW

GND-D

GND-D

100n

CA75

41NC42NC43

SC1_OUT_L

SC1_OUT_R

SC2_OUT_L

SC2_OUT_R

RA48

10K

253D-02

LA21

68uH

CAPL_M

AHVSUP

CAPL-A

VREF1

DACM_SUB

DACM_L

DACM_R

VREF2

DACA_L

RA50

100

GND-D

RA49

GND-D

LA50

SV_DET

+9V

LA56

68uH

2.2n

2.2n

GND-D

RA57

RA58

RA59

RESET#

MUTE

LOUT

ROUT

HP_L

HP_R

CA88

CA89

2.2n

CA90

CA91

1u

1u

+23V_AMP

16V

LA24

STPB3216-380PT

CA94

1n

GND-D

AMP_VCC1

LA52

STPB3216-380PT

10u

RA60

100K

CA92

100

HP_L

HP_R

10K

10K

47u

16V

CA78

CA79

CA77

1.5n

470p

GND-D

CA82

10u

16V

40

39

CA83

38

16V

37

10u

36

35

2.2n

2.2n

CA80

RA53

GND-D

100K

GND-D

CA81

RA56

CA86

2.2n

CA87

100

1u

CA84

34

33

32

NC

31

NC

30

29

NC

28

27

26

25

0

GND-D

1u

CA85

RA54

100K

GND-D

GND-D

10n

CA95

GND-D

AMP_VCC2

LA51

+23V_AMP

STPB3216-380PT

RA61

16V

GND-D

100K

10u

CA93

RA62

35V

CA76

470u

+5V_A

10K

RA55

RA52

10K

VA5

BC847AW

RA51

4.7K

GND-D

GND

8

SCL

CA96

1n

RA63

100K

CA98

4700p

GND-D

GND-D

100K

+9V

4700p

CA100

GND-D

CA97

5

6

7

GND-D

SDA

CA99

CA101

470u

100n

16V

1

NC1

2

REF1

3

IN1

4

AGND1

5

NC5

6

EN1

7

IN2

8

REF2

9

AGND2

10

EN2

10n

4

SV_DET

3.3K

NA6

MP7722

GND-D

RA64

MUTE

CA103

AMP_VCC1

SIGN1818

PGND1

PGND2

3

100n

CA102

CA104

1u

22p

RA65

82K

35V

SW1

VDD1

BS1

NC16

SW2

VDD2

BS2

NC11

AMP_VCC2

CA106

2

35V

470u

HP_SW

470u

20

19

18

17

16

15

14

13

12

11

CA107

1

CA105

RA66

82K

22p

HP_VOL

XA9

TJC10-08A

CA111

CA112

1u

CA109

LL4148

100n

100n

CA114

CA108

LL4148

DA4

100n

SK34A

DA5

1u

+5V_A

+5V_V

1

2

3

4

5

6

7

8

DA6

SK34A

+9V

GND-D

NC

VC1

NC

VI1

VP

VI2

SGND

VC2

DA7

RA67

GND-D

GND-D

CA121

470u

35V

TDA7053AT

RA68

20K

CA116

20K

16V

16V

CA110

1000u

35V

NA7

100n

CA119

100n

LA42

253D-02

CA117

1000u

LA35

253D-02

CA118

1000u

CA115

1000u

OUT1+

NC

PGND

OUT1-

OUT2-

NC

PGND

OUT2+

BZV55-B6V2

TA78M09P

OUT

35V

16

15

14

13

12

11

10

9

DA9

DA8

BZV55-B6V2

CA124

NA8

GND

CA122

100n

RA70

RA69

390p

GND

INPUT

+23V_AMP

GND-D

10

CA125

GND

10

390p

RA72

+5V

16V

100n

CA126

CA130

1000u

GND-D

+12V

100n

CA141

+23VSC

CA123

CA127

470u

100n

35V

STBL2012-501

STBL2012-501

RA74

10K

CA132

100n

CA133

100n

RA75

10K

STBL2012-501

LA54

DASL983BN-1003

SK34A

LA55

DASL983BN-1003

LA36

LA37

LA38

35V

470u

CA134

GND

SIGN1798

GND

CA128

16V

47u

CA129

16V

47u

10K

RA73

10K

SIGN1804

DA10

LA40

100n

CA131

GND-D

DA11

SK34A

782-PH42R7-5300

470n

470n

CA135

CA137

1000u

35V

CA136

CA138

1000u

35V

TJC3-10A

XA10

CKX3-3.5-1K

10

RA76

100n

CA139

100n

CA140

10

RA77

10

9

8

7

6

5

4

3

2

1

XA11

L

GND-D

R

XA12

GND

2005.06.22

Ver1.0

1

L

2

3

R

4

Analog board

Page 29

ABCDEFGHI

3,5

VBLU[7-0]

VBLU[7]

VBLU[0]

VBLU[1]

VBLU[2]

VBLU[3]

VBLU[4]

VBLU[5]

R214

VBLU[6]

10

81

84

NC8485NC85

NC2122NC22

21

N26

AOUTL

VA

AGND

AOUTR

56

R34

DATA[2]82DATA[1]83DATA[0]

NC2324NC2425NC25

23

10

R215

V_DDC

65

66

67

69

70

72

73

74

75

79

76

GND66

HSOUT71VSOUT

DATA[4]80DATA[3]

8

7

6

5

C264

22p

56

22p

C263

R35

GND74

VDDC75

DATA[7]77DATA[6]78DATA[5]

V_MPLL

G5

14.31818MHz

C300

C16 10n

C17

C18

C19 10n

C20

C21

C22 10n

VDDP73

FIELD/GPO

GND3132AVDD_MPLL33XOUT34XIN35HWRESET36A037SCL38SDA

31

100n

VDDP65

VDDC6768DATACK

SOGOUT/DE

+5V

L53

STBL3216-601

16V

C301

10uF

C3

47p

10n

10n

10n

10n

NC64

NC63

DATA[8]

DATA[9]

DATA[10]

DATA[11]

DATA[12]

DATA[13]

DATA[14]

DATA[15]

GND54

VDDP53

NC52

NC51

DATA[16]

DATA[17]

DATA[18]

DATA[19]

DATA[20]

DATA[21]

DATA[22]

DATA[23]

VDDP39

X22

1

2

3

4

MDA

MCL

INT

3V3SC

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

D9

MMBD1204

V_DDP

R223

10

R216

10

R217

10

R218

10

R219

10

R236 4.7K

R237 4.7K

FLS_DET

AVS

AHS

VGA_SCL

VGA_SDA

VGA_CAB

SOG

BLUE+

BLUE-

GREEN+

GREEN-

RED+

RED-

VGRN[7-0]

VGRN[0]

VGRN[1]

VGRN[2]

VGRN[3]

VGRN[4]

VGRN[5]

VGRN[6]

VGRN[7]

VRED[7-0]

VRED[0]

VRED[1]

VRED[2]

VRED[3]

VRED[4]

VRED[5]

VRED[6]

VRED[7]

100

R239

100

R238

R221

100

8

10K

100n

R235

C299

5

5,7

5,7

5

5

5

5

5

5

5

5

5

5

R222

7

6

R212

100

5

R213

100

0

HDCP KEY

MCLK

LRCK

SCLK

1

HDMI PORT

X2

HDMI

RX2+IN

1

2

RX2-IN

3

RX1+IN

4

5

RX1-IN

6

RX0+IN

8

RX0-IN

9

RXCK+IN

10

11

2

3

5

4

VGA PORT

HDR-F15S-3

5

15

12 13 14

11

12

13

14

15

16

17 7

18

19

HDMI(DVI)_CAB

HDMI_RST

5

X3

5

10

89

234

1

67

RXCK-IN

HDMI_5V

N31

PESD5V0L4UG

1

AO

2

A1

3

A2

4

GND

N27

PESD5V0L4UG

3

1

2

R240

2.2K

N1

24C02N-10SI27

VGA EDID

1

N29

PRTR5V0U4D

8

R3

7

6

5

R4

4

5

PESD5V0L4UG

R22

100K

HDMI(DVI)_CAB

10K

0

5

100

6

4

R5

100n

R11

10K

C2

+5V

1K

R245

R10

10K

R6

100

L1

BG2012B300T

BG2012B300T

BG2012B300T

+5V

10K

MMBD1204

R12

L2

L3

MMBD1204

D2

1

2

3

4

D1

A-RED

R7

75

1

2

3

AO

A1

A2

GND

A-GREEN

A-BULE

PRTR5V0U4D

N30

24C02N-10SI27

HDMI EDID

+5V

R8

75

R9

75

+5V

6

5

4

R14

100

R17

10K

R16

N2

Vcc

WP

SCL

SDA

10V

47uF

C7

C4

100n

10V

47uF

C8

C5

100n

10V

47uF

C9

C6

100n

10K

8

R18

10K

C15

0

R19

SN74AHC14PWR

1

1A

2

1Y

3

2A

4

2Y

5

3A

6

3Y

7

GND84Y

100n

N24

C10

7

6

5

10K

R189

10K

R190

10K

R191

10K

R192

10K

R193

10K

R194

100n

10

R251

RX2-

RX2+

RXCKRXCK+

RX0-

RX0+

RX1-

RX1+

R252

10

DDCSCL

R209

100

DDCSDA

R210

100

R15

100

+3.3V_DIG

14

C14

VCC

13

100n

6A

12

6Y

11

5A

10

5Y

9

4A

C11

100n

PI5V330

1

IN

2

S1A

3

S2A

4

DA

5

S1B

6

S2B

7

DB

8

GND

R2

330K

C1

47uF

L4

+5V+5V_MUX

68uH

C12

16V

16V

100uF

N4

16

VCC

15

/EN

14

S1D

13

S2D

12

DD

11

S1C

10

S2C

9

DC

100uF

V_DVI

V_AUPLL

103

GND103

104

GND104

105

GND105

106

AVDD_AUPLL

107

GND107

108

RX0RX0+

RX1RX1+

RX2RX2+

RXCKRXCK+

DDCSCL

DDCSDA

SDATA

SCLK

LRCK

MCLK

C13

+5V_MUX

390

R220

V_PLL

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

R20

75/1%

RX0N

RX0P

GND110

RX1N

RX1P

AVDD_DVI113

RX2N

RX2P

GND116

RXCKN

RXCKP

AVDD_DVI119

REXT

NC121

GND122

AVDD_PLL

DDCSCL

DDCSDA

AVDD_DVI126

GND127

NC128

R21

75/1%

1

2

3

5

4

V17

BC847AW

Vcc

WP

SCL

SDA

3

1

N28

2

4

3

5

2

SDATA

101

102

100

93

97

98

99

AUWS

MCKO

AUSCK

SPDIFO

AUMUTE

VDDP102

NC12NC23NC34AVDD_DVI45GND56NC67NC78NC89NC910NC1011NC1112NC1213NC1314NC1415NC1516NC1617NC1718NC1819NC1920NC2026NC2627NC2728NC2829AVDD_DVI2930GND30

1

R234

100

R24

10K

R25

750

R26

20

R27

20

R28

20

R23

75/1%

92

NC9394NC9495NC9596AUSD

91

VDDC92

90

GND91

86

87

88

89

GND87

GND89

VDDP88

VDDP90

N34

MST3383MB

1

SDATA

2

SCLK/DEM

3

LRCK

4

MCLK

R32

100K

VDDP86

56

CS4334

R33

VVS

VHS

VDE

VCLK

VGRN[7-0]

VRED[7-0]

3,5

Vcc

WP

SCL

SDA

3,5

3,5

3,5

3,5

5

24LC04

C268

10uF

N5

16V

3V3SC

10V

SW_SDA

SW_SCL

RESET_OUT

AO

A1

A2

GND

C267

10uF

16V

R36

10K

L47

STBL3216-601

L48

STBL3216-601

L49

STBL3216-601

L50

STBL3216-601

47uF

C295

C297

2,3

2,3

5

1

2

3

4

R37

10K

100n

C275

C270

100n

C283

C284

100n

100n

100n

R38

470

R39

470

C271

100n

C276

V_PLL

V_MPLL

AS1117-2V5

IN OUT

STBL3216-601

STBL3216-601

3.9n

C265

100n

C277

16V

16V

N32

100n

V_DVI

16V

C280

10uF

100n

100n

C294

C287

100n

47uF

C296

100n

C281

AL_HDMI

AR_HDMI

V_DDC

10uF

C289

V_DDP

16V

10uF

100n

C282

16V

10uF

C293

9

9

C290

100n

100n

C272

C273

C274

100n

100n

C278

C279

10uF

C291

10uF

C292

10V

100n

C298

L51

100n

100n

C285

C286

L52

C266

3.9n

C288

100n

V_AUPLL

16V

AL_HDMI

AR_HDMI

6

8

Pb

8

Y

8

Pr

Pb

Y

Pr

NOT TO BE POPULATED

版

R29

100

RGB/YPbPr_SEL

5

XOCECO

TITLE:

DWG NO.

Date:

XIAMEN OVERSEAS CHINESE

ELECTRONIC CO., LTD.

CPU

203-L37R70-01DL

Sheet to

1

REV.

A1.0

7

年

月

日

Page 30

ABCDEFGHI

C34

G2

33p

3V3SC

L10

1

2

3

4

5

6

12

11

10

9

8

7

6

5

4

3

2

1

TJC10-12A

X7

3,5

1,3

1,3

/RESET

SW_SDA

SW_SCL

VOUT

R50

75

7

STBL3216-601

C41

100n

C39

100n

L13

STBL3216-601

L14

STBL3216-601

MDEC_D3.3V

C42

100n

C25

100n

MDEC_A3.3V

C37

100n

+1.8VDEC

DECOUPLING FOR TVP5160 DECOUPLING FOR TVP5147

+5V

L65

STBL2012-221

10K

R281

220

R279

VOUT

VOUT

BC857AW

V26

22K

R282

MDEC_A1.8V

TV2

TV2

VOUT

C24

TV1

R49

75

R45

100n

AV2

100n

C302

C303 100n

100n

C304

75

R44

C305

100n

C306

100n

C23

75

100n

Y/AV1

100n

C307

C308

100n

100n

C309

C

C310

100n

C311

100n

R64

100

R63

100

R65

100

3V3SC

R56

2.7K

V1

BSS138LT1

V2

BSS138LT1

10V

100n

C312

C26

100n

C365

100n

R280

C364

47uF

MDEC_A3.3V

G

G

STBL3216-601

STBL3216-601

100uF

0

16V

S

D

S

D

MDEC_A3.3V

1

2

3

4

5

6

7

8

9

C54

100n

C49

100n

C50

100n

C32

33p

C33

33p

A33GND1

A33VDD2

VI_1

VI_2

VI_3

NC

VI_4

VI_5

VI_6

NC

A18VDD11

A18GND12

A18VDD13

A18GND14

A18GND15

A18VDD16

VI_7

VI_8

VI_9

NC20

VI_10

VI_11

VI_12

NC24

A33VDD25

A33GND26

A33GND27

NSUB

TMS

SCL

SDA

INTREQ

129

14.31818MHz

PP

MSTR_SDA

MSTR_SCL

MDEC_D3.3V

C60

C67

100n

100n

MDEC_A1.8V

C55

C61

100n

100n

MDEC_D1.8V

C62

C56

100n

100n

G1

R54

100K

121

122

123

124

125

126

127

128

XOUT

PLL18VDD

PLL18GND

A33VDD125

A33GND126

A33GND128

ANALOG_OUT

DVDD3334DGND3435PWDN36RESETB37IOVDD3738IOGND3839D040D141D242D343D444D545D6

33

5

5

L17

L18

C44

C46

100n

C47

100n

C48

100n

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

R58

2.7K

3V3SC

L9

STBL3216-601

C36

100n

PDEC_A3.3V PDEC_D3.3V

C57

120

XIN

118

119

FSS

AGND

+1.8VDEC

114

115

116

117

FID/GPIO

AVID/GPIO

HS/CS/GPIO

VS/VBLK/GPIO

C51

100n

R57

10K

113

C_1/GPIO

C_0/GPIO

112

DGND112

111

100n

110

DVDD111

C_2/GPIO

C63

100n

L15

STBL3216-601

L16

STBL3216-601

106

107

108

109

C_5/GPIO

C_4/GPIO

C_3/GPIO

C64

105

IOVDD105

IOGND106

N7

TVP5160

(BB/BA)

DVDD4754D1055D9

DGND4849D1550D1451D1352D1253D11

46D747

48

56D857

10V

100n

C52

100n

C53

100n

101

102

103

104

100

99

DGND100

C_9/GPIO/FSO

C_6/GPIO/RED

C_8/GPIO/BLUE

C_7/GPIO/GREEN

GLCO/GPIO/I2CA0

IOVDD5758IOGND5859DQM60CLK61A1162A963A864A7

L11

STBL3216-601

L12

STBL3216-601

C38

100uF

C58

C59

97

Y_198Y_0

DVDD99

IOGND93

IOVDD92

DGND86

DVDD85

DATACLK

GPIO/I2CA1

IOGND75

IOVDD74

DGND66

DVDD65

PDEC_A3.3V

C40

100n

100n

100n

Y_2

Y_3

Y_4

Y_5

Y_6

Y_7

Y_8

Y_9

A3

A2

A1

A0

A10

BA1

BA0

RAS#

CAS#

WE#

A4

A5

A6

PDEC_D3.3V

C43

C45

100n

100n

PDEC_A1.8V

C68

C65

100n

100n

PDEC_D1.8V

C66

C69

100n

100n

MDEC_D3.3V

96

95

94

93

92

91

90

89

88

87

86

85

R224

84

10K

83

82

81

R59

10K

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

3V3SC +1.8VDEC

AS1117-1V8

IN OUT

C71

10V

C70

47uF

100n

C

C

AV2

AV2

Y/AV1

Y/AV1

TV2

R76

22

R77

22

MDEC_D1.8V

22

R72

22

R73

R62

22

R225

22

R226

22

R227

22

R228

22

R229

22

R230

22

R231

22

TP19

1

1

TP21

TP18

R232

22

1

1

R233

22

TP20

N9

Y_PIP

3

3

PDEC_A1.8V

C31

C30

100n

100n

C27

100n

PDEC_A3.3V

C28

100n

C29

100n

C339

100n

75

R278

3

V_SDRAM2

3

K4S161622D-TI/E

1

VDD1

2

DQ0

3

DQ1

4

VSSQ4

5

DQ2

6

DQ3

7

VDDQ7

8

DQ4

9

DQ5

10

VSSQ10

11

DQ6

12

DQ7

13

VDDQ13

14

LDQM

15

WE

16

CAS

17

RAS

18

CS

19

BA

20

AP

21

A0

22

A1

23

A2

24

A3

25

VDD2526VSS26

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

N33

VI_1_B

VI_1_C

CH1_A33GND

CH1_ASSVDD

CH2_ASSVDD

CH2_A33GND

VI_2_A

VI_2_B

VI_2_C

CH2_A18GND

CH2_A18VDD

A18VDD_REF

A18GND_REF

NC14

NC15

VI_3_A

VI_3_B

VI_3_C

NC19

NC20

VSS50

DQ15

DQ14

VSSQ47

DQ13

DQ12

VDD44

DQ11

DQ10

VSS41

DQ9

DQ8

VDD38

NC37

DQMU

CLK

CKE

NC

A9

A8

A7

A6

A5

A4

10V

C72

47uF

+5V

L58

STBL2012-221

+5V

100n

C343

10K

R269

16V

V23

BC847AW

47uF

C342

470

22K

R275

R272

10K

R270

16V

V24

BC847AW

47uF

C341

470

22K

R276

R273

10K

R271

16V

V25

BC847AW

47uF

C340

470

22K

R277

R274

DEC_Y[0]

DEC_Y[1]

DEC_Y[2]

DEC_Y[3]

DEC_Y[4]

DEC_Y[5]

DEC_Y[6]

DEC_Y[7]

DEC_CLK

DECSDA[3]

DECSDA[2]

DECSDA[1]

DECSDA[0]

DECSDA[10]

DECSDBA0

DECSDRAS#

DECSDCAS#

DECSDWE#

DECSDA[4]

DECSDA[5]

DECSDA[6]

DECSDA[7]

DECSDA[8]

DECSDA[9]

DECSDCLK

DECSDDQM

DECSDD[8]

DECSDD[9]

DECSDD[10]

DECSDD[11]

DECSDD[12]

DECSDD[13]

DECSDD[14]

DECSDD[15]

DECSDD[7]

DECSDD[6]

DECSDD[5]

DECSDD[4]

DECSDD[3]

DECSDD[2]

DECSDD[1]

DECSDD[0]

L59

STBL2012-221

100n

C344

L60

STBL2012-221

100n

C345

TV2

DECSDD[0]

DECSDD[1]

DECSDD[2]

DECSDD[3]

DECSDD[4]

DECSDD[5]

DECSDD[6]

DECSDD[7]

DECSDDQM

DECSDWE#

DECSDCAS#

DECSDRAS#

DECSDBA0

DECSDA[10]

DECSDA[0]

DECSDA[1]

DECSDA[2]

DECSDA[3]

+5V

+5V

+5V

DEC_VS

DEC_HS

TP2

DEC_Y[7-0]

DEC_CLK

14.31818MHz

R55

100K

C35

33p

77

PLL_A18VDD

ALL_A18GND

CH4_A18GND

CH4_A18VDD

24

SVS

73

76

75

74

XTAL2

XTAL1

VS/VBLK

SCL

NSUB

TMS

28

25

26

27

PDEC_A1.8V

78

79

80

VI_1_A

CH1_A18VDD

CH1_A18GND

NC21

NC22

VI_4_A

21

22

23

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

SHS

HS/CS

SDA

72

71

FID

N8

TVP5147PFP

(B9/B8)

INTREQ

29

30

70

C_0

C_1

DGND

DVDD

31

DECSDD[15]

DECSDD[14]

DECSDD[13]

DECSDD[12]

DECSDD[11]

DECSDD[10]

DECSDD[9]

DECSDD[8]

DECSDDQM

DECSDCLK

DECSDA[9]

DECSDA[8]

DECSDA[7]

DECSDA[6]

DECSDA[5]

DECSDA[4]

R60

10K

69

68

67

66

65

C_2

C_3

DGND68

DVDD67

PWDN

RESETB

FSS

AVID

33

34

35

32

36

R61

10K

61

62

64

63

C_4

C_5

IOVDD61

IOGND62

C_6/RED

C_7/GREEN

C_8/BLUE

C_9/FSO

DGND56

DVDD55

IOGND49

IOVDD48

DGND42

DVDD41

IOVDD38

IOGND39

DATACLK

GLCL/I2CA

38

39

40

37

C317

C318

C319

100n

VOUT

100n

100n

L66

STBL2012-501

+12V

C353

100uF

16V

GND-D GND-D

C366

VOUT

10uF

PDEC_D1.8V

PDEC_D3.3V

60

59

58

57

56

55

54

Y_0

53

Y_1

52

Y_2

51

Y_3

50

Y_4

49

48

47

Y_5

46

Y_6

45

Y_7

44

Y_8

43

Y_9

42

41

C315

C316

100n

100n

R286

1K

R283

10K

R285

1K

R284

V27

10K

BC857AW

C314

100n

C367

1u

R287

560K

R67

R68

R69 100

10V

47uF

C313

R288

560

C368

1.5n

版

XOCECO

TITLE:

DWG NO.

22

R74

SV[0]

SV[1]

SV[2]

SV[3]

22

R75

SV[4]

SV[5]

SV[6]

SV[7]

R66

22

100

100

L54

STPB3216-380PT

C370

100n

GND-D

15K

R290

V28

BC857AW

C369

560p

12K

R289

R291

560K

CPU

203-L37R70-01DL

SVCLK

SW_SDA

SW_SCL

/RESET

3V3SC

+5V+12V

+5V

C371

100n

C372

1.5n

10K

R292

GND-D

XIAMEN OVERSEAS CHINESE

ELECTRONIC CO., LTD.

Date:

SVS

5

SHS

5

TP1

SV[7-0]

SVCLK

SW_SDA

SW_SCL

/RESET

R293

10K

R294

HS_COUNTER

100

HS_COUNTER

V29

BC847AW

Video Decoders

REV.

A1.0

Sheet to

2

5

5

1,3

1,3

3,5

5

月

日

年

7

Page 31

2

DEC_Y[7-0]

2

SW_SCL

SW_SDA

2

2,5

/RESET

BUF3.3V

BUFFER_OE

FLIRO[4]

FLIRO[5]

FLIRO[6]

FLIRO[7]

FLIGO[0]

FLIGO[1]

FLIGO[2]

FLIGO[3]

FLIGO[4]

FLIGO[5]

FLIGO[6]

FLIGO[7]

173

DAC_GOUT

172

DAC_AVSSB

C112

100n

C113

22uF

10V

170

171

DAC_BOUT

DAC_AVDDB(3.3)

DAC1.8V

169

DAC_VSS

167

168

DAC_PVSS

DAC_VDD(1.8)

165

166

AVSS_PLL_FE

AVDD_PLL_FE(1.8)

R85

180

C114

100n

162

163

164

AVSS_PLL_BE2

AVSS_PLL_SDI

AVDD_PLL_SDI(1.8)

159

160

161

AVSS_PLL_BE1

AVDD_PLL_BE1(1.8)

AVDD_PLL_BE2(1.8)

SDRAM ADDR3

SDRAM ADDR2

SDRAM ADDR1

100

101

102

RDACOUT

GDACOUT

PLL1.8V

157

158

PLL_PVSS

PLL_PVDD(1.8)

G/Y/Y_OUT_7

G/Y/Y_OUT_6

G/Y/Y_OUT_5

G/Y/Y_OUT_4

G/Y/Y_OUT_3

G/Y/Y_OUT_2

G/Y/Y_OUT_1

G/Y/Y_OUT_0

VDD8(3.3)

R/Y/Pr_OUT_7

R/Y/Pr_OUT_6

R/Y/Pr_OUT_5

R/Y/Pr_OUT_4

R/Y/Pr_OUT_3

R/Y/Pr_OUT_2

VDDcore7(1.8)

R/Y/Pr_OUT_1

R/Y/Pr_OUT_0

B/U/b_OUT_7

B/U/b_OUT_6

B/U/b_OUT_5

B/U/b_OUT_4

B/U/b_OUT_3

B/U/b_OUT_2

VDD7(3.3)

B/U/b_OUT_1

B/U/b_OUT_0

VDDcore6(1.8)

TEST OUT1

TEST OUT0

SDRAM CLKIN

VDD6(3.3)

SDRAM CLKOUT

SDRAM DQM

SDRAM CSN

SDRAM BA0

SDRAM BA1

SDRAM CASN

SDRAM RASN