Page 1

Zynq-7000 AP SoC and

7 Series Devices

Memory Interface

Solutions v4.1

User Guide

UG586 November 30, 2016

Page 2

Send Feedback

Date Version Revision

• Renamed QuestaSim to Questa Advanced Simulator.

QDR II+

• Updated qdr_k_n/p directions in Physical Interface Signals table.

11/30/2016 4.1

10/05/2016 4.1

06/08/2016 4.0

04/06/2016 3.0

• Updated in qdr_k_n/p directions I/O Standards table.

RLDRAM II/RLDRAM 3

• Updated rld_dk_p/n directions in Physical Interface Signals table.

• Updated rld_dk_p/n directions in RLDRAM II I/O Standards and RLDRAM 3 Standards

tables.

• Updated to core version 4.1.

• Updated file name path to _ex/imports in all sections.

DDR3 and DDR2

• Updated Controller Options Page figure.

• Added Number of Bank Machines bullet in the Controller Options section.

DDR3 and DDR2

• Updated Memory Part description in Controller Option section.

• Added app_ecc_single_err[7:0] in Table 1-17: User Interface table.

• Added app_ecc_single_err[7:0] and note in Table 1-56: User Interface for ECC

Operation.

• Updated description in dbg_pi_phase_locked_phy4lanes and

dbg_pi_dqs_found_lanes_phy4lanes in Table 1-74: DDR2/DDR3 Debug Signals.

• Updated to core version 3.0.

• Updated Termination for all sections.

• Updated 1.0 µF capacitor in General Memory Routing Guideline chapter.

DDR3 and DDR2

• Added note in FPGA Options section.

• Added note in Interfacing to the Core section.

• Updated sys_rst descriptions in DDR3 and DD2 Configuration sections.

• Added note in Debug Signals section.

• Updated reset description in General Checks section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 2

UG586 November 30, 2016

www.xilinx.com

Page 3

Date Version Revision

Send Feedback

• Added asynchronous to sys_rst in all sections.

• Added note to RELAXED mode in DDR3/DDR2 and LDDR2 sections.

• Updated code in all Configuration sections

• Added Important jitter note in Pinout Requirements in all sections.

DDR3 and DDR2

• Added Synplify Pro Black Box Testing section.

11/18/2015 2.4

09/30/2015 2.4

06/24/2015 2.3

QDR II+

• Updated DEBUG_PORT Signal Descriptions, Write Init Debug Signal Map, and Read

Stage 1 Debug Signal Map tables.

• Updated Calibration of Read Clock and Data description.

• Updated Write Calibration description.

RLDRAM II/ RLDRAM 3

• Updated Read Stage 1 Debug Signal Map table.

• Updated Calibration of Read Clock and Data description.

• Added CLOCK_DEDICATED_ROUTE Constraints in all sections.

DDR3 and DDR2

• Updated Trace Lengths section.

QDR II+

• Added Termination section.

RLDRAM II/ RLDRAM 3

• Added Termination section.

• Updated Margin Check section.

• Updated Automatic Margin Check section.

• Updated Table 3-33: Debug Port Signals.

LPDDR2

• Updated Trace Lengths section.

Appendix

• Added General Memory Routing Guidelines.

• Added Simulation Flow Using VCS and IES to all sections.

• Added Clocking sections to QDR II+, RLDRAM II/RLDRAM 3, and LPDDR2 chapters.

RLDRAM II/ RLDRAM 3

• Added address/control signal and SSI descriptions in Pinout Requirements section.

• Updated Input Clock Guidelines section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 3

UG586 November 30, 2016

www.xilinx.com

Page 4

Date Version Revision

Send Feedback

• Updated description in all Configuration sections.

• Updated SIM_BYPASS_INIT_CAL.

Chapter 1

• Added description in Setting DDR3 Memory Parameter Option section.

• Added Note to Answer Record: 54025 in Controller Options section.

• Added description to app_rd_data_end in Table 1-17: User Interface.

• Updated Table 1-19: AXI4 Slave Interface Parameters.

• Updated description in AXI4 Slave Interface Signals section.

• Updated Time Division Multiplexing (TDM), Round-Robin, and Read Priority

(RD_PRI_REG) sections.

• Updated GES description in Calibration Times section.

• Updated Fig. 1-50: Clocking Architecture.

• Updated Table 1-87: Memory Controller to Calibration Logic Interface Signals.

• Updated AXI Addressing section.

• Updated Write Path section.

• Updated Fig. 1-84: Command Processing.

04/01/2015 2.3

Continued

• Updated Physical Layer Interface (Non-Memory Controller Design) section.

• Updated CK signal description in Trace Length section.

• Updated Fig. 1-93: Calibration Stages.

• Updated description in Determine the Failing Calibration Stage section.

• Updated Table 1-100: DDR2/DDR3 Debug Signals.

• Updated Table 1-102: Debug Signals of Interest for Write Leveling Calibration.

• Updated Table 1-103: Debug Signals of Interest for MPR Read Leveling Calibration.

• Updated calibration overview in Debugging OCLKDELAYED Calibration Failures

section.

• Updated Debug bullets in Debugging OCLKDELAYED Calibration Failures section.

• Updated Table 1-104: Debug Signals of Interest for OCLKDELAYED Calibration to

Table 1-106: Debug Signals of Interest for Read Leveling Stage 1 Calibration.

• Updated Table 1-108: Calibration Time in Hardware.

• Updated Checking and Varying Read Timing to Manual Window Check sections.

• Updated Calibration Times section.

Chapter 2

• Updated Fig. 2-43: High-Level PHY Block Diagram for a 36-Bit QDR II+ Interface.

• Updated Margin Check and Automated Margin Check sections.

Chapter 3

• Updated description in Interfacing with the Core through the Client Interface section.

Chapter 4

• Corrected app_wdf_data[APP_DATA_WIDTH – 1:0] and

app_wdf_mask[APP_MASK_WIDTH – 1:0] sections.

• Updated Fig. 4-43: Clocking Architecture.

• Updated Read Path section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 4

UG586 November 30, 2016

www.xilinx.com

Page 5

Date Version Revision

Send Feedback

Chapter 1

• Updated description in Round-Robin section.

• Updated RTT_WR in Table 1-92: 7 Series FPGA Memory Solution Configuration

Parameters.

11/19/2014 2.3

10/01/2014 2.2

Continued

• Updated description in Debugging OCLKDELAYED Calibration Failures section.

• Updated Table 1-106: Debug Signals of Interest for OCLKDELAYED Calibration.

•Updated GES time in Calibration Times section.

• Updated bits in left_loss_pb and right_gain_pb in Table 1-109: Debug Signals of

Interest for PRBS Read Leveling Calibration.

• Global update to example design link in Files in example_design/sim Directory tables,

updated links in Simulation Flow Using IES and VCS Script Files section, updated

Simulation Flow Using Vivado Simulator section, and updated Simulation Flow Using

QuestaSim section.

Chapter 1

• Updated Reference Clock description in FPGA Option section.

• Updated C_S_AXI_DATA_WIDTH description in Table 1-19: AXI4 Slave Interface

Parameters.

• Updated Fig. 1-50: Clocking Architecture.

• Updated OCLKDELAYED Calibration section.

• Updated Write Path section.

• Added REF_CLK_MMCM_IODELAY_CTRL in Table 1-92: 7 Series FPGA Memory

Solution Configuration Parameters.

• Added note for nBANK_MACHS in Table 1-93: Embedded 7 Series FPGAs Memory

Solution Configuration Parameters.

• Added row and updated Table 1-94: DDR2/DDR3 SDRAM Memory Interface Solution

Pinout Parameters

• Updated CK/CK# bullet in Trace Length section.

• Updated Table 1-102: DDR2/DDR3 Debug Signals.

• Updated debug signals in Table 1-112: Debug Signals Used for Checking and Varying

Read/Write Timing.

Chapter 2

• Added Bank Sharing Among Controllers section in Design Guideline section.

Chapter 3

• Added Bank Sharing Among Controllers section in Design Guideline section.

Chapter 4

• Updated Figs. 4-57 to 4-59 and Figs. 4-62 to 4-63.

• Updated 2:1 description in Write Path section.

• Updated rules in Termination section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 5

UG586 November 30, 2016

www.xilinx.com

Page 6

Date Version Revision

Send Feedback

Chapter 1

• Added reference to data sheet in Features section.

• Added Important note about Data Mask in Controller Options section.

• Added note in Precharge Policy section.

• Added PRBS_SADDR_ MASK)POS to Table 1-11: Traffic Generator Parameters Set in

the example_top Module.

• Updated IDELAYCTRL frequency in IDELAYCTRL section.

• Updated IDELAY Reference Clock section.

• Updated PRBS Read Leveling section.

• Updated CL description for DDR3 in Table 1-93: Embedded 7 Series FPGAs Memory

Solution Configuration Parameters.

• Updated package length descriptions in Trace Length section.

• Added simulation description in Note in Debugging DDR3/DDR2 Designs.

• Updated description in Debugging PRBS Read Leveling Failures section.

06/04/2014 2.1

Continued

• Updated Table 109: Debug Signals of Interest for PRBS Read Leveling Calibration.

Chapter 2

• Added reference to data sheet in Introduction section.

• Updated package length descriptions in Trace Length Requirements section.

• Added CPT_CLK_SEL_* row in Table 2-11: QDR II+ SRAM Memory Interface Solution

Pinout Parameters.

• Added simulation description in Note in Debugging QDR II+ Designs.

Chapter 3

• Added reference to data sheet in Features section.

• Added note in Memory Controller section.

• Added PRBS_SADDR_ MASK)POS to Table 3-8: Traffic Generator Parameters Set in the

example_top Module.

• Updated rules and package length descriptions in Trace Length Requirements

section.

• Added simulation description in Note in Debugging RLDRAM II and 3 Designs.

Chapter 4

• Added note in Precharge Policy section.

• Added PRBS_SADDR_ MASK)POS to Table 4-11: Traffic Generator Parameters Set in

the example_top Module.

• Updated package length descriptions in Trace Length Requirements section.

• Added simulation description in Note in Read Path section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 6

UG586 November 30, 2016

www.xilinx.com

Page 7

Date Version Revision

Send Feedback

Chapter 1

• Updated book to DQS.

• Updated Table 1-4: Files in example_design/sim Directory.

• Updated file description in Simulation Flow Using IES and VCS Script Files section.

• Added No Buffer description in the System Clock bullet in FPGA Options section.

• Updated mc_data_offset description in Memory Controller to Calibration Logic

Interface Signals table.

• Added MPR read leveling process in Multi-Purpose Register Read Leveling section.

• Updated Temperature Monitor section.

• Added tempmon information in Physical Layer Interface (Non-Memory Controller

Design) section.

• Added description in address and control signals in Termination section for DDR3.

• Added description in address and control signals and updated CKE signal bullet in

Termination section for DDR2.

• Added CK description in Trace Lengths section.

• Added new code constraints for DDR3/DDR2 Configuration sections.

04/02/2014 2.0

• Added Clocking section.

• Updated ocal signals in Table 1-102: DDR2/DDR3 Debug Signals.

Chapter 2

• Added new code constraints in Configuration section.

• Updated Table 2-3: Files in example_design/sim Directory.

• Updated file description in Simulation Flow Using IES and VCS Script Files section.

Chapter 3

• Added new code constraints in Configuration section.

• Updated Table 3-3: Files in example_design/sim Directory.

• Added important note on write and read commands in Interfacing with the Core

through the Client Interface section.

• Updated option for MRS_RD_LATENCY in RLDRAM II Memory Interface Solution

Configurable Parameters table.

• Updated file description in Simulation Flow Using IES and VCS Script Files section.

Chapter 4

• Added new code constraints in Configuration section.

• Updated Table 4-4: Files in example_design/sim Directory.

• Updated file description in Simulation Flow Using IES and VCS Script Files section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 7

UG586 November 30, 2016

www.xilinx.com

Page 8

Date Version Revision

Send Feedback

• Vivado Design Suite release only for MIG v2.0.

Chapter 1

• Added Out of Context content.

• Updated Table 1-4: Modules in example_design/sim Directory.

• Updated <component name>/user_design section.

• Updated Fig. 1-39: Synthesizable Example Design Block Diagram.

• Added simulator flows.

• Added Bits[39:32] to Table 1-15: Debug Status for the Write Transaction.

• Added Bits[39:32] to Table 1-16: Debug Status for the Read Transaction.

• Added OOC description in Customizing the Core section.

• Added ILA trigger settings in Vivado Lab Tools section.

• Added note on read latency in Debug section.

• Updated Chipscope triggers to R in Debug section.

Chapter 2

• Added Out of Context content.

• Updated Table 2-3: Modules in example_design/sim Directory.

• Updated <component name>/user_design section.

• Added OOC description in Customizing the Core section.

• Added simulator flows.

12/18/2013 2.0

• Added ILA trigger settings in Vivado Lab Tools section.

Chapter 3

• Added Out of Context content.

• Updated Table 3-3: Modules in example_design/sim Directory.

• Updated <component name>/user_design section.

• Updated Fig. 3-35: Synthesizable Example Design Block Diagram.

• Added OOC description in Customizing the Core section.

• Added simulator flows.

• Added ILA trigger settings in Vivado Lab Tools section.

• Updated Fig. 3-48 Write Path Block Diagram of the RLDRAM II Interface Solution.

• Added note on read latency in Debug section.

Chapter 4

• Added Out of Context content.

• Updated Table 4-4: Modules in example_design/sim Directory.

• Updated <component name>/user_design section.

• Updated Fig. 4-37: Synthesizable Example Design Block Diagram.

• Added OOC description in Customizing the Core section.

• Added simulator flows.

• Added note on read latency in Debug section.

Chapter 5

• Added Out of Context content.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 8

UG586 November 30, 2016

www.xilinx.com

Page 9

Date Version Revision

Send Feedback

• Vivado Design Suite release only for MIG v2.0.

• Removed ISE content throughout book and updated screenshots to v2.0.

Chapter 1

• Updated Memory Part bullet description.

• Updated Table 1-4 sim.do description and simulation directory.

• Updated Fig. 1-44 7 Series FPGAs MIS.

• Added aresetn in Table 1-20 AXI4 Slave Interface Signals.

• Added Caution note in Single Error and Double Error Reporting section.

• Updated Table 1-77 Memory Interface Commands.

• Updated and added stage 3 tap in OCLKDELAYED Calibration section.

• Added #4 table note to Table 1-91 7 Series FPGA Memory Solution Configuration

Parameters.

• Updated description in app_wdf_mask[APP_MASK_WIDTH - 1:0] section.

• Added Memory Address Mapping description in User Interface section.

• Updated Table 1-106 Debug Signals of Interest for OCLKDELAYED Calibration

Chapter 2

10/02/2013 2.0

• Updated Table 2-3 sim.do description and simulation directory.

• Updated DIFF_HSTL_I in I/O Standards table.

• Updated reference clock descriptions in Clocking Architecture section.

• Added #1 table note to Table 2-11 7 Series FPGAs QDR II+ SRAM Memory Interface

Solution Configurable Parameters. And updated SIM_BYPASS_INIT_CAL.

Chapter 3

• Updated Table 3-3 sim.do description and simulation directory.

• Updated reference clock descriptions in Clocking Architecture section.

• Added #1 table note to Table 3-13 RLDRAM II Memory Interface Solution

Configurable Parameters. And updated SIM_BYPASS_INIT_CAL.

Chapter 4

• Updated Table 4-4 sim.do description and simulation directory.

• Updated Fig. 4-37 7 Series FPGAs MIS.

• Updated Table 4-14 User Interface.

• Added #4 note to Table 4-25 7 Series FPGA Memory Solution Configuration

Parameters.

• Updated description in app_wdf_mask[APP_MASK_WIDTH - 1:0] section.

• Added Memory Address Mapping description in User Interface section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 9

UG586 November 30, 2016

www.xilinx.com

Page 10

Date Version Revision

Send Feedback

• Vivado Design Suite release only for MIG v2.0. Revision number advanced to 2.0 to

align with core version number.

Chapter 1

• Updated ChipScope to Vivado logic analyzer, VIO, and ILA.

• Updated ui_clk and ui_clk_sync_rst descriptions in Table 1-17 User Interface.

• Updated ui_clk and ui_clk_sync_rst descriptions.

• Added Ordering Modes in Reordering section and added modes in Table 1-91.

• Updated ECC enable in AXI4 Slave Interface Block section.

• Updated Read Priority (RD_PRI) section.

• Updated Table 1-19 AXI4 Slave Interface Parameters, C_S_AXI_ADDR_WIDTH value

and descriptions.

• Added Write Priority description.

• Updated PHASER_IN DQSFOUND Calibration section.

•Removed Downsizing Option.

• Added DM in DQ descriptions.

• Added Dynamic Calibration and Periodic Read Behavior section.

• Added Vivado Lab Tools section.

• Added AR 54025 for Vivado.

• Updated Debugging PHASER_IN DQSFOUND Calibration Failures

06/19/2013 2.0

(dbg_pi_dqsfound_err = 1) section.

Chapter 2

• Updated ChipScope to Vivado logic analyzer, VIO, and ILA.

• Added Fixed Latency Mode description in Controller Options section.

• Removed qdr_qvld in Table 2-12 Physical Interface Signals.

• Updated Figure 2-26 Four-Word Burst Length Memory Device Protocol.

• Updated Output Architecture section in Write Path.

• Added Write Calibration section.

•Removed QVLD.

• Updated Table 2-20 Write Init Debug Signal Map.

• Updated Tables 2-21 and 2-22 Read Stage 1 and Stage 2 Debug Signal Map tables.

Chapter 3

• Updated ChipScope to Vivado logic analyzer, VIO, and ILA.

• Removed rld_qvld in Table 3-13 Physical Interface Signals.

• Removed QVLD and QVLD_MAP in Table 3-16 RLDRAM II Memory Interface Solution

Pinout Parameters.

•Removed QVLD.

• Updated descriptions in Manual Pinout Changes section.

• Added new calibration description in Calibration section.

• Updated Table 3-26 Physical Layer Simple Status Bus Description Defined in the

rld_phy_top Module.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 10

UG586 November 30, 2016

www.xilinx.com

Page 11

Date Version Revision

Send Feedback

• Updated Table 3-27 DEBUG_PORT Signal with

dbg_rd_stage1_rtr_error[N_DATA_LANES - 1:0] and

dbg_rd_stage1_error[N_DATA_LANES - 1:0].

• Updated Tables 3-31 and 3-32 Read Stage 1 and Stage 2 Debug Signal Map tables.

• Added Fig. 3-36 Calibration Flow Diagram and Fig. 3-37 Read Level Stage 1.

• Added description to Data Alignment and Valid Generation section.

• Updated description and added Figs. 3-38 to 3-43 in Write Calibration section.

• Added Write Calibration Debug Map section.

Continued

03/20/2013 1.9

Chapter 4

• Updated ChipScope to Vivado logic analyzer, VIO, and ILA.

• Updated ui_clk and ui_clk_sync_rst descriptions in Table 4-14 User Interface.

• Updated ui_clk and ui_clk_sync_rst descriptions.

• Added Ordering Modes in Reordering section and added modes in Table 4-25.

• Added DM in DQ descriptions.

• Added Termination description in LPDDR2 Pinout Examples section.

Chapter 6

• Added Upgrading the ISE/CORE Generator MIG Core in Vivado section.

• ISE 14.5 and Vivado Design Suite 2013.1 releases for MIG v1.9 and v1.9a.

Chapter 1

• Added Memory Part frequency in Controller Options section.

• Added No Buffer option description in FPGA Options section.

• Added pinout description in Verify Pin Changes and Update Design section.

• Updated Fig. 1-15 Setting Memory Mode Options.

• Updated Fig. 1-16 FPGA Options.

• Updated Fig. 1-30 7 Series FPGAs Memory Interface Solution to User’s FPGA Logic

• Added ECC description in AXI4 Slave Interface Block section.

• Updated Table 1-91 7 Series FPGA Memory Solution Configuration Parameters.

• Updated Table 1-92 Embedded 7 Series FPGAs Memory Solution Configuration

Parameters.

• Updated Table 1-93 DDR2/DDR3 SDRAM Memory Interface Solution Pinout

Parameters.

• Added description in Verifying the Simulation Using the Example Design section.

• Reworked Design Guidelines DDR3 SDRAM section.

• Added new debug section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 11

UG586 November 30, 2016

www.xilinx.com

Page 12

Date Version Revision

Send Feedback

Chapter 2

• Added No Buffer option description in FPGA Options section.

• Added pinout description in Verify Pin Changes and Update Design section.

• Updated Fig. 2-15 FPGA Options.

• Updated REFCLK_FREQ and RST_ACT_LOW in Table 2-13 7 Series FPGAs QDR II+

SRAM Memory Interface Solution Configurable Parameters

• Updated Table 2-14 QDR II+ SRAM Memory Interface Solution Pinout Parameters.

• Added description in Verifying the Simulation Using the Example Design section.

Chapter 3

• Added No Buffer option description in FPGA Options section.

Continued

• Updated Fig. 3-14 FPGA Options.

• Added Verify Pin Changes and Update Design section.

• Updated nCK_PER_CLK in Table 3-10 Traffic Generator Parameters Set in the

example_top Module

• Updated Table 3-15 RLDRAM II Memory Interface Solution Configurable Parameters.

• Updated Table 3-16 RLDRAM II Memory Interface Solution Pinout Parameters.

• Added description in Verifying the Simulation Using the Example Design section.

Chapter 4

• Added new LPDDR2 SDRAM section.

Chapter 6

• Updated to new GUIs.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 12

UG586 November 30, 2016

www.xilinx.com

Page 13

Date Version Revision

Send Feedback

• ISE 14.4 and Vivado 2012.4 Design Suite releases for MIG v1.8.

Chapter 1

• Updated Table 1-2 to 1-9 with new table note and.v name.

• Updated Fig. 1-16 FPGA Options GUI.

• Added XADC Instantiation bullet.

• Added description to sim.do in Table 1-4.

• Updated Table 1-11 DATA_PATTERN to 0xA.

• Updated Table 1-13 vio_data_mode_value[3:0] to 0xA.

• Updated description in Setting Up for Simulation.

• Added description to EDK Clocking.

• Updated ui_clk and ui_clk_sync_rst in Table 1-17.

• Added description in Internal (FPGA) Logic Clock.

• Added TEMP_MON_CONTROL to Table 1-91.

• Added DATA_IO_IDLE_PWRDWN and CA_MIRROR to Table 1-92.

• Added HP bank description in Bank and Pin Selection Guides for DDR3 Designs.

• Added DDR3 SDRAM interface description to Configuration.

• Added HP bank description in Bank and Pin Selection Guides for DDR2 Designs.

• Added DDR2 SDRAM interface description to Configuration.

12/18/2012 1.8

Chapter 2

• Updated Table 2-2 and 2-7 to 2-8 with new table note and.v name.

• Added description to sim.do in Table 2-3.

• Updated descriptions and added Fig 2-26 to Clocking Architecture.

• Updated description in Write Path Output Architecture.

• Updated descriptions in Trace Length Requirements.

• Added QDRII description in Configuration.

• Added description to Verifying the Simulation Using the Example Design.

• Added Margin Check and Automated Margin Check sections.

Chapter 3

• Updated Table 3-2 and 3-6 to 3-8 with new table note and.v name.

• Added description to sim.do in Table 3-3.

• Updated Table 3-10 DATA_PATTERN to 0xA.

• Updated descriptions and added Fig 3-30 to Clocking Architecture.

• Updated descriptions in Trace Length Requirements.

• Added descriptions in RLDRAM II.

• Added RLDRAM II description in Configuration.

• Added description to Verifying the Simulation Using the Example Design.

• Added Debug section.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 13

UG586 November 30, 2016

www.xilinx.com

Page 14

Date Version Revision

Send Feedback

• MIG 1.7 release. Updated ISE Design Suite version to 14.3.

• Chapter 1: Added AXI4-Lite Slave Control/Status Register Interface Block section.

Updated figures (1-32 and 1-37) and added PRBS and Temperature Monitor sections.

Added CLKIN_PERIOD to USE_DM_PORT parameters in Table 1-37. Updated Table

1-38 PHY0_BITLANES description.

• Chapter 2: Added CLKIN_PERIOD to DIVCLK_DIVIDE parameters in Table 2-13.

10/16/2012 1.7

07/25/2012 1.6

06/13/2012 1.5

• Chapter 3: Added RLDRAM 3 content throughout. Updated/added figures (3-10,

3-13, 3-23 to 3-32, 3-36 to 3-37, 3-40 to 3-41, 3-45 to 3-47, and 3-50). Added

mem_ck_lock_complete parameter in Table 3-11. Added CLKOUT0_PHASE parameter

in Table 3-15. Updated descriptions in Table 3-16 and added Table 3-28. Updated

Table 3-29 user_cmd signal. Updated Table 3-31 and 3-34 descriptions. Added

Debugging Write Calibration section.

• Chapter 4: Added System Clock Sharing section

• Chapter 5: Updated figures (5-15, 5-17 to 5-20), updated steps in Getting Started with

Vivado – MIG IP Generation

• MIG 1.6 release. Updated ISE Design Suite version to 14.2. Updated GUI screen

captures throughout document.

• Chapter 1: Added No Buffer, Use System Clock, and Sample Data Depth in FPGA

Options, page 36. Changed the parameters nCK_PER_CLK, tZQI, SYSCLK_TYPE,

REFCLK_TYPE, and APP_DATA_WIDTH. Added bulleted item about multiple CK

outputs to Bank and Pin Selection Guides for DDR3 Designs, page 186. Updated Trace

Lengths, page 191 and Termination, page 200.

• Chapter 2: Added No Buffer, Use System Clock, and Sample Data Depth in FPGA

Options, page 282. Changed the parameters SYSCLK_TYPE and REFCLK_TYPE.

• Chapter 3: Added No Buffer, Use System Clock, and Sample Data Depth in FPGA

Options, page 282. Changed the parameters SYSCLK_TYPE and REFCLK_TYPE.

• Chapter 6: Added new chapter on migrating to Vivado Design Suite.

Revised the recommended total electrical delay on CK/CK# relative to DQS/DQS# on

page 191.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 14

UG586 November 30, 2016

www.xilinx.com

Page 15

Date Version Revision

Send Feedback

• MIG 1.5 release. Updated ISE Design Suite version to 14.1. Updated GUI screen

captures throughout document. Replaced IODELAYCTRL with IDELAYCTRL

throughout.

• Chapter 1: Added I/O Power Reduction option to FPGA Options. Revised I/O

standards for sys_rst option in Bank Selection. Added Creating ISE Project Navigator

Flow for MIG Example Design, Power-Saving Features, Multi-Purpose Register Read

Leveling, OCLKDELAYED Calibration, Upsizing, and External Vref sections. Changed

bits [16:15] to from Rank Count to Reserved in the PHY Control word. Revised

maximum setting of NUM_DQ_PINS in Table 1-11. Revised Figure 1-55 flowchart.

Removed RankSel[1:0] from Figure 1-56 and Figure 1-58. Added mc_odt and mc_cke

to Table 1-87. Replaced AXI Addressing. Updated REFCLK_FREQ, RANK_WIDTH, and

WRLVL in Table 1-92. Added DATA_IO_PRIM_TYPE to Table 1-93. Added bullet about

04/24/2012 1.4

01/18/2012 1.3

DQS pins to Bank and Pin Selection Guides for DDR3 Designs. Changed DIFF_SSTL_15

to DIFF_SSTL18_II and SSTL15 to SSTL18_II.

• Chapter 2: Changed DIFF_SSTL_15 to DIFF_HSTL_I and SSTL15 to HSTL_I. Revised I/O

standards for sys_rst option in System Pins Selection. Revised the PHY_BITLANE

parameters in Table 2-11. Added System Clock, PLL Location, and Constraints and

Configuration sections.

• Chapter 3: Changed DIFF_SSTL_15 to DIFF_HSTL_I and SSTL15 to HSTL_I. to Revised

I/O standards for sys_rst option in System Pins Selection. Added the Write

Calibration, System Clock, PLL Location, and Constraints, and Configuration sections.

Revised the PHY_BITLANE parameters in Table 3-15. In Table 3-28, added

dbg_wrcal_sel_stg[1:0], dbg_wrcal[63:0], dbg_wrcal_done[2:0],

dbg_wrcal_po_first_edge[5:0], dbg_wrcal_po_second_edge[5:0], and

dbg_wrcal_po_final[5:0].

• MIG 1.4 release. Updated ISE Design Suite version to 13.4. Updated GUI screen

captures throughout document.

• Chapter 1: Added support for DDR2 SDRAM. Added option 3 to MIG Output Options.

Added EDK Clocking. Added Replaced Figure 1-41 and Figure 1-69.

• Chapter 2: Removed Input Clock Period option from Controller Options. Added

Memory Options. Added Reference Clock option to FPGA Options. Updated Debug

Signals.

• Chapter 3: Removed Input Clock Period option from Controller Options. Added Input

Clock Period option to Memory Options. Added Reference Clock option to FPGA

Options. Added Debugging RLDRAM II and RLDRAM 3 Designs.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 15

UG586 November 30, 2016

www.xilinx.com

Page 16

Date Version Revision

Send Feedback

• MIG 1.3 release. Updated ISE Design Suite version to 13.3.

• Chapter 1: Added step 2 to MIG Output Options, page 26. Added note about

optional use of the memory controller to Controller Options, page 30. Added

arbitration scheme to AXI Parameter Options, page 33. Added description of DCI

Cascade under Figure 1-23. Updated text about devices with SSI technology and SLRs

on page 41 and page 187. Changed error to tg_compare_error on page 42. Replaced

Table 1-8. Added qdr_wr_cmd_o, vio_fixed_instr_value, vio_fixed_bl_value,

vio_pause_traffic, and vio_data_mask_gen signals to Table 1-13. Added signals to the

User Interface in Figure 1-49 and Figure 1-51. Added app_sr_req, app_sr_active,

app_ref_req, app_ref_ack, app_zq_req, and app_zq_ack signals to Table 1-17. Added

app_wdf_rdy, app_ref_req, app_ref_ack, app_zq_req, app_zq_ack, Read Priority with

Starve Limit (RD_PRI_REG_STARVE_LIMIT), Native Interface Maintenance Command

Signals, User Refresh, and User ZQ sections. Added C_RD_WR_ARB_ALGORITHM to

Table 1-19. Updated fields in Table 1-84, changed Hi Index (Rank) to Rank Count, and

added CAS slot field. Updated AXI Addressing and Physical Layer Interface

(Non-Memory Controller Design). Added Figure 1-75 through Figure 1-77 in Write

Path. In Table 1-92, removed DISABLED option from RTT_NOM for DDR3_SDRAM,

changed RTT_NOM to RTT_WR in RTT_WR, updated SIM_BYPASS_INIT_CAL, and

updated table note 2. In Table 1-93, updated tZQI and added USER_REFRESH. Added

Table 1-94. In Configuration, updated constraints example and removed paragraph

10/19/2011 1.2

about SCL and SDA.

• Chapter 2: Added step 2 to MIG Output Options, page 275. Added Input Clock Period

description in Controller Options, page 279. Added Debug Signals Control and

Internal Vref Selection options to FPGA Options, page 282. Added I/O Planning

Options, page 285. In System Pins Selection, page 288, changed cal_done signal to

init_calib_complete and error signal to tg_compare_error. Replaced Table 2-2.

Changed file names in Table 2-5. Updated signal names in Figure 2-38, Figure 2-39,

and Figure 2-40. Updated signal names in Table 2-7. Added CPT_CLK_CQ_ONLY and

updated value for SIM_BYPASS_INIT_CAL in Table 2-10. Added Table 2-11. Updated

pinout rules in Pinout Requirements, page 337. Added paragraph about DCI and

IN_TERM after Table 2-12. Added Debugging QDR II+ SRAM Designs, page 340.

• Chapter 3: Added step 2 to MIG Output Options, page 375. Added Input Clock Period

description in Controller Options. Added Debug Signals Control and Internal Vref

Selection options to FPGA Options, page 382. In System Pins Selection, changed

cal_done signal to init_calib_complete and error signal to tg_compare_error. Changed

file names in Table 3-6. Removed Table 3-12, which contained Reserved signals not

used. Added rst_phaser_ref to Table 3-11. Removed PHY-Only Interface section. In

Table 3-14, added RLD_ADDR_WIDTH, MEM_TYPE, CLKIN_PERIOD, and SIMULATION,

and renamed CLKFBOUT_MULT, CLKOUT0_DIVIDE, CLKOUT1_DIVIDE,

CLKOUT2_DIVIDE, and CLKOUT3_DIVIDE. Updated Table 3-15. Added paragraph

about DCI and IN_TERM after Table 3-24.

• Added Chapter 5, Multicontroller Design.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 16

UG586 November 30, 2016

www.xilinx.com

Page 17

Date Version Revision

Send Feedback

• MIG 1.2 release. Updated ISE Design Suite version to 13.2. Updated GUI screen

captures throughout document.

• Chapter 1: Added Verify Pin Changes and Update Design, Simulating the Example

Design (for Designs with the AXI4 Interface), Error Correcting Code, and DDR3 Pinout

Examples sections. Added paragraph about SLRs to Pin Compatible FPGAs, page 27.

Added Input Clock Period and PHY to Controller bullets in Controller Options,

page 30. To Setting DDR3 Memory Parameter Option, page 35, indicated that DDR3

SDRAM supports burst lengths of 8. Added Internal Termination for High Range

Banks option under Figure 1-23. Added bulleted item about Pin/Bank selection mode

on page 39. Added notes about chip select and data mask options on page 74. Added

app_correct_en_i to Table 1-17. Added three command types to Command Path,

06/22/2011 1.1

03/01/2011 1.0 Initial Xilinx release.

page 134. Added phy_mc_ctl_full, phy_mc_cmd_full, and phy_mc_data_full signals to

Table 1-87. Added paragraph about FIFOs at the end of Physical Layer Interface

(Non-Memory Controller Design), page 168. Updated the description and options for

DATA_BUF_ADDR_WIDTH in Table 1-93. Added bullet about SLRs to Bank and Pin

Selection Guides for DDR3 Designs, page 186. Added LVCMOS15 and DIFF_SSTL15

I/O standards to Configuration, page 194. Changed resistor values in Figure 1-88,

Figure 1-89, and Figure 1-90. Changed resistor values in FPGA DCI or IN_TERM

column in Table 1-95.

• Chapter 2: Added the Verify Pin Changes and Update Design and Output Path

sections. Revised latency mode description on page 280. Added bulleted item about

Pin/Bank selection mode on page 285. Added Internal Termination for High Range

Banks option under Figure 2-22. Updated Implementation Details, page 324.

• Chapter 3: Added new chapter on RLDRAM II.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 17

UG586 November 30, 2016

www.xilinx.com

Page 18

Table of Contents

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Using MIG in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Synplify Pro Black Box Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Core Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Designing with the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Interfacing to the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Customizing the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

Design Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Debugging DDR3/DDR2 Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

Chapter 2: QDR II+ Memory Interface Solution

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Using MIG in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

Core Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

Customizing the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

Design Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342

Debugging QDR II+ SRAM Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 18

UG586 November 30, 2016

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

Using MIG in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

Core Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 424

Customizing the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 458

Design Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

Debugging RLDRAM II and RLDRAM 3 Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 481

Chapter 4: LPDDR2 SDRAM Memory Interface Solution

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

Using MIG in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

Core Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 575

www.xilinx.com

Page 19

Designing with the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 611

Send Feedback

Interfacing to the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 611

Customizing the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 621

Design Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 631

Chapter 5: Multicontroller Design

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 644

Using MIG in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 645

Chapter 6: Upgrading the ISE/CORE Generator MIG Core in Vivado

Appendix A: General Memory Routing Guidelines

Appendix B: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 677

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 677

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 678

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 19

UG586 November 30, 2016

www.xilinx.com

Page 20

DDR3 and DDR2 SDRAM Memory

Send Feedback

Interface Solution

Introduction

The Xilinx® 7 series FPGAs Memory Interface Solutions (MIS) core is a combined

pre-engineered controller and physical layer (PHY) for interfacing 7 series FPGA user

designs and AMBA

DDR2 SDRAM devices. This user guide provides information about using, customizing, and

simulating a LogiCORE™ IP DDR3 or DDR2 SDRAM interface core for 7 series FPGAs. The

user guide describes the core architecture and provides details on customizing and

interfacing to the core.

®

Advanced eXtensible Interface (AXI4) slave interfaces to DDR3 and

Chapter 1

IMPORTANT: Memory Interface Solutions v4.1 only supports the Vivado

Design Suite is not supported in this version.

®

Design Suite. The ISE®

Features

Enhancements to the Xilinx 7 series FPGA memory interface solutions from earlier memory

interface solution device families include:

• Higher performance.

• New hardware blocks used in the physical layer: PHASER_IN and PHASER_OUT, PHY

control block, and I/O FIFOs (see Core Architecture, page 90).

• Pinout rules changed due to the hardware blocks (see Design Guidelines, page 192).

• Controller and user interface operate at 1/4 the memory clock frequency.

For a full list of supported features, see the Zynq-7000 AP SoC and 7 Series FPGAs Memory

Interface Solutions Data Sheet (DS176) [Ref 1].

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 20

UG586 November 30, 2016

www.xilinx.com

Page 21

X-Ref Target - Figure 1-1

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Using MIG in the Vivado Design Suite

This section provides the steps to generate the Memory Interface Generator (MIG) IP core

using the Vivado Design Suite and run implementation.

1. Start the Vivado Design Suite (see Figure 1-1).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 21

UG586 November 30, 2016

Figure 1-1: Vivado Design Suite

2. To create a new project, click the Create New Project option shown in Figure 1-1 to

open the page as shown in Figure 1-2.

www.xilinx.com

Page 22

X-Ref Target - Figure 1-2

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-2: Create a New Vivado Tool Project

3. Click Next to proceed to the Project Name page (Figure 1-3). Enter the Project Name

and Project Location. Based on the details provided, the project is saved in the

directory.

X-Ref Target - Figure 1-3

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 22

UG586 November 30, 2016

Figure 1-3: Project Name

www.xilinx.com

Page 23

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

4. Click Next to proceed to the Project Type page (Figure 1-4). Select the Project Type as

RTL Project because MIG deliverables are RTL files.

X-Ref Target - Figure 1-4

Figure 1-4: Project Type

5. Click Next to proceed to the Add Sources page (Figure 1-5). RTL files can be added to

the project in this page. If the project was not created earlier, proceed to the next page.

X-Ref Target - Figure 1-5

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 23

UG586 November 30, 2016

Figure 1-5: Add Sources

www.xilinx.com

Page 24

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

6. Click Next to open the Add Existing IP (Optional) page (Figure 1-6). If the IP is already

created, the XCI file generated by the IP can be added to the project and the previous

created IP files are automatically added to the project. If the IP was not created earlier,

proceed to the next page.

X-Ref Target - Figure 1-6

Figure 1-6: Add Existing IP (Optional)

7. Click Next to open the Add Constraints (Optional) page (Figure 1-7). If the constraints

file exists in the repository, it can be added to the project. Proceed to the next page if

the constraints file does not exist.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 24

UG586 November 30, 2016

www.xilinx.com

Page 25

X-Ref Target - Figure 1-7

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-7: Add Constraints (Optional)

8. Click Next to proceed to the Default Part page (Figure 1-8) where the device that

needs to be targeted can be selected. The Default Part page appears as shown in

Figure 1-8.

X-Ref Target - Figure 1-8

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 25

UG586 November 30, 2016

Figure 1-8: Default Part (Default Window)

www.xilinx.com

Page 26

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

Select the target Family, Package, and Speed Grade. The valid devices are displayed in

the same page, and the device can be selected based on the targeted device

(Figure 1-9).

X-Ref Target - Figure 1-9

Figure 1-9: Default Part (Customized Window)

Apart from selecting the parts by using Parts option, parts can be selected by choosing

the Boards option, which brings up the evaluation boards supported by Xilinx

(Figure 1-10). With this option, design can be targeted for the various evaluation

boards. If the XCI file of an existing IP was selected in an earlier step, the same part

should be selected here.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 26

UG586 November 30, 2016

www.xilinx.com

Page 27

X-Ref Target - Figure 1-10

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-10: Default Part Boards Option

9. Click Next to open the New Project Summary page (Figure 1-11). This includes the

summary of selected project details.

X-Ref Target - Figure 1-11

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 27

UG586 November 30, 2016

Figure 1-11: New Project Summary

10. Click Finish to complete the project creation.

www.xilinx.com

Page 28

X-Ref Target - Figure 1-12

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

11. Click IP Catalog on the Project Manager window to open the IP catalog window. The

Vivado IP catalog window appears on the right side panel (see Figure 1-12, highlighted

in a red circle).

12. The MIG tool exists in the Memories & Storage Elements > Memory Interface

Generators section of the IP catalog window (Figure 1-12) or you can search from the

Search tool bar for the string “MIG.”

Figure 1-12: IP Catalog Window – Memory Interface Generator

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 28

UG586 November 30, 2016

www.xilinx.com

Page 29

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

13. Select MIG 7 Series to open the MIG tool (Figure 1-13).

X-Ref Target - Figure 1-13

Figure 1-13: 7 Series FPGAs Memory Interface Generator FPGA Front Page

14. Click Next to display the Output Options page.

Customizing and Generating the Core

CAUTION! The Windows operating system has a 260-character limit for path lengths, which can affect

the Vivado tools. To avoid this issue, use the shortest possible names and directory locations when

creating projects, defining IP or managed IP projects, and creating block designs.

MIG Output Options

1. Select the Create Design to create a new Memory Controller design. Enter a component

name in the Component Name field (Figure 1-14).

2. Choose the number of controllers to be generated. This option determines the

replication of further pages.

3. DDR2 and DDR3 SDRAM designs support the memory-mapped AXI4 interface. The AXI4

interface is implemented in Verilog only. If an AXI4 interface is required, select the

language as “Verilog” in the Vivado Design Suite before invoking the MIG tool. If the

AXI4 interface is not selected, the user interface (UI) is the primary interface.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 29

UG586 November 30, 2016

www.xilinx.com

Page 30

X-Ref Target - Figure 1-14

UG586_c1_09_120311

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-14: MIG Output Options

MIG outputs are generated with the folder name <component name>.

IMPORTANT: Only alphanumeric characters can be used for <component name>. Special characters

cannot be used. This name should always start with an alphabetical character and can end with an

alphanumeric character.

When invoked from Xilinx Platform Studio (XPS), the component name is corrected to be

the IP instance name from XPS.

4. Click Next to display the Pin Compatible FPGAs page.

Pin Compatible FPGAs

The Pin Compatible FPGAs page lists FPGAs in the selected family having the same

package. If the generated pinout from the MIG tool needs to be compatible with any of

these other FPGAs, this option should be used to select the FPGAs with which the pinout

has to be compatible (Figure 1-15).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 30

UG586 November 30, 2016

www.xilinx.com

Page 31

X-Ref Target - Figure 1-15

UG586_c1_10_110610

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Xilinx 7 series devices using stacked silicon interconnect (SSI) technology have super logic

regions (SLRs). Memory interfaces cannot span across SLRs. If the device selected or a

compatible device that is selected has SLRs, the MIG tool ensures that the interface does

not cross SLR boundaries.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 31

UG586 November 30, 2016

Figure 1-15: Pin-Compatible 7 Series FPGAs

1. Select any of the compatible FPGAs in the list. Only the common pins between the target

and selected FPGAs are used by the MIG tool. The name in the text box signifies the

target FPGA selected.

2. Click Next to display the Memory Selection page.

www.xilinx.com

Page 32

X-Ref Target - Figure 1-16

UG586_c1_11_120311

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Creating 7 Series FPGA DDR3 Memory Controller Block Design

Memory Selection

This page displays all memory types that are supported by the selected FPGA family.

1. Select the DDR3 SDRAM controller type.

2. Click Next to display the Controller Options page (Figure 1-16).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 32

UG586 November 30, 2016

Figure 1-16: Memory Type and Controller Selection

www.xilinx.com

Page 33

X-Ref Target - Figure 1-17

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Controller Options

This page shows the various controller options that can be selected (Figure 1-17).

TIP: The use of the Memory Controller is optional. The Physical Layer, or PHY, can be used without the

Memory Controller. The Memory Controller RTL is always generated by the MIG tool, but this output

need not be used. See Physical Layer Interface (Non-Memory Controller Design), page 174 for more

information. Controller-only settings such as ORDERING are not needed in this case, and the defaults

can be used. Settings pertaining to the PHY, such as the Clock Period, are used to set the PHY

parameters appropriately.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 33

UG586 November 30, 2016

Figure 1-17: Controller Options Page

If the design has multiple controllers, the controller options page is repeated for each of the

controllers. This page is partitioned into a maximum of nine sections. The number of

partitions depends on the type of memory selected. The controller options page also

contains these pull-down menus to modify different features of the design:

www.xilinx.com

Page 34

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

• Frequency – This feature indicates the operating frequency for all of the controllers.

The frequency block is limited by factors such as the selected FPGA and device speed

grade.

• PHY to Controller Clock Ratio – This feature determines the ratio of the physical layer

(memory) clock frequency to the controller and user interface clock frequency. The 2:1

ratio lowers the maximum memory interface frequency due to FPGA logic timing

limitations. The user interface data bus width of the 2:1 ratio is four times the width of

the physical memory interface width, while the bus width of the 4:1 ratio is eight times

the physical memory interface width. The 2:1 ratio has lower latency. The 4:1 ratio is

necessary for the highest data rates.

• VCCAUX_IO – Set based on the period/frequency setting. 2.0V is required at the

highest frequency settings in the High Performance column. The MIG tool

automatically selects 2.0V when required. Either 1.8 or 2.0V can be used at lower

frequencies. Groups of banks share the VCCAUX_IO supply. For more information, see

the 7 Series FPGAs SelectIO™ Resources User Guide (UG471) [Ref 2] and the 7 Series

FPGAs Packaging and Pinout Specification (UG475) [Ref 3].

• Memory Type – This feature selects the type of memory parts used in the design.

• Memory Part – This option selects a memory part for the design. Selections can be

made from the list or a new part can be created.

Note:

For a complete list of memory parts available, see Answer Record: 54025.

• Data Width – The data width value can be selected here based on the memory type

selected earlier. The list shows all supported data widths for the selected part. One of

the data widths can be selected. These values are generally multiples of the individual

device data widths. In some cases, the width might not be an exact multiple. For

example, 16 bits is the default data width for x16 components, but eight bits is also a

valid value.

• Data Mask – This option allocates data mask pins when selected. This should be

deselected to deallocate data mask pins and increase pin efficiency. Also, this is

disabled for memory parts that do not support data mask.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 34

UG586 November 30, 2016

www.xilinx.com

Page 35

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

UG586_c1_20_091410

Send Feedback

IMPORTANT: The Data Mask (DM) option is always selected for AXI designs and is grayed out (you

cannot select it). For AXI interfaces, Read Modify Write (RMW) is supported and for RMW to mask

certain bytes of Data Mask bits should be present. Therefore, the DM is always enabled for AXI interface

designs. This is the case for all data widths except 72-bit.

For 72-bit interfaces, Error Correcting Code (ECC) is enabled and DM is deselected and grayed out. If

DM is enabled for 72-bit designs, computing ECC is not compatible, therefore DM is disabled for 72-bit

designs.

• Number of Bank Machines – The list shows the number of bank machines that are

supported for the selected design configuration.

• Ordering – This feature allows the Memory Controller to reorder commands to

improve the memory bus efficiency.

• Memory Details – The bottom of the Controller Options page (Figure 1-17) displays

the details for the selected memory configuration (Figure 1-18).

X-Ref Target - Figure 1-18

Figure 1-18: Memory Details

Create Custom Part

1. On the Controller Options page select the appropriate frequency. Either use the spin

box or enter a valid value using the keyboard. Values entered are restricted based on the

minimum and maximum frequencies supported.

2. Select the appropriate memory part from the list. If the required part or its equivalent is

unavailable, a new memory part can be created. To create a custom part, click the

Create Custom Part below the Memory Part pull-down menu. A new page appears, as

shown in Figure 1-19.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 35

UG586 November 30, 2016

www.xilinx.com

Page 36

X-Ref Target - Figure 1-19

UG586_c1_21_110610

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-19: Create Custom Part

The Create Custom Part page includes all the specifications of the memory component

selected in the Select Base Part pull-down menu.

3. Enter the appropriate memory part name in the text box.

4. Select the suitable base part from the Select Base Part list.

5. Edit the value column as needed.

6. Select the suitable values from the Row, Column, and Bank options as per the

requirements.

7. After editing the required fields, click Save. The new part is saved with the selected

name. This new part is added in the Memory Parts list on the Controller Options page.

It is also saved into the database for reuse and to produce the design.

8. Click Next to display the Memory Options page (or the AXI Parameter Options page

if AXI Enable is checked on the Memory Type selection page).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 36

UG586 November 30, 2016

www.xilinx.com

Page 37

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

AXI Parameter Options

This feature allows the selection of AXI parameters for the controller (Figure 1-20). These

are standard AXI parameters or parameters specific to the AXI4 interface. Details are

available in the ARM

These parameters specific to the AXI4 interface logic can be configured:

• Address Width and AXI ID Width – When invoked from XPS, address width and ID

width settings are automatically set by XPS so the options are not shown.

• Base and High Address – Sets the system address space allocated to the Memory

Controller. These values must be a power of 2 with a size of at least 4 KB, and the base

address must be aligned to the size of the memory space.

• Narrow Burst Support – Deselecting this option allows the AXI4 interface to remove

logic to handle AXI narrow bursts to save resources and improving timing. XPS

normally auto-calculates whether narrow burst support can be disabled based on the

known behavior of connected AXI masters.

• Arbitration Scheme – Selects the arbitration scheme between read and write address

channels.

®

AMBA® specifications [Ref 4].

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 37

UG586 November 30, 2016

www.xilinx.com

Page 38

X-Ref Target - Figure 1-20

UG586_c1_22_090511

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-20: Setting AXI Parameter Options

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 38

UG586 November 30, 2016

www.xilinx.com

Page 39

X-Ref Target - Figure 1-21

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Setting DDR3 Memory Parameter Option

This feature allows the selection of various memory mode register values, as supported by

the controller specification (Figure 1-21).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 39

UG586 November 30, 2016

Figure 1-21: Setting Memory Mode Options

The mode register value is loaded into the load mode register during initialization. Only

burst length 8 (BL8) is supported for DDR2 and DDR3 SDRAM.

The Output Driver Impedance Control sets the output driver impedance on the DRAM.

The selections listed are determined by specific DRAM chosen. RZQ is 240Ω. For example,

if RZQ/6 is chosen, the output drive impedance is 40Ω. For more information, consult the

memory vendor data sheet.

The DDR2 SDRAM interface has a separate option to select the number of memory clocks

called Memory Clock Selection. Each component has a Number of Memory Clocks

setting, and the maximum number of clocks allowed is four.

www.xilinx.com

Page 40

X-Ref Target - Figure 1-22

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

The desired input clock period is selected from the list. These values are determined by the

memory clock period chosen and the allowable limits of the parameters. See Design

Guidelines, page 192 for more information on the PLL parameter limits.

Select Additional Clocks option appears for AXI interface designs only. Selection is

allowed for up to five additional clocks which are generated from the same MMCM that

generates UI_CLK.

IMPORTANT: The Select Additional Clocks option appears in Vivado IP integrator flow only.

Click Next to display the FPGA Options page.

FPGA Options

Figure 1-22 shows the FPGA Options page.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 40

UG586 November 30, 2016

Figure 1-22: FPGA Options

www.xilinx.com

Page 41

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

• System Clock – This option selects the clock type (Single-Ended, Differential, or No

Buffer) for the sys_clk signal pair. When the No Buffer option is selected, IBUF

primitives are not instantiated in RTL code and pins are not allocated for the system

clock.

If the designs generated from MIG for the No Buffer option are implemented without

performing changes, designs can fail in implementation due to IBUFs not instantiated

for the sys_clk_i signal. So for No Buffer scenarios, sys_clk_i signal needs to be

connected to an internal clock.

The No Buffer option must only be selected for designs that already have a system

input clock assigned that meets all rules specified in the Clocking, page 210.

• Reference Clock – This option selects the clock type (Single-Ended, Differential, No

Buffer, or Use System Clock) for the clk_ref signal pair. The Use System Clock option

appears when the input frequency is between 199 and 201 MHz (that is, the Input Clock

Period is between 5,025 ps (199 MHz) and 4,975 ps (201 MHz). The reference clock

frequency is based on the data rate and note that an MMCM is added to create the

appropriate ref_clk frequency above 1,333 Mb/s. When the No Buffer option is

selected, IBUF primitives are not instantiated in RTL code and pins are not allocated for

the reference clock.

If the designs generated from MIG for the No Buffer option are implemented without

performing changes, designs can fail in implementation due to IBUFs not instantiated

for the ref_clk_i signal. So for No Buffer scenarios, ref_clk_i signal needs to be

connected to an internal clock.

• System Reset Polarity – The polarity for system reset (sys_rst) can be selected. If the

option is selected as active-Low, the parameter RST_ACT_LOW is set to 1 and if set to

active-High the parameter RST_ACT_LOW is set to 0.

• Debug Signals Control – Selecting this option enables calibration status and user port

signals to be port mapped to the ILA and VIO in the example_top module. This helps

in monitoring traffic on the user interface port with the Vivado Design Suite debug

feature. Deselecting the Debug Signals Control option leaves the debug signals

unconnected in the example_top module and no ILA/VIO modules are generated by

the IP catalog. Additionally, the debug port is always disabled for functional

simulations.

Note:

This option is not available in the Vivado IP integrator flow.

• Sample Data Depth – This option selects the Sample Data depth for the ILA module

used in the Vivado debug logic. This option can be selected when the Debug Signals

for Memory Controller option is ON.

• Internal V

use of the V

Selection – Internal V

REF

pins for normal I/O usage. Internal V

REF

can be used for data group bytes to allow the

REF

should only be used for data

REF

rates of 800 Mb/s or below.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 41

UG586 November 30, 2016

www.xilinx.com

Page 42

X-Ref Target - Figure 1-23

UG586_c1_29_090511

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

• I/O Power Reduction – This option reduces the average I/O power by disabling DQ

and DQS IBUFs automatically whenever the controller is in the idle state.

• XADC Instantiation – When enabled, this option directs MIG core to instantiate the

XADC and a temperature polling circuit for the Temperature Monitor feature (see

Temperature Monitor). This option can be disabled if the XADC is already used

elsewhere in the design. In this case, the device temperature must be periodically

sampled and driven onto the device_temp_i bus in the memory interface top-level

user design module. If the device_temp_i signal is left unconnected, then the XADC

is instantiated. Otherwise the XADC is not instantiated.

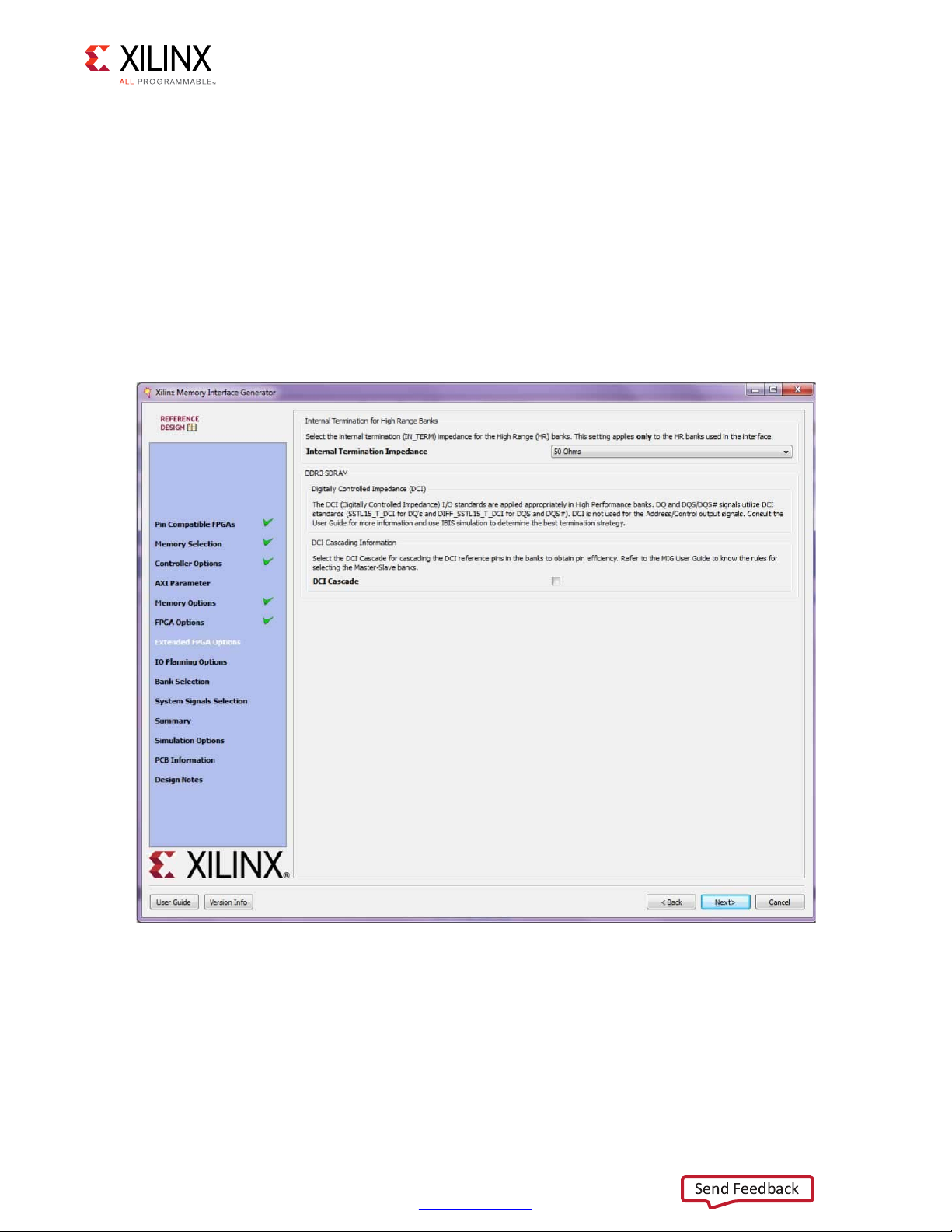

Click Next to display the DCI Description page (Figure 1-23).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 42

UG586 November 30, 2016

Figure 1-23: DCI Description

• Digitally Controlled Impedance (DCI) – The DCI option allows the use of the FPGA

on-chip internal resistors for termination. DCI must be used for DQ and DQS/DQS#

signals. DCI cascade might have to be used, depending on the pinout and bank

selection. DCI is available in the High Performance Banks.

• Internal Termination for High Range Banks – The internal termination option can be

set to 40, 50, or 60Ω or disabled. This selection is only for High Range banks.

www.xilinx.com

Page 43

X-Ref Target - Figure 1-24

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

• DCI Cascade – This selection enables the VRN/VRP pins that are available in High

Performance banks to allocate for the address/control and reset_n ports.

• Pin/Bank Selection Mode – This allows you to specify an existing pinout and generate

the RTL for this pinout, or pick banks for a new design. Figure 1-24 shows the options

for using an existing pinout. You must assign the appropriate pins for each signal. A

choice of each bank is available to narrow down the list of pins. It is not mandatory to

select the banks prior to selection of the pins. Click Validate to check against the MIG

pinout rules. You cannot proceed until the MIG DRC has been validated by clicking

Validate.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 43

UG586 November 30, 2016

Figure 1-24: Pin/Bank Selection Mode

www.xilinx.com

Page 44

X-Ref Target - Figure 1-25

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Bank Selection

This feature allows the selection of bytes for the memory interface. Bytes can be selected

for different classes of memory signals, such as:

• Address and control signals

• Data signals

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 44

UG586 November 30, 2016

Figure 1-25: Bank Selection

For customized settings, click Deselect Banks and select the appropriate bank and memory

signals. Click Next to move to the next page if the default setting is used.

To unselect the banks that are selected, click Deselect Banks. To restore the defaults, click

Restore Defaults.

VCCAUX_IO groups are shown for HP banks in devices with these groups using dashed lines.

VCCAUX_IO is common to all banks in these groups. The memory interface must have the

same VCCAUX_IO for all banks used in the interface. The MIG core automatically sets the

VCCAUX_IO constraint appropriately for the data rate requested.

www.xilinx.com

Page 45

X-Ref Target - Figure 1-26

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

For devices implemented with SSI technology, the SLRs are indicated by a number in the

header in each bank, for example, SLR 1. Interfaces cannot span across Super Logic Regions.

Select the pins for the system signals on this page (Figure 1-26). The MIG tool allows the

selection of either external pins or internal connections, as desired.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 45

UG586 November 30, 2016

Figure 1-26: System Pins

• sys_clk – This is the system clock input for the memory interface and is typically

connected to a low-jitter external clock source. Either a single input or a differential

pair can be selected based on the System Clock selection in the FPGA Options page

(Figure 1-22). The sys_clk input must be in the same column as the memory

interface. If this pin is connected in the same banks as the memory interface, the MIG

tool selects an I/O standard compatible with the interface, such as DIFF_SSTL15 or

SSTL15. If sys_clk is not connected in a memory interface bank, the MIG tool selects

an appropriate standard such as LVCMOS18 or LVDS. The XDC can be modified as

desired after generation.

www.xilinx.com

Page 46

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Send Feedback

• clk_ref – This is the reference frequency input for the IDELAY control. The clk_ref

input can be generated internally or connected to an external source. A single input or

a differential pair can be selected based on the System Clock selection in the FPGA

Options page (Figure 1-22). The I/O standard is selected in a similar way as sys_clk.

• sys_rst – This is the asynchronous system reset input that can be generated internally

or driven from a pin. The MIG tool selects an appropriate I/O standard for the input

such as LVCMOS18 and LVCMOS25 for HP and HR banks, respectively. The default

polarity of sys_rst pin is active-Low. The polarity of sys_rst pin varies based on the

System Reset Polarity option chosen in FPGA Options page (Figure 1-22).

• init_calib_complete – This output indicates that the memory initialization and

calibration is complete and that the interface is ready to use. The

init_calib_complete signal is normally only used internally, but can be brought

out to a pin if desired.

• tg_compare_error – This output indicates that the traffic generator in the example

design has detected a data compare error. This signal is only generated in the example

design and is not part of the user design. This signal is not typically brought out to a

pin but can be, if desired.

Click Next to display the Summary page.

Summary

This page provides the complete details about the 7 series FPGA memory core selection,

interface parameters, IP catalog options, and FPGA options of the active project

(Figure 1-27).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 46

UG586 November 30, 2016

www.xilinx.com

Page 47

X-Ref Target - Figure 1-27

UG586_c1_38_110610

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-27: Summary

Memory Model License

The MIG tool can output a chosen vendor’s memory model for simulation purposes for

memories such as DDR2 or DDR3 SDRAMs. To access the models in the output sim folder,

click the license agreement (Figure 1-28). Read the license agreement and check the Accept

License Agreement box to accept it. If the license agreement is not agreed to, the memory

model is not made available. A memory model is necessary to simulate the design.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 47

UG586 November 30, 2016

www.xilinx.com

Page 48

X-Ref Target - Figure 1-28

UG586_c1_39_110610

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-28: License Agreement

Click Next to move to PCB Information page.

PCB Information

This page displays the PCB-related information to be considered while designing the board

that uses the MIG tool generated designs. Click Next to move to the Design Notes page.

Design Notes

Click Generate to generate the design files. The MIG tool generates two output directories:

example_design and user_design. After generating the design, the MIG GUI closes.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 48

UG586 November 30, 2016

www.xilinx.com

Page 49

X-Ref Target - Figure 1-29

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Vivado Integrated Design Flow for MIG

1. After clicking Generate, the Generate Output Products window appears. This window

has the Out-of-Context Settings as shown in Figure 1-29.

Figure 1-29: Generate Output Products Window

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 49

UG586 November 30, 2016

www.xilinx.com

Page 50

X-Ref Target - Figure 1-30

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

2. Click Out-of-Context Settings to configure generation of synthesized checkpoints. To

enable the Out-of-Context flow, enable the check box. To disable the Out-of-Context

flow, disable the check box. The default option is “enable” as shown in Figure 1-30.

Figure 1-30: Out-of-Context Settings Window

3. MIG core designs comply with “Hierarchical Design" flow in Vivado. For more

information, see the Vivado

Design Suite User Guide: Hierarchical Design (UG905) [Ref 5]

and the Vivado Design Suite Tutorial: Hierarchical Design (UG946) [Ref 6].

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 50

UG586 November 30, 2016

www.xilinx.com

Page 51

X-Ref Target - Figure 1-31

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

4. After generating the MIG core design, the project window appears as shown in

Figure 1-31.

Figure 1-31: Vivado Tool Project Window (After IP Generation)

5. After project creation, the XCI file is added to the Project Hierarchy. The same view also

displays the module hierarchies of the user design. The list of HDL and XDC files is

available in the IP Sources view in the Sources window. Double-clicking on any module

or file opens the file in the Vivado Editor. These files are read only.

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 51

UG586 November 30, 2016

www.xilinx.com

Page 52

X-Ref Target - Figure 1-32

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Figure 1-32: Vivado Tool Project Sources Window

Design generation from the MIG tool can be generated using the Create Design flow or

the Verify Pin Changes and Update Design flows. There is no difference between the

flow when generating the design from the MIG tool. Irrespective of the flow by which

designs are generated from the MIG tool, the XCI file is added to the Vivado tool

project. The implementation flow is the same for all scenarios because the flow depends

on the XCI file added to the project.

6. All MIG generated user design RTL and XDC files are automatically added to the project.

If files are modified and you wish to regenerate them, right-click the XCI file and select

Generate Output Products (Figure 1-33).

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 52

UG586 November 30, 2016

www.xilinx.com

Page 53

X-Ref Target - Figure 1-33

Send Feedback

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

X-Ref Target - Figure 1-34

Figure 1-33: Generate RTL and Constraints