Page 1

ZCU111 Evaluation Board

User Guide

UG1271 (v1.1) August 6, 2018

Page 2

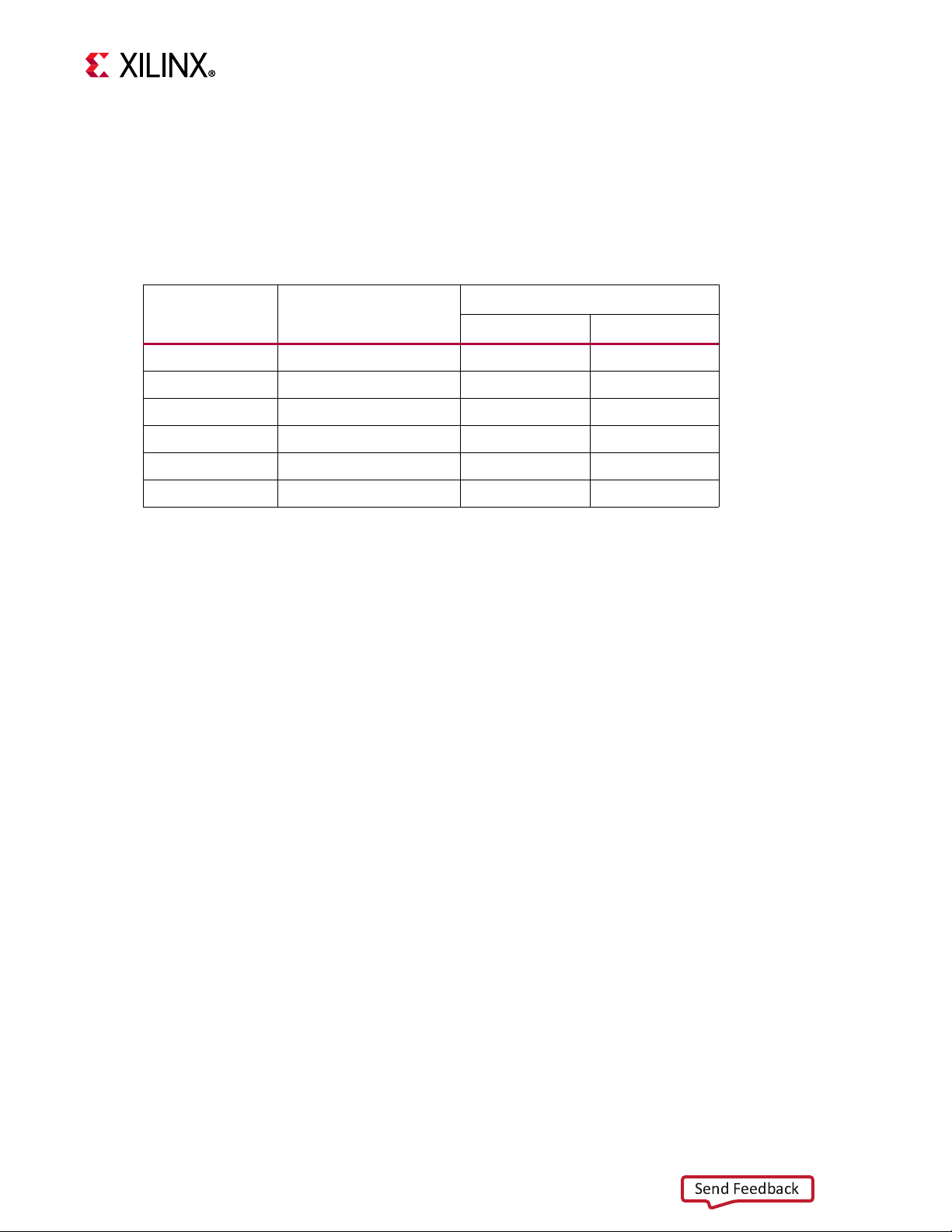

Revision History

Send Feedback

The following table shows the revision history for this document.

Section Revision Summary

8/06/2018 Version 1.1

RF Data Converter Clocking Removed RF Clocking Overview figure.

Figure 3-18 Added capacitor option.

Table 3-18 and Tab le 3- 19 Added optional RFMC and SYSREF capacitor options.

SFP28 Module Connectors

Added note and reference to SNIA Technology

Affiliates website.

06/28/2018 Version 1.0

Initial Xilinx release.

ZCU111 Board User Guide 2

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 3

Table of Contents

Send Feedback

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Chapter 1: Introduction

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Board Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Board Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Environmental . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Operating Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Chapter 2: Board Setup and Configuration

Board Component Location. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Default Jumper and Switch Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

RFSoC Device Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Quad SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

SD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

ZCU111 Board User Guide 3

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Chapter 3: Board Component Descriptions

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Component Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Zynq UltraScale+ XCZU28DR RFSoC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Encryption Key Battery Backup Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

PS-Side: DDR4 SODIMM Socket . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

PL-Side: DDR4 Component Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

PSMIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Quad SPI Flash Memory (MIO 0–12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

GPIO (MIO 13, 38) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

I2C0 (MIO 14-15), I2C1 (MIO 16-17) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

I2C0 (MIO 14-15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

I2C1 (MIO 16-17) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

UART0 (MIO 18-19) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

UART1 (MIO 20-21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

GPIO (MIO 22-23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

CAN1 (MIO 24-25) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Page 4

PMU GPI (MIO 26) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Send Feedback

DPAUX (MIO 27-30) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

PMU GPO (MIO 32-37) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

SD Card Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

USB 3.0 Transceiver and USB 2.0 ULPI PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

GEM3 Ethernet (MIO 64-77) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

10/100/1000 MHz Tri-Speed Ethernet PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Programmable Logic JTAG Programming Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

RF Data Converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

RF Data Converter Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

RF RFMC Plug-in Card Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

SFP28 Module Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

User PMOD GPIO Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

User I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Power and Status LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

GTY Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PS-Side: GTR Transceivers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

PS M.2 SATA Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

FPGA Mezzanine Card Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Cooling Fan Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

VADJ_FMC Power Rail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

ZCU111 System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

Board Power System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

Monitoring Voltage and Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

. . . . . . . . . . . . . . . . . . .71

Appendix A: VITA 57.4 FMCP Connector Pinouts

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Appendix B: Xilinx Design Constraints

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Appendix C: Regulatory and Compliance Information

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

CE Directives. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

CE Standards. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Electromagnetic Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

Safety . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

Markings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Appendix D: HW-FMC-XM500

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

AMS RFMC Plug-in Card Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

XM500 Card Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

ADC/DAC Bank Data and Clock Channel Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

XM500 ADC/DAC Data and Clock SMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

ZCU111 Board User Guide 4

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 5

Appendix E: Additional Resources and Legal Notices

Send Feedback

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Documentation Navigator and Design Hubs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

ZCU111 Board User Guide 5

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 6

Introduction

Send Feedback

Overview

The ZCU111 evaluation board features the Zynq® UltraScale+™ RFSoC ZCU28DR device.

This board enables the evaluation of the integrated RF-DAC and RF-ADC functionality, soft

decision forward error correction (SDFEC), and FPGA fabric and RFSoC features, such as the

quad core Arm® Cortex™-A53 processing system (PS) and the dual-core Arm Cortex-R5

real-time processors. The ZCU111 evaluation board is equipped with many of the common

board-level features needed for design development, such as DDR4 memory, networking

interfaces, FMC+ expansion port, and access to the new RF-FMC interface.

The Z C U111 eva luation b oard kit i ncludes a n out-of - the-box FMC XM500 balun transformer

add-on card to support signal analysis and loopback evaluation. This card includes

on-board high-frequency and low frequency baluns and SMAs for custom baluns and

filtering. For more information on this card, see Appendix D, HW-FMC-XM500.

Chapter 1

Additional Resources

See Appendix E, Additional Resources and Legal Notices for references to documents, files,

and resources relevant to the ZCU111 evaluation board.

ZCU111 Board User Guide 6

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 7

X-Ref Target - Figure 1-1

RFMC_ADC[06:07]

RFMC_ADC[00:01]

RFMC_ADC[04:05]

RFMC_ADC[02:03]

X21110-062118

Send Feedback

Chapter 1: Introduction

Block Diagram

The ZCU111 board block diagram is shown in Figure 1-1.

ZCU111 Board User Guide 7

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 1-1: ZCU111 Evaluation Board Block Diagram

Board Features

The ZCU111 evaluation board features are listed here. Detailed information for each feature

is provided in Board Component Descriptions in Chapter 3.

• XCZU28DR-2E, FFVG1517 package

• Form factor: rectangular 11.811 in. x 7.874 in. x 0.1 in.

• Configuration from:

Dual Quad SPI

°

Page 8

Micro SD card

Send Feedback

°

USB-to-JTAG bridge

°

•Clocks

GTR_REF_CLK_DP 27 MHz

°

GTR_REF_CLK_USB3 26 MHz

°

GTR_REF_CLK_SATA 125 MHz

°

CLK_100 100 MHz

°

CLK_125 125 MHz

°

PS_REF_CLK 33.33 MHz

°

USER_MGT_SI570 (default 156.25 MHz)

°

USER_SI570 (default 300 MHz)

°

• PS DDR4 4 GB 64-bit SODIMM

• PL DDR4 4 GB 64-bit component (4x16-bit)

Chapter 1: Introduction

• PS GTR (bank 505) assignment

DisplayPort 1.2 transmit only (two GTR)

°

USB3 (one GTR)

°

SATA with M2 connector (one GTR)

°

• PL GTY assignment (16 total)

SFP28 (four, bank GTY128)

°

FMCP HSCP DP (four, bank GTY129)

°

FMCP HSCP DP (four, bank GTY130)

°

FMCP HSCP DP (four, bank GTY131)

°

• PL FMCP HSCP (FMC+) connectivity - full LA[00:33] bus

• PS MIO connectivity

PS MIO[0:5, 7:12]: dual Quad SPI flash memory

°

PS MIO[13]: PS_GPIO2

°

PS MIO[14:17]: two channels of I2C

°

ZCU111 Board User Guide 8

UG1271 (v1.1) August 6, 2018 www.xilinx.com

PS MIO[18:19]: UART (one of three FT4232 UART channels)

°

PS MIO[22:23]: PS_PB, PS_LED I/F

°

PS MIO[26]: platform management unit (PMU)

°

PS MIO[27:30]: DisplayPort control

°

Page 9

PS MIO[32:37]: PMU_GPIO[0:5]

Send Feedback

°

PS MIO[38]: PS_GPIO1

°

PS MIO[44:51]: SD I/F

°

PS MIO[52:63]: USB3.0

°

PS MIO[64:77]: GEM3 Ethernet

°

• PL I/O connections:

PL-side user DIP switch (8-position)

°

PL-side CPU reset pushbutton

°

PL-side user LEDs (eight)

°

PL-side user pushbuttons (five, geographic N, S, E, W, C)

°

PL-side PMOD0/1 (two R.A. 2x6 receptacles)

°

• Security - PSBATT button battery backup

•SYSMON header

Chapter 1: Introduction

• Operational switches (power on/off, PROG_B, boot mode DIP switch)

• Operational status LEDs (INIT, DONE, PS STATUS, PGOOD)

• Power management

• System controller (MSP430)

The ZCU111 provides a rapid prototyping platform using the XCZU28DR-2EFFVG1517

device. See the Zynq UltraScale+ RFSoC Data Sheet: Overview (DS889) [Ref 1] for a feature

set overview, description, and ordering information.

Board Specifications

Dimensions

Height: 11.811 inches (30.0 cm)

Width: 7.874 inches (20.0 cm)

Thickness: 100.8 mil (0.2743 cm)

ZCU111 Board User Guide 9

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Note:

A 3D model of this board is not available.

See ZCU111 board documentation for the XDC listing and board schematics.

Page 10

Environmental

Send Feedback

Temperature

Operating: 0°C to +45°C

Storage: -25°C to +60°C

Humidity

10% to 90% non-condensing

Operating Voltage

Chapter 1: Introduction

+12 V

DC

ZCU111 Board User Guide 10

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 11

Board Setup and Configuration

Send Feedback

Board Component Location

Figure 2-1 shows the ZCU111 board component locations. Each numbered component

shown in the figure is keyed to Tab l e 2- 1. Ta ble 2 -1 identifies the components, references

the respective schematic (0381811) page numbers, and links to a detailed functional

description of the components and board features in Chapter 3.

IMPORTANT: Figure 2-1 is for visual reference only and might not reflect the current revision of the

board.

IMPORTANT: There could be multiple revisions of this board. The specific details concerning the

differences between revisions are not captured in this document. This document is not intended to be

a reference design guide and the information herein should not be used as such. Always refer to the

schematic, layout, and XDC files of the specific ZCU111 version of interest for such details.

Chapter 2

CAUTION! The ZCU111 board can be damaged by electrostatic discharge (ESD). Follow standard ESD

prevention measures when handling the board.

ZCU111 Board User Guide 11

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 12

X-Ref Target - Figure 2-1

1

00

Round callout references a component

on the front side of the board

Square callout references a component

on the back side of the board

00

26

41

28

15

43

20

19

27

18

52

42

60

40

62

61

1

57

26

41

28

13

15

43

20

19

27

32

18

52

42

60

40

63

30

12

62

61

16

22

7

6

24

25

17

17

35

29 5

37

55

53

36

54

56

23

2

4

8

51

49

14

45

50

34

3

14

31

58

33

38

39

21

9

10

59

28

11

44

X20477-06211

Send Feedback

Chapter 2: Board Setup and Configuration

ZCU111 Board User Guide 12

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 2-1: ZCU111 Evaluation Board Components

Page 13

Table 2-1: Board Component Locations

Send Feedback

Chapter 2: Board Setup and Configuration

Callout Ref. Des. Feature [B] = Bottom Notes

1U1

2J50

3 U80, U94-U96 PL-Side: DDR4 Component Memory Micron MT40A512M16JY-075E 72-75

4 U17, U18 Quad SPI Flash Memory (MIO 0–12) Micron MT25QU02CBB8E-0SIT 25

5 U12, J96

6 J100 SD Card Interface MOLEX 5025700893 28

7 U34, J83 UART0 (MIO 18-19)

8U46

9U47Programmable User SI570 Clock Silicon Labs SI570BAB001614DG 45

10 U49

Zy nq U ltra Sca le+ XCZU 28DR RFS oC

fansink

PS-Side: DDR4 SODIMM Socket,

w/64-bit DDR4 SODIMM

USB 3.0 Transceiver and USB 2.0

ULPI PHY [B]

SI5341B 10 Independent Output

Any-Frequency Clock Generator

Programmable User MGT SI570

Clock, user MGT clock,

156.250 MHz, 3.3V LVDS

XCZU28DR-2FFVG1517

COFAN 30-4988-10

LOTES ADDR0067-P001A

with MICRON

MTA4ATF51264HZ-2G6E1

SMSC USB3320-EZK,

WURTH 692122030100

FTDI FT4232Hx-REEL,

Hirose ZX62D-AB-5P8

Silicon Labs SI5341B-D07833-GM 40

Silicon Labs SI570BAB000544DG 45

Schematic

Page

43

24

29

11 U48 SI5382A SFP28 Clock Recovery [B] Silicon Labs SI5382B-C-GMR 39

12 U37, P12

13 U22, U23 I2C0 (MIO 14-15), expander

14 U26, U27 I2C1 (MIO 16-17) [B] Two each TI TCA9548APWR 27

15

16 U42 ZCU111 System Controller TI MSP430F5342 32

17 J48, J49

18 DS11-DS18

19 SW9-SW13

20 SW14

21 SW20

22 SW8 System controller 5-pole C&K SDA05H1SBD 32

J27, J32, J37,

J42

10/100/1000 MHz Tri-Speed

Ethernet PHY, RJ45 with mag

SFP28 Module Connectors Molex 170382-0001 38

User PMOD GPIO Connectors,

PMOD0/1 RA receptacles

User I/O, eight user LEDs, active

High

User I/O, user pushbutton switches,

active High

User I/O, user 8-pole DIP switch,

active High

User I/O, CPU_RESET pushbutton,

active High

TI DP83867IRPAP,

Wurth 7499111221A

TI TCA6416APWR,

TI PCA9544ARGYR

SULLINS PPPC062LJBN-RC 42

GPIO LEDs, GREEN 0603 41

E-Switch TL3301EP100QG

(N,S,W,E,C pattern)

C&K SDA08H1SBD 41

E-switch TL3301EP100QG 41

30

26

41

23 SW3, SW4

ZCU111 Board User Guide 13

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Switches, PS_SRST_B, PS_POR_B

pushbuttons

E-switch TL3301EP100QG 12

Page 14

Table 2-1: Board Component Locations (Cont’d)

Send Feedback

Chapter 2: Board Setup and Configuration

Callout Ref. Des. Feature [B] = Bottom Notes

24 SW16

25 J52

26 SW2

27 J26

28 - Board Power System, (top, [B]) Infineon regulators 47-61

29 P11 DPAUX (MIO 27-30), DisplayPort MOLEX 0472720001 22-23

30 J19

31 J92

32 SW6

33 J5

Power On/Off Slide Switch, power

ON/OFF slide switch

Power On/Off Slide Switch, power

connector

Program_B Pushbutton, PS_PROG

pushbutton

FPGA Mezzanine Card Interface,

FMCP HSPC connector

Monitoring Voltage and Current,

PMBUS connector

System controller, MSP430 SC

emulation cable connector

RFSoC Device Configuration, FPGA

MODE 4-pole DIP switch

SYSMON 2X6 vertical male pin

header

C&K 1201M2S3AQE2 46

MOLEX 39-30-1060 46

E-switch TL3301EP100QG 12

Samtec ASP_184329_01 33-37

SULLINS PBC36SAAN 26

TYCO 5103308-2 32

4-pole C&K SDA04H1SBD 12

SULLINS PBC36DAAN 3

Schematic

Page

34 J47

35 J94

36 U40 PS M.2 SATA Connector Amphenol MDT420M02001 31

37 M2CAGE1

38 U52

39 J60

40 J14

41 J15

42 J95

43 J108

44 J109

RF Data Converters, low profile

array (LPAF) socket

RF Data Converters, low profile

array (LPAF) socket

PS M.2 SATA Connector, M.2 conn.

EMI cage

Cooling Fan Connector, fan

controller

Cooling Fan Connector, fan

controller

User SMA MGT Clock, SMA

USER_SMA_MGT_CLOCK_P

User SMA MGT Clock, SMA

USER_SMA_MGT_CLOCK_N

User SMA MGT Clock, SMA

RF_FPGA_REF_CLK

RF clocking, U90 LMK04208 RF

REFCLK SMA

RF clocking, U90 LMK04208 RF

external REFCLK SMA

Samtec

Samtec

Leader Tech

20S-CBSFNSV-1.0x2.25x0.40

Maxim MAX6643LBBAEE++ 46

Molex 22-11-2032 46

Rosenberger 32K10K-400L5 8

Rosenberger 32K10K-400L5 8

Rosenberger 32K10K-400L5 4

Rosenberger 32K10K-400L5 67

Rosenberger 32K10K-400L5 67

LPAF-40-03.0-S-08-2-K-TR 63

LPAF-40-03.0-S-08-2-K-TR 64

31

45 U90 RF clocking, LMK04208 RF REFCLK T I L M K 04208 67

ZCU111 Board User Guide 14

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 15

Table 2-1: Board Component Locations (Cont’d)

Send Feedback

Chapter 2: Board Setup and Configuration

Callout Ref. Des. Feature [B] = Bottom Notes

49 U102 RF clocking, ADC RFPLL TI LMX2594RHAT 68

50 U103 RF clocking, DAC RFPLL TI LMX2594RHAT 69

51 U104 RF clocking, ADC RFPLL TI LMX2594RHAT 70

52 U6

53 U13

54 J20

55 J8

56 J9

57 U53

58 U55

59 U57

System Reset Pushbuttons,

power-on reset

USB 3.0 Transceiver and USB 2.0

ULPI PHY, USB3 power switch,

System Reset Pushbuttons,

2-pin HDR PS_POR_B

System Reset Pushbuttons,

2-pin HDR PS_SRST_B

System Reset Pushbuttons, 2-pin

HDR MR_B (U6 MAX16025 POR)

Board Power System,

INFINEON PMIC1

Board Power System,

INFINEON PMIC2

Board Power System,

INFINEON PMIC3

Maxim MAX16025TE+ 12

Micrel MIC2544A-1YM 24

SULLINS PBC36SAAN 12

SULLINS PBC36SAAN 12

SULLINS PBC36SAAN 12

Infineon IRPS5401MXI04TRP 47

Infineon IRPS5401MXI04TRP 49

Infineon IRPS5401MXI04TRP 51

Schematic

Page

60 U83 Power and Status LEDs, LED driver TI SN74AVC8T245PWR 62

61 U84 Power and Status LEDs, LED driver TI SN74AVC8T245PWR 62

62 U85 Power and Status LEDs, LED driver TI SN74AVC8T245PWR 62

63 SW7

PB U42 MSP430 reset,

PB reset (U42 MSP430).

E-switch TL3301EP100QG 32

ZCU111 Board User Guide 15

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 16

X-Ref Target - Figure 2-2

1

2

4

3

8

9

10

11

12

15

14

13

16

18

17

19

20

27 23

25

26

29

32

28

24

21

22

31

7

6

5

30

X20479-062118

Send Feedback

Chapter 2: Board Setup and Configuration

Default Jumper and Switch Settings

Figure 2-2 shows the ZCU111 board jumper header and switch locations. Each numbered

component shown in the figure is keyed to Tab l e 2- 2 (for default jumper settings) or

Tab l e 2- 3 (for default switch settings). Both tables reference the respective schematic page

numbers.

Figure 2-2: Board Jumper Header and Switch Locations

ZCU111 Board User Guide 16

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 17

Jumpers

Send Feedback

Table 2-2: Default Jumper Settings

Chapter 2: Board Setup and Configuration

Callout

Number

1 J85 POR_OVERRIDE 2-3 3

1-2: Enable

2-3: Disable

2 J2 SYSMON I2C address On 3

Off: SYSMON_VP_R floating

On: SYSMON_VP_P pulled down

3 J3 SYSMON I2C Address On 3

Off: SYSMON_VN_R floating

On: SYSMON_VP_N pulled down

4J4SYSMON VREFP 1-2 3

1-2: 1.25V VREFP connected to fpga

2-3: VREFP connected to GND

5 J20 Reset sequencer PS_POR_B On 12

Off: sequencer does not control PS_POR_B

On: sequencer can control PS_POR_B

Ref Des Function Default

Schematic

Page

6 J8 Reset sequencer PS_SRST_B On 12

Off: sequencer does not control PS_SRST_B

On: sequencer can control PS_SRST_B

7 J9 Reset sequencer inhibit Off 12

Off: sequencer normal operation

On: sequencer inhibit (resets will stay asserted)

8 J17 USB 3.0 connector J96 shield connection options 2-3 24

1-2: J96 shield capacitor C171 to GND

2-3: J96 shield directly to GND

9 J18 ULPI USB3320 U12 ULPIO_VBUS_SEL option jumper Off 24

On: Selects U13 MIC2544A switch 5V for VBUS

Off: normal operation, VBUS from J96 USB3.0 conn.

10 J1 SD3.0 U107 IP4856CX25 level-trans. ref. voltage select 1-2 28

1-2: track SD3.0 J100 socket UTIL_3V3 3.3V

2-3: GND = revert to internal voltage reference

11 J23 U93 SC18IS602IPW I2C-to-SPI bridge enable Off 66

On: U93 bridge RESET_B to GND, U93 inhibited

ZCU111 Board User Guide 17

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 18

Table 2-2: Default Jumper Settings (Cont’d)

Send Feedback

Chapter 2: Board Setup and Configuration

Callout

Number

Off: U93 bridge enabled

12 J164 U111 MPS430 RST_B and test pin options 32

1-2: MSP430_RST_B connected to PMOD1_0 Open

2-3: MSP430_TEST connected to PMOD1_1 Open

13 J29 SFP0 J29 enable jumper On 38

On: SFP0 TX_DISABLE = GND = enabled

Off: SFP0 TX_DISABLE = high = disabled

14 J35 SFP1 J35 enable jumper On 38

On: SFP1 TX_DISABLE = GND = enabled

Off: SFP1 TX_DISABLE = high = disabled

15 J40 SFP2 J40 enable jumper On 38

On: SFP2 TX_DISABLE = GND = enabled

Off: SFP2 TX_DISABLE = high = disabled

16 J44 SFP3 J44 enable jumper On 38

On: SFP3 TX_DISABLE = GND = enabled

Ref Des Function Default

Schematic

Page

Off: SFP3 TX_DISABLE = high = disabled

17 J87 USB2ANY cable select jumper Off 66

On: USBANY_SDO connected to I2CSPI_SDO

Off: USBANY_SDO not connected to I2CSPI_SDO

18 J89 ZU28DR RFSoC U1 ADC bank 224 ADC_REXT select Off 9

On: bank 224 ADC_REXT pin AB8 = GND

Off: bank 224 ADC_REXT pin AB8 = 2.49K to GND

19 J90 ZU28DR RFSoC U1 DAC bank 228 DAC_REXT select Off 10

On: bank 228 DAC_REXT pin W8 = GND

Off: bank 228 DAC_REXT pin W8 = 2.49K to GND

20 J101 SPI CS select header 66

1-2:

3-4:

5-6:

7-8:

21 J111 SPI SDO select header 66

1-2:

ZCU111 Board User Guide 18

UG1271 (v1.1) August 6, 2018 www.xilinx.com

3-4:

5-6:

Page 19

Table 2-2: Default Jumper Settings (Cont’d)

Send Feedback

Chapter 2: Board Setup and Configuration

Callout

Number

7-8:

22 J110 U92 12.8MHz TXCO power On 67

On: U92 is on

Off: U92 is off

Ref Des Function Default

Switches

Table 2-3: Default Switch Settings

Callout

Number

23 SW6 RFSoC U1 Mode 4-Pole DIP Switch 0010 12

Switch OFF = 1 = High; ON = 0 = Low

Mode = SW6[4:1] = Mode[3:0]

JTAG = ON,ON,ON,ON = 0000

QSPI32 = ON,ON,OFF,ON = 0010

SD = OFF,OFF,OFF,ON = 1110

24 SW2 PS_PROG_B pushbutton

25 SW3 PS_POR_B pushbutton

Ref Des Function Default

(1)

(1)

SW4 PS_SRST_B pushbutton

(1)

Schematic

Page

Schematic

Page

12

12

12

26 SW8

27 SW8

28 SW9 GPIO pushbutton (geographic) GPIO_SW_N

SW10 GPIO pushbutton (geographic) GPIO_SW_W

SW11 GPIO pushbutton (geographic) GPIO_SW_C

SW12 GPIO pushbutton (geographic) GPIO_SW_E

SW13 GPIO pushbutton (geographic) GPIO_SW_S

29 SW14

30 SW15 CPU_RESET pushbutton

31 SW16 Main power slide switch off 46

32 SW19 PS MIO22_BUTTON pushbutton

Notes:

1. Pushbutton switch default = open (not pressed).

MSP430 U42 5-Pole GPIO DIP switch

Switch Off = 1 = High; On = 0 = Low

RST_B pushbutton for MSP430 U42/MSP430

EMUL. cable J92

GPIO 8 -Pole D IP sw it ch

Switch Off = 0 = Low; On = 1 = High

11111 32

(1)

(1)

(1)

(1)

(1)

(1)

00000000 41

(1)

(1)

32

41

41

41

41

41

41

11

ZCU111 Board User Guide 19

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 20

Chapter 2: Board Setup and Configuration

Send Feedback

RFSoC Device Configuration

Zynq UltraScale+ XC ZU28 DR-2 E RFS oC de vices use a multi-stage boot process as described

in the “Boot and Configuration” chapter of the Zynq UltraScale+ Device Technical Reference

Manual (UG1085) [Ref 3]. Switch SW6 configuration option settings are listed in Tabl e 2- 4 .

Table 2-4: Switch SW6 Configuration Option Settings

Boot Mode Mode Pins [3:0] Mode SW6 [4:1]

JTAG 0000 ON,ON,ON,ON

QSPI32 0010

SD 1110 OFF,OFF,OFF,ON

Notes:

1. Default switch setting.

JTAG

(1)

ON,ON,OFF,ON

Vivado®, Xilinx SDK, or third-party tools can establish a JTAG connection to the Zynq

UltraScale+ RFSoC device through the FTDI FT4232 USB-to-JTAG/USB UART device (U34)

connected to micro-USB connector (J83).

Quad SPI

To boot from the dual Quad SPI nonvolatile configuration memory:

1. Store a valid Zynq UltraScale+ RFSoC boot image in the Quad SPI flash devices

connected to the MIO Quad SPI interface. See the ZCU111 Restoring Flash Tutorial

XTP515 [Ref 13] for information on programming the QSPI.

2. Set the boot mode pins SW6 [3:0] PS_MODE[3:0] as indicated in Ta b le 2 - 4 for Quad

SPI32.

3. Either power-cycle or press the power-on reset (POR) pushbutton. SW6 is callout 46 in

Figure 2-1.

SD

To boot from an SD card:

ZCU111 Board User Guide 20

UG1271 (v1.1) August 6, 2018 www.xilinx.com

1. Store a valid Zynq UltraScale+ RFSoC boot image file on to an SD card (and then plug

the SD card into ZCU111 board socket J100).

2. Set the boot mode pins SW6 [3:0] PS_MODE[3:0] as indicated in Ta b le 2 - 4 for SD.

3. Either power-cycle or press the power-on reset (POR) pushbutton. SW6 is callout 46 in

Figure 2-1.

Page 21

Chapter 2: Board Setup and Configuration

Send Feedback

See the Zynq UltraScale+ Device Technical Reference Manual (UG1085) [Ref 3] for more

information about Zynq UltraScale+ RFSoC configuration options.

ZCU111 Board User Guide 21

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 22

Board Component Descriptions

Send Feedback

Overview

This chapter provides a detailed functional description of the board’s components and

features. Tab le 2-1 , pa ge 13 identifies the components, references the respective schematic

page numbers, and links to the corresponding detailed functional description in this

chapter. Component locations are shown in Figure 2-1, page 12.

Component Descriptions

Chapter 3

Zynq UltraScale+ XCZU28DR RFSoC

[Figure 2-1, callout 1]

The ZCU111 board is populated with the Zynq UltraScale+ XCZU28DR-2FFVG1517 RFSoC,

which combines a powerful processing system (PS) and programmable logic (PL) in the

same device. The PS in a Zynq UltraScale+ RFSoC features the Arm

64-bit quad-core processor and Cortex-R5 dual-core real-time processor.

For additional information on the Zynq UltraScale+ XCZU28DR-2FFVG1517 RFSoC, see the

Zynq UltraScale+ RFSoC Data Sheet (DS926) [Ref 2]. See the Zynq UltraScale+ Device

Technical Reference Manual (UG1085) [Ref 3] for more information about Zynq UltraScale+

RFSoC configuration options.

®

flagship Cortex®-A53

ZCU111 Board User Guide 22

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 23

Chapter 3: Board Component Descriptions

X20480-062118

Send Feedback

Encryption Key Battery Backup Circuit

The XCZU28DR RFSoC U1 implements bitstream encryption key technology. The ZCU111

board provides the encryption key backup battery circuit shown in Figure 3-1.

X-Ref Target - Figure 3-1

ZCU111 Board User Guide 23

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-1: Encryption Key Backup Circuit

The Seiko TS518FE rechargeable 1.5V lithium button-type battery B1 is soldered to the

board with the positive output connected to the XCZU28DR-2E RFSoC U1 V

Y23. The battery supply current I

specification is 150 nA maximum when board power is

BATT

CC_PSBATT

pin

off. B1 is charged from the UTIL_1V8 1.8V rail through a series diode with a typical forward

voltage drop of 0.38V and 4.7 ΩK current limit resistor. The nominal charging voltage is

1.42V.

Page 24

Chapter 3: Board Component Descriptions

Send Feedback

I/O Voltage Rails

The XCZU28DR RFSoC PL I/O bank voltages on the ZCU111 board are listed in Tabl e 3-1 .

Table 3-1: I/O Voltage Rails

XCZU28DR

PL bank 64 VCC1V8 1.8V GPIO

PL bank 65 VADJ_FMC

PL bank 66 VADJ_FMC

PL bank 67 VCC1V2 1.2V PL_DDR4_DQ[32:63]

PL bank 68 VCCIV2 1.2V PL_DDR4_DQ[0:31], SFPx_TX_DISABLE, SYSMON_SDA/SCL

PL bank 69 VCC1V2 1.2V PL_DDR4 ADDR/CTRL, PMOD0&1[0:7],MSP430_GPIO[0:3]

PL bank 84 VCC1V8 1.8V ADCIO[0:19], GPIO_SW[N,E,C,W]

PL bank 87 VCC1V8 1.8V DACIO[0:19], GPIO_SW[S], SFP_SI5382_CLK_IN_SEL

PS bank 500 VCC1V8 1.8V QSPI LWR/UPR, PS_GPIO2, I2Cx_SDA/SCL, UART0_RXD/TXD

PS bank 501 VCC1V8 1.8V DP CTRL, PMU_GPO[0:5], SDIO I/F, PS_GPIO1

PS bank 502 VCC1V8 1.8V USB I/F, ENET I/F

PS bank 503 VCC1V8 1.8V PS CONFIG I/F

PS bank 504 VCC1V2 1.2V PS_DDR4 64-BIT SODIMM I/F

Notes:

1. The ZCU111 board is shipped with VADJ_FMC set to 1.8V by the MSP430 system controller.

Power Net

Name

(1)

(1)

Voltage Connected To

1.8V FMCP_HSPC LA BUS [0:16]

1.8V FMCP_HSPC LA BUS [17:32]

PS-Side: DDR4 SODIMM Socket

[Figure 2-1, callout 2]

The PS-side memory is wired to the Zynq UltraScale+ DDRC bank 504 hard memory

controller. A 64-bit single rank DDR4 SODIMM is inserted into socket J50. The ZCU111

board is shipped with a DDR4 SODIMM installed:

• Manufacturer: Micron

• Part Number: MTA4ATF51264HZ-2G6E1

•Description:

4 GByte 260-pin DDR4 SODIMM

°

Single rank x16

°

512 Mbit x 64-bit

°

Supports 1333 MT/s – 2666 MT/s

°

ZCU111 Board User Guide 24

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 25

Chapter 3: Board Component Descriptions

Send Feedback

The ZCU111 XCZU28DR RFSoC PS DDR interface maximum 2133 MT/s performance is

documented in the Zynq UltraScale+ RFSoC Data Sheet (DS926)[Ref 2].

The ZCU111 DDR4 SODIMM interface adheres to the constraints guidelines documented in

the PCB guidelines for DDR4 section of the UltraScale Architecture PCB Design User Guide

(UG583) [Ref 4]. The DDR4 SODIMM interface is a 40Ω impedance implementation. Other

memory interface details are also available in the UltraScale Architecture-Based FPGAs

Memory IP LogiCORE IP Product Guide (PG150) [Ref 5]. For more details, see the Micron

MTA4ATF51264HZ-2G6E1 data sheet at the Micron website [Ref 15].

The connections between the DDR4 SODIMM socket J50 and XCZU28DR PS bank 504 are

referenced in Appendix B, Xilinx Design Constraints.

PL-Side: DDR4 Component Memory

[Figure 2-1, callout 3]

The 4 GB, 64-bit wide DDR4 memory system is comprised of four 512 Mb x 16 SDRAM, U80

and U94-U96.

• Manufacturer: Micron

• Part Number: MT40A512M16JY-075E

• Description:

8 Gb (512 Mb x 16)

°

1.2V 96-ball TFBGA

°

DDR4-2666

°

This memory system is connected to PL-side XCZU28DR banks 67, 68, and 69. The DDR4

0.6V VTT termination voltage is supplied from sink-source regulator U81.

The ZCU111 board DDR4 64-bit component memory interface adheres to the constraints

guidelines documented in the PCB guidelines for DDR4 section of UltraScale Architecture

PCB Design User Guide (UG583) [Ref 4]. The ZCU111 DDR4 component interface is a 40Ω

impedance implementation. Other memory interface details are also available in the

UltraScale Architecture-Based FPGAs Memory IP LogiCORE IP Product Guide (PG150) [Ref 5].

For more details, see the Micron MTA4ATF51264HZ-2G6E1 data sheet at the Micron website

[Ref 15]

The connections between the DDR4 component memories and the XCZU28DR banks are

referenced in Appendix B, Xilinx Design Constraints.

ZCU111 Board User Guide 25

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 26

Chapter 3: Board Component Descriptions

Send Feedback

PSMIO

Tab l e 3- 2 provides PS MIO peripheral mapping implemented on the ZCU111 board. See the

Zynq UltraScale+ Device Technical Reference Manual (UG1085) [Ref 3] for more information

on PS MIO peripheral mapping.

Table 3-2: MIO Peripheral Mapping

MIO[0:25] Bank 500 MIO[26:51] Bank 501 MIO[52:77] Bank 502

0 QSPI 26 PMU IN 52 USB0

1QSPI27DPAUX53USB0

2 QSPI 28 DPAUX 54 USB0

3QSPI29DPAUX55USB0

4 QSPI 30 DPAUX 56 USB0

5 QSPI 31 Not assigned/no connect 57 USB0

6 Not assigned/no connect 32 PMU OUT 58 USB0

7 QSPI 33 PMU OUT 59 USB0

8 QSPI 34 PMU OUT 60 USB0

9 QSPI 35 PMU OUT 61 USB0

10 QSPI 36 PMU OUT 62 USB0

11 QSPI 37 PMU OUT 63 USB0

12 QSPI 38 GPIO 64 GEM3

13 GPIO 39 SD1 65 GEM3

14 I2C0 40 SD1 66 GEM3

15 I2C0 41 SD1 67 GEM3

16 I2C1 42 SD1 68 GEM3

17 I2C1 43 Not assigned/no connect 69 GEM3

18 UART0 44 Not assigned/no connect 70 GEM3

19 UART0 45 SD1 71 GEM3

20 Not assigned/no connect 46 SD1 72 GEM3

21 Not assigned/no connect 46 SD1 73 GEM3

22 GPIO 48 SD1 74 GEM3

23 GPIO 49 SD1 75 GEM3

24 Not assigned/no connect 50 SD1 76 MDI03

ZCU111 Board User Guide 26

UG1271 (v1.1) August 6, 2018 www.xilinx.com

25 Not assigned/no connect 51 SD1 77 MDI03

Page 27

Chapter 3: Board Component Descriptions

Send Feedback

Quad SPI Flash Memory (MIO 0–12)

[Figure 2-1, callout 4]

The Micron dual MT25QU02GCBB8E12-0sit serial NOR flash Quad SPI flash memory can

hold the boot image for the RFSoC system. This interface is used to support QSPI32 boot

mode as defined in the Zynq UltraScale+ Device Technical Reference Manual (UG1085)

[Ref 3].

The dual Quad SPI flash memory located at U17/U18 provides 4 Gb of non-volatile storage

that can be used for configuration and data storage.

• Part number: MT25QU02GCBB8E12-0SIT (Micron)

• Supply voltage: 1.8V

• Datapath width: 8 bits

• Data rate: various depending on single, dual, or quad mode

The configuration and Quad SPI flash memory section of the Zynq UltraScale+ Device

Technical Reference Manual (UG1085) [Ref 3] provides details on using the memory. For

more Quad SPI details, see the Micron MT25QU02GCBB8E12-0SIT data sheet at the Micron

website [Ref 15].

The connections between the Quad SPI flash memory and XCZU28DR PS bank 500 are

referenced in Appendix B, Xilinx Design Constraints.

GPIO (MIO 13, 38)

These two GPIO bits are connected to the U42 MSP430 system controller for general

purpose signaling or communications between the Zynq UltraScale+ RFSoC device and the

MSP430 system controller. These signals are level-shifted by TSX0108E U41. The

connections between the U42 system controller and the XCZU28DR RFSoC are listed in

Tab l e 3- 3.

Table 3-3: System Controller U42 GPIO Connections to XCZU28DR U1

XCZU28DR (U1)

Pin

E27 MIO38_PS_GPIO1 P1_6 19

R28 MIO13_PS_GPIO2 P1_7 20

Net Name

Pin Name Pin #

MSP430 U42

ZCU111 Board User Guide 27

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 28

X-Ref Target - Figure 3-2

Zynq UltraScale+

RFSoc PS-Side

RFSoC PL-Side

I2C0

PS_I2C0

PS_I2C1

PL_I2C0

PL_I2C1

0x74

0

1

2

3

4

5

6

7

EEPROM

SI5341

USER_SI570

USER_MGT_S1570

SI5328

I2CSP1

RFMC

N.C.

12C

Mux

#1

0x75

0

1

2

3

4

5

6

7

FMC+ HSPC

N.C.

SYSMON (DNP resistors)

PS_DDR4_SODIMM

SFP283

SFP282

SFP281

SFP280

12C

Mux

#2

0x75

0

1

2

3

INA226 PMBus

N.C.

IRPS5401 PS + PL Voltage Controller PMBus

SYSMON

12C

Mux

#3

PMBus Cable

0x20

GPIO

Expander

U22 TCA6416A

System Controller

P3

P4

U42 MSP430

U23 PCA9544A

I2C0

J19

I2C1

U27 TCA9548A

U26 TCA9548A

I2C1

U1 XCZU28DR

L/S

U19

L/S

U20

L/S

U25

L/S

U24

X20530-062118

Send Feedback

Chapter 3: Board Component Descriptions

I2C0 (MIO 14-15), I2C1 (MIO 16-17)

Figure 3-2 shows a high-level view of the I2C0 and I2C1 bus connectivity.

Figure 3-2: I2C0 and I2C1 Bus Connectivity Overview

ZCU111 Board User Guide 28

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 29

X-Ref Target - Figure 3-3

TCA6416A

P00

P01

P02

P04

P05

P06

MAX6643_OT_B

MAX6643_FANFAIL_B

MI026_PMU_INPUT_LS

SFP28_SI5328_INT_ALM

IIC_MUX_RESET_B

GEM3_EXP_RESET_B

SDA/

SCL

BANK 500

PS I2C0

MIO15/

MIO14

U1

BANK 64

PL I2C0

AW16/AT16

U1

MPS430

U42

22 P3_0

23 P3_1

L/S

U19

0x20

P10

P11

P12

P16

P17

FMC_HSPC_PRSNT_M2C_B

CLK_SPI_MUX_SEL0

CLK_SPI_MUX_SEL1

IRPS5401_ALERT_B

INA226_PMBUS_ALERT

U20

TCA6416A

SDA/

SCL

0x75

INA226_PMBUS_SCA/SCL

Not Connected

IRPS5401_PMBUS_SDA/SCL

SYSMON_SCA/SCL

U23

SD0/SC0

SD1/SC1

SD2/SC2

SD3/SC3

U22

I2C0_SDA/SCL

L/S

X20531-062118

Send Feedback

Chapter 3: Board Component Descriptions

I2C0 (MIO 14-15)

[Figure 2-1, callout 13]

The I2C bus I2C0 connects the RFSoC U1 PS bank 500, PL bank 64, and the system controller

U42 to a GPIO 16-bit port expander (TCA6416A U22) and I2C switch (PCA9544A U23). The

port expander enables controlling resets and power system enable pins, and accepting

various alarm inputs without requiring the PL-side to be configured. The I2C0 bus also

provides access to the PMBus power controllers and the INA226 power monitors via the

U23 PCA9544A switch. TCA6416A U22 is pin-strapped to respond to I2C address 0x20. The

PCA9544A U23 switch is set to 0x75.

The devices on each port of the I2C0 U22 TCA6416A port expander are listed in Tab l e 3- 4 ,

and the devices on each bus of the I2C0 U23 PCA9544A switch are listed in Ta bl e 3 - 5.

Figure 3-3 shows a high-level view of the I2C0 bus connectivity represented in Ta bl e 3 -4

and Tab le 3-5 .

ZCU111 Board User Guide 29

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-3: I2C0 Bus Topology

Page 30

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-4: I2C0 Port Expander TCA6416A U22 Addr. 0x20 Connections

TCA6416A

Connected To

U22

Schematic Net Name

Pin

Name

SDA 23 I2C0_SDA

SCL 22 I2C0_SCL

P00 4 MAX6643_OT_B 9 OT_B U52 MAX6643

P01 5 MAX6643_FANFAIL_B 4 FANFAIL_B U52 MAX6643

P02 6 MIO26_PMU_INPUT_LS G25 PS_MIO26 U1 XCZU28DR

P04 8 SFP_SI5382_INT_ALM 12 INTRB U48 SI5382A

P05 9 IIC_MUX_RESET_B 3 RESET_B U26,U27 TCA9548A

P06 10 GEN3_EXP_RESET_B 2 B U14 SN74LVC1G08

P10 13 FMCP_HSPC_PRSNT_M2C_B

P11 14 CLK_SPI_MUX_SEL0 14 S0 U97 IDTQS3VH253QG8

Pin

No.

Pin

No.

4 OE U45 NC7SZ66P5X

H2 PRSNT_M2C_L J26(H) ASP_184329_01

Z1 PRSNT_M2C_L J26(Z) ASP_184329_01

Pin Name

Refer to connections shown in Figure 3-3.

TCA6416A U22 Addr. 0x20

Reference

Designator

Device

P12 15 CLK_SPI_MUX_SEL1 2 S1 U97 IDTQS3VH253QG8

11 INT2_B U23 PCA9544A

P16 19 IRPS5401_ALERT_B

P17 20 INA226_PMBUS_ALERT

17 ALERT_B U53,U55,U57 IRPS5401

17 SALERT_B U68,U70,U74,U75 IR38060

4 INT0_B U23 PCA9544A

3ALERT

3ALERT

U3,U59-U61

U63-U66

INA226

U67,U69,U71,U73,

U77,U79

ZCU111 Board User Guide 30

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 31

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-5: I2C0 Multiplexer PCA9544A U23 Addr. 0x75 Connections

PCA9544A U23

Pin

Name

SDA 19 I2C0_SDA

SCL 18 I2C0_SCL

Notes:

1. SYSMON SDA/SCL are level-shifted via U99.

Pin No. Pin No. Pin Name Reference Designator Device

Port Mux'd I2C Bus

0 INA226_PMBUS_SDA/SCL 4/5 SDA/SCL See P17 in Tab le 3 -4 INA226

2 IRPS5401_SDA/SCL 19/18 DATA/CLK U53,U55,U57 IRPS5401

3 SYSMON_SDA/SCL D11/B12 Bank 68 U1

Schematic Net Name

I2C1 (MIO 16-17)

[Figure 2-1, callout 14]

The I2C bus I2C1 connects the RFSoC U1 PS bank 500, PL bank 64, and system controller

U42 to two I2C switches (TCA9548A U26 and U27). These I2C1 connections enable I2C

communications with other I2C capable target devices. TCA9548A U26 is pin-strapped to

respond to I2C address 0x74. TCA9548A U27 is pin-strapped to respond to I2C address

0x75. Figure 3-4 shows a high-level view of the I2C1 bus connectivity represented in

Tab l e 3- 6 and Ta ble 3 -7.

Connected To

Refer to connections shown in Figure 3-3.

PCA9544A U23 Addr. 0x75

(1)

XCZU28DR

ZCU111 Board User Guide 31

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 32

X-Ref Target - Figure 3-4

TCA9548A

SD0/SC0

SD1/SC1

SD2/SC2

SD3/SC3

SD4/SC5

SD5/SC5

SD6/SC6

SD7/SC7

IIC_EEPROM_SDA/SCL

S15341_SDA/SCL

USER_S1570_SDA/SCL

USER_MGT_S1570_SDA/SCL

SI5382_SDA/SCL

I2C2SPI_SDA/SCL

RFMC_I2C_SDA/SCL

NOT CONNECTED

SDA/SCL

BANK 500

PS I2C1

U1

BANK 64

U1

MPS430

U42

28 P4_1

29 P4_2

L/S

U24

0x74

U25

U26

I2C1_SDA/SCL

L/S

MIO17/

MIO16

PL I2C1

AL21/AH19

TCA9548A

SD0/SC0

SD1/SC1

SD2/SC2

SD3/SC3

SD4/SC5

SD5/SC5

SD6/SC6

SD7/SC7

FMCP_HSPC_II_SDA/SCL

NOT CONNECTED

SYSMON_SDA/SCL

PS_DDR4_SODIMM_SDA/SCL

SFP3_IIC_SDA/SCL

SFP2_IiC_SDA/SCL

SFP1_IiC_SDA/SCL

SFP0_IIC_SDA/SCL

SDA/SCL

0x75

U27

X20532-062118

Send Feedback

Chapter 3: Board Component Descriptions

ZCU111 Board User Guide 32

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-4: I2C1 Bus Topology

Page 33

Table 3-6: I2C1 TCA9548A U26 Adr. 0x74 Connections

Send Feedback

Chapter 3: Board Component Descriptions

TCA9548A U26

(Addr 0x74)

I2C1 Bus Device

Target Devic e

Port

0 EEPROM U88 0X54

1 Si5341 clock U46 0x36

2 USER Si570 clock U47 0X5D

3 USER MGT Si570 clock U49 0X5D

4 Si5382 (SFP28 ClK recovery) U48 0x68

5 SC18IS602B U93 0x2F

6 LPAF-40 J47 connector USER

7 No connection NA

Table 3-7: I2C1 TCA9548A U27 Adr. 0x75 Connections

TCA9548A U27

(Addr 0x75)

I2C1 Bus Device

Target Device

Port

0 FMCP HSPC J26 0x##

1 Not connected NA

2 SYSMON U1 BANK 68 0x32

Address

Address

3 PS DDR4 SODIMM SKT. J50 0x51

4 SFP3 P2 0x50

5 SFP2 P1 0x50

6 SFP1 P2 0x50

7 SFP0 P1 0x50

For more information on the TCA9548A and PCA9544A, see the Texas Instruments website

[Ref 20].

ZCU111 Board User Guide 33

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 34

X-Ref Target - Figure 3-5

X20481-062118

Send Feedback

Chapter 3: Board Component Descriptions

UART0 (MIO 18-19)

[Figure 2-1, callout 7]

This is the primary Zynq UltraScale+ RFSoC PS-side UART interface and is connected to the

FTDI U34 FT4232HL USB-to-Quad-UART bridge port B through TXS0108E level-shifter U21.

The FT4232HL U34 port assignments are listed in Tabl e 3-8 . The FT4232HL UART interface

circuit is shown in Figure 3-5.

Table 3-8: FT4232HL Port Assignments

FT4232HL U34 Zynq UltraScale+ RFSoC U1

Port A JTAG ZCU111 JTAG chain

Port B UART0 PS_UART0 (MIO 18-19)

Port C UART2 PL_UART2 bank 64

Port D UART3 U42 system controller UART

ZCU111 Board User Guide 34

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-5: ZCU111 FT4232HL UART Connections

Page 35

The FT4232HL U34 UART connections are listed in Ta ble 3 -9.

Send Feedback

Table 3-9: FT4232HL UART Connections

Chapter 3: Board Component Descriptions

FT4232HL

U34 Pin

26 LS_UART0_TXD_OUT U21 UART0_TXD_MIO18_RXD U1 Y27

27 LS_UART0_RXD_IN U21 UART0_RXD_MIO19_TXD U1 W28

38 LS_UART2_TXD_OUT U21 UART2_TXD_FPGA_RXD U1 AT15

39 LS_UART0_RXD_IN U21 UART2_RXD_FPGA_TXD U1 AU15

40 LS_UART2_RTS_B U21 UART2_RTS_B U1 AU14

41 LS_UART2_CTS_B U21 UART2_CTS_B U1 AT14

48 UART3_TXD_O_MSP430_UCA0_RXD NA NA U42 26

52 UART3_RXD_I_MSP430_UCA0_TXD NA NA U42 25

For more information on the FT4232HL, see the Future Technology Devices International Ltd

website [Ref 26].

Schematic Net Name

Level

Shifter

Level-Shifted Net Name

Targ et UA RT

Ref Des., Pin

UART1 (MIO 20-21)

The PS-side UART1 is not connected.

GPIO (MIO 22-23)

The PS-side pushbutton SW19 is connected to MIO22 (pin U1.Y28). The PS-side LED DS50,

which is physically placed adjacent to the pushbutton, is connected to MIO23 (pin U1.U29).

CAN1 (MIO 24-25)

The PS-side CAN bus TX and RX MIO pins are not connected.

PMU GPI (MIO 26)

The PS-side MIO 26 is reserved as an input to the PMU for indicating a warm boot. PS bank

501 MIO26 (U1.G25) is connected to the I2C0 U22 TCA6416A bus expander (port P02 U22.6)

through a 0Ω series resistor R92. See the Zynq UltraScale+ Device Technical Reference

Manual (UG1085) [Ref 3] for more details about the PMU interface.

DPAUX (MIO 27-30)

[Figure 2-1, callout 29]

The Zynq UltraScale+ RFSoC provides a VESA DisplayPort 1.2 source-only controller that

supports up to two lanes of main link data at ra tes of 1.6 2 Gb/s, 2.70 Gb/s, or 5.40 Gb/s. The

ZCU111 Board User Guide 35

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 36

Chapter 3: Board Component Descriptions

X20482-062118

Send Feedback

DisplayPort standard defines an auxiliary channel that uses LVDS signaling at a 1 Mb/s data

rate, which is translated from single-ended MIO signals to the differential DisplayPort AUX

channel, DPAUX (see Ta b le 3 - 10). The DisplayPort circuit is shown in Figure 3-6.

Table 3-10: DPAUX/MIO Connections

X-Ref Target - Figure 3-6

XCZU28DR (U1) Pin Net Name

SN74AVC4T245 Level Shifter U10

Pin Name Pin #

D25 MIO30_DP_AUX_IN 2A1 8

B25 MIO29_DP_OE 1A2 7

F25 MIO28_DP_HPD 2A2 9

C25 MIO27_DP_AUX_OUT 1A1 6

ZCU111 Board User Guide 36

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-6: DisplayPort Circuit

Page 37

Chapter 3: Board Component Descriptions

Send Feedback

PMU GPO (MIO 32-37)

The platform management unit (PMU) in the Zynq UltraScale+ RFSoC device signals power

domain changes using the PMU output pins. The Zynq UltraScale+ RFSoC device PMU GPO

pins are connected to inputs of the MSP430 system controller via TXS0108E level-shifter

U41. The RFSoC U1 bank 501 and MSP430 U42 pin numbers are listed in Ta bl e 3 - 11.

Table 3-11: XCZU28DR U1 to MSP430 Connections

XCZU28DR

(U1) Pin

F26 MIO37_PMU_GPO5 P1_0 13

C27 MIO36_PMU_GPO4 P1_1 14

E26 MIO35_PMU_GPO3 P1_2 15

B27 MIO34_PMU_GPO2 P1_3 16

A27 MIO33_PMU_GPO1 P1_4 17

A26 MIO32_PMU_GPO0 P1_5 18

Through the I2C0 bus RFSoC MIO pins, the PMU has access to the board power controllers

and power monitors. See Figure 3-3, page 29 for more details.

See the Zynq UltraScale+ Device Technical Reference Manual (UG1085) [Ref 3] for more

details about the PMU interface.

Net Name

Pin Name Pin #

MSP430 U42

SD1 (MIO 39-51)

A PS-side interface to an SD card connector is provided for booting and file system storage.

This interface is used for the SD boot mode and supports SD3.0 access post boot.

ZCU111 Board User Guide 37

UG1271 (v1.1) August 6, 2018 www.xilinx.com

SD Card Interface

[Figure 2-1, callout 6]

The ZCU111 board includes a secure digital input/output (SDIO) interface to provide access

to general purpose non-volatile SDIO memory cards and devices. Information for the SD

I/O card specification can be found at the SanDisk Corporation [Ref 17] or SD Association

[Ref 18] websites. The ZCU111 SD card interface supports the SD1_LS configuration boot

mode documented in the Zynq UltraScale+ Device Technical Reference Manual (UG1085)

[Ref 3].

The SDIO signals are co nnect ed to XCZU28DR RFSoC PS ba nk 501 , which has it s VCCMIO set

to 1.8V. The six SD interface nets MIOxx_SDIO_DAT[0:3], MIO50_SDIO_CMD, and

MIO51_SDAIO_CLK each have a series 30Ω resistor at the bank 501 source. An NXP

IP4856CX25 SD 3.0-compliant voltage level-translator U107 is present between the

XCZU28DR RFSoC and the SD card connector (J100). The NXP IP4856CX25 U107 device

provides SD3.0 capability with SDR104 performance.

Page 38

X-Ref Target - Figure 3-7

X20483-062118

Send Feedback

Chapter 3: Board Component Descriptions

Figure 3-7 shows the connections of the SD card interface on the ZCU111 board.

Figure 3-7: SD Card Interface

The NXP SD3.0 level shifter is mounted on an Aries adapter board that has the pin mapping

shown in Tab l e 3- 1 2.

Table 3-12: IP4856CX25 U107 Adapter Pin-Out

Aires Adapter Pin

Number

1 C1 CLK_IN

2 C3 GND

3 D3 CD

4 D2 CMD_H

5 E2 CLK_FB

6 E4 WP

7 B4 VLDO

8 C4 VSD_REF

9 A3 DIR_0

10 A4 VSUPPLY

11 B3 VCCA

IP4856CX25 U107 Pin

Number

IP4856CX25 U107 Pin

Name

ZCU111 Board User Guide 38

UG1271 (v1.1) August 6, 2018 www.xilinx.com

12 A2 DIR_CMD

13 D1 DATA0_H

14 B2 SEL

15 B1 DATA3_H

Page 39

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-12: IP4856CX25 U107 Adapter Pin-Out (Cont’d)

Aires Adapter Pin

Number

16 E1 DATA1_H

17 E3 DIR_1_3

18 A1 DATA2_H

19 E5 DATA1_SD

20 D5 DATA0_SD

21 C5 CLK_SD

22 D4 CMD_SD

23 B5 DATA3_SD

24 A5 DATA2_SD

25 C2 ENABLE

IP4856CX25 U107 Pin

Number

IP4856CX25 U107 Pin

Name

The connections between the SD NXP IP4856CX25 (U107) level-shifter and the XCZU28DR

RFSoC PS bank 501 are referenced in Appendix B, Xilinx Design Constraints.

USB0 (MIO 52-63)

The USB interface on the PS-side serves multiple roles as a host or device controller. The

USB 3.0 interface is supported by the RFSoC GTR interface while the USB 2.0 capabilities of

the SMSC USB3320C controller are shared on a common USB 3.0 micro USB type A

connector (J96).

USB 3.0 Transceiver and USB 2.0 ULPI PHY

[Figure 2-1, callout 5]

The ZCU111 board uses a Standard Microsystems Corporation USB3320 USB 2.0 ULPI

transceiver at U12 to support a USB connection to the host computer (see Figure 3-8). A

USB cable is supplied in the ZCU111 evaluation kit (standard-A connector to host computer,

USB 3.0 A connector to ZCU111 board connector J96). The USB3320 is a high-speed USB 2.0

PHY supporting the UTMI+ low pin interface (ULPI) interface standard. The ULPI standard

defines the interface between the USB controller IP and the PHY device, which drives the

physical USB bus. Using the ULPI standard reduces the interface pin count between the USB

controller IP and the PHY device.

ZCU111 Board User Guide 39

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 40

Chapter 3: Board Component Descriptions

USB

MIO

SM3320

USB2.0

ULPI

USB3

Connector

USB

GTR

GTR Tx, Rx

X20533-062118

Send Feedback

X-Ref Target - Figure 3-8

Figure 3-8: USB Interface

The USB3320 is clocked by a 24 MHz crystal (X2). See the Standard Microsystems

Corporation (SMSC) USB3320 data sheet for clocking mode details [Ref 16]. The interface to

the USB3320 PHY is implemented through the IP in the XCZU28DR RFSoC PS.

Tab l e 3- 13 describes the jumper settings for the USB 2.0 circuit.

Note:

The bold text in Tabl e 3 -1 3 identifies the default shunt positions for USB 2.0 high-speed

on-the-go (OTG) mode.

Table 3-13: USB Jumper Settings

Header Function Shunt Position Notes

J18 VBUS select

J17 Shield select

ON = Device mode (150 µF) and VBus power source

OFF = Device mode (5.7 µF)

Position 2-3 = Shield connected to GND

Position 1-2 = Shield floating

VBUS load capacitance

Optional C171 in position 1-2

Note: The shield for the USB 3.0 micro-B connector (J96) can be tied to GND by a jumper on header

J17 pins 2-3 (default). The USB shie ld can optionally be connected through a series capacitor to GND

by installing a capacitor (body size 0402) at location C171 and jumping pins 1-2 on header J17.

The USB3320 ULPI U12 transceiver circuit (see Figure 3-9) has a Micrel MIC2544 high-side

programmable current limit switch (U13). This switch has an open-drain output fault flag on

pin 2, which turns on LED DS7 if over current or thermal shutdown conditions are detected.

DS7 is located in the U13 circuit area (Figure 2-1, callout 53). Figure 3-9 shows the ULPI U12

transceiver circuit.

ZCU111 Board User Guide 40

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 41

X-Ref Target - Figure 3-9

X20484-062118

GEM

MIO

RGMII

MDIO

TI

DP83867IR

RJ45 and

Magnetics

X20534-062118

Send Feedback

Chapter 3: Board Component Descriptions

Figure 3-9: USB3320 ULPI Transceiver Circuit

The connections between the USB 2.0 PHY (U12) and the XCZU28DR RFSoC PS bank 502 are

referenced in Appendix B, Xilinx Design Constraints.

GEM3 Ethernet (MIO 64-77)

The PS-side Gigabit Ethernet MAC (GEM) implements a 10/100/1000 Mb/s Ethernet

interface (see Figure 3-10), which connects to a TI DP83867IRPAP Ethernet RGMII PHY

before being routed to an RJ45 Ethernet connector. The RGMII Ethernet PHY is boot

strapped to PHY address 5'b01100 (0x0C) and Auto Negotiation is set to Enable. The

communication with the device is described in the DP83867 RGMII PHY data sheet [Ref 20].

X-Ref Target - Figure 3-10

Figure 3-10: Ethernet Block Diagram

ZCU111 Board User Guide 41

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 42

Chapter 3: Board Component Descriptions

Send Feedback

10/100/1000 MHz Tri-Speed Ethernet PHY

[Figure 2-1, callout 12]

The ZCU111 board uses the TI DP83867IRPAP Ethernet RGMII PHY [Ref 20] (U37) for

Ethernet communications at 10 Mb/s, 100 Mb/s, or 1000 Mb/s. The board supports RGMII

mode only. The PHY connection to a user-provided Ethernet cable is through a Wurth

7499111221A RJ-45 connector (P12) with built-in magnetics. The Ethernet connections from

XCZU28DR RFSoC U1 to the DP83867IRPAP PHY device at U37 are listed in Table 3 -14 .

Table 3-14: DP83867 PHY Connections to XCZU28DR RFSoC

XCZU28DR

(U1) Pin

J31 MIO64_ENET_TX_CLK 40 GTX_CLK

J32 MIO65_ENET_TX_D0 38 TX_DO

J34 MIO66_ENET_TX_D1 37 TX_D1

K28 MIO67_ENET_TX_D2 36 TX_D2

K29 MIO68_ENET_TX_D3 35 TX_D3

K30 MIO69_ENET_TX_CTRL 52 TX_EN_TX_CTRL

K31 MIO70_ENET_RX_CLK 43 RX_CLK

K32 MIO71_ENET_RX_D0 44 RX_DO

K33 MIO72_ENET_RX_D1 45 RX_D1

K34 MIO73_ENET_RX_D2 46 RX_D2

L29 MIO74_ENET_RX_D3 47 RX_D3

L30 MIO75_ENET_RX_CTRL 53 RX_DV_RX_CTRL

L33 MIO76_ENET_MDC 20 MDC

L34 MIO77_ENET_MDIO 21 MDIO

Net Name

DP83867 PHY U37

Pin # Pin Name

ZCU111 Board User Guide 42

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 43

X-Ref Target - Figure 3-11

X20485-062118

Send Feedback

Chapter 3: Board Component Descriptions

Ethernet PHY Reset

[Figure 2-1, callout 12]

The DP83867IRPAP PHY U37 LED interface is shown in Figure 3-11. The DP83867IRPAP can

be reset by the GEN3_EXP_RESET_B signal via the I2C0 TCA6416A U22 bus expander P06 pin

10 or the PS_POR_B signal generated by the MAX16025 U6 POR device pin 11. The SW3

pushbutton at the MAX16025 U6 pin 6 input also triggers a PS_POR_B signal.

Figure 3-11: Ethernet PHY Reset Circuit

Ethernet PHY LED Interface

[Figure 2-1, callout 9]

The DP83867IRPAP PHY U37 LED interface (LED_0, LED_2) uses the two LEDs embedded in

the P12 RJ45 connector bezel. The LED functional description is listed in Ta ble 3 -15.

Table 3-15: Ethernet PHY LED Functional Description

DP83867IR PHY U37 Pin

Name Number

LED_2 61 S, I/O, PD

LED_1 62 S, I/O, PD

LED_0 63 S, I/O, PD

Type Description

By default, this pin indicates receive or transmit

activity. Additional functionality is configurable using

LEDCR1[11:8] register bits.

This pin is a strap configuration pin for RGZ devices

Note:

only.

By default, this pin indicates that 100BASE-T link is

established. Additional functionality is configurable

using LEDCR1[7:4] register bits.

By default, this pin indicates that link is established.

Additional functionality is configurable using

LEDCR1[3:0] register bits.

ZCU111 Board User Guide 43

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 44

X-Ref Target - Figure 3-12

JTAG

2 mm 2X7

Header

J13

TDO

TDI

FT4232HL

UART

BRIDGE

U34

TDO

TDI

JTAG

IF

PS Config

Bank 503

U1

TDI

TDO

JTAG

TDI

BUF

U32

AB

U45

JTAG

TDO

BUF

U30

BA

FMCP HSPC

Connector

(D)

J26

TDI TDO

N.C.

X20535-062118

Send Feedback

Chapter 3: Board Component Descriptions

The LED functions can be repurposed with a LEDCR1 register write available via the PHY's

management data interface, MDIO/MDC. LED_2 is assigned to ACT (activity indicator) and

LED_0 indicates link established. For more Ethernet PHY details, see the TI DP83867 data

sheet [Ref 20]. LED_1 (100BASE-T link established) is a separate LED DS27 located on the

top side of the board near the RJ45 P12 connector (Figure 2-1, callout 12).

Programmable Logic JTAG Programming Options

[Figure 2-1, callouts 7 and 63]

ZCU111 JTAG chain:

• J83 USB micro AB connector connected to U34 FT4232HL USB-JTAG bridge

• J13 2x7 2 mm shrouded, keyed JTAG pod flat cable connector

The ZCU111 board JTAG chain is shown in Figure 3-12.

ZCU111 Board User Guide 44

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-12: JTAG Chain Block Diagram

Page 45

Chapter 3: Board Component Descriptions

Send Feedback

FMC Connector JTAG Bypass

When an FPGA mezzanine card (FMC) is attached to J26, it is automatically added to the

JTAG chain through electronically controlled single-pole single-throw (SPST) switch U45.

The SPST switch is normally closed and transitions to an open state when an FMC is

attached. Switch U45 adds an attached FMC to the JTAG chain as determined by the

FMCP_HSPC_PRSNT_M2C_B signal. The attached FMC card must implement a TDI-to-TDO

connection using a device or bypass jumper to ensure that the JTAG chain connects to the

U1 XCZU28DR RFSoC.

Clock Generation

The ZCU111 board provides fixed and variable clock sources for the XCZU28DR RFSoC.

Tab l e 3- 16 lists the source devices for each clock.

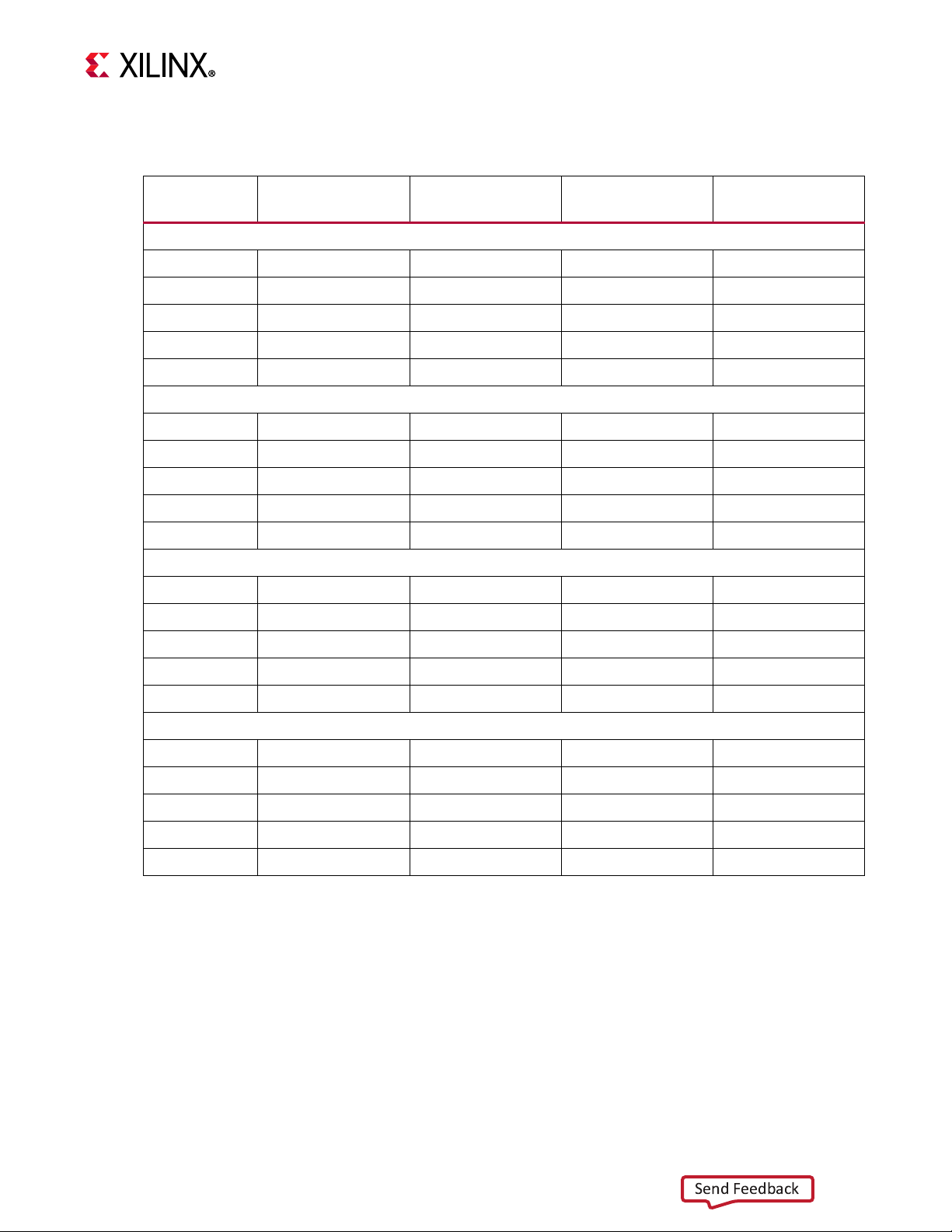

Table 3-16: Clock Sources

Clock (Net) Name Frequency Clock Source

Fixed Frequency Clocks

PS_REF_CLK 33.33 MHz

CLK_100 100 MHz

CLK_125 125 MHz

GTR_REF_CLK_SATA 125 MHz

GTR_REF_CLK_USB3 26 MHz

GTR_REF_CLK_DP 27 MHz

Programmable Frequency Clocks

USER_SI570 300 MHz (default) U47 SI570 I2C PROG. OSC.

USER_MGT_SI570 156.25 MHz (default) U49 SI570 I2C PROG. OSC.

USER_SMA_MGT_CLOCK User-provided source J14 (P)/J15 (N) SMA CONN.

SFP_SI5382_CLOCKS Variable U48 SI5382A clock recovery

U46 SI5341B clock generator

ZCU111 Board User Guide 45

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 46

Tab l e 3- 17 lists the connections for each clock.

Send Feedback

Table 3-17: Clock Connections to XCZU28DR U1

Chapter 3: Board Component Descriptions

Clock Source Ref.

Des. and Pin

Net Name I/O Standard

U46 SI5341B Clock Generator

U46.59 PS_REF_CLK (series R310)

(1)

U46.45 CLK_125_P LVDS AL17

U46.44 CLK_125_N LVDS AM17

U46.42 CLK_100_P LVDS AM15

U46.41 CLK_100_N LVDS AN15

U46.35 GTR_REF_CLK_SATA_P

U46.34 GTR_REF_CLK_SATA_N

U46.31 GTR_REF_CLK_USB3_P

U46.30 GTR_REF_CLK_USB3_N

U46.24 GTR_REF_CLK_DP_P

U46.23 GTR_REF_CLK_DP_N

(2)

(2)

(2)

(2)

(2)

(2)

U47 SI570 I2C Prog. Oscillator (300 MHz default)

U47.4 USER_SI570_P LVDS J19

U47.5 USER_SI570_N LVDS J18

XCZU28DR (U1)

Pin

AC30

AC34

AC35

AE34

AE35

AG34

AG35

U49 SI570 I2C Prog. Oscillator (156.250 MHz default)

U49.4 USER_MGT_SI570_P

U49.5 USER_MGT_SI570_N

J14 (P)/J15 (N) SMA Connectors

J14 USER_SMA_MGT_CLOCK_P

J15 USER_SMA_MGT_CLOCK_N

U48 SI5382A Clock Recovery

U48.1 SFP_SI5382_IN1_P

U48.2 SFP_SI5382_IN1_N

U48.21 SFP_SI5382_OUT_P

U48.20 SFP_SI5382_OUT_N

U48.63 SFP_REC_CLOCK_P LVDS

U48.64 SFP_REC_CLOCK_N LVDS

Notes:

1. U1 XCZU28DR bank 503 supports LVCMOS18 level inputs.

2. Series capacitor coupled, U1 MGT (I/O standards do not apply).

3. Series capacitor coupled.

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(3)

(3)

V31

V32

T31

T32

AA33

AA34

Y31

Y32

AW14

AW13

ZCU111 Board User Guide 46

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 47

X-Ref Target - Figure 3-13

X20486-062118

Send Feedback

Chapter 3: Board Component Descriptions

SI5341B 10 Independent Output Any-Frequency Clock Generator

[Figure 2-1, callout 8]

• Clock generator: Silicon Labs SI5341B-D07833-GM

• Jitter: <100 fs RMS typical

• Differential and single-ended outputs

The SI5341B is a one-time programmable clock source. The clock circuit is shown in

Figure 3-13.

ZCU111 Board User Guide 47

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-13: SI5341B Clock Generator

Page 48

Chapter 3: Board Component Descriptions

X20487-062118

Send Feedback

Programmable User SI570 Clock

[Figure 2-1, callout 9]

The ZCU111 board has an I2C programmable SI570 low-jitter 3.3V LVDS differential

oscillator (U47) connected to the GC inputs of PL bank 69. The USER_SI570_P and

USER_SI570_N clock signals are connected to XCZU28DR RFSoC U1 pins J19 and J18,

respectively. At power-up, the user clock defaults to an output frequency of 300.000 MHz.

User applications can change the output frequency within the range of 10 MHz to 810 MHz

through the I2C1 bus interface. Power cycling the ZCU111 board reverts this user clock to

the default frequency of 300.000 MHz.

This oscillator can be reprogrammed from MSP430 system controller U42 (see TI MSP430

System Controller, page 88 for more system controller information and the ZCU111 web

page for the tutorial on the system controller user interface (XTP517) [Ref 11].

• Programmable oscillator: Silicon Labs Si570BAB001614DG (10 MHz-810 MHz, 300 MHz

default)

•LVDS differential output

X-Ref Target - Figure 3-14

• Total Stability: 61.5 ppm

The programmable user clock circuit is shown in Figure 3-14.

Figure 3-14: Programmable User Clock

ZCU111 Board User Guide 48

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Page 49

Chapter 3: Board Component Descriptions

X20488-062118

Send Feedback

Programmable User MGT SI570 Clock

[Figure 2-1, callout 10]

The ZCU111 board has a programmable low-jitter 3.3V LVDS SI570 differential oscillator

(U49) connected to the XCZU28DR U1 GTY bank 129. The USER_MGT_SI570_CLOCK_P and

USER_MGT_SI570_CLOCK_N clock signals are connected through series capacitors to

XCZU28DR RFSoC U1 pins V31 and V32, respectively. At power-up, the user clock defaults to

an output frequency of 156.250 MHz. User applications can change the output frequency

within the range of 10 MHz to 81 0 MHz through an I2C interface. Power c ycling the ZCU111

board reverts this user clock to the default frequency of 156.250 MHz.

This oscillator can be reprogrammed from MSP430 system controller U41 (see TI MSP430

System Controller, page 95 for more system controller information and the ZCU111 web

page for the tutorial on the system controller user interface (XTP517) [Ref 11].

• Programmable oscillator: Silicon Labs Si570BAB000544DG (10 MHz-810 MHz,

156.250 MHz default)

•LVDS differential output

X-Ref Target - Figure 3-15

• Total stability: 61.5 ppm

The programmable user clock MGT circuit is shown in Figure 3-15.

ZCU111 Board User Guide 49

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-15: Programmable User MGT Clock

Page 50

X-Ref Target - Figure 3-16

X20489-062118

Send Feedback

Chapter 3: Board Component Descriptions

User SMA MGT Clock

[Figure 2-1, callout 48]

The ZCU111 board provides a pair of SMAs for differential AC coupled user MGT clock input

into FPGA U1 GTY bank 130. This differential signal pair is series-capacitor coupled. The

P-side SMA J14 signal USER_SMA_MGT_CLOCK_P is connected to U1 MGTREFCLK1P pin T31,

and the N-side SMA J15 signal USER_SMA_MGT_CLOCK_N is connected to U1

MGTREFCLK1N pin T32. The transceiver reference clock pin absolute input voltage range is

–0.5V min. to 1.3V max. The user SMA MGT clock circuit is shown in Figure 3-16.

ZCU111 Board User Guide 50

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Figure 3-16: User SMA MGT Clock

Page 51

Chapter 3: Board Component Descriptions

Send Feedback

SI5382A SFP28 Clock Recovery

[Figure 2-1, callout 8]

The ZCU111 board includes a Silicon Labs SI5382A jitter attenuator U48. The RFSoC U1 PL

user logic can implement a clock recovery circuit and output this series capacitor coupled