XILINX XQV1000-4BG560N, XQV100-4PQ240N, XQV100-4CB228M, XQV100-4BG256N, XQV600-4HQ240N Datasheet

...

DS002 (v1.5) December 5, 2001

www.xilinx.com

1

Preliminary Product Specification

1-800-255-7778

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at

http://www.xilinx.com/legal.htm

.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

7

Features

• Certified to MIL-PRF-38535 (Qualified Manufacturer

Listing)

• Guaranteed over the full military temperature range

(–55°C to +125°C)

• Ceramic and Plastic Packages

• Fast, high-density Field-Programmable Gate Arrays

- Densities from 100K to 1M system gates

- System performance up to 200 MHz

- Hot-swappable for Compact PCI

• Multi-standard SelectI/O™ int erfaces

- 16 high-performance interface standards

- Connects directly to ZBTRAM devices

• Built-in clock-management circuitry

- Four dedicated delay-locked loops (DLLs) for

advanced clock control

- Four primary low-skew global clock distribution

nets, plus 24 secondary global nets

• Hierarchical memory system

- LUTs configurable as 16-bit RAM, 32-bit RAM,

16-bit dual-ported RAM, or 16-bit Shift Register

- Configurable synchronous dual-ported 4K-bit

RAMs

- Fast interfaces to external high-performance RAMs

• Flexible architecture that balances speed and density

- Dedicated carry logic for high-speed arithmetic

- Dedicated multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with clock enable, and

dual synchronous/asynchronous set and reset

- Internal 3-state bussing

- IEEE 1149.1 boundary-scan logic

- Die-temperatur e se ns ing device

• Supported by FPGA Foundation™ and Alliance

Development Systems

- Complete support for Unified Libraries, Relationally

Placed Macros, and Design Manager

- Wide selection of PC and workstation platforms

• SRAM-based in-system configuration

- Unlimited reprogrammability

- Four programming modes

•0.22 µm 5-la yer metal process

• 100% factory tested

• Available to Standard Microcircuit Drawings

- 5962-99572 for XQV300

- 5962-99573 for XQV600

- 5962-99574 for XQV1000

- Contact Defense Supply Center Columbus (DSCC)

for more information at

http://www.dscc.dla.mil

Description

The QPro™ Virtex™ FPGA family delivers high-performance, high-capacity programmable logic solutions. Dramatic increases in silicon efficiency result from optimizing

the new architecture for place-and-route efficiency and

exploiting an aggressive 5-layer-metal 0.22 µm CMOS process. These advances make QPro Virtex FPGAs powerful

and flexible alternatives to mask-programmed ga te arrays.

The Virtex family comprises the four members shown in

Table 1.

Building on experience gained from previous generations of

FPGAs, the Virtex family represents a revolutionary step

forward in programmable logic design. Combining a wide

variety of programmable system features, a rich hierarchy of

fast, flexible interconnect resources, and advanced process

technology, the QPro Virtex family delivers a high-speed

and high-capacity programmable logic solution that

enhances design flexibility while reducing time-to-market.

Refer to the “Virtex™ 2.5V Field Programmable Gate

Arrays” commercial data sheet for more information on

device architecture and timing specifications.

0

QPro Virtex 2.5V QML

High-Reliability FPGAs

DS002 (v1.5) December 5, 2001

02

Preliminary Product Specification

R

QPro Virtex 2.5V QML High-Reliability FPGAs

2

www.xilinx.com

DS002 (v1.5) December 5, 2001

1-800-255-7778

Preliminary Product Specification

R

Virtex Electrical Characteristics

Based on preliminary characterization. Further changes are not expected.

All specifications are representative of worst-case supply voltage and junction temperature conditions. The parameters

included are common to popula r designs and typical applica tions. Contact the factory for design considerations requi ring

more detailed information.

Virtex DC Characteristics

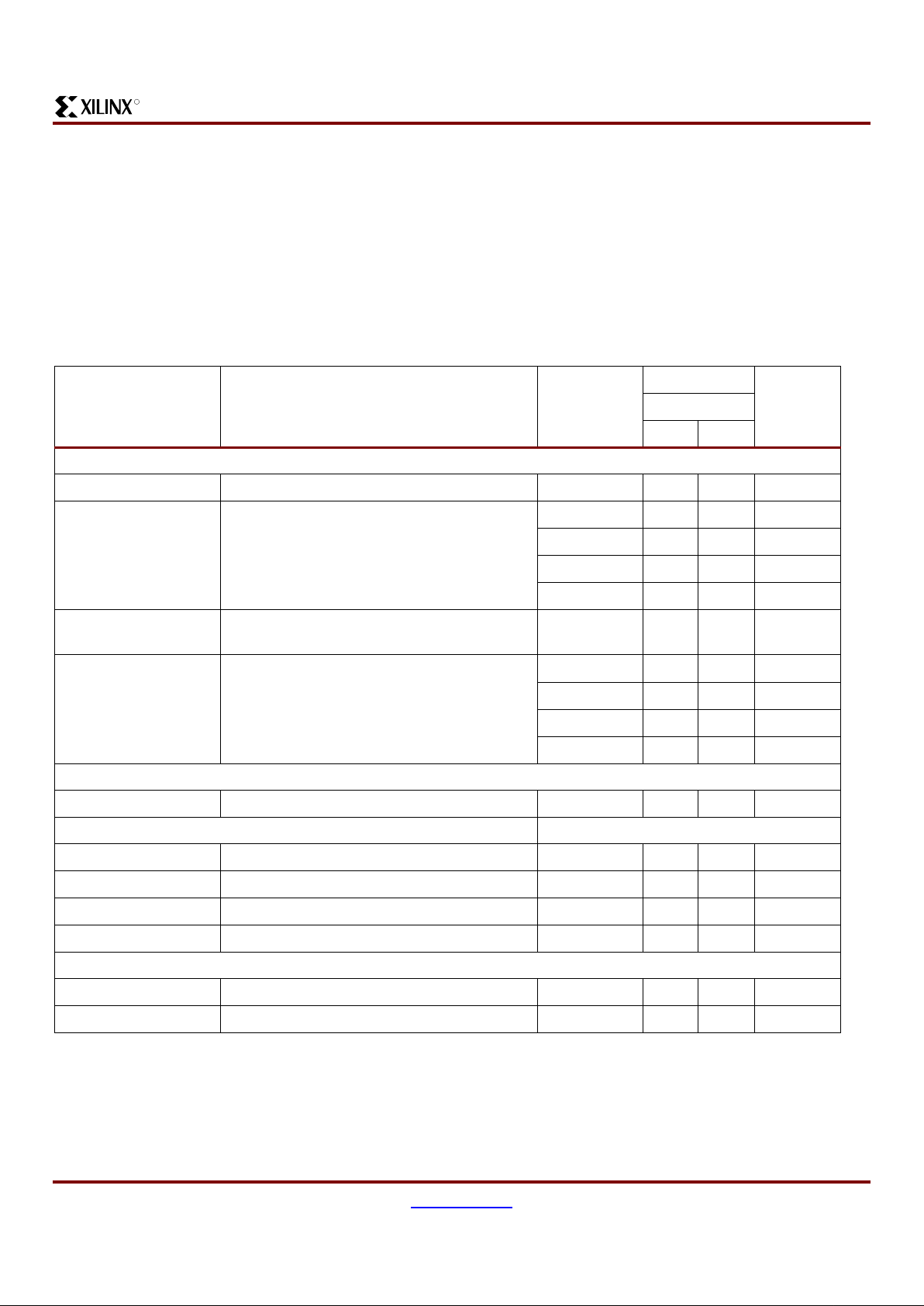

Absolute Maximum Ratings

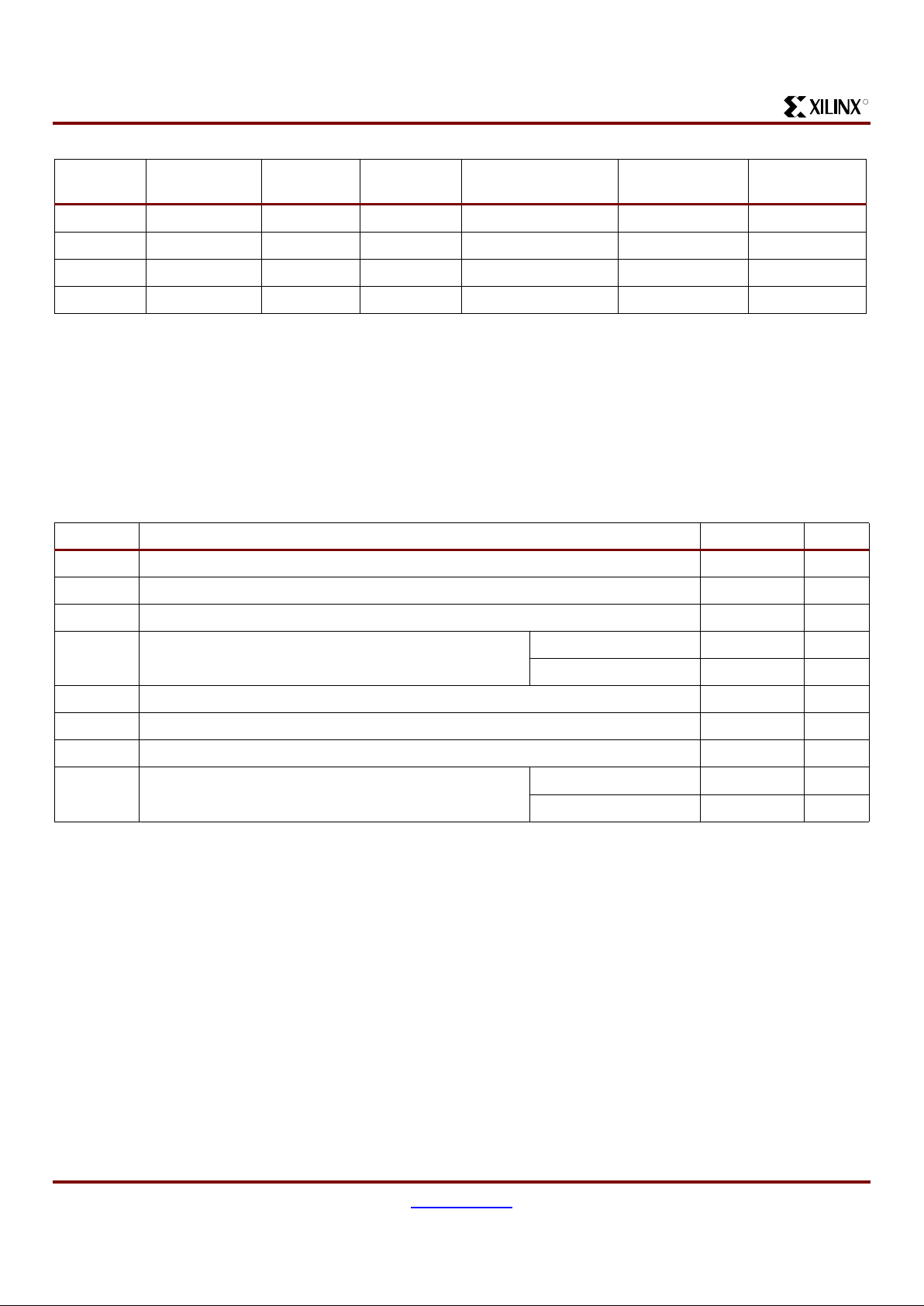

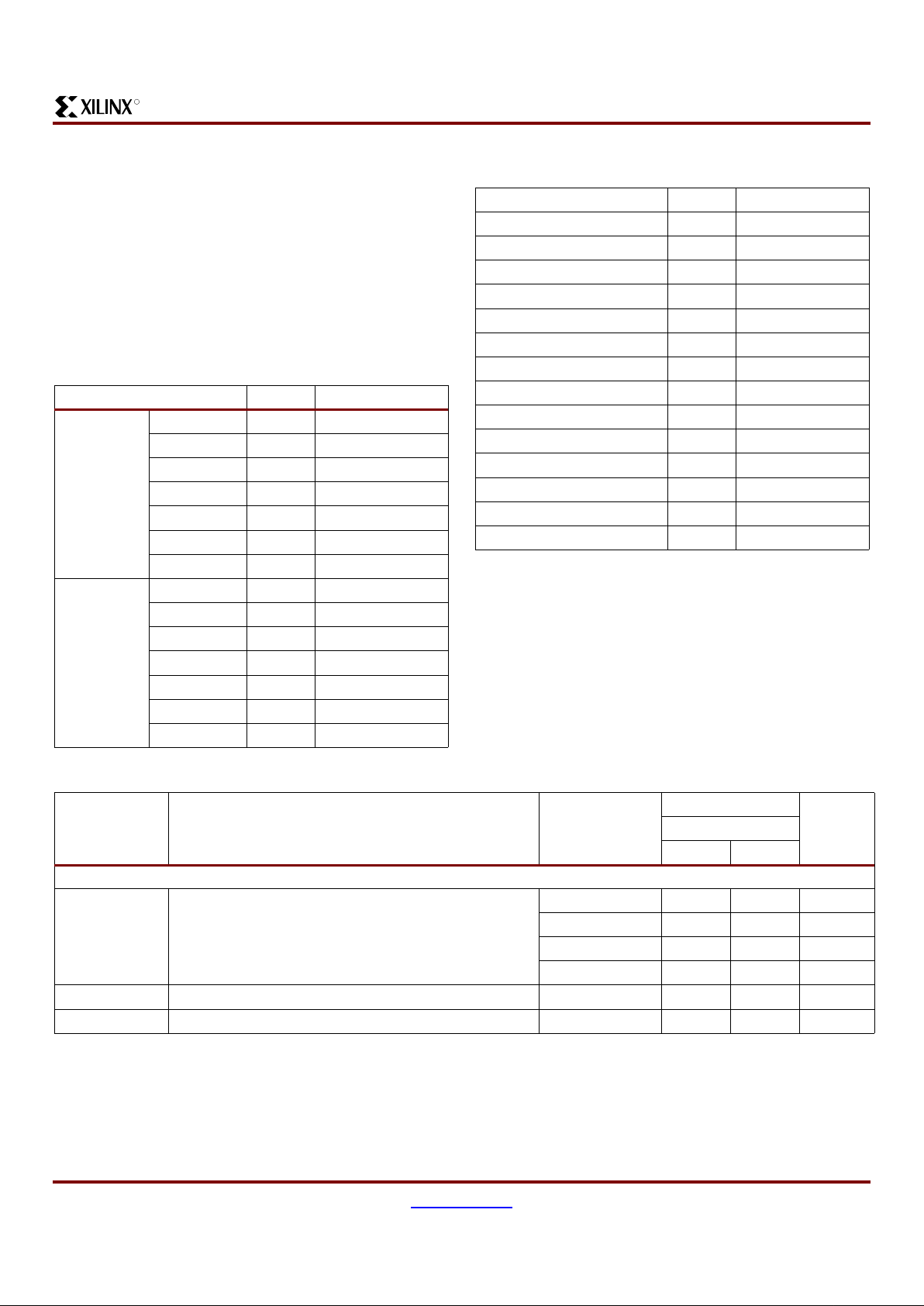

Table 1:

QPro Virtex Field-Programmable Gate Array Fa mily Members

Device System Gates CLB Array Logic Cells

Maximum

Available I/O Block RAM Bits

Max Select

RAM Bits

XQV100 108,904 20 x 30 2,700 180 40,960 38,400

XQV300 322,970 32 x 48 6,912 316 65,536 98,304

XQV600 661,111 48 x 72 15,552 316 98,304 221,184

XQV1000 1,124,022 64 x 96 27,648 404 131,072 393,216

Symbol Description Min/Max Units

V

CCINT

Supply voltage relative to GND –0.5 to 3.0 V

V

CCO

Supply voltage relative to GND –0.5 to 4.0 V

V

REF

Input reference Voltage –0.5 to 3.6 V

V

IN

(3)

Input voltage relative to GND Using V

REF

–0.5 to 3.6 V

Internal threshold –0.5 to 5.5 V

V

TS

Voltage applied to 3-state output –0.5 to 5.5 V

V

CC

Longest supply voltage rise time from 1V to 2.375V 50 ms

T

STG

Storage temperature (ambient) –65 to +150

°

C

T

J

Junction temperature Ceramic packages +150

°

C

Plastic packages +125

°

C

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional op er ation of the device at these or any other cond iti ons b eyond those listed under Oper a tin g C o ndi tions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

2. Power supplies may turn on in any order.

3. For protracted periods (e.g., longer than a day), V

IN

should not exceed V

CCO

by more that 3.6V.

QPro Virtex 2.5V QML High-Reliability FPGAs

DS002 (v1.5) December 5, 2001

www.xilinx.com

3

Preliminary Product Specification

1-800-255-7778

R

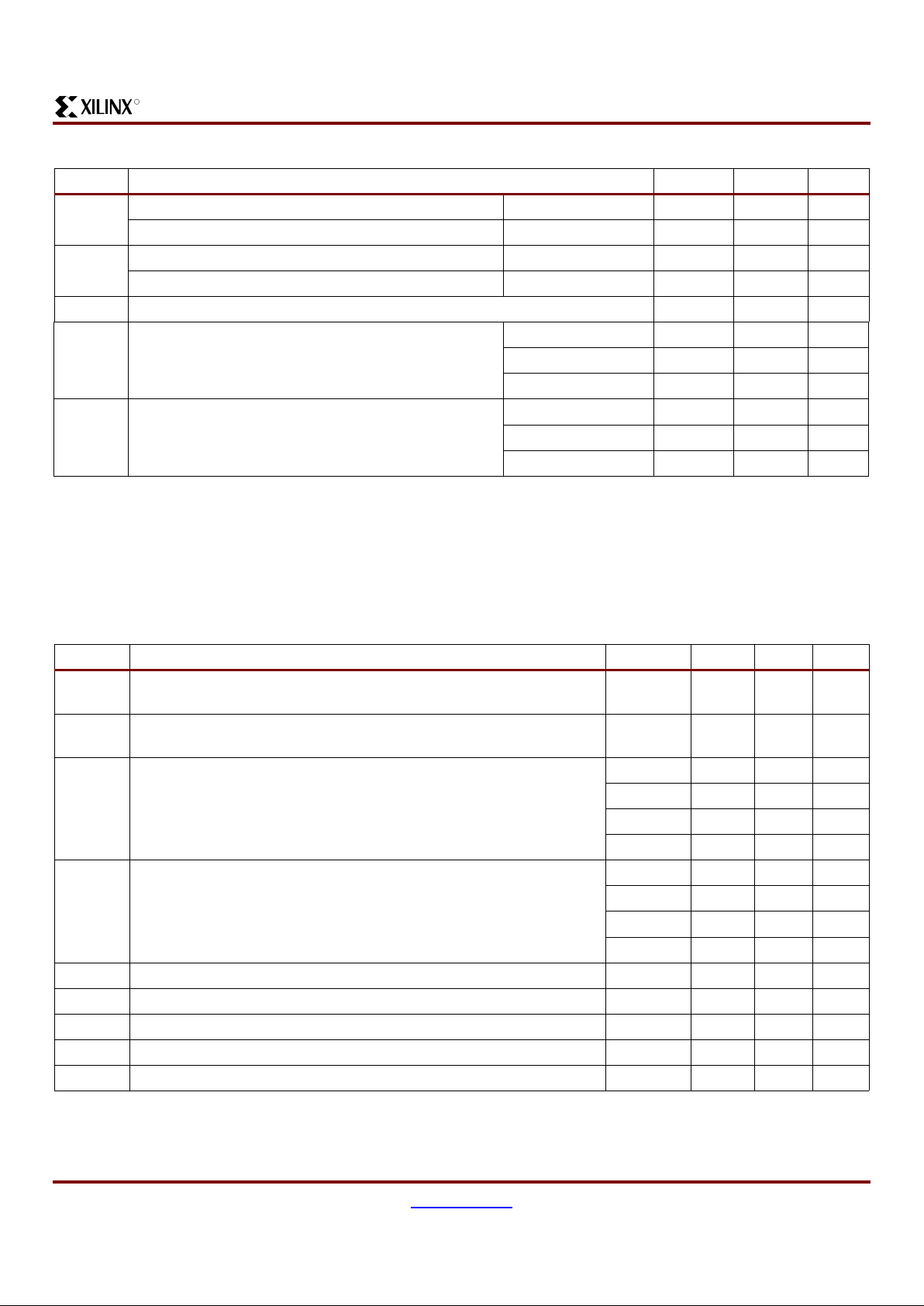

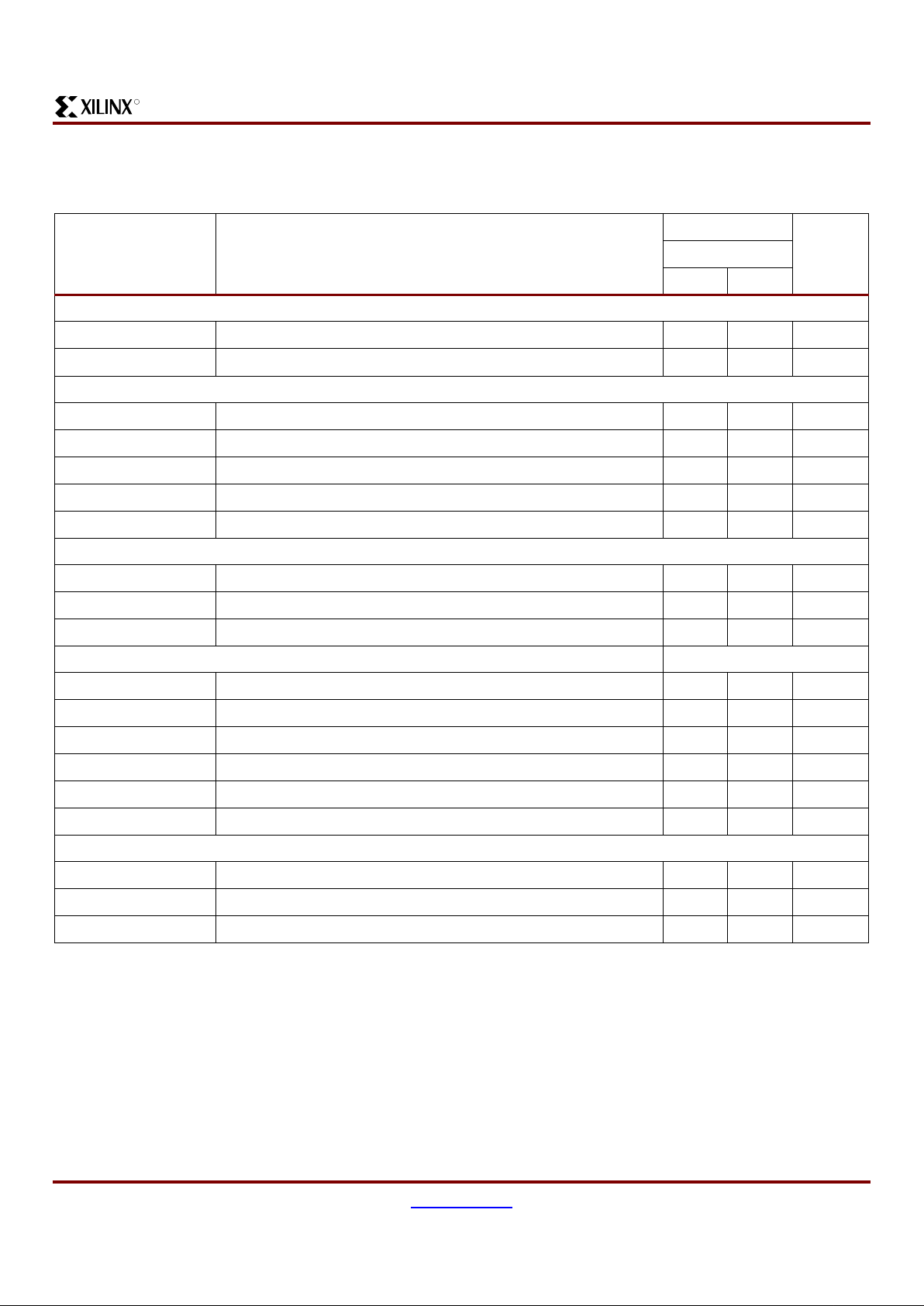

Recommended Operating Conditions

DC Characteristics Over Recommended Operating Conditions

Symbol Description Min Max Units

V

CCINT

Supply voltage relative to GND, TC = –55°C to +125°C Ceramic packages 2.5 – 5% 2.5 + 5% V

Supply voltage relative to GND, T

J

= –55°C to +125°C Plastic packages 2.5 – 5% 2.5 + 5% V

V

CCO

Supply voltage relative to GND, TC = –55°C to +125°C Ceramic packages 1.2 3.6 V

Supply voltage relative to GND, T

J

= –55°C to +125°C Plastic packages 1.2 3.6 V

T

IN

Input signal transition time - 250 ns

T

IC

Initialization Temperature Range

(4)

XQVR300 –55 +125

°

C

XQVR600 –55 +125

°

C

XQVR1000 –40 +125

°

C

T

OC

Operational Temperature Range

(5)

XQVR300 –55 +125

°

C

XQVR600 –55 +125

°

C

XQVR1000 –55 +125

°

C

Notes:

1. Correct operation is guar an teed with a min imu m V

CCINT

of 2.25V (Nominal V

CCINT

– 10%). Below the m inim um v alue stated abo v e,

all delay parameters increase by 3% for each 50 mV reduction in V

CCINT

below the specified range.

2. At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.35% per

°

C.

3. Input and output measurement threshold is ~50% of V

CC

.

4. Initialization occurs from the moment of V

CC

ramp-up to the rising transition of the INIT pin.

5. The device is operational after the INIT pin has transitioned high.

Symbol Description Device Min Max Units

V

DRINT

Data retention V

CCINT

voltage

(below which configuration data may be lost)

All 2.0 - V

V

DRIO

Data retention V

CCO

voltage

(below which configuration data may be lost)

All 1.2 - V

I

CCINTQ

Quiescent V

CCINT

supply current

(1)

XQV100 - 50 mA

XQV300 - 75 mA

XQV600 - 100 mA

XQV1000 - 100 mA

I

CCOQ

Quiescent V

CCINT

supply current

(1)

XQV100 - 2 mA

XQV300 - 2 mA

XQV600 - 2 mA

XQV1000 - 2 mA

I

REF

V

REF

current per V

REF

pin - - 20

µ

A

I

L

Input or output leakage current - –10 +10

µ

A

C

IN

Input capacitance (sample tested) - - 8 pF

I

RPU

Pad pull-up (when selected) at VIN = 0V, V

CCO

= 3.3V (sample tested) -

(2)

0.25 mA

I

RPD

Pad pull-down (when selected) at VIN = 3.6V (sample tested) -

(2)

0.15 mA

Notes:

1. With no output current loads, no active input pull-up resistors, all I/O pins in a High-Z state and floating.

2. Internal pull-up and pull-down res istors guar antee v alid logic le v els at unconn ected input pins . These pull -up and pull-do wn resistors

do not guarantee valid logic levels when input pins are connected to other circuits.

QPro Virtex 2.5V QML High-Reliability FPGAs

4

www.xilinx.com

DS002 (v1.5) December 5, 2001

1-800-255-7778

Preliminary Product Specification

R

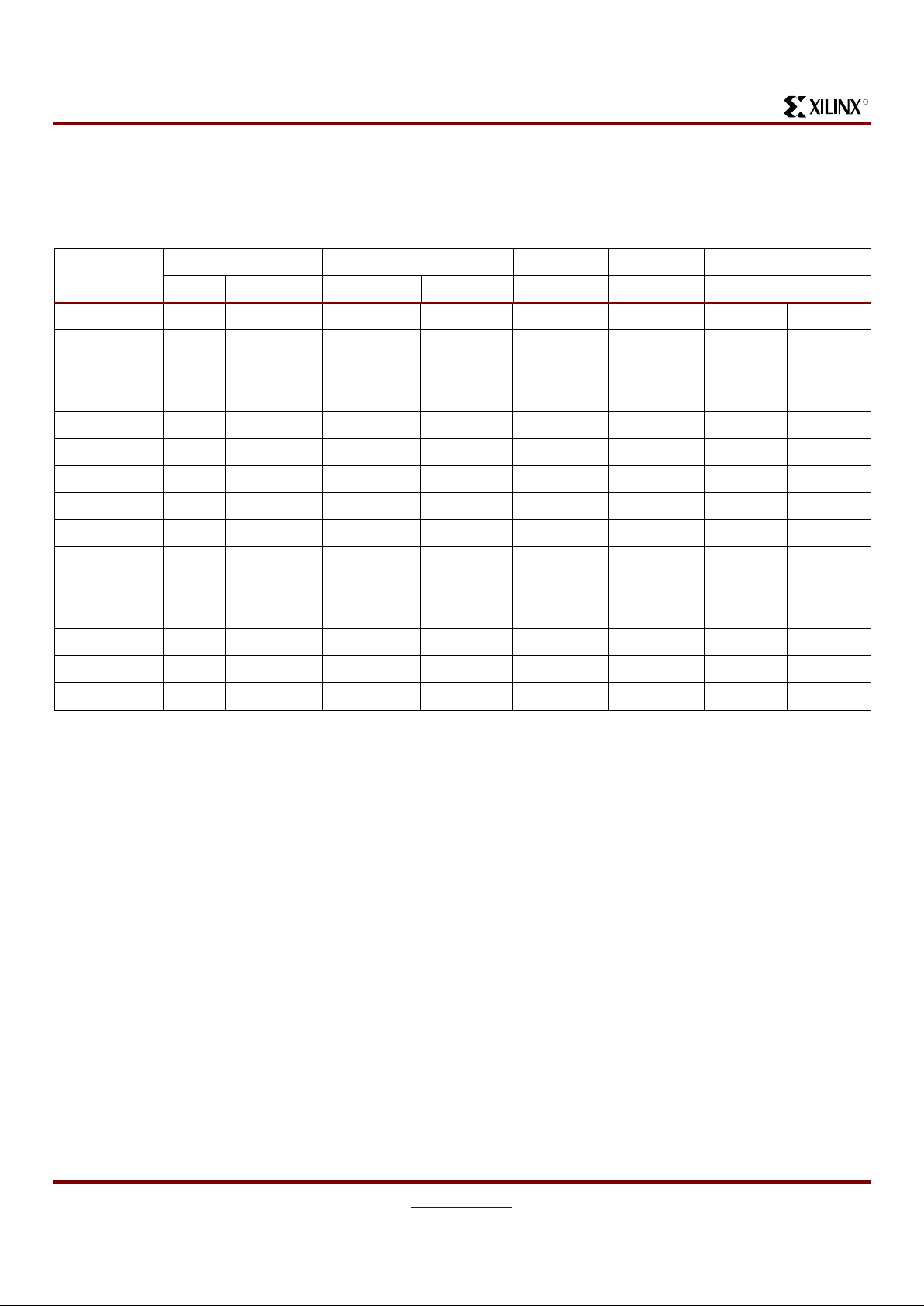

DC Input and Output Levels

Values fo r VIL and VIH are recommended input voltages.

Va lues for I

OL

and IOH are guaranteed output currents over

the recommended operating con di tio ns at the V

OL

and V

OH

test points. Only selec ted standards a re tested. Thes e are

chosen to ensure that all standards meet their specifications. The selected standa rds a re tested at min imum V

CCO

with the respective VOL and VOH voltage levels shown.

Other standards are sample tested.

Input/Output

Standard

V

IL

V

IH

V

OL

V

OH

I

OL

I

OH

V, min V, max V, min V, max V, max V, min mA mA

LVTTL

(1)

–0.5 0.8 2.0 5.5 0.4 2.4 24 –24

LVCMOS2 –0.5 0.7 1.7 5.5 0.4 1.9 12 –12

PCI, 3.3V –0.5 44% V

CCINT

60% V

CCINTVCCO

+ 0.5 10% V

CCO

90% V

CCO

(2) (2)

PCI, 5.0V –0.5 0.8 2.0 5.5 0.55 2.4

(2) (2)

GTL –0.5 V

REF

– 0.05 V

REF

+ 0.05 3.6 0.4 n/a 40 n/a

GTL+ –0.5 V

REF

– 0.1 V

REF

+ 0.1 3.6 0.6 n/a 36 n/a

HSTL I –0.5 V

REF

– 0.1 V

REF

+ 0.1 3.6 0.4 V

CCO

– 0.4 8 -8

HSTL III –0.5 V

REF

– 0.1 V

REF

+ 0.1 3.6 0.4 V

CCO

– 0.4 24 –8

HSTL IV –0.5 V

REF

– 0.1 V

REF

+ 0.1 3.6 0.4 V

CCO

– 0.4 48 –8

SSTL3 I –0.5 V

REF

– 0.2 V

REF

+ 0.2 3.6 V

REF

– 0.6 V

REF

+ 0.6 8 –8

SSTL3 II –0.5 V

REF

– 0.2 V

REF

+ 0.2 3.6 V

REF

– 0.8 V

REF

+ 0.8 16 –16

SSTL2 I –0.5 V

REF

– 0.2 V

REF

+ 0.2 3.6 V

REF

– 0.65 V

REF

+ 0.65 7.6 –7.6

SSTL2 II –0.5 V

REF

– 0.2 V

REF

+ 0.2 3.6 V

REF

– 0.80 V

REF

+ 0.80 15.2 –15.2

CTT –0.5 V

REF

– 0.2 V

REF

+ 0.2 3.6 V

REF

– 0.4 V

REF

+ 0.4 8 –8

AGP –0.5 V

REF

– 0.2 V

REF

+ 0.2 3.6 10% V

CCO

90% V

CCO

(2) (2)

Notes:

1. V

OL

and VOH for lower drive currents are sample tested.

2. Tested according to the relevant specifications.

QPro Virtex 2.5V QML High-Reliability FPGAs

DS002 (v1.5) December 5, 2001

www.xilinx.com

5

Preliminary Product Specification

1-800-255-7778

R

Virtex Switching Characteristics

Testing of switching parameters is modeled after testing

methods specified by MIL-M-38510/605. All devices are

100% functionally tested. Internal timing parameters are

derived from measurin g internal test patter n s. Listed bel ow

are representative values. For more specific, more precise,

and worst-case guarante ed data, use the values repor ted

by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotate d to the simulati on netli st.

All timing parameters as sume worst-case operating c onditions (supply voltage and junction temperature). Values

apply to all Virtex devices unless otherwise noted.

IOB Input Switching Characteristics

Input delays associated with the pad are specified for

LVTTL levels. For other standards, adjust the delays with

the values shown in "IOB Input Switching Characteristics

Standard Adjustments" on page 6.

Symbol Description Device

Speed Grade

Units

-4

Min Max

Propagation Delays

T

IOPI

Pad to I output, no delay All - 1.0 ns

T

IOPID

Pad to I output, with delay XQV100 - 1.9 ns

XQV300 - 1.9 ns

XQV600 - 2.3 ns

XQV1000 - 2.7 ns

T

IOPLI

Pad to output IQ via transparent latch, no

delay

All - 2.0 ns

T

IOPLID

Pad to output IQ via transparent latch, with

delay

XQV100 - 4.8 ns

XQV300 - 5.1 ns

XQV600 - 5.5 ns

XQV1000 - 5.9 ns

Sequential Delays

T

IOCKIQ

Clock CLK to output IQ All - 0.8 ns

Setup and Hold Times with Respect to Clock CLK Setup Time / Hold Time

T

IOPICK

/ T

IOICKP

Pad, no delay All 2.0 / 0 - ns

T

IOPICKD

/ T

IOICKPD

Pad, with delay All 5.0 / 0 - ns

T

IOICECK

/ T

IOCKICE

ICE input All 1.0 / 0 - ns

T

IOSRCKI

/ T

IOCKISR

SR input (IFF, synchronous) All 1.3 / 0 - ns

Set/Reset Delays

T

IOSRIQ

SR input to IQ (asynchronous) All - 1.8 ns

T

GSRQ

GSR to output IQ All - 12.5 ns

Notes:

1. A Zero “0” Hold Time lis ting i ndica tes no hold time or a ne gative hold time. Negative values can not be guaranteed “best-case”,

but if a “0” is listed, there is no positive hold time.

QPro Virtex 2.5V QML High-Reliability FPGAs

6

www.xilinx.com

DS002 (v1.5) December 5, 2001

1-800-255-7778

Preliminary Product Specification

R

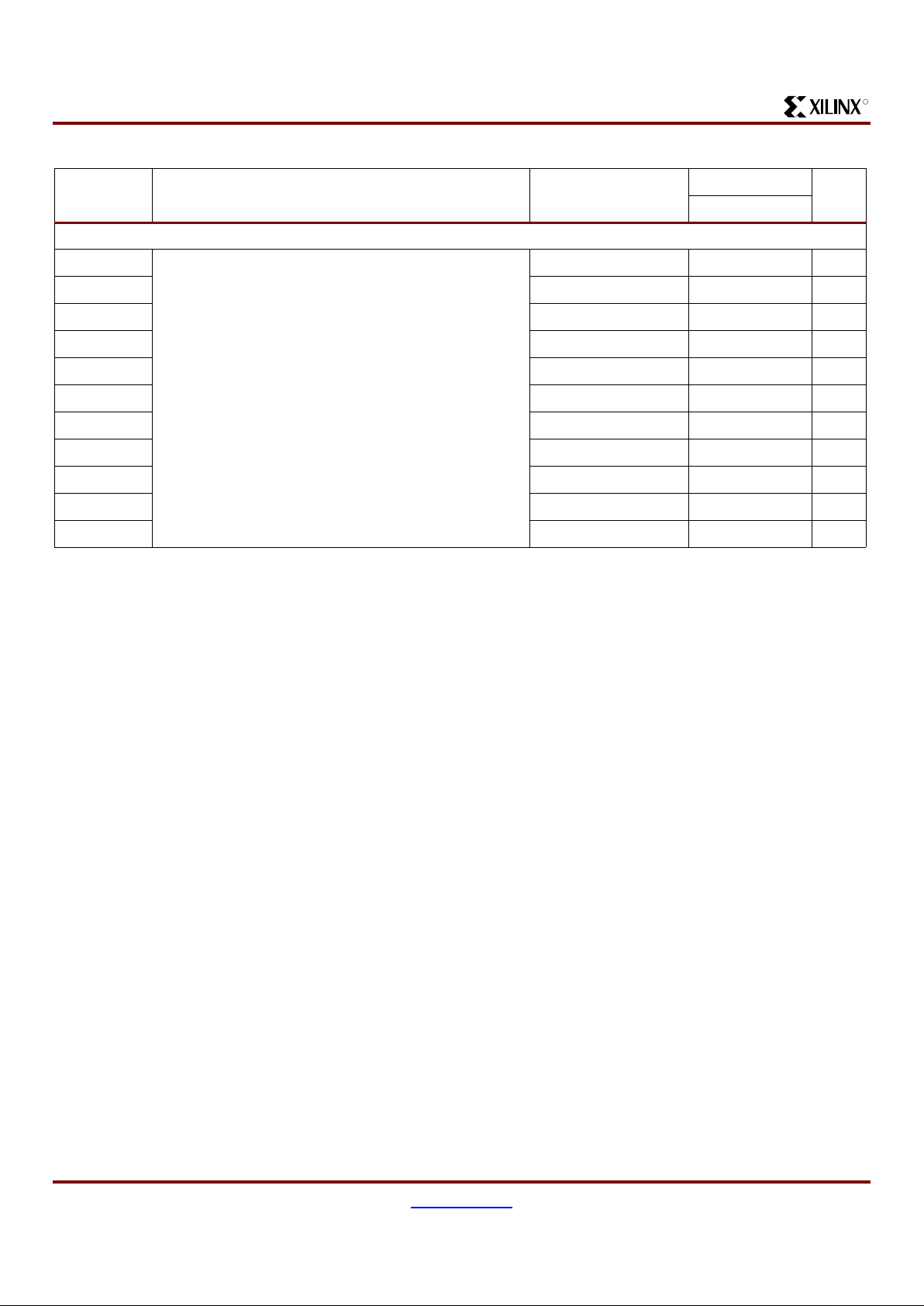

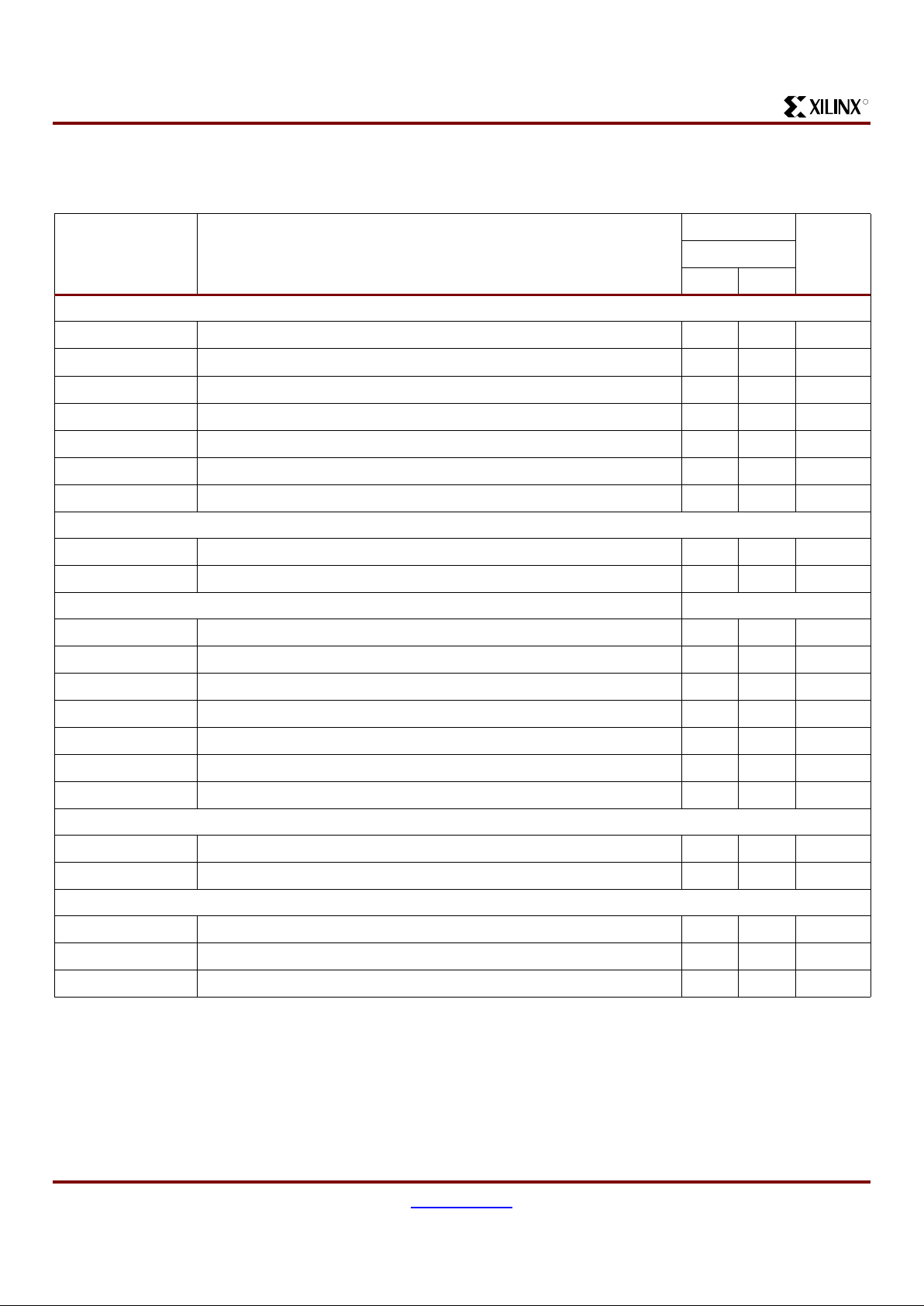

IOB Input Switching Characteristics Standard Adjustments

Symbol Description Standard

Speed Grade

Units-4

Data Input Delay Adjustments

T

ILVTTL

Standard-specific data input delay adjustments LVTTL 0.0 ns

T

ILVCMOS2

LVCMOS2 –0.05 ns

T

IPCI33_3

PCI, 33 MHz, 3.3V –0.14 ns

T

IPCI33_5

PCI, 33 MHz, 5.0V 0.33 ns

T

IGTL

GTL 0.26 ns

T

IGTLP

GTL+ 0.14 ns

T

IHSTL

HSTL 0.04 ns

T

ISSTL2

SSTL2 –0.10 ns

T

ISSTL3

SSTL3 –0.06 ns

T

ICTT

CTT 0.02 ns

T

IAGP

AGP –0.08 ns

QPro Virtex 2.5V QML High-Reliability FPGAs

DS002 (v1.5) December 5, 2001

www.xilinx.com

7

Preliminary Product Specification

1-800-255-7778

R

IOB Output Switching Characteristics

Output delays terminatin g at a pad are s pec ifi ed for LVTTL wi th 12 mA dr ive and fast slew rate. For other standards, adjust

the delays with the values shown in "IOB Output Switching Characteristics Standard Adjustments" on page 8.

Symbol Description

Speed Grade

Units

-4

Min Max

Propagation Delays

T

IOOP

O input to pad - 3.5 ns

T

IOOLP

O input to pad via transparent latch - 4.0 ns

3-State Delays

T

IOTHZ

T input to pad high-impedance

(1)

-2.4ns

T

IOTON

T input to valid data on pad - 3.7 ns

T

IOTLPHZ

T input to pad high-impedance via transparent latch

(1)

-3.0ns

T

IOTLPON

T input to valid data on pad via transparent latch - 4.2 ns

T

GTS

GTS to pad high-impedance

(1)

-6.3ns

Sequential Delays

T

IOCKP

Clock CLK to pad - 3.5 ns

T

IOCKHZ

Clock CLK to pad high-impedance (synchronous)

(1)

-2.9ns

T

IOCKON

Clock CLK to valid data on pad (synchronous) - 4.1 ns

Setup and Hold Times before/after Clock CLK Setup Time / Hold Time

(2)

T

IOOCK/TIOCKO

O input 1.3 / 0 - ns

T

IOOCECK/TIOCKOCE

OCE input 1.0 / 0 - ns

T

IOSRCKO/TIOCKOSR

SR input (OFF) 1.4 / 0 - ns

T

IOTCK/TIOCKT

3-state setup times, T input 0.9 / 0 - ns

T

IOTCECK/TIOCKTCE

3-state setup times, TCE input 1.1 / 0 - ns

T

IOSRCKT/TIOCKTSR

3-state setup times, SR input (TFF) 1.3 / 0 - ns

Set/Reset Delays

T

IOSRP

SR input to pad (asynchronous) 4.6 - ns

T

IOSRHZ

SR input to pad high-impedance (asynchronous)

(1)

3.9 - ns

T

IOSRON

SR input to valid data on pad (asynchronous) 5.1 - ns

Notes:

1. High-impedance turn-off delays should not be adjusted.

2. A Zero “0” Hold Time listing ind ic ate s no hold time or a negative hold time. Ne gat ive values can not be guarantee d “best-case”, but

if a “0” is listed, there is no positive hold time.

QPro Virtex 2.5V QML High-Reliability FPGAs

8

www.xilinx.com

DS002 (v1.5) December 5, 2001

1-800-255-7778

Preliminary Product Specification

R

IOB Output Switching Characteristics Standard Adjustments

Output delays terminatin g at a pad are s pec ifi ed for LVTTL wi th 12 mA dr ive and fast slew rate. For other standards, adjust

the delays by the values shown.

Symbol Description Standard

Speed Grade

Units-4

Output Delay Adjustments

T

OLVTTL_S2

Standard-specific adjustments for output delays

terminating at pads (based on standard capacitive

load, C

sl

)

LVTTL, slow 2 mA 17.0 ns

T

OLVTTL_S4

4 mA 8.6 ns

T

OLVTTL_S6

6 mA 5.6 ns

T

OLVTTL_S8

8 mA 3.5 ns

T

OLVT TL_S12

12 mA 2.2 ns

T

OLVT TL_S16

16 mA 2.0 ns

T

OLVT TL_S24

24 mA 1.6 ns

T

OLVTTL_F2

LVTTL, fast 2 mA 15.1 ns

T

OLVTTL_F4

4 mA 6.1 ns

T

OLVTTL_F6

6 mA 3.6 ns

T

OLVTTL_F8

8 mA 1.2 ns

T

OLVTTL_F12

12 mA 0.0 ns

T

OLVTTL_F16

16 mA –0.05 ns

T

OLVTTL_F24

24 mA –0.23 ns

T

OLVCMOS2

LVCMOS2 0.12 ns

T

OPCI33_3

PCI, 33 MHz, 3.3V 2.7 ns

T

OPCI33_5

PCI, 33 MHz, 5.0V 3.3 ns

T

OGTL

GTL 0.6 ns

T

OGTLP

GTL+ 1.0 ns

T

OHSTL_I

HSTL I –0.5 ns

T

OHSTL_III

HSTL III –1.0 ns

T

OHSTL_IV

HSTL IV –1.1 ns

T

OSSTL2_I

SSTL2 I –0.5 ns

T

OSSTL2_II

SSTL2 II –1.0 ns

T

OSSTL3_I

SSTL3 I –0.5 ns

T

OSSTL3_II

SSTL3 II –1.1 ns

T

OCTT

CTT –0.6 ns

T

OAGP

AGP –1.0 ns

QPro Virtex 2.5V QML High-Reliability FPGAs

DS002 (v1.5) December 5, 2001

www.xilinx.com

9

Preliminary Product Specification

1-800-255-7778

R

Calculation of T

ioop

as a Function of Capacitance

The values for T

ioop

were based on the stan dar d c apa ci tive

load (Csl) for each I/O standard as listed in Table 2.

For other capacitive loads, use the formulas below to calcu-

late the corresponding T

ioop

:

T

ioop

= T

ioopl

+ T

opadjust + (Cload

- Csl) * fl

Where:

T

opadjust

is reported above in the Output Delay

Adjustment section.

C

load

is the capacitive load for the design.

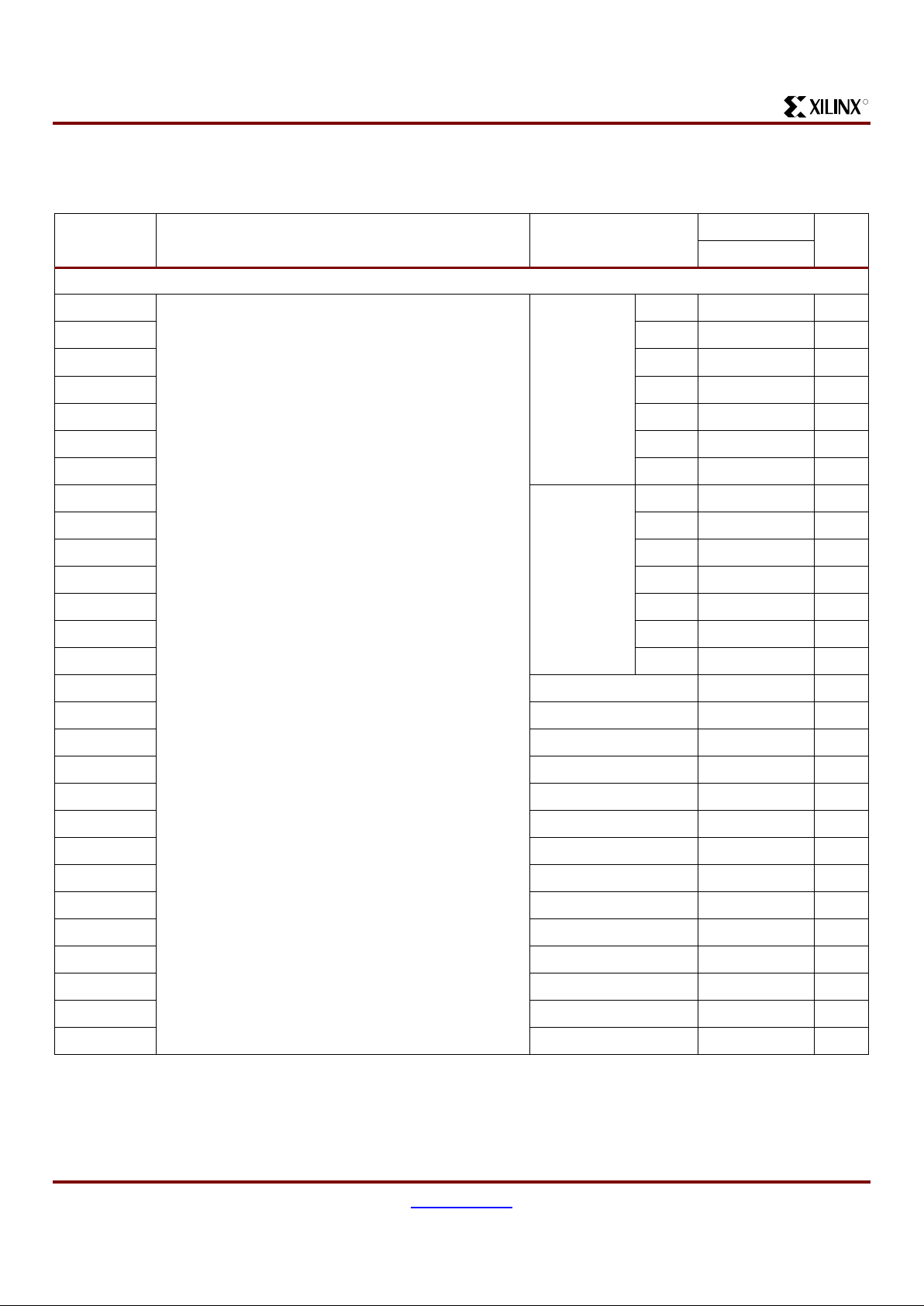

Clock Distribution Guidelines and Switching Characte ris ti cs

Table 2:

Constants for Use in Calculation of T

op

Standard C

sl

(pF) fl (ns/pF)

LVTTL slow

slew rate

2 mA drive 35 0.41

4 mA drive 35 0.20

6 mA drive 35 0.100

8 mA drive 35 0.086

12 mA drive 35 0.058

16 mA drive 35 0.050

24 mA drive 35 0.048

LVTTL fast

slew rate

2 mA drive 35 0.41

4 mA drive 35 0.20

6 mA drive 35 0.13

8 mA drive 35 0.079

12 mA drive 35 0.044

16 mA drive 35 0.043

24 mA drive 35 0.033

LVCMOS2 35 0.041

PCI 33 MHz 5V 50 0.050

PCI 33 MHZ 3.3V 10 0.050

GTL 0 0.014

GTL+ 0 0.017

HSTL Class I 20 0.022

HSTL Class III 20 0.016

HSTL Class IV 20 0.014

SSTL2 Class I 30 0.028

SSTL2 Class II 30 0.016

SSTL3 Class 1 30 0.029

SSTL3 Class II 30 0.016

CTT 20 0.035

AGP 10 0.037

Table 2:

Constants for Use in Calculation of T

op

Standard C

sl

(pF) fl (ns/pF)

Symbol Description Device

Speed Grade

Units

-4

Min Max

Global Clock Skew

T

GSKEWIOB

Global clock skew between IOB flip-flops XQV100 - 0.15 ns

XQV300 - 0.18 ns

XQV600 - 0.17 ns

XQV1000 - 0.25 ns

T

GPIO

Global clock PAD to output All - 0.9 ns

T

GIO

Global clock buffer I input to O output All - 0.9 ns

Notes:

1. These clock-distribution delays are provided for guidance only. They reflect the delays encountered in a typical design under

worst-case conditions. Precise values for a particular design are provided by the timing analyzer.

QPro Virtex 2.5V QML High-Reliability FPGAs

10

www.xilinx.com

DS002 (v1.5) December 5, 2001

1-800-255-7778

Preliminary Product Specification

R

CLB Switching Characteristics

Delays originating at F/G inputs vary sli ghtly acco rding t o the inp ut used. T he values listed be low are worst-cas e. Precise

values are provided by the timing analyzer.

Symbol Description

Speed Grade

Units

-4

Min Max

Combinatorial Delays

T

ILO

4-input function: F/G inputs to X/Y outputs - 0.8 ns

T

IF5

5-input function: F/G inputs to F5 output - 0.9 ns

T

IF5X

5-input function: F/G inputs to X output - 1.0 ns

T

IF6Y

6-input function: F/G inputs to Y output via F6 MUX - 1.2 ns

T

F5INY

6-input function: F5IN input to Y output - 0.5 ns

T

IFNCTL

Incremental delay routing through transparent latch to XQ/YQ outputs - 0.8 ns

T

BYYB

BY input to YB output - 0.7 ns

Sequential Delays

T

CKO

FF clock CLK to XQ/YQ outputs - 1.4 ns

T

CKLO

Latch clock CLK to XQ/YQ outputs - 1.6 ns

Setup and Hold Times before/after Clock CLK Setup Time / Hold Time

T

ICK/TCKI

4-input function: F/G Inputs 1.5 / 0 - ns

T

IF5CK/TCKIF5

5-input function: F/G inputs 1.7 / 0 - ns

T

F5INCK/TCKF5IN

6-input function: F5IN input 1.2 / 0 - ns

T

IF6CK/TCKIF6

6-input function: F/G inputs via F6 MUX 1.9 / 0 - ns

T

DICK/TCKDI

BX/BY inputs 0.8 / 0 - ns

T

CECK/TCKCE

CE input 1.0 / 0 - ns

T

RCKTCKR

SR/BY inputs (synchronous) 0.9 / 0 - ns

Clock CLK

T

CH

Minimum pulse width, High 2.0 - ns

T

CL

Minimum pulse width, Low 2.0 - ns

Set/Reset

T

RPW

Minimum pulse width, SR/BY inputs 3.3 - ns

T

RQ

Delay from SR/BY inputs to XQ/YQ outputs (asynchronous) - 1.4 ns

T

IOGSRQ

Delay from GSR to XQ/YQ outputs - 12.5 ns

Notes:

1. A Zero “0” Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed “best-case”, but

if a “0” is listed, there is no positive hold time.

Loading...

Loading...