XICOR X76F041WE-3, X76F041WE, X76F041W-3, X76F041W, X76F041PE-3 Datasheet

...

APPLICATION NOTE

A V A I L A B L E

AN83 • Development Tools XK76C

Password Access Security Supervisor

4K

X76F041

PASS

TM

FEATURES

• 64-Bit Password Security

• Three Password Modes

—Secure Read Access

—Secure Write Access

—Secure Configuration Access

• Programmable Configuration

—Read, Write and Configuration Access

Passwords

—Multiple Array Access/Functionality

—Retry Register/Counter

• 8 Byte Sector Write

• (4) 1K Memory Arrays

• ISO Response to Reset

• Low Power CMOS

—50 µ A Standby Current

—3mA Active Current

• 1.8V to 3.6V or 5V “Univolt” Read and Program

Power Supply Versions

• High Reliability

—Endurance: 100,000 Cycles

—Data Retention: 100 Years

—ESD Protection: 2000V on All Pins

SecureFlash

DESCRIPTION

The X76F041 is a password access security supervisor

device, containing four 128 x 8 bit SecureFlash arrays.

Access can be controlled by three 64-bit programmable

passwords, one for read operations, one for write operations and one for device configur ation.

The X76F041 features a serial interface and software

protocol allowing operation on a simple two wire bus . The

bus signals are a clock input (SCL) and a bidirectional

data input and output (SDA). Access to the device is controlled through a chip select input (CS

number of devices to share the same bus .

The X76F041 also features a synchronous response to

reset; providing an automatic output of a pre-configured

32-bit data stream conforming to the ISO standard for

memory cards.

The X76F041 utilizes Xicor’s proprietary Direct Write

cell, providing a minimum endurance of 100,000 cycles

per sector and a minimum data retention of 100 years.

4 x 128 x 8 Bit

), allowing any

TM

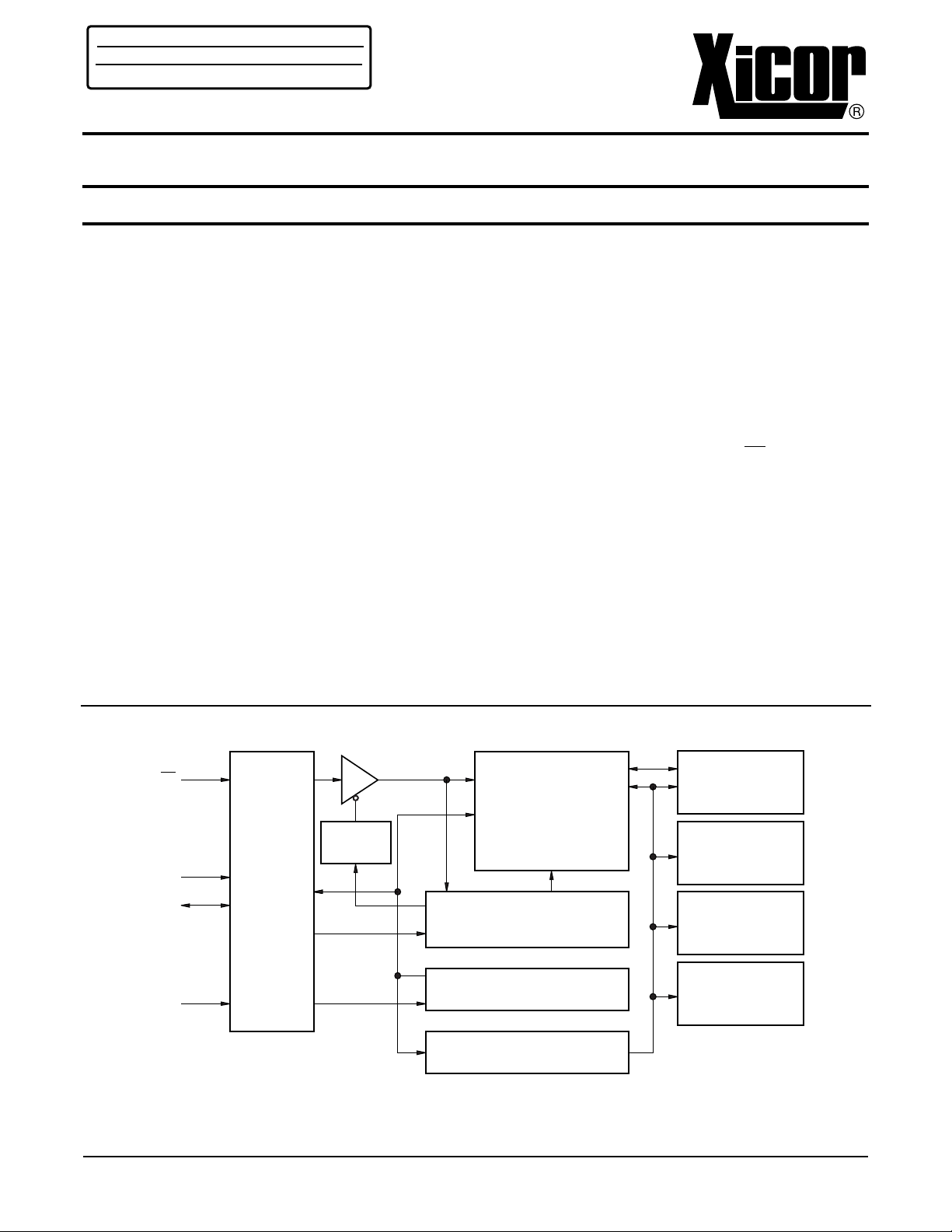

FUNCTIONAL DIAGRAM

CS

SCL

SDA

RST

©Xicor, Inc. 1994, 1995, 1996 Patents Pending

7002-2.2 4/30/97 T3/C0/D0 SH

INTERFACE

LOGIC

RETRY

COUNTER

CHIP

ENABLE

DATA

TRANSFER

ARRAY ACCESS

ENABLE

PASSWORD ARRAY AND

PASSWORD VERIFICATION

LOGIC

ISO RESET RESPONSE

DATA REGISTER

CONFIGURATION

REGISTER

1

000–07F

080–0FF

100–17F

180–1FF

(4) 16 x 64

SECUREFLASH

ARRAYS

7002 ILL F01

Characteristics subject to change without notice

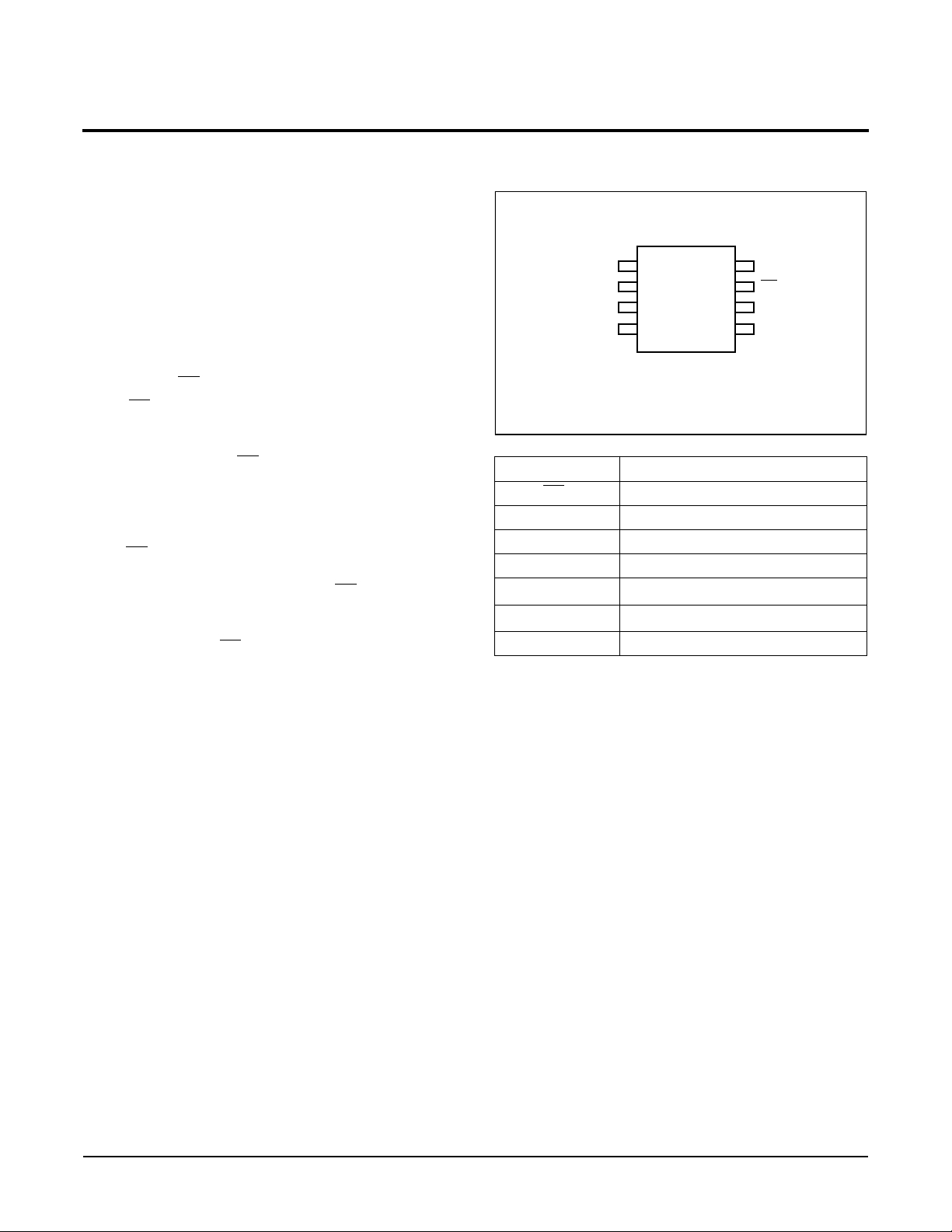

7002 ILL F02

V

CC

RST

SCL

NC

1

2

3

4

8

7

6

5

V

SS

CS

SDA

NC

X76F041

DIP/SOIC

X76F041

PIN DESCRIPTION

Serial Data Input/Output (SDA)

SDA is a true three state serial data input/output pin.

During a read cycle, data is shifted out on this pin.

During a write cycle, data is shifted in on this pin. In all

other cases this pin is in a high impedance state.

Serial Clock (SCL)

The Serial Clock controls the serial bus timing for data

input and output.

Chip Select (CS

)

When CS is HIGH, the X76F041 is deselected and the

SDA pin is at high impedance and unless an internal

write operation is underway the X76F041 will be in the

standby power mode. CS LOW enables the X76F041,

placing it in the active power mode.

Reset (RST)

RST is a device reset pin. When RST is pulsed HIGH

while CS is LOW the X76F041 will output 32 bits of

fixed data which conforms to the ISO standard for

“synchronous response to reset”. CS must remain

LOW and the part must not be in a write cycle for the

response to reset to occur. If at any time during the

response to reset CS goes HIGH, the response to

reset will be aborted and the part will return to the

standby mode.

PIN CONFIGURATION

Symbol Description

CS Chip Select Input

SDA Serial Data Input/Output

RST Reset Input

SCL Serial Clock Input

V

SS

V

CC

Ground

Supply Voltage

NC No Connect

7002 FRM T01

2

X76F041

DEVICE OPERATION

There are three primary modes of operation for the

X76F041; READ, WRITE and CONFIGURATION. The

READ and WRITE modes may be performed with or

without an 8-byte password. The CONFIGURATION

mode always requires an 8-byte pass word.

The basic method of communication is established by

first enabling the device (CS

LOW), generating a start

condition and then transmitting a command and address

field followed by the correct password (if configured to

require a password). All par ts will be shipped from the

factory in the non-password mode. The user must perform an ACK Polling routine to deter mine the validity of

the password and start the data transfer (see Acknowledge Polling). Only after the correct password is

accepted and an ACK Polling has been performed can

the data transfer occur .

To ensure correct communication, RST must remain

LOW under all conditions except when initiating a

“Response to Reset sequence”.

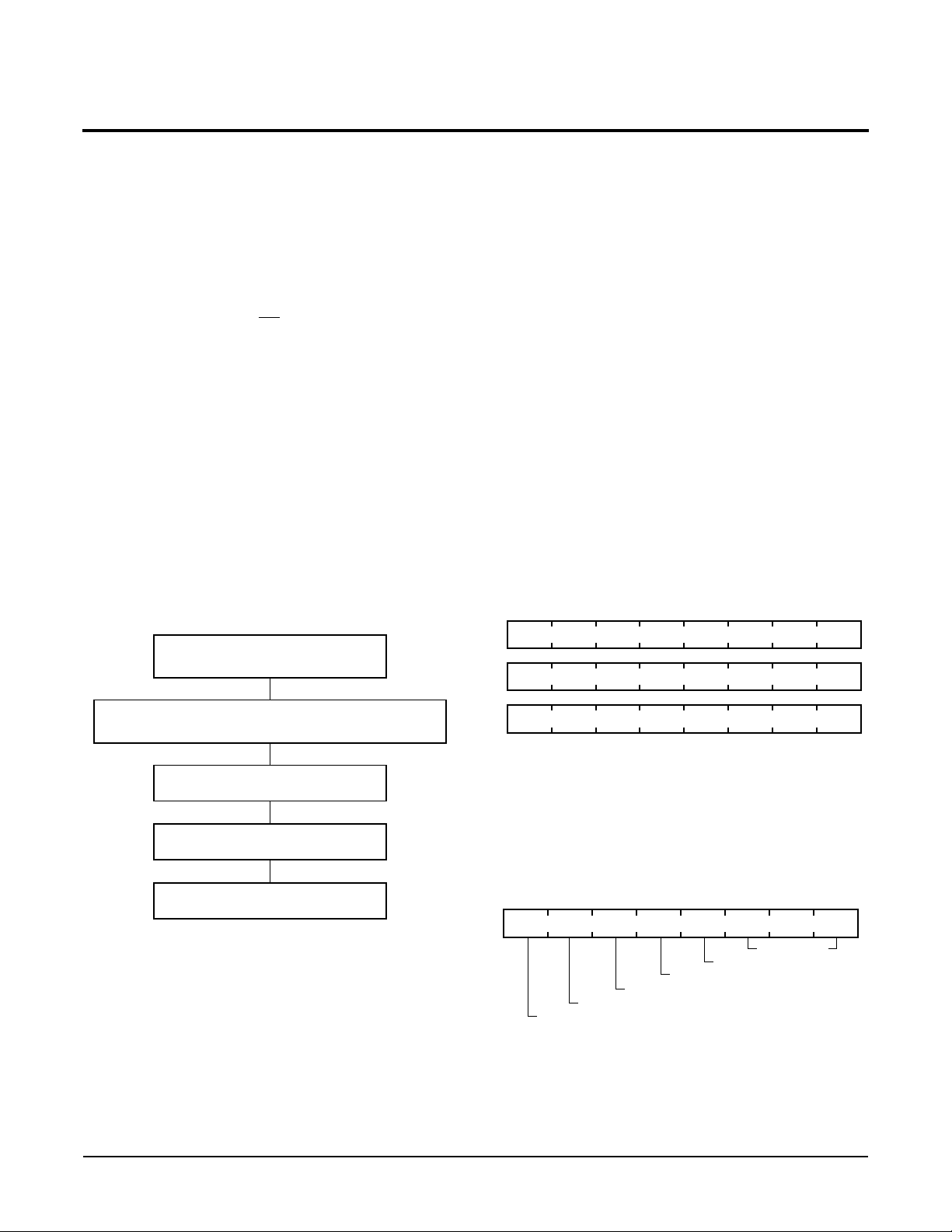

Figure 1. X76F041 Device Operation

COMMAND+HIGH ORDER ADDRESS

LOAD

BYTE

Data is transferred in 8-bit segments, with each transfer

being followed by an ACK, generated by the receiving

device.

If the X76F041 is in a nonvolatile write cycle a “no ACK”

(SDA HIGH) response will be issued in response to loading of the command + high order address byte. If a stop

condition is issued prior to the nonvolatile write cycle the

write operation will be terminated and the part will reset

and enter into a standby mode.

The basic sequence is illustrated in Figure 1.

After each transaction is completed, the X76F041 will

reset and enter into a standby mode. This will also be the

response if an attempt is made to access any limited

array.

Password Registers

The three passwords, Read, Write and Configuration

are stored in three 64 bit Write Only registers as illustrated in figure 2.

Figure 2. Password Registers

63 0

64 BIT WRITE PASSWORD

64 BIT READ PASSWORD

LOW ORDER ADDRESS / CONFIGURATION INSTRUCTION

LOAD 8–BYTE PASSWORD

VERIFY PASSWORD ACCEPTANCE BY USE

OF ACK POLLING (IF APPLICABLE)

LOAD

BYTE

(IF APPLICABLE)

READ / WRITE

DATA BYTES

7002 ILL F03

64 BIT CONFIGURATION PASSWORD

7002 ILL F04

Device Configuration

Five 8-Bit configuration registers are used to configure

the X76F041. These are sho wn in figure 3.

Figure 3. Configuration Registers

63 0

ACR1 ACR2 CR RR RC RES RES RES

RESERVED

RETRY COUNTER

RETRY REGISTER

CONFIGURATION REGISTER

ARRAY CONTROL REGISTER 2

ARRAY CONTROL REGISTER 1

7002 ILL F04B

3

X76F041

Array Control

The four 1K arrays, are each programmable to different

levels of access and functionality. Each array can be programmed to require or not require the read/write passwords. The functional options are:

• Read and Write Access.

• Read access with all write operations locked out.

• Read access and program only (writing a “1” to a

“0”). If an attempt to change a “0” to a “1” occurs the

X76F041 will reset, issue a “no ACK” and enter the

standby power mode.

• No read or write access to the memory. Access only

through use of the configuration password.

Array Map

First ‘1k’

Second ‘1k’

Third ‘1k’

Fourth ‘1k’

Addresses 000 07F (hex)

Addresses 080 0FF (hex)

Addresses 100 17F (hex)

Addresses 180 1FF (hex)

High-order

Addresses

7002 ILL F04A

8 Bit Array Control Register 1

SECOND 1K FIRST 1K

X2 Y2 Z2 T2 X1 Y1 Z1 T1

ACCESS FUNCTION ACCESS FUNCTION

MSB LSB

7002 ILL F05A

8 Bit Array Control Register 2

UPPER 1K THIRD 1K

X4 Y4 Z4 T4 X3 Y3 Z3 T3

ACCESS FUNCTION ACCESS FUNCTION

MSB LSB

7002 ILL F05B

Functional Bits

Z T FUNCTIONALITY

0 0 READ AND WRITE UNLIMITED

1 0 READ ONLY, WRITE LIMITED

PROGRAM & READ ONLY,

0 1

ERASE LIMITED

NO READ OR WRITE, FULLY

1 1

LIMITED

7002 FRM T02

Access Bits

X Y

READ

PASSWORD

WRITE

PASSWORD

0 0 NOT REQUIRED NOT REQUIRED

1 0 NOT REQUIRED REQUIRED

0 1 REQUIRED NOT REQUIRED

1 1 REQUIRED REQUIRED

7002 FRM T03

8-Bit Configuration Register

MSB LSB

UA1 UA2 1 0 RCR RCE 0 0

RESERVED

7002 ILL F06

RESERVED

RESERVED

UNAUTHORIZED ACCESS BIT 2

UNAUTHORIZED ACCESS BIT 1

RETRY COUNTER ENABLE

RETRY COUNTER RESET

Unauthorized Access Bits (UA1, UA2):

1 0

Access is forbidden if retry register equals the retry

counter (provided that the retry counter is enabled) and

no further access of any kind will be allowed.

0 1, 0 0, 1 1

Only configuration operations are allowed if the retry register equals the retry counter (provided that the retry

counter is enabled).

Retry Counter Reset Bit (RCR):

If the retry counter reset bit is a “1” then the retry counter

will be reset following a correct password, provided the

retry counter is enabled.

If the retry counter reset bit is a “0” then the retry counter

will not be reset following a correct password, provided

the retry counter is enabled.

Retry Counter Enable Bit (RCE):

If the Retry counter enable bit is a “1”, then the retry

counter is enabled. An initial comparison between the

retry register and retry counter deter mines whether the

number of allowed incorrect password attempts has

been reached. If not, the protocol continues and in case

of a wrong password, the retry counter is incremented by

one. If the password is correct then the retr y counter will

either be reset or unchanged, depending on the reset bit.

4

X76F041

The retry register must have a higher value than the retry

counter for correct device operation. If the retry counter

value is larger than the retry register and the retry

counter is enabled, the device will wrap around allowing

up to an additional 255 incorrect access attempts.

If the Retry counter enable bit is a “0”, then the retry

counter is disabled.

Retry Register/Counter

Both the retry register and retry counter are accessible in

the configuration mode and may be programmed with a

value of 0 to 255.

The difference between the retry register and the retry

counter is the number of access attempts allowed, therefore the retry counter must be programmed to a smaller

value than the retry register to prevent wrap around.

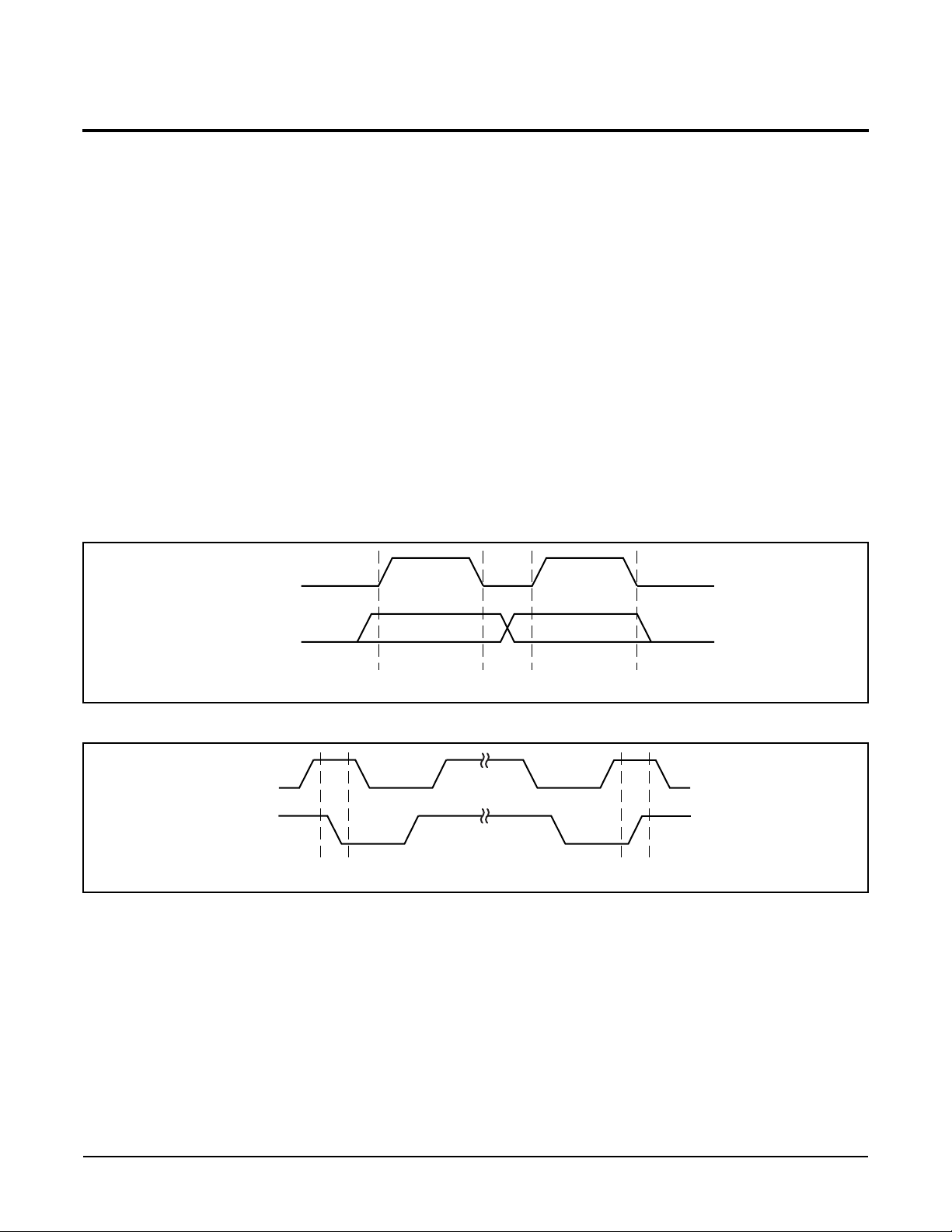

Figure 4. Data Validity During Write

SCL

DEVICE PROTOCOL

The X76F041 supports a bidirectional bus oriented protocol. The protocol defines any device that sends data

onto the bus as a transmitter , and the receiving de vice as

the receiver. The device controlling the transfer is a master and the device being controlled is the slav e . The master will always initiate data transfers, and provide the

clock for both transmit and receive operations. Therefore,

the X76F041 will be considered a slave in all applications.

Start Condition

All commands except for response to reset are preceded

by the start condition, which is a HIGH to LOW transition

of SDA when SCL is HIGH. The X76F041 continuously

monitors the SDA and SCL lines for the star t condition

and will not respond to any command until this condition

has been met.

SDA

DATA STABLE DATA

CHANGE

7002 ILL F07

Figure 5. Definition of Start and Stop

SCL

SDA

START BIT STOP BIT

NOTE: The part requires the SCL input to be LOW during non-active periods of operation. In other words, the SCL will need to be LOW prior to

any START condition and LOW after a ST OP condition. This is also reflected in the timing diagr am.

7002 ILL F08

5

X76F041

Stop Condition

All communications must be terminated by a stop condition, which is a LOW to HIGH transition of SDA when

SCL is HIGH. A stop condition can only be issued after

the transmitting device has released the bus .

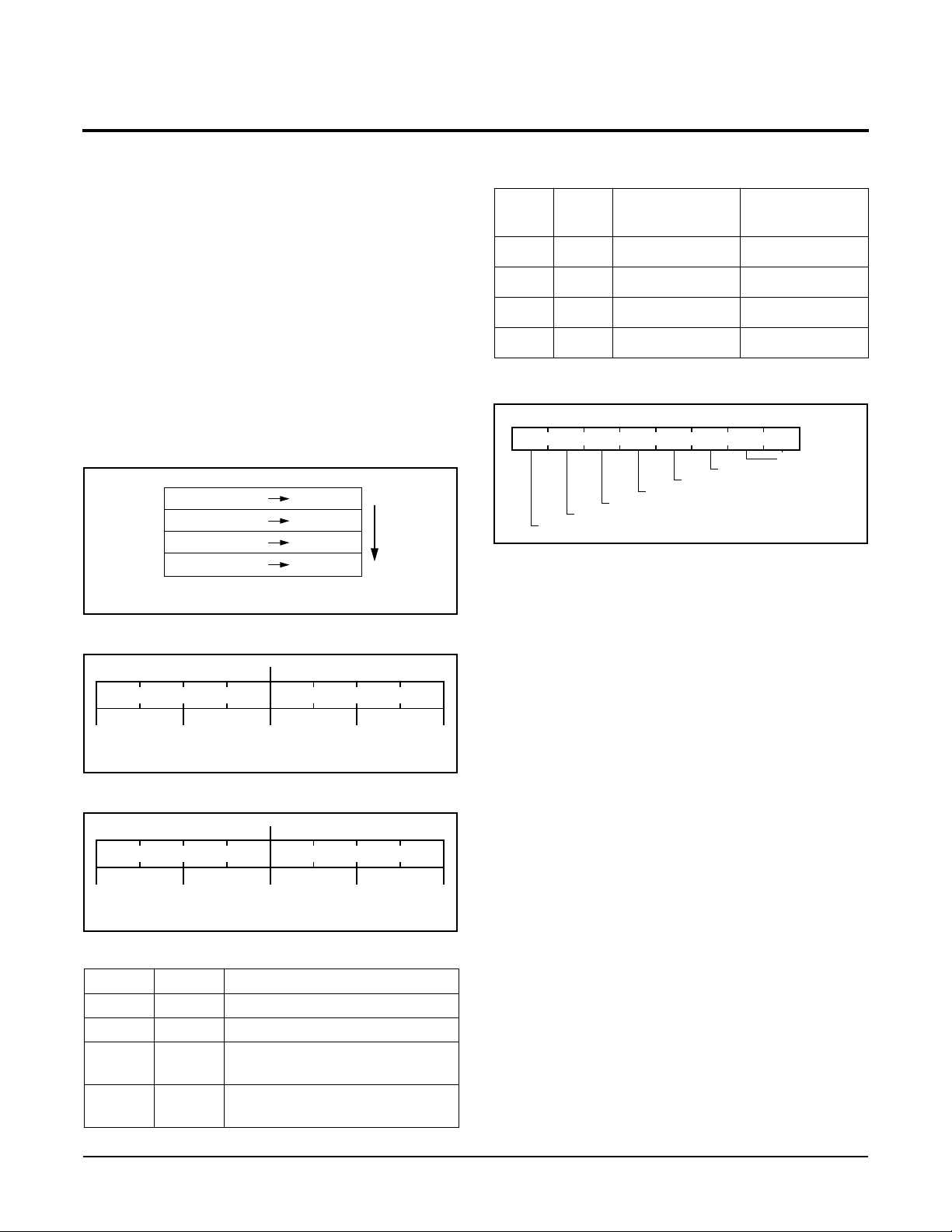

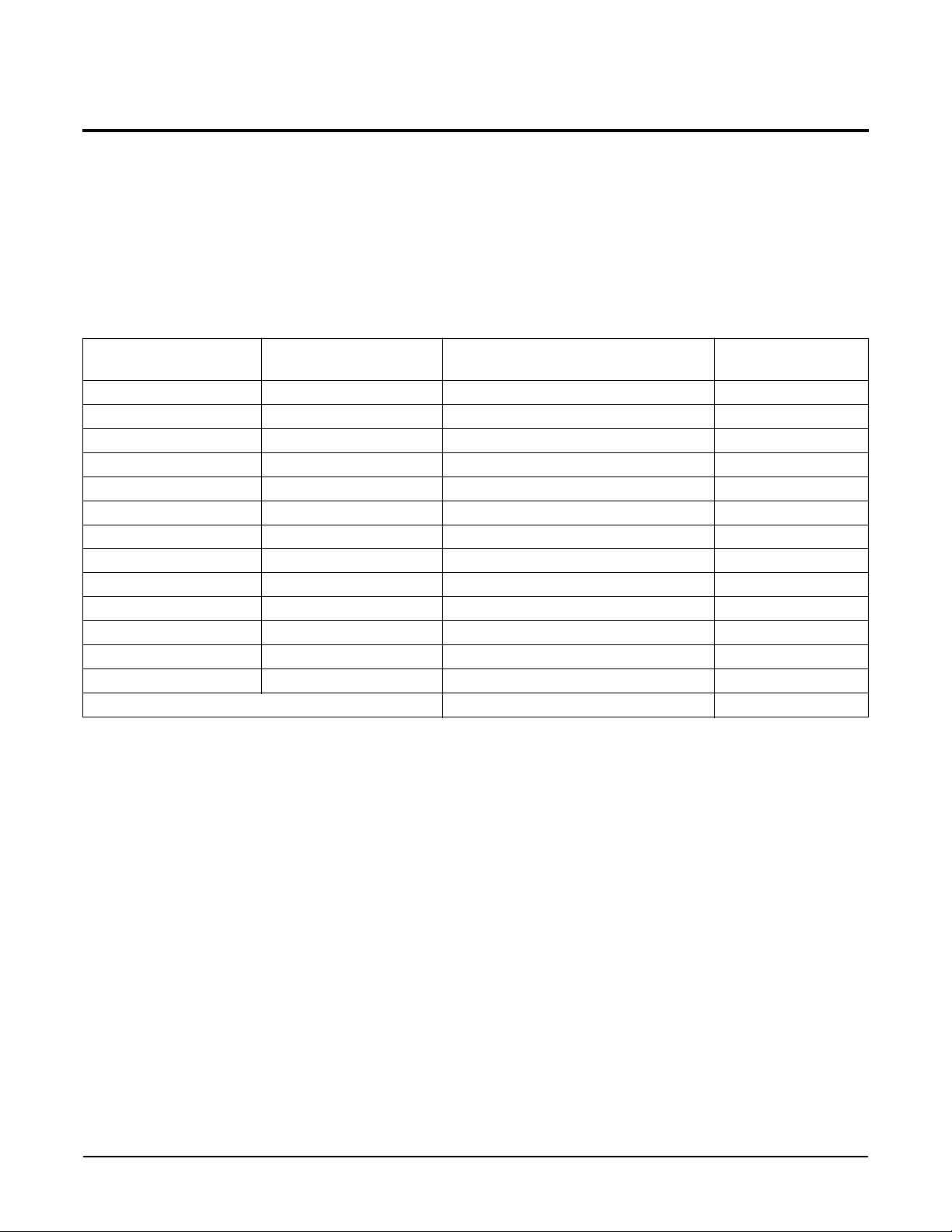

OPERATIONAL MODES

THE FIRST BYTE

IN THE PROTOCOL

0 0 0XXXXA Write address Write (Sector) Write

0 0 1XXXXA Read address Read (Random / Sequential) Read

0 1 0XXXXA Write address Write (Sector) Configuration

0 1 1XXXXA Read address Read (Random / Sequential) Configuration

1 0 0XXXXX 0 0 0 0 0 0 0 0 Program write-password Write

1 0 0XXXXX 0 0 0 1 0 0 0 0 Program read-password Read

1 0 0XXXXX 0 0 1 0 0 0 0 0 Program configuration-password Configuration

1 0 0XXXXX 0 0 1 1 0 0 0 0 Reset write password (all 0’s) Configuration

1 0 0XXXXX 0 1 0 0 0 0 0 0 Reset read password (all 0’s) Configuration

1 0 0XXXXX 0 1 0 1 0 0 0 0 Program configuration registers Configuration

1 0 0XXXXX 0 1 1 0 0 0 0 0 Read configuration registers Configuration

1 0 0XXXXX 0 1 1 1 0 0 0 0 Mass program Configuration

1 0 0XXXXX 1 0 0 0 0 0 0 0 Mass erase Configuration

All the rest Reserved

THE SECOND BYTE

IN THE PROTOCOL COMMAND DESCRIPTION PASSWORD USED:

Acknowledge

Acknowledge is a software convention used to indicate

successful data transfer. The transmitting device, either

master or slave, will release the bus after transmitting

eight bits. Dur ing the ninth clock cycle the receiver will

pull the SDA line LOW to acknowledge that it received

the eight bits of data.

7002 FRM T04

6

X76F041

.

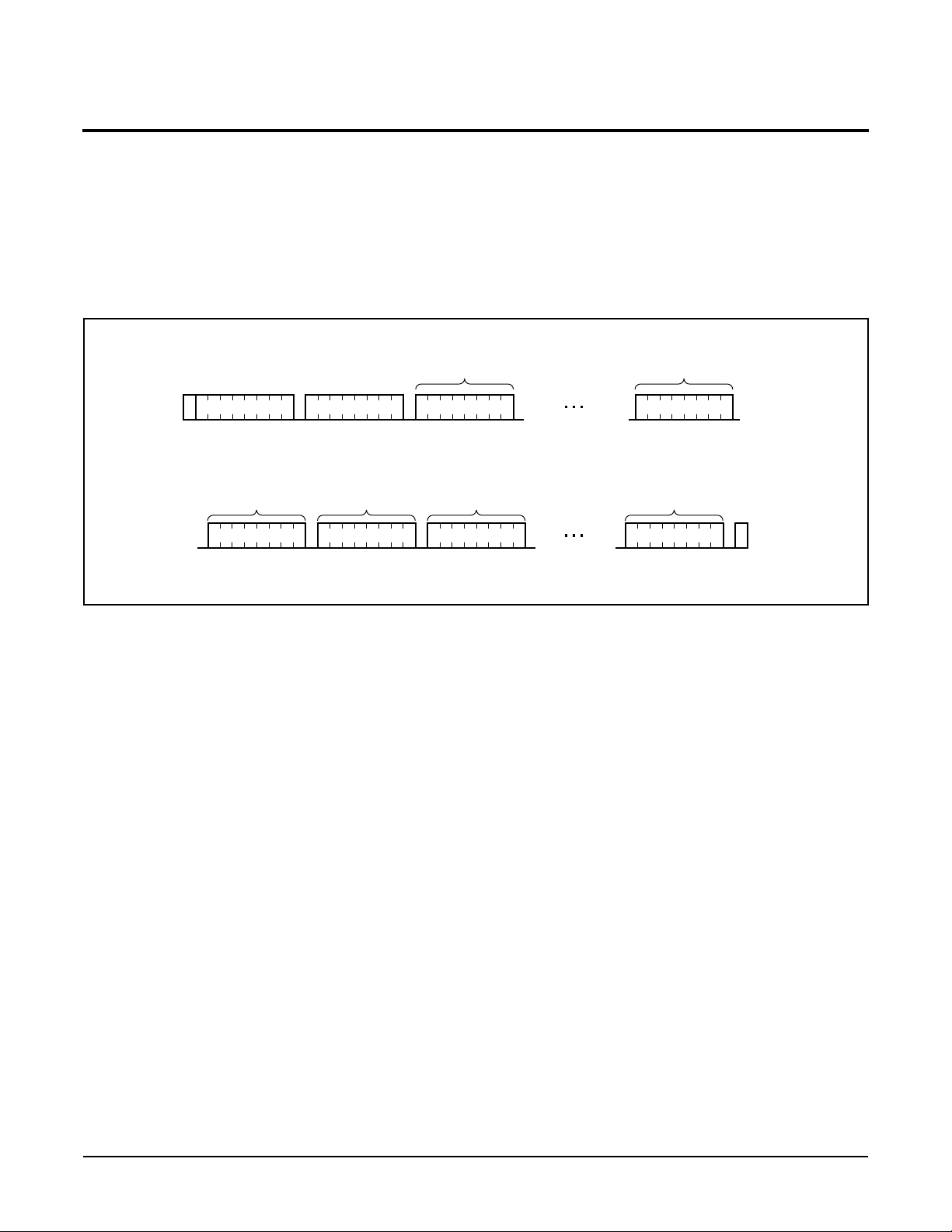

WRITE OPERATION

Sector Write

The Sector Write mode requires issuing the 3-bit write

command followed by the address, password if required

and then the data bytes transferred as illustrated in Fig-

Figure 6. Sector Write

S

T

SDA LINE

IF PASSWORD

MATCH THEN

A

C M D AXAXAXAXA8A7A6A5A4A3A2A1A

R

T

S

A

C

K

DATA 0

A

C

K

DATA 1 DATA 2

A

C

K

PASSWORD 7

0

A

C

K

A

C

K

WRITE

ure 6. Eight bytes must be transferred. After the last byte

to be transferred is acknowledged, a stop condition is

issued, which starts the nonvolatile write cycle. If more

than 8 bytes are transferred the data will wrap around

and previous data will be ov erwritten. All data will be written to the same sector as defined by A

WRITE

PASSWORD 0

A

C

K

A

C

K

A

C

K

DATA 7

–A

8

3

WAIT

tWC/ACK POLLING

A

C

K

S

T

O

P

WAIT

t

WC

S

A

C

K

7002 ILL F10.1

7

Loading...

Loading...