Xiaomi MiA3 Shematics

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

6

5

4

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

BLOCKSHEET

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

C

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

B

41

42

43

44

45

46

47

48

49

50

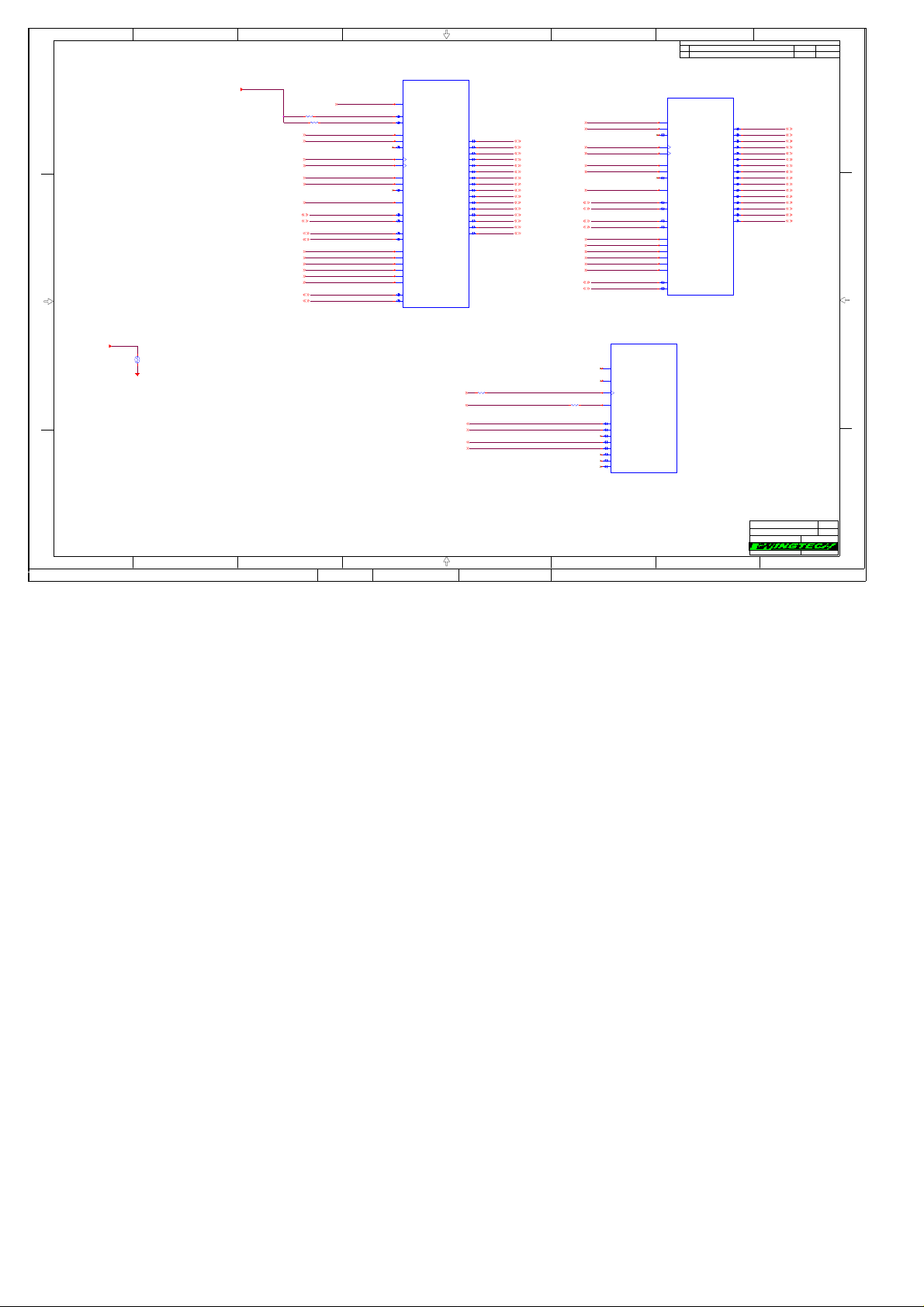

SCHEMATIC

TITLE

TABLE_OF_CONTENTS

GPIO TABLE

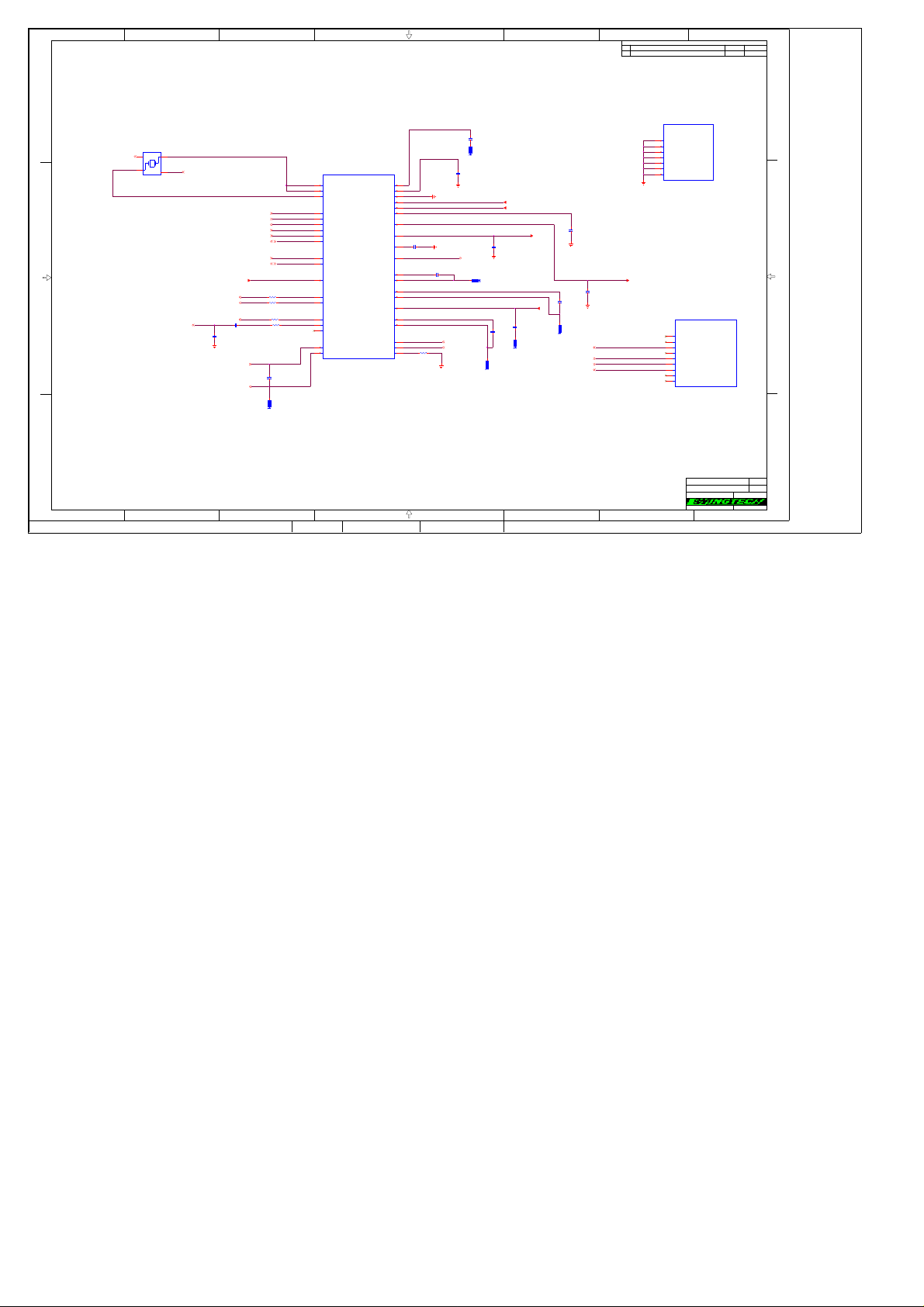

BLOCK DIAGRAM

SM6150 CONTROL

SM6150 GPIO

SM6150 LP GPIO

SM6150 EBI0/1

SM6150 MIPI-CSI/DSI

SM6150 WCSS/RF

SM6150 PWR_1

SM6150 PWR_2

SM6150 PWR_3

SM6150 DECAPS

SM6125 GND

Reserved_1

PM6125 HK/IO

PM6125_Bucks_S1-S4

PM6125_Bucks_S5-S8

PM6125_LDOs

DECAPS

PMI632_Control

PMI632_Charger/PD PHY

PMI632_LCD/VIB/RGB/Flash

SMB1355

eMCP/uMCP

eMCP_POWER

WCD9370

AUDIO

DISPLAY

FRONT CAMERA

REAR CAMERA

CAM eLDO

Sensors

PM8008 CAM_LDO

SIM/SD

KEYPAD/INDICATOR

BATT/B2B

Audio over Type C

RCM/DEBUG

SDR480_POWER

SDR480_GND

SDR480_PRX_DRX_FBRX

QPA8673

QET4101

Reserved_4

Reserved_5

PRx_HB

PRx_MB

PRx_LB

A

TABLE_OF_CONTENTS

BLOCK

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

6 47 58 3 2 1

SCHEMATIC

Reserved_6

Reserved_7

QPA8687

DRX_QDM2302

DRX_Reserved_1

DRX_Reserved_2

DRX_Reserved_3

DRX_Reserved_4

QAT3522

QAT3518_DRX_ANT1

WCN3950_SH

WLAN_RF_SH

WCS_NFC_SN100U

SHEILDING_FRAME

CHANGE LIST

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

SHEET

BLOCK BLOCK

LAST EDIT DATE

SCHEMATICSHEET

SHEET

SCHEMATIC

Title

Title

Title

Page Name = 01_TABLE_OF_CONTENTS

Page Name = 01_TABLE_OF_CONTENTS

Page Name = 01_TABLE_OF_CONTENTS

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

1 53

1 53

1 53

D

C

B

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

D

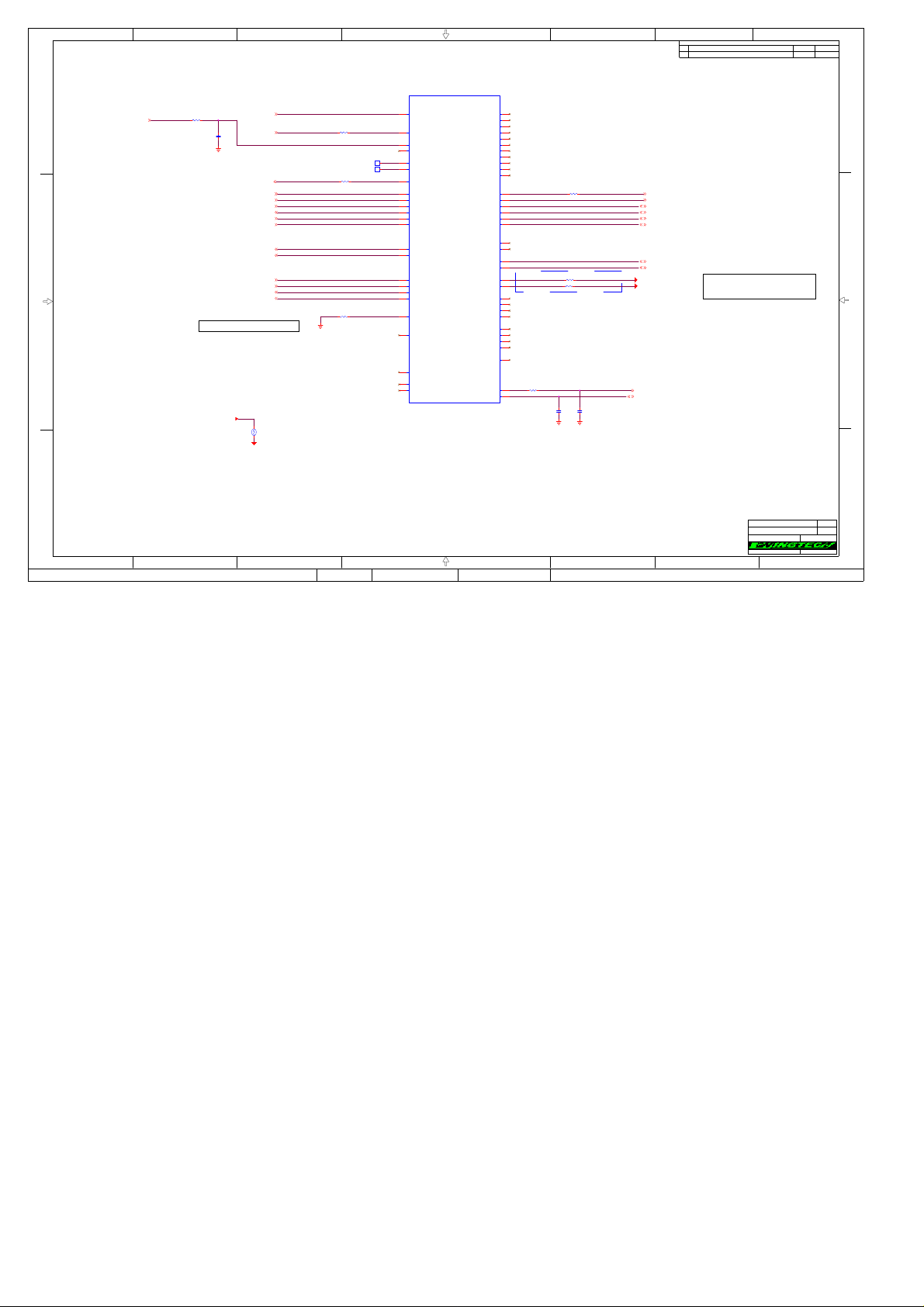

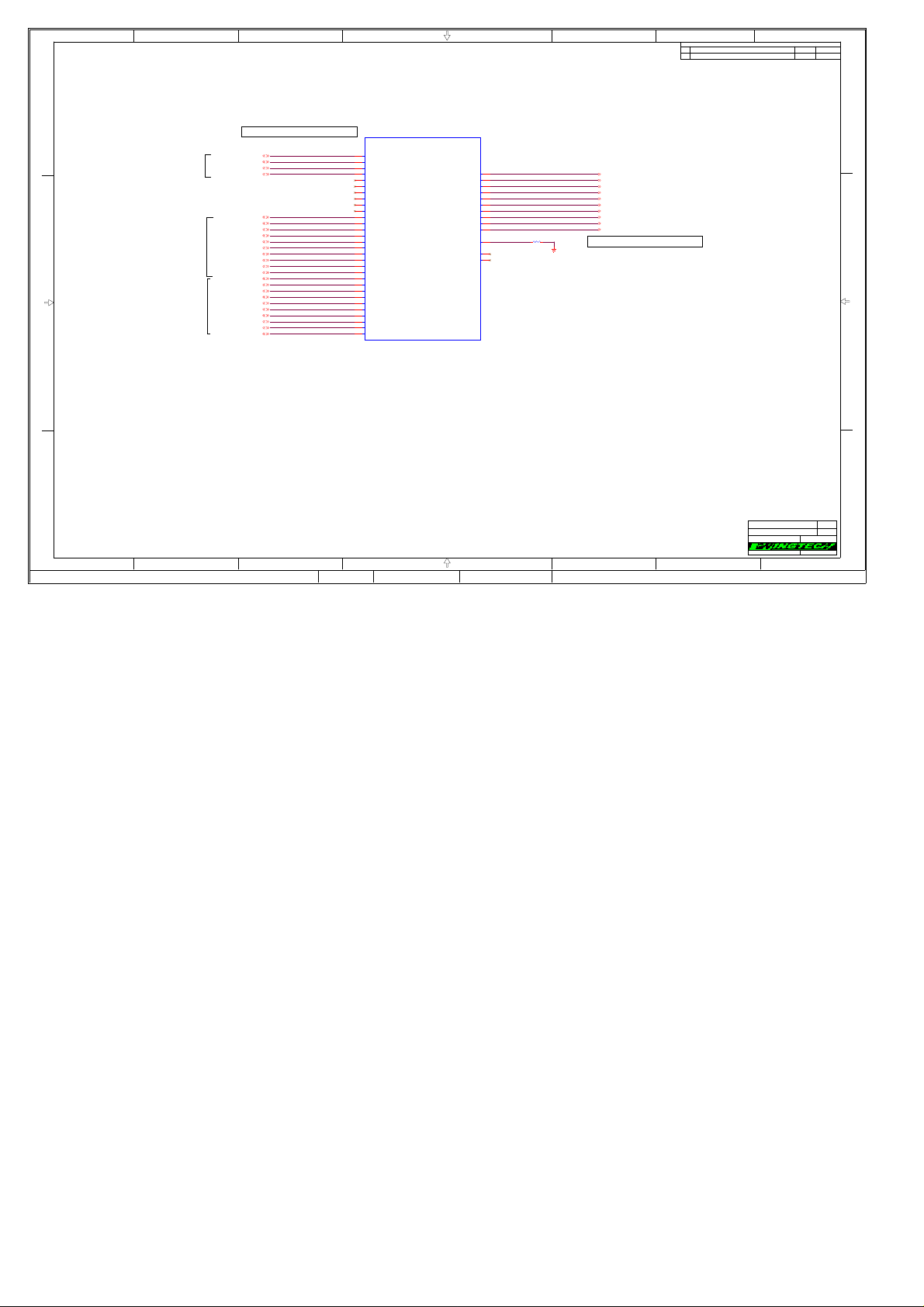

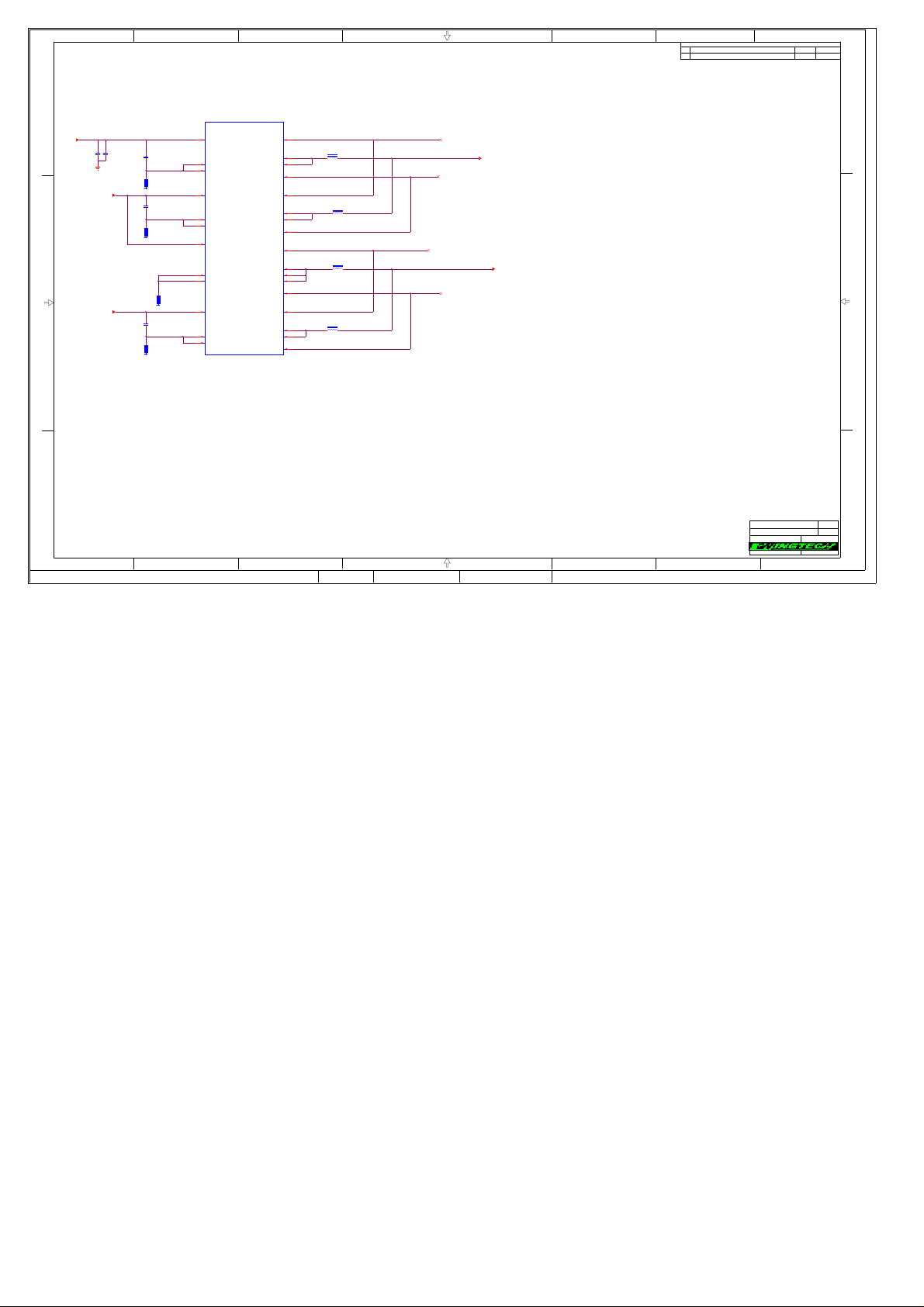

PON_RESET_N[16,17]

R0205

0;0.5A;0201

C0203

0.047uF;20%;6.3V;0201

C

UFS_REXT: DNI on Internal test chip, 100 OHM on SM6125

Can float if UFS is not used

B

QUIET_THERM [16]

LN_BB_CLK1[16]

SLEEP_CLK[16,77]

PS_HOLD[16]

JTAG_SRST_N[47]

JTAG_TCK[47]

JTAG_TDI[47]

JTAG_TMS[47]

JTAG_TRST_N[47]

12

6

SDM_RESIN_N_R

JTAG_TDO[47]

UFS_RESET[11]

UFS_REF_CLK[11]

UFS_RX_M[11]

UFS_RX_P[11]

UFS_TX_M[11]

UFS_TX_P[11]

Place near to the SDM about 1cm and put ino the shielding

NTC0201

100K;1%;0201

5

MFG_NO

CONTROL

AB34

R0225

0;0.5A;0201

R0206

0;0.5A;0201

R0210

UFS_REXT

100;5%;0201

CXO

AF24

SLEEP_CLK

AH19

RESIN_N

AE23

RESOUT_N

AG29

1

TP0203

MODE_0

AF29

1

TP0204

MODE_1

AG21

PS_HOLD

AC32

SRST_N

AC33

TCK

AA32

TDI

AD33

TDO

AB32

TMS

AD34

TRST_N

B30

UFS_RESET_N

A30

UFS_REFCLK

D17

UFS_L0_RX_M

E17

UFS_L0_RX_P

D16

UFS_L0_TX_M

E16

UFS_L0_TX_P

B16

UFS_REXT

AE13

QPHY_TPA

AH27

PLL_TEST_SE

AJ30

ATEST0

AE29

ATEST1

4

U0501A

SDC1_RCLK

SDC1_DATA_0

SDC1_DATA_1

SDC1_DATA_2

SDC1_DATA_3

SDC1_DATA_4

SDC1_DATA_5

SDC1_DATA_6

SDC1_DATA_7

SDC2_DATA_0

SDC2_DATA_1

SDC2_DATA_2

SDC2_DATA_3

USB0_DP_AUX_M

USB0_DP_AUX_P

USB0_HS_DM

USB0_HS_DP

USB0_HS_REXT

USB0_SS_REXT

USB0_SS_RX0_M

USB0_SS_RX0_P

USB0_SS_TX0_M

USB0_SS_TX0_P

USB0_SS_RX1_M

USB0_SS_RX1_P

USB0_SS_TX1_M

USB0_SS_TX1_P

USB0_SS_TPA

C32

D32

SDC1_CLK

D31

SDC1_CMD

C34

B33

D33

D34

C33

B34

A33

C31

SDC2_CLK_R

AH21

SDC2_CLK

AJ22

SDC2_CMD

AH22

AH23

AJ24

AH24

W33

W34

P33

P34

USB0_HS_REXT

R34

USB0_SS_REXT

T34

V33

V34

T32

T31

U33

U34

R32

R31

P32

R0211 22;5%;0201

R0213 4.02K;1%;0201

R0208 NF_100;5%;0201

3

SDC2_CLK [45]

SDC2_CMD [45]

SDC2_DATA_0 [45]

SDC2_DATA_1 [45]

SDC2_DATA_2 [45]

SDC2_DATA_3 [45]

USB0_HS_DM [19,47,48]

USB0_HS_DP [19,47,48]

28

DESCRIPTIONLTR

A INITIAL RELEASE

USB0_HS_REXT: 6.04K on Internal test chip, 4.02K on SM6125

R34 can connect to GND if USB0 is not used

USB0_SS_REXT: 0OHM on Internal test chip, 100OHM on SM6125

T34 can float if DP/USB0 is not used

REVISIONS

1

APPROVED

DATE

D

C

B

R0215

PMIC_SPMI_CLK

PMIC_SPMI_DATA

AH18

AJ19

0;0.5A;0201

NF_33pf;30%;50V;0201

C0202

C0201

NF_33pf;30%;50V;0201

PMIC_SPMI_CLK [16,17]

PMIC_SPMI_DATA [16,17]

A

SM6125 CONTROL

Title

Title

Title

Page Name = 02_SM6125 CONTROL

Page Name = 02_SM6125 CONTROL

Page Name = 02_SM6125 CONTROL

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER:

DESIGNER:

Sheet of

Sheet of

Sheet of

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

6 47 58 3 2 1

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

Date:

REV:

REV:

REV:

Size

Size

Size

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

2 53

2 53

2 53

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

D

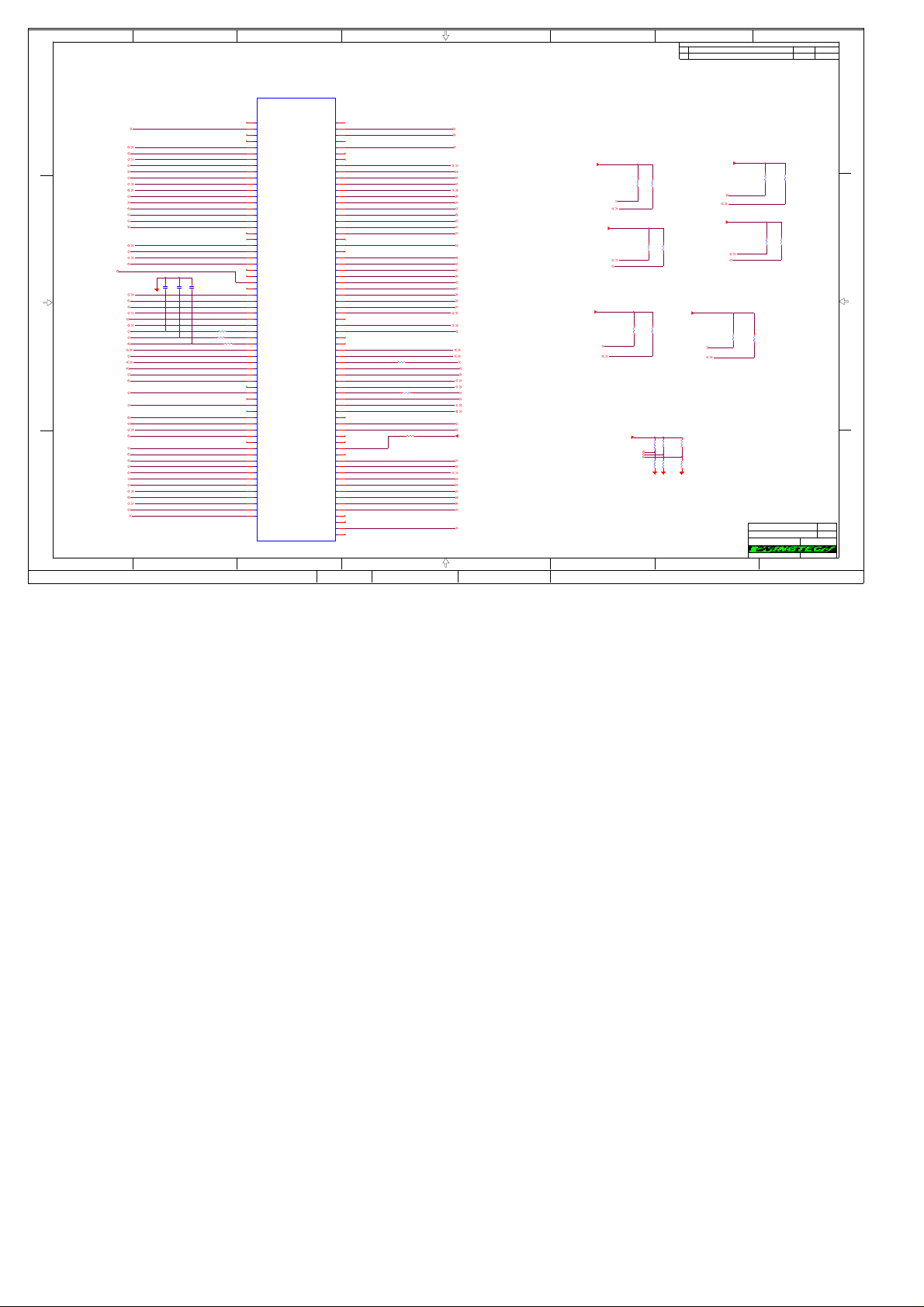

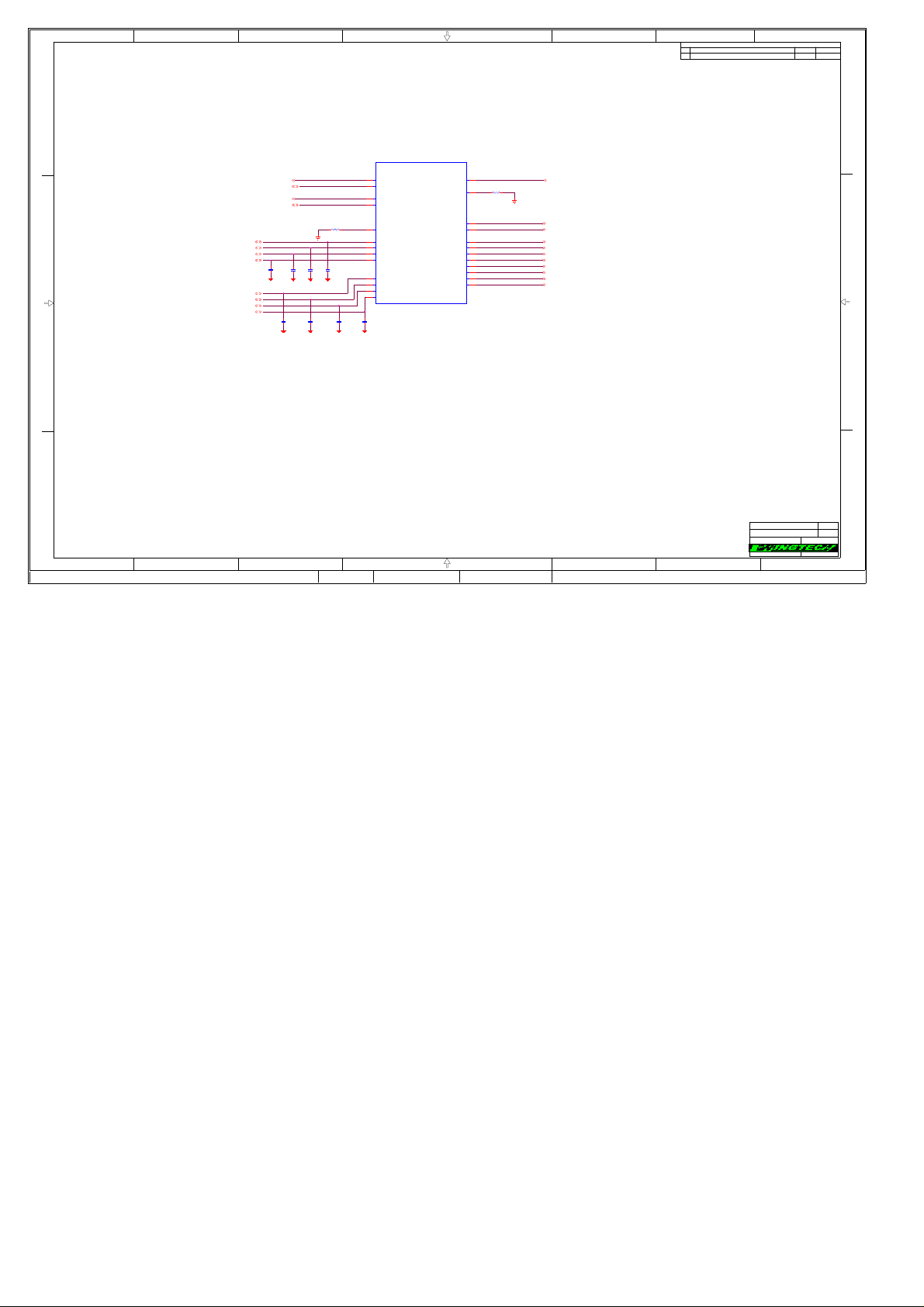

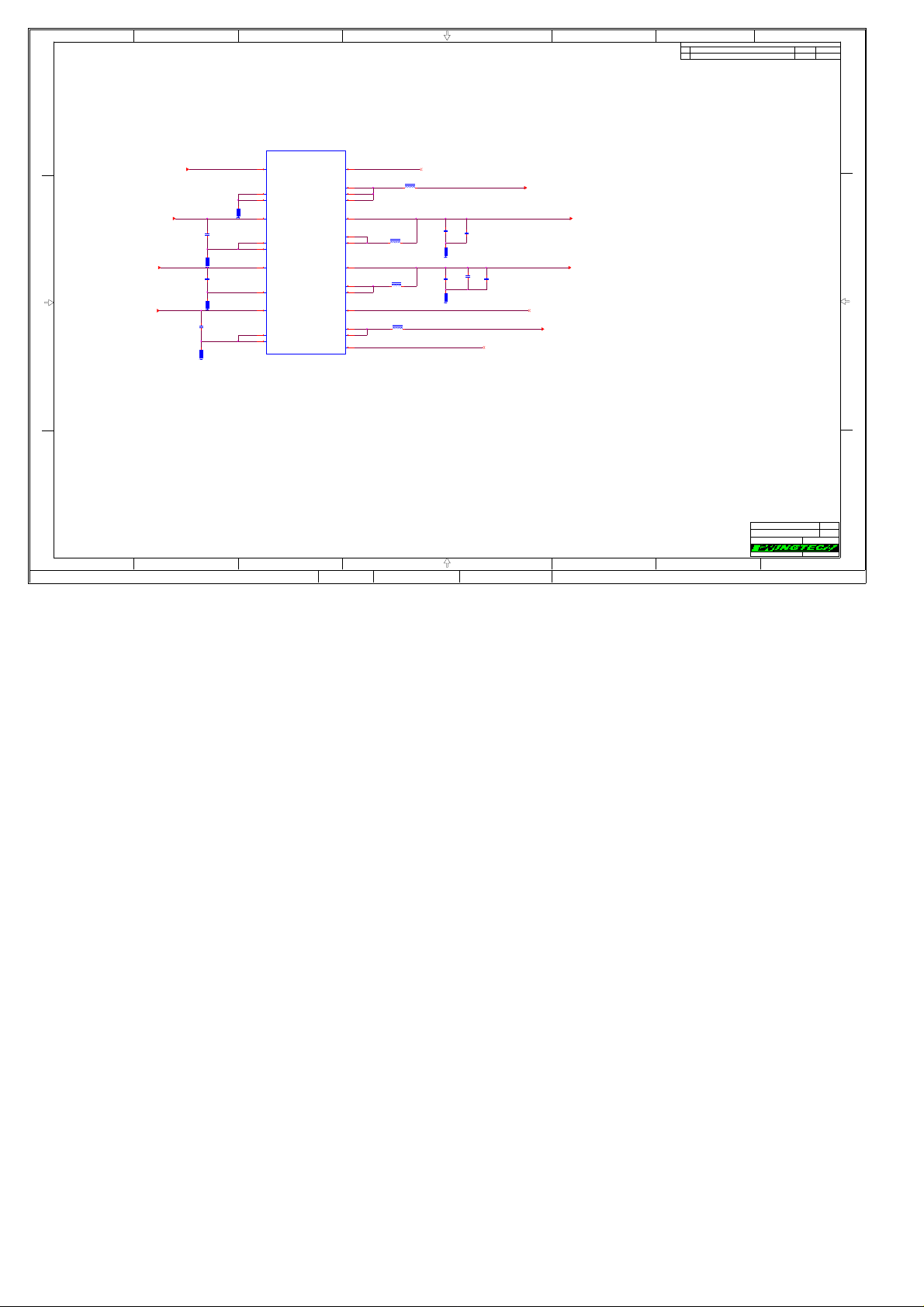

IRTX_OUT[42]

SPK_SDA[3,37]

SPK_SCL[3,37]

TS_I2C_SDA[3,40]

TS_I2C_SCL[3,40]

LCD_ID[40]

BOARD_ID1[3]

WCN_UART_CTS_N[77]

WCN_UART_RFR_N[77]

WCN_UART_TX_N[77]

WCN_UART_RX_N[77]

CAM0_DVDD_EN[21]

CAM0_AVDD_EN[21]

DBG_UART_TX[47]

C

B

A

DBG_UART_RX[47]

CAM1_2_3_AVDD_EN[21]

CAM1_2_DVDD_EN[21]

SNS_I3C_SDA[3,44]

SNS_I3C_SCL[3,44]

VDDI_1P8_EN[40]

SNS_I2C_SDA[3,44,61]

SNS_I2C_SCL[3,44,61]

FP_SPI_MISO[48]

FP_SPI_MOSI[48]

FP_SPI_SCLK[48]

FP_SPI_CS_N[48]

CAM_MCLK0[41]

CAM_MCLK1[41]

CAM_MCLK2[41]

CCI_I2C_SDA0[3,41]

CCI_I2C_SCL0[3,41]

CCI_I2C_SDA1[3,41]

CCI_I2C_SCL1[3,41]

CAM3_RST_N[41]

CAM2_RST_N[41]

CAM_MCLK3[41]

CAM1_RST_N[41]

CAM0_RST_N[41]

CAM0_AVDD_EN2[21]

QLINK_REQUEST[58]

QLINK_ENABLE[58]

GRFC1

GRFC2

GRFC3[67]

GRFC4[69]

GRFC5[69]

GRFC8

GRFC9

RFFE1_DATA[58]

RFFE1_CLK[58]

RFFE2_DATA[62,67,70,75]

RFFE2_CLK[62,67,70,75]

GRFC10[48]

33pf;30%;50V;0201

C0301

33pf;30%;50V;0201

33pf;30%;50V;0201

C0302

C0303

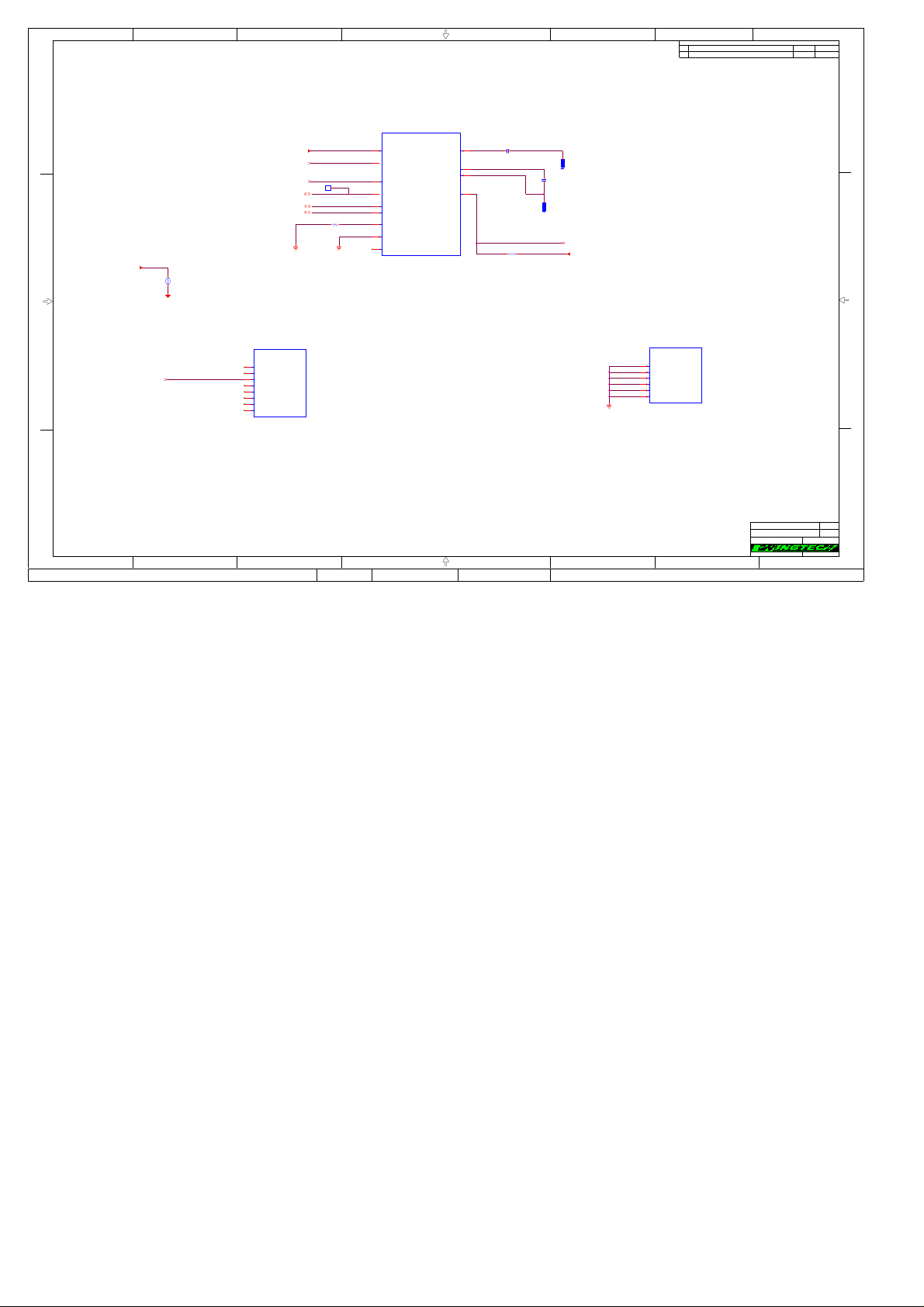

BOOT_CONFIG [2]

BOOT_CONFIG [10]

BOOT_CONFIG [11]

BOOT_CONFIG [8]

R0313

0;0.5A;0201

SM6125 GPIO

6

U0501B

MFG_NO

GPIO

L33

GPIO_0

L34

BOOT_CONFIG [9]

GPIO_1

L32

GPIO_2

L31

GPIO_3

AG34

GPIO_4

AD32

GPIO_5

N34

GPIO_6

M33

GPIO_7

N33

GPIO_8

M31

GPIO_9

L4

GPIO_10

K1

GPIO_11

K2

GPIO_12

L5

GPIO_13

AF34

GPIO_14

AE33

GPIO_15

AF33

GPIO_16

AE32

GPIO_17

AH1

GPIO_18

AG1

GPIO_19

AF2

GPIO_20

AF1

GPIO_21

AH34

GPIO_22

AG33

GPIO_23

AF32

GPIO_24

AH33

GPIO_25

AJ33

GPIO_26

AG32

GPIO_27

AE31

GPIO_28

AC31

GPIO_29

AB31

GPIO_30

AB30

GPIO_31

AC30

GPIO_32

AD30

GPIO_33

R0325

AH5

GPIO_34

AG6

0;0.5A;0201

GPIO_35

R0314

AD7

GPIO_36

AE7

0;0.5A;0201

GPIO_37

AE6

GPIO_38

AF6

GPIO_39

AG5

GPIO_40

AH4

GPIO_41

AJ3

GPIO_42

AH3

GPIO_43

AH8

GPIO_44

AG8

GPIO_45

AH7

GPIO_46

AE8

GPIO_47

AD8

GPIO_48

AG7

GPIO_49

AG20

GPIO_50

AE19

GPIO_51

AG26

GPIO_52

AF21

BOOT_CONFIG[3]

GPIO_53

AG22

GPIO_54

AJ27

GPIO_55

AE20

BOOT_CONFIG[0]

GPIO_56

AH26

GPIO_57

AH25

GPIO_58

AJ25

GPIO_59

AF16

GPIO_60

AG17

GPIO_61

AE15

GPIO_62

AD15

GPIO_63

AJ18

GPIO_64

6 47 58 3 2 1

AH17

GPIO_65

AG16

GPIO_66

AG15

GPIO_67

AH16

GPIO_68

AJ16

GPIO_69

AH15

GPIO_70

AJ15

GPIO_71

AJ21

GPIO_72

AG19

GPIO_73

AH20

GPIO_74

AE18

GPIO_75

AF18

GPIO_76

AE17

GPIO_77

AG18

GPIO_78

AE16

GPIO_79

AH29

GPIO_80

AG28

GPIO_81

AH28

GPIO_82

AE22

GPIO_83

AE21

GPIO_84

AJ28

GPIO_85

AG27

GPIO_86

AH32

GPIO_87

AG31

GPIO_88

AH31

GPIO_89

AJ31

GPIO_90

AG30

GPIO_91

AF30

GPIO_92

AH30

GPIO_93

AJ9

GPIO_94

AE9

GPIO_95

AJ8

GPIO_96

AH9

GPIO_97

AF19

GPIO_98

AF25

GPIO_99

AF27

GPIO_100

AF28

GPIO_101

AF9

GPIO_102

AG9

GPIO_103

L2

GPIO_104

L3

GPIO_105

N3

GPIO_106

N4

GPIO_107

N5

GPIO_108

M1

GPIO_109

M2

GPIO_110

L1

GPIO_111

M5

GPIO_112

AF3

GPIO_113

AJ2

GPIO_114

AH2

GPIO_115

AG2

GPIO_116

AH6

GPIO_117

AJ6

GPIO_118

AJ5

GPIO_119

AF7

GPIO_120

P5

GPIO_121

P4

GPIO_122

N1

GPIO_123

N2

GPIO_124

AG4

GPIO_125

AF5

GPIO_126

AG3

GPIO_127

AE4

GPIO_128

AF22

GPIO_129

AG23

GPIO_130

AG24

GPIO_131

AG25

GPIO_132

5

BOOT_CONFIG [7]

BOOT_CONFIG [15]

Force USB boot pol sel

R0324

NF_2.2K;5%;0201

R0328

0;0.5A;0201

R0350

10K;5%;0201

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

VREG_L9A_1P8[3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

4

GRFC11 [48]

GRFC_ANT_DET [61]

GRFC13 [48]

UIM2_DATA [45]

UIM2_CLK [45]

UIM2_RESET [45]

UIM2_PRESENT [45]

UIM1_DATA [45]

UIM1_CLK [45]

UIM1_RESET [45]

UIM1_PRESENT [45]

ACCEL_INT [44]

GYRO_INT [44]

IR_LED_EN [21]

FP_LDO_EN [43]

INT_SMARTPA [37]

TS_RESET_N [40]

TS_INT_N [40]

MDP_VSYNC_P [40]

LCD_RESET_N [40]

ALSP_INT_N [44]

FP_INT_N [48]

FP_RST_N [48]

TP_LDO_EN [40]

AUDIO_PA_RST [37]

WCN_SW_CTRL [77]

SD_CARD_DET_N [45]

FORCED_USB_BOOT [47]

USB_PHY_PS [19]

WMSS_RESET [58]

VREG_L9A_1P8 [3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

MSS_LTE_COXM_RXD [77]

SWR_TX_CLK [20]

SWR_TX_DATA0 [20]

SWR_TX_DATA1 [20]

MSS_LTE_COXM_TXD [77]

SWR_RX_CLK [20]

SWR_RX_DATA0 [20]

SWR_RX_DATA1 [20]

CAM_SW_EN [41]

FCAM_SEL [41]

WCD_RESET_N [20]

QCA_SB_CLK [77]

QCA_SB_DATA [77]

CAM_AFVDD_EN [21]

VCI_3P0_EN [40]

I2S1_SCK [37]

I2S1_WS [37]

I2S1_DATA0 [37]

I2S1_DATA1 [37]

SAR_INT_GRFC0 [61]

LAST EDIT DATE

3

I2C BUS PULL-UPs

VREG_L9A_1P8 [3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

R0301

2.2K;5%;0201

R0302

2.2K;5%;0201

TS_I2C_SCL[3,40]

TS_I2C_SDA[3,40]

VREG_L9A_1P8 [3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

R0346

2.2K;5%;0201

SPK_SDA[3,37]

SPK_SCL[3,37]

VREG_L12A_1P8 [3,15,41]

R0312

R0311

2.2K;5%;0201

CCI_I2C_SCL1[3,41]

CCI_I2C_SDA1[3,41]

2.2K;5%;0201

BOARD_ID

VREG_L9A_1P8[3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

R0340

NF_1K;5%;0201

BOARD_ID1[3]

BOARD_ID2[16]

BOARD_ID3[16]

R0341

1K;5%;0201

D_GND D_GND D_GND

A INITIAL RELEASE

R0347

2.2K;5%;0201

CCI_I2C_SCL0[3,41]

CCI_I2C_SDA0[3,41]

R0342

R0344

200K;1%;0201

NF_1K;5%;0201

R0343

R0345

68K;5%;0201

1K;5%;0201

28

SNS_I2C_SCL[3,44,61]

SNS_I2C_SDA[3,44,61]

SNS_I3C_SDA[3,44]

SNS_I3C_SCL[3,44]

VREG_L12A_1P8 [3,15,41]

REVISIONS

DESCRIPTIONLTR

VREG_L9A_1P8 [3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

R0307

2.2K;5%;0201

VREG_L9A_1P8 [3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

R0348

2.2K;5%;0201

R0309

R0310

2.2K;5%;0201

2.2K;5%;0201

Title

Title

Title

Page Name = 03_SM6125 GPIO

Page Name = 03_SM6125 GPIO

Page Name = 03_SM6125 GPIO

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

R0349

2.2K;5%;0201

R0308

2.2K;5%;0201

1

DATE

DESIGNER:

DESIGNER:

DESIGNER:

Sheet of

Sheet of

Sheet of

APPROVED

REV:

REV:

REV:

Size

Size

Size

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

3 53

3 53

3 53

D

C

B

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

D

C

B

6

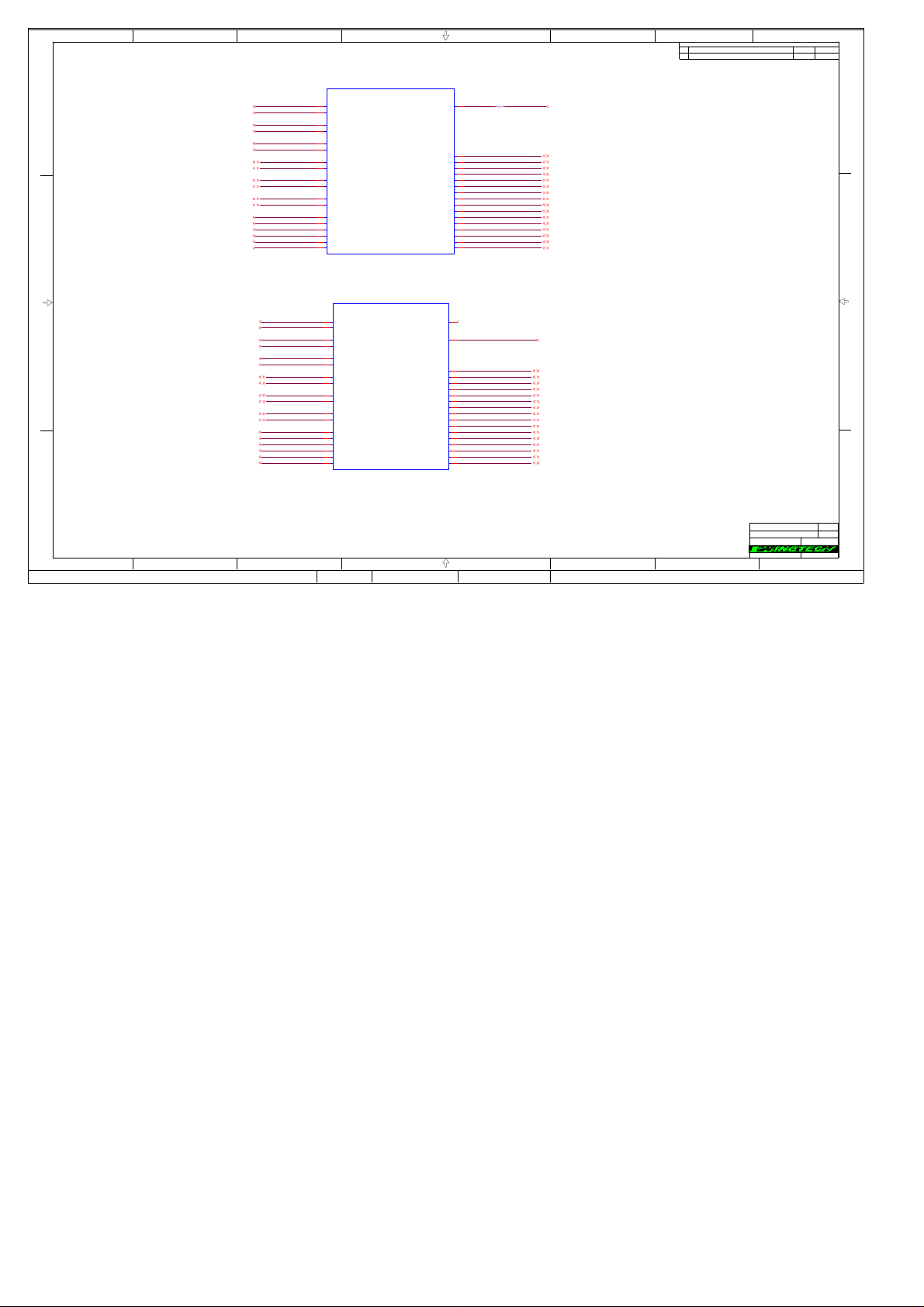

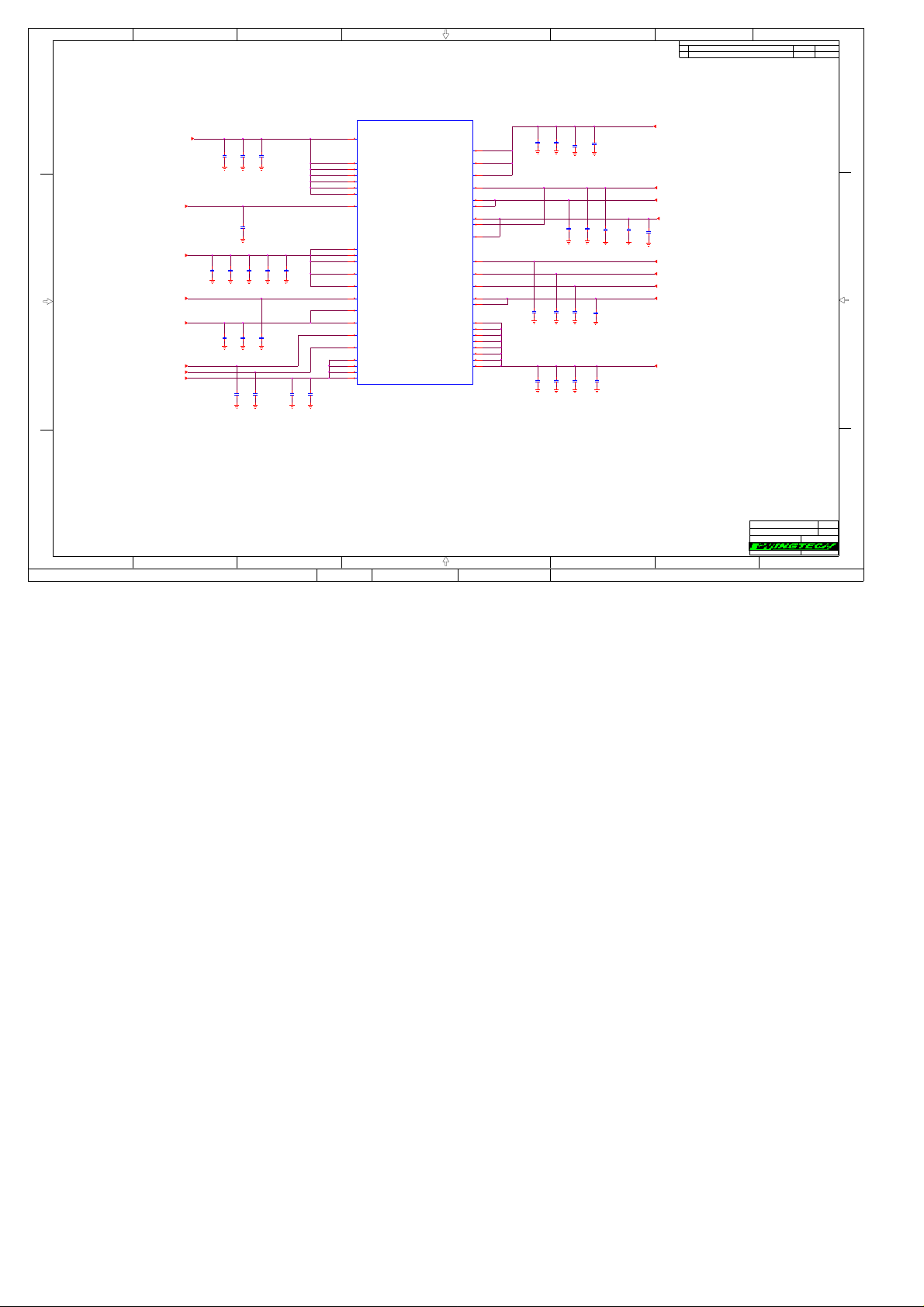

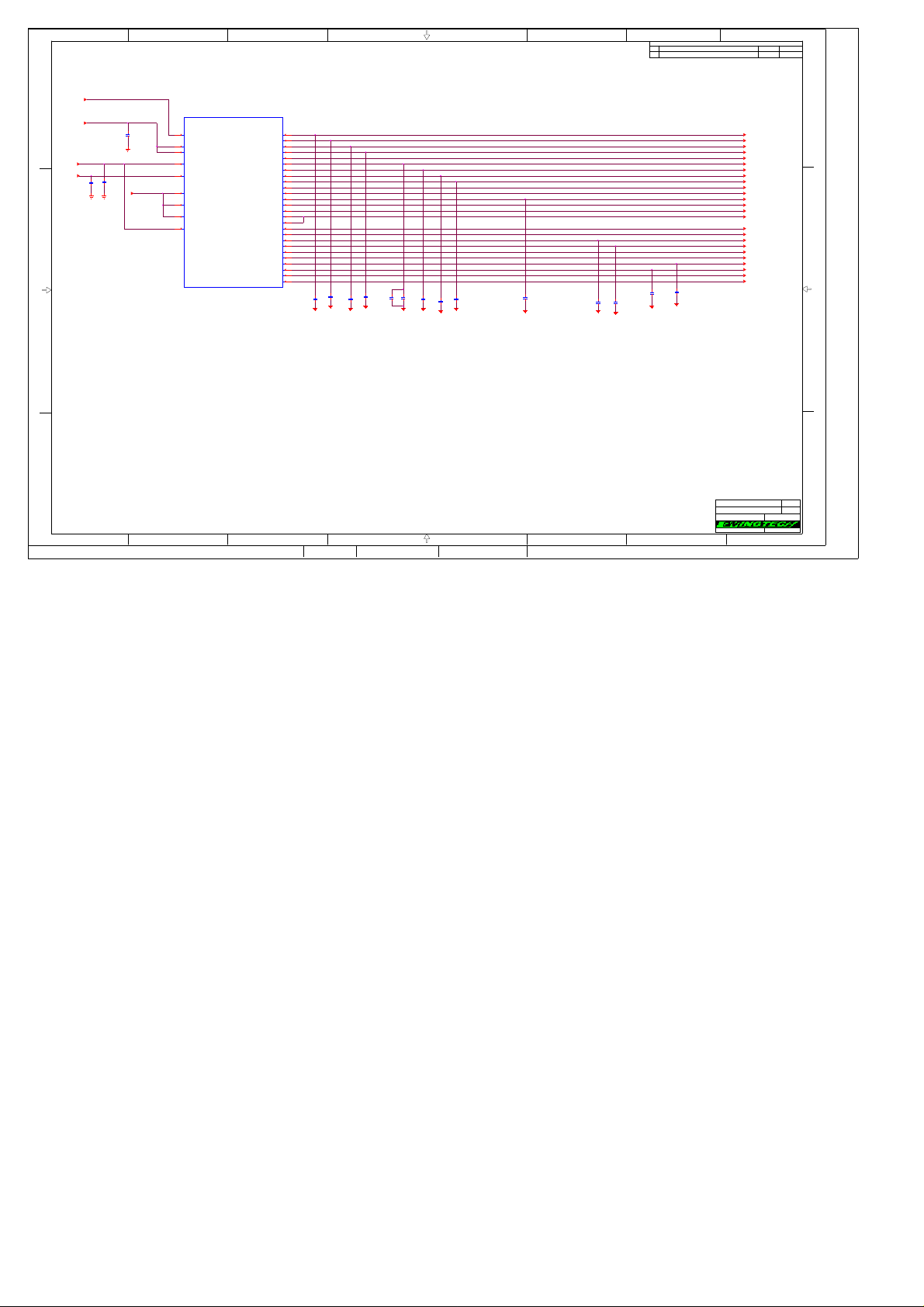

EBI0_CA_CS_0[11]

EBI0_CA_CS_1[11]

EBI0_CA_CK_C[11]

EBI0_CA_CK_T[11]

EBI0_CA_CKE_0[11]

EBI0_CA_CKE_1[11]

EBI0_DMI_0[11]

EBI0_DMI_1[11]

EBI0_DQS_C_0[11]

EBI0_DQS_T_0[11]

EBI0_DQS_C_1[11]

EBI0_DQS_T_1[11]

EBI0_CA_CA_0[11]

EBI0_CA_CA_1[11]

EBI0_CA_CA_2[11]

EBI0_CA_CA_3[11]

EBI0_CA_CA_4[11]

EBI0_CA_CA_5[11]

EBI1_CA_CS_0[11]

EBI1_CA_CS_1[11]

EBI1_CA_CK_C[11]

EBI1_CA_CK_T[11]

EBI1_CA_CKE_0[11]

EBI1_CA_CKE_1[11]

EBI1_DMI_0[11]

EBI1_DMI_1[11]

EBI1_DQS_C_0[11]

EBI1_DQS_T_0[11]

EBI1_DQS_C_1[11]

EBI1_DQS_T_1[11]

EBI1_CA_CA_0[11]

EBI1_CA_CA_1[11]

EBI1_CA_CA_2[11]

EBI1_CA_CA_3[11]

EBI1_CA_CA_4[11]

EBI1_CA_CA_5[11]

D8

EBI0_LP4X_CS0_LP3_CA0

D9

EBI0_LP4X_CS1_LP3_CA2

E11

EBI0_LP4X_CLK_C

D11

EBI0_LP4X_CLK_T

E9

EBI0_LP4X_CKE0_LP3_CKE0

E10

EBI0_LP4X_CKE1

D6

EBI0_LP4X_DMI0_LP3_DQ21

A12

EBI0_LP4X_DMI1_LP3_DQ2

D7

EBI0_LP4X_DQS0_C_LP3_DQS2_C

E7

EBI0_LP4X_DQS0_T_LP3_DQS2_T

E13

EBI0_LP4X_DQS1_C_LP3_DQS0_C

D13

EBI0_LP4X_DQS1_T_LP3_DQS0_T

D10

EBI0_LP4X_CA0_LP3_CS0

B11

EBI0_LP4X_CA1_LP3_CS1

A9

EBI0_LP4X_CA2

B9

EBI0_LP4X_CA3_LP3_CA3

B10

EBI0_LP4X_CA4_LP3_CA4

E8

EBI0_LP4X_CA5_LP3_CA1

E25

EBI1_LP4X_CS0_LP3_CA7

E24

EBI1_LP4X_CS1_LP3_CA6

D22

EBI1_LP4X_CLK_C_LP3_CLK_C

E22

EBI1_LP4X_CLK_T_LP3_CLK_T

D24

EBI1_LP4X_CKE0

D23

EBI1_LP4X_CKE1_LP3_CKE1

E27

EBI1_LP4X_DMI0_LP3_DQ26

A20

EBI1_LP4X_DMI1_LP3_DQ14

E26

EBI1_LP4X_DQS0_C_LP3_DQS3_C

D26

EBI1_LP4X_DQS0_T_LP3_DQS3_T

D20

EBI1_LP4X_DQS1_C_LP3_DQS1_C

E20

EBI1_LP4X_DQS1_T_LP3_DQS1_T

E23

EBI1_LP4X_CA0_LP3_CA5

B21

EBI1_LP4X_CA1

A23

EBI1_LP4X_CA2_LP3_CA8

B23

EBI1_LP4X_CA3

B22

EBI1_LP4X_CA4

D25

EBI1_LP4X_CA5_LP3_CA9

5

U0501C

MFG_NO

EBI0

U0501D

MFG_NO

EBI1

EBI0_LP4X_DQ0_LP3_DQ20

EBI0_LP4X_DQ1_LP3_DQ19

EBI0_LP4X_DQ2_LP3_DQ23

EBI0_LP4X_DQ3_LP3_DMI2

EBI0_LP4X_DQ4_LP3_DQ18

EBI0_LP4X_DQ5_LP3_DQ22

EBI0_LP4X_DQ6_LP3_DQ16

EBI0_LP4X_DQ7_LP3_DQ17

EBI0_LP4X_DQ8_LP3_DQ7

EBI0_LP4X_DQ9_LP3_DMI0

EBI0_LP4X_DQ10_LP3_DQ3

EBI0_LP4X_DQ11_LP3_DQ1

EBI0_LP4X_DQ12_LP3_DQ4

EBI0_LP4X_DQ13_LP3_DQ0

EBI0_LP4X_DQ14_LP3_DQ5

EBI0_LP4X_DQ15_LP3_DQ6

DDR_RESET_N

EBI1_LP4X_DQ0_LP3_DQ27

EBI1_LP4X_DQ1_LP3_DQ28

EBI1_LP4X_DQ2_LP3_DQ24

EBI1_LP4X_DQ3_LP3_DMI3

EBI1_LP4X_DQ4_LP3_DQ29

EBI1_LP4X_DQ5_LP3_DQ25

EBI1_LP4X_DQ6_LP3_DQ31

EBI1_LP4X_DQ7_LP3_DQ30

EBI1_LP4X_DQ8_LP3_DQ8

EBI1_LP4X_DQ9_LP3_DMI1

EBI1_LP4X_DQ10_LP3_DQ12

EBI1_LP4X_DQ11_LP3_DQ13

EBI1_LP4X_DQ12_LP3_DQ11

EBI1_LP4X_DQ13_LP3_DQ15

EBI1_LP4X_DQ14_LP3_DQ10

EBI1_LP4X_DQ15_LP3_DQ9

EBI0_CAL

EBI1_TEST

4

R0401

F15

240;1%;0201

A6

B6

B7

A8

E5

B8

E6

D5

E14

D14

B14

B12

B13

A11

E12

D12

F18

B29

A26

B26

B25

A24

D28

B24

D27

E28

D19

E19

B18

B20

B19

A21

D21

E21

DDR_RESET_N [11]

EBI1_DQ_0 [11]

EBI1_DQ_1 [11]

EBI1_DQ_2 [11]

EBI1_DQ_3 [11]

EBI1_DQ_4 [11]

EBI1_DQ_5 [11]

EBI1_DQ_6 [11]

EBI1_DQ_7 [11]

EBI1_DQ_8 [11]

EBI1_DQ_9 [11]

EBI1_DQ_10 [11]

EBI1_DQ_11 [11]

EBI1_DQ_12 [11]

EBI1_DQ_13 [11]

EBI1_DQ_14 [11]

EBI1_DQ_15 [11]

VREG_L6A_0P6 [9,11,12,15]

EBI0_DQ_0 [11]

EBI0_DQ_1 [11]

EBI0_DQ_2 [11]

EBI0_DQ_3 [11]

EBI0_DQ_4 [11]

EBI0_DQ_5 [11]

EBI0_DQ_6 [11]

EBI0_DQ_7 [11]

EBI0_DQ_8 [11]

EBI0_DQ_9 [11]

EBI0_DQ_10 [11]

EBI0_DQ_11 [11]

EBI0_DQ_12 [11]

EBI0_DQ_13 [11]

EBI0_DQ_14 [11]

EBI0_DQ_15 [11]

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

C

B

A

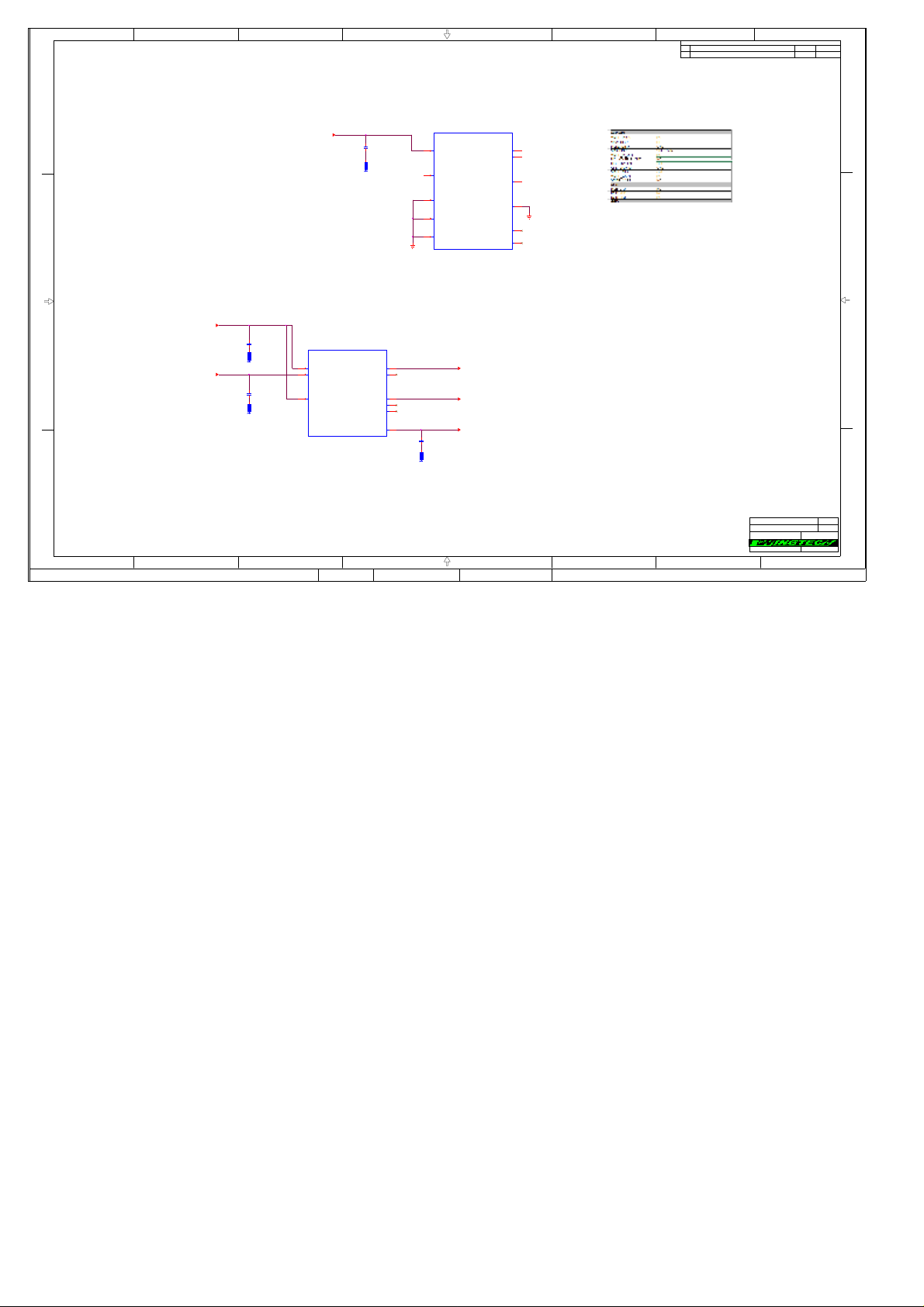

SM6125 EBI0/1

Title

Title

Title

Page Name = 04_SM6125 EBI0_1

Page Name = 04_SM6125 EBI0_1

Page Name = 04_SM6125 EBI0_1

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

6 47 58 3 2 1

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

4 53

4 53

4 53

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

6

5

4

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

C

B

A

SM6125 MIPI-CSI/DSI

Depth

Rear CAMERA

FRONT/WIDE CAMERA

compatible MIPI interface camera

MIPI_CSI0_CLK_P[41]

MIPI_CSI0_CLK_M[41]

MIPI_CSI0_L0_P[41]

MIPI_CSI0_L0_M[41]

MIPI_CSI1_CLK_P[41]

MIPI_CSI1_CLK_M[41]

MIPI_CSI1_L0_P[41]

MIPI_CSI1_L0_M[41]

MIPI_CSI1_L1_P[41]

MIPI_CSI1_L1_M[41]

MIPI_CSI1_L2_P[41]

MIPI_CSI1_L2_M[41]

MIPI_CSI1_L3_P[41]

MIPI_CSI1_L3_M[41]

MIPI_CSI2_CLK_P[41]

MIPI_CSI2_CLK_M[41]

MIPI_CSI2_L0_P[41]

MIPI_CSI2_L0_M[41]

MIPI_CSI2_L1_P[41]

MIPI_CSI2_L1_M[41]

MIPI_CSI2_L2_P[41]

MIPI_CSI2_L2_M[41]

MIPI_CSI2_L3_P[41]

MIPI_CSI2_L3_M[41]

U0501E

MFG_NO

R4

CSI0_NC_CLK_P

R3

CSI0_A0_CLK_M

R2

CSI0_B0_LN0_P

R1

CSI0_C0_LN0_M

T4

CSI0_A1_LN1_P

T3

CSI0_B1_LN1_M

U4

CSI0_C1_LN2_P

U3

CSI0_A2_LN2_M

U2

CSI0_B2_LN3_P

U1

CSI0_C2_LN3_M

V1

CSI1_NC_CLK_P

V2

CSI1_A0_CLK_M

V3

CSI1_B0_LN0_P

V4

CSI1_C0_LN0_M

W3

CSI1_A1_LN1_P

W4

CSI1_B1_LN1_M

Y1

CSI1_C1_LN2_P

Y2

CSI1_A2_LN2_M

Y3

CSI1_B2_LN3_P

Y4

CSI1_C2_LN3_M

AA3

CSI2_NC_CLK_P

AA4

CSI2_A0_CLK_M

AB1

CSI2_B0_LN0_P

AB2

CSI2_C0_LN0_M

AB3

CSI2_A1_LN1_P

AB4

CSI2_B1_LN1_M

AC3

CSI2_C1_LN2_P

AC4

CSI2_A2_LN2_M

AD1

CSI2_B2_LN3_P

AD2

CSI2_C2_LN3_M

6 47 58 3 2 1

MIPI

DSI0_CLK_M

DSI0_CLK_P

DSI0_LN0_M

DSI0_LN0_P

DSI0_LN1_M

DSI0_LN1_P

DSI0_LN2_M

DSI0_LN2_P

DSI0_LN3_M

DSI0_LN3_P

DSI0_REXT_PLL

DSI1_CLK_M

DSI1_CLK_P

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

F33

F34

G33

G34

J33

J34

G31

G32

H32

H31

K34

J31

J32

R0502

1.4K;1%;0201

MIPI_DSI0_CLK_M [40]

MIPI_DSI0_CLK_P [40]

MIPI_DSI0_L0_M [40]

MIPI_DSI0_L0_P [40]

MIPI_DSI0_L1_M [40]

MIPI_DSI0_L1_P [40]

MIPI_DSI0_L2_M [40]

MIPI_DSI0_L2_P [40]

MIPI_DSI0_L3_M [40]

MIPI_DSI0_L3_P [40]

MIPI_DSI0_REXT_PLL: DNI on Internal test chip, 1.4K on SM6150

Title

Title

Title

Page Name = 05_SM6125 MIPI-CSI_DSI

Page Name = 05_SM6125 MIPI-CSI_DSI

Page Name = 05_SM6125 MIPI-CSI_DSI

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER:

DESIGNER:

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

5 53

5 53

5 53

D

C

B

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

6

5

4

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

C

B

A

SM6125 WCSS/RF

WLAN_BT_COEX_CLK[77]

WLAN_BT_COEX_DATA[77]

WL_CMD_CLK[77]

WL_CMD_DATA[77]

WL_Rx_BB_I_N[77]

WL_Rx_BB_I_P[77]

WL_Rx_BB_Q_N[77]

WL_Rx_BB_Q_P[77]

C0601

C0602

C0603

2.7pF;0.25pF;50V;0201

2.7pF;0.25pF;50V;0201

2.7pF;0.25pF;50V;0201

WL_Tx_BB_I_N[77]

WL_Tx_BB_I_P[77]

WL_Tx_BB_Q_N[77]

WL_Tx_BB_Q_P[77]

C0605

2.7pF;0.25pF;50V;0201

C0606

2.7pF;0.25pF;50V;0201

Add C1001-C1008 caps place holder for CLK desense to improve sensitivity.

6 47 58 3 2 1

R0601

6.04K;1%;0201

C0604

2.7pF;0.25pF;50V;0201

H1

WLAN_CXM_CLK

J1

WLAN_CXM_DATA

F1

WLAN_BBD_CLK

G1

WLAN_BBD_DATA

G2

WLAN0_REXT

B2

WLAN_RX_I_M

A2

WLAN_RX_I_P

B1

WLAN_RX_Q_M

C1

WLAN_RX_Q_P

J4

WLAN_TX_I_M

H4

WLAN_TX_I_P

H3

WLAN_TX_Q_M

J3

WLAN_TX_Q_P

C0607

C0608

2.7pF;0.25pF;50V;0201

2.7pF;0.25pF;50V;0201

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

D

U0501F

MFG_NO

WLAN_QLINK

WLAN_XO_CLK

QREFS_CXO_REXT

QLINK_CLK_M

QLINK_CLK_P

QLINK_DL0_M

QLINK_DL0_P

QLINK_DL1_M

QLINK_DL1_P

QLINK_DL2_M

QLINK_DL2_P

QLINK_UL0_M

QLINK_UL0_P

E1

R0602

AA33

3.01K;1%;0201

AF11

AG11

AH13

AJ13

AG12

AF12

AJ11

AH11

AG13

AF13

WLAN_XO_CLK [16]

QPHY_CLK_M [58]

QPHY_CLK_P [58]

QPHY_DL0_M [58]

QPHY_DL0_P [58]

QPHY_DL1_M [58]

QPHY_DL1_P [58]

QPHY_DL2_M [58]

QPHY_DL2_P [58]

QPHY_UL0_M [58]

QPHY_UL0_P [58]

C

B

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

6 53

6 53

6 53

A

V10

V10

V10

Custom

Custom

Custom

LAST EDIT DATE

Title

Title

Title

Page Name = 06_SM6125 WCSS_RF

Page Name = 06_SM6125 WCSS_RF

Page Name = 06_SM6125 WCSS_RF

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

D

JP0701

L9

VREG_S5A_SNS[14]

C

MX

1 2

TOP;BOT

B

C0701

1.0UF;20%;6.3V;0201

21

21

C0706

1.0UF;20%;6.3V;0201

21

C0704

1.0UF;20%;6.3V;0201

21

21

C0705

1.0UF;20%;6.3V;0201

C0707

1.0UF;20%;6.3V;0201

6

VREG_S5A [9,14,15]

21

C0708

1.0UF;20%;6.3V;0201

C0726

10uF;20%;6.3V;0402

21

C0709

1.0UF;20%;6.3V;0201

C0718

10uF;20%;6.3V;0402

21

C0710

1.0UF;20%;6.3V;0201

C0720

NF_10uF;20%;6.3V;0402

21

C0711

1.0UF;20%;6.3V;0201

VDD_QFPROM

VDDPX_VBIAS_SDC

VDD_APC0_1

VDD_APC0_2

VDD_APC0_3

VDD_APC0_4

VDD_APC0_5

VDD_APC0_6

VDD_APC0_7

VDD_APC0_8

VDD_APC0_9

VDD_APC0_10

VDD_APC0_11

VDD_APC0_12

VDD_APC0_13

VDD_APC0_14

VDD_APC0_15

VDD_APC0_16

VDD_APC0_17

VDD_APC0_18

VDD_APC0_19

VDD_APC0_20

VDD_APC0_21

VDD_APC0_22

VDD_APC0_23

4

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

L28

AC18

AA25

AA26

AB25

AB26

AC25

AC26

AD25

AD26

U24

U26

V25

V26

W20

W21

W22

W25

Y20

Y21

Y22

Y23

Y24

Y25

Y26

C0729

0.1uF;20%;6.3V;0201

21

C0712

1.0UF;20%;6.3V;0201

C0727

0.1uF;20%;6.3V;0201

21

C0730

1.0UF;20%;6.3V;0201

C0702

0.1uF;20%;6.3V;0201

C0728

0.1uF;20%;6.3V;0201

C0719

10uF;20%;6.3V;0402

C0717

2.2uF;20%;6.3V;0201

C0722

10uF;20%;6.3V;0402

C0703

2.2uF;20%;6.3V;0201

C0725

10uF;20%;6.3V;0402

C0713

2.2uF;20%;6.3V;0201

VREG_L10A_1P8[8,9,15,16]

VREF_MSM[8,16]

BULK CAPS

C0723

10uF;20%;6.3V;0402

C0714

2.2uF;20%;6.3V;0201

VREG_S1A_S2A[13]

JP0702

RMT_VREG_S1A_S2A_P[13]

L9

1 2

TOP;BOT

C0724

C0721

10uF;20%;6.3V;0402

10uF;20%;6.3V;0402

C0715

2.2uF;20%;6.3V;0201

JJP0703

1 2

TOP;BOT

C0716

2.2uF;20%;6.3V;0201

L9

RMT_VREG_S1A_S2A_M[13]

C

5

U0501G

MFG_NO

VDDMX_1_1

VDDMX_1_2

VDDMX_1_3

VDDMX_1_4

VDDMX_1_5

VDDMX_1_6

VDDMX_1_7

VDDMX_1_8

VDDMX_1_9

VDDMX_1_10

VDDMX_1_11

VDDMX_1_12

VDDMX_1_13

VDDMX_1_14

VDDMX_1_15

VDDMX_1_16

VDDMX_1_17

VDDMX_1_18

VDDMX_1_19

VDDMX_1_20

VDDMX_1_21

VDDMX_1_22

VDDMX_1_23

VDDMX_1_24

VDDMX_1_25

VDDMX_1_26

VDDMX_1_27

VDDMX_1_28

VDDMX_1_29

VDDMX_1_30

VDDMX_1_31

VDDMX_1_32

VDDMX_1_33

VDDMX_1_34

VDDMX_1_35

VDDMX_1_36

VDDMX_1_37

PWR1

AA19

AA20

AA28

AB28

J12

J26

L11

L12

L13

L15

L16

L17

L19

L20

L21

L22

L23

L24

L26

N9

T24

U11

U12

U13

U14

U15

U16

U17

U18

U19

U20

U22

U23

U28

V10

W28

Y18

B

A

SM6125 PWR_1

Title

Title

Title

Page Name = 07_SM6125 PWR_1

Page Name = 07_SM6125 PWR_1

Page Name = 07_SM6125 PWR_1

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

6 47 58 3 2 1

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

7 53

7 53

7 53

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

6

5

4

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

C

RTM_VREG_S3A_S4A_P[13]

RTM_VREG_S3A_S4A_M[13]

B

A

SM6125 PWR_2

1 2

1 2

D

U0501H

MFG_NO

PWR2

VREG_S3A_S4A [13]

MODEM

C0804

1.0UF;20%;6.3V;0201

21

C0826

10uF;20%;6.3V;0402

C0805

1.0UF;20%;6.3V;0201

21

BULK CAPS

C0828

10uF;20%;6.3V;0402

C0806

1.0UF;20%;6.3V;0201

21

C0832

0.1uF;20%;6.3V;0201

C0831

10uF;20%;6.3V;0402

C0833

0.1uF;20%;6.3V;0201

C0807

1.0UF;20%;6.3V;0201

21

C0829

10uF;20%;6.3V;0402

C0808

21

1.0UF;20%;6.3V;0201

C0834

0.1uF;20%;6.3V;0201

C0830

10uF;20%;6.3V;0402

21

C0809

1.0UF;20%;6.3V;0201

C0835

0.1uF;20%;6.3V;0201

C0827

10uF;20%;6.3V;0402

21

C0810

1.0UF;20%;6.3V;0201

JP0802

L9

TOP;BOT

JP0801

L9

TOP;BOT

21

C0803

1.0UF;20%;6.3V;0201

K13

VDDCX_1_1

K14

VDDCX_1_2

K15

VDDCX_1_3

K16

VDDCX_1_4

K17

VDDCX_1_5

K18

VDDCX_1_6

K19

VDDCX_1_7

K20

VDDCX_1_8

K24

VDDCX_1_9

K25

VDDCX_1_10

N10

VDDCX_1_11

N12

VDDCX_1_12

N14

VDDCX_1_13

N16

VDDCX_1_14

N18

VDDCX_1_15

N20

VDDCX_1_16

N22

VDDCX_1_17

N24

VDDCX_1_18

N26

VDDCX_1_19

R8

VDDCX_1_20

R10

VDDCX_1_21

R11

VDDCX_1_22

R12

VDDCX_1_23

R13

VDDCX_1_24

R14

VDDCX_1_25

R15

VDDCX_1_26

R16

VDDCX_1_27

R17

VDDCX_1_28

R18

VDDCX_1_29

R19

VDDCX_1_30

R20

VDDCX_1_31

R21

VDDCX_1_32

R22

VDDCX_1_33

R23

VDDCX_1_34

R24

VDDCX_1_35

R25

VDDCX_1_36

W8

VDDCX_1_37

W10

VDDCX_1_38

W12

VDDCX_1_39

W14

VDDCX_1_40

W16

VDDCX_1_41

W17

VDDCX_1_42

Y8

VDDCX_1_43

Y10

VDDCX_1_44

Y14

VDDCX_1_45

VDDPX_1_A

VDDPX_1_B

VDDPX_1_C

VDDPX_1_D

VDDPX_1_E

VDDPX_3_1

VDDPX_3_2

VDDPX_3_3

VDDPX_3_4

VDDPX_3_5

VDDPX_3_6

VDDPX_3_7

VDDPX_3_8

VDDPX_3_9

VDDPX_3_A

VDDPX_3_B

VDDPX_VBIAS_UIM

VDD_WCSS_CX_1

VDD_WCSS_CX_2

AC14

VDDPX_0

F11

DDR

F14

F19

F22

G26

SDC2

AC19

VDDPX_2

AA6

AC10

C0811

AC29

1.0UF;20%;6.3V;0201

21

C0812

C0813

C0814

1.0UF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

21

21

21

C0815

1.0UF;20%;6.3V;0201

21

21

C0816

1.0UF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

C0821

21

C0823

C0822

21

1.0UF;20%;6.3V;0201

21

1.0UF;20%;6.3V;0201

C0824

1.0UF;20%;6.3V;0201

21

1.0UF;20%;6.3V;0201

C0837

0.1uF;20%;6.3V;0201

C0825

21

UIM1

UIM2

eMMC

UFS

CXO

C0801

0.1uF;20%;6.3V;0201

WCSS CX

1.0UF;20%;6.3V;0201

G28 can float if UFS is not used

1.0UF;20%;6.3V;0201

C0820

1.0UF;20%;6.3V;0201

21

AD17

AD20

F29

L30

P6

W30

F12

F21

AC16

VDDPX_5

AC17

VDDPX_6

G29

VDDPX_7

G28

VDDPX_10

V30

VDDPX_11

AB16

J10

J11

MSM PX_3

21

C0817

C0836

0.1uF;20%;6.3V;0201

21

C0818

1.0UF;20%;6.3V;0201

C0802

4.7uF;20%;6.3V;0402

21

1.0UF;20%;6.3V;0201

C0819

VIO_OUT[16,17]

VREG_S8A[11,12,14,15]

VREG_L5A_2P96[15,45]

VREG_L9A_1P8[3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

VREG_L19A_1P8[15,45]

VREG_L20A_1P8[15,45]

VREG_L9A_1P8[3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

VREG_L8A_0P736[15]

VREG_L18A_1P232[9,15]

VREG_L10A_1P8[7,9,15,16]

VREF_MSM[7,16]

VREG_L9A_1P8[3,8,12,15,16,17,20,37,44,45,47,60,61,62,75,77]

21

C0838

1.0UF;20%;6.3V;0201

21

C0839

1.0UF;20%;6.3V;0201

C

B

A

Title

Title

Title

Page Name = 08_SM6125 PWR_2

Page Name = 08_SM6125 PWR_2

Page Name = 08_SM6125 PWR_2

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

6 47 58 3 2 1

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

8 53

8 53

8 53

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

6

5

4

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

C

B

A

SM6125 PWR_3

VREG_S5A [7,9,14,15]

1.0UF;20%;6.3V;0201

VREG_L4A_0P928 [9,15]

VREG_L18A_1P232 [8,9,15]

C0933

21

1.0UF;20%;6.3V;0201

VREG_S5A [7,9,14,15]

VREG_L10A_1P8 [7,8,9,15,16]

VREG_L16A_1P8 [15,77,79]

VREG_S5A [7,9,14,15]

VREG_L4A_0P928 [9,15]

C0901

21

C0905

1.0UF;20%;6.3V;0201

C0911

1.0UF;20%;6.3V;0201

21

1.0UF;20%;6.3V;0201

21

1.0UF;20%;6.3V;0201

C0912

1.0UF;20%;6.3V;0201

21

C0902

21

C0904

1.0UF;20%;6.3V;0201

21

C0906

1.0UF;20%;6.3V;0201

C0910

21

U0501I

MFG_NO

V23

VDDA_APC0_PLL

H10

VDDA_EBI0_A

H12

VDDA_EBI0_B

H14

VDDA_EBI0_C

H19

VDDA_EBI1_A

H21

VDDA_EBI1_B

H23

VDDA_EBI1_C

G16

VDDA_EBI_PLL

T8

VDDA_CSI0_1P2

U8

VDDA_CSI1_1P2

V8

VDDA_CSI2_1P2

K29

VDDA_DSI_PLL

H28

VDDA_DSI_1P2

J29

VDDA_DSI_0P9

L10

VDDA_AUDIO_PLL

T17

VDDA_CAMSS_PLL

L7

VDDA_WCSS_PLL

H16

VDDA_CC_EBI

G25

VDDA_QREFS_0P9_4

AD28

VDDA_QREFS_0P9_5

AD22

VDDA_QREFS_0P9_6

AB13

VDDA_QREFS_0P9_7

21

21

C0909

1.0UF;20%;6.3V;0201

C0913

1.0UF;20%;6.3V;0201

21

C0903

21

1.0UF;20%;6.3V;0201

C0907

1.0UF;20%;6.3V;0201

21

C0908

1.0UF;20%;6.3V;0201

21

21

C0914

C0915

1.0UF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

21

6 47 58 3 2 1

PWR3

VDDA_QLINK_LV_CK

VDDA_QLINK_LV

VDDA_UFS_CORE

VDDA_UFS_1P8

VDDIO_CK_EBI0

VDDIO_CK_EBI1

VDDA_USB_SS_DP_CORE

VDDA_USB_SS_DP_1P8

VDD_USB_HS_CORE

VDDA_USB_HS_1P8

VDDA_USB_HS_3P1

VDDA_PLL_HV_CC_EBI

VDDA_WCSS_ADCDAC_0

VDDA_WCSS_ADCDAC_1

VDDIO_EBI_A1

VDDIO_EBI_A2

VDDIO_EBI_B1

VDDIO_EBI_B2

VDDIO_EBI_C1

VDDIO_EBI_C2

VDDIO_EBI_D1

VDDIO_EBI_D2

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

21

21

C0932

C0931

C0930

1.0UF;20%;6.3V;0201

AC12

AB12

F17

G17

F13

F20

R28

P30

N28

N30

N29

F16

K8

J8

G10

G11

G14

G15

G18

G19

G22

G23

1.0UF;20%;6.3V;0201

C0916

1.0UF;20%;6.3V;0201

2.2uF;20%;6.3V;0201

eMMC compatible UFS soltion

21

21

C0924

1.0UF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

C0920

1.0UF;20%;6.3V;0201

21

21

C0921

C0923

1.0UF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

C0918

C0917

1.0UF;20%;6.3V;0201

21

21

21

1.0UF;20%;6.3V;0201

VREG_L4A_0P928[9,15]

C0929

2.2uF;20%;6.3V;0201

VREG_L10A_1P8[7,8,9,15,16]

VREG_L6A_0P6[4,9,11,12,15]

VREG_L7A_0P928[15]

21

21

C0925

C0927

C0926

1.0UF;20%;6.3V;0201

C0928

2.2uF;20%;6.3V;0201

VREG_L10A_1P8[7,8,9,15,16]

VREG_L15A_3P104[15]

VREG_L18A_1P232[8,9,15]

VREG_L17A_1P304[15,77]

VREG_L6A_0P6[4,9,11,12,15]

1.0UF;20%;6.3V;0201

C0922

21

1.0UF;20%;6.3V;0201

C0919

10uF;20%;6.3V;0402

Title

Title

Title

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Name = 09_SM6125 PWR_3

Page Name = 09_SM6125 PWR_3

Page Name = 09_SM6125 PWR_3

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

9 53

9 53

9 53

D

C

B

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

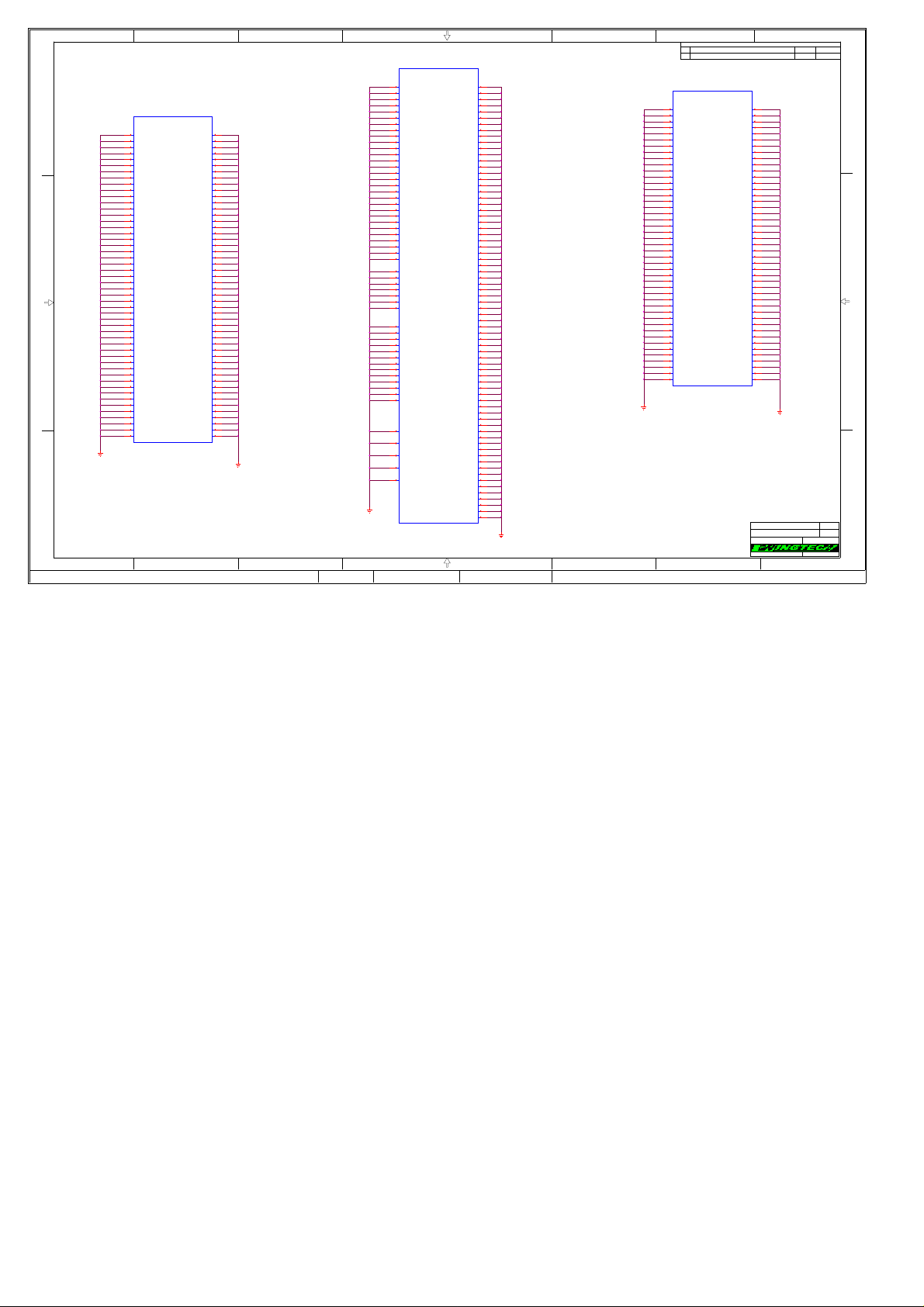

D

A5

VSSX_0_1

A14

VSSX_0_2

A15

VSSX_0_3

A17

VSSX_0_4

A18

VSSX_0_5

A27

VSSX_0_6

A29

VSSX_0_7

A32

VSSX_0_8

A34

VSSX_0_9

AA1

VSSX_0_10

AA2

VSSX_0_11

AA5

VSSX_0_12

AA7

VSSX_0_13

AA8

VSSX_0_14

AA21

VSSX_0_15

AA22

VSSX_0_16

AA24

VSSX_0_17

C

B

AA27

VSSX_0_18

AA29

VSSX_0_19

AA30

VSSX_0_20

AA31

VSSX_0_21

AA34

VSSX_0_22

AB5

VSSX_0_23

AB7

VSSX_0_24

AB9

VSSX_0_25

AB11

VSSX_0_26

AB14

VSSX_0_27

AB23

VSSX_0_28

AB24

VSSX_0_29

AB29

VSSX_0_30

AB33

VSSX_0_31

AC1

VSSX_0_32

AC2

VSSX_0_33

AC5

VSSX_0_34

AC6

VSSX_0_35

AC7

VSSX_0_36

AC8

VSSX_0_37

AC9

VSSX_0_38

AC11

VSSX_0_39

AC13

VSSX_0_40

AC21

VSSX_0_41

AC22

VSSX_0_42

AC23

VSSX_0_43

AC24

VSSX_0_44

AC27

VSSX_0_45

AC28

VSSX_0_46

AC34

VSSX_0_47

AD3

VSSX_0_48

AD4

VSSX_0_49

AD5

VSSX_0_50

7

U0501J

MFG_NO

GND1

VSSX_0_51

VSSX_0_52

VSSX_0_53

VSSX_0_54

VSSX_0_55

VSSX_0_56

VSSX_0_57

VSSX_0_58

VSSX_0_59

VSSX_0_60

VSSX_0_61

VSSX_0_62

VSSX_0_63

VSSX_0_64

VSSX_0_65

VSSX_0_66

VSSX_0_67

VSSX_0_68

VSSX_0_69

VSSX_0_70

VSSX_0_71

VSSX_0_72

VSSX_0_73

VSSX_0_74

VSSX_0_75

VSSX_0_76

VSSX_0_77

VSSX_0_78

VSSX_0_79

VSSX_0_80

VSSX_0_81

VSSX_0_82

VSSX_0_83

VSSX_0_84

VSSX_0_85

VSSX_0_86

VSSX_0_87

VSSX_0_88

VSSX_0_89

VSSX_0_90

VSSX_0_91

VSSX_0_92

VSSX_0_93

VSSX_0_94

VSSX_0_95

VSSX_0_96

VSSX_0_97

VSSX_0_98

VSSX_0_99

VSSX_0_100

AD9

AD11

AD13

AD16

AD19

AD23

AD24

AD27

AD29

AD31

AE1

AE2

AE3

AE5

AE10

AE11

AE12

AE14

AE24

AE25

AE26

AE27

AE28

AE30

AE34

AF4

AF8

AF10

AF14

AF15

AF17

AF20

AF23

AF26

AF31

AG10

AG14

AH10

AH12

AH14

AJ1

AJ4

AJ7

AJ10

AJ12

AJ14

AJ17

AJ20

AJ23

AJ26

A

SM6125 GND

VSSX_0_130

VSSX_0_131

VSSX_0_132

VSSX_0_133

VSSX_0_134

VSSX_0_135

VSSX_0_136

VSSX_0_137

VSSX_0_138

VSSX_0_139

VSSX_0_140

VSSX_0_141

VSSX_0_142

VSSX_0_143

VSSX_0_144

VSSX_0_145

VSSX_0_146

VSSX_0_147

VSSX_0_148

VSSX_0_149

VSSX_0_150

VSSX_0_151

VSSX_0_152

VSSX_0_153

VSSX_0_154

VSSX_0_155

VSSX_0_156

VSSX_0_157

VSSX_0_158

VSSX_0_159

VSSX_0_160

VSSX_0_161

VSSX_0_162

VSSX_0_163

VSSX_0_164

VSSX_0_165

VSSX_0_166

VSSX_0_167

VSSX_0_168

VSSX_0_169

VSSX_0_170

VSSX_0_171

VSSX_0_172

VSSX_0_173

VSSX_0_174

VSSX_0_175

VSSX_0_176

VSSX_0_177

VSSX_0_178

VSSX_0_179

VSSX_0_180

VSSX_0_181

VSSX_0_182

VSSX_0_183

VSSX_0_184

VSSX_0_185

VSSX_0_186

VSSX_0_187

VSSX_0_188

VSSX_0_189

VSSX_0_190

VSSX_0_191

VSSX_0_192

VSSX_0_193

VSSX_0_194

VSSX_0_195

VSSX_0_196

VSSX_0_197

VSSX_0_198

VSSX_0_199

VSSX_0_200

LAST EDIT DATE

4

C24

C25

C26

C27

C28

C29

D1

D2

D15

D18

D29

D30

E2

E15

E18

E29

E30

E33

E34

F2

F3

F6

F7

F8

F9

F10

F23

F24

F25

F26

F27

F28

F31

F32

G7

G12

H2

H8

H30

H33

H34

J2

J13

J14

J15

J16

J18

J19

J20

J21

J22

J24

J25

J30

K3

K10

K11

K21

K22

K31

K32

K33

L6

L29

M4

M6

M12

M14

M16

M18

M20

3

A INITIAL RELEASE

M22

VSSX_0_201

M24

VSSX_0_202

M26

VSSX_0_203

M29

VSSX_0_204

M30

VSSX_0_205

M32

VSSX_0_206

M34

VSSX_0_207

N6

VSSX_0_208

N7

VSSX_0_209

N31

VSSX_0_210

N32

VSSX_0_211

P1

VSSX_0_212

P2

VSSX_0_213

P3

VSSX_0_214

P7

VSSX_0_215

P11

VSSX_0_216

P12

VSSX_0_217

P13

VSSX_0_218

P14

VSSX_0_219

P15

VSSX_0_220

P17

VSSX_0_221

P18

VSSX_0_222

P19

VSSX_0_223

P20

VSSX_0_224

P21

VSSX_0_225

P23

VSSX_0_226

P24

VSSX_0_227

P25

VSSX_0_228

P31

VSSX_0_229

R5

VSSX_0_230

R6

VSSX_0_231

R7

VSSX_0_232

R29

VSSX_0_233

R30

VSSX_0_234

R33

VSSX_0_235

T1

VSSX_0_236

T2

VSSX_0_237

T7

VSSX_0_238

T10

VSSX_0_239

T11

VSSX_0_240

T12

VSSX_0_241

T13

VSSX_0_242

T14

VSSX_0_243

T15

VSSX_0_244

T18

VSSX_0_245

28

MFG_NO

GND2

REVISIONS

DESCRIPTIONLTR

U0501L

T20

VSSX_0_246

T21

VSSX_0_247

T22

VSSX_0_248

T23

VSSX_0_249

T25

VSSX_0_250

T26

VSSX_0_251

T29

VSSX_0_252

T33

VSSX_0_253

U5

VSSX_0_254

U6

VSSX_0_255

U7

VSSX_0_256

U10

VSSX_0_257

U21

VSSX_0_258

U25

VSSX_0_259

U30

VSSX_0_260

U31

VSSX_0_261

U32

VSSX_0_262

V7

VSSX_0_263

V12

VSSX_0_264

V14

VSSX_0_265

V16

VSSX_0_266

V19

VSSX_0_267

V20

VSSX_0_268

V21

VSSX_0_269

V24

VSSX_0_270

V28

VSSX_0_271

W1

VSSX_0_272

W2

VSSX_0_273

W5

VSSX_0_274

W6

VSSX_0_275

W7

VSSX_0_276

W24

VSSX_0_277

W26

VSSX_0_278

W31

VSSX_0_279

W32

VSSX_0_280

Y7

VSSX_0_281

Y11

VSSX_0_282

Y15

VSSX_0_283

Y16

VSSX_0_284

Y17

VSSX_0_285

Y19

VSSX_0_286

Y28

VSSX_0_287

Y32

VSSX_0_288

Y33

VSSX_0_289

Y34

VSSX_0_290

Title

Title

Title

Page Name = 10_SM6125 GND

Page Name = 10_SM6125 GND

Page Name = 10_SM6125 GND

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

6

6 47 58 3 2 1

5

U0501K

MFG_NO

GND2

AJ29

VSSX_0_101

AJ32

VSSX_0_102

AJ34

VSSX_0_103

B5

VSSX_0_104

B15

VSSX_0_105

B17

VSSX_0_106

B27

VSSX_0_107

B28

VSSX_0_108

B31

VSSX_0_109

B32

VSSX_0_110

C5

VSSX_0_111

C6

VSSX_0_112

C7

VSSX_0_113

C8

VSSX_0_114

C9

VSSX_0_115

C10

VSSX_0_116

C11

VSSX_0_117

C12

VSSX_0_118

C13

VSSX_0_119

C14

VSSX_0_120

C15

VSSX_0_121

C16

VSSX_0_122

C17

VSSX_0_123

C18

VSSX_0_124

C19

VSSX_0_125

C20

VSSX_0_126

C21

VSSX_0_127

C22

VSSX_0_128

C23

VSSX_0_129

G3

VSSA_WCSS_ADCDAC_0_1

G4

VSSA_WCSS_ADCDAC_0_2

H5

VSSA_WCSS_ADCDAC_0_3

J5

VSSA_WCSS_ADCDAC_0_4

K4

VSSA_WCSS_ADCDAC_0_5

K5

VSSA_WCSS_ADCDAC_0_6

K7

VSSA_WCSS_ADCDAC_0_7

A1

VSSA_WCSS_ADCDAC_1_1

A3

VSSA_WCSS_ADCDAC_1_2

B3

VSSA_WCSS_ADCDAC_1_3

B4

VSSA_WCSS_ADCDAC_1_4

C2

VSSA_WCSS_ADCDAC_1_5

C3

VSSA_WCSS_ADCDAC_1_6

C4

VSSA_WCSS_ADCDAC_1_7

E3

VSSA_WCSS_ADCDAC_1_8

E4

VSSA_WCSS_ADCDAC_1_9

F4

VSSA_WCSS_ADCDAC_1_10

F5

VSSA_WCSS_ADCDAC_1_11

H6

VSSA_WCSS_ADCDAC_1_12

H7

VSSA_WCSS_ADCDAC_1_13

J7

VSSGR_WCSS_ADC_1

V22

VSSA_APC0_PLL

M7

VSSA_WCSS_PLL

M8

VSSA_AUDIO_PLL

T16

VSSA_CAMSS_PLL

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

1

DATE

DESIGNER:

DESIGNER:

DESIGNER:

Sheet of

Sheet of

Sheet of

APPROVED

REV:

REV:

REV:

Size

Size

Size

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

DESIGNER = zhanglieqiang

10 53

10 53

10 53

D

C

B

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

D

C

Pls near to the memory

EMMC_UFS_THERM [16]

12

NTC1101

B

100K;1%;0201

VREG_L6A_0P6 [4,9,12,15]

6

DDR_RESET_N[4]

240;1%;0201

R1103

R1101 240;1%;0201

EBI0_CA_CS_0[4]

EBI0_CA_CS_1[4]

EBI0_CA_CK_T[4]

EBI0_CA_CK_C[4]

EBI0_CA_CKE_0[4]

EBI0_CA_CKE_1[4]

VREG_S8A[8,11,12,14,15]

EBI0_DQS_T_0[4]

EBI0_DQS_T_1[4]

EBI0_DQS_C_0[4]

EBI0_DQS_C_1[4]

EBI0_CA_CA_0[4]

EBI0_CA_CA_1[4]

EBI0_CA_CA_2[4]

EBI0_CA_CA_3[4]

EBI0_CA_CA_4[4]

EBI0_CA_CA_5[4]

EBI0_DMI_0[4]

EBI0_DMI_1[4]

5

U1101A

MFG_NO

LPDDR4_A

AA16

RST_N_2

B16

ZQ0

C16

ZQ1

E15

CS0_A

F15

CS1_A

H14

NC_7

H16

CLK_T_A

G16

CLK_C_A

E16

CKE0_A

F16

CKE1_A

J14

NC_8

J13

NC_11

C9

DQS0_T_A

K9

DQS1_T_A

D9

DQS0_C_A

J9

DQS1_C_A

G14

CA0_A

F13

CA1_A

C13

CA2_A

D13

CA3_A

E13

CA4_A

C15

CA5_A

D5

DMI0_A

H3

DMI1_A

4

eMCP and UFS compatible design

EBI1_CA_CS_0[4]

A3

DQ0_A

B3

DQ1_A

C3

DQ2_A

D3

DQ3_A

B7

DQ4_A

C6

DQ5_A

D7

DQ6_A

C8

DQ7_A

K5

DQ8_A

K6

DQ9_A

K3

DQ10_A

J3

DQ11_A

J7

DQ12_A

G3

DQ13_A

H6

DQ14_A

H8

DQ15_A

R1105 0;0.5A;0201

UFS_REF_CLK[2]

UFS_RESET[2]

UFS_RX_P[2]

UFS_TX_M[2]

UFS_RX_M[2]

UFS_TX_P[2]

EBI0_DQ_0 [4]

EBI0_DQ_1 [4]

EBI0_DQ_2 [4]

EBI0_DQ_3 [4]

EBI0_DQ_4 [4]

EBI0_DQ_5 [4]

EBI0_DQ_6 [4]

EBI0_DQ_7 [4]

EBI0_DQ_8 [4]

EBI0_DQ_9 [4]

EBI0_DQ_10 [4]

EBI0_DQ_11 [4]

EBI0_DQ_12 [4]

EBI0_DQ_13 [4]

EBI0_DQ_14 [4]

EBI0_DQ_15 [4]

EBI1_CA_CS_1[4]

EBI1_CA_CK_T[4]

EBI1_CA_CK_C[4]

EBI1_CA_CKE_0[4]

EBI1_CA_CKE_1[4]

VREG_S8A[8,11,12,14,15]

EBI1_DQS_T_0[4]

EBI1_DQS_T_1[4]

EBI1_DQS_C_0[4]

EBI1_DQS_C_1[4]

EBI1_CA_CA_0[4]

EBI1_CA_CA_1[4]

EBI1_CA_CA_2[4]

EBI1_CA_CA_3[4]

EBI1_CA_CA_4[4]

EBI1_CA_CA_5[4]

EBI1_DMI_0[4]

EBI1_DMI_1[4]

R1102

0;0.5A;0201

3

Y15

W15

U14

U16

V16

Y16

W16

T14

T13

AB9

R9

AA9

T9

V14

W13

AB13

AA13

Y13

AB15

AA5

U3

U1101C

MFG_NO

EMMC

N9

RST_N_1

M9

CMD

P12

CLKM

M12

DS

P16

DAT0

M15

DAT1

N13

DAT2

P15

DAT3

M16

DAT4

N14

DAT5

L14

DAT6

L13

DAT7

CS0_B

CS1_B

NC_9

CLK_T_B

CLK_C_B

CKE0_B

CKE1_B

NC_10

NC_12

DQS0_T_B

DQS1_T_B

DQS0_C_B

DQS1_C_B

CA0_B

CA1_B

CA2_B

CA3_B

CA4_B

CA5_B

DMI0_B

DMI1_B

28

A INITIAL RELEASE

U1101B

MFG_NO

LPDDR4_B

DESCRIPTIONLTR

AD3

DQ0_B

AC3

DQ1_B

AB3

DQ2_B

AA3

DQ3_B

AC7

DQ4_B

AB6

DQ5_B

AA7

DQ6_B

AB8

DQ7_B

R5

DQ8_B

R6

DQ9_B

R3

DQ10_B

T3

DQ11_B

T7

DQ12_B

V3

DQ13_B

U6

DQ14_B

U8

DQ15_B

REVISIONS

1

DATE

EBI1_DQ_0 [4]

EBI1_DQ_1 [4]

EBI1_DQ_2 [4]

EBI1_DQ_3 [4]

EBI1_DQ_4 [4]

EBI1_DQ_5 [4]

EBI1_DQ_6 [4]

EBI1_DQ_7 [4]

EBI1_DQ_8 [4]

EBI1_DQ_9 [4]

EBI1_DQ_10 [4]

EBI1_DQ_11 [4]

EBI1_DQ_12 [4]

EBI1_DQ_13 [4]

EBI1_DQ_14 [4]

EBI1_DQ_15 [4]

APPROVED

D

C

B

A

Title

Title

Title

Page Name = 11_eMCP_uMCP

Page Name = 11_eMCP_uMCP

Page Name = 11_eMCP_uMCP

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

6 47 58 3 2 1

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

11 53

11 53

11 53

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

D

VREG_L11A_1P8 [15]

C1240

4.7uF;20%;6.3V;0402

VREG_L24A_2P96 [15]

C1201

2.2uF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

21

C1242

C1202

0.1uF;20%;6.3V;0201

2.2uF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

21

21

C1208

C1207

C1205

1.0UF;20%;6.3V;0201

0.1uF;20%;6.3V;0201

C

VREG_L6A_0P6 [4,9,11,12,15]

C1214

C1229

2.2uF;20%;6.3V;0201

2.2uF;20%;6.3V;0201

10uF;20%;6.3V;0402

B

C1213

C1203

1.0UF;20%;6.3V;0201

21

C1204

0.1uF;20%;6.3V;0201

C1206

0.1uF;20%;6.3V;0201

C1212

21

1.0UF;20%;6.3V;0201

C1211

21

C1241

1.0UF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

C1235

2 1

1.0UF;20%;6.3V;0201

21

C1209

1.0UF;20%;6.3V;0201

C1226

10uF;20%;6.3V;0402

10uF;20%;6.3V;0402

R1201

NF_240;1%;0201

21

C1237

4

21

C1218

21

1.0UF;20%;6.3V;0201

C1217

JP1201

RTM_VREG_S8A_P[14]

L9

1 2

TOP;BOT

C1228

C1233

C1227

M3

N3

M4

N4

M5

N5

M6

N6

M7

D16

K17

N7

T17

AB16

AC16

NF_10uF;20%;6.3V;0402

VSF1

VSF2

VSF3

VSF4

VSF5

VSF6

VSF7

VSF8

VSF9

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

1 2

JP1202

L9

TOP;BOT

C1232

4.7uF;20%;6.3V;0402

U1101E

MFG_NO

NC_DNU

4.7uF;20%;6.3V;0402

1.0UF;20%;6.3V;0201

21

C1219

1.0UF;20%;6.3V;0201

RTM_VREG_S8A_M[14]

A1

DNU_1

A2

DNU_2

A17

DNU_3

A18

DNU_4

B1

DNU_5

B18

DNU_6

AC1

DNU_7

AC18

DNU_8

AD1

DNU_9

AD2

DNU_10

AD17

DNU_11

AD18

DNU_12

3

VREG_L9A_1P8[3,8,15,16,17,20,37,44,45,47,60,61,62,75,77]

VREG_S8A[8,11,14,15]

21

C1221

21

C1223

1.0UF;20%;6.3V;0201

21

21

C1222

C1224

1.0UF;20%;6.3V;0201

1.0UF;20%;6.3V;0201

28

A INITIAL RELEASE

K13

VSSM_1

K14

VSSM_2

K16

VSSM_3

L12

VSSM_4

L15

VSSM_5

L16

VSSM_6

M8

VSSM_7

M13

VSSM_8

M14

VSSM_9

N8

VSSM_10

N12

VSSM_11

N15

VSSM_12

N16

VSSM_13

P13

VSSM_14

P14

VSSM_15

R15

VSSM_16

R16

VSSM_17

R17

VSSM_18

U13

VSS_46

U15

VSS_47

V13

VSS_48

V15

VSS_49

W14

VSS_50

Y14

VSS_51

AA14

VSS_52

AA15

VSS_53

AB14

VSS_54

B4

VSS_1

B6

VSS_2

B8

VSS_3

C4

VSS_4

C5

VSS_5

C7

VSS_6

C14

VSS_7

D4

VSS_8

DESCRIPTIONLTR

U1101F

MFG_NO

GND

REVISIONS

1

APPROVED

DATE

D

D6

VSS_9

D8

VSS_10

D14

VSS_11

D15

VSS_12

E14

VSS_13

F14

VSS_14

G4

VSS_15

G5

VSS_16

G6

VSS_17

G13

VSS_18

G15

VSS_19

H4

VSS_20

H7

VSS_21

H13

VSS_22

H15

VSS_23

J6

VSS_24

K4

VSS_25

K7

VSS_26

K8

VSS_27

R4

VSS_28

R7

VSS_29

R8

VSS_30

T6

VSS_31

U4

VSS_32

U7

VSS_33

V4

VSS_34

V5

VSS_35

V6

VSS_36

AA4

VSS_37

AA6

VSS_38

AA8

VSS_39

AB4

VSS_40

AB5

VSS_41

AB7

VSS_42

AC4

VSS_43

AC6

VSS_44

AC8

VSS_45

C

B

6

L17

VDDI

M17

VCC_1

N17

VCC_2

P17

VCC_3

J15

VCCQ_1

J16

VCCQ_2

J17

VCCQ_3

K15

VCCQ_4

R13

VCCQ_5

R14

VCCQ_6

T15

VCCQ_7

T16

VCCQ_8

A6

VDDQ_1

A7

VDDQ_2

A13

VDDQ_3

A14

VDDQ_4

B5

VDDQ_5

H5

VDDQ_6

H9

VDDQ_7

J4

VDDQ_8

J5

VDDQ_9

J8

VDDQ_10

T4

VDDQ_11

T5

VDDQ_12

T8

VDDQ_13

U5

VDDQ_14

U9

VDDQ_15

AC5

VDDQ_16

AD6

VDDQ_17

AD7

VDDQ_18

AD13

VDDQ_19

AD14

VDDQ_20

5

U1101D

MFG_NO

PWR

A4

VDD1_1

A9

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD2_1

VDD2_2

VDD2_3

VDD2_4

VDD2_5

VDD2_6

VDD2_7

VDD2_8

VDD2_9

VDD2_10

VDD2_11

VDD2_12

VDD2_13

VDD2_14

VDD2_15

VDD2_16

VDD2_17

VDD2_18

VDD2_19

VDD2_20

VDD2_21

VDD2_22

VDD2_23

VDD2_24

A15

A16

B15

AC15

AD4

AD9

AD15

AD16

A5

A8

B9

B13

B14

G7

G8

G9

K2

L7

L8

L9

P7

P8

P9

R2

V7

V8

V9

AC9

AC13

AC14

AD5

AD8

C1215

2.2uF;20%;6.3V;0201

10uF;20%;6.3V;0402

VREG_L6A_0P6 [4,9,11,12,15]

1.0UF;20%;6.3V;0201

C1216

2.2uF;20%;6.3V;0201

21

C1236

C1225

1.0UF;20%;6.3V;0201

A

eMCP_POWER

Title

Title

Title

Page Name = 12_EMCP_POWER

Page Name = 12_EMCP_POWER

Page Name = 12_EMCP_POWER

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

6 47 58 3 2 1

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

12 53

12 53

12 53

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR

ITS CONTENTS REVEALED IN ANY MANNER TO OTHERS WITHOUT THE EXPRESS WRITTEN

PERMISSION OF QUALCOMM TECHNOLOGIES, INC.

THIS TECHNICAL DATA MAY BE SUBJECT TO U.S. AND INTERNATIONAL EXPORT,

RE-EXPORT, OR TRANSFER ("EXPORT") LAWS. DIVERSION CONTRARY TO U.S. AND

INTERNATIONAL LAW IS STRICTLY PROHIBITED.

7

6

5

4

3

28

A INITIAL RELEASE

DESCRIPTIONLTR

REVISIONS

1

APPROVED

DATE

D

Shares input cap with VDD_S5

VPH_PWR [13,14,15,16,18,19,20,21,37,40,42,43,44,62,67,75]

C1321

C1322

10uF;20%;6.3V;0402

10uF;20%;6.3V;0402

1.0UF;20%;6.3V;0201

VPH_PWR [13,14,15,16,18,19,20,21,37,40,42,43,44,62,67,75]

1.0UF;20%;6.3V;0201

C

VPH_PWR [13,14,15,16,18,19,20,21,37,40,42,43,44,62,67,75]

B

Place Cin as close to PMIC as possible to achieve this requirement.

Loop inductance from (VIN_Sx to Cin + Cin to GND_Sx) must be < 3nH

A

PM6125_Bucks_S1-S4

21

C1301

4/L8

2

JP1301

21

C1302

4/L8

2

JP1302

C1303

10uF;20%;6.3V;0402

4/L8

2

JP1304

U1301D

MFG_NO

VREG1

48

VDD_S1

71

GND_S1_1

72

GND_S1_2

108

VDD_S2

83

GND_S2_1

84

GND_S2_2

120

VDD_S3

131

GND_S3_1

143

GND_S3_2

4/L8

2

JP1303

139

VDD_S4

129

GND_S4_1

141

GND_S4_2

RMT_GND_S1

RMT_GND_S2

RMT_GND_S3

RMT_GND_S4

58

VREG_S1

VSW_S1_1

VSW_S1_2

VREG_S2

VSW_S2_1

VSW_S2_2

VREG_S3

VSW_S3_1

VSW_S3_2

VSW_S3_3

VREG_S4

VSW_S4_1

VSW_S4_2

L1304

VSW_S1

59

0.47UH;20%;2016

60

46

70

L1303

VSW_S2

95

0.47UH;20%;2016

96

82

142

L1302

VSW_S3

119

0.47UH;20%;2016

132

144

130

118

L1301

VSW_S4

128

0.47UH;20%;2016

140

117

RMT_VREG_S1A_S2A_P [7]

VREG_S1A_S2A[7]

RMT_VREG_S1A_S2A_M [7]

Dual-phased buck

RTM_VREG_S3A_S4A_P [8]

RTM_VREG_S3A_S4A_M [8]

Dual-phased buck

VREG_S3A_S4A[8]

Diff Pair back to PMIC

from load cap

Diff Pair back to PMIC

from load cap

VREG_S1A is REMOTE diff sense,

VREG_Sx & RMT_GND_Sx should be routed as a differential pair

Do not route VREG_Sx & RMT_GND_Sx near VIN_Sx

Do not route VREG_Sx & RMT_GND_Sx near VSW_Sx unless separated by ground shield

VREG_S2A is REMOTE diff sense,

VREG_Sx & RMT_GND_Sx should be routed as a differential pair

Do not route VREG_Sx & RMT_GND_Sx near VIN_Sx

Do not route VREG_Sx & RMT_GND_Sx near VSW_Sx unless separated by ground shield

VREG_S3A is REMOTE diff sense,

VREG_Sx & RMT_GND_Sx should be routed as a differential pair

Do not route VREG_Sx & RMT_GND_Sx near VIN_Sx

Do not route VREG_Sx & RMT_GND_Sx near VSW_Sx unless separated by ground shield

VREG_S4A is REMOTE diff sense,

VREG_Sx & RMT_GND_Sx should be routed as a differential pair

Do not route VREG_Sx & RMT_GND_Sx near VIN_Sx

Do not route VREG_Sx & RMT_GND_Sx near VSW_Sx unless separated by ground shield

D

C

B

Nicobar Power Grid v1.31 10/31/2018

S1A-2A: FTS510 0.8V default 8000mA Ipeak 8110.00mA APC

S3A-4A: FTS510 0.8V default 8000mA Ipeak 8480mA CX, MODEM

S5A: HFS510 0.912V default 4000mA Ipeak 3620.00mA EBI, MX, nLDO

S6A: HFS510 1.352V default 4000mA Ipeak 1560mA LDO

S7A: HFS510 2.04V default 2500mA Ipeak 2350mA LDO

S8A: FTS510 1.128V default 4000mA Ipeak 1790mA LDO, LPDDR4x

Title

Title

Title

Page Name = 13_PM6125_Bucks_S1-S4

Page Name = 13_PM6125_Bucks_S1-S4

Page Name = 13_PM6125_Bucks_S1-S4

DOCUMENT NO.:

DOCUMENT NO.:

DOCUMENT NO.:

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

Design Name = S88512AA1_1_21_20190515_1605

DEPARTMENT:

DEPARTMENT:

DEPARTMENT:

Date:

Date:

Date:

Page Modify Date = Wednesday, May 15, 2019

Page Modify Date = Wednesday, May 15, 2019

6 47 58 3 2 1

EDITED BYVERSION

LAST_EDITOR1 2-23-2007_10:06

LAST EDIT DATE

Page Modify Date = Wednesday, May 15, 2019

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

DESIGNER:

DESIGNER = zhanglieqiang

Sheet of

Sheet of

Sheet of

REV:

REV:

REV:

Size

Size

Size

13 53

13 53

13 53

A

V10

V10

V10

Custom

Custom

Custom

CONFIDENTIAL AND PROPRIETARY - QUALCOMM TECHNOLOGIES, INC.

NOT TO BE USED, COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART, NOR