Page 1

Pixie-16

User Manual

Version 3.00

August 21, 2018

Hardware Revisions: B, C, D, F

XIA LLC

31057 Genstar Rd

Hayward, CA 94544 USA

Email: support@xia.com

Tel: (510) 401-5760; Fax: (510) 401-5761

http://www.xia.com/

Information furnished by XIA LLC is believed to be accurate and reliable. However, no responsibility is assumed by

XIA LLC for its use, or for any infringements of patents or other rights of third parties which may result from its use.

No license is granted by implication or otherwise under any patent or patent rights of XIA LLC. XIA LLC reserves

the right to change hardware or software specifications at any time without notice.

Page 2

Pixie-16 User Manual August 21, 2018

Table of Contents

Safety ............................................................................................................................................................ 5

Specific Precautions .................................................................................................................................. 5

Power Source ........................................................................................................................................ 5

User Adjustments/Disassembly ............................................................................................................ 5

Detector and Preamplifier Damage ....................................................................................................... 5

Servicing and Cleaning ......................................................................................................................... 5

Warranty Statement ...................................................................................................................................... 6

Contact Information: ................................................................................................................................. 6

Manual Conventions ..................................................................................................................................... 7

1 Introduction ........................................................................................................................................... 8

1.1 Pixie-16 Features .......................................................................................................................... 9

1.2 Specifications .............................................................................................................................. 10

1.3 System Requirements .................................................................................................................. 11

1.3.1 Pixie-16 Crate ..................................................................................................................... 11

1.3.2 Host Computer .................................................................................................................... 11

1.3.3 Drivers and Software .......................................................................................................... 12

1.3.4 Detector Signals .................................................................................................................. 12

1.3.5 Power Requirements ........................................................................................................... 12

1.3.6 Connectors and Cabling ...................................................................................................... 12

1.4 Software and Firmware Overview .............................................................................................. 12

1.5 Front Panel .................................................................................................................................. 12

1.5.1 16 Analog Signal Input Connectors (all Pixie-16 revisions)............................................... 13

1.5.2 LVDS I/O Port (all Pixie-16 revisions) ............................................................................... 13

1.5.3 Digital I/O Connectors (A, B, C, D, E in red color font) (Rev. F Modules only) ............... 14

1.5.4 Front Panel LEDs (all Pixie-16 revisions) .......................................................................... 16

1.5.5 3.3V I/O Connector (Rev. D Modules only) ....................................................................... 17

1.5.6 GATE Inputs (Rev. D Modules only) ................................................................................. 17

1.5.7 3.3V I/O Connector (Rev. B and C Modules only) ............................................................. 18

1.5.8 Digital Input/output Signals Supported by Standard Firmware (all Pixie-16 revisions) .... 19

1.6 Front End Attenuation and Termination ..................................................................................... 21

1.6.1 Rev. F Modules ................................................................................................................... 21

1.6.2 Rev. B, C, D Modules ......................................................................................................... 22

1.7 Operating Multiple Pixie-16 Modules Synchronously ............................................................... 22

1.7.1 Clock Distribution ............................................................................................................... 22

1.7.1.1 Individual Clock Mode ............................................................................................... 23

1.7.1.2 PXI Clock Mode ......................................................................................................... 23

1.7.1.3 Daisy-chained Clock Mode ......................................................................................... 24

1.7.1.4 Multi-Crate Clock Mode ............................................................................................. 24

1.7.2 Trigger Distribution and Run Synchronization ................................................................... 28

2 Installation .......................................................................................................................................... 30

2.1 Hardware Setup ........................................................................................................................... 30

2.2 Software Installation in Windows ............................................................................................... 32

2.3 Software Installation in Linux..................................................................................................... 33

2.4 Getting Started ............................................................................................................................ 34

2.4.1 Startup ................................................................................................................................. 34

2.4.2 Settings ................................................................................................................................ 35

Version 3.00 www.xia.com 2

Page 3

Pixie-16 User Manual August 21, 2018

2.4.3 Run ...................................................................................................................................... 35

2.4.4 Results ................................................................................................................................. 36

3 Navigating the Pixie-16 User Interface ............................................................................................... 37

3.1 Overview ..................................................................................................................................... 37

3.2 Startup ......................................................................................................................................... 37

3.3 Settings ........................................................................................................................................ 38

3.3.1 Filter .................................................................................................................................... 39

3.3.2 Analog Signal Conditioning & Acquire ADC Traces ......................................................... 39

3.3.3 Histogram Control............................................................................................................... 40

3.3.4 Decay Time ......................................................................................................................... 40

3.3.5 Pulse Shape Analysis .......................................................................................................... 40

3.3.6 Baseline Control & Acquire Baselines ............................................................................... 41

3.3.7 Control Registers................................................................................................................. 41

3.3.8 CFD Trigger ........................................................................................................................ 45

3.3.8.1 100 MHz and 250 MHz Pixie-16 modules ................................................................. 45

3.3.8.2 500 MHz Pixie-16 modules ........................................................................................ 47

3.3.9 Trigger Stretch Lengths ...................................................................................................... 48

3.3.10 FIFO Delays ........................................................................................................................ 49

3.3.11 Multiplicity ......................................................................................................................... 51

3.3.11.1 Illustrations of Multiplicity, Coincidence and Group Triggers ................................... 51

3.3.11.2 Parameters for Configuring Multiplicity, Coincidence and Group Triggers .............. 55

3.3.11.3 Local Fast Trigger Gated by External Fast Trigger .................................................... 58

3.3.11.4 Channel Validation Triggers ....................................................................................... 58

3.3.11.5 Module Validation Trigger ......................................................................................... 61

3.3.11.6 Module Fast Trigger .................................................................................................... 63

3.3.12 QDC .................................................................................................................................... 65

3.4 Run .............................................................................................................................................. 65

3.5 Results ......................................................................................................................................... 66

4 Data Acquisition and Data Structures ................................................................................................. 70

4.1 Run Types ................................................................................................................................... 70

4.1.1 MCA Runs .......................................................................................................................... 70

4.1.2 List Mode Runs ................................................................................................................... 70

4.1.3 Summary of Run Types ...................................................................................................... 70

4.2 Output Data Structures ................................................................................................................ 71

4.2.1 MCA Histogram Data Structure ......................................................................................... 71

4.2.2 List Mode Data Structures .................................................................................................. 71

4.2.3 List Mode Data Values ....................................................................................................... 74

4.2.3.1 List Mode Time Stamps .............................................................................................. 74

4.2.3.2 List Mode Energy ........................................................................................................ 75

4.2.3.3 List Mode Trace Length .............................................................................................. 76

4.2.3.4 List Mode Event Length ............................................................................................. 76

4.2.3.5 List Mode Energy Sums .............................................................................................. 76

4.2.3.6 List Mode Baseline ..................................................................................................... 76

4.2.3.7 List Mode QDC Sums ................................................................................................. 76

4.2.3.8 List Mode External Clock Timestamps ....................................................................... 77

4.2.4 Settings Files (Run Statistics Included) .............................................................................. 77

4.2.4.1 File Format .................................................................................................................. 77

4.2.4.2 File Content ................................................................................................................. 77

5 Hardware Description ......................................................................................................................... 78

Version 3.00 www.xia.com 3

Page 4

Pixie-16 User Manual August 21, 2018

5.1 Analog Signal Conditioning........................................................................................................ 78

5.2 Pulse Processing .......................................................................................................................... 79

5.3 Digital Signal Processor (DSP) and Event Building ................................................................... 79

5.4 PCI and Trigger Interface ........................................................................................................... 80

6 Theory of Operation ............................................................................................................................ 81

6.1 Digital Filters for Radiation Detectors ........................................................................................ 81

6.2 Trapezoidal Filtering in a Pixie-16 Module ................................................................................ 83

6.3 Baselines and Preamplifier Decay Times ................................................................................... 84

6.4 Thresholds and Pileup Inspection ............................................................................................... 85

6.5 Filter Range ................................................................................................................................. 87

6.6 Run Statistics .............................................................................................................................. 88

6.6.1 Time and trigger counters ................................................................................................... 88

6.6.2 Count Rates ......................................................................................................................... 89

Version 3.00 www.xia.com 4

Page 5

Pixie-16 User Manual August 21, 2018

Safety

Please take a moment to review these safety precautions. They are provided both for your

protection and to prevent damage to the Pixie-16 module and connected equipment. This

safety information applies to all operators and service personnel.

Specific Precautions

Observe all of these precautions to ensure your personal safety and to prevent damage to

either the Pixie-16 module or equipment connected to it.

Power Source

The Pixie-16 module is powered through a custom made PXI/Compact PCI 6U crate.

Please refer to the crate manual for the correct AC voltage connections. The crate must be

powered down to insert and remove the module. The Pixie-16 module is not hot

swappable!

User Adjustments/Disassembly

To avoid personal injury, and/or damage, always turn off power before accessing the Pixie16 module’s on-board jumpers.

Detector and Preamplifier Damage

Because the Pixie-16 module does not provide power for the detector or preamplifier there

is little risk of damage to either resulting from the Pixie-16 module itself. Nonetheless,

please review all instructions and safety precautions provided with these components

before powering a connected system.

Servicing and Cleaning

To avoid personal injury, and/or damage to the Pixie-16 module or connected equipment,

do not attempt to repair or clean these units. These modules are warranted against all

defects for one (1) year. Please contact the factory or your distributor before returning items

for service.

Version 3.00 www.xia.com 5

Page 6

Pixie-16 User Manual August 21, 2018

Warranty Statement

XIA LLC warrants that this product will be free from defects in materials and workmanship

for a period of one (1) year from the date of shipment. If any such product proves defective

during this warranty period, XIA LLC, at its option, will either repair the defective products

without charge for parts and labor, or will provide a replacement in exchange for the

defective product.

In order to obtain service under this warranty, Customer must notify XIA LLC of the defect

before the expiration of the warranty period and make suitable arrangements for the

performance of the service.

This warranty shall not apply to any defect, failure or damage caused by improper uses or

inadequate care. XIA LLC shall not be obligated to furnish service under this warranty a)

to repair damage resulting from attempts by personnel other than XIA LLC representatives

to repair or service the product; or b) to repair damage resulting from improper use or

connection to incompatible equipment.

THIS WARRANTY IS GIVEN BY XIA LLC WITH RESPECT TO THIS PRODUCT IN

LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. XIA LLC AND

ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF

MERCHANTABILITYOR FITNESS FOR A PARTICULAR PURPOSE. XIA’S

RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE

SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH

OF THIS WARRANTY. XIA LLC AND ITS VENDORS WILL NOT BE LIABLE FOR

ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES

IRRESPECTIVE OF WHETHER XIA LLC OR THE VENDOR HAS ADVANCE

NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Contact Information:

XIA LLC

31057 Genstar Rd.

Hayward, CA 94544 USA

Telephone: (510) 401-5760

Downloads: http://support.xia.com

Customer Support: support@xia.com

Version 3.00 www.xia.com 6

Page 7

Pixie-16 User Manual August 21, 2018

Convention

Description

Example

»

The » symbol leads you

through nested menu items

and dialog box options.

The sequence

Run Results»MCA Histogram directs you to

pull down the Run Results menu, and select the

MCA Histogram item.

Bold

Bold text denotes items that

you must select or click on in

the software, such as menu

items, and dialog box options.

...click on the Startup tab.

[Bold]

Bold text within [ ] denotes a

command button.

[Start] indicates the command button labeled

Start Run.

monospace

Items in this font denote text

or characters that you enter

from the keyboard, sections

of code, file contents, and

syntax examples.

Setup.exe refers to a file called “setup.exe”

on the host computer.

“window”

Text in quotation refers to

window titles, and quotations

from other sources

“Acquire ADC Traces” indicates the window

accessed via Settings»Acquire ADC Traces.

Italics

Italic text denotes a new term

being introduced , or simply

emphasis

rise time refers to the length of the slow filter.

...it is important first to set the energy filter flat

top so that it is at least one unit greater than the

preamplifier risetime...

<Key>

<Shift-AltDelete> or

<Ctrl+D>

Angle brackets denote a key

on the keybord (not case

sensitive).

A hyphen or plus between

two or more key names

denotes that the keys should

be pressed simultaneously

(not case sensitive).

<W> indicates the W key

<Ctrl+W> represents holding the control key

while pressing the W key on the keyboard

Bold italic

Warnings and cautionary text.

CAUTION: Improper connections or settings

can result in damage to system components.

CAPITALS

CAPITALS denote DSP

parameter names

SLOWLEN is the length of the slow energy

filter

SMALL CAPS

SMALL CAPS are used for

panels/windows/graphs in the

GUI.

…go to the READ HISTOGRAMS panel and you

see…

Manual Conventions

The following conventions are used throughout this manual

Version 3.00 www.xia.com 7

Page 8

Pixie-16 User Manual August 21, 2018

1 Introduction

The Digital Gamma Finder (DGF) family of digital pulse processors are capable of

measuring both the amplitude and shape of pulses in nuclear spectroscopy applications.

The DGF architecture was originally developed for use with arrays of multi-segmented

HPGe gamma ray detectors, but has since been applied to an ever broadening range of

applications.

The DGF Pixie-16 is a 16-channel all-digital waveform acquisition and spectrometer card

based on the CompactPCI/PXI standard for fast data readout to the host. It combines

spectroscopy with waveform digitizing and the option of on-line pulse shape analysis. The

Pixie-16 accepts signals from virtually any radiation detector. Incoming signals are

digitized by 12-bit, 14-bit, and 16-bit, 100 Mega Samples per Second (MSPS), 250 MSPS,

and 500 MSPS ADCs. Waveforms of up to 163 μs in length for each channel can be stored

in a FIFO. The waveforms are available for onboard pulse shape analysis, which can be

customized by adding user functions to the core processing software. Waveforms,

timestamps, and the results of the pulse shape analysis can be read out by the host system

for further off-line processing. Pulse heights are calculated to 16-bit precision and can be

binned into spectra with up to 32K channels. The Pixie-16 supports coincidence

spectroscopy and can recognize complex hit patterns.

Data readout rates through the CompactPCI/PXI backplane to the host computer can be up

to 109 Mbyte/s. The standard PXI backplane, as well as additional custom backplane

connections are used to distribute clocks and trigger signals between several Pixie-16

modules for group operation. A complete data acquisition and processing systems can be

built by combining Pixie-16 modules with commercially available CompactPCI/PXI

processor, controller or I/O modules in the same crate.

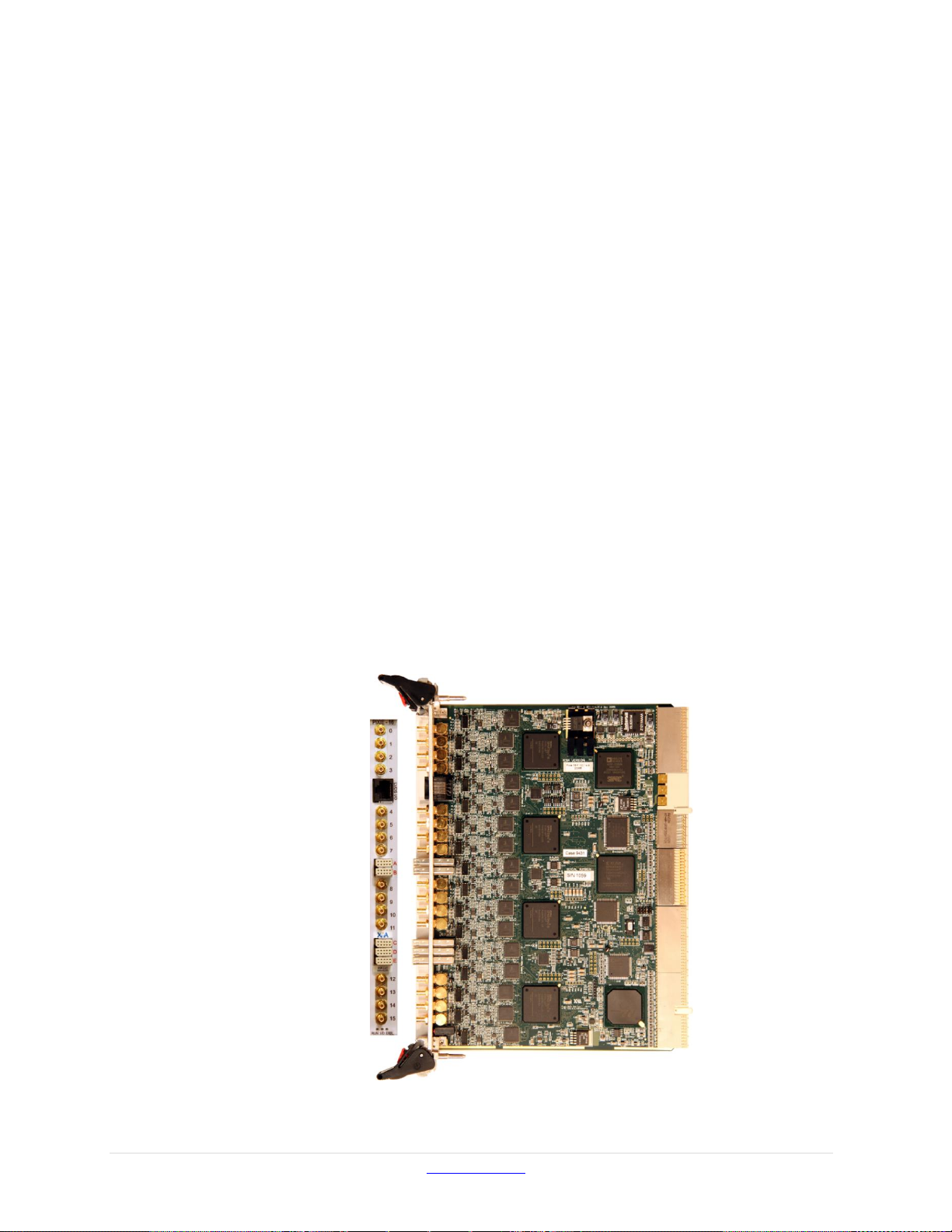

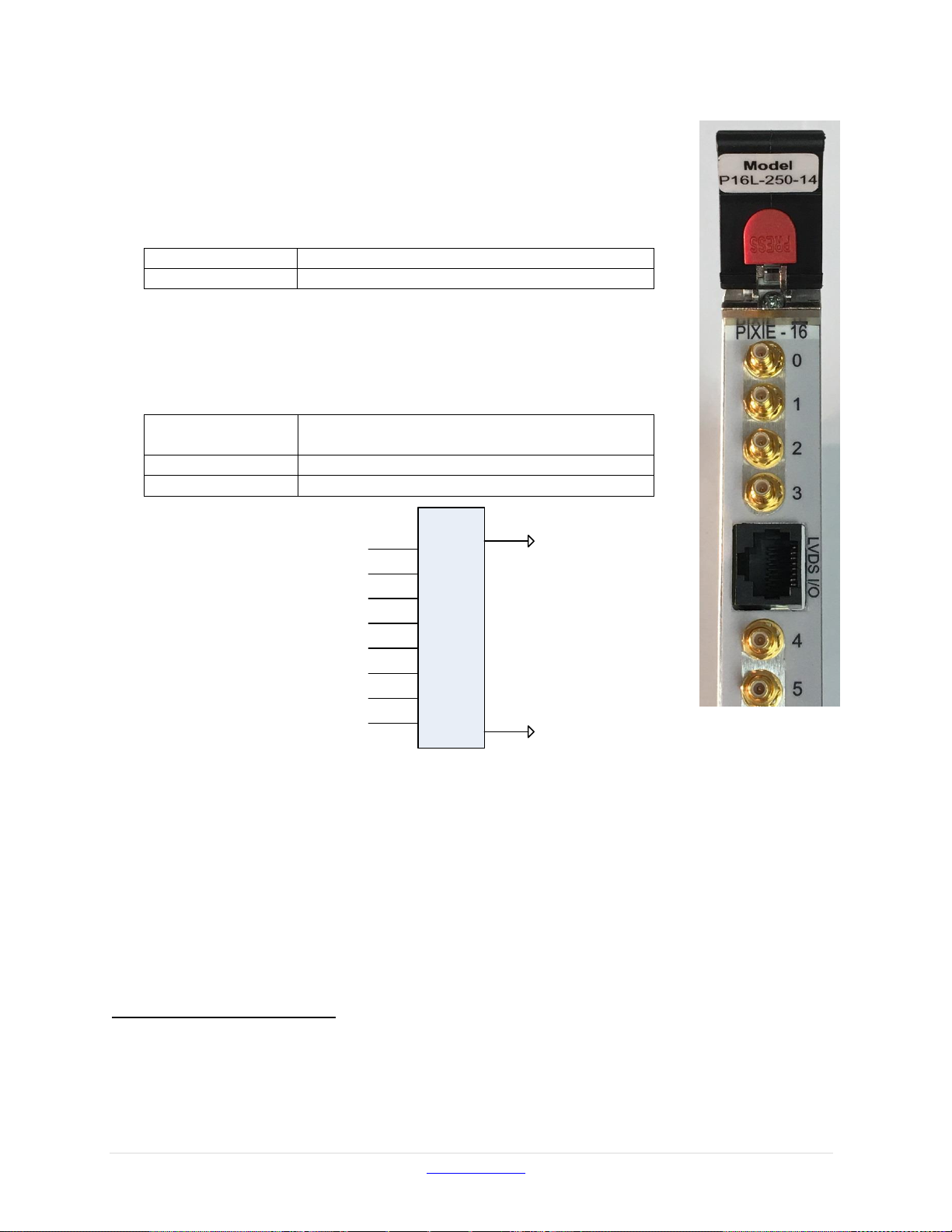

Figure 1-1: Picture of the front and side view of the Pixie-16.

Version 3.00 www.xia.com 8

Page 9

Pixie-16 User Manual August 21, 2018

1.1 Pixie-16 Features

Designed for

o Segmented germanium detectors,

o Silicon strip detectors,

o Arrays of scintillation detectors,

o Synchronous waveform capture for gamma- ray tracking,

o Sub-nanosecond timing measurements,

o Mixed systems with different detector types.

Accepts input signals directly from detector preamplifier outputs or scintillator/PMT

or SiPM combinations

12, 14, 16 bits; 100, 250, 500 MSPS ADC

Two software selectable gain/attenuation settings for each analog input

Programmable DC-offset for each analog input

Onboard CFD trigger with adjustable parameters

Programmable pileup inspection criteria include trigger filter parameters, threshold,

and rejection criteria

Triggered synchronous acquisition across channels and modules of waveforms up to

163 µs in length

On-board MCA spectrum from 1K to 32K bins (software selectable), up to 4.3

billion counts per bin

Event processing and optional pulse shape analysis performed with 100 MHz, 32-bit

floating point SHARC® DSP

Event by event list mode data buffered to allow zero dead-time acquisition

Full speed 32-bit, 33 MHz PCI interface to host computer, up to 109 MBytes/s

readout sustained

Configurable digital inputs and outputs

More than 120 backplane lines for clock and trigger distribution or general purpose

I/O and run synchronization between modules

Graphical user interfaces to control and diagnose system

Digital oscilloscope for health-of-system analysis

Compact C driver libraries available for easy integration in existing user interface

Version 3.00 www.xia.com 9

Page 10

Pixie-16 User Manual August 21, 2018

Front Panel I/O

Signal Input

16 analog signal inputs (SMB). Switchable input impedance and

attenuation: 50 Ω or 1 kΩ or 4 kΩ (or according to user specification), 1:4

or 1:1 attenuation

Jumper selectable 50 Ω input termination

Sixteen preamplifier inputs, switchable input impedance and attenuation:

50 Ω or 1 kΩ or 4 kΩ (or according to user specification)

Input signal is not recommended to exceed +/-3.5V if 50 Ohm input

termination jumper is installed and the 1:4 attenuation is not used

Works with common resistive feedback preamplifiers of either signal

polarity

Logic Input/output

28 digital inputs/outputs, including:

4 high speed LVDS input/output connections

16 LVDS inputs for channel specific veto (or validation)

2 LVDS inputs for module veto (or validation) or general purpose I/O

6 single-ended inputs and 6 single-ended outputs

Option for external clock through front panel input. In addition, there are

more than 120 digital lines on the backplane for low skew system clock

distribution, trigger, run synchronization, and global veto lines, and

complex trigger logic, multiplicity information, or data transfers between

modules

Backplane I/O

Clock Input/output

Distributed 50 MHz clock, dedicated PXI_CLK line from slot 2 or daisychained

Synchronization

Wired-or SYNC signal distributed through PXI backplane to synchronize

timers and run start/stop

Veto

VETO signal distributed through PXI backplane to suppress event

triggering

General purpose

I/O

More than 120 (121 for Rev F modules, 164 for Rev B/C/D modules)

bussed and neighboring lines on custom backplane to distribute

multiplicity and triggers and for I/O between modules

Data Interface

PCI

32-bit, 33MHz Read/Write, external memory or FIFO readout rate to host

over 100 MByte/s

Digital Controls

Input

Choice of two attenuation options through software settable input relay

Gain

Fixed analog voltage gain set to factory standard or per user specification,

digital gain adjustment possible

Offset

DC offset adjustment from –1.5V to +1.5V, in 65536 steps

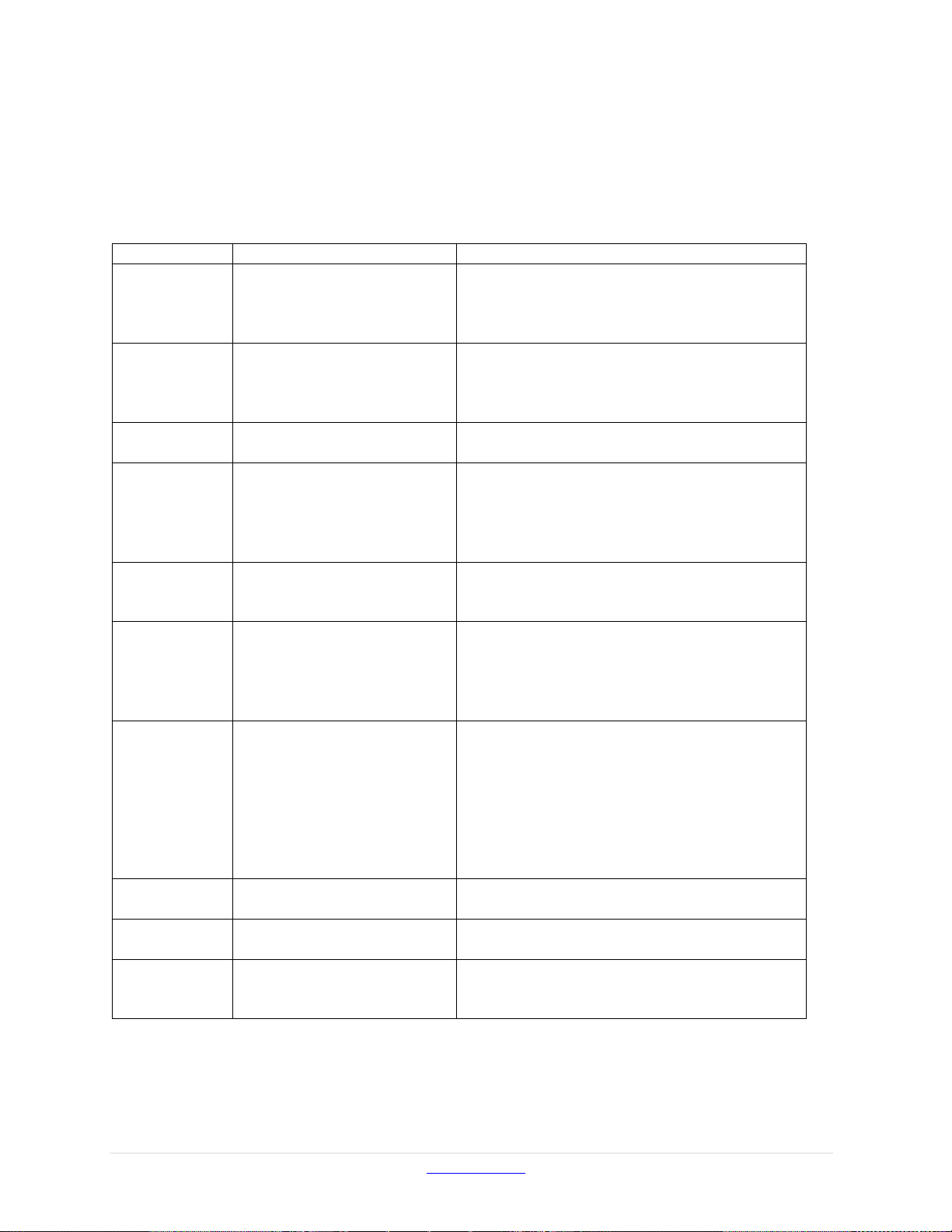

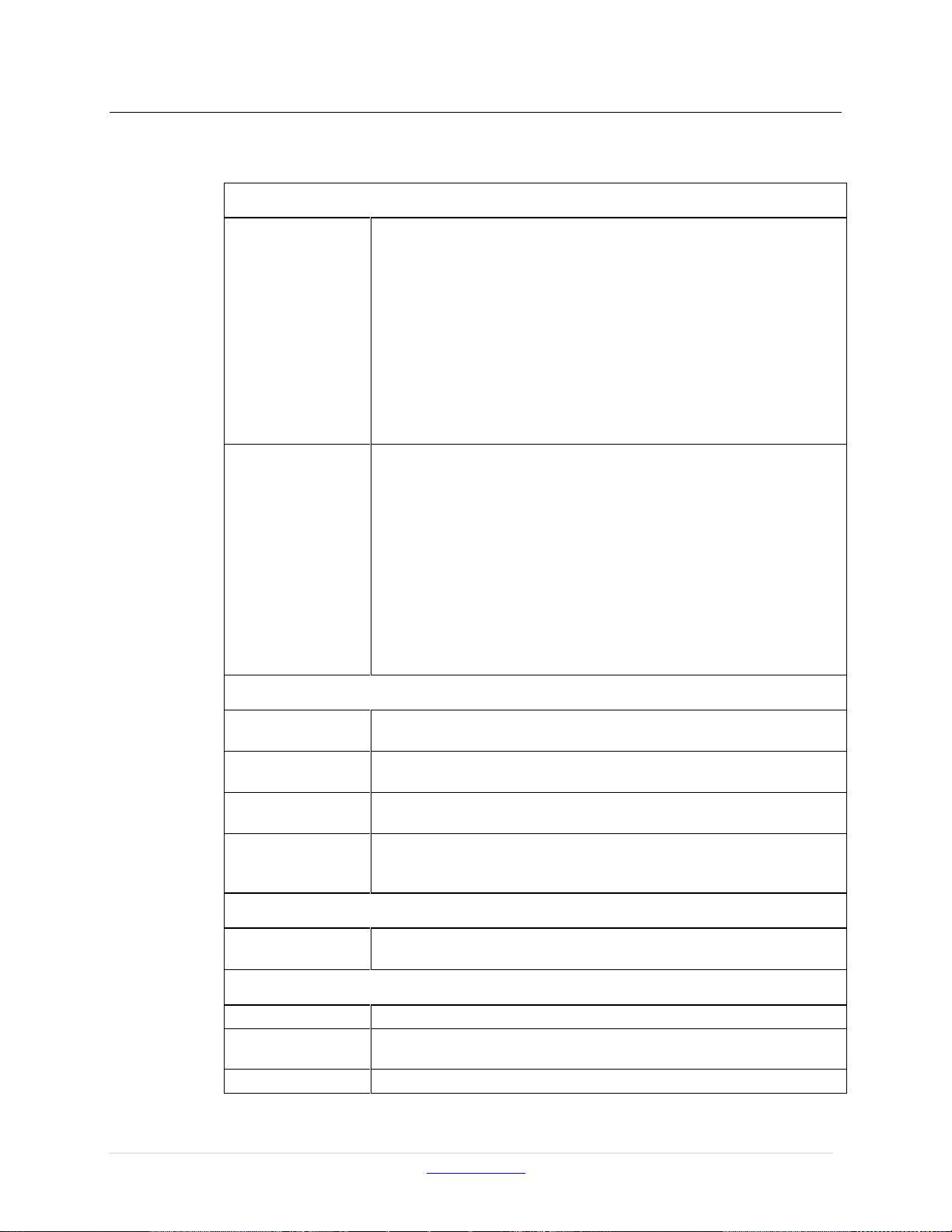

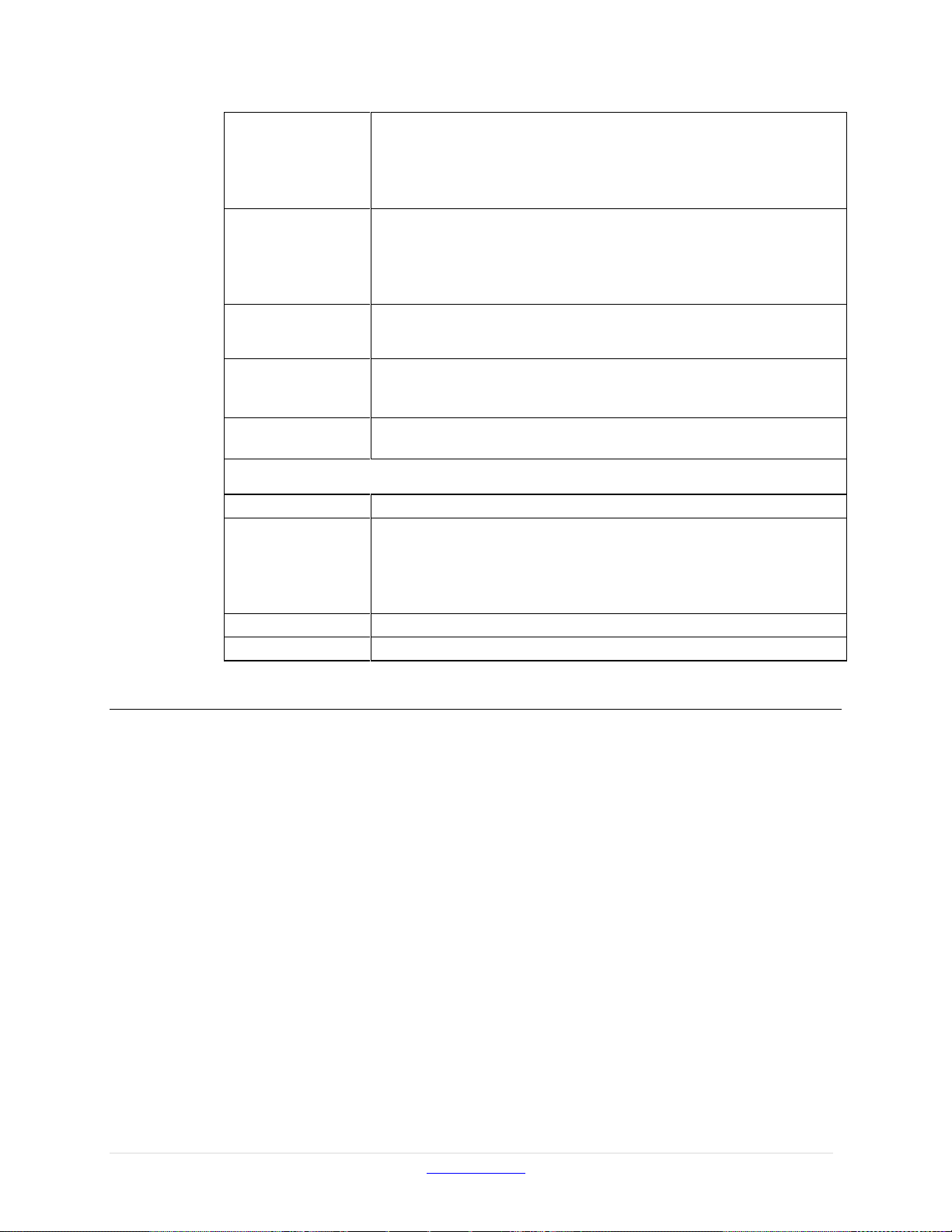

1.2 Specifications

Table 1-1 Detailed Specifications of Pixie-16

Version 3.00 www.xia.com 10

Page 11

Pixie-16 User Manual August 21, 2018

Shaping (Slow

Filter)

Digital trapezoidal filter with adjustable rise time and flat top for pulse

height computation

Rise time and flat top: 0.04 to 80 s (0.032 to 65.5 s for 250 MHz

modules), set independently

Adjustable flat top to eliminate ballistic deficit effects

Trigger (Fast

Filter)

Digital trapezoidal filter with adjustable rise time, flat top and threshold

for pulse trigger detection

Rise time and flat top: 0.02 to 1.27 s (0.016 to 1.016 s for 250 MHz

modules), set independently

9-bit threshold values corresponding to 0 to 511 ADC steps

Constant Fraction

Discriminator

(CFD) trigger

Programmable CFD length, delay and scaling factor

Coincidence or

Multiplicity

Programmable coincidence pattern, coincidence window length, fast

trigger delays

Programmable multiplicity group pattern, multiplicity threshold

Data collection

MCA binning factor and number of bins

Waveform length and pre-trigger delay

Data Outputs

MCA spectrum

32,768 bins, 32 bit deep (4.2 billion counts/bin) for each channel

List mode event

data

256K16bit FIFO memory for buffering list mode data which consist of

event ID, time stamp (48-bit), CFD time (16-bit), energy (16-bit), and

optional waveform, raw energy sums, baseline, and QDC sums

Events are time stamped with 100 or 125 MHz clock with fractional CFD

time that is captured at full ADC clock rate (100 or 250 or 500 MHz)

Statistics

Real time, live time, input and output counts for each channel

Diagnostics

ADC trace, baseline history, baseline distribution, FFT noise spectrum

1.3 System Requirements

The digital spectroscopy system considered here consists of a host computer, one or more

Pixie-16 modules in a Pixie-16 crate, and a gamma ray detector with appropriate power

supplies.

1.3.1 Pixie-16 Crate

The Pixie-16 can be operated in any slot from 2 to 14 of a Pixie-16 crate. Slot 1 is used by

the crate controller.

1.3.2 Host Computer

The Pixie-16 module communicates with a host computer through a PCI interface. The

host computer is usually either an embedded PC installed in slot 1 of the Pixie-16 crate or

a remote desktop or laptop that is linked to the crate via a PCI bridge that is also installed

in slot 1.

The host computer must have the following minimum capabilities

~100 MB of disk space for operation software

Sufficient disk space for acquired data

Version 3.00 www.xia.com 11

Page 12

Pixie-16 User Manual August 21, 2018

Windows 7/10 (32 bit or 64 bit) (currently still compatible with Windows XP).

Operation under Linux is supported, please contact XIA for details.

There are no minimum processor requirements, but a clock rate of 1 GHz or more

and memory of 512 MB or more are recommended.

1.3.3 Drivers and Software

Communication between the Pixie-16 module and the host PC is facilitated by the PCI

driver files and API functions provided by PLX Technology (version 7.10). Drivers are

provided by the XIA software distribution. Standalone PLX PCI library files can be

downloaded from XIA’s web site. Please contact XIA for details.

The Pixie-16 software is a Windows based user interface for the Pixie-16 modules.

Alternative interfaces are ROOT (under Linux) or command line C programs; demo code

is provided on request.

1.3.4 Detector Signals

The Pixie-16 is designed for single exponentially decaying signals. Step pulses or short

non-exponential pulses can be accommodated with specific parameter settings. Staircase

type signals from reset preamplifiers generally need to be AC coupled.

The amplitude of the detector output signals is not recommended to exceed +/-3.5V if 50

Ohm input termination jumper is installed and the 1:4 attenuation is not used.

1.3.5 Power Requirements

The Pixie-16 consumes roughly between 40W and 50W (depending on ADC variants of

100 MHz to 500 MHz), requiring the following currents from the Pixie-16 crate:

1.8V 3 - 4 A

3.3V 3 - 4 A

5V5 3 - 4 A

-6V 1.5 A

1.3.6 Connectors and Cabling

The Pixie-16 uses SMB connectors for the analog inputs from the detectors. SMB to BNC

adapter cables are provided with the module.

A 10pin har-link® connector is used for digital inputs and outputs. The pin pitch is 2mm.

Matching cables are e.g. Harting 33 27 243 1000 002.

1.4 Software and Firmware Overview

For installation of the software and an introduction to the user interface, please refer to the

following chapter of this manual. For details on the driver layer, please refer to the

programmer’s manual.

1.5 Front Panel

On the front panel of each Pixie-16 module, there are 16 analog signal input connectors,

one LVDS I/O port, five digital I/O connectors as well as three LEDs near the bottom of

the front panel. In addition, a sticker showing Pixie-16 model number (e.g., P16L-250-14,

meaning the 14-bit, 250 MHz variant of the Pixie-16) is affixed to the top handle of the

Version 3.00 www.xia.com 12

Page 13

Pixie-16 User Manual August 21, 2018

Connector Labels

0 to 15 for 16 channels

Connector Type

SMB Jack

Connected Signals

4 LVDS pairs (Fo1p/Fo1n, Fi1p/Fi1n, Fi5p/Fi5n,

Fo5p/Fo5n, see below for pin layout)

Signal Direction

Input or Output, software configurable

Cable Type

Cat 5 or Cat 6 (the same ones used for Ethernet)

J101

5

4

3

2

1

6

7

8

10

9

Fo

1p

Fo

1n

Fi

1p

Fi

1n

Fi

5p

Fi

5n

Fo

5p

Fo

5n

1

front panel, and another sticker indicating the serial number of the

Pixie-16 module (e.g., S/N 1100) is placed at the bottom handle of

the front panel.

1.5.1 16 Analog Signal Input Connectors (all Pixie-16 revisions1)

Table 1-2 Pixie-16 Analog Signal Input Connectors

Each Pixie-16 module accepts 16 analog input signals, and each

input connector is a SMB Jack (male contact) connector.

1.5.2 LVDS I/O Port (all Pixie-16 revisions)

Table 1-3 Pixie-16 LVDS I/O Port

Each Pixie-16 module is equipped with one LVDS I/O port on its front panel. LVDS stands

for low voltage differential signaling. The LVDS I/O connector is a RJ45 connector, which

implies that the same Cat 5 or Cat 6 Ethernet cables can be used to connect signals to or

from this I/O port. However, no Ethernet connectivity is available through this Pixie-16

I/O port.

Four differential signal pairs, i.e., between pin-pairs Fo1p/Fo1n, Fi1p/Fi1n, Fi5p/Fi5n, and

Fo5p/Fo5n, are available from this I/O port. Each pair can be configured as either an input

or output signal.

The most frequent use of this LVDS I/O port is accepting veto signals in Compton

Revision for a given Pixie-16 module can be determined based on its serial number: S/N 120-134 -> Rev. B; S/N

135-199 -> Rev. C; S/N 200-274 -> Rev. D; S/N 1000 and up -> Rev. F

Version 3.00 www.xia.com 13

suppressed Clover detector systems. In such systems, each Clover detector has four

Figure 1-2: Pixie-16 LVDS I/O Port.

Page 14

Pixie-16 User Manual August 21, 2018

G0_P FI4

B

A2

FI3

B2 C2 D2 E2

A1 B1 C1 D1 E1

G0_N

G1_P G2_P G3_P

G1_N

G2_N G3_N

G7_P FI0

C

A2

FI2

B2 C2 D2 E2

A1 B1 C1 D1 E1

G7_N

G6_P G4_P G5_P

G6_N

G4_N G5_N

G9_P MG_P

D

A2

MG_N

B2 C2 D2 E2

A1 B1 C1 D1 E1

G9_N

G8_P G10_P G11_P

G8_N

G10_N G11_N

G14_P SG_P

E

A2

SG_N

B2 C2 D2 E2

A1 B1 C1 D1 E1

G14_N

G12_P G15_P G13_P

G12_N

G15_N G13_N

FO0 FI6

A

A2

FI7

B2 C2 D2 E2

A1 B1 C1 D1 E1

FO2 FO4

FO3

FO6 FO7

individual HPGe crystals which are surrounded by an anti-Compton shield (e.g., BGO

crystal + PMT readout). If the veto signals from the anti-Compton shield are generated

using external electronics and then converted to LVDS format (e.g., using XIA’s LVDS

fanout boards), 4 such veto signals can then be input to one Pixie-16 module using the

LVDS I/O port. In this way, 4 Compton suppressed Clover detectors (16 HPGe crystal

outputs to 16 input channels of the Pixie-16) can be instrumented by one Pixie-16 module.

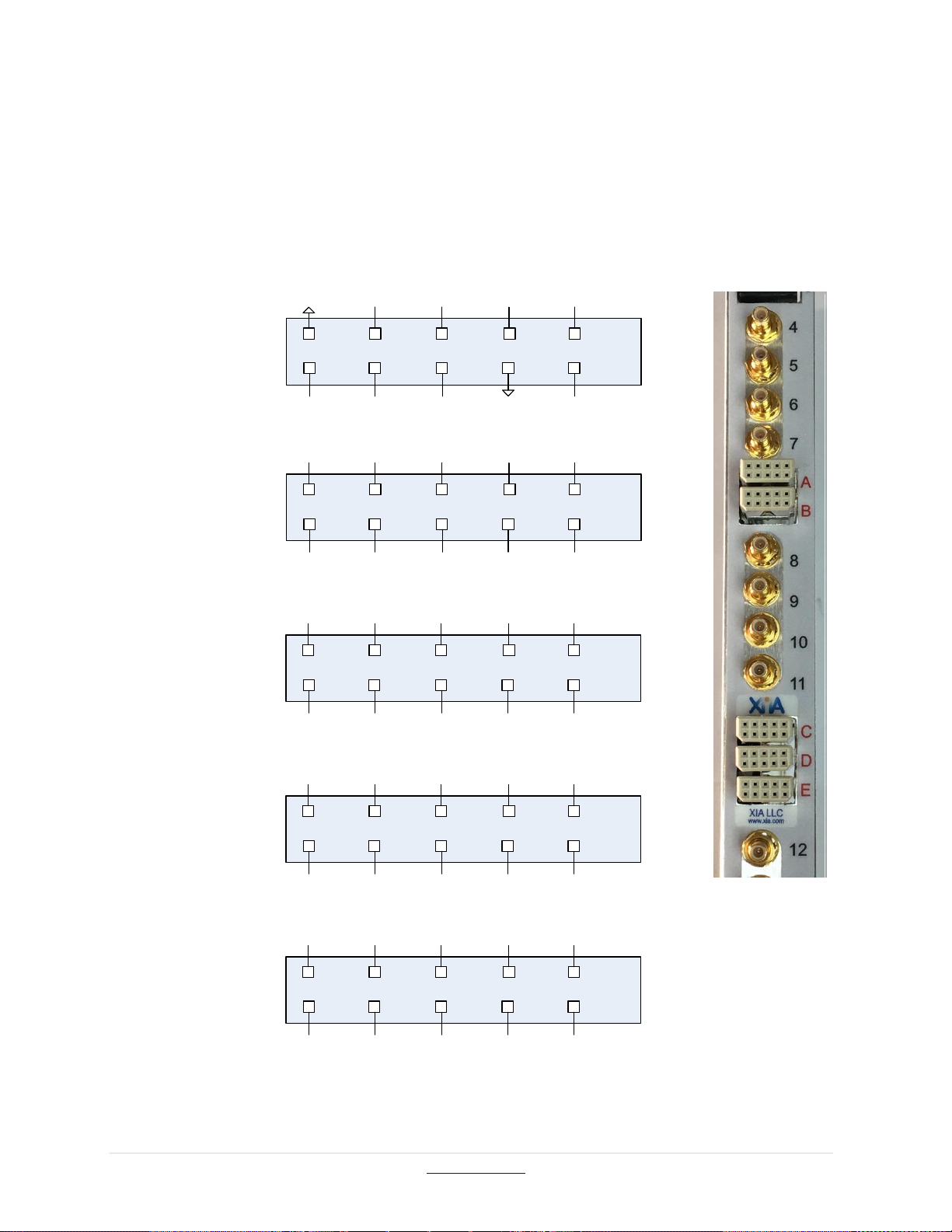

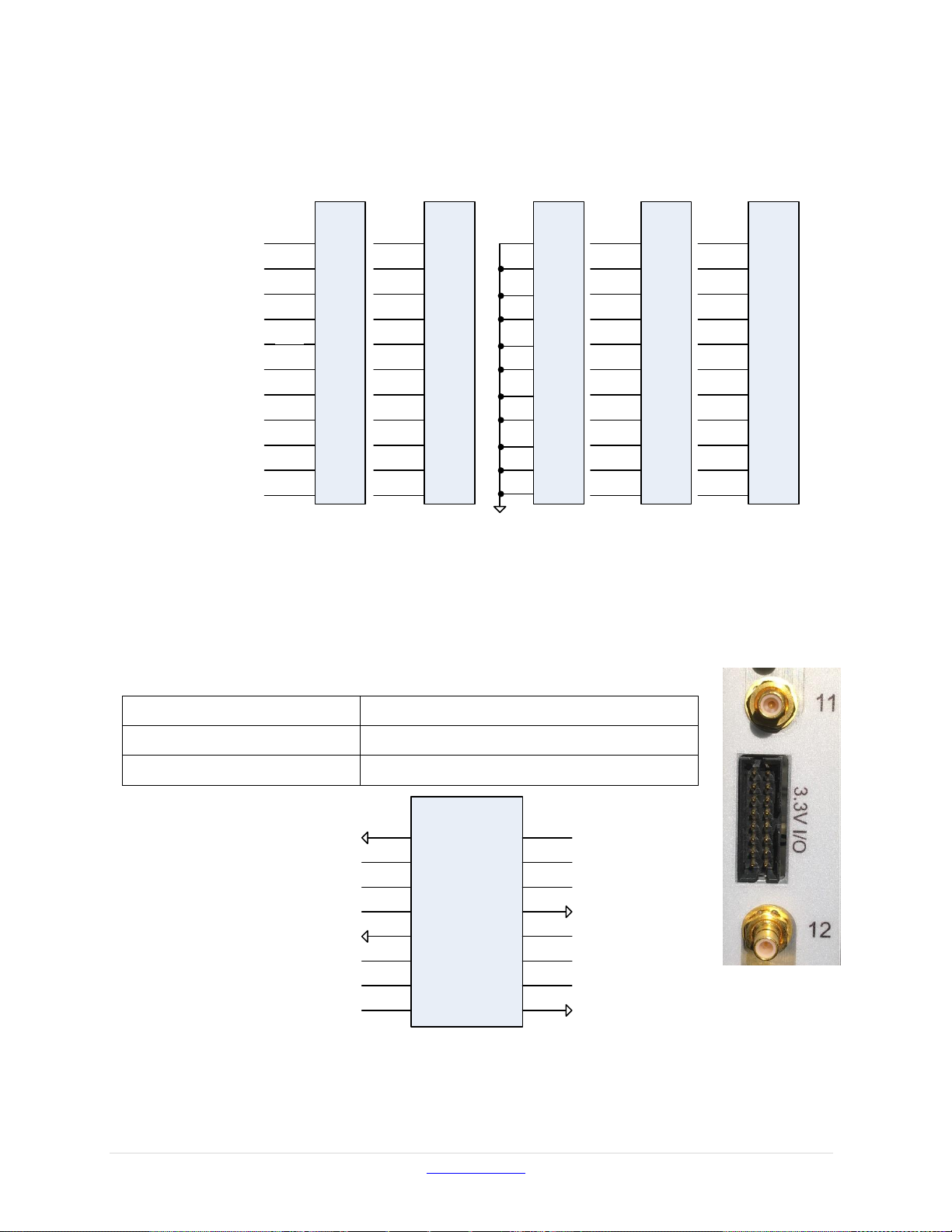

1.5.3 Digital I/O Connectors (A, B, C, D, E in red color font) (Rev. F Modules only)

Figure 1-3: Pixie-16 Digital I/O Connectors A, B, C, D and E.

Version 3.00 www.xia.com 14

Page 15

Pixie-16 User Manual August 21, 2018

Connector Type

har-link (HARTING, 2mm pin spacing)

FI0, FI2, FI3, FI4, FI6, FI7

TTL digital input signals (max. 5V)

FO0, FO2, FO3, FO4, FO6, FO7

Digital outputs for test/debug purpose (TTL 5V)

Gx_P/Gx_N (x=0-15)

Channel Gate Inputs (0-15 for 16 channels) (LVDS format)

MG_P/MG_N

Module Gate Input (LVDS format)

SG_P/SG_N

Spare Gate Input (LVDS format)

Table 1-4 Pixie-16 Rev. F Module’s Digital I/O Connectors

The Pixie-16 Rev. F modules are equipped with five har-link connectors on its front panel

which act as digital I/O connectors. The 2mm pitch har-link connector from HARTING

is designed for high speed data transfer with rates up to 2 Gbit/s. Its EMI shielding, shown

in Figure 1-4, guarantees excellent performance in EM-polluted environment.

Figure 1-4: 2mm pitch har-link connector from HARTING.

Each har-link connector has 2 rows with 5 pins on each row, and is labelled using one of

the five letters in red color font, from A to E. The signals connected to each pin of these

five connectors are shown in Table 1-4. Among them, FI0, FI2, FI3, FI4, FI6, FI7 are six TTL

digital input signals. They can be signals like global fast trigger, global validation trigger,

external clock, run inhibit, etc. The specific usage of each input pin is determined by the

specific firmware that is downloaded to the Pixie-16 module (see Table 1-9 for input

signals supported by the standard firmware). The six digital output signals, FO0, FO2, FO3,

FO4, FO6, FO7, which are connected to six test output pins on the System FPGA of the

Pixie-16, can be used to assist a user in the process of system setup. These test pins are

connected to various internal signals of the Pixie-16 to provide insight of the current status

of the system.

The Channel Gate Inputs (0-15 for 16 channels) are LVDS format input signals which

independently gate the data acquisition of each of the 16 channels of a Pixie-16 module.

The Channel Gate signal is level sensitive signal, i.e., when the level of the Channel Gate

Signal is logic high (1), the gate signal is effective; when the level of the Channel Gate

Signal is logic low (0), the gate signal is not in use. In normal cases, the Channel Gate

Signal is set up to veto the data acquisition in a given channel, i.e., at the time of the arrival

of fast trigger in that channel, if the Channel Gate Signal is logic high (1), that fast trigger

is discarded since it is vetoed. However, this type of logic can be reversed through setting

corresponding registers in the FPGA via software. In such cases, the Channel Gate Signal

is set up to validate the data acquisition in a given channel, i.e., at the time of fast trigger

in that channel, only if the Channel Gate Signal is logic high (1) will that fast trigger be

accepted to have the event recorded.

Version 3.00 www.xia.com 15

Page 16

Pixie-16 User Manual August 21, 2018

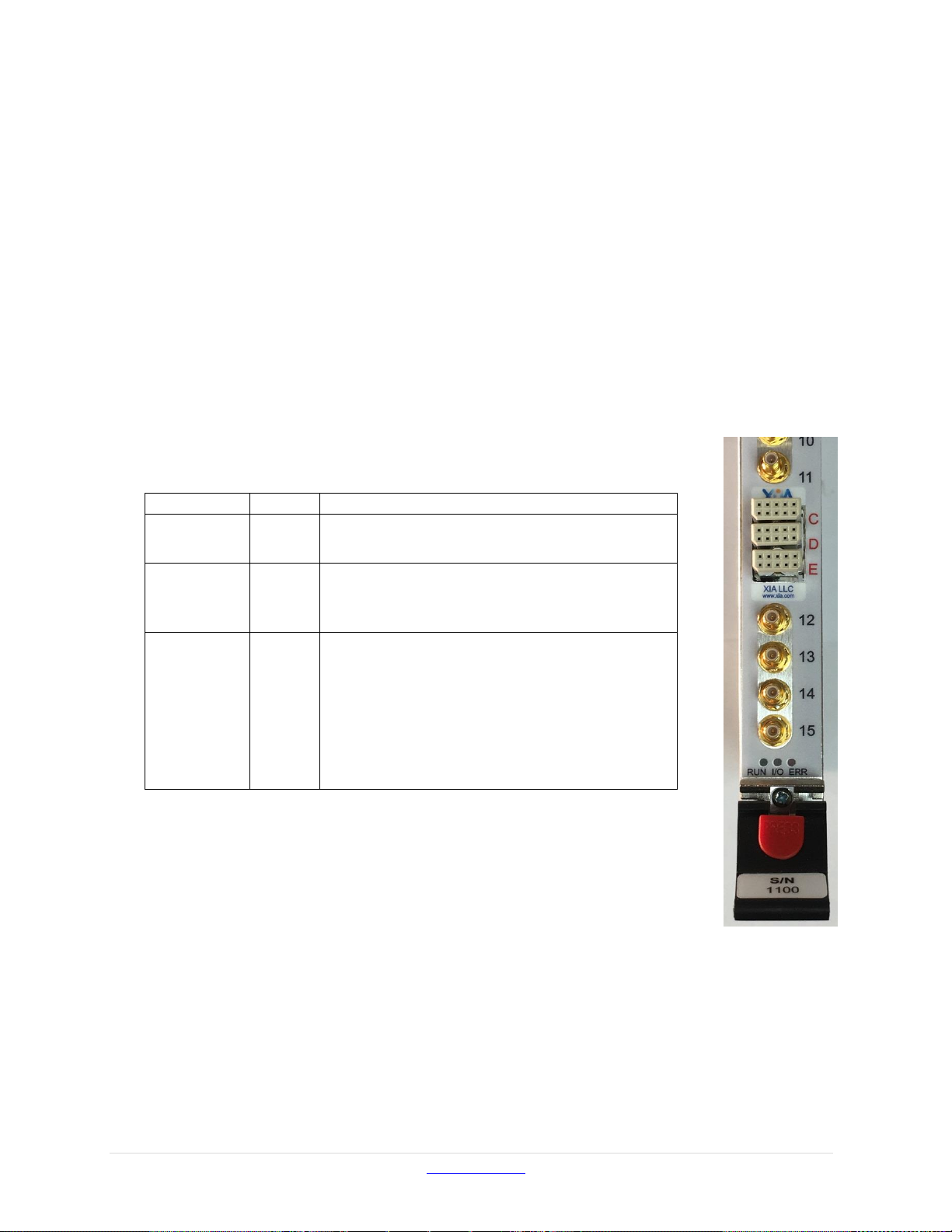

LED Name

Color

Function

RUN

Green

ON when run is in progress, and OFF if run is

stopped or not started yet

I/O

Yellow

Flashing when there is I/O activity on the PCI

bus between the Pixie-16 module and host

computer

ERR

Red

ON when there is no more space in the External

FIFO for storage of list mode event data, and

OFF when there is sufficient space to store at

least one more list mode event data

(ON does not indicate any actual error

condition. Rather, it simply indicates the

External FIFO’s FULL condition)

The Module Gate Input is a LVDS format signal that gates the data acquisition in all 16

channels of a Pixie-16 module. It is also a level sensitive signal, i.e., when the level of the

Module Gate Signal is logic high (1), the gate signal is effective; when the level of the

Module Gate Signal is logic low (0), the gate signal is not in use. In normal cases, the

Module Gate Signal is set up to veto the data acquisition in all 16 channels, i.e., at the time

of the arrival of fast trigger in any of the 16 channels, if the Module Gate Signal is logic

high (1), that fast trigger of that channel is discarded since it is vetoed. However, this type

of logic can be reversed through setting corresponding registers in the FPGA via software.

In such cases, the Module Gate Signal is set up to validate the data acquisition in all 16

channels, i.e., at the time of fast trigger in any of the 16 channel, only if the Module Gate

Signal is logic high (1) will that fast trigger of that channel be accepted to have the event

recorded.

The Spare Gate Input is a LVDS format signal that is reserved for special applications.

Such applications typically require development of custom firmware to support special

functionalities of the Pixie-16 system.

1.5.4 Front Panel LEDs (all Pixie-16 revisions)

Table 1-5 Front Panel LEDs for the Pixie-16 Modules

Near the bottom of the Pixie-16 front panel, there are three LEDs. They

are labelled as RUN, I/O, and ERR, respectively, from left to right. They

correspond to three different colors, green, yellow, and red,

respectively.

The RUN LED will be turned on when a run in the Pixie-16 module is

in progress, and will be turned off when the run is stopped or not started

yet. The I/O LED will blink when there is I/O activity on the PCI bus

between the Pixie-16 module and host computer. The ERR LED is, in fact, not to signal

any error condition in the Pixie-16 module. Instead, it is used to indicate whether or not the

External FIFO of the Pixie-16 module is full. It will be ON when there is no more space in

the External FIFO for storage of list mode event data, and OFF when there is sufficient

space to store at least one more list mode event data. When the External FIFO is full, no

more list mode event data can be written into it until the host software reads out part of the

Version 3.00 www.xia.com 16

data in the External FIFO through the PCI bus.

Page 17

Pixie-16 User Manual August 21, 2018

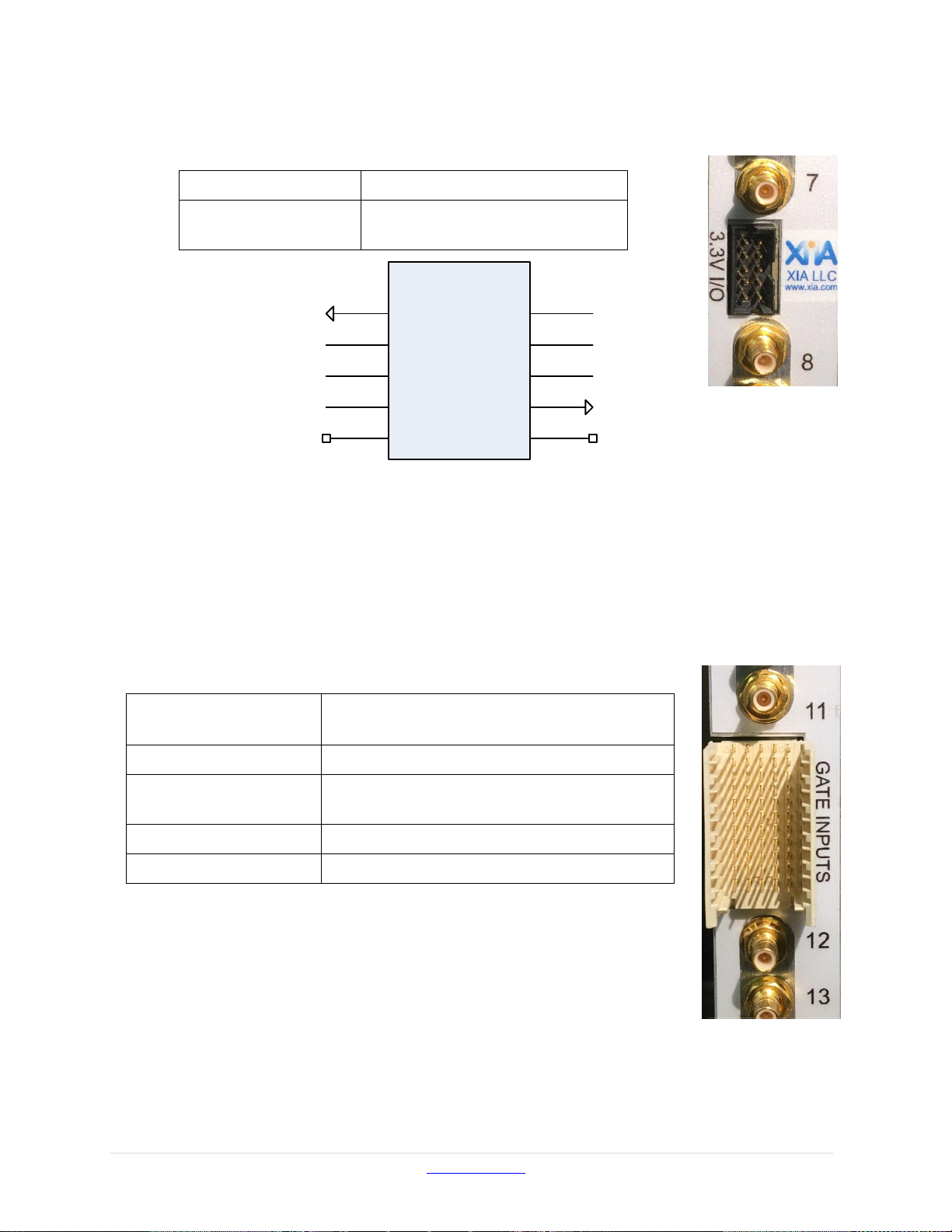

Connector Type

Single-ended, 2mm pin spacing

FO0, FO2, FO3, FO4,

FO6, FO7

Digital outputs for test/debug

purpose (3.3V)

J200

10

8

6

4

2 1

3

5

7

9

Fo

0

Fo

2

Fo

4

Fo

3

Fo

6

Fo

7

Connector Type

Amphenol FCI 55 Position Header, 2mm pin

spacing

FI0, FI2, FI3, FI4, FI6, FI7

TTL digital input signals (max. 5V)

Gxin+/Gxin- (x=0-15)

Channel Gate Inputs (0-15 for 16 channels)

(LVDS format)

MGin+/MGin-

Module Gate Input (LVDS format)

SGin+/SGin-

Spare Gate Input (LVDS format)

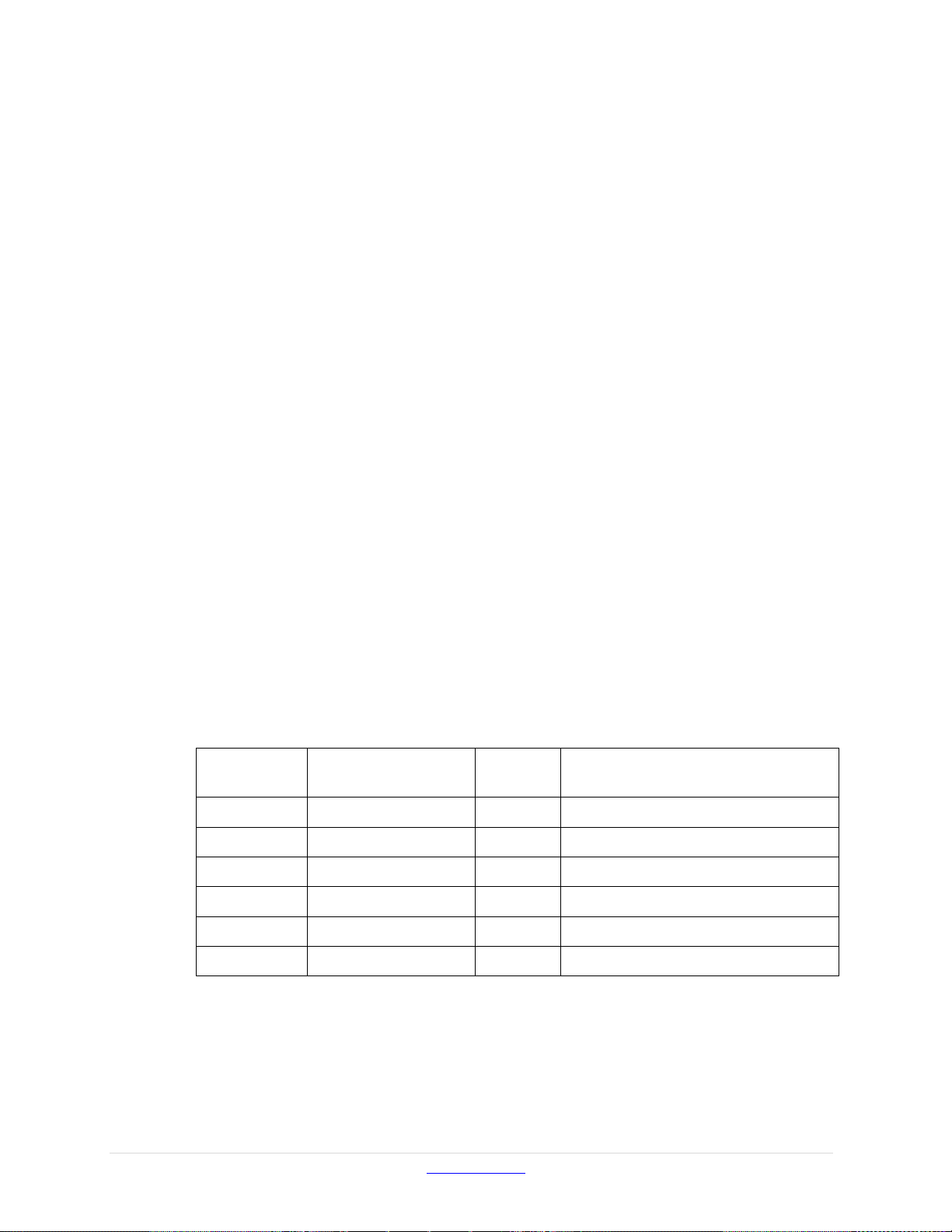

1.5.5 3.3V I/O Connector (Rev. D Modules only)

Table 1-6 Pixie-16 Rev. D Module’s 3.3V I/O Connector

Figure 1-5: Pixie-16 Rev. D Module’s 3.3V I/O Connector.

On Rev. D Pixie-16 modules, between analog input SMB connectors for channel 7 and

channel 8, respectively, is the 3.3V I/O Connector (J200). It has 10 single-ended pins with

2mm spacing. Pins #1, 3, 4, 5, 6, and 8 are connected to six digital output signals from the

System FPGA of the Pixie-16 module, i.e. FO0, FO2, FO3, FO4, FO6, FO7, mainly for the

purpose of testing and debugging. Pins #2 and 7 are ground pins, and pins #9 and 10 are

not in use.

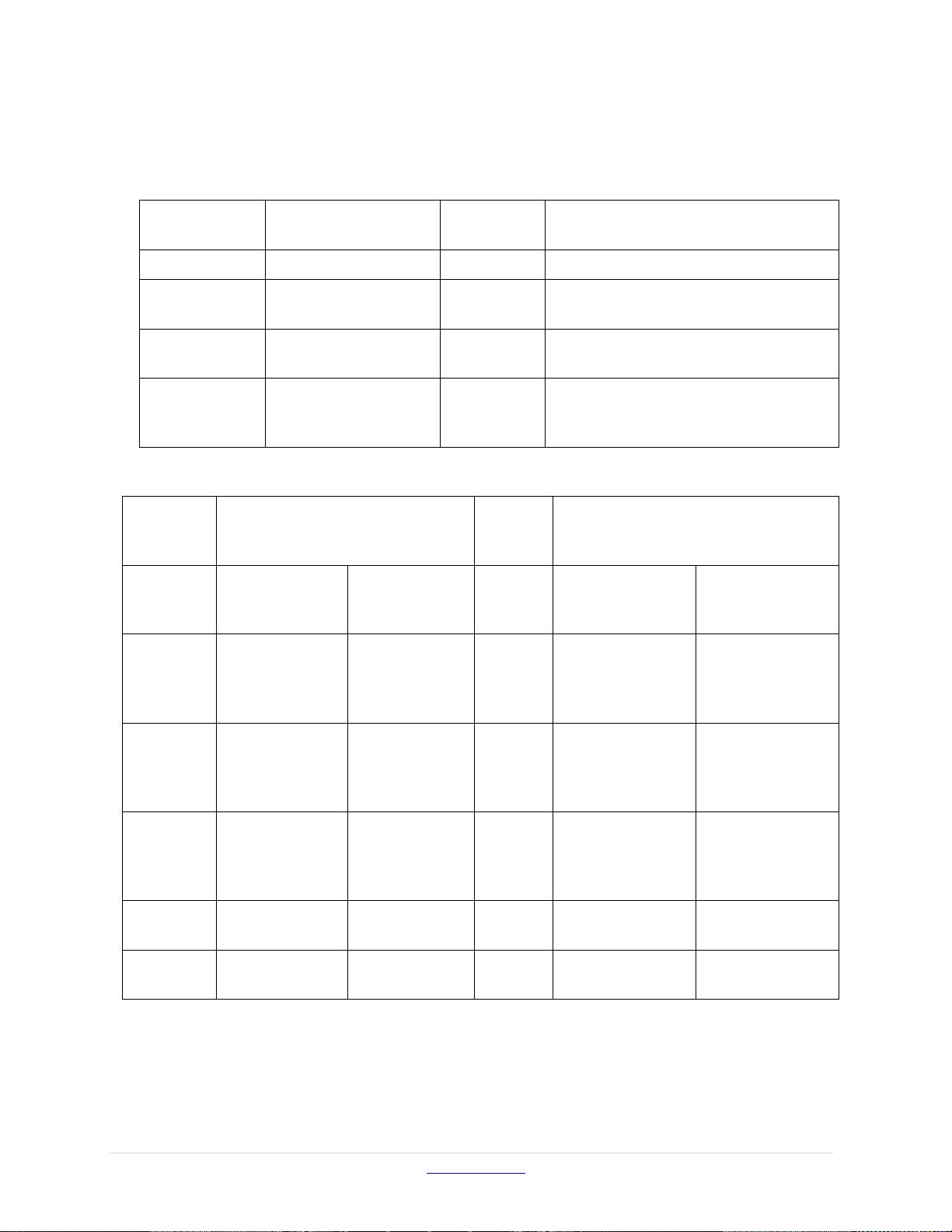

1.5.6 GATE Inputs (Rev. D Modules only)

Table 1-7 Pixie-16 Rev. D Module’s GATE Inputs

On Rev. D Pixie-16 modules, between analog input SMB connectors

for channel 11 and channel 12, respectively, is the GATE INPUTS

connector. This connector is an Amphenol FCI 55 Position Header

with 2mm pin spacing. The layout of these 55 pins is shown in Figure

1-6. The 11 pins from the middle pin column (J150C) are all tied to

the Ground. Among the first 8 rows of the GATE INPUTS

connector, each differential pair of pins from the A/B columns

Version 3.00 www.xia.com 17

(J150A/J150B) or the D/E columns (J150D/J150E) corresponds to one channel’s GATE

INPUT, which has the LVDS format, e.g. Gxin+/Gxin- (x=0-15). Differential pair of pins at

J150A3/J150B3 is the Module Gate Input signal, MGin+/MGin-. Channel Gate Input signal

can be used to veto or validate that given channel’s own trigger. Module Gate Input signal

Page 18

Pixie-16 User Manual August 21, 2018

J150A

A1

A5

A4

A3

A2

A6

A7

A8

A9

A10

A11

Fi6

Fi0

MGin+

G14in +

G12in +

G10in +

G8in+

G6in+

G4in+

G2in+

G0in+

J150B

B1

B5

B4

B3

B2

B6

B7

B8

B9

B10

B11

Fi7

Fi2

MGin-

G14in-

G12in-

G10in-

G8in-

G6in-

G4in-

G2in-

G0in-

J150C

C1

C5

C4

C3

C2

C6

C7

C8

C9

C10

C11

J150D

D1

D5

D4

D3

D2

D6

D7

D8

D9

D10

D11

Fi3

SGin+

G15in+

G13in+

G11in+

G9in+

G7in+

G5in+

G3in+

G1in+

J150E

E1

E5

E4

E3

E2

E6

E7

E8

E9

E10

E11

Fi4

SGin-

G15in-

G13in-

G11in-

G9in-

G7in-

G5in-

G3in-

G1in-

Connector Type

Single-ended, 2mm pin spacing

FI0, FI2, FI3, FI4, FI6, FI7

TTL digital input signals (max. 5V)

FO0, FO2, FO3, FO4, FO6, FO7

Digital outputs for test/debug purpose (3.3V)

J100

10

8

6

4

2 1

3

5

7

9

12 11

14 13

16 15

Fo

3

Fo

6

Fo

7

Fo

0

Fo

2

Fo

4

Fi

0

Fi

2

Fi

4

Fi

3

Fi

6

Fi

7

works on the whole module level, i.e. it can be used to veto or validate all 16 channels’

own trigger of that given module. Differential pair of pins at J150D3/J150E3 is the Spare

Gate Input signal, SGin+/SGin-. Spare Gate Input signal can be used for special applications

which require a custom firmware.

Figure 1-6: Pixie-16 Rev. D Module’s GATE INPUTS Connector.

On Rev. D Pixie-16 modules, the TTL digital input signals (max. 5V), i.e. FI0, FI2, FI3, FI4,

FI6, FI7, are distributed among the bottom two rows of the GATE INPUTS Connector, as

illustrated in Figure 1-6.

1.5.7 3.3V I/O Connector (Rev. B and C Modules only)

Table 1-8 Pixie-16 Rev. B and C Module’s 3.3V I/O Connector

Version 3.00 www.xia.com 18

On Rev. B and C Pixie-16 modules, between analog input SMB connectors for channel 11

and channel 12, respectively, is the 3.3V I/O Connector (J100). It has 16 single-ended pins

Figure 1-7: Pixie-16 Rev. B and C Module’s 3.3V I/O Connector.

Page 19

Pixie-16 User Manual August 21, 2018

TTL digital

input signals

Connected signals in

standard firmware

Direction

Description

FI0

EXT_FASTTRIG

Input

External fast trigger signal

FI2

INHIBIT

Input

Run inhibit signal

FI3

EXT_TS_CLK

Input

External timestamp clock signal

FI4

EXT_VALIDTRIG

Input

External validation signal

FI6

not used

FI7

EXT_TS_CLR

Input

External timestamp clear signal

with 2mm spacing. Pins #1, 3, 4, 5, 6, and 8 are connected to six digital output signals from

the System FPGA of the Pixie-16 module, i.e. FO0, FO2, FO3, FO4, FO6, FO7, mainly for

the purpose of testing and debugging. Pins #2, 7, 10 and 15 are ground pins. Pins #9, 11,

12, 13, 14 and 16 are connected to the six TTL digital input signals (max. 5V), i.e. FI0, FI2,

FI3, FI4, FI6, FI7.

1.5.8 Digital Input/output Signals Supported by Standard Firmware (all Pixie-16

revisions)

The standard firmware of the Pixie-16 supports input and output of digital signals through

its front panel I/O connectors, which were discussed earlier.

Table 1-9 shows the five TTL digital input signals supported by the Pixie-16 standard

firmware. Among them, the signals EXT_TS_CLK and EXT_TS_CLR are used for

external timestamping in the Pixie-16, i.e. the Pixie-16 accepting an external clock signal

(the frequency of this external clock is not recommended to exceed about 20 MHz in order

to avoid the clock signal integrity issue), counting such clock signal with a 48-bit counter,

and outputting such counter value to the list mode data stream when an event trigger occurs.

The external timestamping is useful for synchronizing the Pixie-16 data acquisition system

with another data acquisition system through correlating the external timestamps of the

events recorded by both systems.

The INHIBIT signal is used by an external system to inhibit the data acquisition run in a

Pixie-16 system when synchronization requirement is enabled in the Pixie-16 modules. It

is a level sensitive signal, i.e. when the INHIBIT signal is at the logic high level, the run in

the Pixie-16 won’t start. Only when the INHIBIT signal goes to the logic low level will the

run start in the Pixie-16. During the run, if the INHIBIT signal returns to the logic high

level, the run will be aborted.

The EXT_FASTTRIG signal is the external fast trigger signal, which can be used to replace

the local fast trigger for recording events in the Pixie-16 modules. The EXT_VALIDTRIG

signal is the external validation signal, which can be used to validate events in the Pixie16 modules.

Table 1-9 Pixie-16 TTL Digital Input Signals

Version 3.00 www.xia.com 19

Table 1-10 shows the Pixie-16 connector J101 LVDS I/O port signals. This J101 LVDS

I/O port can use the regular Ethernet cable for connection but it does not have Ethernet

connectivity. Among the four LVDS pairs available from this J101 port, one pair is

currently not in use, two pairs are used for input and one pair is used for output. The

LVDS_VALIDTRIG is the external validation trigger signal in LVDS format, and the

LVDS_FASTTRIG is the external fast trigger signal in LVDS format. The

Page 20

Pixie-16 User Manual August 21, 2018

Connector

J101 Pins

Connected signals in

standard firmware

Direction

Description

Fo1p/Fo1n

not used

Fi1p/Fi1n

LVDS_VALIDTRIG

Input

External validation trigger signal in

LVDS format

Fi5p/Fi5n

LVDS_FASTTRIG

Input

External fast trigger signal in LVDS

format

Fo5p/Fo5n

SYNC_LVDS_FP

Output

Pixie-16 synchronization output signal

in LVDS format (to synchronize with

other DAQ systems)

TTL digital

output

signals

Connected signals in standard

firmware

Direction

Description

FO0

FTRIG_DELAY

FTRIG_DELAY

Output

Delayed local fast

trigger of one of

the 16 channels

Delayed local fast

trigger of one of

the 16 channels

FO2

FTRIG_VAL

VETO_CE

Output

Validated,

delayed local fast

trigger one of the

16 channels

Stretched veto

trigger of one of

the 16 channels

FO3

ETRIG_CE

LDPMFULL

Output

Stretched external

global validation

trigger of one of

the 16 channels

Module level dual

port memory

(DPM) full status

flag

FO4

CHANTRIG_CE

SDPMFULL

Output

Stretched channel

validation trigger

of one of the 16

channels

System level dual

port memory

(DPM) full status

flag

FO6

FTIN_OR

FTIN_OR

Output

OR of 16 local

fast triggers

OR of 16 local

fast triggers

FO7

TEST_SEL

TEST_SEL

Output

Selected test

signal

Selected test

signal

SYNC_LVDS_FP is an output signal from the Pixie-16 module to indicate to external data

acquisition systems the synchronization status of the Pixie-16 system so that both data

acquisition systems can be synchronized.

Table 1-10 Pixie-16 Connector J101 LVDS I/O Port Signals

Table 1-11 Pixie-16 TTL Digital Output Signals

Table 1-11 lists the six Pixie-16 TTL digital output signals. Two groups of six output

signals can be chosen through software settings (see Table 3-9, bits [14:12] and [19:16] of

TrigConfig0). The last output signal TEST_SEL can be further selected through software

settings. More details about these signals will be provided in later sections of this manual.

Version 3.00 www.xia.com 20

Page 21

Pixie-16 User Manual August 21, 2018

Detector Preamp

50 W

Pixie-16 Rev. F

Illustration of one channel’s analog input stages

50

W

Jumper

JP1_x

x=1...16

3k W

Relay Switch (software controllable)

1k

W

Offset DAC

Gain

(x2.5)

ADC

(Max Vp-p = 2V)

If Jumper is not installed:

If Relay Switch is closed, attenuation is 1:1 (1k W termination), and overall effective gain is 2.5;

If Relay Switch is opened, attenuation is 1:4 (4k W termination), and overall effective gain is 0.625;

If Jumper is installed and detector preamplifier has 50 W output impedance:

If Relay Switch is closed, attenuation is 1:1 (47.6 W termination), and overall effective gain is 1.25;

If Relay Switch is opened, attenuation is 1:4 (49.4 W termination), and overall effective gain is 0.3125.

[-1.5V...+1.5V]

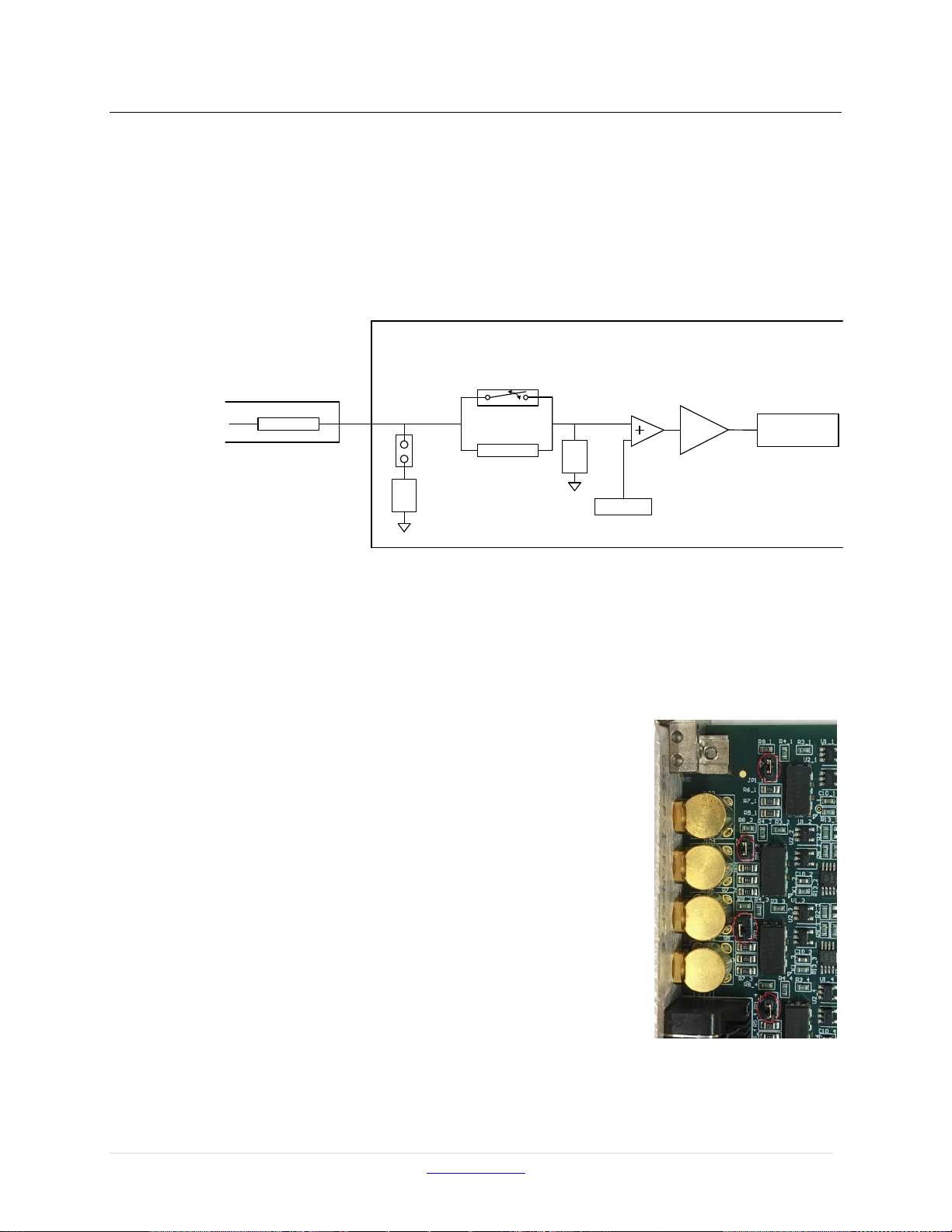

1.6 Front End Attenuation and Termination

Each Pixie-16 module has 16 independent analog input channels. To ensure analog input

signal can be properly digitized by each channel’s ADC, the signal must undergo proper

signal conditioning including 1) adjusting DC offset of the analog input signal using each

channel’s independent Offset DAC and 2) selecting proper input attenuation. The goal of

the analog signal conditioning is to fit the analog input signal into the ADC input voltage

range (2Vpp).

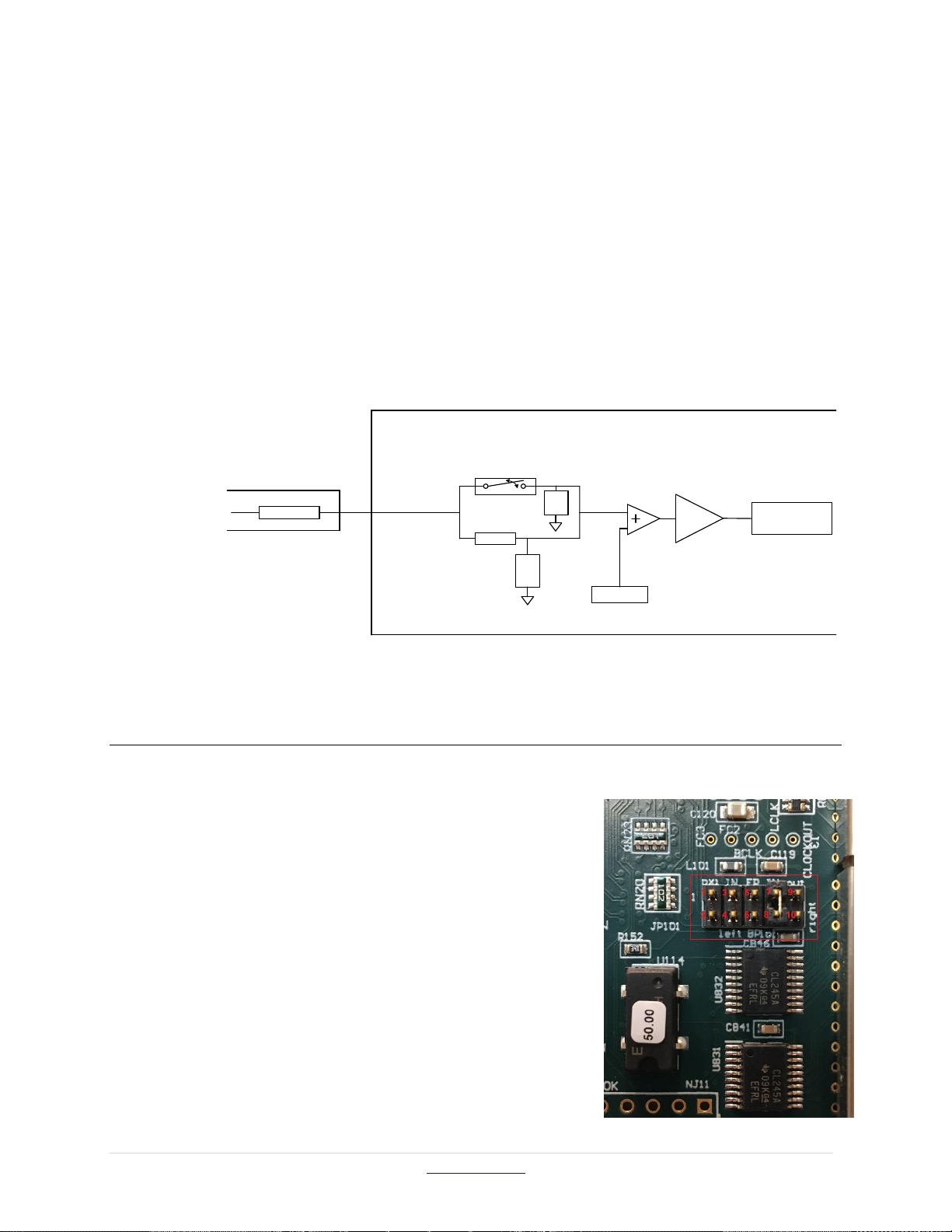

1.6.1 Rev. F Modules

The input stages of the Rev. F Pixie-16 modules are shown in

Figure 1-8. Each channel’s input termination jumper (JP1_x,

x=1…16), shown on the right in red circles, is used to connect

the analog input signal to a 50 W resistor then to ground. It is

installed by default at the factory, and is recommended for

being used to avoid input signal reflection when using long

coaxial cables to connect detector outputs to the Pixie-16

front panel connectors. However, if the detector outputs have

50 W output impedance, the signal will be effectively halved

at the input of the Pixie-16 when the input termination jumper

is installed.

A relay switch, which is controlled by software for closing or

opening, can be used to choose between two attenuation

factors and thus two overall effective gains for each of the 16

Pixie-16 input channels. The notes section of Figure 1-9

describes the effective attenuation factor, input impedance,

and overall gain for the four cases of the combinations of jumper installation and relay

switch. If different overall effective gains than the ones provided by the factory standard

(i.e. 2.5/0.625 or 1.25/0.3125) are necessary, please contact XIA for possible custom input

Figure 1-8: Rev. F Pixie-16 input stages.

Version 3.00 www.xia.com 21

Page 22

Pixie-16 User Manual August 21, 2018

Detector Preamp

50 W

Pixie-16 Rev. B,C,D

Illustration of one channel’s analog input stages

820 W

Relay Switch (software controllable)

240

W

Offset DAC

Gain

(x4)

ADC

(Max Vp-p = 2V)

If detector preamplifier has 50 W output impedance:

If Relay Switch is closed, attenuation is 1:1 (50 W termination), and overall effective gain is 2;

If Relay Switch is opened, attenuation is 1:4 (1k W termination), and overall effective gain is 0.9.

[-1.5V...+1.5V]

50

W

gains. That most likely will involve changing certain parts of the Pixie-16 input stages.

Other options will be either to change the gain of the detector preamplifier (if feasible) or

to change the high voltage supplied to the detectors (e.g. PMT or SiPM, etc.).

1.6.2 Rev. B, C, D Modules

Different from their Rev. F counterparts, Rev. B, C, D modules do not have the input

termination jumpers, and the input signal attenuation factors are also slightly different.

Figure 1-9 illustrates the input stages of the Rev. B, C, D Pixie-16 modules. Same as the

Rev. F modules, they also have a software controlled relay switch. When the relay switch

is closed, the input signal is tied to ground via a 50 W resistor, which effectively halves the

input signal if it has a 50 W output impedance. If the relay switch is opened, the input signal

passes through a second branch, which results in a 1:4 attenuation with a 1k W input

termination. The overall effective gain is 2 or 0.9 when the relay switch is closed or opened,

respectively.

Figure 1-9: Rev. B, C, D Pixie-16 input stages.

1.7 Operating Multiple Pixie-16 Modules Synchronously

When many Pixie-16 modules are operated together

as a system, it may be required to synchronize clocks

and timers between them and to distribute triggers

across modules. It will also be necessary to ensure that

runs are started and stopped synchronously in all

modules. All these signals are distributed through the

PXI backplane of the Pixie-16 crate.

1.7.1 Clock Distribution

In a multi-module system there will be one clock

master and a number of clock slaves or repeaters. The

clock function of a module can be selected by setting

shunts on Jumper JP101 near the bottom right corner

of the board. The 10-pin Jumper JP101 is shown in the

picture on the right with those pins labelled in red

color. Shunts are provided to connect pins that are

Version 3.00 www.xia.com 22

Page 23

Pixie-16 User Manual August 21, 2018

appropriate for each chosen clock distribution mode. Four clock distribution modes,

individual clock mode, PXI clock mode, daisy-chained clock mode, and multi- crate clock

mode, are described below.

Please note, in 250 MHz or 500 MHz Pixie-16 modules, the frequency of signal processing

clock in the FPGA has been divided down to either 125 MHz or 100 MHz, respectively,

for more practical implementation of the design. That division might result in different

clock phase and thus different timestamp offset for each channel within a given 250 MHz

or 500 MHz Pixie-16 module whenever the module is reinitialized. Calibration might be

needed to quantify the different timestamp offset for each channel.

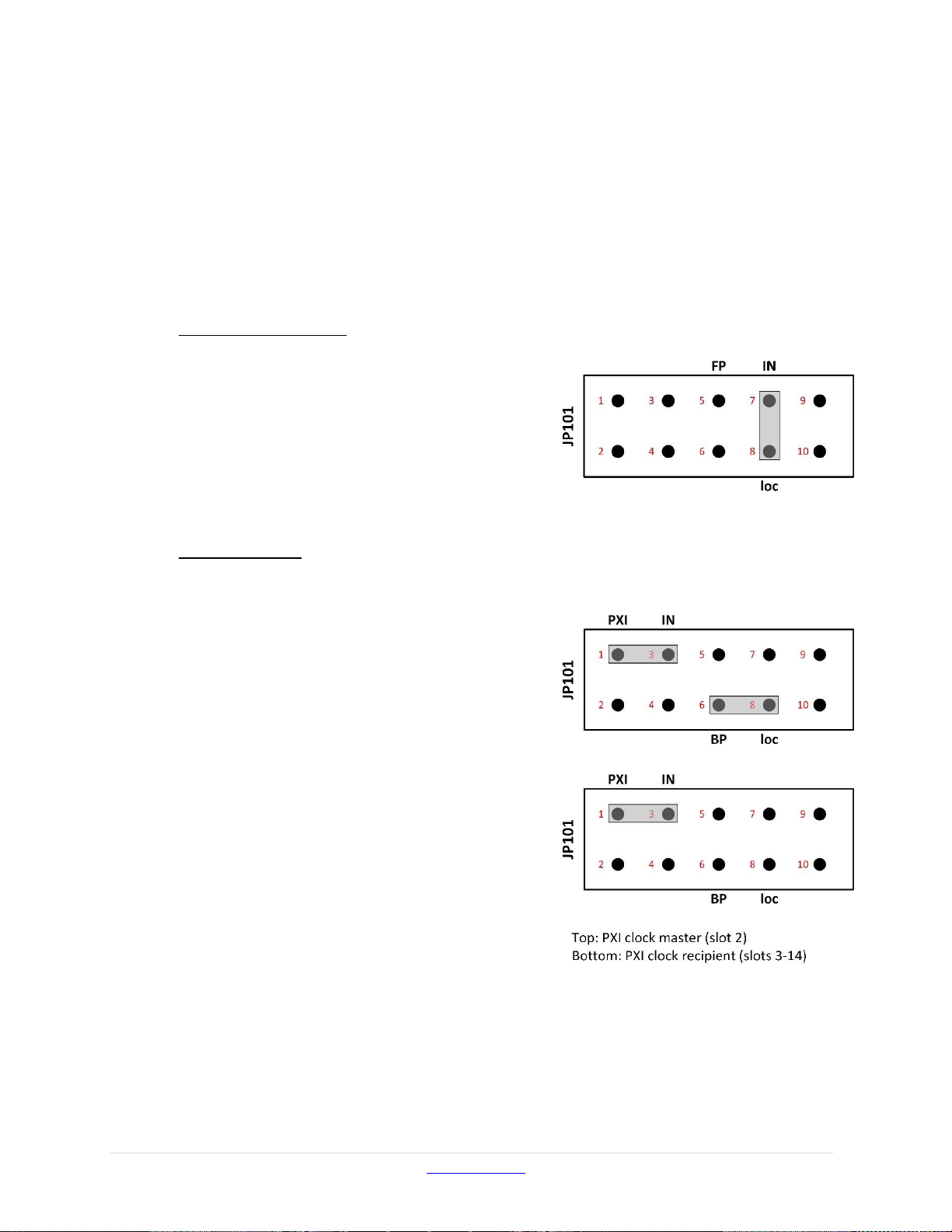

1.7.1.1 Individual Clock Mode

If only one Pixie-16 module is used in the

system, or if clocks between modules do not

need to be synchronized, the module(s) should

be set into individual clock mode. Connect pin

7 of JP101 (the clock input) with a shunt to pin

8 (loc – IN). This will use the 50 MHz local

crystal oscillator of the Pixie-16 module as the

clock source.

Figure 1-10: Pixie-16 individual clock mode.

1.7.1.2 PXI Clock Mode

The preferred way to distribute clocks among multiple Pixie-16 modules is to use the PXI

clock distributed on the backplane. This clock

is by default generated on the backplane and is

a 10MHz clock signal, which is then repeated

by a fan out buffer and connected to each crate

slot by a dedicated line with minimum skew

(equal trace length to each slot). Although the

10MHz is too slow to be a useful clock for the

Pixie-16, it can be overridden by a local clock

signal from a Pixie-16 module that is installed

in slot 2 through proper shunt settings on the

JP101.

A Pixie-16 module can be configured to be the

PXI clock master in slot 2 by connecting pins

6 and 8 (loc – BP) of the JP101. All modules,

including the clock master, should be set to

receive the PXI clock by connecting pin 1 and

3 on JP101 (PXI – IN). In this way, the 50

MHz clock from the Pixie-16 clock master is

distributed to all Pixie-16 modules through the

backplane with nearly identical clock phase.

Figure 1-11: Pixie-16 PXI clock mode.

One other advantage of the PXI clock mode over the daisy-chained clock mode, which will

be discussed next, is that except for the Pixie-16 master module, which has to be installed

in slot 2, other Pixie-16 slave modules can be installed in any other slot of the Pixie-16

crate. In contrast, when the daisy-chained clock mode is used, all Pixie-16 modules have

to be installed next to each other, i.e. no gap is allowed between modules.

Version 3.00 www.xia.com 23

Page 24

Pixie-16 User Manual August 21, 2018

1.7.1.3 Daisy-chained Clock Mode

A further option for clock distribution is to

daisy-chain the clocks from one module to

the other, with each module repeating the

clock signal and transmitting it to the

neighbor on the right. This requires one

master module, located in the leftmost slot of

the group of Pixie-16 modules. The master

module uses its local crystal oscillator as the

input and sends its output to the right (loc –

IN, out – right). Other Pixie-16 modules in

the crate should be configured as clock

repeaters by using the signal from the left

neighbor as the input and sending its output

to the right (left – IN, out – right). However,

as mentioned earlier, there must be no slot

gap between modules.

Figure 1-12: Pixie-16 daisy-chained clock mode.

1.7.1.4 Multi-Crate Clock Mode

In multi- crate systems, a global clock signal

can be distributed among these crates using

dedicated trigger and clock distribution

cards, i.e. the Pixie-16 Rear I/O trigger

modules, which are available from XIA.

An example of clock distribution between

two crates is illustrated below.

Installation of Pixie-16 Modules

Multiple Pixie-16 modules can be installed

in two 14-slot Pixie-16 crates, #1 and #2. For

clock distribution purpose, crate #1 is called

the Master crate, where the system-wide

global clock for all Pixie-16 modules is

originated, and crate #2 is called the Slave

crate, which receives the global clock from

the Master crate.

The Pixie-16 module installed in slot 2 of the

Master crate is designated as the System

Director Module, whose local 50 MHz

crystal oscillator acts as the source of the

system-wide global clock. The distribution

of the clock signal from the System Director

Module to all Pixie-16 modules in the 2-crate

system is done through the Pixie-16 Rear I/O

trigger modules.

Figure 1-13: Pixie-16 multi-crate clock mode.

Version 3.00 www.xia.com 24

Page 25

Pixie-16 User Manual August 21, 2018

Crate #

1

Slot # 2 3 … 13

14

Module

System Director Module /

Crate Master Module

Regular

Module

…

Regular

Module

Regular

Module

Crate #

2

Slot # 2 3 … 13

14

Module

Crate Master Module

Regular

Module

…

Regular

Module

Regular

Module

System Director Module

Connect pins 1 and 3, 4 and 6, 8 and 10.

Crate Master Module

Connect pins 1 and 3, 4 and 6.

Regular Module

Connect pins 1 and 3.

The Pixie-16 module installed in slot 2 of the Slave crate is called the crate Master module,

which is responsible for receiving the global clock from the Master crate and sending such

clock to all modules in that crate through length-matched traces on the backplane. The

System Director Module is also responsible for sending the global clock to all modules in

the Master crate. Therefore, it is also a crate Master module. Other modules in these two

crates are regular modules. Table 1-12 shows the different types of modules in a 2-crate

system.

Table 1-12 Pixie-16 Module Definitions in a 2-crate System

Clock Jumper (JP101) Settings on the Pixie-16 Modules

For all Pixie-16 modules in a 2-crate system to use the same global clock signal, the clock

jumper (JP101) in all modules should be set according to Table 1-13 and Figure 1-13.

Table 1-13 Pixie-16 Clock Jumper JP101 Settings in a 2-crate System

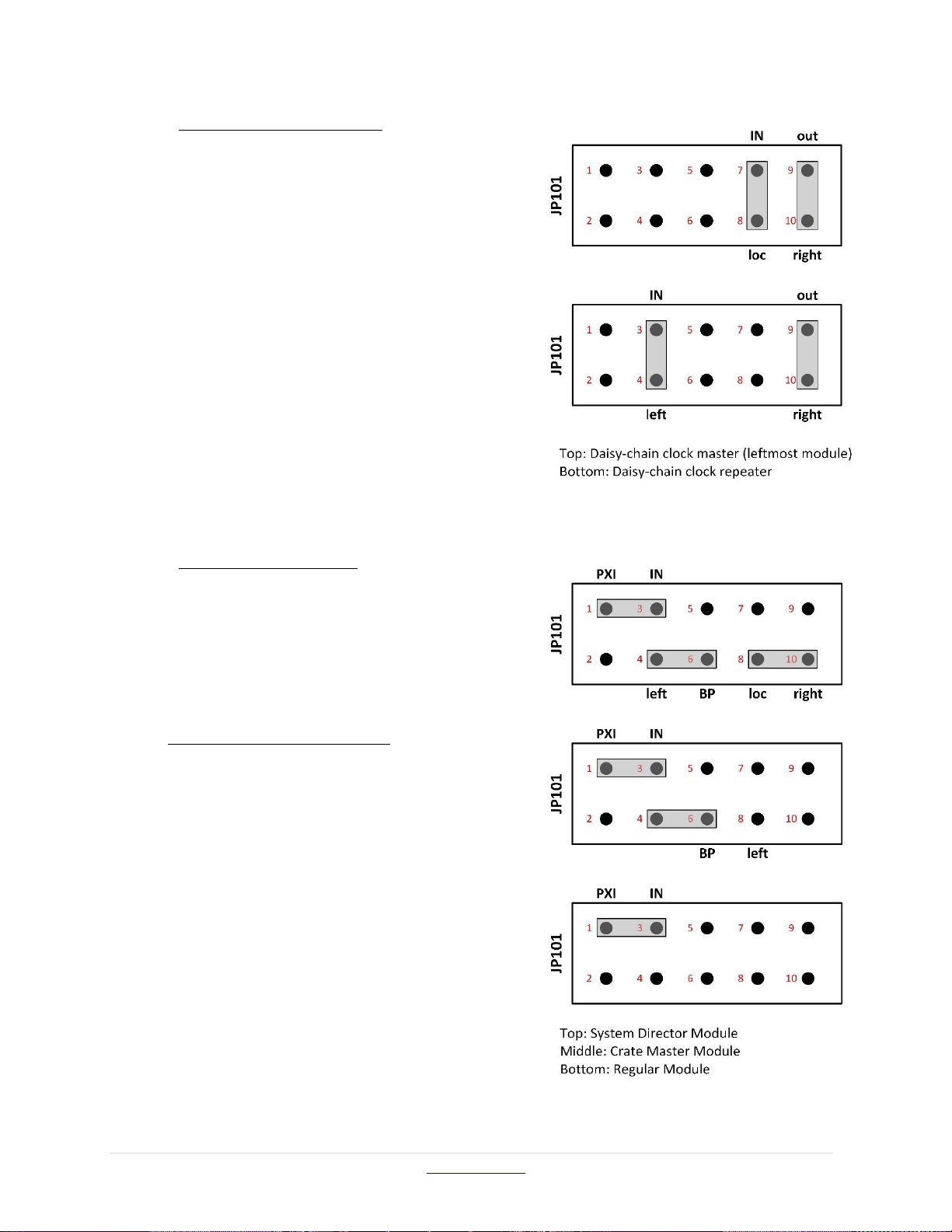

Cable Connections for Pixie-16 Rear I/O Trigger Modules

The Pixie-16 Rear I/O trigger modules are

installed at the rear side of each crate where a

6U card cage is installed. Figure 1-14 shows

a Pixie-16 Rear I/O trigger module is

installed directly behind either the Director or

the Master module, respectively, to share

clock, triggers, and run start or stop

synchronization signals among multiple

Pixie-16 crates. The rear of the backplane has

connectors J3, J4 and J5, but it does not have

J1 and J2, since it does not need to use

CompactPCI or PXI communication.

Typically the first slot at the rear of the

backplane with J3, J4, J5 connectors installed

is the slot where the Pixie-16 Rear I/O trigger

module should be installed. While installing

the module, please ensure the alignment of

top and bottom rails with the trigger module

to avoid damage to the backplane pins.

Figure 1-14: Pixie-16 rear I/O trigger modules.

Version 3.00 www.xia.com 25

Page 26

Pixie-16 User Manual August 21, 2018

J200

J201

J202

J203

J204

J205

J206

J207

J209

J208

Trigger

board #1

installed in

the rear

slot #2 of

Crate #1

Trigger

board #2

installed in

the rear

slot #2 of

Crate #2

J200

J201

J202

J203

J204

J205

J206

J207

J209

J208

Figure 1-15 shows the cable connections between two Pixie-16 rear I/O trigger modules

that are installed in two separate crates. All connection cables are Category 5 or 6 Ethernet

cables and shall have the same length to minimize clock phase difference between Pixie16 modules in the two crates.

Figure 1-15: Cable connections between two Pixie-16 rear I/O trigger modules.

Jumper Settings on the Pixie-16 Rear I/O Trigger Modules

Trigger module #1 is installed in the rear slot #2 of crate #1. As mentioned earlier, the rear

slot #2 is located at the back of the crate and is at the direct opposite side of the front slot

#2 of the crate. Care should be taken when installing the trigger module into the rear slot

#2 by avoiding bending any pins of the rear side of the backplane, since that could cause

the 3.3V pin to be shorted to neighboring ground pin and thus damage the whole backplane.

Please note pin numbering for all jumpers on the trigger module is counted from right to

left when facing the top side of the module, i.e. the backplane connectors J3 to J5 are on

the left (only exception is JP1, which is in vertical orientation and should be counted from

bottom to top). A tiny ‘1’ label is painted on the right hand side of the jumpers, indicating

pin 1. Figure 1-16 shows the pin ‘1’ in red boxes.

Figure 1-16: Pin numbering for the jumpers on the Pixie-16 rear I/O trigger module.

Version 3.00 www.xia.com 26

Page 27

Pixie-16 User Manual August 21, 2018

JP1

Connect pins 1 and 2 for “P16”

JP20

Connect pins 2 and 3, 6 and 7

JP40

Connect pins 2 and 3, 6 and 7

JP60

Connect pins 1 and 2, 7 and 8

JP21

Connect pins 2 and 3

JP41

Connect pins 2 and 3

JP61

Connect pins 1 and 2

JP100

Connect pins 2 and 3 (connect to J4)

JP101

Connect pins 2 and 3 (connect to J4)

JP102

Connect pins 2 and 3 (connect to J4)

JP103

Connect pins 2 and 3 (connect to J4)

JP104

Connect pins 2 and 3 (connect to J4)

JP105

Connect pins 2 and 3 (connect to J4)

JP1

Connect pins 2 and 3 for “loc”

JP20

Connect pins 1 and 2, 7 and 8

JP40

Connect pins 1 and 2, 7 and 8

JP60

Connect pins 2 and 3, 6 and 7

JP21

Don’t connect any pin

JP41

Don’t connect any pin

JP61

Connect pins 1 and 2

JP100

Connect pins 2 and 3 (connect to J4)

JP101

Connect pins 2 and 3 (connect to J4)

JP102

Connect pins 2 and 3 (connect to J4)

JP103

Connect pins 2 and 3 (connect to J4)

JP104

Connect pins 2 and 3 (connect to J4)

JP105

Connect pins 2 and 3 (connect to J4)

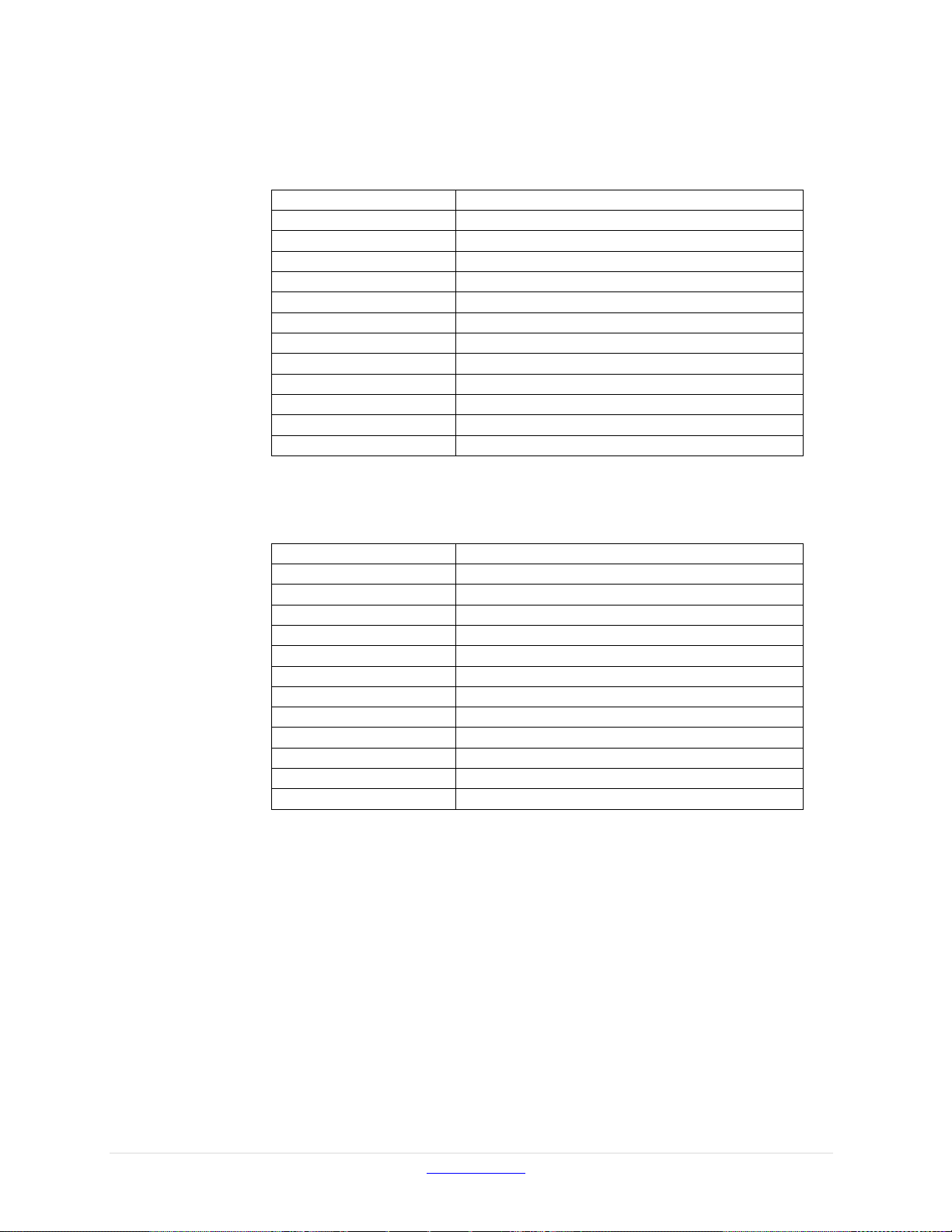

Table 1-14 shows the jumper settings of the Pixie-16 rear I/O trigger module #1 in a 2crate system.

Table 1-14 Pixie-16 Rear I/O Trigger Module #1’s Jumper Settings

Trigger module #2 is installed in the rear slot #2 of crate #2. Table 1-15 shows the jumper

settings of the Pixie-16 rear I/O trigger module #2 in a 2-crate system.

Table 1-15 Pixie-16 Rear I/O Trigger Module #2’s Jumper Settings

Version 3.00 www.xia.com 27

Page 28

Pixie-16 User Manual August 21, 2018

J200

J201

J202

J203

J204

J205

J206

J207

J209

J208

Trigger

board #1

installed in

the rear

slot #2 of

Crate #1

Trigger

board #2

installed in

the rear

slot #2 of

Crate #2

Trigger

board #3

installed in

the rear

slot #2 of

Crate #3

Trigger

board #4

installed in

the rear

slot #2 of

Crate #4

J200

J201

J202

J203

J204

J205

J206

J207

J209

J208

J200

J201

J202

J203

J204

J205

J206

J207

J209

J208

J200

J201

J202

J203

J204

J205

J206

J207

J209

J208

Figure 1-17: Cable connections among four Pixie-16 rear I/O trigger modules.

Please note, if there are a total of four crates, the cable connections among those four Pixie16 rear I/O trigger modules that are installed in those four separate crates should follow the

connection methods shown in Figure 1-17. For the jumper settings on the Pixie-16 rear I/O

trigger modules, trigger module #1 and #2 should use the same jumper settings as those in

the trigger module #1 and #2 of the 2-crate system (Table 1-14 and Table 1-15),

respectively, whereas trigger module #3 and #4 should use the same jumper settings as

those in trigger module #2 (Table 1-15).

1.7.2 Trigger Distribution and Run Synchronization

In addition to distributing the global clock signal, the Pixie-16 rear I/O trigger module can

also share global triggers and run synchronization signals. The global trigger signals

include the global validation trigger and global fast trigger, plus the Pixie-16 FPGA data

storage buffers’ full flag signal. The run synchronization signals include synchronous run

start and stop signals that can be shared among multiple crates.

Version 3.00 www.xia.com 28

Page 29

Pixie-16 User Manual August 21, 2018

In order to enable the distribution of such global triggers and run synchronization signals,

certain Pixie-16 parameters have to be set properly. The parameter that controls the trigger

distribution and run synchronization is the Module Control Register B (ModCSRB).

ModCSRB is a 32-bit parameter with each of 32 bits controlling different operation modes

of the Pixie-16 module.

For the System Director module that is installed in the Master crate, bits 0, 4, 6 and 11 of

ModCSRB should be set to 1 (checked & enabled), as illustrated in Figure 1-18.

Figure 1-18: ModCSRB bit settings for the System Director Module in the Master crate.

For the Crate Master module that is installed in the Slave crate, bits 0, 6 and 11 of

ModCSRB should be set to 1 (checked & enabled), as illustrated in Figure 1-19.

Figure 1-19: ModCSRB bit settings for the Crate Master Module in the Slave crate.

For the General modules that are installed in both the Slave crate and Master crate, bit 11

of ModCSRB should be set to 1 (checked & enabled), as illustrated in Figure 1-20.

Figure 1-20: ModCSRB bit settings for the General Modules in both Master and Slave crates.

Version 3.00 www.xia.com 29

Page 30

Pixie-16 User Manual August 21, 2018

Use studs

at both

sides of the

crate to lift

it up in

order to

facilitate

air flow

from the

bottom.

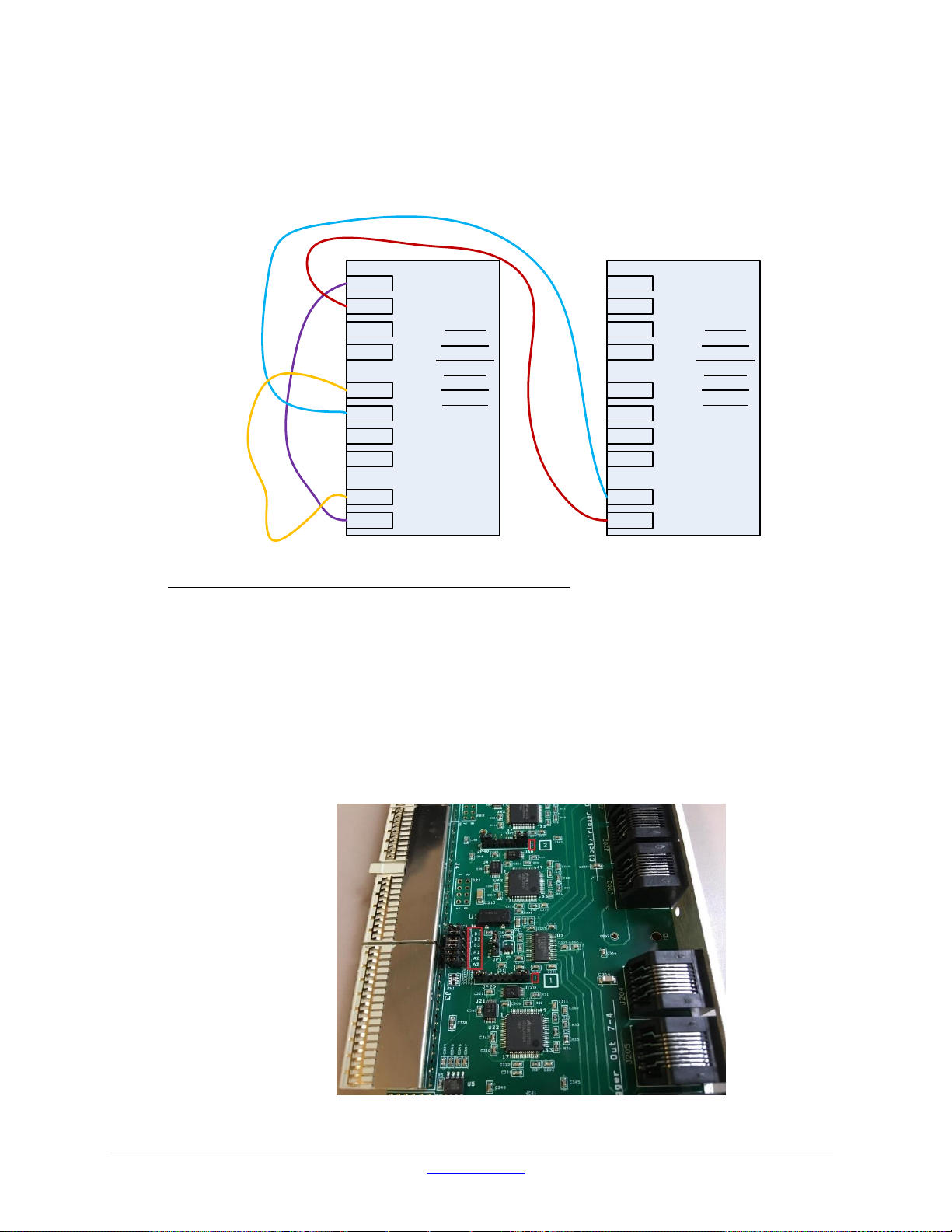

2 Installation

2.1 Hardware Setup

A Pixie-16 system typically consists of a custom 14-slot 6U PXI crate, one or more Pixie16 modules, a crate controller, and accessories. The system is shipped out of the factory in

a large wooden box. We recommend proper storage of this wooden box after unpacking,

just in case there is a need to return the crate to factory for service or repair (the nails that

were used to seal the box are reusable).

When unpacking the Pixie-16 system, please be sure to collect the following items from

the wooden box:

1) The 14-slot 6U PXI crate

2) Power cord for the crate as well as VME version manual for the crate

3) Pixie-16 module(s)

4) Crate controller cards to be installed in the crate’s slot #1 and computer’s PCI slot

5) BNC-to-SMB cables

6) 2mm shunts for changing jumper settings on the Pixie-16 modules

A picture of a typical Pixie-16 digital data acquisition system is shown in Figure 2-1.

Figure 2-1: A typical Pixie-16 digital data acquisition system.

The Pixie-16 modules must be operated in this custom 6U CompactPCI/PXI crate which

provides high currents at specific voltages that are not included in the CompactPCI/PXI

Version 3.00 www.xia.com 30

Page 31

Pixie-16 User Manual August 21, 2018

standard. Of the 5 backplane connectors available in a 6U format, the lower two (J1, J2)

are defined by the CompactPCI/PXI standard, providing basic supply voltages, PCI host

I/O, and basic trigger connections. Pixie-16 modules follow this standard and are thus

compatible with any CompactPCI/PXI module that uses these two connectors only. The

upper three connectors (J3, J4, J5) are undefined in the CompactPCI/PXI standard. On

Pixie-16 modules, these connectors are used for custom power supplies with high currents

(1.8V, 5.5V, 3.3V) and for extended trigger distribution. Third party modules or crate using

the upper three connectors are most likely not compatible with Pixie-16 modules.

The AC power cords that come with the crates have North America NEMA 5-15 style

power plugs on one of the two ends (the other end plugs into the back of the crate) with

two flat parallel blades and one ground pin (one example of such power plug is shown in

Figure 2-2 top). For non-North America customers, it might be necessary to either find a

power socket that is compatible with the NEMA 5-15 style power plugs, or replace the

NEMA 5-15 style power plug with the one that is the standard in the customer’s country.