Xerox

Data

Systems

XIDlS

SIGMA 9 COMPUTER

Reference Manual

XoS

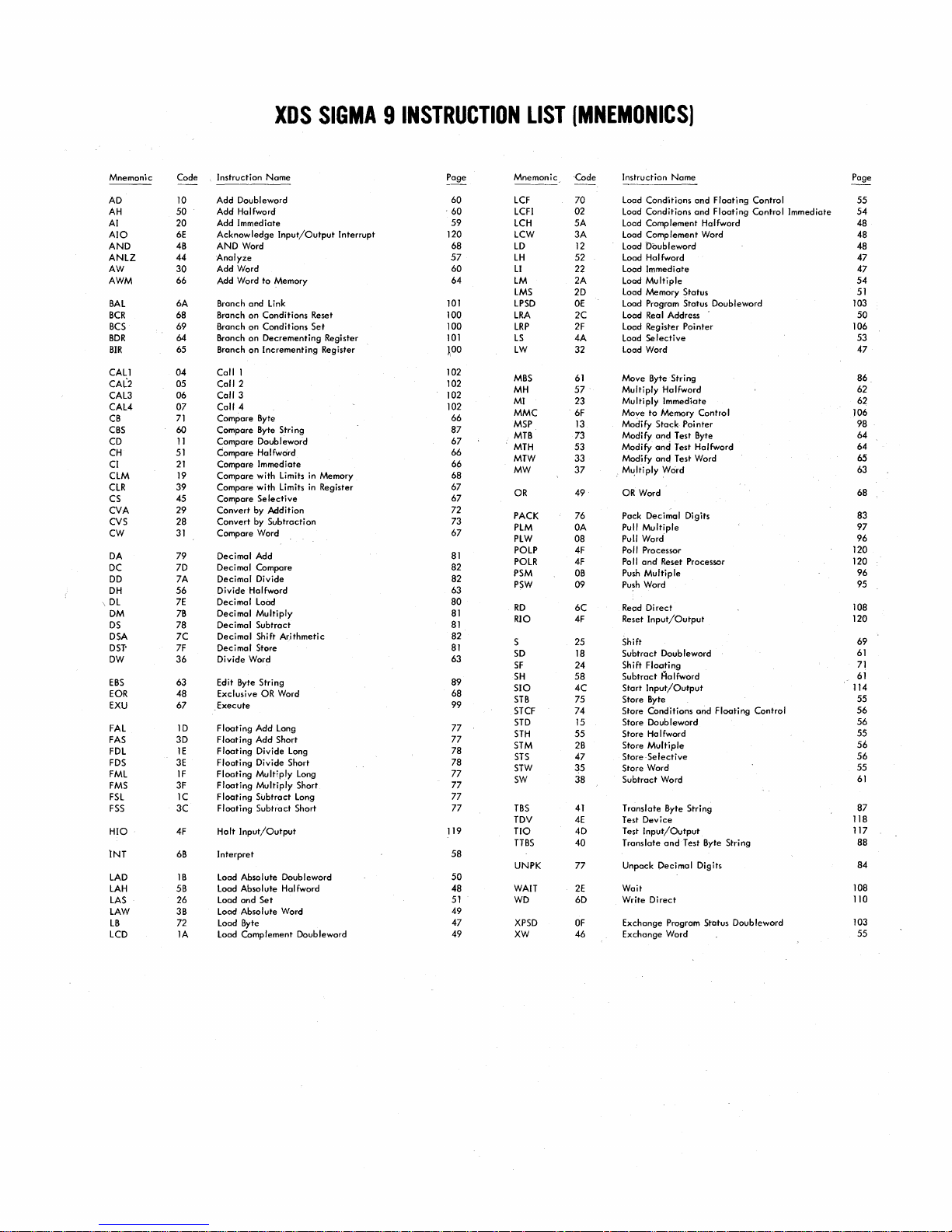

SIGMA

9

INSTRUCTION

LIST

(MNEMONICS)

Mnemonic Code

AD 10

AH

AI

AIO

AND

ANLZ

AW

AWM

BAL

BCR

BCS

BDR

BIR

CAll

CAL2 05

CAL3

CAL4

CB

CBS

CD

CH

CI

CLM 19

CLR

CS

CVA

CVS

CW

DA

DC 7D

DD

DH

•

DL

DM

DS

DSA

DST'

DW

EBS

EOR

EXU

FAL

FAS

FDL

FDS

FML

FMS

FSL

FSS

HIO

lNT

LAD

LAH

LAS

LAW

LB

LCD

Instruction

Add

Add Halfword

50

Add Immediate

20

6E

Acknowledge

4B

AND

44

Analyze

Add Word

30

66

Add Word

6A

Branch

Branch

68

69

Branch

Branch

64

65 Branch

Call

04

Call

06

Call

07

Call

71

Compare Byte

Compare Byte String

60

11

Compare Doubleword

51 Compare Halfword

21

Compare Immediate

Compare

39

Compare

45

Compare

29

Convert

Convert

28

Compare Word

31

79

Decimal

Decimal Compare

Decimal

7A

Divide

56

Decimal Load

7E

Decimal

7B

Decimal

78

Decimal Shift

7C

7F

Decimal

Divide

36

Edit Byte String

63

48

Exclusive OR Word

Execute

67

ID

Floating

3D

Floating

Floating

IE

3E

Floating

Floating

IF

Floating

3F

lC

Floating

Floating

3C

4F

Halt

Interpret

6B

Load Absolute Doubleword

1B

5B

Load

26

Load

Load Absolute Word

3B

Load Byte

72

Load Complement Doubleword

lA

Name

Doubleward

Input/Output

Word

to

Memory

and

link

on

Conditions

on

Conditions

on

Decrementing

on

Incrementing

1 102

2 102

3 102

4

with

Limits in Memory

with

Limits in Register

Selective

by

Addition

by

Subtraction

Add

Divide

Halfword

Multiply

Subtract

Arithmetic

Store

Word

Add Lang

Add Short 77

Divide Long

Divide

Multlply

Multiply

SiJbtract Long

Subtract

Input/Output

Absolute

Halfword

and

Set

Interrupt

Reset

Set

Register

Register

Short

Long

Short 77

Short

~age

60

'

60

59

120

68

57

60

64

101

100

100

101

JOO

102

66

87

67

66

66

68

67

67

72

73

67

81

82

82

63

80

81

81

82

81

63

89

68

99

77

78

78

77

77

77

119

58

50

48

51

49

47

49

Mnemonic

LCF

LCFI

LCH

LCW

LD

LH

LI

LM

LMS

LPSD

LRA

LRP

LS

LW

MBS

MH

MI

MMC 6F

MSP

MTB

MTH

MTW

MW

OR

PACK

PLM

PLW

POLP

POLR

PSM

PSW

RD

RIO 4F

S

SD

SF

SH

SIO

STB

STCF

STD

STH

STM

STS

STW

SW

TBS

TDV

TIO

HBS

UNPK 77 Unpack Decimal Digits

WAIT

WD

XPSD

XW

~ode

70

02

5A

3A

12

52

22

2A

2D

OE

2C

2F Load Register

4A Load

32

61

57

23

13

73 Modify

53

33

37

49

76

OA

08

4F Poll Processor

4F Poll

OB

09

6C

25 Shift

18

24

58

4C

75

74

15 Store Doubleword

55

2B

47

~5

38

41

4E

4D Test

40

2E

6D

OF

46

Instruction

Load

Load

Load

Load

Load'Doubleword

Load Halfword

Load Immediate

Lood

Load Memory

Load Program Status Doubleword 103

Load Rea I Address

Load Word

Move Byte String

Multiply

Multiply

Move

Modify

Modify

Modify

,

M~ltiply

OR Word

Pack Decimal Digits

Pull

Pull Word

Push

Push Word

Read

Reset

Subtract

Shift

Subtract

Start

Store Byte

Store

Store Ha I fword

Store

Store

Store Word

Subtract

Translate

Test

Translate

Wait

Write

Exchange Program Status Doubleword

Exchange Word

Name

Conditions

Conditions

Complement

Complement

Multiple

Selective

Multiple

and

Multiple

Direct

Input/Output

Floating

Input/Output

Conditions

Multiple

,Selective

Device

Input/Output

ond

and

Halfword

Word

Status 51

Pointer

Halfword

Immedi-ate

to

Memory Control 106

Stack

Pointer

and

Test Byte

and

Test Halfword

and

Test Word

Word

Reset Processor

Doubleword

Ralfword

and

Word

Byte String

and

Test Byte String

Direct

Floating

Floating

Floating

Control

Control

Control

Immediate

Page

55

54

48

48

48

47

47

54

50

106

53

47

86

62

62

98

64

64

65

63

68

83

97

96

120

120

96

95

108

120

69

61

71

61

114

55

56

56

55

56

56

55

61

87

118

117

88

84

108

110

103

55

Price:

$6.50

XDS

SIGMA

REFERENCE

FIRST

October

9

COMPUTER

MANUAL

EDITION

90 17 33A

1970

Xerox

© 1970, Xerox Data Systems, Inc.

Data

Systems/701 South Aviation Boulevard/EI Segundo,

California

Printed

90245

in U.S.A.

RELATED

PUBLICATIONS

Title

XDS

Sigma Glossary of Computer Terminology

XDS

Symbol/Meta-Symbol Reference Manual (Sigma

XDS

Macro-Symbol Reference Manual (Sigma

5/7

Computers)

5/7

Computers)

Publ

ication No.

90 09

90

90

57

0952

15

78

ii

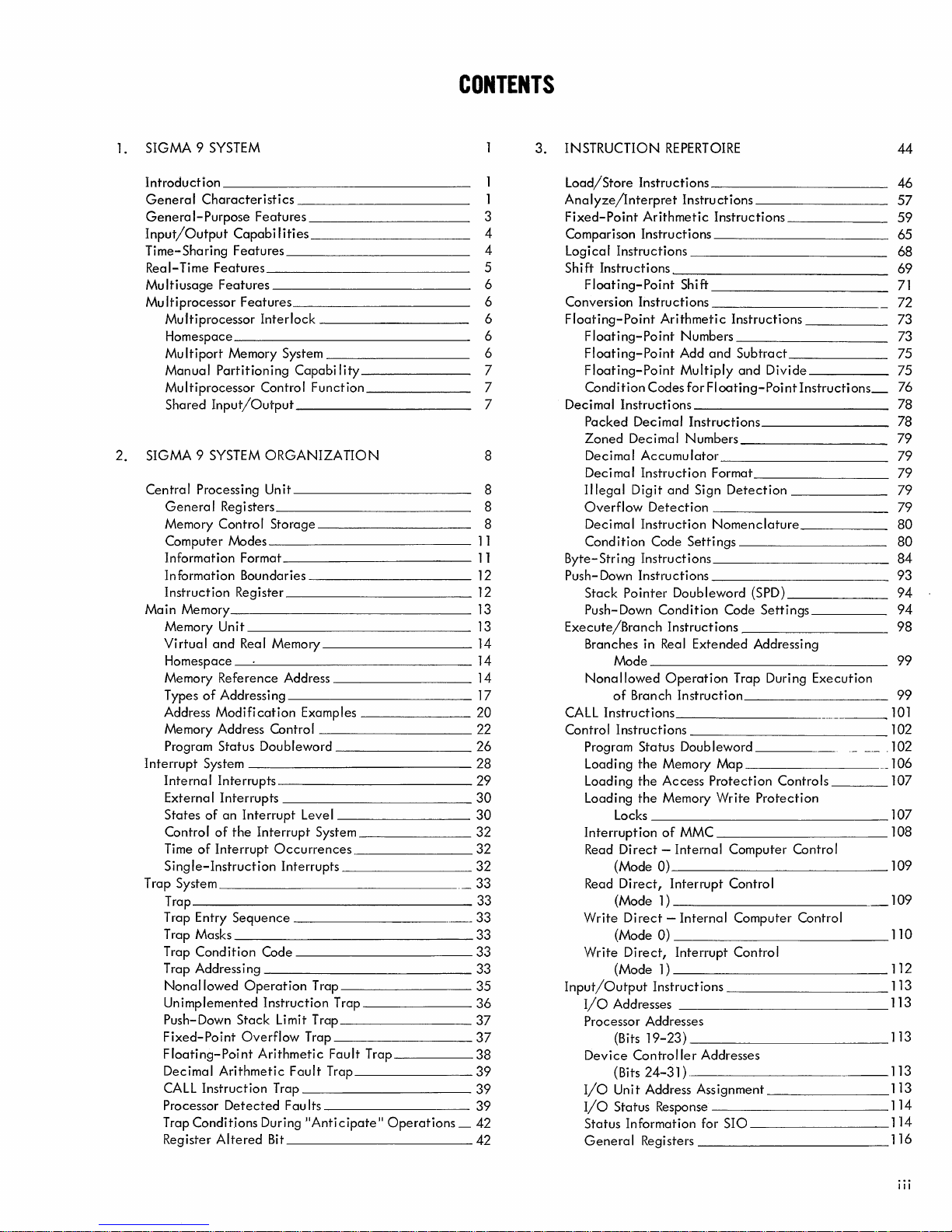

CONTENTS

SIGMA

l.

Introduction

General

General-Purpose

Input/Output

Time-Sharing

RealMultiusage

Multiprocessor

Multiprocessor

Homespace

Multiport

Manual

Multiprocessor

Shared

SIGMA

2.

Central

General

Memory

Computer

Information

Information

Instruction

Main

Memory

Virtual

Homespace

Memory

Types

Address

Memory Address Control

Program

Interrupt

Internal

Externa I

States

Control

Time

Single-Instruction

Trap System

Trap

T

rap

Trap Masks

Trap

Trap Addressing

Nonallowed

Unimplemented

Push-Down

Fixed-Point

Floating-Point

Decimal

CALL

Processor

Trap

Register

9 SYSTEM

Characteristics

Capabi I ities

Features

Time

Features

Features

Memory System

Partitioning

Input/Output

9 SYSTEM

Processing

Registers

Control

Modes

Memory

Unit

and

Reference

of

Addressing

Modification

Status

System

Interrupts

Interrupts

of

an

of

the

of

Interrupt

Entry

Sequence

Condition

Arithmetic

Instruction

Detected

ConditIons

Altered

Features

Features

Interlock

Capabi

Control

ORGANIZA

Un

Format

Boundaries

Register

Real Memory

Doubleword

Interrupt

Interrupt

Code

Operation

Instruction

Stack

Overflow

Arithmetic

During HAnti cipateJl

Function

it

Storage

Address

Examples

Level

System

Occurrences_

Interrupts

Trap

Limit Trap

Trap

Fault

Trap

Fau Its

Bit

lity

nON

Trap

Fault

Trap

Trap

Operations

3

4

4

5

6

6

6

6

6

7

7

7

8

8

8

8

11

11

12

12

13

13

14

14

14

17

20

22

26

28

29

30

30

32

32

32

__

33

33

_______

33

33

33

33

35

36

37

37

38

39

39

39

_ 42

42

3.

INSTRUCTION

1

1

Load/Store

Analyze/Interpret

Fixed-Point

Comparison

Logical

Shift

Byte-String

Push-Down

Execute/Branch

CALL

Control

Input/Output

Instructions

Instructions~

Floating-Point

Zoned

Decimal

Decimal

Illegal

Overflow

Decimal

Condition

Stack

Push-Down

Branches in

Mode

Nonallowed

of

Instructions

Instructions

Program Status

Loading

Loading

Loading

Locks

Interruption

Read

(Mode 0)

Read

(Mode

Write

(Mode

Write

(Mode

I/O

Addresses

Processor Addresses

(Bits

Device

(Bits

I/O

Unit

I/O

Status Response 114

Status

General

REPERTOIRE

Instructions

Arithmetic

Instructions

Decimal

Accumulator

Instruction

Digit

Detection

Instruction

Code

Instructions

Instructions

Pointer

Condition

Real

______________

Branch

the

Memory

the

Access

the

Memory

_______________

of

Direct -Internal

__________

Instructions

____________

____________

Shift

__________

Numbers

Format

and

Sign

__________

Nomenclature

Settings

__________

__________

Doubleword

Instructions

Extended

Operation

Instruction

Doubleword

Protection

MMC

____________

Direct,

Interrupt

1)

_________________

Direct -Internal

0)

____________

Direct,

Interrupt

1)

____________________

Instructions

19-23)

___________

Controller

Addresses

24-31)---

Address Assignment

Information

Registers

for

_____________

________

Instructions

__________

________

__________

________

Detection

_________

(SPD)

Code

Settings

________

Addressing

Trap During

_________

Map

Write

Protection

Computer

Control

Computer

Control

__________

SIO

_____

_____

_____

_____

____

Execution

Controls

Control

Control

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

__

_________

______

_

_

_

_

__

44

99

99

101

102

102

106

107

107

108

109

109

110

112

113

113

113

113

113

114

116

iii

INPUT/OUTPUT OPERATIONS

4.

Operational Command Doublewords

Order

Memory

Flags

Byte

Control Command Doublewords

OPERATOR

5.

Processor Contro I Pane I

Contro I Mode

POWER

MEMORY

SYS

I/O

LOAD

UNIT

SENSE

NOT

HALT

WAIT

RUN

Program Status Doubleword

INSERT

CPU

INTERRUPT

ADDRESS

SELECT

DISPLA

INSTR

DISPLAY

DISPLAY

FORMAT

DATA

STORE

COMPUTE

Maintenance Controls

Alarm

Margins

PHASES

CLOCK

SNAP

MEMORY

OVERRIDE

SCAN

EXT

Operating Procedures

Loading Operation

Fetchi

Byte

Address 123 (USASCII)

Count

CONTROLS 127

CLEAR

RESET

RESET

ADDRESS

NORMAL

RESET

STOP

ADDRESS

Y (switch)

ADDR

(Indicator) 132

FORMAT

SEL

MODE

MODE

MODE

DIO

ng

and Storing Procedure 137

APPENDIXES

REFERE

NCE

A.

XDS

XDS

TABLES

Standard

Standard Character Sets

Symbols

and Codes

122

123

123

123

125

125

127 Hexadecimal-Decimal Fraction Conversion

127

·128

128

128

128

128

128

128

128

128

129 Timing Considerations

129 Effects of Memory Interference

129 Effects of Indexing

130 Effects of Indi rect Addressi

130

130

130

131

131

131

132

132

132

132

132

133

133

133

133

133

133

134

134

134

135

135

135

138

138

138

Contro I Codes

Special Code Properties

XDS

Standard 8-Bit Computer· Codes

XDS

Standard 7-Bit

XDS

Standard Symbol-Code Correspondences

Hexadecimal Arithmetic 144

Addition Table

Multiplication Table

Table of Powers

Table of Powers

Hexadecimal-Decimal Integer Conversion

Table of Powers

Mathematical

SIGMA 9 INSTRUCTION

B.

INSTRUCTION TIMING

C.

SYSTEM

D.

System Maintainabi I ity Features

GLOSSARY OF

E.

RELIABILITY

CPU

Features 167

Main Memory Features

Multiplexor

(MIOP)

High-Speed

Features

Communi

of

of

of

Two

Constants 156

Input/Output

Features

RAD

I/O

SYMBOLIC

cation Codes

Sixteen

Ten16

AND MAINTAINABILITY 166

10

LIST

Processor

Processor (HSRIOP)

TERMS

(EBCDIC)

ng

ILLUSTRATIONS

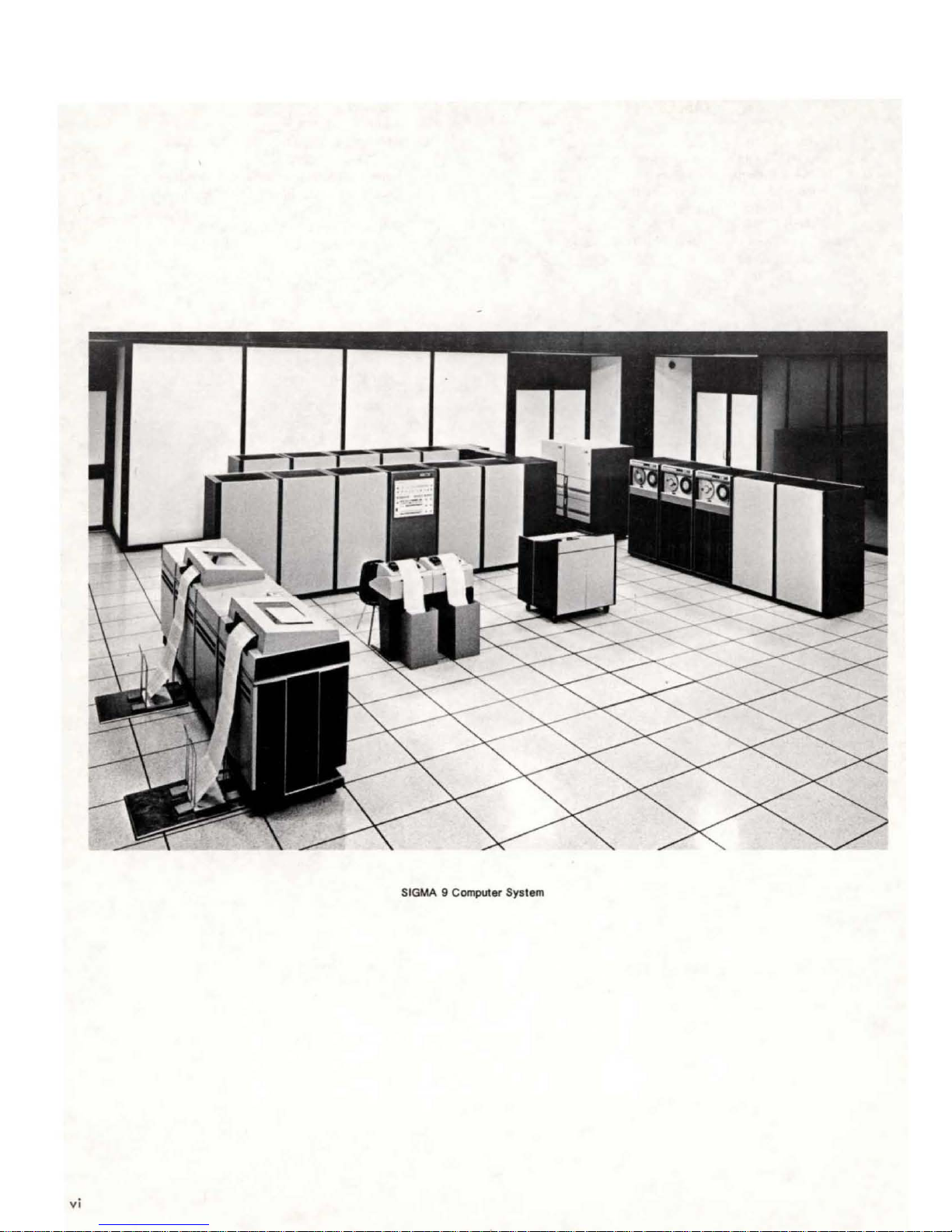

SIGMA 9 Computer System

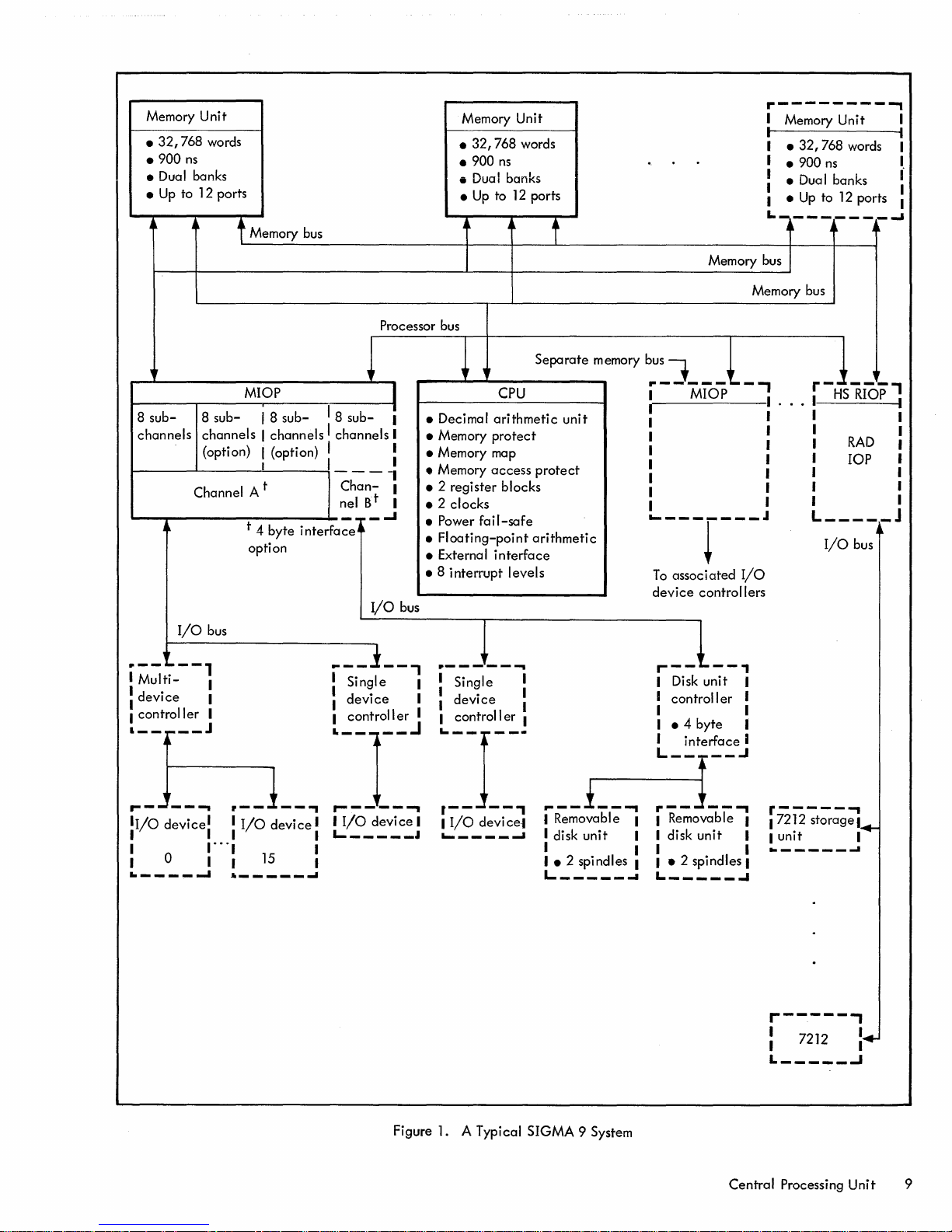

A Typical SIGMA 9 System 9

l.

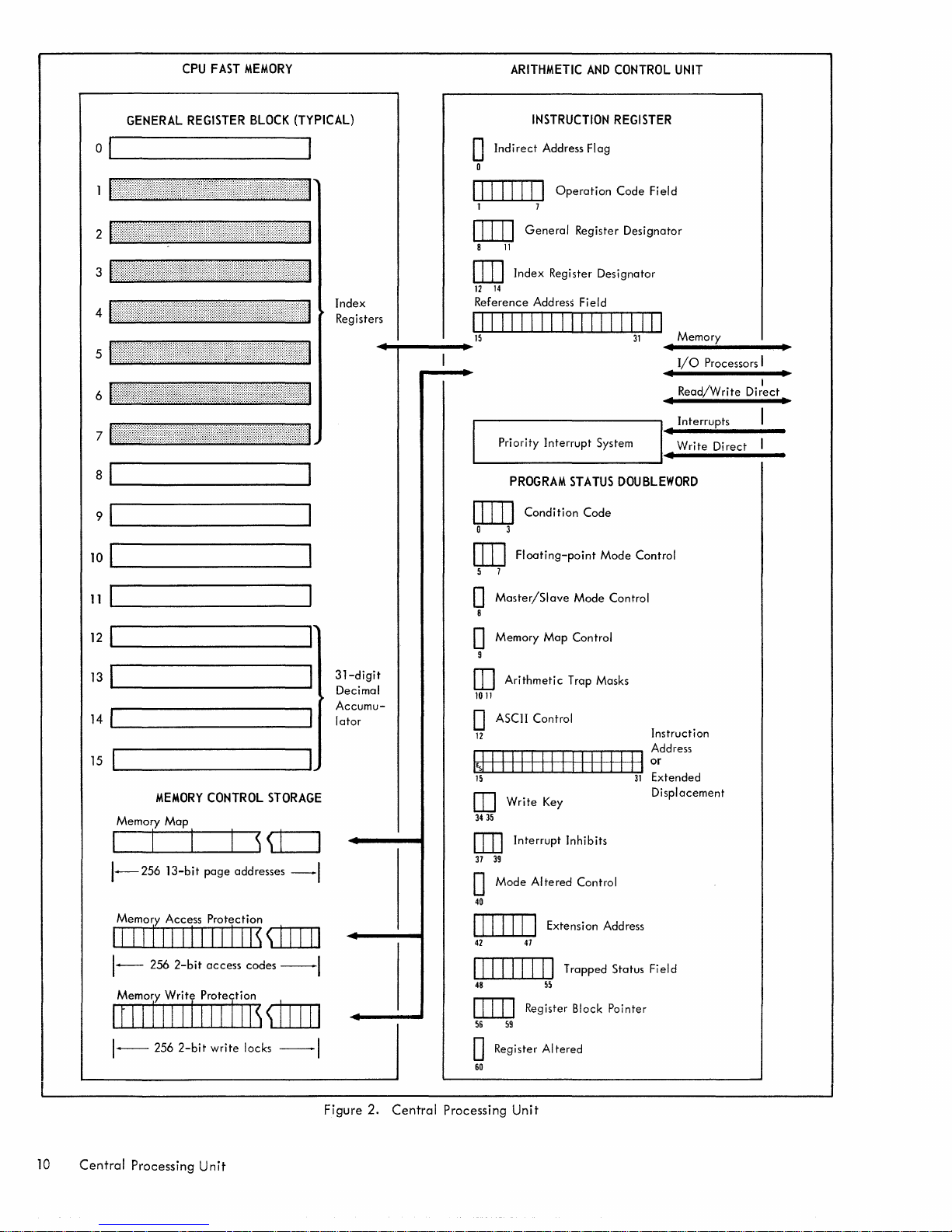

Central Processing Unit

2.

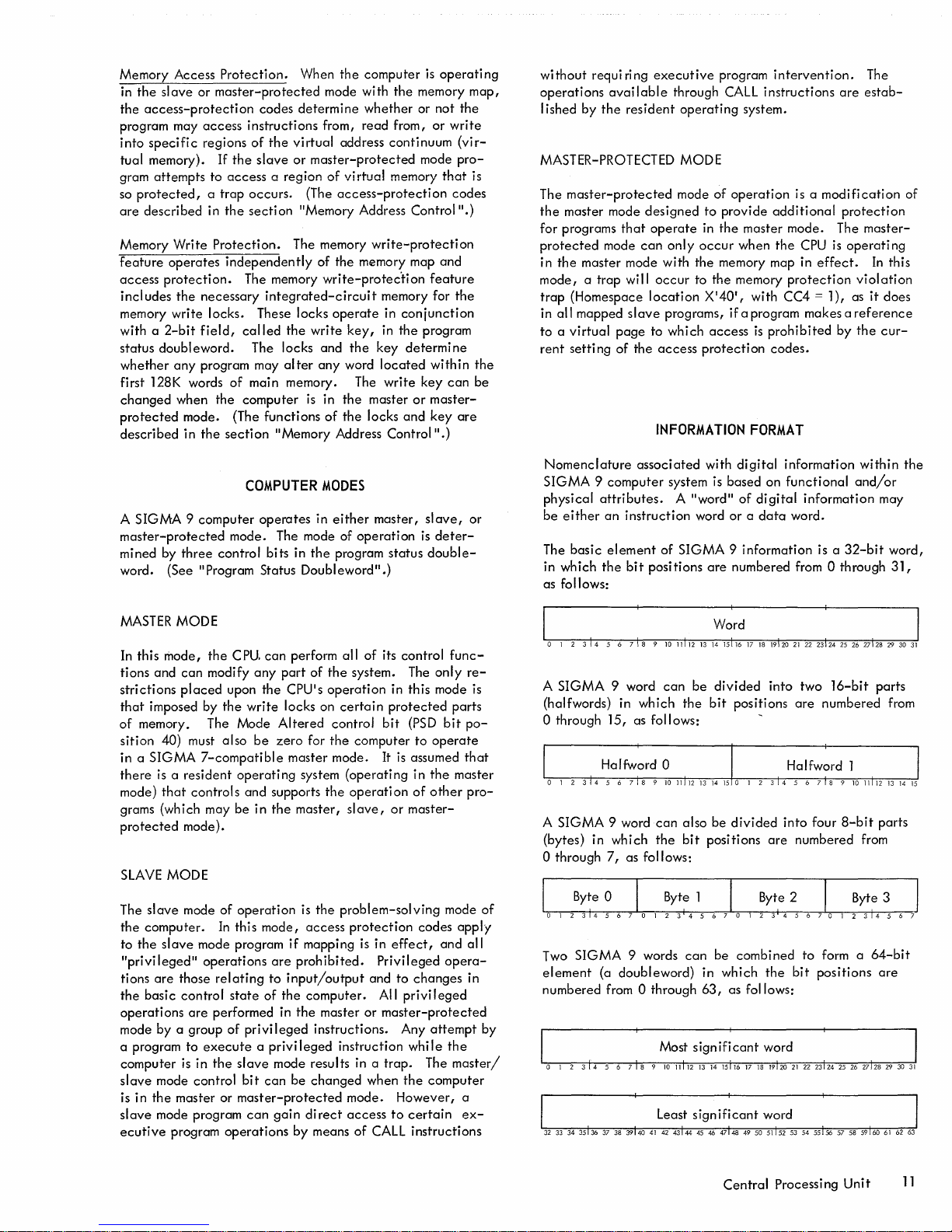

Information Boundaries

3.

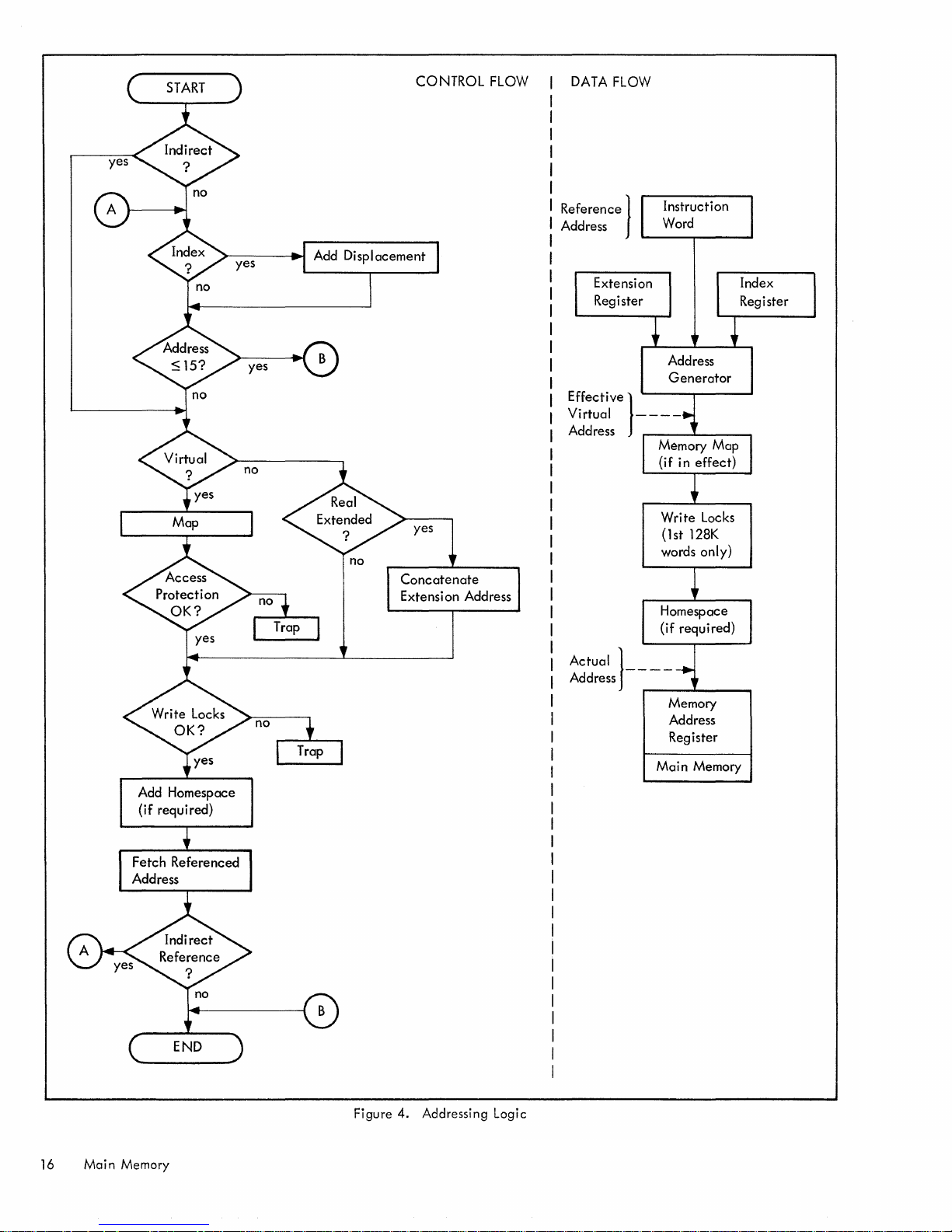

Addressing Logic

4.

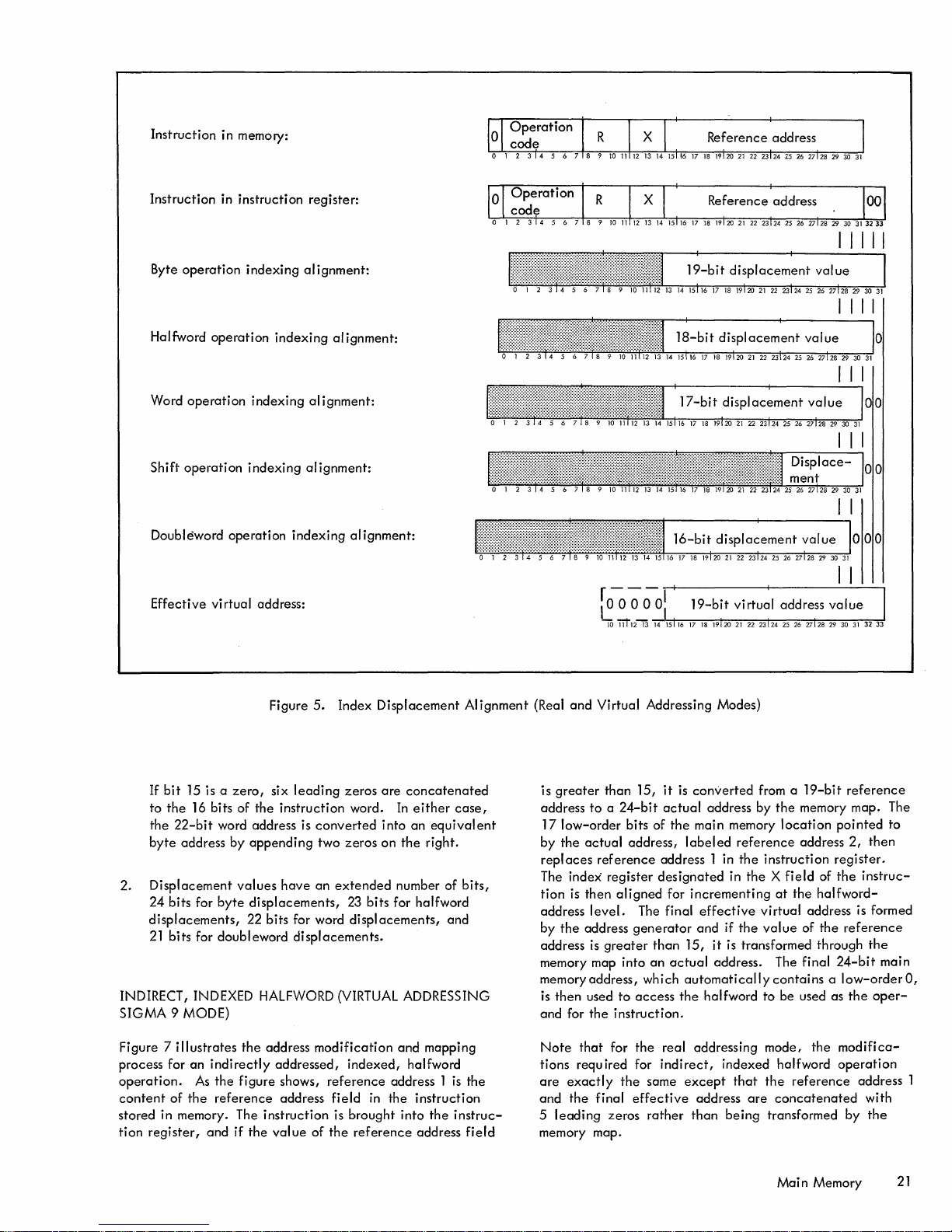

Index Displacement

5.

Virtual Addressing Modes)

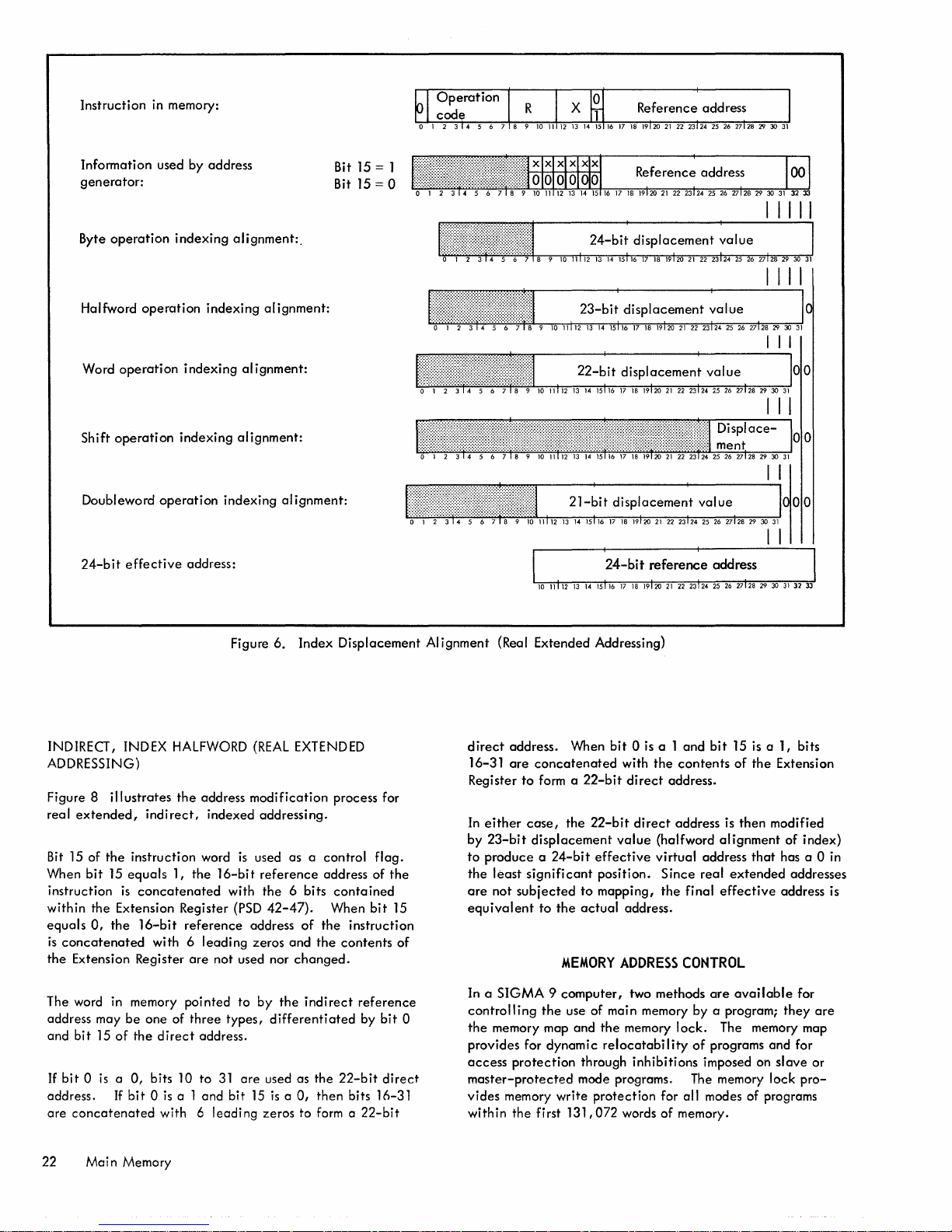

Displacement

Index

6.

Addressing}

Generation of

7.

Virtual Addressing (SIGMA 9 Mode)

Generation of Effective

8.

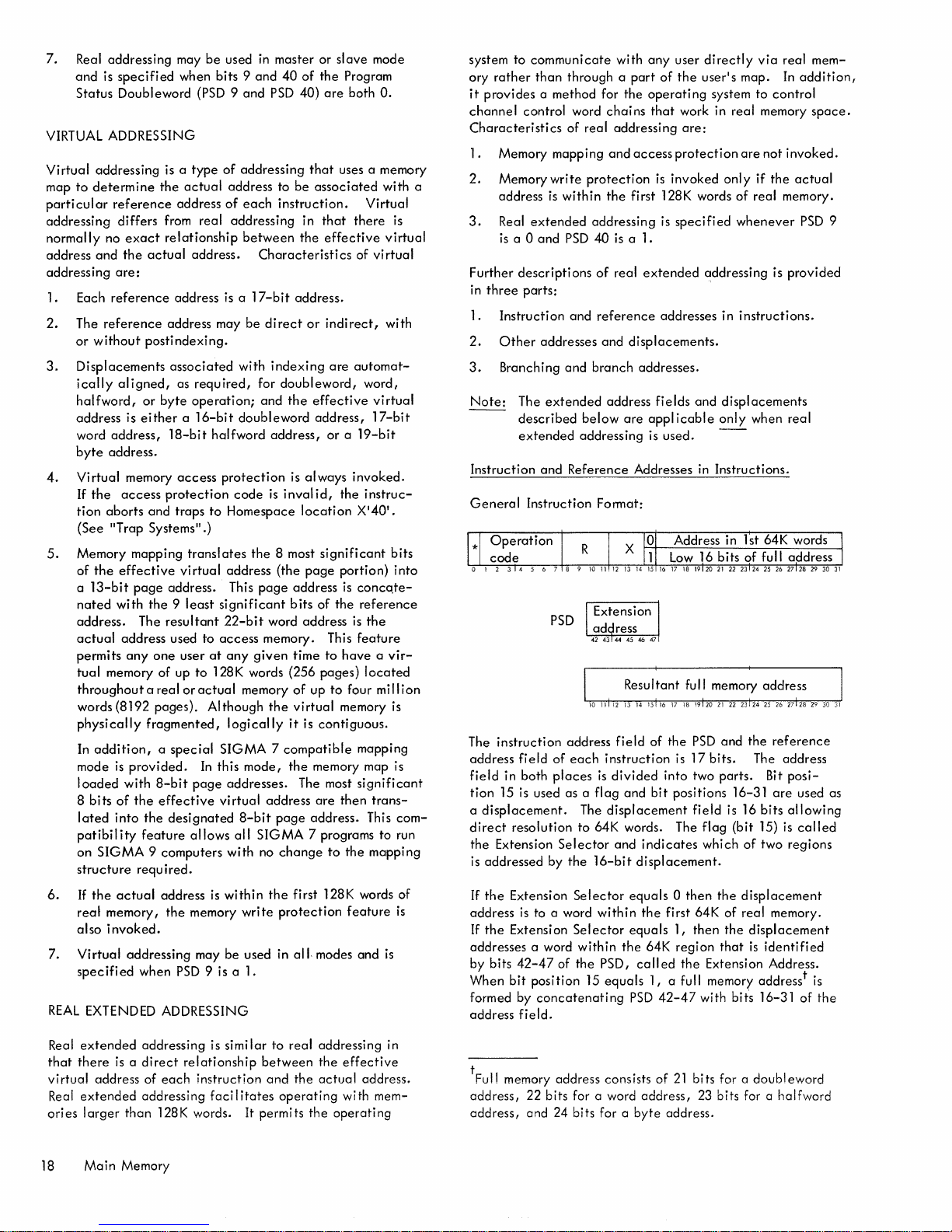

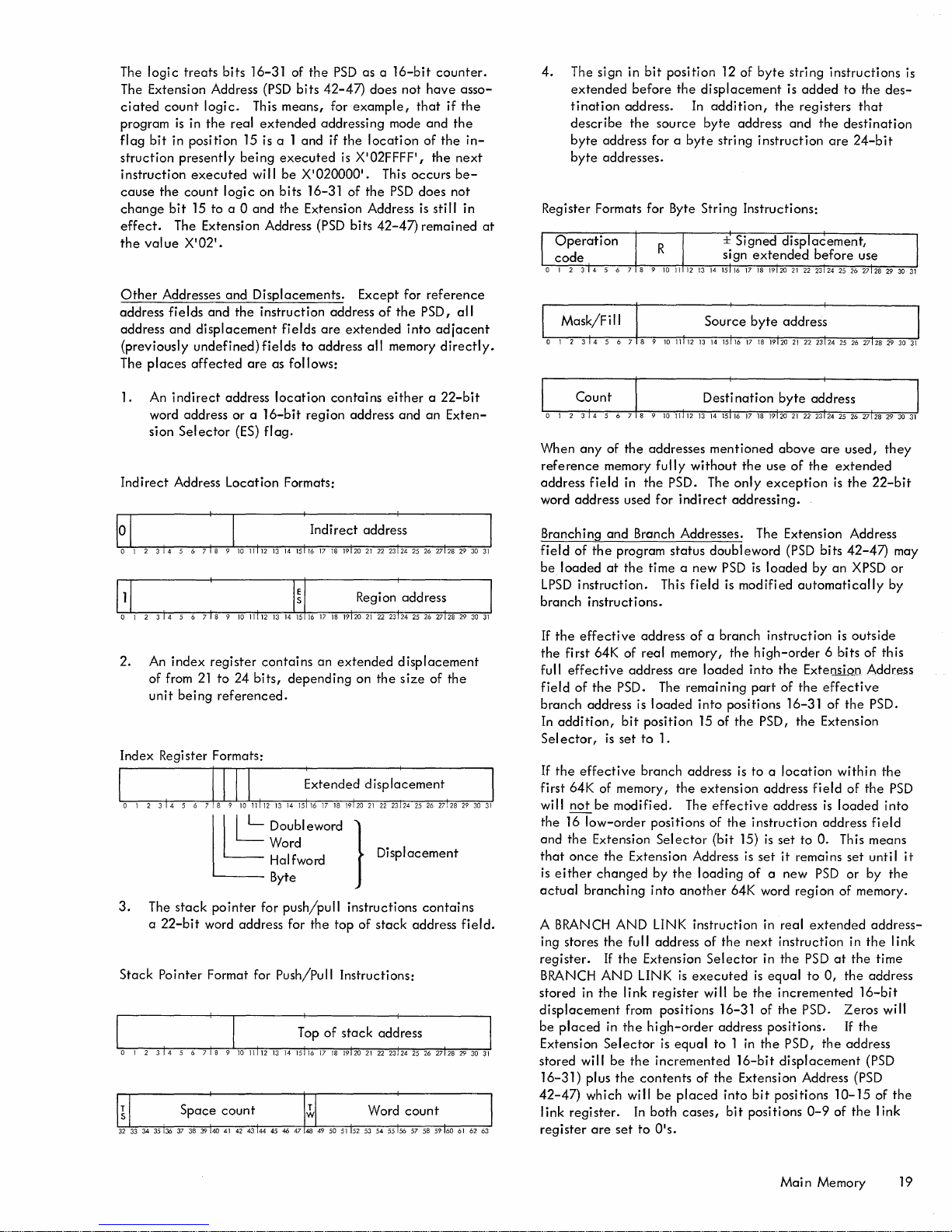

Extended Addressi

Interrupt

9.

Operational

10.

Processor Control Panel 127

11.

Priority Chain

AI

ignment (Real and

AI

ignment

Actual Memory Addresses,

ng

States of an Interrupt Level

{Real

Extended

Virtual Address,

__

__

Table_146

Table_152

Real

138

138

139

139

140

144

144

145

145

156

157

158

158

158

158

158

166

169

169

170

171

vi

10

12

16

21

22

23

24

29

31

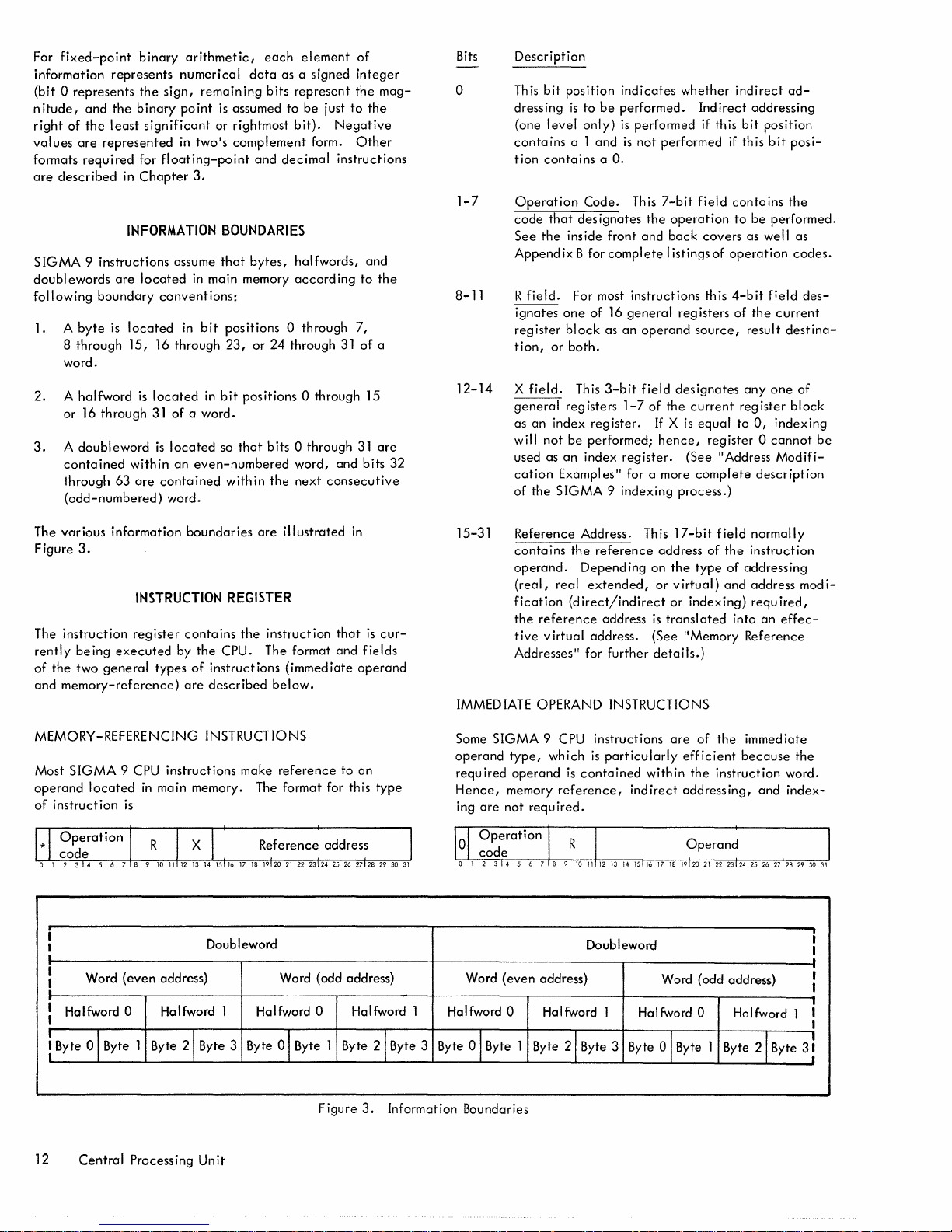

iv

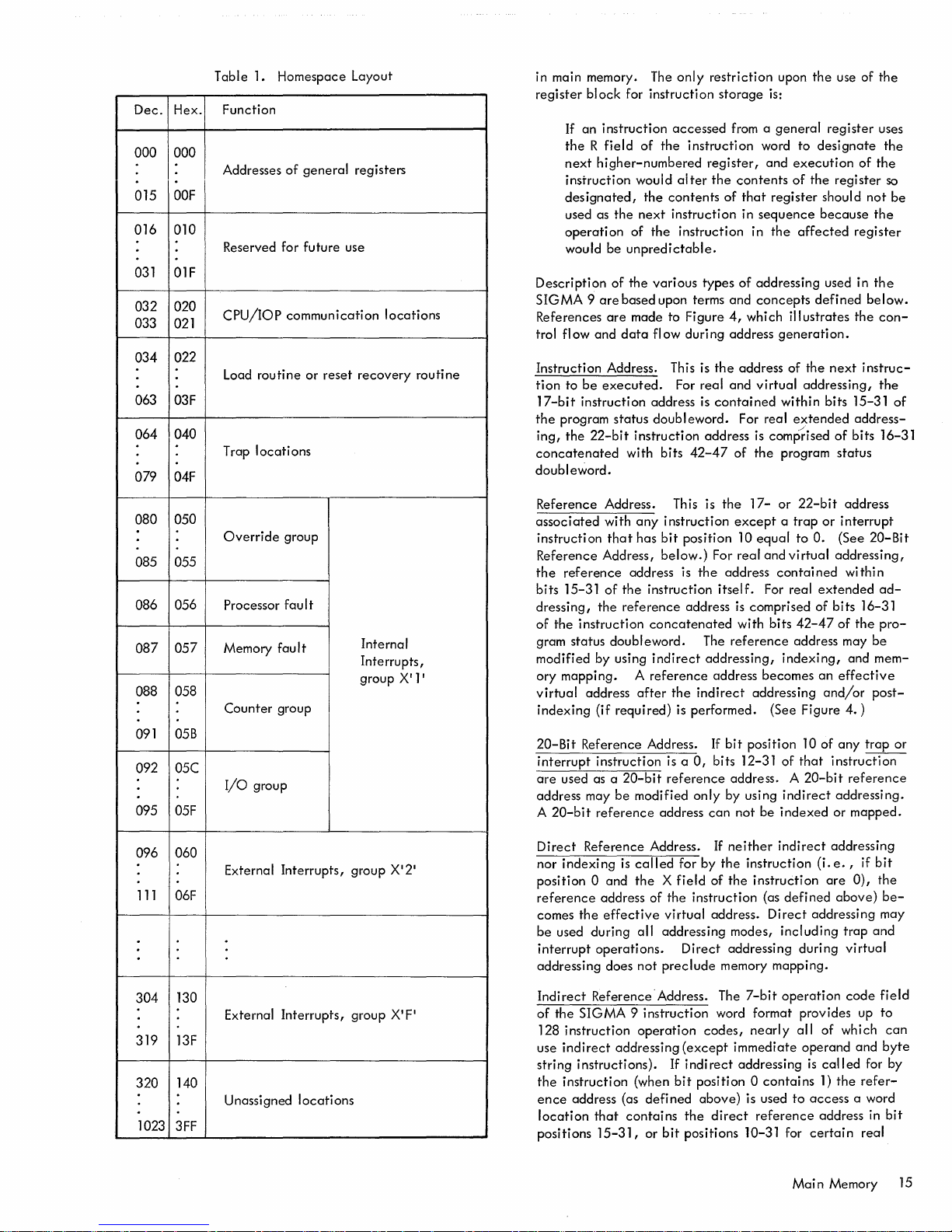

Homespace Layout

1.

Computer

2.

SIGMA 9 Interrupt Locations

3.

Summary

4.

TCe

5.

Registers Changed

6.

Status Word 0

7.

Operating

of

SIGMA 9 Trap Locations

Setting for Instruction Exception

(XI4D')

Trap

an

Operand

Access

TABLES

and

Addressing Modes

at

Time

of

a Trap

Due

to

___

Status Word 1

8.

Status Word 2

9.

15

28

29

34

41

42 Indi

52

ANAL

10.

11.

12.

13.

14.

C-l.

YZE

Codes

Floating-Point

Condition Code Settings for

Instructions

Status Response for

Program Status Doubleword

Basic Instruction Timing

Table for

cation

SIGMA 9

Number Representation

I/O

Operation

Floating-Point

Instructions

(PSD)

53

53

58

74

76

115

129

J58

v

1.

SIGMA 9 SYSTEM

INTRODUCTION

The

XDS

SIGMA 9 Computer System

general-purpose

variety

for a

time-sharing

central

and

system

other

The basic system can be

the

for four million words. Memory access paths

creased

Input/output

input/output

devices.

The CPU has a large instruction

point

1I100k-ahead

cution

execution

(512K) words

16

of

independent

CPUs or lOPs. Each bank

address

banks. This multibanK, multiaccess memory subsystem with

interleaving

single

clude

port expansion

processors

transfer

concurrent

The SIGMA 9 computer design

SIGMA 7 computer, so

on SIGMA 9. Therefore, comprehensive, modular

ware,

operating

and

Reliabi lity,

significantly

A

an

lOP,

tem for diagnosis

continues

This manual describes

features, system organ

ations,

prbcessing unit (CPU), a main memory subsystem,

an

independent

element

elements.

user1s requirements. Main memory has addressing

from

and

with memory

modular units

ports

in

interleaving

memory bank designs. The SIGMA 9 system

up

to

data

requiring no reprogramming

uti I ity routines.

partitioning

entire

and

operator

digital

computer system. It

of

scientific,

applications.

performs asynchronously with

the

basic two ports to a maximum

capability

processors (lOPs),

decimal instructions. A

ll

enables

time.

and

systems, assemblers, compilers,

subsystem, consisting

attached

operation.

A large main memory

is

provided. The memory consists

of

each

memory unit

access to memory by

achieves

11

independent

capability)

high-speed

at

rates

with CPU instruction

maintainabi

improved

feature,

peripherals to be isolated

and

controls,

business

A basic system includes a

input/output

readi

Iy

can

be increased

device

set

the

CPU

to

accessing,

32,768 (32K) words

can

system performance far

up

to

lity,

over

for

repair

the

ization,

thereby

can

operates

be provided between

I/O

of

two types - multiplexor

RAD

I/O

three

that

SIGMA 7 programs will run

and

previous SIGMA computers.

example,

whi Ie

general

instruction

and

timing

is a high-speed,

is

designed

data

processing,

subsystem

expanded

that

special

overlap

be

up

to

processors (limited only by

processors - which

mill ion bytes per

execution.

is

compatible

is

avai

of

a CPU, memory

the

characteristics

..

Each major

respect

to accommodate

by

controllers,

includes

feature

instruction

reducing program

of

up

each.

expanded

12

processors -

asynchronously,

avai

lable,

mathematical

labi lity have been

permits faulty units or

from

primary system

set,

of

the

system.

and

to

space

can

be

of

12

ports.

adding more

and

I/O

floating-

called

exe-

to 524,288

of

up

to

The number

to

allow

either

and

adjacent

in

excess

can

I/O

can

second,

with

the

soft-

including

un

it,

the

sys-

and

I/O

oper-

in-

of

in-

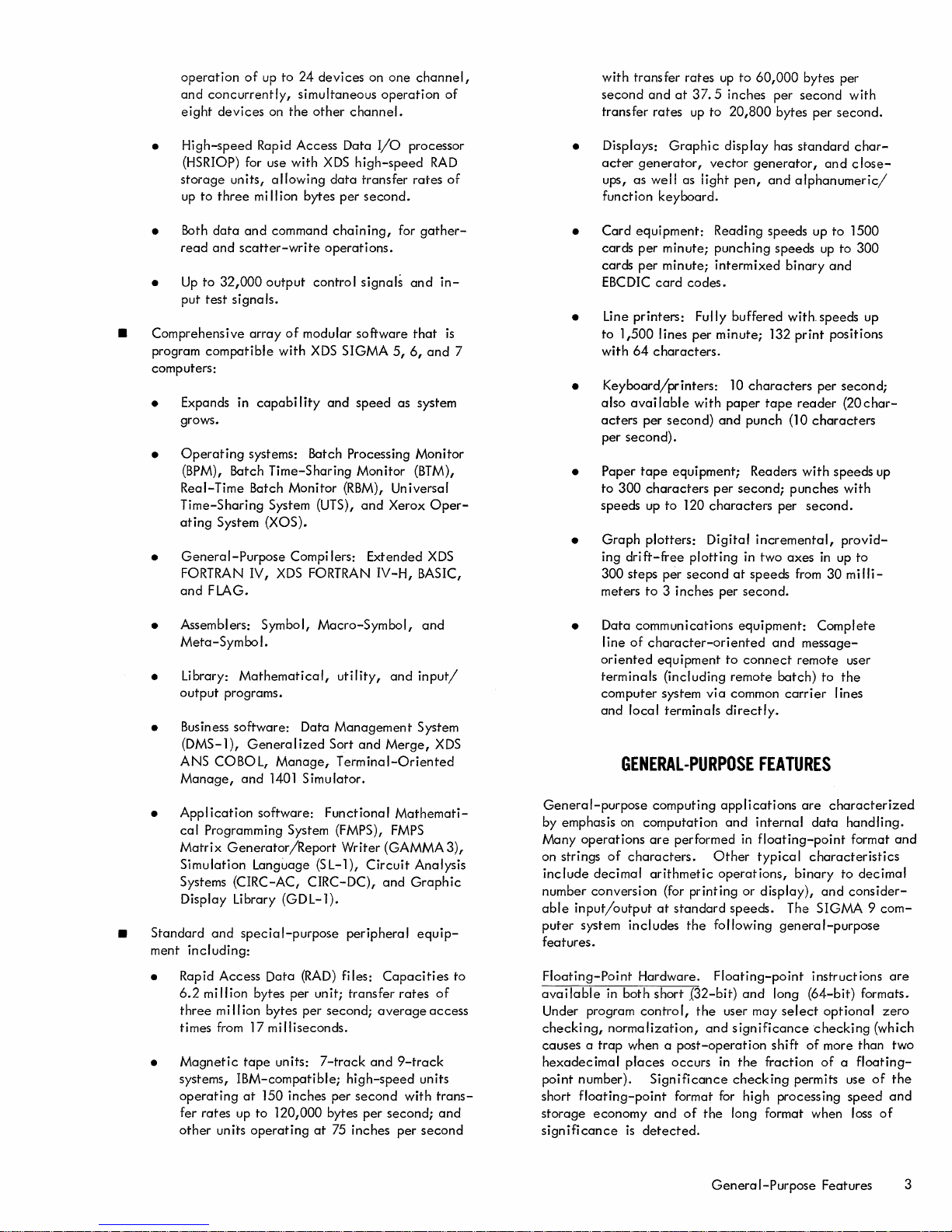

GENERAL

A SIGMA 9 computer system has

characteristics

purpose, multiprocessing,

multiusage environments:

•

Word-oriented

which

halfword

(8-byte)

• Memory

(512K) words in blocks

and

blocks

256K to 512K (where K

• Direct addressing

entire

• Indirect addressing with or without

• Displacement index registers, automati

adjusting for

• Immediate

effi

•

16

general-purpose

blocks

isters

• Hardware memory mapping, which

nates memory fragmentation

program

• Four modes

and

• Memory

destruction

• Watchdog timer

•

Real-time

identification

time,

armed,

• Instructions with long

terrupted

• Automatic traps for error or fault

masking

under program contro

• Power

event

that

can

be addressed

(2-byte),

quantities.

expandable

65,536 (64K) words. Expansion proceeds in 32K

from

128K to 256K,

memory.

all

operand

ciency

and

of

16)

in

a multiusage environment.

relocation.

of

information

write

of

priority

and

up to 238 levels

enabled,

to

guarantee

capabi

fail-safe

of

power fai lure.

CHARACTERISTICS

features

permit

efficient

time-sharing,

memory

increased

reduce

memory

security

protection

critical

to

and

lity

for

(32-bit

and

word

from

of

= 1024 words).

capability

data

sizes.

instructions, for

registers,

data

access

areas

assure nonstop

interrupt system with

priority

and

triggered

execution

response

and

maximum

I.

automatic,

functioning

word plus

a Itered as

(4-byte),

131,072 (l28K) to

16,384 (16K),

and

in 64K blocks from

(real

speed.

expandable

transfer to

and

protection

and

protection.

preventing

of

memory.

assignment, fast response

that

can

by program

to

safe

real-time,

and

extended

post-indexing.

greater

and

virtually

provides dynamic

inadvertent

operation.

be

times

interrupts.

conditions,

recoverabi

shutdown

and

operating

in

general-

parity

bit)

byte

(8-bit),

doubleword

524,288

32,768

(32K),

mode)

ca

lIy

self-

storage

to

64

(in

from

reg-

elimi-

for system

automatic

individually

control.

can

be

in-

with

lity,

in

and

of

SIGMA 9 System

Multiple

•

for

Privi

•

in

multi usage

Complete

•

• Byte,

• Use

•

•

•

•

•

•

• Decimal

• Push-down

•

•

•

• Shift

interval

independent

leged

operations.

of

register-to-register

out

indirect

within

Multiple

Fixed-point

halfword,

Floating-point

and

long formats

normalization

un

der

Full

complement

OR,

exclusive

Comparison

between

registers).

Call

amically

and

allow

system functions

intervention.

metic,

plemented)

automatic

allocation,

recursive

Automatic

binary/BCD

systems.

Analyze

address

Interpret

interpretive

doubleword,

arithmetic,

point

timers with a

time

instruction

environments.

instruction

halfword,

all

memory-referencing

addressing

normal instruction format.

register

integer

word,

fu

II

program

operations,

limits (with limits

instructions

variable,

a program

hardware

edit,

and

stack

of

single

limit

subroutine

routine

conversion

and

instruction

computati

instruction

programs.

operations

including

searching

modes.

choice

bases.

logic for program

set

that

includes:

word,

and

operations,

and

operations.

arithmetic

and

doubleword modes.

hardware

with

control

of

OR).

without

pack/unpack.

operations

checking,

capabi

any

on.

(left

operations

significance,

and

contro

I.

logical

including

that

permit up

user-defined

access

operating

operations,

or

multiple

for

communication,

lity.

operations,

other

that

facilitates

that

increases

and

right)

logical,

shift,

of

resolutions

integrity

doubleword

instructions for

with or

post-indexing,

operations

checking,

operations

in

memory or

to

operating

including

(hardware

words, with

dynamic

weighted-number

of

circular,

and

with-

and

in

in short

zero,

and

all

(AND,

compare

to

64

dyn-

instructions,

system

arith-

im-

space

and

including

effective

speed

of

word or

floating-

Built-in

•

that

•

• Extensive

• Full

• Address stop

in

• Programmable "snapshot" registers

• CPU

•

Independently

•

lowing features:

•

•

•

reliabi

lity

and

include:

Diagnostic

tem

faulty

mine

faulty;

what

tected,

available

subsequent

communicated

tween

It

fau

mit

the

quickly

to

maintenance

diagnostic

snapshot

tion,

conditions.

variety

designed

recoverability.

Partitioning

figuration.

from

from

subsystem, consisting

input/output

peripherals,

ational

of a faulty

tinues

Direct

of a channel.

use

Up

to

by port limitations).

Multiplexor

channel

programs with

verification

unit; unit

the

and

physical component

system status and

parity

memory units

detection

operating

Stop on

Stop on

Stop when

of

register

thus

traps,

of

the

system by

busses. Thus,

system

operation.

input/output

eleven

capability,

and

functional

specific

memory

accurately

to

function

fault

location

error

logging.

for program

analysis.

checking

in

either

and

system or

determine a faulty

feature

personnel to:

any

instruction address.

any

memory

any

is

routines to

with

which

provide

CPU

and

enable

unit

operating

a high

features

SIGMA 9

selectively

processor

can

be

to

enable

while

I/O

processors

I/O

processors (MIOP) with dual

maintainabi

testing

retrieval

on

all

direction

and

processors, providing

location

that

word in a

referenced.

compare

known

determining

system

that

un

faulty

of

a CPU, memory

(lOP),

isolated

the

I/O

of

a full word, without

providing forsimultaneous

lity

capabilities

to

determine

testing

of

diagnosing

is

When a

fault

data

diagnostic

permits

reference

for

fault

degree

enable

its

units or an

diagnosis

primary system

system with

to

a unit

malfunctioning.

information

and logging for

and

on busses

capabi

lity

unit.

operator

address.

selected

that

contents

correct

system

detection

conditions,

of

system

can

be

partitioned

disabling

and

attached

from

the

and

(restricted

features

for:

sys-

the

deter-

that

is

to

analyze

fault

is

addresses

to

per-

program

page

enable

of

informa-

fault

of

system

recon-

them

entire

unit,

oper-

repair

con-

the

only

de-

are

be-

or

a

a

fol-

2

General

Characteristics

operation

and

concurrently,

eight

devices

of

up

to 24 devices on one

simultaneous

on

the

other

operation

channel.

channel,

of

with transfer rates

and

at

rates

37.5

up

second

transfer

up

to

60,000

inches per second with

to

20,800

bytes

bytes per

per

second.

• High-speed Rapid Access Data

(HSRIOP) for use with

•

•

Comprehensive

•

program

computers:

• Expands in

•

•

storage units,

up

to

three

Both

data

read

and

Up

to

32,000

put

test

compatible

grows.

Operating

(BPM), Batch Time-Sharing Monitor

Real-Time Batch Monitor

Time-Sharing System (UTS),

ating

System (XOS).

General-Purpose

FORTRAN IV,

and

FLAG.

allowing

million bytes

and

command

scatter-write

output

signals.

array

of

with

capability

systems: Batch Processing Monitor

Compilers: Extended

XDS

I/O

processor

XDS

high-speed

data

transfer

per

second.

chaining,

operations.

control signals

modular software

XDS

SIGMA

and

speed

(RBM),

and

FORTRAN IV-H, BASIC,

RAD

rates

for

gather-

and

that

5,

6,

and

as system

(BTM),

Universal

Xerox

Oper-

XDS

in-

of

is

• Displays:

acter

ups, as well as iight

function keyboard.

• Card equipment: Reading speeds up

cards

cards

EBCDIC

Line printers: Fully buffered with. speeds up

•

7

• Keyboard/printers:

• Paper

•

1,500 lines per minute; 132 print positions

to

with

also

acters

per second).

to

300

speeds

Graph

ing

300 steps per

meters

Graphic

generator,

per

minute; punching speeds

per

minute; intermixed binary

card

64

characters.

available

per second)

tape

equipment; Readers

characters

up

to 120

plotters: Digital

drift-free

to

3 inches per second.

display has

vector

codes.

with

and

per

characters

plotting

second

pen,

10

paper

second; punches with

in

at

standard

generator,

and

alphanumeric/

characters

tape

reader

punch

(l0

with

per

incremental,

two axes

speeds

from

char-

and c lose-

to

1500

up

to 300

and

per second;

(20char-

characters

speeds

second.

provid-

in

up

30

milli-

up

to

• Assemblers: Symbol, Macro-Symbol,

Meta-Symbo

• Library:

output programs.

• Business software: Data Management System

(DMS-l),

ANS COBOL,

Manage,

•

Application

cal

Programming System (FMPS),

Matrix

Simulation Language

Systems (CIRC-AC, CIRC-DC),

Display Library

Standard

•

ment including:

• Rapid Access Data

•

and

6.2

million bytes per unit; transfer

three

times from 17

Magnetic

systems, IBM-compatible;

operating

fer rates

other

I.

Mathematical,

Generalized

Manage,

and

1401

software: Functional

Generator/Report

(GDL-l).

special-purpose

mill ion bytes per second;

mi

IIiseconds.

tape

units:

at

150 inches per

up

to 120,000 bytes per second;

units

operating

utility,

Sort

and

Terminal-Oriented

Simulator.

Writer (GAMMA 3),

(S

L-1),

peripheral

(RAD)

files:

7-track

high-speed

second

at

75

inches per

Circuit

average

and

and

and

input/

Merge,

and

Capacities

XDS

Mathemati-

FMPS

Analysis

Graphic

equip-

rates

of

access

9-track

units

with

trans-

and

second

to

• Data communications equipment: Complete

of

character-oriented

line

oriented

terminals (including remote batch) to

computer system

and

equipment

via

local terminals

GENERAL-PURPOSE

General-purpose

by emphasis

Many operations

on strings

include

number conversion (for printing or display),

able

puter

features.

Floating-Point

available

Under program

checking,

causes a

hexadecimal

point number).

short

storage economy

sign ifi

decimal

input/output

system includes

trap

floating-point

cance

computing

on

computation

are

performed

of

characters.

arithmetic

at

standard speeds. The SIGMA 9

the

Hardware.

in

both short

control,

normalization,

when a

places

is

post-operation

occurs in

Significance

format

and

of

detected.

applications

Other

operations,

following

Floating-point

J32-bit)

the

user may

and

for

the

and

message-

to

connect

common

directly.

remote user

carrier

FEATURES

are

and

internal

in

floating-point

typical

binary to decimal

general-purpose

and

long (64-bit) formats.

select

significance

shift of more than two

the

fraction

checking

high processing

long format when

permits use

the

lines

characterized

data

handling.

format

characteristics

and

consider-

com-

instructions

optional

checking

of a f/oating-

of

speed

loss

zero

(which

of

and

are

the

and

Genera

I-Purpose Features 3

Decimal

instructions

struction

verting

and a genera

check

display

Indirect

linkages

separate

Displacement

displacement

without

ca

register

For

word,

may be

using

register

cesses

word, or doubleword. Incrementing by various

according

is

the

Instruction

short,

rapidly

execution

Translate

rapid

from a variety

verted

Arithmetic

operate

set

to/from

protection,

or

print

Addressing.

and

from

considering

lIy al ign themselves

may

example,

single-precision,

stored

the

same

contains

the

kth

to

always

by units

size

of

data

Set.

highly

assembled

time.

Instruction. The

translation

easi

Iy

on up

includes

the

packed

Ii

zed

edit

and

it.

permits

procedure

indexing.

permits

be

used on arrays with

in a matrix multipl

in a

second

index

the

element,

data

size

in a continuous

element

More

optimized

and

between

of

input sources

for

output.

Hardware. Decimal

to

31

digits plus

pack/unpack

format

instruction for

formatting, with

Indirect

keeping

accessing

its

quantity

value

data

sections

Indexing by means

size.

appropriately;

fixed-point

array

of

whether

is

not

required;

used.

than

100 major instructions permit

programs

minimize both program

Translate

any

instructions for

of

two digits per

zero

addressing faci

sections

for

ease

a desired unit

The

index

thus,

different

ication

numbers,

as

double-precision

for both arrays.

k,

then

the

it is a

byte,

instead,

array

table

to

be

written,

instruction permits

two

8-bit

can

be

handled

arithmetic

sign.

suppression,

punctuation

of

of

maintenance.

of a "floating"

registers

the

of

any

user always

codes; thus

This

conbyte,

to

litates

table

a program

of

data

automati-

same

index

data

sizes.

array

of

the

results

numbers,

If

an

index

ac-

halfword,

quantities

incrementing

regardless

which

are

space

and

data

and

recon-

in-

full

of

INPUT

jOUTPUT

Multiplexing

initialized,

CPU,

needs. The

CPU by using

mit both command

tervening

slow rates involving human

example) to transfer

up to

one

operated

Direct Data

program control

With this

or

from

need

not be used for

High-Speed

feature

one

RAD

This

high-speed

logic

sufficient

bytes per

this

enables

less

than

Input/Output

I/o processors

leaving

it free

to

MIOP requires minimal

channel

chaining

CPU

control.

rates

million bytes per

simultaneous Iy.

Input/Output

of

asynchronous or

feature

general-purpose

is

simi lar to

per

second.

40

information

relatively

RAD

Input/Output

multiplexing

channel

channel

to sustain transfer rates up

In a typical

a program swap into

milliseconds.

provide faster response to system

command doublewords, which

I/O

registers so

controller

contains

TIME-SHARING

Time-sharing

capacities

can

be performing a

share

of

interactive,

Other

requires on

is

the

among many users

the

available

"conversational"

users may be

Iy

final

ability

different

resources)

entering

output.

CAPABILITIES

Processor (MIOP).

operate

and

interaction

of

second.

(DIO). DIO

independently

interaction

data

chaining

equipment

rotating

can

infrequent

Processor (HSRIOP). This

is

time-sharing

or

speeds

(teletypewriter,

memory

Many

devices

facilitates

special-purpose

be transmitted

that

an

I/O

transmissions.

input/output

operating

the

buffering

to

out

of

main memory

FEATURES

of

a system

at

the

task (requiring a

and

mode with

work

to

same time. Each user

may be

the

to

be processed

Once

of

the

with

the

per-

without

range

from

devices

at

three

application,

share

on-line

of

can

in-line

devices.

directly

channel

except

that

a time.

and

priority

million

its

total

different

in an

computer.

that

in-

for

be

to

in

Conversion Instructions. Two

structions

internal

cluding

Call

up

machine

erating

Interpret

and

thus

other

Four-Bit

results by

every

flow, underflow,

without

4

provide

binary

BCD.

Instructions. These four instructions permit

to

64

user-defined

instructions,

system

Instruction. The

speeds

reducing

interpretive

Condition

automatically

instruction

requiring

Input/Output

for

and

any

services

interpretive

space

and

systems.

Code.

execution,

zero,

an

extra

Capabi

bidirectional

other

subroutines,

and

without

operations

minus,

generalized

conversions

weighted

as if

gaining

time

This simpl ifies

providing information on almost

instruction

lities/fime-Sharing

access

requiring

Interpret

such as

requirements for compi lers

including

and

pi

conversion

between

number system,

they

were

to

specified

its

intervention.

instruction simplifies

compilation,

the

checking

indicators for

us, as

appropriate,

execution.

Features

in-

handling

built-in

op-

and

over-

in-

of

The SIGMA 9 system provides

features

Rapid

another,

quickly

mit storing

registers by a

automatically

when

program status doubleword (PSD), which

description

operation,

PSD

Multiple

to

sponse time by

blocks. A

tions as

cally

described

Context

and

needed

loaded,

four blocks

needed;

selects

Saving. When

the

operating

easily.

in

a push-down

single

and

(also, by a

of

the

can

be

all

Register Blocks. The

of

reducing

distinct

the

below.

Stack-manipulating

instruction.

information in

current

stored

with a

16

general-purpose

block

the

program status doubleword

applicable

the

time-sharing

changing

environment

stack

single

user's environment

anywhere

single

the

need

can

register block.

can

of

1 to 16

Stack

the

stack

instruction). The

in

instruction.

optional

to

store

be assigned for

computer

from

one

user to

be

switched

instructions

general-purpose

status

is

updated

can

be

retrieved

current

contains

memory

avai

registers improves

and

and

labi lity

and

load register

different

automati-

the

mode

a new

entire

of

per-

of

up

re-

func-

User Protection. The

user to his own

set

operating system

tions

that

could destroy

correctly.

vents a user

Also, a memory

From

those assigned to him. It permits

areas for

reading

routines, while preventing

accessing instructions-in areas

Storage Management. SIGMA 9 memory

from

128K

sizes

provide the

for expansion.

the

memory map hardware permits storing a user's program

in

fragments as small as a

space

is

avai

(l31,072)words

capacity

To

lable;

contiguous block

map also

so

at

in

automatically

that

the

program appears

execution

time,

a different set

memory. The memory map

compatible SIGMA 7 mode in addition to providing

ability

words. Thus,

memory

output

to

locate

in

the

SIGMA 9's logical addressing

the

of

128K words regardless

Input/Output

quirements

Capabi I ity. Time-sharing

are

handled by

capabilities

Features

Nonstop

II.

Operation.

system continues to

due to failure

of

slave

mode feature restricts

of

instructions whi

certain

"privileged"

another

accessing

only,

such as those

access-protection

any

him

Ie

reserving

{master mode)

user's program

system

storage areas other than

him

to access

certain

containing

from

reading,

set

aside for other users.

writing, or

is

available

to 512K (524,288) words

make

yet

of

needed

storage

while assuring

efficient

page

a

II

fragments

at

use

of

available

of

512 words wherever

appear

execution

time.

the

as a sing Ie,

The memory

handles dynamic program

to

be stored in a standard way

even though it may

of

locations

any

128K-word (131,072) virtual program

system

each

for

SIGMA 9 can

can

always address a virtual

actua

time it

of

is

space

of

physical memory

lIy be stored

brought into

operate

four million

input/output

the

same

general-purpose

described under

A IIwatchdog

operate

special

even

I/O

"General-purpose

II

timer assures

in

case

devices.

of

halts or delays

Multiple

each

to

the

instruc-

if

used

pre-

public

sub-

in

potential

memory,

relocation

in a

the

size.

re-

input/

that

the

real-time

clocks with varying resolutions permit independent time

bases for flexible

allocation

of

time slices to

each

user.

to

in-

and

easy,

even

quick

progress.

each

group

In

establ ishing a con figuration

of

up

while a

to

16

interrupt levels

ity assigned in different ways

of

a problem;

not

affected

Programs

that

the

way interrupt levels

by

the

priority assignment.

deal

with interrupts

equipment sometimes must be

ment

is

actually

cia

I equipment,

IItriggered

struction. This

hierarchy

high-priority

pleted,

it may

ll

by

the

of

responses.

interrupt,

be

available.

any

SIGMA 9 interrupt level

CPU through

capability

after

desirable

the remaining portion so

other

to respond to

critical

real-time

to

checked

To

permit simulating this

execution

is also useful in establishing a

For

example,

the

to assign a lower priority

that

the

stimuli. The interrupt

can accomplish this by triggering a

which processes

rupts have been

Certain

instructions

described in

interrogate

to

restore

and

Nonstop

(on a ready/resume

become

respond

excessively

quickly. A built-in

the SIGMA 9 computer

length

of

Real-Time

occur

to

also

event

up

at

needed

/ or

to four

solution to meet

easy handling

the

remaining

handled.

(READ

Chapter

the

condition

that

system

Operation.

basis),

delayed

time.

Clocks. Many

specific

- for

the

instants.

example,

current

real-time

these

of

separate

data

DIRECT

3)

allow

the

of

the interrupt system

at a later

When

connected

the

computer

if

the

watchdog timer assures

cannot

be

real-time

Other

elapsed

time

of

day. SIGMA 9

clocks with varying degrees

needs. These clocks a

time bases

priorities.

meet

from

process

for

can

the

specific

are

programmed

specially

out

before

the

system,

have its

designed

the

is

can

of a single

in responding to a

urgent processing

interrupt

routine

is

routine

lower-priority

only

after

and

WRITE

program

other

DIRECT,

to

completely

at

level,

any

time.

to

special

delayed

special

can

device

for

devices

sometimes

does not

an

excessive

functions must be timed

timing information

time

since

a given

can

contain

Iso

and

relative

time

in

prior-

needs

is

equip-

spe-

be

in-

is

com-

to

free

inter-

that

of

re-

allow

time

is

REAL-TIME

Real-time

(1)

environment,

real-time

flexibi lity to handle a wide

applications

hardware

process itself,

that

(2)

provi des

speed

FEATURES

are

characterized

qu

i ck response to

great

enough to

and

(3)

varietyof

speeds. The SIGMA 9 system includes provisions for

following

Multilevel,

oriented

rupts by means

source

responded

be programmed.)

individually

disabled

real-time

computing features.

True Priority Interrupt System. The

SIGMA 9 system provides quick response to

of

up

to 224 external interrupt levels. The

of

each

to

according

interrupt

For

is

automatically

to

its priority.

further flexibi lity,

disarmed (to discontinue input

(to

defer responses). Use

ture makes programmed dynamic reassignment

keep

sufficient

data

(This

each

of

the

disarm/disable

by a need

an

extern a I

up with

input/output

types

at

varying

real-time-

inter-

identified

function must

level

can

acceptance)

of

priorities

for

the

the

and

and

be

fea-

Context

Rapid

interrupt-initiated

preserve

later,

while

of

environments must be done

1I0verhead

of

up

to

can,

if

relevant

tion address,

protection

Switching. When responding to a new

circumstances, a computer system must

the

current

setting

ll

time costs.

four blocks

operating

up

of

desired, be assigned to a

"information

about

current

key/etc.)

is

doubleword (PSD). A

PSD

anywhere in memory

to establish a new

environment/which

identifying a new block

can

SIGMA 9 system

environment

completely

thus preserve

instruction.

environment/for

the

new environment. This changing

quickly,

In

the

SIGMA 9 system/

with a minimum

general-purpose

specific

the

current environment (instruc-

general

single

register

kept

in a 64-bit

instruction stores

and

loads a new

block,

includes

of

general-purpose

and

change

through

the

execution

Rea 1-Ti

continuance

each

arithmetic

environment. All

memory-

program status

the

one

from

informatic:>n

registers. A

its

of a single

me

Features 5

set

of

of

one

registers

current

memory

operating

SIGMA 9 Computer System

vi

Memory

background

system

destruction

operating

feature

tions

Variable

tered

this

operations

arithmetic

included.

Direct

a

general-purpose

be

transm

because

prevents

of

in

real-time

data

Data

32-bit

occupied

iss

Protection.

programs

by

system

reading,

Precision

efficiently,

in

addition

operations

Input/Output.

word

with

ions.

Both foreground

can

be

run

concurrently

a foreground program

an

unchecked

control,

accessing

writing,

Arithmetic.

systems

can

be

register

relatively

SIGMA

background

the

memory for

and

are

16 bits or less.

9provides

to

fullword

(for

extended

For

transferred

so

that

infrequent

memory

instruction

Much

handling

an

(real-time)

is

protected

program. Under

access-protection

specified

acquisition.

of

the

halfword

operations.

precision)

asynchronous

directly

I/O

to or from a

channel

and

and

in a SIGMA

against

combina-

data

encoun-

To

process

arithmetic

Doubleword

are

also

need

not

nonperiodic

I/O,

Instruction

9

provides

required

each

and

SIGMA 9

multiprocessor system. It

processing units

(the

maximum memory port

SIGMA

a

This

wi"

cessor system.

Set.

The

large

SIGMA 9

the

user

the

computational

for

widely

IS

program

speed

of

differing

obtaining

length

and

application

and

runn ing

results

MULTIPROCESSING

is

designed

sum

of

both

9 system address memory uniformly.

section

allow

describes

growth from a monoprocessor

to function as a

can

and

up

to n input/output

types

of

processors

limitation

the

major

contain

instruction

data-handling

is

increased.

areas;

time

capabilities

therefore,

is

decreased,

FEATURES

shared-memory

up

to

four

processors

is

restricted

of

12). All processors in

features

of

SIGMA 9

to a multipro-

set

central

by

the

that

MULTI

As

implemented

bines two or more

difficult

cation

the

application

Because

time

tions in a

that

useful

capability

usage

puter

Priority

ments

interrupt

With it

proper

without

lengthy

Quick

duce a quick-response

rapid

fit

able

Memory

only

guarantee

real-time

general

because

most

the

base,

prove

in

applications.

features

Interrupt.

operate

system (as in

the

order,

the

execution

Response. The many features

context

all

users

at

any

Protection.

protect

in

the

computer

computing

of

its

difficult

it

multiusage

valuable

others,

makes

computer system corresponds qui ck Iy,

the

appl

multiusage

that

includes

SIGMA 9 system has

is

uniquely

for

although

SIGMA 9 particularly

The

are

described

In a multiusage

asynchronously.

to

the

many demands

high

overhead

time,

saving,

because

instant

each

more

for useful work.

user from

integrity

ications.

USAGE

SIGMA

severe

environment.

SIGMA

system (multiple

multiple

The memory

FEATURES

9 system, IImultiusage

application

problem

requirements.

problem

one

or more

been

qualified

certain

of

in

major

costs

and

of

every

programs

application

different

SIGMA

below.

Thus,

9)

is

of

extensive

push-pull

the

machine's

protection

other

areas.

is

the

real-time

is a time-sharing

real-time

designed

for a

mixtureof

Many

hardware features

areas

ways. This

effective

9 multi usage

environment,

having a true

especially

being

made

complicated

storage

that

combine

register

operations)

power

features not

user,

they

essential

ll

com-

The most

appli-

Similarly,

processes.

on a

real-

applica-

are

equally

multiple

in

mu

Iti-

com-

many

ele-

priority

important.

and

in

upon

it,

programming

allocations.

to

pro-

blocks,

bene-

is

avai

also

to

critical

MULTIPROCESSOR

In

a multiprocessor system,

often

need

(CPUs)

This

resource

peripheral

process.

required

LOAD

AND

position

store

cycle

previously

to

be

IIset"

On

the

other

a

zero,

the

and

simultaneously

processor.

device

SIGMA

multiprocessor

of

the

of

set

and

resource

exclusive

may be a region

or,

9 has a

SET,

unconditionally

referenced

the

memory

by

another

the

testing

hand,

in some

interlock.

if

the

is

allocated

the

interlock

INTERLOCK

the

central

control

of

memory, a

cases, a specific

special

instruction

memory

operation.

processor,

program

sign bit

to

The

sets a

proceeds

of

the

is

processing units

of

a system

particular

software

to

provide

special

111"

bit

location

If

the

the

set

during

this

bit

interlock

to

tested

testing

for

any

another

processor,

resource.

this

instruction,

in

the

sign

the

had

been

is

said

task.

location

other

re-

is

HOMESPACE

Since

all

processors in a multiprocessor system address

ina

un

i form

memory

vate

memory

and

interrupt

This

private

1,024 words for

real

with

tions,

1-

tions,

ters,

occupy

remaining words in

private,

that

memory

address

interrupt

plus

the

the

independent

manner,

is

un

locations,

is

each

CPU. Each Homespace

zero.

locations,

16

locations

first

the

storage

MUL

TIPORT

ique

320

it

is

necessary

to

each

processor for its

I/O

communication

called

Homespace region

The

implicitly

and

that

locations

by

MEMORY

Homespace

assigned

lOP

commun

are

reserved

of

Homespace. The

the

CPU.

SYSTEM

to

locations,

and

region

ica

ti on

for

can

be

reta

ina

trap

consists

trap

loca-

loca-

the

regis-

used as

pr

etc.

of

begins

i-

Input/Output.

speeds,

needs

both in terms

6

the

of

Multiusage/Multiprocessing

Because

SIGMA 9 I/O

many

different

of

equipment

of

its

wide

system

application

and

programming.

range

of

simultaneouslysatisfiesthe

areas

economically,

Features

capacities

and

SIGMA 9 has growth

unit. A basic

ory

16K

words

each,

in

operating

when

addressed

capabi

I ity

of

up

to 12 ports per mem-

memory unit consists

which

each

bank

can

by two

of

the

of

two banks of

be

concurrently

possible

12

ports.

This system

and

provides large amounts

to multiprocessor systems.

SIGMA 9 has manual

units. Thus, besides its primary

throughput

processor system

can

system busses. Faulty units

ational

units to be

A multiprocessor control function

cessor systems. This function provides

1.

architecture

MANUAL

capabi

is

be

partitioned

system. Reenabling

returned

MULTIPROCESSOR

Control

(External DIO), used for

of

the

allows flexibi lity

of

PARTITIONING

partitioning

lity, a

secondary

its fai I-soft

by

selectively

are

to

service.

CONTROL

External Direct

memory bandwi

CAPABILITY

capability

advantage

advantage

abi

lity. Any SIGMA 9 unit

disabling,

thus isolated

the

connection

is

provided on a

controlling

in

growth patterns

dth,

for

all

of

increased

of a multi-

it

from

from

allows

FUNCTION

II

three

basic features:

Input/Output

system

essentia I

system

the

the

oper-

repaired

multipro-

bus

maintenance

AID

converters.

2.

Central

3. Interprocessor interrupt

one

processor

cessor

control

that

an

and

of

to

action

special

system

directly

SHAREDINPUT/OUPUT

Provisions

system for

cessor. This is,

HIO instruction to

or

cess. However,

process

This

uration

action

resolution problems.

have

been

made in a SIGMA 9

any

CPU

to

direct

any

CPU

can

begin,

the

end-action

is

directed

feature

control switches) allows

tasks to a single processor and avoids

at

one

(accomplished by

purpose units such as

partitioning.

connection,

signal

is

to be

I/O

issue an

stop, or

sequence

of

the possible four CPUs.

setting a pair

dedicating

another

taken.

actions

SIO,

test

a !lowing

mul

to

any

no,

any

of

I/O

pro-

tiprocessor

I/O

TDV,

I/O

pro-

the

I/O

of

config-

end-

conflict

pro-

Multiprocessing Features 7

2.

SIGMA 9 SYSTEM

ORGANIZATION

The

primary

system, as

units,

elements

as a group

cati

ng

asynchronously

overlapping

greater

system

duction

subsystem performs

of

digital

selected

expanded

to

16),

cluding

ber

of

elements

illustrated

memory

wi

primarily

central

units,

permit

of

program-control I ed

th a common memory. Each subsystem

and

the

operation

speed

(when

tasks

while

information

peripheral

by

increasing

increasing

MIOPs

and

processors (up

CENTRAL

This

section

SIGMA 9 central

and

data

control.

memory

in Figure 2.

describes

formats, information

Basically, a SIGMA

and

an

arithmetic

of a basic

in Figure

and

input/output

the

total

computer

semi-independently,

of

the

circumstances

performs

overall

each

lOP

the

tasks

associated

between

devices.

the

number

the

number of lOPs (up

HSRIOPs), or by

to

PROCESSING

the

organization

processing

unit

processing,

and

SIGMA 9 computer

1,

are

central

processors. These

system

subsystems commun

other

permit).

control

(MIOP

the

main

A

basic

4).

to

automatically

subsystems for

and

or

HSRIOP)

wi

th

memory

system may be

of

memory units (up

to

increasing

UNIT

and

operation

in terms

9 CPU consists

control

unit

of

and

as

processor

be

viewed

i-

operates

A

CPU

data

re-

the

exchange

and

11,

in-

the

num-

of

instruction

program

of

a fast

illustrated

sub-

the

The

CPU

has

three

storage

for

codes

protection

computer

Memory

standing

and

A

virtual

used by a

the

of

data,

It

may

addresses

through

loading

during

clude

addresses,

gram,

An

actual

(memory address

location

by

the

addresses

ware.

of

a memory

associated

codes.

is

in

Map.

of

the

actual

address.

address

machine-level

location

of

or

the

also

be

are

derived

an

assembly (or

process.

a program's

all

instruction

and

as

well as those addresses

address

for

storage

execution

are

fixed

(See

"Main

MEMORY

the

Two terms

memory mapping

an

location

an

addresses used as

CONTROL

high-speed

map,

with

the

memory

This

storage

master or

is a value

instruction,

explicit

Virtual

execution.

addresses,

is a value

register)

or

sequence

and

Memory" for

master-protected

are

pertaining

program,

of a data

quantity.

from programmer-suppl ied

compilation)

addresses may

used

to

retrieval

of

dependent

STORAGE

integrated-circuit

memory

essenti al

access a specific

an

access

map,

can

be

concept:

and

the

location

address

Normally,

process

Thus,

virtual

data

addresses,

counts

computed

within

of

information,

instruction.

on

the

further

protection

and

memory

changed

to a proper

virtual

to

the

which

of

(indirect

followed

also

addresses

within a stored

by

the

memory

wired-in

details.)

memories

write-

when

mode.

under-

address

logical

be

the

space

designates

an

element

address).

virtual

labels

computed

indirect

program.

unit

memory

as

required

Thus,

actual

hard-

the

by a

in-

pro-

GENERAL

An

integrated-circuit

general-purpose

CPU. These 16 reg i sters

register

a

register

4

ister

block

selects

are

block

master

fied

(0 through 15 in

decimal

fixed-point

temporary

formation such

General

ters,

accumulator

31

used when a

the

general

16

referred

pointer

or

master-protected

Each

general

by a 4-bit

notation).

registers

and regi sters 12 through 15 may be used as a

digits

plus

registers,

block. A SIGMA

blocks. A 4-bit