xrclS

.

.

.

XDL5SIGMA 2 COMPUTER

Xerox Data Systems

Reference Manual

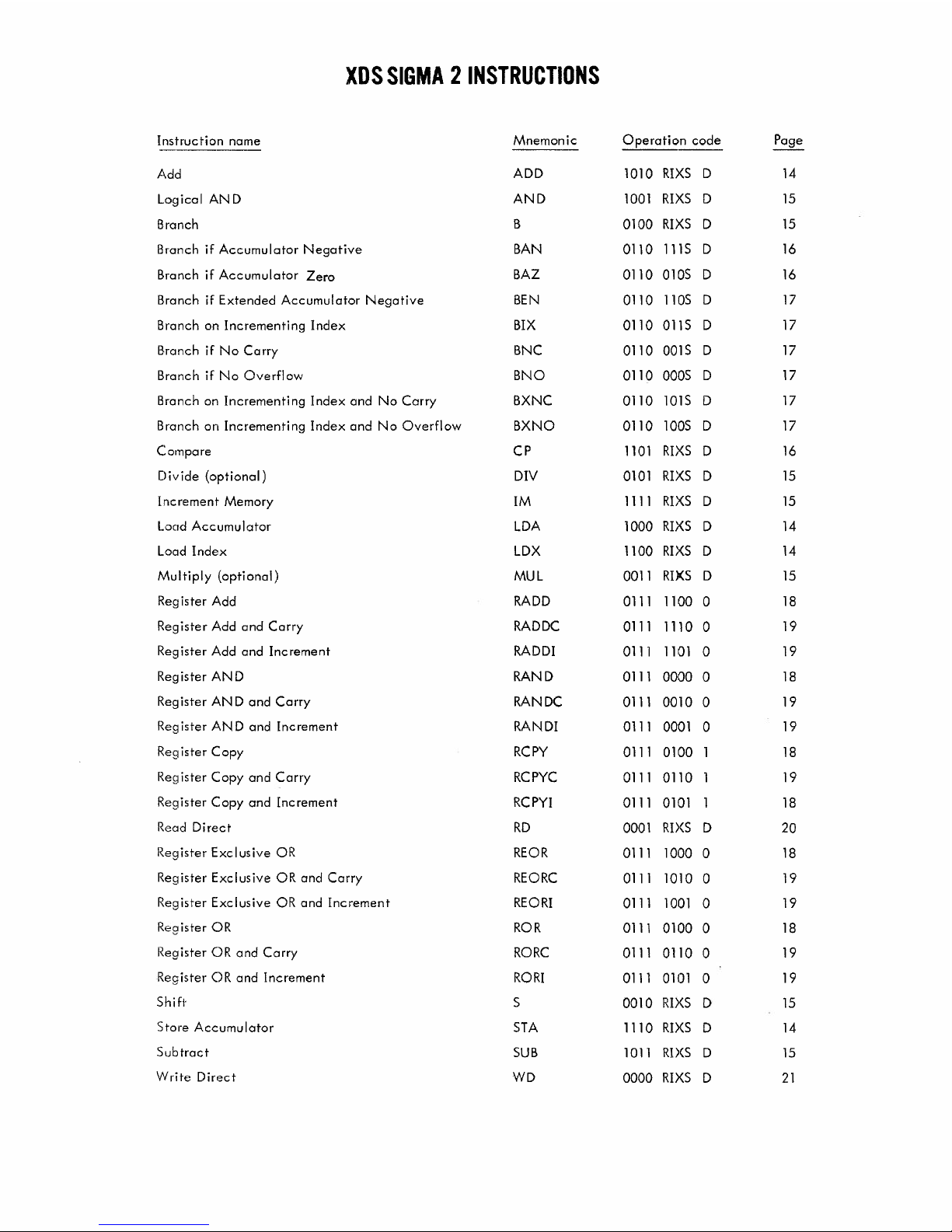

XDS SIGMA 2 INSTRUCTIONS

Instruction name

Mnemonic Operation code

Page

---------

Add

ADD

1010

RIXS D

14

Logical AND

AND 1001 RIXS D 15

Branch

B 0100 RIXS D 15

Branch if Accumulator Negative BAN

0110

ins

D 16

Branch if Accumulator Zero

BAZ

0110 010S D 16

Branch if Extended Accumulator Negative BEN

0110 lIDS D

17

Branch on Incrementing Index BIX 0110 OIlS D 17

Branch if No Carry BNC

0110 001S D 17

Branch if No Overflow BNO

0110

ODDS

D 17

Branch on Incrementing Index and No Carry BXNC

0110 101S

D 17

Branch on Incrementing Index and No Overflow

BXNO 0110 100S D 17

Compare CP

1101

RIXS

D 16

Divide (optional)

DIY 0101 RIXS D 15

Increment Memory

1M 1111 RIXS D 15

Load Accumulator LDA 1000 RIXS

D 14

Load Index

LDX 1100 RIXS D 14

Multiply (optional)

MUL 0011

RIXS D

15

Register Add

RADD 0111

1100

a

18

Register Add and Carry RADDC

0111 1110

a

19

Register Add and Increment RADD!

0111

1101

a

19

Register AND

RAND

0111 0000

0

18

Register AND and Carry

RAN DC

0111

0010

0

19

Reg ister AN D and Increment

RAND!

0111 0001

0

19

Reg ister Copy

RCPY

0111

0100

18

Register Copy and Carry

RCPYC

0111 0110 19

Register Copy and Increment

RCPYI

0111 0101 18

Read Direct

RD

0001

RD(S

D

20

Register Exclusive OR

REOR

0111 1000

a

18

Register Exclusive OR and Carry

REORC

0111

1010

a

19

Register Exclusive OR and Increment

REORI

0111 1001

0

19

Register OR

ROR

0111 0100

0

18

Register OR and Carry

RORC

0111

0110

0

19

Register OR and Increment

RORI

0111

0101

0

19

Shift

S

0010 RIXS D 15

Store AccumuIator

STA

1110

RIXS

D 14

Sub trac t

SUB

1011

RIXS

D 15

Write Direct

WD

0000

RIXS

D 21

Price: $2.00

XDS SIGMA 2 COMPUTER

REFERENCE MANUAL

900964F

December 1969

XJD:5

Xerox Data Systems/70l

South Aviation Boulevarcl/EI Segundo, California 90245

©

1966,1967,1966,1969,

Xerox Data Systems, Inc.

Printed in U.S.A.

REVISION

This publication, XDS 9009 64F, is a revision of the XDS Sigma 2 Computer Reference

Manual, XDS 9009 64E (dated May 1969). The primary revision is the addition of Appen-

dix D describing the Watchdog Timer. A change in text from that of the previous manual

is indicated by a vertical line in the margin of the page.

RELATED PUBLICATIONS

Title

XDS Sigma 2/3 Symbol Reference Manual

XDS Sigma 2/3 Extended Symbol Reference Manual

XDS Sigma 2/3 Basic FORTRAN/Basic FORTRAN IV Reference Manual

XDS Sigma 2 Mathematical Routines Technical Manual

XDS Sigma 2 Stand-Alone Systems Reference Manual

XDS Sigma 2/3 Basic Control Monitor Reference Manual

XDS Sigma 2/3 Real-Time Batch Monitor Reference Manual

XDS Sigma Interface Design Manual

ALL SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

ii

Publication No.

90 1051

90 1052

900967

90 1036

90 1047

90 1037

90 1037

900973

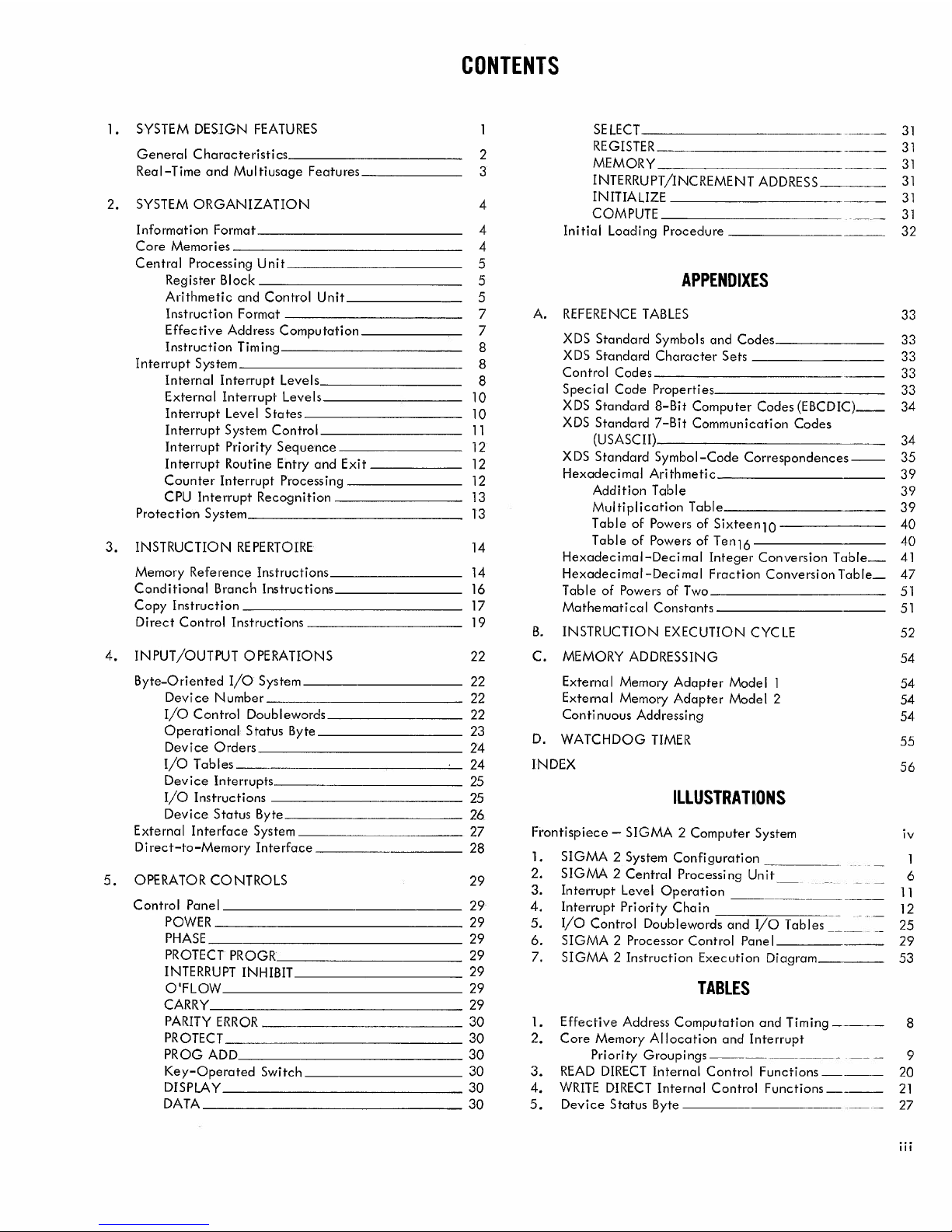

CONTENTS

1.

SYSTEM DESIGN FEATURES

SELECT

31

REGISTER

31

General Characteristi cs

2

MEMORY

31

Real-Time and Mul tiusage Features

3

INTERRUPT/INCREMENT ADDRESS

31

4

INITIALIZE

31

2. SYSTEM ORGANIZATION

COMPUTE

31

Information Format

4

Initial Loading Procedure

32

Core Memories

4

Central Processing Unit

5

Register Block

5

APPENDIXES

Arithmetic and Control Unit

5

Instruction Format

7

A. REFERENCE TABLES

33

Effective Address Computation

7

XDS Standard Symbols and Codes

33

Instruction Timing

8

XDS Standard Character Sets

33

Interrupt System

8

Control Codes

33

Internal Interrupt Levels

8

Special Code Properties

33

External Interrupt Levels

10

XDS Standard 8-Bit Computer Codes (EBCDIC) __

34

Interrupt Level States

10

XDS Standard 7-Bit Communication Codes

Interrupt System Control

11

(USASCII)

34

Interrupt Priority Sequence

12

Interrupt Routine Entry and Exit

12

XDS Standard Symbol-Code Correspondences--

35

Hexadecimal Arithmetic

39

Counter Interrupt Processing

12

Addition Table

39

CPU Interrupt Recognition

13

Multiplication Table

39

Protection System

13

Table of Powers of SixteenlO

40

3.

INSTRUCTION REPERTOIRE

14

Table of Powers of Ten16 40

Hexadecimal-Decimal Integer Conversion Toble.L;

41

Memory Reference Instructions

14

Hexadecimal-Decimal Fraction Conversion Toble.L

47

Conditional Branch Instructions

16

Table of Powers of Two

51

Copy Instruction

17

Mathematical Constants

51

Direct Control Instructions

19

B.

INSTRUCTION EXECUTION CYCLE

52

4. INPUT/OUTPUT OPERATIONS

22 C.

MEMORY ADDRESSING

54

Byte-Oriented I/O System

22

External Memory Adapter Model

54

Device Number

22 External Memory Adapter Model 2

54

I/o Control Doublewords

22 Conti nuous Addressing

54

Operational Status Byte

23

D.

WATCHDOG TIMER

Device Orders

24

55

I/O Tables

24

INDEX

56

Device Interrupts

25

I/O Instructions

25

ILLUSTRATIONS

Device Status Byte

26

External Interface System

27

Frontispiece - SIGMA 2 Computer System

iv

Direct-to-Memory Interface

28

1.

SIGMA 2 System Configuration

1

5.

OPERATOR CONTROLS

29

2.

SIGMA 2 Central Processing Unit_

6

3.

Interrupt Level Operation _____________

11

Control Panel

29

4.

Interrupt Priority Chain

12

POWER

29

5.

I/O Control Doublewords and I/o Tables _~ __

25

PHASE

29

6. SIGMA 2 Processor Control Pane

I

29

PROTECT PROGR

29

7.

SIGMA 2 Instruction Execution Diagram

53

INTERRUPT INHIBIT

29

O'FLOW

29

TABLES

CARRY

29

PARITY ERROR

30

1.

Effective Address Computation and Timing ____

8

PROTECT

30 2. Core Memory Allocation and Interrupt

PROG ADD

30 Priority Groupings ------ ---------- -- -

9

Key-Operated Switch 30 3.

READ DIRECT Internal Control Functions ___

20

DISPLAY

30

4.

WRITE DIRECT Internal Control

Functions ___

21

DATA

30

5.

Device Status Byte

27

iii

1. SYSTEM DESIGN FEATURES

SIGMA 2, a third-generation computer system, is a totally

integrated combination of high performance hardware and

efficient software. The SIGMA 2 system makes fuIIuse of

advanced design features first developed for SIGMA?, and

it provides the user with a balanced system that offers ad-

vantages normally found onl y in large computer systems.

Large Capacity, Low-Cost Input/Output. SIGMA 2 uses

XDS-designed monolithic integrated circuit registers. to pro-

vide four fully automatic, buffered input/output channels

as standard equipment. Up to 16 additional automatic chan-

nels as well as direct input/output capability can be added

at low cost. Maximum channel I/O transfer rate is 400,000

8-bit bytes per second.

Concurrent Foreground/Background Processing. This multi-

programming capabiIity permits the user to operate one or

more fully-protected, real-time programs in the foreground

while concurrentIy operating a general-purpose program in

the background. Overhead in switching from one task to

another is minimized because both hardware and software

are specificially designed for rapid context switching. A

hardware register permits the software to generate re-

entrant code efficiently. Thus, routines common to several

programs, whether in foreground or background, need to be

stored in memory only once.

Comprehensive, User-Oriented Software. SIGMA 2 pro-

gramming systems increase user productivity by providing

powerful, easy-to-use programming tools. As a result,

user programs are written more quickly at lower cost. The

avai labi Iity of thi s comprehensive software package makes

it possible to exploit the full potential of the hardware.

The package includes two operating systems (Monitors),

a FORTRAN compiler, two assemblers, and a variety of

library and utility programs. To store these extensive soft-

ware systems yet keep core memory costs at a minimum,

XDS has developed its Rapid Access Data (RAD) fiIes. RAD

units offer the large capacity and low cost of ordinary disc

files. In addition, by using one fixed read/write head for

every track of data rather than sharing a movable head

among a large group of tracks, the RAD eliminates the

access delays associated with head movement. The RAD's

fast access time and high data transfer rates produce greater

overall system throughput. Forbasic computer configurations

that do not have a RAD unit, a comprehensive group of

stand-alone programming systems is provided. For use with

larger computer configurations, SIGMA 2 programming

systems are RAD-oriented to capitalize on the inherent

benefits of this high-performance secondary storage.

Powerful, Multilevel Priority Interrupt System. The real-

time oriented SIGMA 2 system provides for quick response

to environmental conditions with up to 132 external inter-

rupt levels. The source of each interrupt signal is auto-

matically identified and responded to according to its pri-

ority. For further system flexibility, each interrupt level

can be individually disarmed (so it stops accepting inputs)

and/or disabled (so response is deferred), all under program

control. Use of the arm/disarm, enable/disable features

makes programmed dynamic reassignment of priorities quick

and convenient, even while a real-time process is occurring.

In establishing a configuration for any system, each group

of 16 interrupt levels can have its group priority assigned

differently, to meet the specific needs of an application.

The way interrupt levels are programmed is not affected by

their priority assignments.

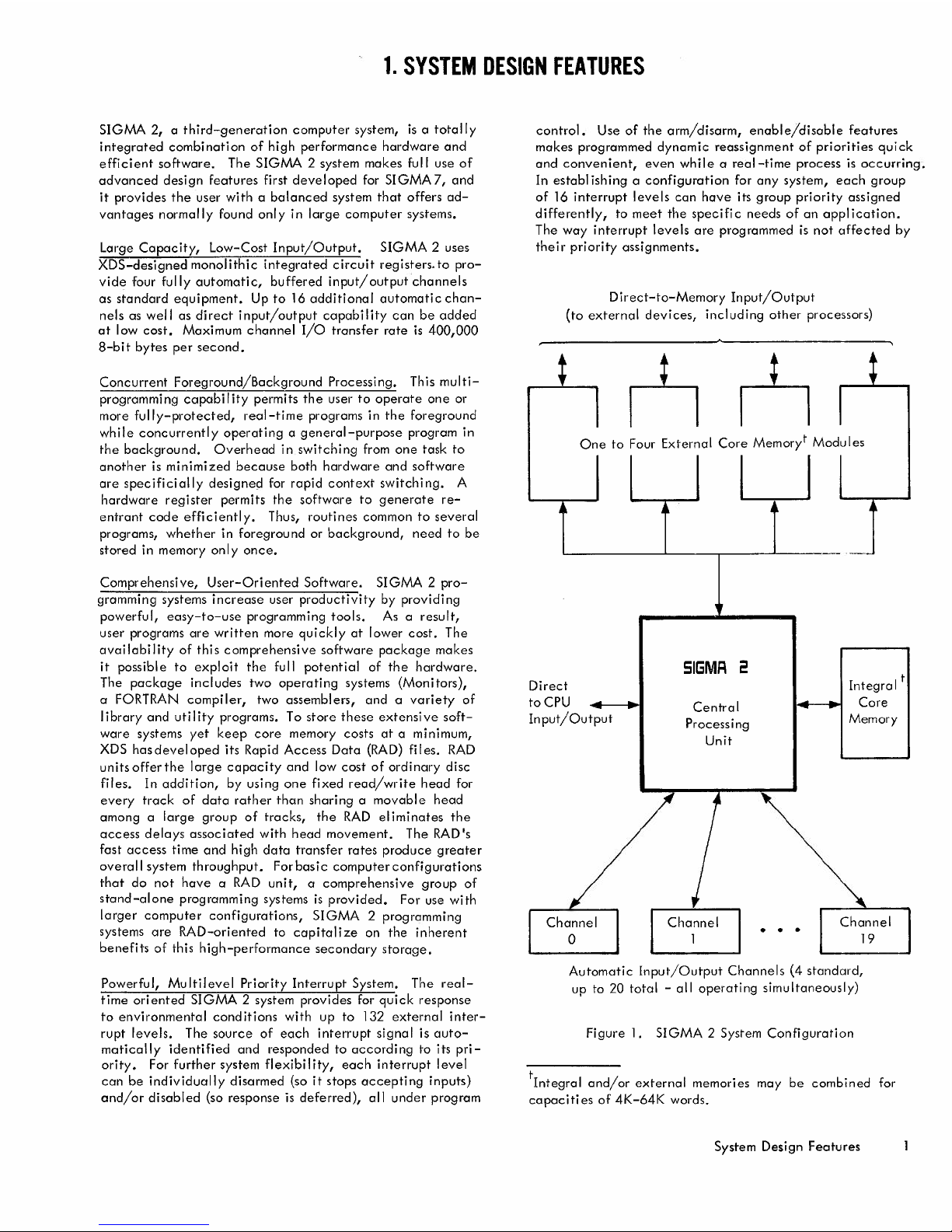

Direct-to-Memory Input/Output

(to external devices, including other processors)

One to Four External Core Memoryt Modules

U

Direct

toCPU

Input/Output

SIGMR 2

Central

Processing

Unit

t

Integra

I

Core

Memory

~lnnel

~

...

Channel

19

Automatic Input/Output Channels (4 standard,

up to 20 total - all operating simultaneously)

Figure 1. SIGMA 2 System Configuration

tIntegral and/or external memories may be combined for

capacities of 4K-64K words.

System Design Features

GENERAL CHARACTERISTICS

In its field, the SIGMA 2 computer is unique in its ability

to function efficiently in general-purpose, real-time, and

multiusage computing environments. The advanced features

and operating characteristics contributing to this capabi Iity

are:

• both word and byte organizotion of memory for maxi-

mum efficiency (words are 16 bits plus

pori+y)

bytes

are 8 bits.)

• 16 memory sizes available, 4096 to 65,536 words

• ability to connect to SIGMA 5 or SIGMA 7 memory

systems

• an extensive instruction set that facilitates efficient

programming; SIGMA 2 instruction characteristics

include:

•

only one word of storage required for each

instruction

•

two levels of indexing and indirect addressing may

be invoked individually or simultaneously

relative addressing (forward and backward)

•

• use of index register 2 as a base address register

• direct reference of up to 1024 addresses; 256

addresses beginning with location zero, 256

addresses beginning with the base address; 256

addresses beginning with the current instruction

location (relative forward), 256 addresses back-

ward from the current instruction (relative

backward)

• eight general-purpose registers to control program

operations; all are available to the program, providing:

• two hardware index registers for preindexing (base

address), post-indexing, or both (double indexing)

• hardware register for subroutine linkages

• double-precision accumulator

• program address register

•

zero register (for a source of zeros)

temporary storage register

•

• rapid context switching, to preserve computer environ-

ment when switching from one program to another, in-

cluding automatic status preservation on interrupt

• both word- and byte-oriented I/O systems, for maxi-

mum flexibil ity

• up to 20 fully automatic I/O channels operating simul-

taneously (4 channels are standard)

• I/O data chaining, for gather-read and scatter-write

operatians

• information transfer rate of approximately one million

words per second for each external memory interface

• direct input/output of a full word without the use of an

I/O channel (optional)

2 General CharacterisHcs

• a real-time priority interrupt system that features:

• 2 to 16 internal interrupt levels and up to 132

external interrupt levels that can be individually

armed, enabled and triggered by program control

• automatic identification, customer-designoted pri-

ority assignments, and extremely fast response time

• memory parity interrupt (optional)

• an optional power fail-safe feature, for automatic

and safe shutdown in the event of a power fai lure,

and unattended startup when power returns

• an optional system protection feature that incl udes

both memory write protection and operation pro-

tection for foreground programs

• up to four real-ti'me clocks (with a choice of reso-

lutions)for independent time bases, available as

an option

a comprehensive array of modular software that expands

in capability and speed as the system grows, with no

reprogramming required

•

• Free-standing software for small systems includes

Symbol and XDS Basic FORTRAN

• XDS Monitor for user convenience and increased

capability in large systems

• Symbol, a basic symbol ic assembler

• Extended Symbol for expanded features

• XDS Basic FORTRAN

• XDS FORTRAN IV

General Debug for symbol ic program

troubl eshooti ng

• Concordance program for documentation

•

• System Generation program for creating instal-

lation master

• Mathematics Library of standard functions

• Bootstrap Generator for producing self-loading

object programs

The wide range of standard and special-purpose peripheral

equipment, already proven in field operations, includes:

• Rapid-Access Data Files: Capacities for 750,000 to

24,000,000 bytes per control unit; transfer rate of

over 185,000 bytes/second; average access time of

17 milliseconds. Fixed read/write head per track

eliminates positioning time associated with movable-

arm storage devices

• Magnetic Tape Units: 9-track, IBM-compatible

60, 000 or 120, 000 bytes/second transfer rate; 7-track,

IBM-compatible, 15,000/20,000/41,700/60,000

characters/second transfer rates

• Paper Tape Readers and Punches: readers with speeds

of 20 and 300 characters/second, punches with speeds

of 10 and 120 characters/second, plus spoolers

• Keyboard Printers: available with or without a paper

tape reader and paper tape punch

• Card Readers: read cards punched in binary or EBCDIC

card code, 200 to 1500 cpm

• Card Punches: binary or EBCDIC card codes, 300 cpm

• Line Printers: fully buffered, with 132 print positions

and carriage control, 600 or 1000 Ipm

• Graph Plotter: for two-axis plotting of data under

digital control, 300 increments/second

• Display Equipment: oscilloscope display units, light

guns, and character and vector generators

• Data Communications Equipment: a complete line of

character- and message-oriented equipment

REAL-TIME AND MULTIUSAGE FEATURES

Real-time applications are characterized by a need for hard-

ware that provides quick response to an external environment,

sufficient speed to keep up with the real-time process itself,

and input/output flexibility to handle a wide variety of types

of data at varying speeds.

Multiusage applications, as implemented in SIGMA 2, are

defined as the combining of real-time and background pro-

cessing techniques into one system. The most difficult gen-

eral computing problem is the real-time application with its

requirements for extreme speed and capacity. Because the

SIGMA 2 system has been designed on a real-time base, it

is well qualified for the mixture of applications in a multi-

usage envi ronment. Many of its hardware featu res that

prove valuable for real-time applications are equally useful

in background processing, but in different ways.

The major features that make SIGMA 2 uniquely suitable

for both real-time and multiusage appl ications are described

in the following paragraphs.

Input/Output Facilities. Three distinct SIGMA 2 input/

output systems offer flexibil ity and capacity to meet the

needs of both real-time and general-purpose users: the

byte-oriented, the direct-to-CPU, and the direct-to-

memory I/O systems.

In the byte-oriented I/O system, each automatic I/O chan-

nel has its own high-speed registers and operates indepen-

dently without requiring attention from the program once it

has been started. Data is transferred one byte (8 bits) at

a time. For high-speed peripherals, bytes are assembled

into words in the I/O section and only one memory refer-

ence is made for two bytes. For slow-speed peripherals,

one reference is made for every byte, with a partial write

operation performed by the memory. All I/O channels

may operate concurrently and parity checking is performed

automatically.

The optional direct-to-CPU input/output system uses only

a single instruction to transfer a full 16-bit data word to

and from the A register. The same instruction that trans-

fers data also provides a 16-bit control field for external

control and selection, and accepts status information

returned from the external device to permit rapid sensing of

an external condition. The direct I/O system is generally

used for short bursts of asynchronous data transfers to avoid

tying up an automatic channel. Direct I/O is also useful

when data is to be accepted at medium to high speeds and

each input must be examined immediately when received.

The optional direct-to-memory input/output system provides

an additional memory bus to each of four external memories.

It is used for very high speed I/O transfers to and from

external devices or other processors. Transfers proceed at

full memory speed on a word-oriented basis, with overlap-

ping of multiple I/O and compute occurring automatically

when multiple memory modules are available.

Priority Interrupt System. In a multiusage environment,

many elements are operating asynchronously with respect to

each other. Thus, having a true priority interrupt system,

as the SIGMA 2 does, is especially important. With it the

computer system can respond quickly (and in proper order)

to the many demands made upon it, without the high over-

head cost of complicated programming, lengthy execution

time, and extensive storage allocations. Programs that deal

with interrupt signals from special equipment must sometimes

be checked out before the equipment is actually available.

To simulate special equipment, any external SIGMA 2 inter-

rupt level can be triggered by the CPU itself through execu-

tion of a single instruction.

Context Switching. When responding to a new set of

interrupt-initiated circumstances, a computer system must

preserve the current operating environment while it sets up

the new environment. In SIGMA 2, relevant information

about the current environment is retained as a 32-bit pro-

gram status doubleword (PSD). When an interrupt occurs,

the current PSD is automatically stored at an arbitrary loca-

tion in memory and the interrupt-servicing routine begins,

following the location into which the PSD is stored. At the

end of the interrupt-servicing routine, the PSD is restored

and the interrupt level cleared.

Protection System. Both real-time and background programs

can be run concurrently in a SIGMA 2 system because the

real-time program can be protected against alteration. The

optional protection feature guarantees that protected areas

of memory cannot -be written into by a program residing in

unprotected memory. The protection feature also prevents

the execution of unprotected instructions that could change

the I/O system or the protection system. The protection

pattern can be changed very rapidly.

Real-Time Clocks. In real-time systems, timing informa-

tion must be provided to cause certain operations to occur

at specific instants. Other timing information is also neces-

sary, such as elapsed time after a given event, or the cur-

rent time of day. SIGMA 2 provides up to four real-time

clocks, with varying degrees of resolution, to meet these

needs. These clocks also facilitate handling of separate

time bases and relative time priorities. Three of the clock

counters can be driven from commercial o, c , line frequency

(60 or 50 Hz), from 2- or 8-Hz oscillators, or from an ex-

ternal input; the first (operational) counter is driven by a

SOO-Hz source.

Real-Time and Multiusage Features 3

2. SYSTEM ORGANIZATION

INFORMATION FORMAT

The basic element of SIGMA 2 information is a 16-bit word

in which the bit positions are numbered from 0 through 15,

as follows:

A SIGMA 2 word can also be divided into two 8-bit parts

(called bytes) in which the bit positions of each byte are

numbered from 0 through 7, as follows:

Byte 0

Byte 1

12

31.c..5

6701231.567

Two SIGMA 2 words can be combined to form a 32-bit ele-

ment (called a doubleword) in which the bit positions are

numbered from 0 through 31, as follows:

Most significant word Least significant word

o

I 2 3 4 5 6 7 B 9 10 11 12 13 \•• 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

A doubleword is always referred to by the address of its

most significant

word,

Binary information in SIGMA 2 computers is generally

expressed in hexadecimal notation because four binary dig-

its of information can be expressed by a single hexadecimal

digit. Thus, a byte can be expressed with a string of 2

hexadecimal digits, a word with a string of 4 hexadecimal

digits, and a doubleword with a string of 8 hexadecimal

digits. The following table lists hexadecimal digits and

their binary and decimal equivalents.

Hexadecimal Binary Decimal

0 0000 0

1 0001 1

2

0010

2

3 001l 3

4

0100

4

5 0101 5

6 0110 6

7

0111 7

8

1000

8

9 1001 9

A

1010 10

B 1011

11

C

1100

12

D 1101 T3

E

1110 14

F 1111 15

In this reference manual, a hexadecimal number isdisplayed

as a string of hexadecimal digits surrounded by single quotes

and preceded by the letter "X". For example, the binary

number 01011010 is expressed in hexadecimal notation as

X'5A'. Hexadecimal numbers are generally used to denote

4 System.Organization

addresses and data values; however, there are many instan-

ces in which decimal numbers are more meaningful or are

customary. Because the SIGMA assembler systems perform

decimalJhexadecimal conversions, addresses and data

values may be expressed as decimal numbers.

In SIGMA 2, fixed-point data consists of a 15-bit integer

and a sign. Positive numbers are represented in true binary

form, with a sign of zero. Negative numbers are repre-

sented in two's complement form, with a sign of one. All

arithmetic operations assume that this format is used. Logi-

cal operations in SIGMA 2, on the other hand, assume that

a logical data word format, consisting of 16 bits without

sign, is used.

CORE MEMORIES

A SIGMA 2 computer can be equipped with either {or both}

oftwo different types of core memory: integral and external.

A magnetic core memory can be provided as an integral port

of the SIGMA 2 central processor configuration. This inte-

gral memory is available only to the SIGMA 2 central pro-

cessor, and it provides a portion of the total SIGMA 2

system memory. In order to implement the maximum mem-

ory capacity {64K words}, external memory is required in

addition to {or in place of} the integral memory.

The external memory provides independent access poths for

ather processors or special (customer designed) devices;

thus, the SIGMA 2 central processor may share common

storage with other SIGMA 2's, SIGMA 5's, SIGMA 7's,

special I/O processors, or other devices. By using two

SIGMA 7 memory modules (of 16K words each) the external

memory system may constitute a 64K SIGMA 2 memory

system. An external memory adaptor allows the SIGMA 2

computer to treat each 32-bit word of the SIGMA 7memory

system as two 16-bit words. Special registers allow the

programmer to establish a correspondence between any

4096-word portion of SIGMA 2 memory addresses and any

2048-word portion of SIGMA 5/7 memory addresses

(32-bit word).

If integral memory is included in the system that also has

external memory, the integral memory utilizes the lower-

numbered memory locations. For example, if a 16K integral

memory and 16K words of external memory are used, the

integral memory contains locations 0 through 16K-l and

the external memory contains locations 16K through 32K-1.

When the SIGMA 2 memory system is 64K words, the mem-

ory is "wrap-around", or "circular", where the next loca-

tion after 64K-l is location

O.

If a system has less then

64K words, any fetch operation from a nonexistent storage

location causes zeros to be fetched, in which case a

memory parity error also occurs. An attempt to store infor-

mation in a nonexistent storage location essentially results

in a "no operation".

See Appendix C for more information on memory addressing.

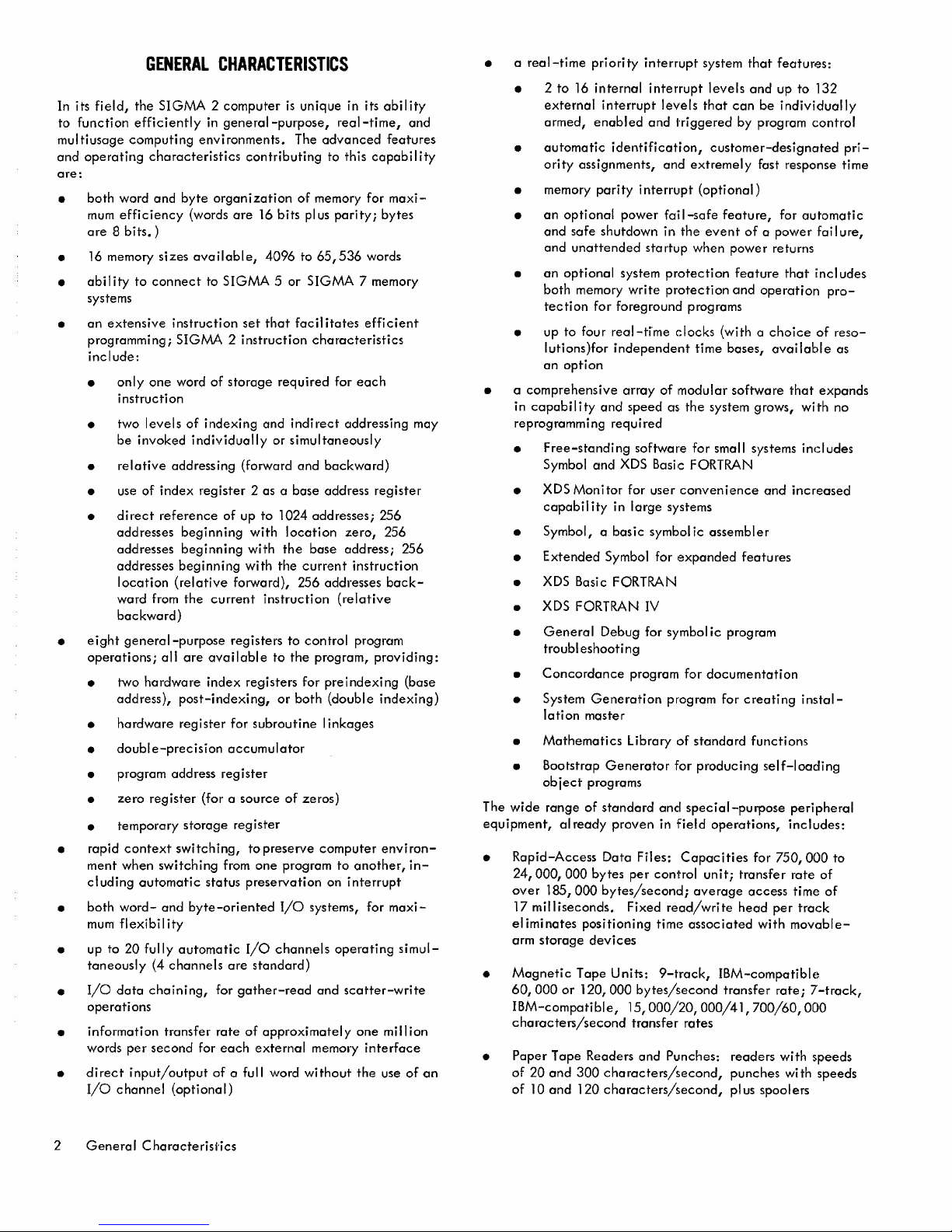

CENTRAL PROCESSING UNIT

The various elements in a SIGMA 2 system - memories,

input/output devices, and device controllers - are orga-

nized around a central processing unit (CPU), whichis.the

primary control Iing element for most system functions. Not

only does the CPU execute instructions, but it also controls

all input/output for both the byte-oriented and the direct

I/O systems. Basically, the SIGMA 2 CPU consists of a

register block and an arithmetic and control unit (see Fig-

ure 2).

REGISTER BLOCK

The CPU register block consists of high-speed, integrated-

circuit registers that are capable of communicating with the

arithmetic and control unit simultaneous with the operation

of the core memory. The register block is functionally di-

vided into three parts: general registers, I/o channel reg-

isters, and memory protection system registers. Each register

of the block is 16 bits in length and is identified by an ad-

dress code in the range 0 through 7 for general registers,

8 through 47 for I/O channel registers, and 0 through 15

for protection system registers. Specific configurations of

the READ DIRECTand WRITEDIRECTinstructions are used

to transfer information from the accumulator (general reg-

ister 7) to other registers of the register block, and vice

versa (see Chapter 3, "Direct Control Instructions").

General Registers

Eight registers of the register block are used mainly for

storage of program control information. These registers

are addressable by a COpy instruction (for register-to-

register operations) and by certain configurations of the

READ DIRECTand WRITEDIRECTinstructions (for internal

computer control operations). The functions of the general

registers are as follows:

Address Designation Functi on

0 Z

Source of zeros for copy

1

P

Program address

2

L Link address

3

T

Temporary storage

4

Xl

Index 1 (post-index)

5

X2 Index 2 (pre-index or base)

6

E Extended accumuIator

7 A Accumulator

A reference to the Z register in a COpy instruction pro-

duces a value of zero. The P register contains the address

of the next instruction which would be executed in normal

sequence. The six remaining registers can be used for vari-

ous purposes by a program.

I/O Channel Registers

The next eight registers of the register block are used to

hold control information for the four standard SIGMA 2

I/o channels (two registers are used for each channel).

Additional I/O channel registers can be added, in groups

of eight (up to a maximum of 40 registers, or 20 I/O chan-

nels). The I/O channel registers are loaded with control

information from the accumulator by a specific configuration

of the WRITEDIRECTinstruction. The operation of I/O

channel registers is described in Chapter 4, "I/O Control

Doublewords" .

Protection System Registers

Sixteen optional registers are available for both operation

protection and memory write protection. Each bit in this

16-register group provides protection for a single 256-word

"page" of core memory. (A complete discussion of this

feature is given on page 13.)

ARITHMETIC AND CONTROL UNIT

The arithmetic and control unit contains the necessary regis-

ters and control circuitry to access general registers or core

memory, to modify instruction addresses, to perform arithme-

tic and logical operations, to provide indications of compu-

tational results, and to preserve interrupt status information.

Basically, the arithmetic and control unit consists of arith-

metic and control registers and program status indicators.

Arithmeti c and Control Registers

Three 16-bit registers (S, H, and D) and an adder are used

to perform arithmetic and logical manipulations and to modi-

fy instruction addresses (see" Effective Address Computation").

Program Status Doubleword

When an interrupt occurs, the current state of the operating

program is saved by the automatic storing of a program status

doubleword (PSD), which is generated automatically from

information in the program status indicators and general reg-

isters. When stored in memory, the PSD has the format

The first word of the PSD contains five status indicators:

protected program (PP), internal interrupt inhibit (II), ex-

ternal interrupt i.!1hibit (EI), overflow

(0),

and carry (C).

The second word of the PSD is the current contents of the

program address register (general register 1). (Use of the

PSD in interrupt entry and exit is discussed on page 12.)

The protected program indicator bit is a 1 if the current pro-

gram is located in an area of core memory that is protected

by the memory protection option; otherwise, this bit is a

O.

The internal and external interrupt inhibits determine whe-

ther a program interruption can occur. If an interrupt in-

hibit is 0, the respective interrupt levels are allowed to

interrupt the program being executed. Conversely, if an

interrupt inhibit is a 1, the respective interrupt levels are

inhibited from interrupting the program. Inhibiting inter-

rupt levels also removes them from the interrupt system pri-

ority chain, allowing a lower-priority interrupt level to

interrupt the program. (Note, however, that the op-

tional override group of internal interrupt levels cannot

be inhibited.)

Central Processing Unit 5

REGISTER BLOCK

ARITHMETIC AND CONTROL UNIT

01

Zero

I

S

I

Memory Address

I

Arithmetic

lL

Program address

I

HI

Control

I

>

and control

registers

21

Link address

I

D

I

Memory Data

I

3L

Temporary storage

I

General

I

registers

0

41

Index 1

Protected program indicator

5 1

Index 2 (base)

I

D

Internal interrupt inhibit

I

D

Program

6

I

Extended accumul ator

External interrupt inhibit

status

indicators

7

I

Accumulator

I

D

Overflow indicator

0

Carry indicator

8L

Channel 0

I

<III

To/from

9L

Channel 0

I

core memory

·

Standard

·

I/O channel

I

Channel

3

I

registers

14

To/from

~

byte I/o system

15 [

Channel

3

I

I

..

READDIRECT

16

I

Channel 4

I

I

17

I

Channel 4

I

WRITEDIRECT

Optional

·

I/O channel

-

·

I

461

Channel

19

I

registers

~

Interrupts

Priority interrupt system

..•

471

Channel 19

1

I

o

~ddresses 0 through 4K-l

Protection

1

fAddresses 4K through 8K-l

I

>

system

·

regi sters

·

(optional)

·

ISIAddresses 60K through 64K-11

Figure 2. SIGMA 2 Central Processing Unit

6 Central Processing Unit

The overflow and carry indicators reflect the results of

various operations. The overflow indicator is set to 1 if

overflow occurs during an arithmetic operation. If, after

an arithmetic operation, there is a carry from the most sig-

nificant position (the sign' position) of the adder, the carry

indicator is set to

1.

This feature is useful in multiple-

precision operations, where the entire 16 bits are considered

to be the low-order part of an extended operation. Also,

on a subtract operation, the carry indicator will be set to

1 if there is a "borrow" from the sign position of the adder.

In arithmetic operations, the carry and overflow indicators

operate as described above. Some instructions, however,

use these indicators to record status information generated

as a resul t of the operation.

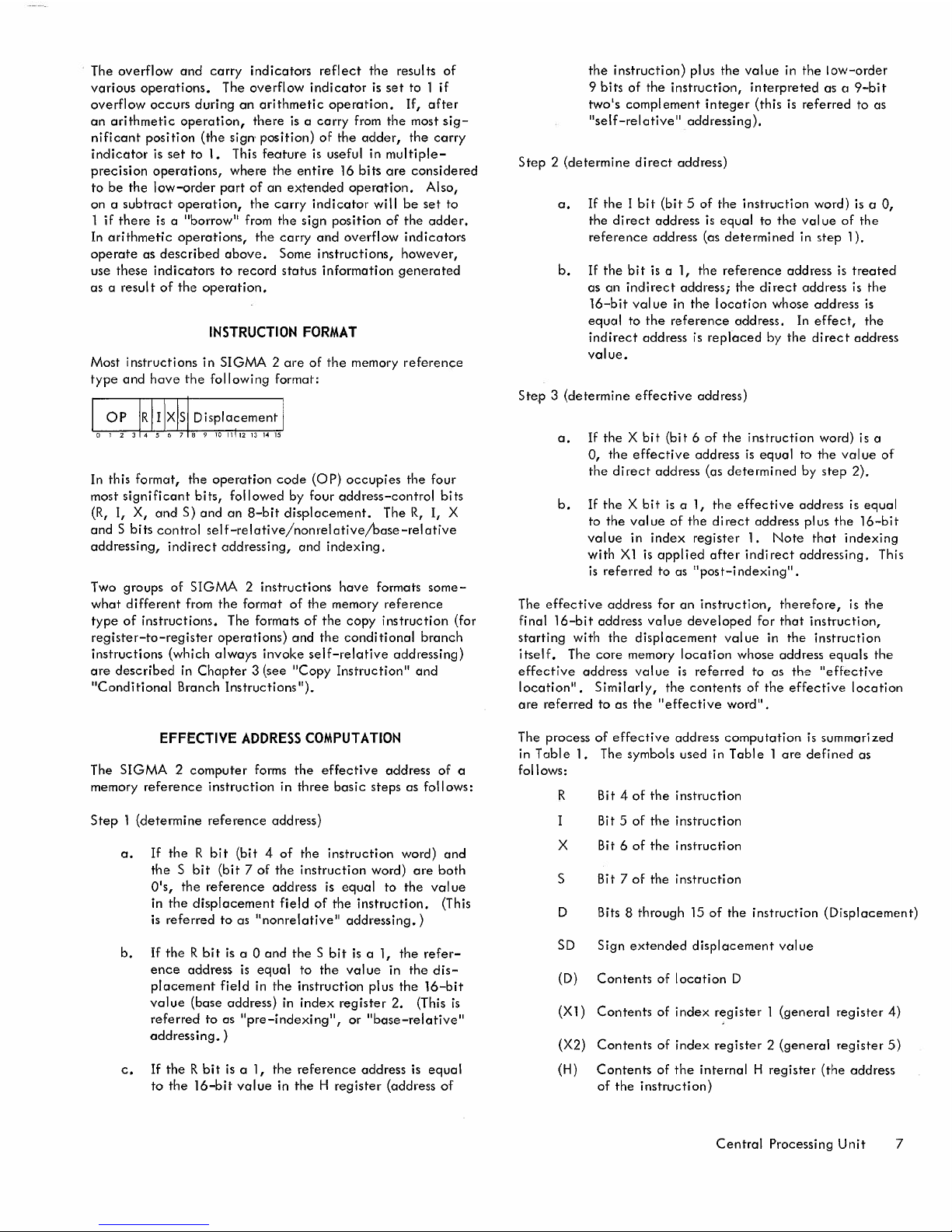

INSTRUCTION FORMAT

Most instructions in SIGMA 2 are of the memory reference

type and have the following format:

In this format, the operorion code (OP) occupies the four

most significant bits, followed by four address-control bits

(R, I, X, and S) and an 8-bit displacement. The R, I, X

and S bits control self-relative/nonrelative/base-relative

addressing, indirect addressing, and indexing.

Two groups of SIGMA 2 instructions have formats some-

what different from the format of the memory reference

type of instructions. The formats of the copy instruction (for

register-to-register operations) and the conditional branch

instructions (which always invoke self-relative addressing)

are described in Chapter 3 (see "Copy Instruction" and

"Conditional Branch Instructions").

EFFECTIVE ADDRESS COMPUTATION

The SIGMA 2 computer forms the effective address of a

memory reference instruction in three basic steps as follows:

Step 1 (determine reference address)

a. If the R bit (bit 4 of the instruction word) and

the S bit (bit 7 of the instruction word) are both

O's, the reference address is equal to the val ue

in the displacement field of the instruction. (This

is referred to as "nonrelative" addressing.)

b. If the R bit is a 0 and the S bit is a 1, the refer-

ence address is equal to the val ue in the dis-

placement field in the instruction plus the 16-bit

value (base address) in index register 2. (This is

referred to as "pre-indexing", or "base-relative"

addressing. )

c. If the R bit is a 1, the reference address is equal

to the 16-bit value in the H register (address of

the instruction) plus the value in the low-order

9 bits of the instruction, interpreted as a 9-bit

two's complement integer (this is referred to as

"self-relative" addressing).

Step 2 (determine direct address)

a. If the I bit (bit 5 of the instruction word) is a 0,

the direct address is equal to the value of the

reference address (as determined in step 1).

b. If the bit is a 1, the reference address is treated

as an indirect address; the direct address is the

16-bit value in the location whose address is

equal to the reference address. In effect, the

indirect address is replaced by the direct address

value.

Step 3 (determine effective address)

a. If the X bit (bit 6 of the instruction word) is a

0, the effective address is equal to the val ue of

the direct address (as determined by step 2).

b. If the X bit is a 1, the effective address is equal

to the value of the direct address plus the 16-bit

value in index register 1. Note that indexing

withXlis applied after indirect addressing. This

is referred to as "post-indexing".

The effective address for an instruction, therefore, is the

final 16-bit address value developed for that instruction,

starting with the displacement value in the instruction

itself. The core memory location whose address equals the

effective address value is referred to as the "effective

location". Similarly, the contents of the effective location

are referred to as the "effective word".

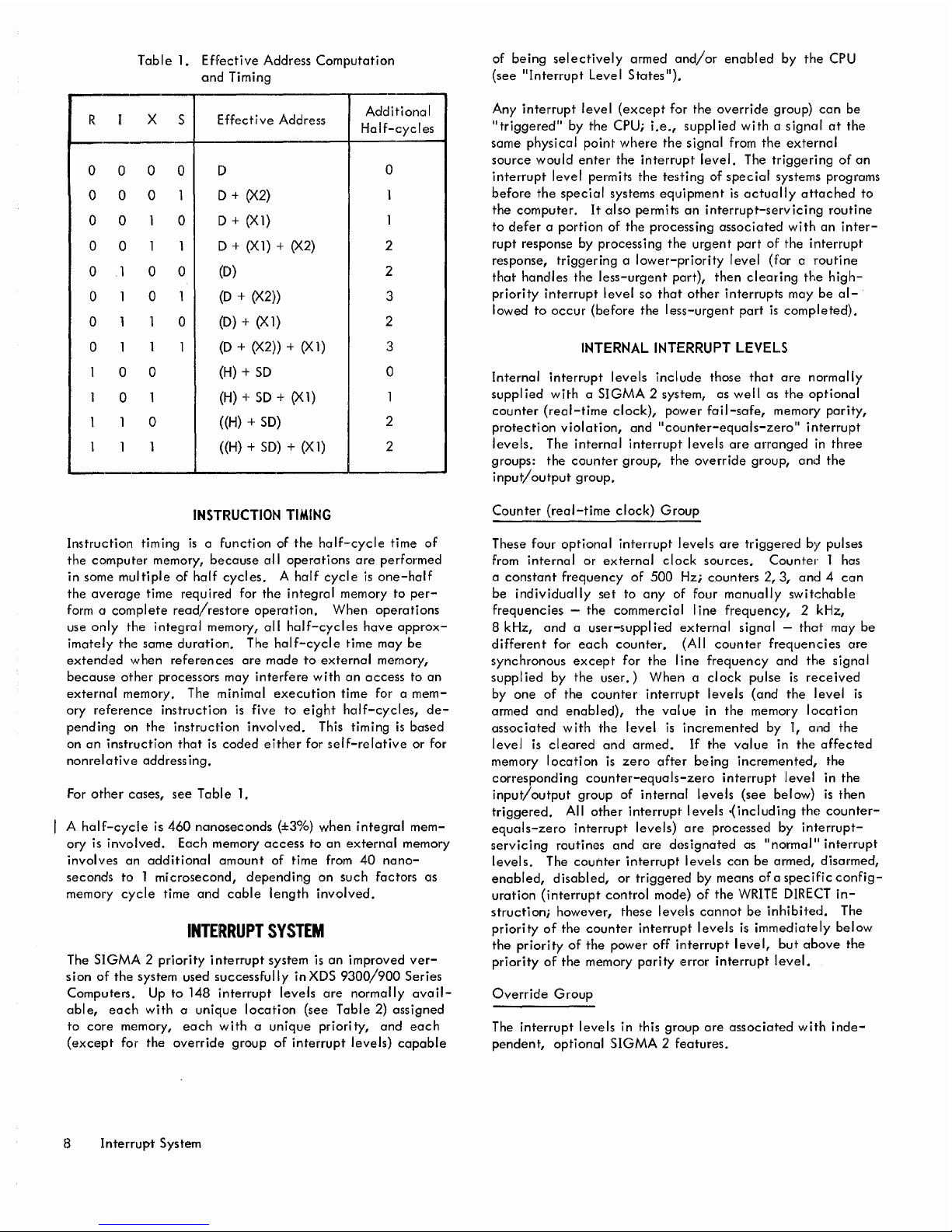

The process of effective address computation is summarized

in Table 1. The symbols used in Table 1 are defined as

follows:

R Bit 4 of the instruction

Bit 5 of the instruction

X Bit 6 of the instruction

S

Bit 7 of the instruction

D

Bits 8 through 15 of the instructian (Displacement)

SD Sign extended displacement value

(D) Contents of location D

(Xl)

Contents of index register 1 (general register 4)

(X2) Contents of index register 2 (general register 5)

(H) Contents of the internal H register (the address

of the instruction)

Central Processing Unit 7

Table 1. Effective Address Computation

and Timing

R I

X

5

Effective Address

Additional

HaIf-cyc Ies

_.

0

0 0 0

D

0

0 0 0

1

D+ (X2)

1

0 0

1

0

D + (Xl)

1

0

0

1 1

D + (Xl) + (X2) 2

0

1

0 0

(D) 2

0

1

0

1

(D + (X2))

3

0

1 1

0

(D) + (Xl) 2

0

1

1

1

(D + (X2)) + (Xl)

3

1

0 0

(H) + SD 0

1

0

1

(H) + SD + (Xl)

1

1

1

0 «H) + SD)

2

1 1 1

«H) + SD) + (Xl)

2

'---.

INSTRUCTION TIMING

Instruction timing is a function of the half-cycle time of

the computer memory, because all operations are performed

in some multiple of half cycles. A half cycle is one-half

the average time required for the integral memory to per-

form a complete read/restore operation. When operations

use only the integral memory, all half-cycles have approx-

imately the same duration. The half-cycle time may be

extended when references ore made to external memory,

because other processors may interfere with an access to an

external memory. The minimal execution time for a mem-

ory reference instruction is five to eight half-cycles, de-

pending on the instruction involved. This timing is based

on an instruction that is coded either for self-relative or for

nonrelative addressing.

For other cases, see Table 1.

A half-cycle is 460 nanoseconds (±3%) when integral mem-

ory is involved. Each memory access to an external memory

involves an additional amount of time from 40 nano-

seconds to 1 microsecond, depending on such factors as

memory cycle time and cable length involved.

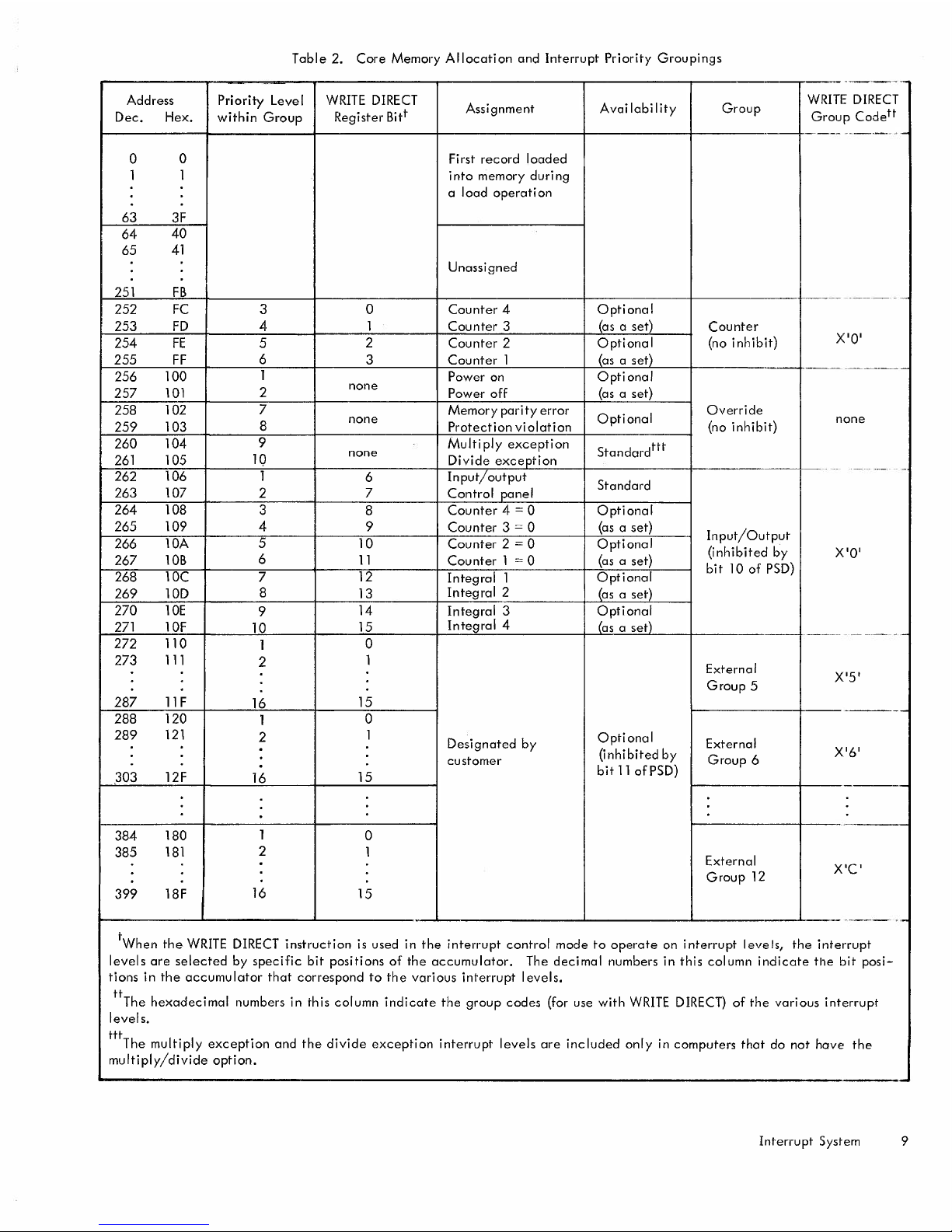

INTERRUPT SYSTEM

The SIGMA 2 priority interrupt system is an improved ver-

sion of the system used successfully inXDS 9300/900 Series

Computers. Up to 148 interrupt levels are normally avail-

able, each with a unique location (see Table 2) assigned

to core memory, each with a unique priority, and each

(except for the override group of interrupt levels) capable

8 Interrupt System

of being selectively armed and/or enabled by the CPU

(see "Interrupt Level States").

Any interrupt level (except for the override group) can be

"triggered" by the CPU; i.e., supplied with a signal at the

same physical point where the signal from the external

source would enter the interrupt level. The triggering of an

interrupt level permits the testing of special systems programs

before the special systems equipment is actually attached to

the computer. It also permits an interrupt-servicing routine

to defer a portion of the processing associated with an inter-

rupt response by processing the urgent part of the interrupt

response, triggering a lower-priority level (for a routine

that handles the less-urgent part), then clearing the high-

priority interrupt level so that other interrupts may be al-

lowed to occur (before the less-urgent part is completed).

INTERNAL INTERRUPT LEVELS

Internal interrupt levels include those that are normally

supplied with a SIGMA 2 system, as well as the optional

counter (real-time clock), power fail-safe, memory parity,

protection violation, and "counter-equals-zero" interrupt

levels. The internal interrupt levels are arranged in three

groups: the counter group, the override group, and the

input/output group.

Counter (real-time clock) Group

These four optional interrupt levels are triggered by pulses

from internal or external clock sources. Counter 1 has

a constant frequency of 500 Hz; counters 2, 3, and 4 can

be individually set to any of four manually switchable

frequencies - the commercial Iine frequency, 2 kHz,

8 kHz, and a user-supplied external signal - that may be

different for each counter. (All counter frequencies are

synchronous except for the Iine frequency and the signal

supplied by the user.) When a clock pulse is received

by one of the counter interrupt levels (and the level is

armed and enabled), the value in the memory location

associated with the level is incremented by 1, and the

level is cleared and armed. If the value in the affected

memory location is zero after being incremented, the

corresponding counter-equals-zero interrupt level in the

input/output group of internal levels (see below) is then

triggered. All other interrupt levels .(including the counter-

equals-zero interrupt levels) are processed by interrupt-

servicing routines and are designated as "normal" interrupt

levels. The counter interrupt levels can be armed, disarmed,

enabled, disabled, or triggered by means of a specific config-

uration (interrupt control mode) of the WRITEDIRECTin-

struction; however, these levels cannot be inhibited. The

priority of the counter interrupt levels is immediately below

the priority of the power off interrupt level, but above the

priority of the memory parity error interrupt level.

Override Group

The interrupt levels in this group are associated with inde-

pendent, optional SIGMA 2 features.

Table 2. Core Memory Allocation and Interrupt Priority Groupings

--

-~-.~---~

Address Priority Level WRITEDIRECT

Assignment

Avai labiIity Group

WRITEDIRECT

Dec. Hex. within Group

Register Bitt

Group Codett

---

---,-

...

---.

,-

0 0

First record loaded

1 1 into memory duri ng

a load operati on

63 3F

64

40

65

41

Unassigned

251 FB

-----

-_------

252 Fe 3 0

Counter 4 Optional

253 FD 4

1 Counter 3 (as a set)

Counter

254 FE

5

2

Counter 2

Optional

(no inhibit)

X'O'

255 FF

6

3 Counter 1

(as a set)

256 100

1

Power on Optional

--_

----------

257

101

2

none

Power off

(as a set)

258

102

7

Memory parity error

Optional

Override

259 103

8

none

Protection violation

(no inhibit)

none

260

104

9

Multiply exception

Standardttt

261 105 10

none

Divide exception

262

106 1

Input/output

-

,~-

-

6

Standard

263 107

2

7

Control panel

264 108

3

8

Counter 4==0 Optional

265 109 4 9

Counter 3==0

(as a set)

Input/Output

266

lOA

5

10

Counter 2==0 Optional

267

lOB

6

11

Counter 1==0

(as a set)

(inhibited by

X'O'

268 10C

7

12

Integral 1

Optional

bit 10 of PSD)

269 10D

8

13

Integral 2

(as a set)

270 10E

9

14

Integral 3

Optional

271 10F

10

15

Integral 4

(as a set)

--

-~----

-----_.-

272 110

1

0

273

111

2

1

External

Group 5

X'5'

287 11F

16

15

288

120

0

------

1

289 121

2

1

Designated by

Optional

External

·

(inhibited by

X'6'

·

customer

bit 11 of PSD)

Group 6

303

12F

16

15

--

384

180

1

0

385

181

2

1

External

·

X'C'

Group 12

399 18F

16

15

.

----_

..

-

,_

tWhen the WRITEDIRECTinstruction is used in the interrupt control mode to operate on interrupt levels, the interrupt

levels are selected by specific bit positions of the accumulator.

The decimal numbers in this column indicate the bit posi-

tions in the accumulator that correspond to the various interrupt levels.

ttThe hexadecimal numbers in this column indicate the group codes (for use with WRITEDIRECT)of the various interrupt

levels.

tttThe multiply exception and the divide exception interrupt levels are included only in computers that do not have

the

multiply/divide option.

Interrupt System 9

The override interrupt levels are always armed (cannot be

disarmed), always enabled (cannot be disabled), cannot be

triggered by a WRITE DIRECT instruction, and cannot be

inhibited.

Power Fail-Safe. The two optional power fail-safe inter-

rupt levels are used to enter routines that save and restore

volati Ie information in the event of a power fai lure. The

power-off interrupt level is triggered whenever the power

supply voltage falls below a safe limit; likewise, the power-

on interrupt level is triggered whenever power returns to

safe limits. The power fail-safe interrupt levels have a

higher-priority than the counter interrupt levels.

Memory Parity Error. The memory parity interrupt option

is used to inform the program (or the computer operator) that

a parity error has occurred upon accessing memory for an

instruction, direct address (in the case of indirect address-

ing), or an operand. If the option is installed and the

PARITY ERROR switches on the control panel are in the

INTERRUPT/NORMAL positions when a parity error occurs,

the memory parity interrupt level is triggered.

Protection Violation. The protection option includes the

protection violation interrupt level. (The protection option

is described on page 13.) If the option is installed and the

PROTECT switch on the processor control panel is in the ON

position when a protection violation is encountered, the

protection violation interrupt level is triggered.

Multiply/Divide Exception. The multiply/divide option

includes the additional logic required for executing the

MULTIPLY and DIVIDE instructions. If the option is not

installed, the multiply exception interrupt level and the

divide exception interrupt levels are provided to allow for

simulation of the unimplemented instructions. In this case,

the appropriate exception interrupt level is triggered, when-

ever an attempt is made to execute a MULTIPLY or DIVIDE

instructi on.

Input/Output Group

This interrupt group includes two standard interrupt levels

and eight optional levels. The I/O and control panel in-

terrupt levels are standard; the four counter-equals-zero

interrupt levels and the four integral interrupt levels are

optional.

All interrupt levels in the input/output group can be in-

hibited by means of the internal interrupt inhibit (bit 10

of the PSD), and can be armed, disarmed, enabled, dis-

abled, and triggered by specific configurations of the

WRITE DIRECT instruction.

I/O Interrupt Level. The I/O interrupt level accepts in-

terrupt signals from the standard I/o system. An I/O rou-

tine must contain an ACKNOWLEDGE I/o INTERRUPT

(AIO) instruction that identifies the source and cause of

an I/O interrupt.

Control Panel Interrupt Level. The control panel interrupt

level is connected to the INTERRUPT switch on the proces-

sor control panel. The control panel interrupt level can

10 Interrupt System

thus be triggered by the computer operator, allowing him to

initiate a specific routine.

Counter-equals-zero Interrupt Levels. The counter-equals-

zero interrupt levels are associated with the four optional

real-time clocks. For each clock option installed, the CPU

automatically increments one of four core memory {counter}

locations as the clock pulses are received. When the value

in a counter location equals zero, the corresponding counter-

equals-zero interrupt level is triggered. Counting continues

after the interrupt level is triggered; unless the counter in-

terrupt level is disarmed or disabled, counting will continue

until zero is reached again. (See "Counter Interrupt Pro-

cessing". )

EXTERNAL INTERRUPT LEVELS

A SIGMA 2 system can contain up to 9 groups of optional

interrupt levels, with up to 4 levels in the first integral

group and up to 16 levels in each of the 8 external groups.

The integral levels are controlled as part of the input/

output group of internal interrupt levels (i. e., inhibited

with the internal interrupt inhibit), and have a lower pri-

ority than the other levels in the input/output group. All

interrupts are controlled separately (i.e., inhibited with the

external interrupt inhibit), and can be arranged in almost

any priority sequence (see "Interrupt Priority Sequenc.e").

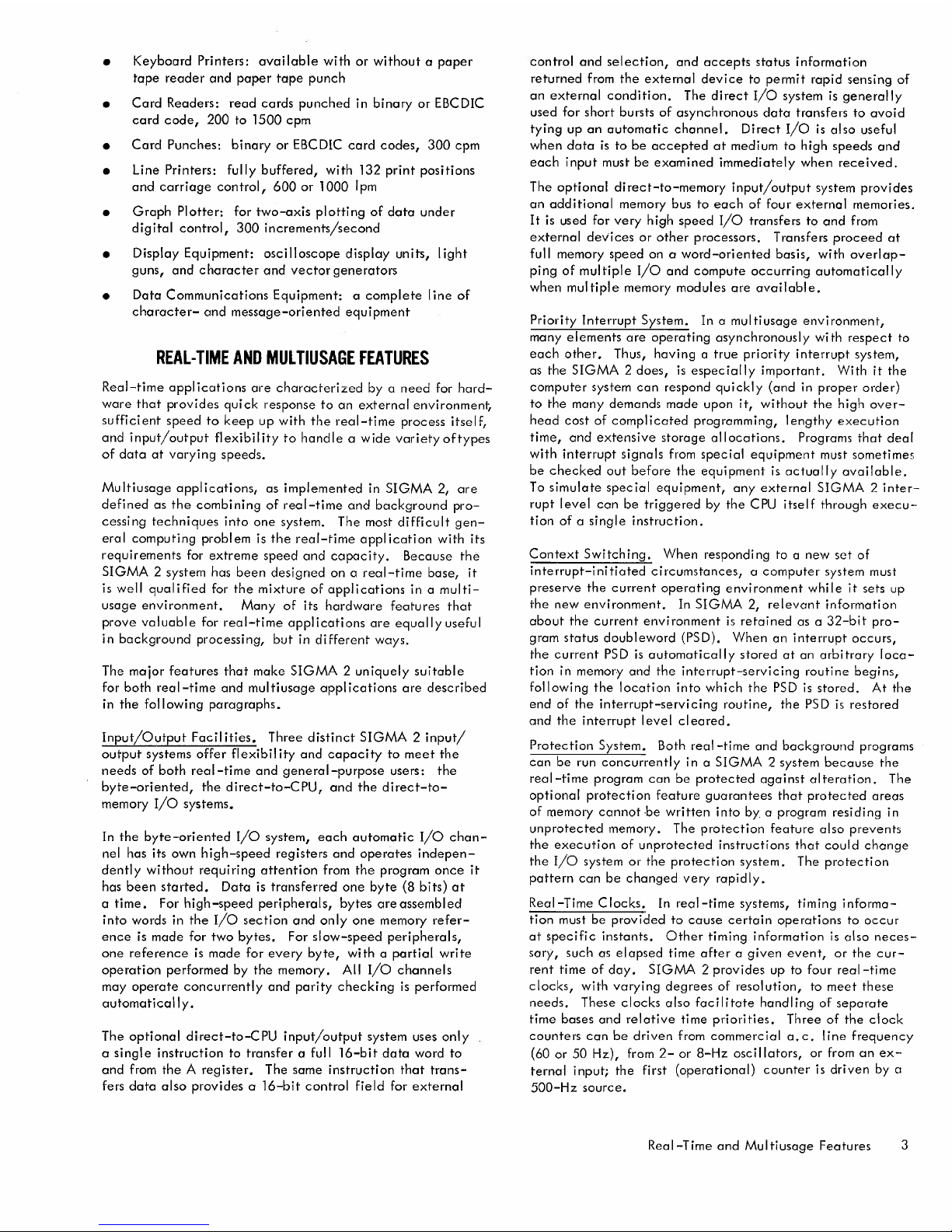

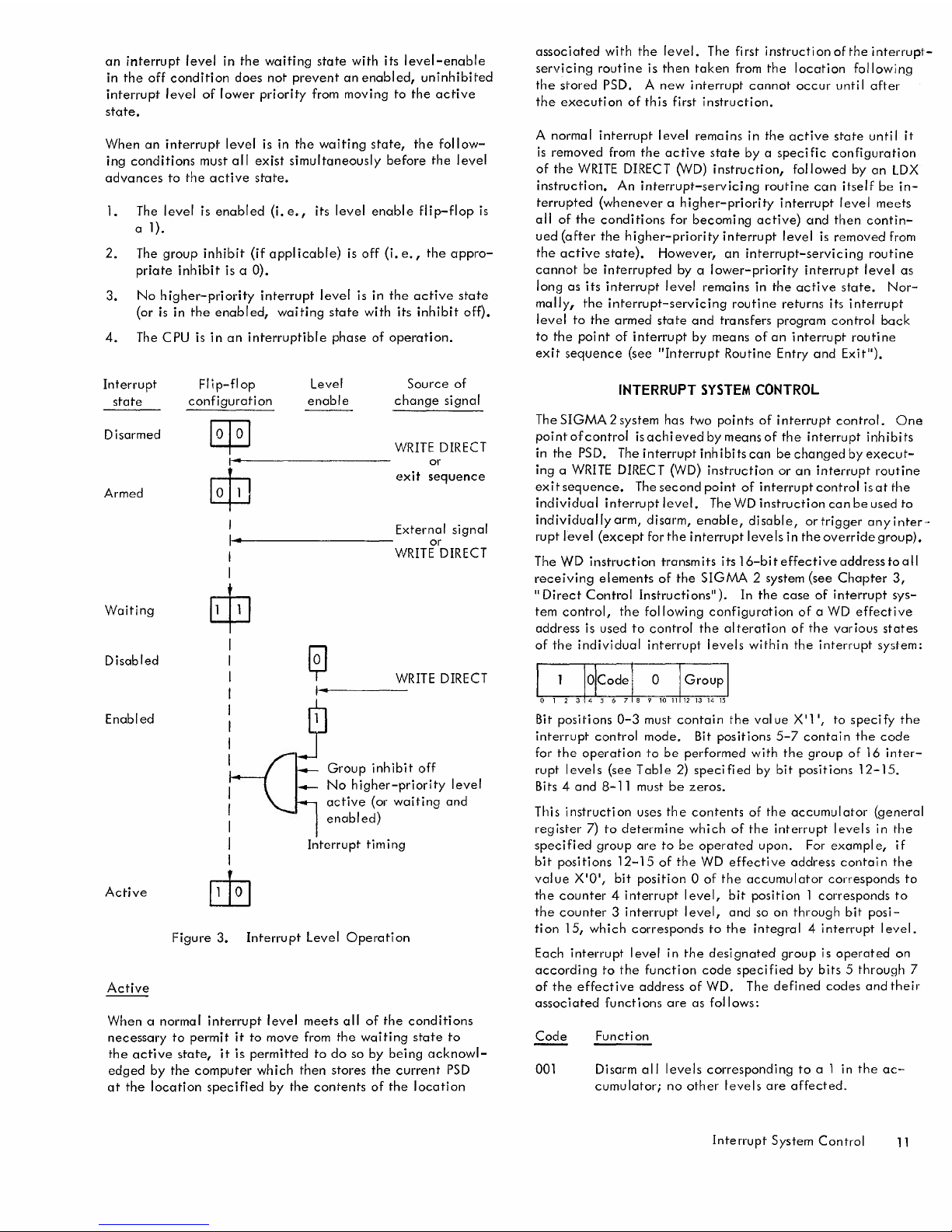

INTERRUPT LEVEL STATES

A SIGMA 2 interrupt level is mechanized by means of three

flip-flops. Twoof the flip-fl opsare used to define any offour

mutually exclusive states: disarmed, armed, waiting, and ac-

tive. Thethird fl

lp-Flop

is used to enabl e or disable the level.

Thevarious states and the condition causing changes in state

(see Figure 3) are described in the following paragraphs.

Disarmed

When an interrupt level is in the disarmed state, no signal

to that interrupt level is admitted; that is, no record is re-

tained of the signal, nor is any program interrupt caused by

it at any time.

Armed

When an interrupt level is in the armed state, it is capable

of accepting and remembering an interrupt signal. The re-

ceipt of such a signal advances the interrupt level to the

waiting state.

Waiting

When an interrupt level in the armed state receives an inter-

rupt signal, it advances to the waiting state, and remains in

the waiting state until it is allowed to advance to the active

state.

If the level-enable flip-flop is off, the interrupt level can

undergo all state changes except that of moving from the

waiting to the active state. Furthermore, if this flip-flop

is off, the interrupt level is completely removed from the

chain that determines the priority of access to the C PU. Thus,

an interrupt level in the waiting state with its level-enable

in the off condition does not prevent an enabled, uninhibited

interrupt level of lower priority from moving to the active

state.

When an interrupt level is in the waiting state, the follow-

ing conditions must all exist simultaneously before the level

advances to the active state.

1. The level is enabled (i. e., its level enable fl ip-flop is

a

I).

2. The group inhibit (if applicable) is off (i. e., the appro-

priate inhibit is a OJ.

3. No higher-priority interrupt level is in the active state

(or is in the enabled, waiting state with its inhibit off).

4.

The CPU is in an interruptible phase of operation.

Interrupt

state

Flip-flop

configurati on

Source of

change signal

Level

enable

Disarmed

WRITEDIRECT

ar

exit sequence

Armed

External signal

~------------------ or

WRITEDIRECT

Waiting

I

I

$

Disabled

WRITEDIRECT

Enabled

Active

I

I

I

I

I

~

Group inhibit off

No higher-priority level

active (or waiting and

enabled)

Interrupt timing

Figure 3. Interrupt Level Operation

Active

When a normal interrupt level meets all of the conditions

necessary to permit it to move from the waiting state to

the active state, it is permitted to do so by being acknowl-

edged by the computer which then stores the current PSD

at the location specified by the contents of the location

associated with the level. The first instruction of the interrupt-

servicing routine is then taken from the location following

the stored PSD. A new interrupt cannot occur untiIafter

the execution of this first instruction.

A normal interrupt level remains in the active state until it

is removed from the active state by a specific configuration

of the WRITEDIRECT(WD) instruction, followed by an LDX

instruction. An interrupt-servicing routine can itself be in-

terrupted (whenever a higher-priority interrupt level meets

all of the conditions for becoming active) and then contin-

ued (after the higher-priority interrupt level is removed from

the active state). However, an interrupt-servicing routine

cannot be interrupted by a lower-priority interrupt level as

long as its interrupt level remains in the active state. Nor-

mally, the interrupt-servicing routine returns its interrupt

level to the armed state and transfers program control back

to the point of interrupt by means of an interrupt routine

exit sequence (see "Interrupt Routine Entry and Exit").

INTERRUPT SYSTEM CONTROL

The SIGMA 2 system has two points of interrupt control. One

point of control isachieved by meansof the interrupt inhibits

in the PSD. Theinterruptinhibitscan be changed byexecut-

ing a WRITEDIRECT(WD) instruction or an interrupt routine

exit sequence. The second point of interrupt control isatthe

individua I interrupt level. The WD instruction can be used to

individually arm, disarm, enable, disable, or trigger any inter-

rupt level (except for the interrupt levels in the override group).

The WD instruction transmits its 16-biteffective address toall

receiving elements of the SIGMA 2 system (see Chapter 3,

"Direct Control Instructions"). In the case of interrupt sys-

tem control, the following configuration of a WD effective

address is used to control the alteration of the various states

of the individual interrupt levels within the interrupt system:

Bit positions 0-3 must contain the value X'I', to specify the

interrupt control mode. Bit positions 5-7 contain the code

for the operation to be performed with the group of 16 inter-

rupt levels (see Table 2) specified by bit positions 12-15.

Bits 4 and 8-11 must be zeros.

Thi5instructi on uses the contents of the accumu Iator (general

register 7) to determine which of the interrupt levels in the

specified group are to be operated upon. For example, if

bit positions 12-15 of the WD effective address contain the

value X'O', bit position 0 of the accumulator corresponds to

the counter 4 interrupt level, bit position 1 corresponds to

the counter 3 interrupt level, and so on through bit posi-

tion 15, which corresponds to the integral 4 interrupt level.

Each interrupt level in the designated group is operated on

according to the function code specified by bits 5 through 7

of the effective address of WD. The defined codes and their

associated functions are as follows:

Code

Functi on

001

Disarm all levels corresponding to a 1 in the ac-

cumulator; no other levels are affected.

Interrupt System Control 11

Code Function

010

Arm and enable all levels corresponding to a 1 in

the accumulator; no other levels are affected.

Arm and disable all levels corresponding to

CI

1 in

the accumulator; no other levels are affected.

Enable all levels corresponding to a 1 in the ac-

cumulator; no other levels are affected.

Disable all levels corresponding to a 1 in the ac-

cumulator; no other levels are affected.

110 Enable all levels corresponding to a 1 in the ac-

cumulator and disable all other levels.

011

100

101

Trigger

011

levels corresponding to a 1 in the ac-

cumulator. All such levels that are currently

armed advance to the waiting state. Those levels

currently disarmed are not altered, and all levels

corresponding to a 0 in the accumulator are not

affected. The interrupt trigger is applied at the

same input point as that used by the device con-

nected to the interrupt level.

The recommended method for produc ing the appropriate con-

figuration of the WRITEDIRECTeffective address is to indi-

rectly address a memory location that contains the appro-

priate bit configuration for the desired effective address.

111

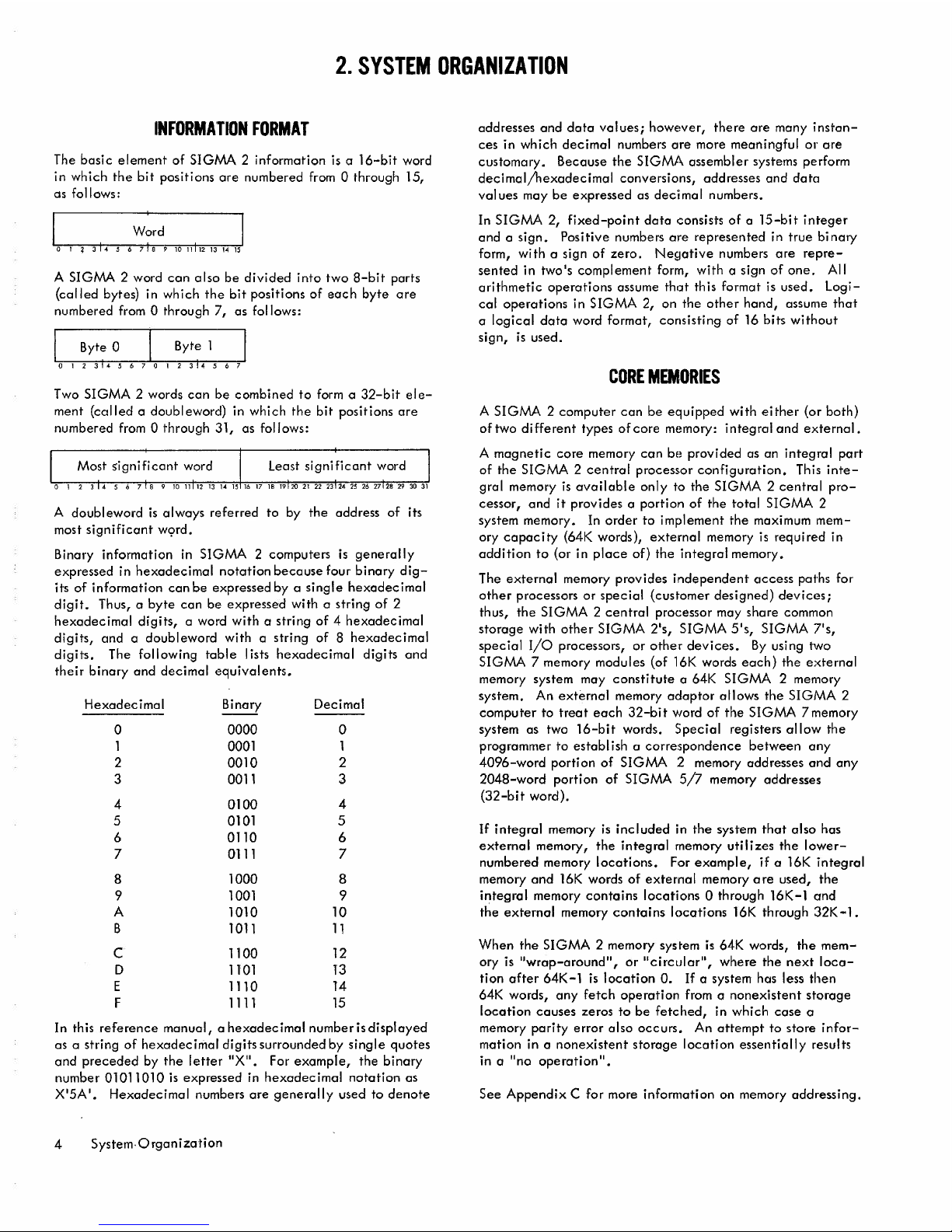

INTERRUPT PRIORITY SEQUENCE

SIGMA 2 interrupts are arranged in groups so that they may

be connected in a predetermined priority arrangement by

groups of levels. The priority of each level within a group

is fixed, with the first level having the highest-priority and

the last level having the lowest-priority. The user has the

option of ordering a machine with a priority chain starting

with the override group and connecting all remaining groups

in any sequence. This a Ilows the user to establ ish external

interrupts above and below the input/output group of inter-

nal interrupts. Figure 4 illustrates this with a configuration

that a user might establ ish, where (after the override and

counter groups) external interrupt group 5 is given second

highest-priority followed by the input/output group and all

succeeding groups of external interrupts.

INTERRUPT ROUTINE ENTRY AND EXIT

When a normal interrupt level becomes active, the computer

automatically saves the program status doubleword (which

contains the protected program indicator, the interrupt in-

hibits, the carry and overflow indicators, and the program

address). The status information is stored in the location

whose address iscontained in the dedicated interrupt location.

The current value in the program address (P)register is stored

in the location following the status information. The sig-

ni ficance of the stored program address depends upon the

particular interrupt level, as follows:

a. For the protection violation, multiply exception,

and divide exception interrupt levels, the stored

program address is the address of the instruction

12 Interrupt System

Override and counter group (1st priority)

Ji

L..------_J

External interrupt group 5 (2nd priority)

Ji

L...------_J

Input/output group (3rd priority)

External interrupt group 6 (4th priority)

Ji

"____--_j

External interrupt group 7 (5th priority)

Figure 4. Interrupt Priority Chain

that was being executed at the time the interrupt con-

dition occurred, or is the address of a nonexistent or

protected location from which an instruction access was

attempted.

b. For all other normal interrupt levels, the stored program

address is the address of the next instruction in sequence

after the instruction whose execution was just completed

at the time the interrupt condition occurred.

After the program address is stored, the next instruction to

be executed is then taken from the location following the

stored program address. The first instruction of the interrupt-

servicing routine is always executed before another inter-

rupt can occur. Thus the interrupt-servicing routine may

inhibit all other normal interrupt levels so that the routine

itself will not be interrupted while in process.

At the end of an interrupt-servicing routine, an exit sequence

restores the program status that existed when the interrupt

level became active. An exit sequence is a WRITEDIRECT

(WD) instruction with an effective address of X'OOD8' fol-

lowed immediately by a LOAD INDEX (LDX) instruction

with an effective address equal to the address value in the

interrupt location for the routine (no interrupt is allowed to

occur between these two instructions). Execution of LDX in

an interrupt routine exit sequence does not affect the con-

tents of index register 1.

COUNTER INTERRUPT PROCESSING

The counter interrupt levels are not associated with interrupt-

servicing routines as such. Instead, an active counter in-

terrupt level is serviced by accessing the contents of the

memory location assigned to the interrupt level, increment-

ing the value in the memory location by I, and restoring the

new value in the same memory location. The processing of

an active counter interrupt level does not affect the over-

flow indicator or the carry indicator. Thus, the on-going

program is not affected by a counter clock pulse (other than

by the time required for processing) unless the result in the

assigned memory location is all O'safter being incremented;

in that case, the corresponding counter-equals-zero inter-

rupt level is triggered.

CPU INTERRUPT RECOGNITION

If all other conditions are met and an interrupt level iswait-

ing and enobled, the CPU will recognize the interrupt fol-

lowing the completion of any instruction except:

1. WD X'OOD8' (precedes LDX for interrupt routine exit)

2. Between the storing of the PSD and the execution of

the next instruction upon entering a normal interrupt

subroutine.

PROTECTION SYSTEM

The primary purpose of the optional protection feature is to

guarantee the integrity of a master or executive-mode (fore-

ground) program whi Ie another (background) program is con-

currently being executed. The SIGMA 2 protection system

provides both operation protection and memory write pro-

tection by means of 16 words of register storage that are in-

stalled as part of the protection option. Each bit in these

16 words is associated with a specific block of core memory.

A block of core memory is a region of 256 consecutive loca-

tions, whose lowest-numbered address issome integer multi-

ple of 256; thus, bit 0 of protection register 0 is associated

with core memory locations 0 through X' FF', bit 1 of pro-

tection register 0 is associated with core memory locations

X'100' through X'1FF', and bit 15 of protection register

X'F' is associated with core memory locations X'FFOO'

through X'FFFF'. A protection bit of 0 designates an

unprotected memory block and a protection bit of 1 desig-

nates a protected block.

The protection registers

.ccn

be individually loaded by exe-

cuting a WRITEDIRECTinstruction with an effective address

of X'8r', where r is a hexadecima I digit that designates

which of the protection registers is to be loaded from the

accumulator (A register). Thus, the protection bits for 16

memory pages (4096 words) can be set up by executing a

single instruction.

Operation of the protection system is under control of the

PROTECTswitch and the key-operated lock on the processor

control panel (see Chapter 5). If the protection system is op-

erative, the following rules apply:

1. The privileged instructions (READ DIRECTand WRITE

DIRECT) can be executed on Iy if they are accessed

from protected memory. If a pri viIeged instruct ion is

accessed from unprotected memory, the instruction is

not executed; instead, the protection violation inter-

rupt level is triggered.

2. An instruction accessed from unprotected memory can be

immediately followed by an instruction accessed from

protected memory only in response to an interrupt con-

dition. If an instruction is accessed from protected

memory and the immediately preceding instruction was

accessed from unprotected memory, the instruction is

not executed (unless it is in response to an interrupt

condition); instead, the protection violation interrupt

level is triggered. This rule applies to branching from

unprotected memory to protected memory as we II as to

executing an instruction in protected memory as the

next instruction in normal sequence after an instruction

in unprotected memory.

3. A STORE ACCUMULATOR (STA) or an INCREMENT

MEMORY (1M)instruction can be used to a Iter protected

memory on Iy if the instruction is accessed from protected

memory. If an attempt is made to alter protected mem-

ory with an instruction accessed from unprotected mem-

ory, the operation is not performed; instead, the

protection violation interrupt level is triggered.

Protection System 13

3.

INSTRUCTION REPERTOIRE

Thissection contains descri ptions of all SIGMA 2 instructions.

With each description is a diagram showing the format of

the instruction and its operation code (as a hexadecimal

digit in the 4 high-order bit positions of the diagram).

Some of the instruction diagrams are divided by a horizon-

rol line, as in the SHIFT instruction on page 15. In these

cases, the upper portion of the diagram represents the in-

struction format, while the lower portion represents the

format of the instruction's effective address. Bit positions

or fields that are shaded represent portions of the instruc-

tion's effective address that are ignored. However, these

areas should always be coded with O's ta preclude conflict

with features that may be implemented in the future.

Above each diagram are the mnemonic code and name of

the instructions, sometimes followed by a parenthetic note

about optional features or privi leged operation. Under

each diagram is a description of the lnstrucrion, followed

by a list of the registers and indicators that can be affected

by the instruction. The minimal execution time of the in-

struction is given in half-cycles (hc).

The following abbreviations are used in the descriptions:

A Accumulator (general register

7)

E Extended accumulator (general register

6)

X1Index1(general register

4)

P Program address register (general register

1)

PP Protected program indicator (PSD bit 8)

II Internal interrupt inhibit (PSD bit 10)

EI External interrupt inhibit (PSD bit 11)

o

Overflow indicator (PSD bit

14)

C Carry indicator (PSD bit 15)

EL Effective location

EW Effective word, or

(EL)

MEMORY REFERENCE INSTRUCTIONS

LDA

LOAD ACCUMULATOR

accumulator (general register 7).

Affected: (A)

Time:5hc

STA

STOREACCUMULATOR

STOREACCUMULATOR stores the contents of the accumu-

lator into the effective location.

Affected: (El)

Time: 5 hc

14 Instruction Repertoire

LDX

LOAD INDEX

Displacement

8 9 10 11 12 13 14 15

LOAD INDEX loads the effective word into index 1 (general

reg ister 4).

Affected: (X

1)

Time:5hc

When LOAD INDEX is executed as the next instruction in

sequence after a WRITEDIRECT(WD) instruction with an

effective address of X'OOD8', index register1is not af-

fected; instead, LOAD INDEX performs the following op-

erations in order to restore the program environment thot

existed before the computer acknowledged an interrupt

condition:

1.

sets the protected program indicator equal to bit8of

the effective doubleword

2. sets the internal interrupt inhibit equal to bit 10 of the

effective doubleword

3. sets the external interrupt inhibit equal to bit 11 of the

effective doubleword

4. sets the overflow indicator equal to bit 14 of the effec-

tive doubleword

5.

sets the carry indicator equal to bit 15 of the effective

doubleword

6. loads bits 16 through 31 of the effective doubleword

into the program address register (general register

1)

7.

clears the highest-priority active interrupt level and re-

turns the interrupt level to the armed state

8. resets the exit condition that was set by the precedi ng

WD instruction (that caused LDXto perform the above

operations)

Bits 0 through 7, 12, and 13 of the effective doubleword are

ignored.

Affected: PP, II, EI,0,C, (P), highest-

priority active interrupt level

Time:6hc

ADD

ADD

AIRII

!xisI

Displacement I

o

I 2 3 " 5 6 7a9 10

11112

13 14 15

ADD adds the effective word to the contents of the accumu-

lator and then loads the result into the accumulator. If the

signs of the two operands are equal but the sign of the re-

sult is different, overflow has occurred, in which case the

overflow indicator is set to1.If overflow does not occur,

the overflow indicator is reset to O. The carry indicator is

settol ifacarryoccurs from the sign bit position oftheadder;

if such a carry does not occur, the carry indicator is reset

to O.

Affected: (A), 0, C

Time: 5 hc

SUB

SUBTRACT

SUBTRACTformsthe two's compl ement ofthe effective word,

adds this value to the contents of the accumulator, and then

loads the result into the accumulator. If the sign of thetesult

in the accumulator is equal to the sign ofthe effective word but

the sign of the origi nal operand in the accumul ator was different,

overflow has occurred, in which case the overflow indicator is

set to 1. If overflow does not occur, the overflow indicator is

reset to O. The carry indicator is set to 1if a carry occurs from

the sign bit position ofthe adder; if no carry occurs, the carry

indicator is reset toO. (A carry occurs if the 16-bit magni-

tude in the effective location is equal to or less than the

16-bit magnitude in A.)

Affected: (A),0,C

Time: 5 hc

MUL

MULTIPLY(optional)

Displacement

8 9 10 11 12 13 14 15

MULTIPLYmultiplies the effective word by the contents of

the accumulator, loads the 16 high-order bits of the double-

word product into the extended accumulator (general register

6), and loads the 16 low-order bits of the doubleword prod-

uct into the accumulator. Neither overflow nor carry can

occur; however, the carry indicator is set equal to the sign

of the doubl eword product.

If the multiply/divide option is not implemented and an at-

tempt is made to execute the instruction, the multiply ex-

ception interrupt level is triggered instead. The program

address stored in memory as a result of the interrupt level

becoming active is the address of the MULTIPLYinstruction.

Affected: (E, A), C

Time: 23 hc

DIY

DIVIDE (opti ona

I)

Displacement

8 9 10 11 12 13

14 15

DIVIDE divides the contents of the extended occumvl otor

and the accumulator by the effective word.

If the absolute value of the quotient is equal to or greater

than 32,768 (215), the overflow indicator is set to 1 and the

instruction is terminated with the contents of the extended

accumu lator and the accumu lator unchanged from their pre-

vious values, and the carry indicator set equal to the sign

of the dividend.

If the absolute value of the quotient is less than 215, the

overflow indicator is reset to 0, the integer quotient is

loaded into the accumulator, the integer remainder is load-

ed into the extended accumulator, and the carry indicator

is set equal to the sign of the remainder. (The sign of the

remainder is the same as the sign of the dlvidend.}

If the multiply/divide option is not implemented and an at-

tempt is made to execute the DIVIDE instruction, the divide

exception interrupt l<evelis triggered instead. The program