Page 1

Xerox

Data

Systems

Reference

Manual

Page 2

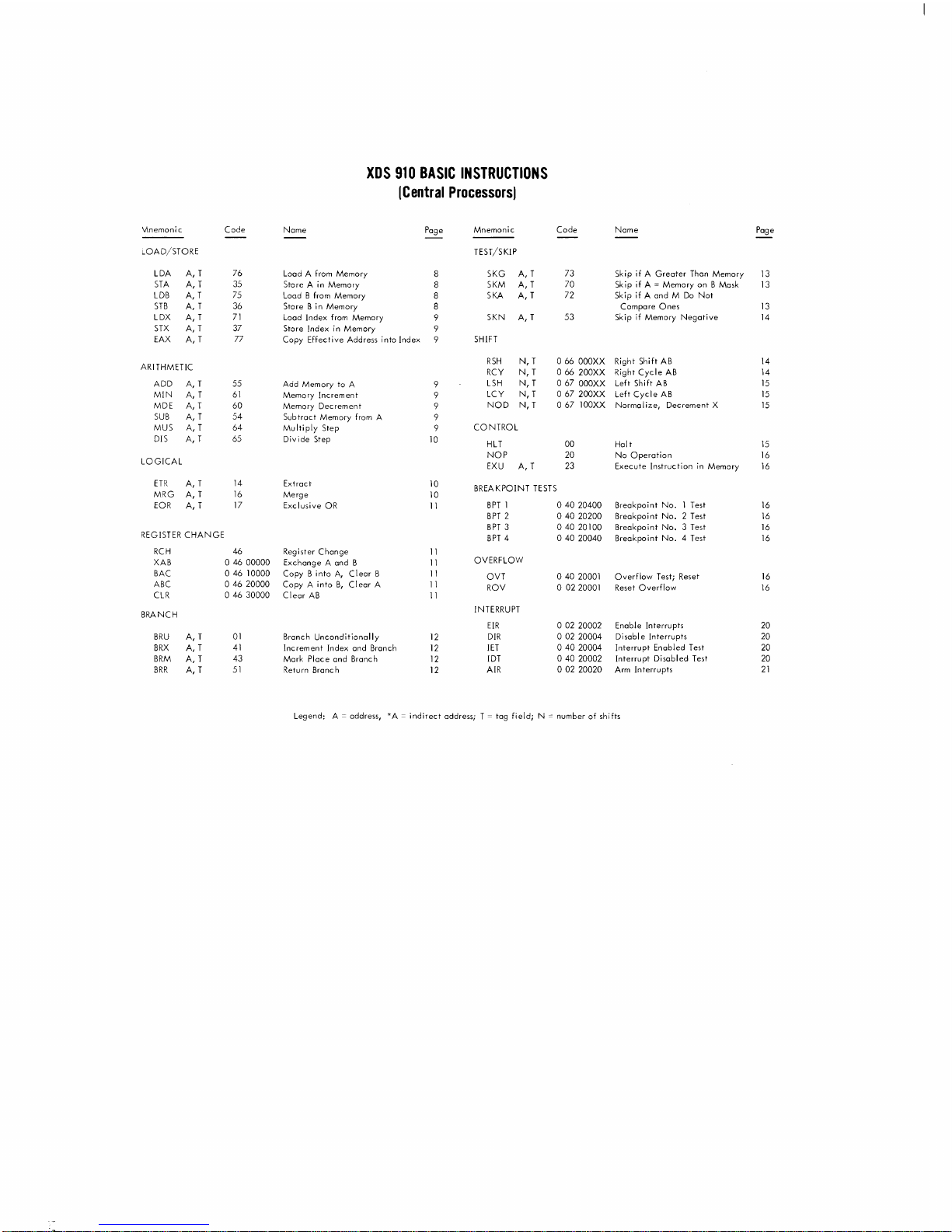

XDS

910

BASIC

INSTRUCTIONS

ICentral

Processorsj

Vlnemonic Code

Name

Page

Mnemonic Code Name

Page

LOAD/STORE

TEST/SKIP

LDA

A,

T

76

Load A

from

Memory

SKG

A,

T

73 Skip if A

Greater

Than Memory

13

STA

A,

T

35

Store A

in

Memory

SKM

A, T

70

Skip if A = Memory on B Mask

13

LDB

A,

T

75

Load B

from

Memory

SKA

A, T

72 Skip if A and M

Do

Not

STB

A,

T

36 Store B in Memory Compare

Ones

13

LDX

A, T

71

Load Index

from

Memory

SKN

A,

T

53 Skip if Memory

Negative

14

STX

A,

T 37

Store Index

in

Memory

EAX

A, T

77

Copy Effective Address into Index

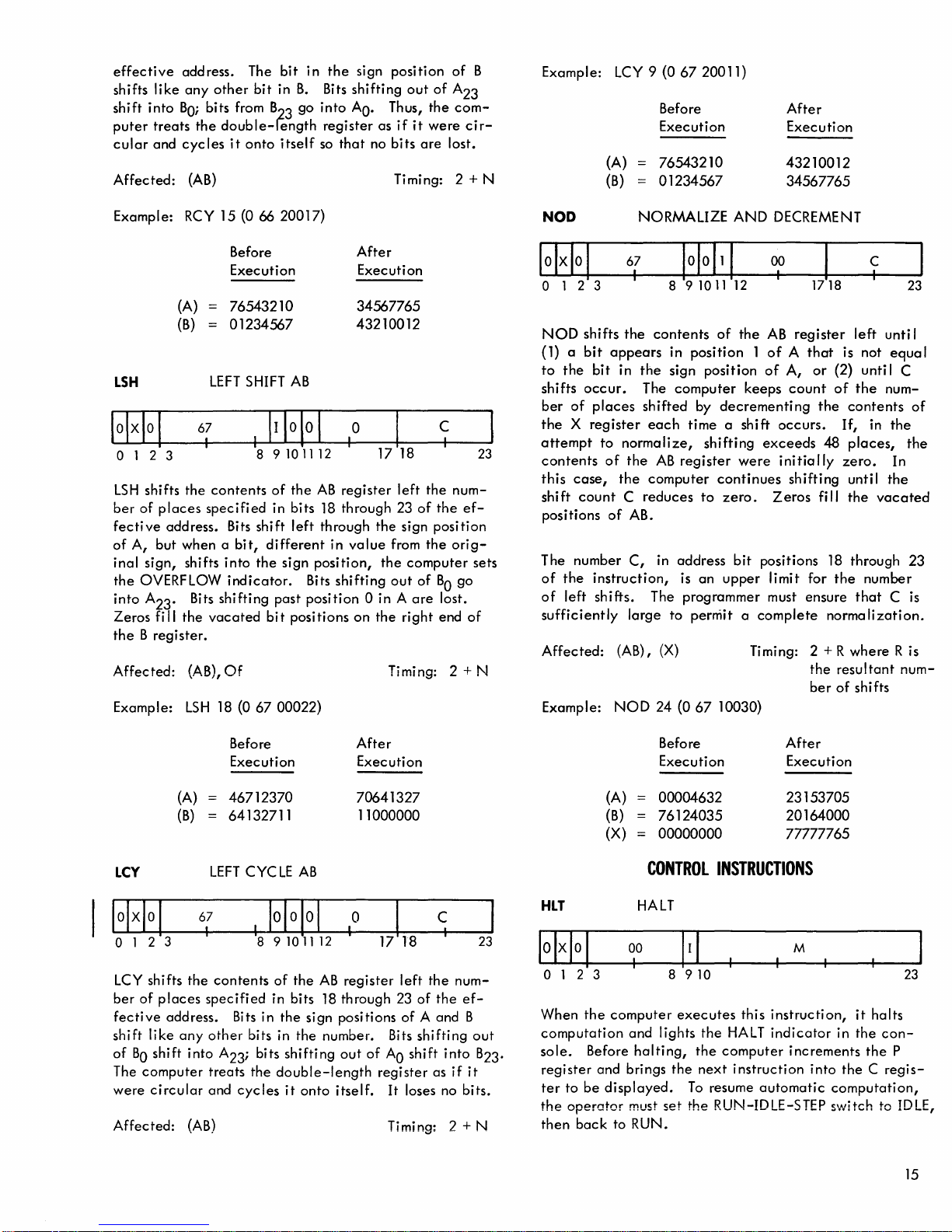

SHIFT

ARITHMETIC

RSH

N, T

066

OOOXX

Right Shift

AB

14

RCY

N, T

066

200XX

Right

Cycle

AB

14

ADD

A,

T 55

Add

Memory to A

LSH

N, T

067

OOOXX

Left Shift

AB

15

MIN

A,

T

61

Memory Increment

LCY

N, T

067200XX

Left

Cycle

AB

15

MDE

A,

T 60

Memory Decrement

NOD

N, T

067

100XX Normalize, Decrement X

15

SUB

A,

T

54

Subtract Memory

from

A

MUS

A,

T 64

Multiply Step

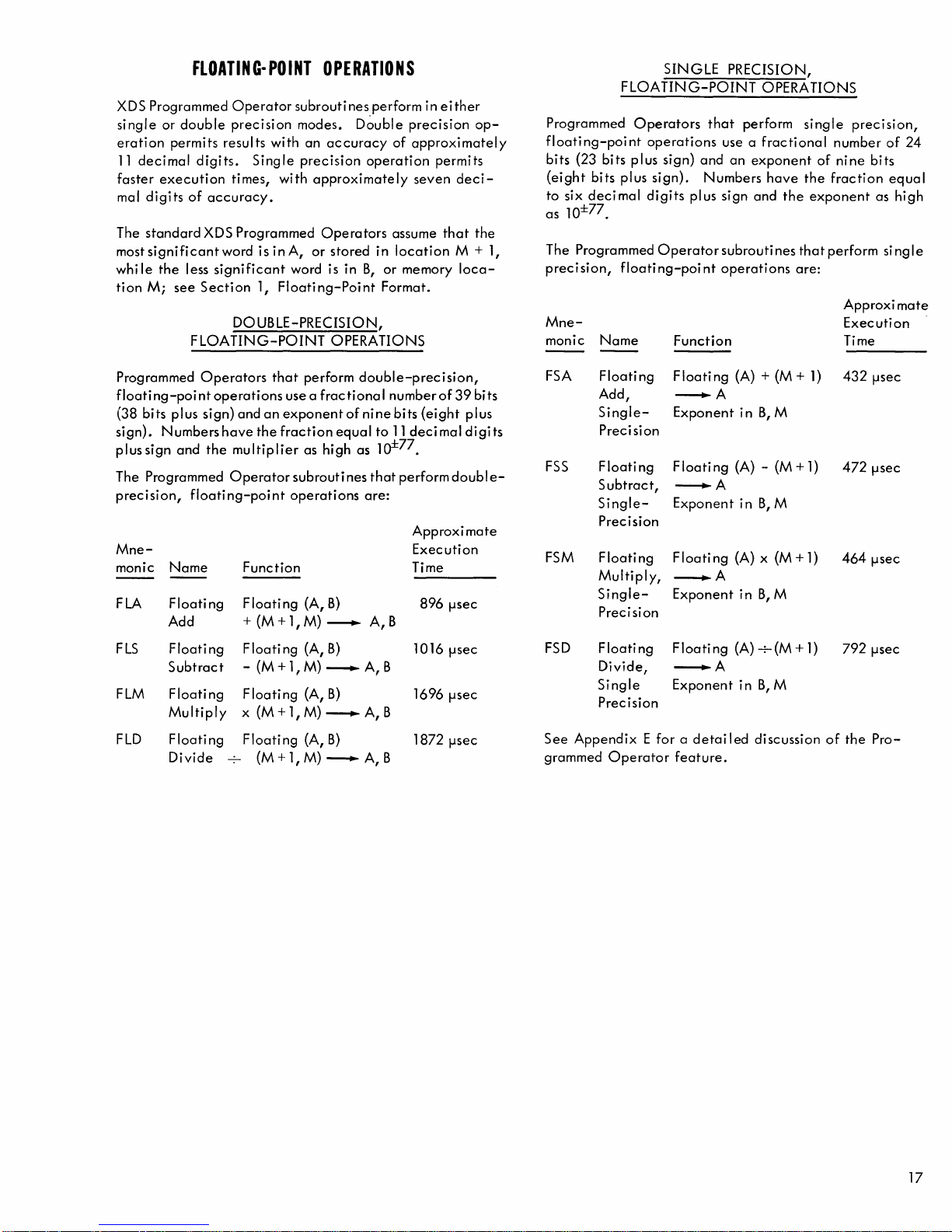

CONTROL

DIS

A,

T 65 Divide Step

10

HLT

00 Halt

15

NOP

20 No

Operation

16

LOGICAL

EXU

A, T 23 Execute Instruction

in

Memory

16

ETR

A,

T

14

Extract

10

BREA

KPOINT

TESTS

MRG A, T

16

Merge

10

EOR

A,

T

17

Exclusive

OR

11

BPT

1

04020400

Breakpoint No. 1 Test

16

BPT

2

04020200

Breakpoint

No.2

Test

16

BPT

3

04020100

Breakpoint

No.3

Test

16

REGISTER

CHANGE

BPT

4

04020040

Breakpoint

No.4

Test

16

RCH

46

Register

Change

11

XAB

04600000

Exchange A and B

11

OVERFLOW

BAC

046

10000 Copy B into

A,

Clear

B

11

OVT

o 40 20001 Overflow Test; Reset

16

ABC

046

20000

Copy A into

B,

Clear

A

11

ROV

o 0220001 Reset Overflow

16

CLR

046

30000

Clear

AB

11

BRANCH

INTERRUPT

EIR

002

20002 Enable Interrupts 20

BRU

A,

T

01

Branch Unconditionally

12

DIR

00220004

Di

sabl e Interrupts 20

BRX

A,

T

41

Increment Index and Branch

12

lET

04020004

Interrupt Enabled Test

20

BRM

A, T 43 Mark Place and Branch

12

!DT

040

20002

Interrupt Disabled Test

20

BRR

A,

T

51

Retu

rn

Bronc

h

12

AIR

002

20020

Arm

Interrupts

21

Legend: A = address,

*A = indirect

address; T = tag field; N = number

of

shifts

Page 3

Price: $3.25

XOS

910

COMPUTER

REFERENCE

90

00

080

February 1970

MANUAL

Xerox

:91963-1970,

Data

Systems/70i

Xerox

Data

Systems,

Inc

South

Aviation Bouievard/Ei Segundo, Caiifornia 90245

Printed

in

U.S.A

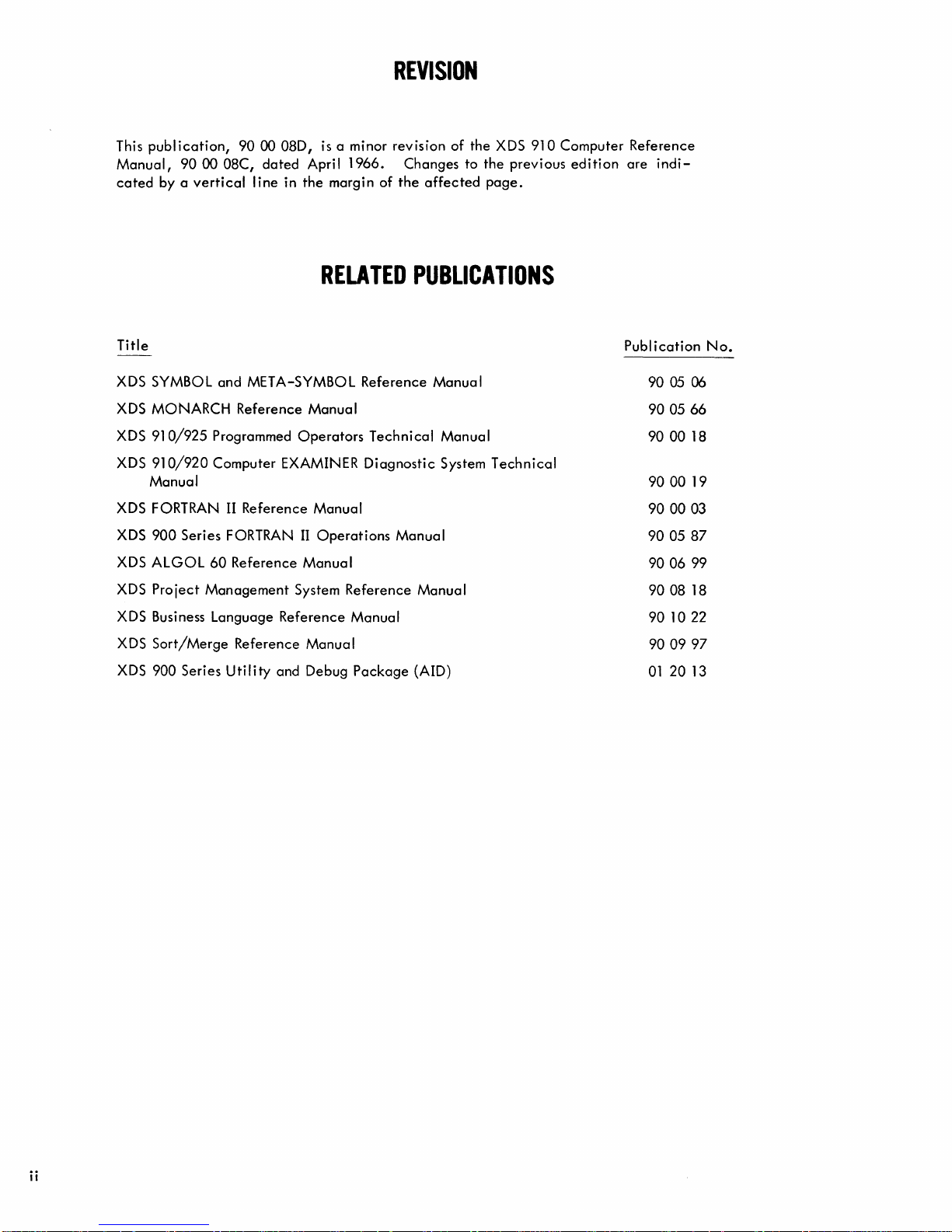

Page 4

This

publication,

Manual,

cated

by a vertical

90

00

90

08C,

00

dated

line

08D,

in

the

is a minor

April

1966.

margin

REVISION

revision

Changes

of

the

of

to

affected

the XDS

the

page.

910

previous

Computer

edition

Reference

are

indi-

Title

XDS SYMBOL

XDS MONARCH Reference

XDS

910/925

XDS

910/920

Manual

XDS FORTRAN II Reference

XDS

900

XDS

ALGOL

XDS

Project

XDS Business Language

XDS

Sort/Merge

XDS

900 Series

and

META-SYMBOL

Programmed

Computer EXAMINER

Series

FORTRAN II

60

Reference

Management

Reference

Reference Manual

Utility

and Debug

Operators

System

RELATED

Reference

Manual

Technical

Diagnostic

Manual

Operations

Manual

Reference

Manual

Package

PUBLICATIONS

Manual

Manual

System

Manual

Manual

(AID)

Technical

Publication

90

05 06

900566

90 00 18

90

00 19

90

00 03

9005

87

90 06 99

90

08 18

90

1022

9009

01

20

No.

97

13

ii

Page 5

CONTENTS

GENERAL DESCRIPTION

1.

Introduction

XDS910

XDS910

Instruction

Specia I Characteristics

Programmed

MACHINE INSTRUCTIONS

2.

Introduction

Load/Store

Arithmetic

Logical

Regi

Branch

Test

Shift

Contro I Instructions

Breakpoint

Overflow

Floating-Point

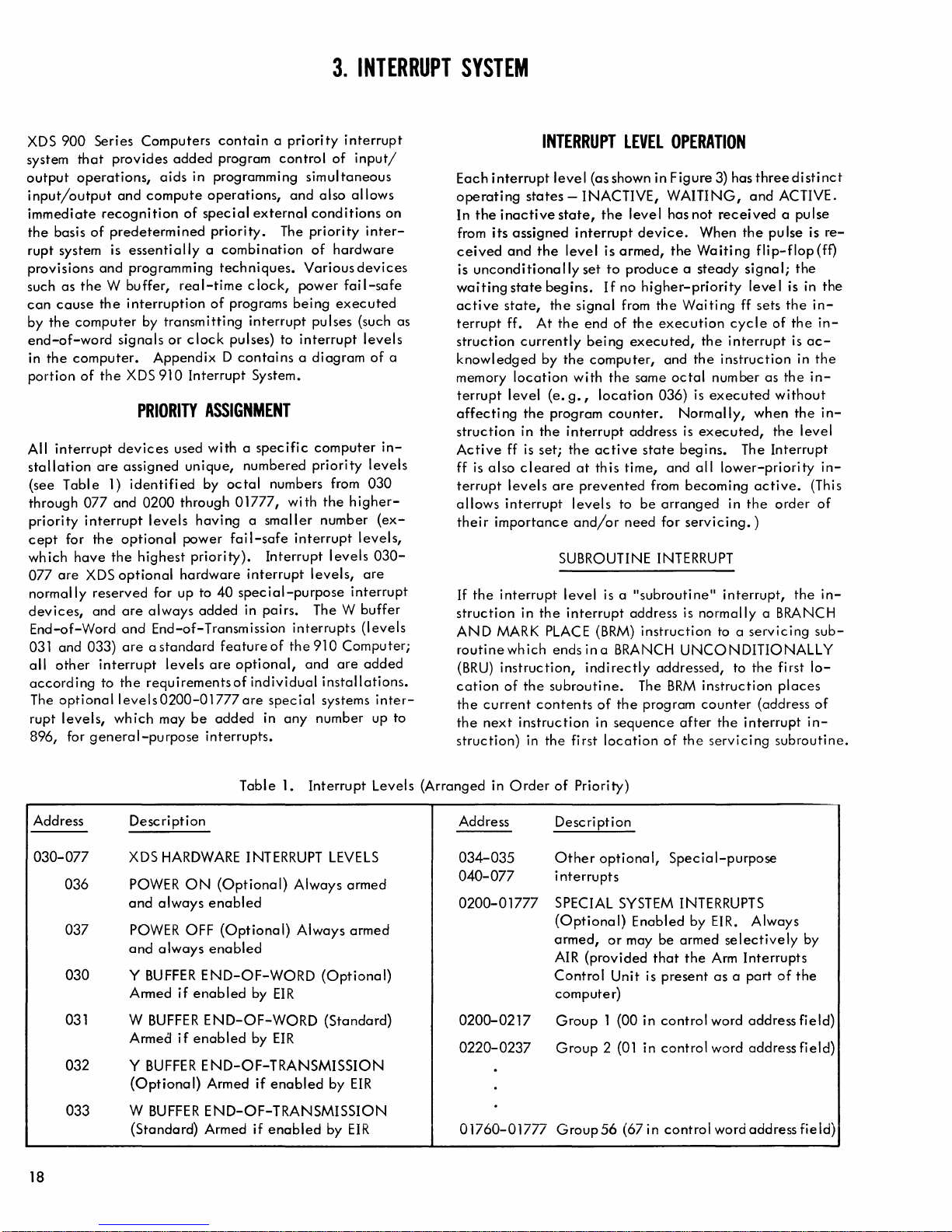

INTERRUPT SYSTEM

3.

Priority

Interrupt

Interrupt

Interrupt

and

Special

Registers

Memory

Word Format

Instructions

Instructions

Instructions

ster

Change

Instructions

and

Skip

Instructions

Tests 16

Instructions

Assignment 18

Level

Arm/Enable

Enable/Disable

Tests

Systems

Operators

Instructions

Instructions

Operations

Operations

Interrupts

Response

Instructions

10

11

12

13

14

15

16

17

18

19

20

21

APPENDIXES

1

2

3

4

5

6

8

8

9

A.

CONVERSION

XDS

Table

Octal-Decimal

Octal-Decimal

B.

TWO'S

COMPUTER

C.

D.

DETAILED MACHINE

PROGRAMMED OPERATORS

E.

INSTRUCTION

F.

INDEX

COMPLEMENT ARITHMETIC

Instruction

Typical

Buffered

Functional

Numerical

Alphabetical

TABLES

Character

of

Powers

OPERATING

Execution

Interrupt

Input/Output

LISTS

Categories

Order

Codes

of

Two

IntegerConversion

Fraction

Order.

Conversion

PROCEDURES_

FUNCTIONS

Cycle

Table_

Table

Index-1

A-1

A-2

A-3

A-7

A-10

A-11

A-13

A-15

A-17

A-19

A-21

A-26

A-29

ILLUSTRATIONS

4.

INPUT/OUTPUT

Introduction.

Primary

Buffer

Standard

Standard

Single-Word

Interlaced

Direct

Single-Bit

CONTROL

5.

Controls

Displays

6.

PERIPHERAL

Input/Output

Paper

Card

li

Moanetic

Input/Output

Control

Parallel

CONSOLE

EQUIPMENT

Tape

Input/Output

ne Pri

nter

v

SYSTEM

Instructions

EOM

Buffer

EOM

Instructions

Buffer SKS

Transmission

Block Transmission

Input/Output

Input/Output

Tone T

• - 1- . -

Instructions

Input/Output

Typewriter

nnut/Outnut

'.---,

- - - 1- - -

___

23

25

26

28

29

30

32

34

35

36

37

38

38

43

48

52

XDS910

XDS

l.

Basic Register Flow Diagram 3

2.

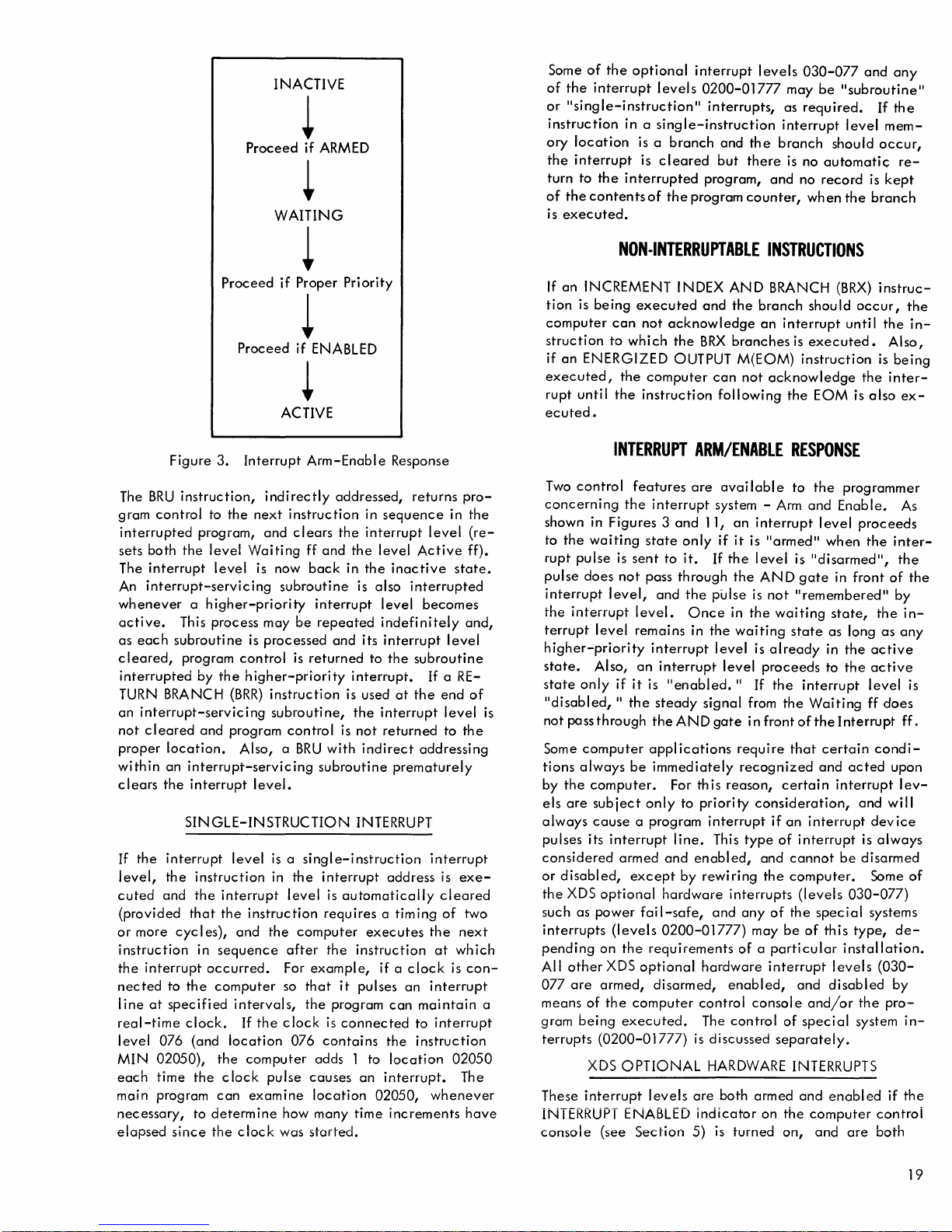

Interrupt

3.

XDS

4.

Interlace

5.

6.

XDS910Controi

Card

7.

8.

Printer

Switches

9.

Instruction

10.

Priority

Buffer

1l.

Transmission

12.

Buffer

Transmission

Computer

910

Computer

Arm-Enable

910

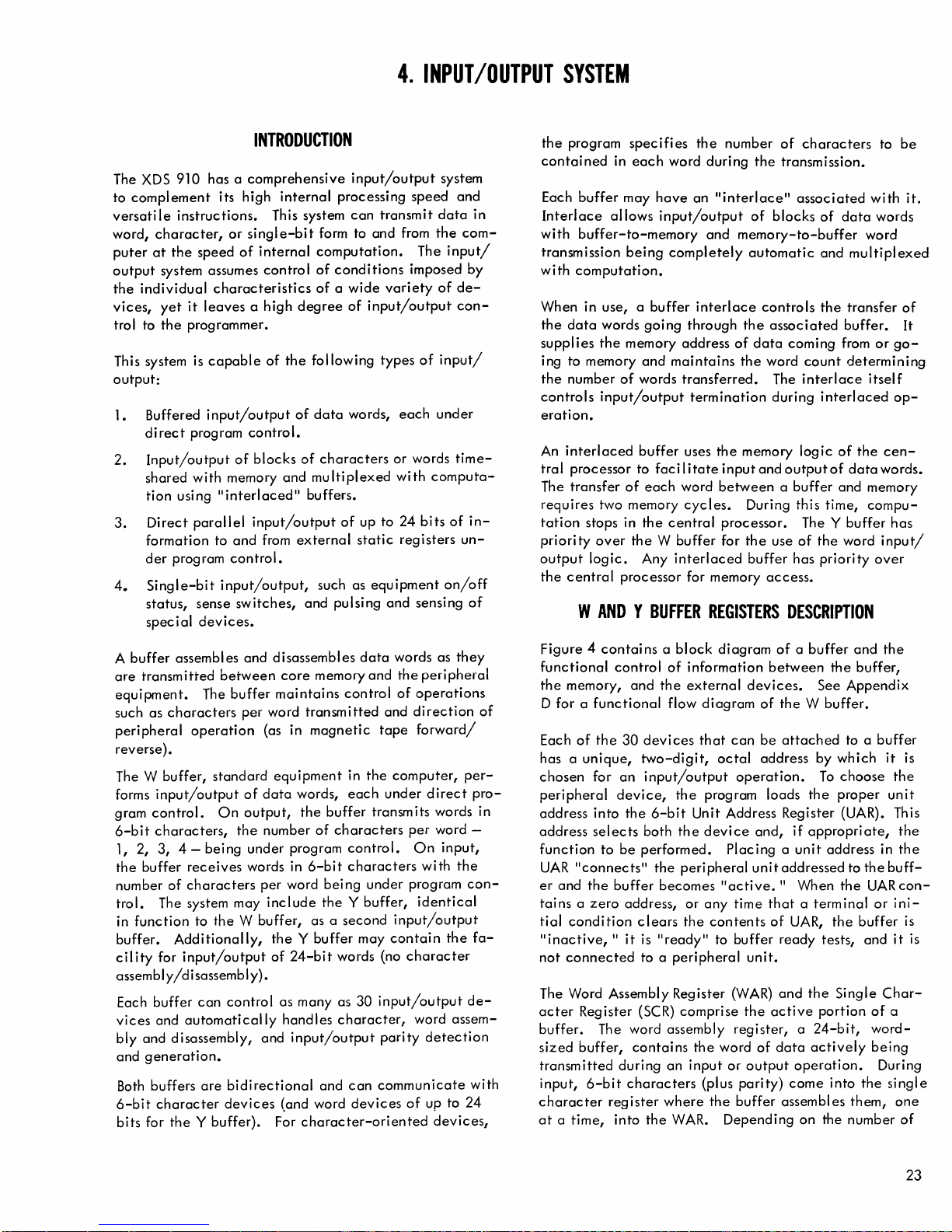

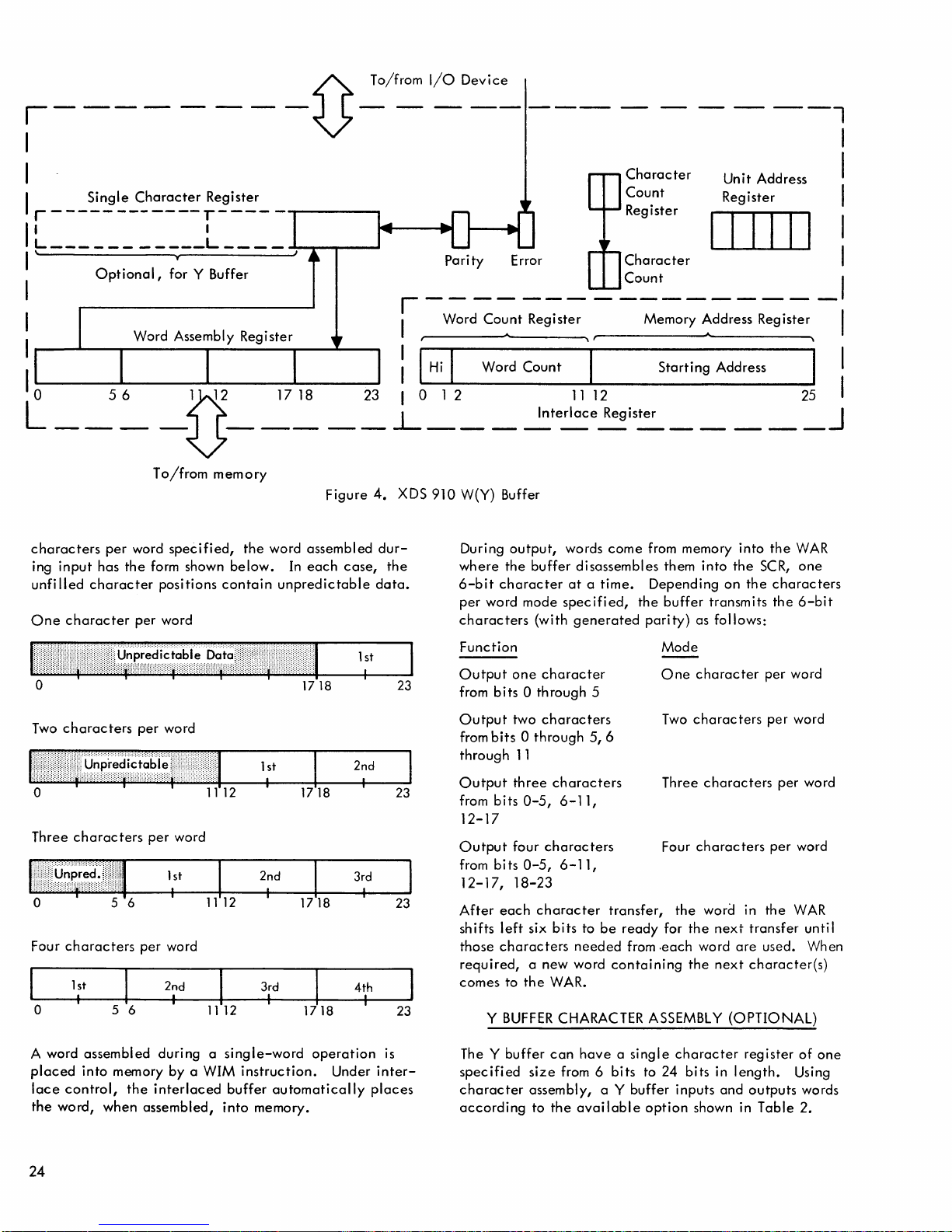

W (Y) Buffer.

Input/Output

Read

into

Control

Interrupt

Operation,

Operation,

(Frontispiece)

Configuration

Panel

Memory in

Indicator

Execution

System Diagram

Single-Word

Interlaced

Response

Hollerith

lights

Diagram

and

TABLES

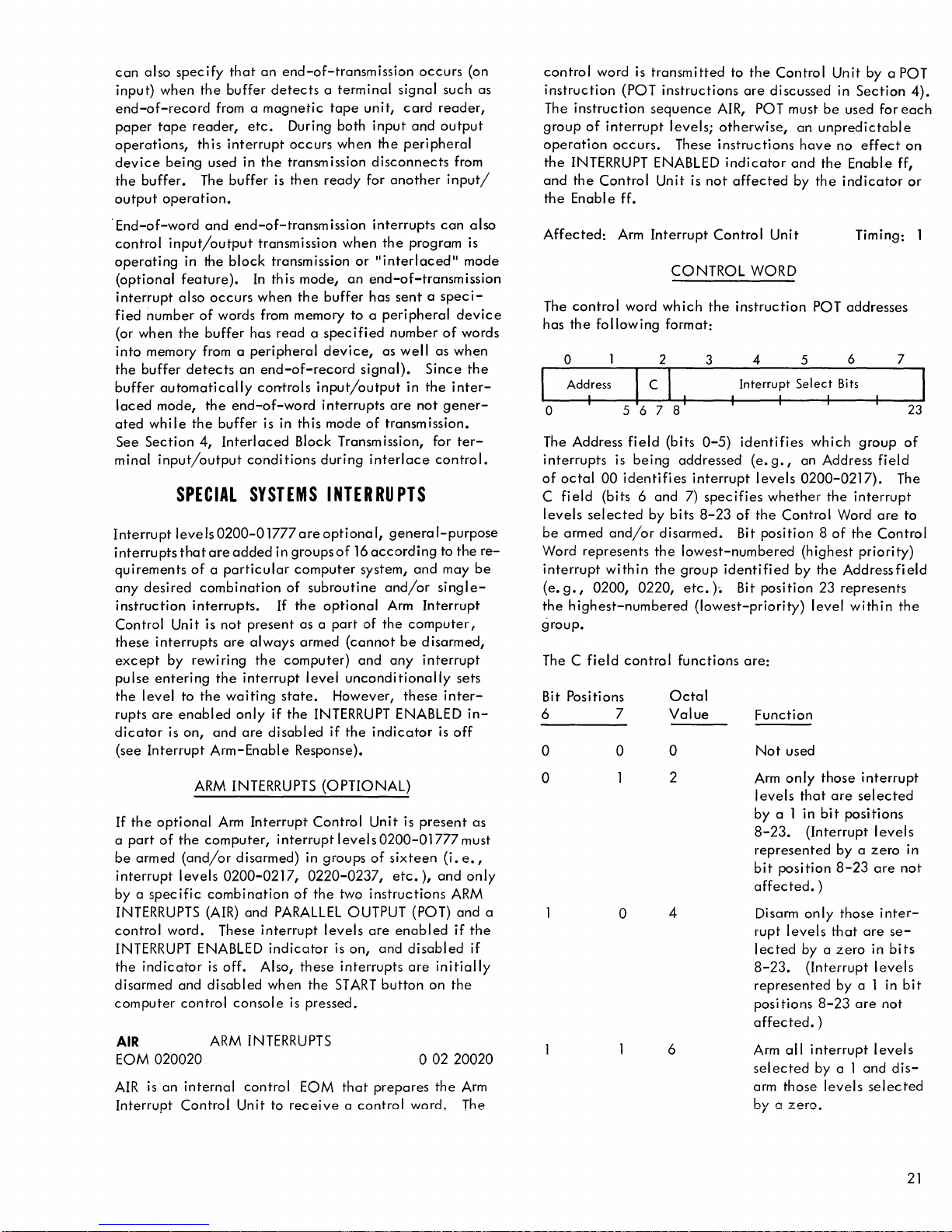

I

nte

l.

2.

3.

4=

rru pt Leve I s

Y Buffer

Unit

Address

Format

Character

Codes

Control

Assembly

Characters

Options

iv

2

19

24

32

36

43

48

A-12

A-14

A-16

A-18

18

25

27

51

iii

Page 6

XDS

910

Computer

iv

Page 7

1.

GENERAL

DESCRIPTION

INTRODUCTION

The XDS 910, Figure 1,

general-purpose,

characteristi

24-bit

•

Bi

•

nary

Single-address

•

Index Register

Indirect

Programmed

• Basic

•

• Typical

core

able

to

dressable

2048-

and

indexing)

Fixed-Point

Add

Multiply

digital

cs:

word, plus

arithmetic

instructions

Addressing

memory

16,384

and

execution

words. All words

with

8-microsecond

4096-word

in microseconds:

Operations

16

248

Operators

is a high-speed,

computer

parity

bit

with

of

2048

or

4096

cycle

memory modules

times

(including

with

are

low-cost,

the

following

words,

di

rectly

time

available

memory

expand-

ad-

access

Buffered

•

characters/second

Standard

•

Display

Full-word

The minimum

photoelectric

board

punch.

Optional

•

Input/output

Keyboard pri

punch

300-character/second

character/second

tape

MAGPAK

Magnetic

and

Card

reader/punch,

input/output

simultaneous

input/output

and

manual

input/output

910

printer

input/output

spoo I ers

BC

readers,

with

typewriters

nter

Magnetic

tape

D), disc

card

at

rates

control

buffer

system

paper

units

line

tape

paper

devices

with

paper

paper

paper

tape

Tape Systems

(IBM-compatible;

fi

les

punches,

printers

in

excess

with

of

internal

includes

reader

tape

reader

tape

tape

punches,

combination

of

60,000

computation

registers

either

reader

readers,

a

or a key-

and

and

paper

binary

card

60-

Floating-Point

Add

Multiply

Add 896

Multiply

Program

•

Series Computers

Parity

•

Priority

•

Two

38

Up

Memory

•

tional

tents

of programmable registers

Operations

24-bit

432

464

39-bit

1696

interchangeability

checking

Interrupt

standard

more,

to 896

nonvolatile

power

Fraction

Fraction

of

memory

System

XDS

optional

optional

fail-safe

hardware

special

in

event

feature

(plus

(plus

with

and

of

9-bit

9-bit

other

I/O

operations

interrupts;

system

power

permits

exponent)

exponent)

XDS 900

up to

interrupts

failure;

saving

con-

op-

Off-line

punched

Communications

display

A to D

ment,

MONARCH

•

pi I

er,

and

complete

All

•

•

•

•

silicon

O

Dimensions (inches):

Power:

. t 100 to

peratmg

Doubl e

mounting:

Single

mounting:

110v,

facility

cards

osci 1I0scopes,

converters,

and

other

Monitor

META-SYMBOL Assembl

software

semiconductors

emperature

rack

rack

60

for

printing

or

magnetic

equi

pment, tel

graph

digital

special

Routine, FORTRAN

package

65-1/2 x 48-1/4 x 25-1/2

75-3/4 x 25-1/4 x 25-1/4

cps,

range:

17

amp

system

directly

tape

etype

plotters

multiplexer

equipment

er,

as

0

55

from

consol es,

equip-

II

Com-

part

of

C

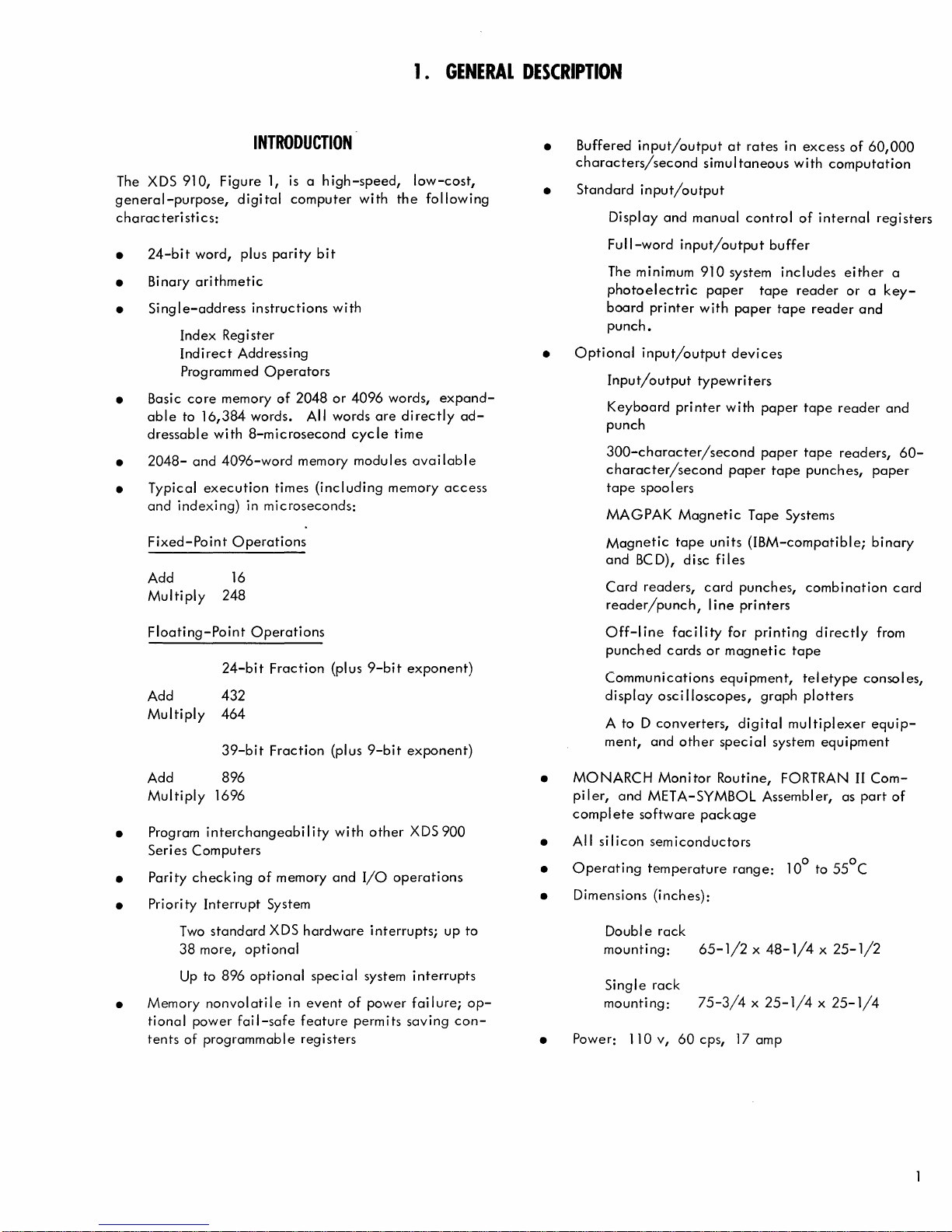

Page 8

Up

to

896

special

I I I I

I I I I I I , , I I I

I I I I I I I I I : I

system

interrupts

Items with

dotted

lines

are

optional.

Single-Bit

and

Sense

Word

Parallel

(24 lines) .....

Buffer

Interrupt

Character

(6

bits,

plus

Buffer

parity)

XDS

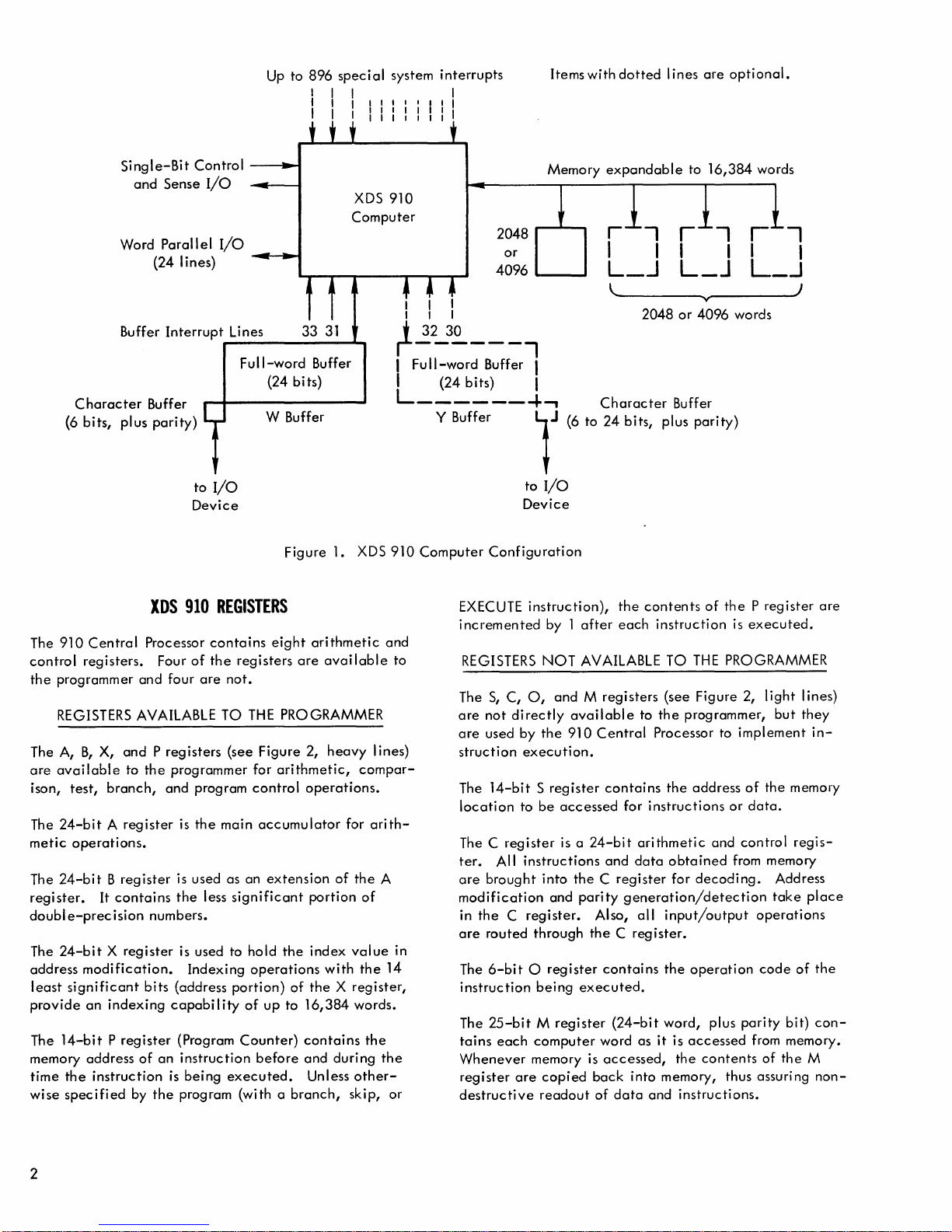

The

910

Central

control

the

The A,

are

ison,

The

metic

The

register.

doubl

The

address

least

provide

The

memory address

time

wise

registers.

programmer

REGISTERS AVAILABLE TO

B,

available

test,

24-bit A register

operations.

24-bit B register

e-prec

24-bit X register

modification.

significant

an

14-bit P register

the

instruction

specified

Processor

Four

and

four

X,

and P registers

to

the

branch,

It

contains

i sion numbers.

indexing

by

bits

of

and

an

is

the

programmer for

(address

capability

Control

to

Device

910

of

are

program

is

the

is used as an

the

is used to

Indexing

(Program

instruction

being

program (with a

---l

.....

I/O

I/O

---

...

~~~,-----~~--~

Lines

----------------~

Full-word

I/O

33

(24 bits)

W Buffer

Figure 1.

XDS

Computer

31

Buffer

XDS

REGISTERS

contains

the

main

less

eight

registers

not.

THE

(see Figure 2,

significant

hold

operations

portion)

of

Counter)

executed.

are

PROGRAMMER

arithmetic,

control

accumulator

before

operations.

extension

the

of

up

to

16,384

contains

and

Unless

branch,

arithmetic

available

heavy

lines)

compar-

for

arith-

of

the

portion

index

the X register,

with

during

skip, or

of

value

the

words.

the

other-

910

2048

4096

I I

I I I

~2~~

I

Full-word

___

Buffer I

I (24 bits) I

L------4-,

Y Buffer

910

Computer

and

to

A

in

14

the

Configuration

EXECUTE

incremented

REGISTERS

The

S,

are

not

are

used by

struction

The

14-bit S register

location

The C

ter.

All

are

brought

modification

in

the C register.

are

routed

The

6-bit 0 register

instruction

The

25-bit M register

tains

each

Whenever

register

destructive

Memory

or

__

..,

lJ

to

I/O

Device

instruction),

by 1

NOT

C,

0,

directly

the

execution.

to

be

register

instructions

into

and

through

being

computer

memory is

are

copied

readout

expandable

_

l~--------_v~--------~)

2048

Character

(6 to

24

bits,

the

contents

after

each

AVAILABLE TO

and M registers

available

910

accessed

is a 24-bit

the C register

parity

the C register.

executed.

back

to

Central

contains

for

instructions

arithmetic

and

data

generation/detection

Also,

all

contains

(24-bit

word as

accessed,

into memory, thus assuring

of

data

and

to

16,384

or

4096

Buffer

plus

parity)

of

the P register

instruction

THE

PROGRAMMER

(see Figure 2,

the

programmer,

Processor to

the

address

and

obtained

for

decoding.

input/output

the

operation

word, plus

it

is

accessed

the

contents

instructions.

words

r

-,

I I

L_..J

words

is

executed.

light

but

implement

of

the

memory

or

data.

control

from memory

parity

regis-

Address

take

operations

code

of

bit)

from memory.

of

the

are

lines)

they

in-

place

the

con-

M

non-

2

Page 9

A

(Main

Accumulator)

(Ins

P

(Program

S

Register

(Memory

Register

0

Reg.

true

tion)

Register

Counter)

Address)

B

Register

(Extended

1

.

C

Register

(Arithmetic

-----------------~

Accumulator)

II

and

Control)

X

Register

(Index)

•

,

M

~

Register

(Memory

Memory

Access)

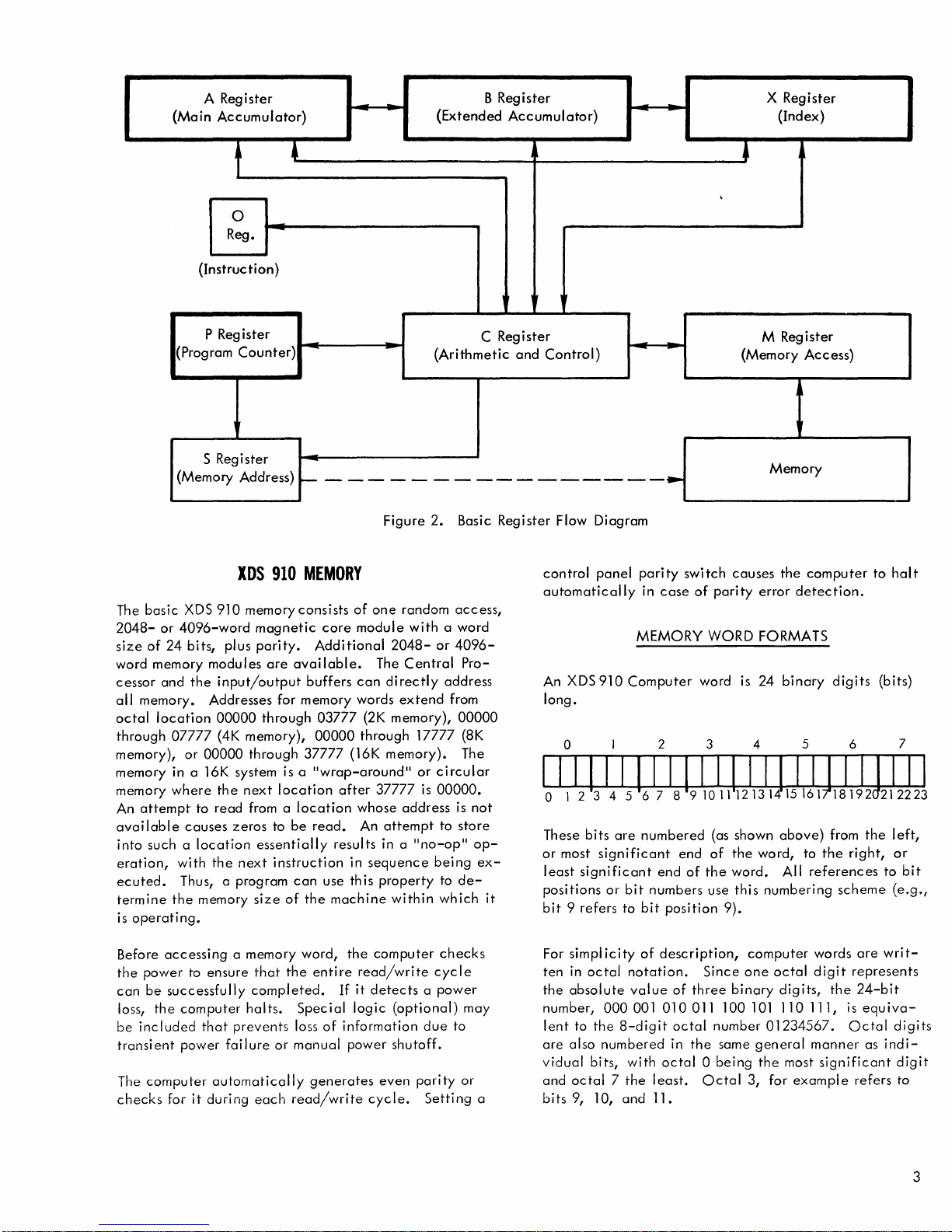

The

basic

2048-

or

size

of

24

word

memory

cessor

and

all

memory.

octal

location

through

memory),

memory

memory

An

available

into

eration,

ecuted.

termine

is

Before

the

can

loss,

be

transient

The

checks

07777

in a 16K

where

attempt

such a location

the

operating.

accessing a memory

power

be

successfu

the

inc I uded

computer

for

XDS

910

4096-word

bits,

plus

modules

the

input/output

Addresses

00000

(4K

or

00000

the

to

read

causes

with

the

Thus, a

memory

to

ensure

Ily

computer

that

power

failure

automatically

it

during

XDS

910

memory

magnetic

parity.

are

through

memory),

through

system

next

from a

zeros

to

essentially

next

instruction

program

size

that

compl

halts.

prevents

or

each

MEMORY

consists

core

Additional

available.

buffers

for

memory

03777

00000

37777

is a

IIwrap-aroundli

location

location

be

read.

can

use

of

the

word,

the

entire

eted.

Special

loss

of

manual

generates

read/write

Figure

of

one

module

The

can

directly

words

(2K

through

(16K

memory).

after

37777

whose

An

attempt

results

machine

in a IIno-opli

in

sequence

this

property

the

computer

read/write

If

it

detects a power

logic

information

power

even

cycle.

2.

random

with a word

2048-

or

Central

extend

memory),

17777

or

circular

is

00000.

address

to

being

to

within

shutoff.

which

checks

cycle

(optional)

due

pari

ty

Setting

Basic

access,

4096-

Pro-

address

from

00000

(8K

The

is

not

store

op-

ex-

de-

may

to

or

a

Register

it

Flow

Diagram

control

automatically

An XDS

long.

panel

910

pari

ty

in

case

MEMORY

Computer

swi

of

tch

parity

WORD

word

causes

error

FORMATS

is

24

the

computer

detection.

binary

digits

o I 2 3 4 5 6 7

IIIIIIIIIIIIIIIIIIJ

o

123

4 5

67 8 9101112131415161

These

bits

are

or

most

significant

least

significant

positions

bit 9 refers

For

ten

the

number,

lent

are

vidual

and

bits

or

simplicity

in

octal

absolute

000001010011100101110111,

to

the

also

numbered

bits,

octal 7 the

9,

10,

numbered

bit

numbers

to

bit

of

notation.

value

8-digit

with

least.

and

11.

end

description,

octal 0 being

end

of

the

position

Since

of

three

octal

in

the

Octal

(as

shown

of

the

word.

use

this

9).

binary

number

same

above)

word,

All

numbering

computer

one

octal

digits,

01234567.

general

the

most

3,

for

example

II

18192

from

to

the

references

scheme

words

digit

the

is

Octal

manner

significant

to

hal

(bits)

Jill

212223

the

left,

right,

or

to

(e.g.,

are

writ-

represents

24-bit

equiva-

digits

as

indi-

digit

refers

to

t

bit

3

Page 10

The

computer

012

Bit

position

coding

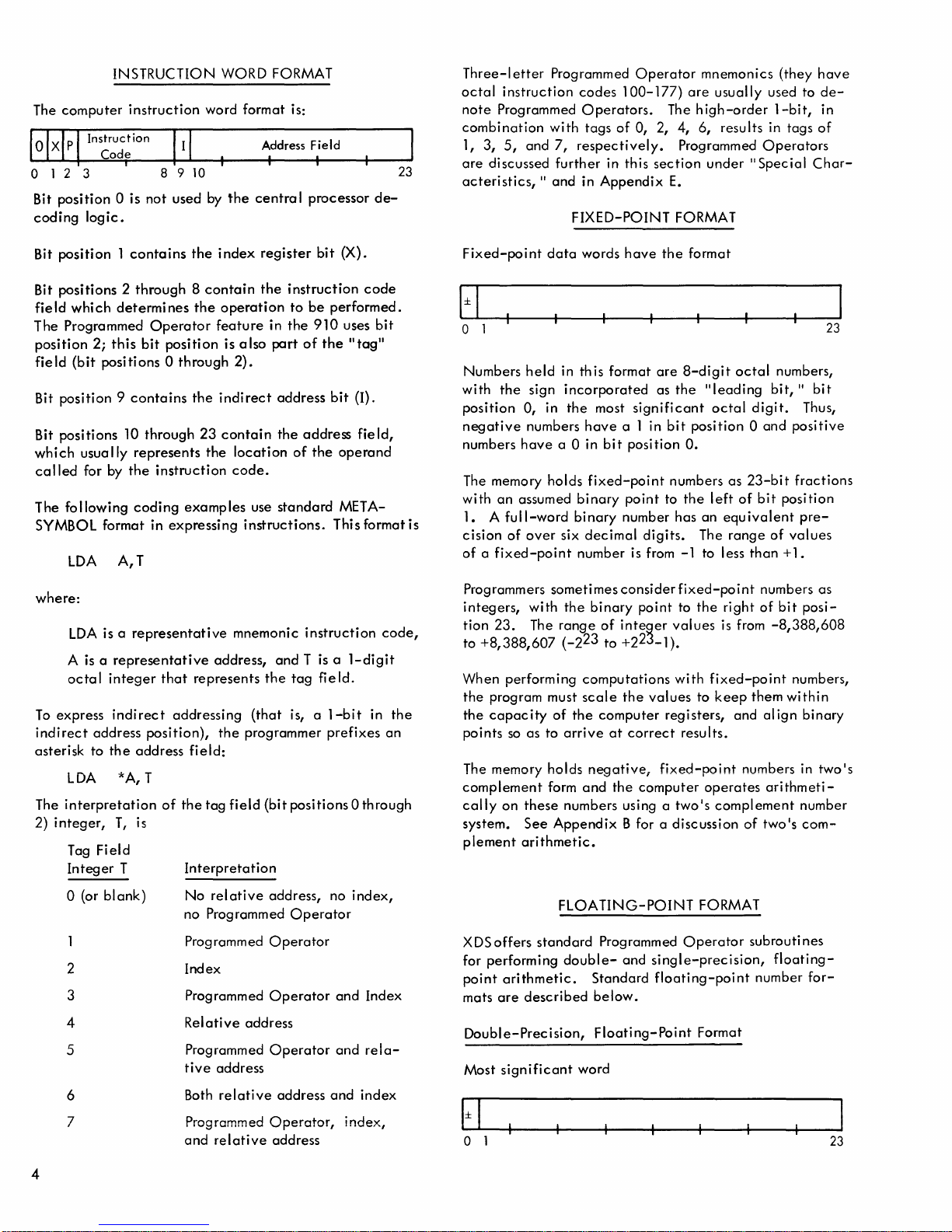

INSTRUCTION WORD FORMAT

3

instruction

0 is

not

word format is:

8910

used

by

the

Address

centra

logic.

I I

I processor

Field

de-

23

Three-I

octal

note

etter

instruction

Programmed

combination

1,

3,

5,

and

are

discussed

acteristics,

Programmed

codes

Operators.

with tags

7,

respectively.

further

II

and in

FIXED-POINT

Operator

100-177)

of

0, 2, 4, 6, results in tags

mnemonics (they

are

usually used to

The

high-order

Programmed

in this

Appendix

section

E.

under

FORMAT

1-bit,

Operators

"Special

have

dein

of

Char-

Bit

position 1 contains

Bit positions 2 through 8

field

which

determines

The Programmed

position

field

Bit position 9

2;

this

bit

(bit

positions 0 through

contains

Bit positions 10 through

which

usually

called

for by

The following

represents

the

coding

the

contain

the

Operator

position

the

23

the

instruction

examples

index

operation

feature

is a

indirect

contain

SYMBOL format in expressing

LDA

A,

T

where:

LDA

is a

representative

A is a

octal

To

express

indirect

address

asterisk to

LDA

interpretation

The

2)

integer,

representative

integer

that

indirect

position),

the

address

*A, T

of

T,

is

address,

represents

addressing

the

field:

the

tag

Tag Field

Integer

T

Interpretation

register

the

in

Iso

bit

instruction

to

be

the

910

part

of

performed.

the

2).

address

the

location

address

of

the

bit

code.

use

standard

instructions.

mnemonic

This format is

instruction

and T is a 1-digit

the

tag

field.

(that

is, a

1-bit

programmer

field

(bit positions 0 through

prefixes

(X).

code

uses

bit

II

tag"

(I).

fie Id,

operand

META-

in

code,

the

an

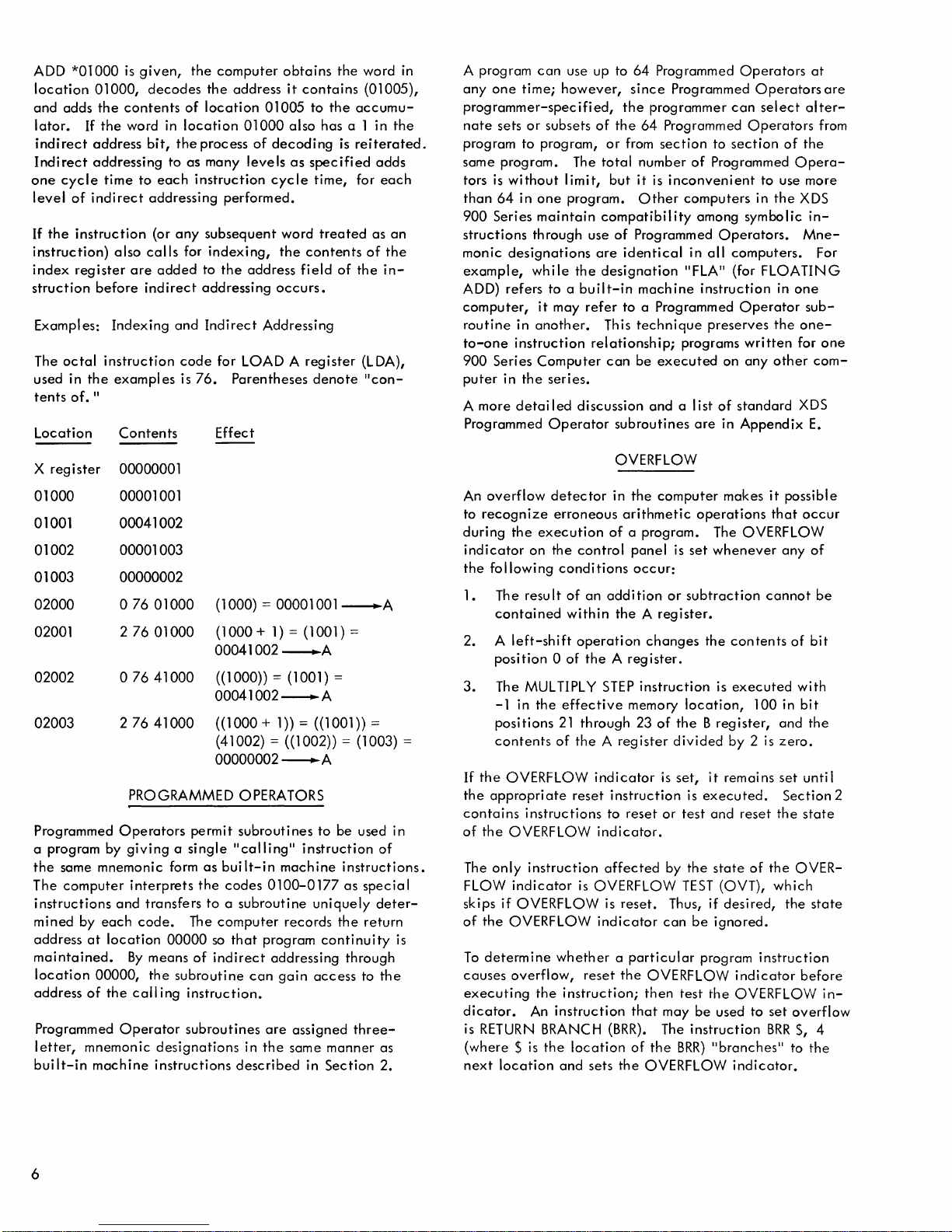

Fixed-point

data

o 1

Numbers

with

position

negative

numbers

The memory holds

with

1. A

cision

of a fixed-point

Programmers

integers,

tion

to

When performing

the

the

points

The memory holds

complement

cally

system.

plement

held

the

sign

0, in

numbers

have

an

assumed

full-word

of

over

sometimesconsiderfixed-point

with

23.

The

+8,388,607

program must

capacity

so

as to

form

on

these

See

arithmetic.

in this format

incorporated

the

a 0 in

six

the

range

(-2

of

arrive

numbers using a

Appendix

words

have

the

format

are

8-digit

as

the

"Ieading

most

have

a 1 in

bit

fixed-point

binary

binary

point

number has

decimal

significant

position

digits.

octal

bit

position 0 and

O.

numbers as

to

the

left

an

equivalent

The

number is from -1 to less

binary

23

computations

scale

the

negative;

and

point

of

integer

to +223_1).

the

values

computer

at

correct

fixed-point

the

computer

to

the

right

values

with

is

fixed-point

to

keep

registers, and

results.

operates

two's

complement

B for a discussion

octal

bit,

digit.

23-bit

of

bit

range

of

than

numbers as

of

from

-8,388,608

them

align

numbers in

arithmeti-

of

two's

numbers,

II

bit

Thus,

positive

fractions

position

pre-

values

+ 1.

bit

posi-

numbers,

within

binary

two's

number

com-

23

o (or

blank)

2

3

4

5

6

7

No

relative

address, no

no Programmed

Programmed

Operator

Index

Programmed

Relative

Programmed

tive

address

Both

relative

Programmed

and

relative

Operator

address

Operator

Operator,

address

Operator

address

4

index,

and Index

and

rela-

and

index

index,

FLOA

XDS

offers

standard

for performing

point

arithmetic.

mats

are

double-

described

Double-Precision,

Most

significant

o 1

lING-POINT

Programmed

and

Standard

below.

Floating-Point

word

FORMAT

Operator

subrouti nes

single-precision,

floating-point

Format

floating-

number

for-

23

Page 11

Least

significant

word

SPECIAL

CHARACTERISTICS

o

The

fractional

point

number

ing

bit

being

just

bit

(bit 1 of

nent

is a

sign.

Standard

exponent

contents

tents

of

x 2±E.

F

Double-precision,

decimal

exponent

Standard

significant

location

the B register,

Single-Precision,

Fractional

is a 39-bit

being

the

to

the

the

9-bit

in

two's

of

the

the

exponent

digits

of

range

Programmed

word

M+

1,

word

portion

sign

left

of

upper

integer,

routines

complement

fractional

field,

floating-point

precision

of

10-

Operators

is

in

the A register,

and

that

or

stored

Floating-Poi

141516

of a double-precision,

proper

bit

and

the

the

most

word).

with

77

The

the

operate

form.

fi

eld

and E represents

the

and a decimally

to

10+77•

the

less

in memory

nt

fraction,

assumed

significant

leading

on

number

numbers

assume

significant

Format

with

floating-point

bit

both

fraction

If

F

has

that

or

stored

location

floating-

the

binary

represents

have

point

magnitude

expo-

being

and

the

the

form

over

equivalent

the

more

in memory

word

M.

lead-

the

the

con-

is in

23

11

Certain

vide

program

Address

and

In

performs

tion

tion

of

of

Indexing

The

modification.

address

execution

If

computer

X

instruction

retain

address

computer

significant

running

modification

indirect

both

indexing

address

from

remains

the

address

the

instruction

computer

in

bit

position 1 of

register

any

bi

memory

an

time.

adds

t.

economi

time.

ADDRESS

addressing,

and

modification

in

memory

modification

contains

The

instruction

the

to

the

prior

to

overflow

features

es

MODIFICATION

is

accomplished

used

indirect

but

before

in

operand.

an

use

of

does

an

instruction

contents

contents

execution.

or

carry

simplify

in

memory

singly

addressing,

after

executing

its

original

forms

index

this

register

not

of

bits

of

the

This

beyond

programming

uti I ization

through

or

in

bringing

it.

form. The

the

"effective

(X)

register

increase

contains

10

through

address

addition

the

and

indexing

combination.

the

computer

the

instruc-

The

instruc-

address"

for

address

to

modify

instruction

a 1,

23

of

field

of

does

most

significant

pro-

and

result

the

the

the

the

not

" 1

v I

Exponent

word

o

The

fractional

point

number

ing

bit

ing just

The

floating-point

leading

fraction

Single-precision,

decimal

exponent

Standard

tional

word

and

that

location

Operator

ignored.

is a 24-bit

being

the

to

the

sign

bit.

and

exponent

digits

range

Programmed

is

the

exponent

M. When

routine,

portion

sign

left

of

the

exponent

Standard

floating-point

of

precision

of

10-

Operators

in A,

or

enterina

bits

141516

of a single-precision,

proper

and

in

77

stored

word is in

0-14""

fraction,

the

assumed

most

significant

is a

9-bit

routines

two's

and a decimally

to 10+77•

of

operate

complement

numbers

assume

in memory

B,

or

a stcmcJrm1

the

ex~onen;:~;d··;r-e

.

binary

integer

that

stored

floating-

with

the

point

magnitude

with

on

both

form.

have

over

equivalent

the

frac-

location

in memory

Prnnrnmmpej

lead-

be-

a

M+

23

23

bit.

six

1,

The

computer's

modifying

information

Indirect

The

struction.

the

tion

A 0 in

puter

tions

requested

posi

X

A 1 in

puter

as

an

reinitiates

by

For

puter

contains

accumulator

Addressing

indirect

computer

being

bit

to

use

10-23

tion

causes

register

bit

to

decode

described

instruction

the

instruction.

example,

to

obtain

00001005)

instruction

and

testing

between

address

This

uses

executed.

position 9 of

the

of

by

the

to

this

position 9 of

above,

code;

address

the

(A

the X register

bit

bit

position

indirect

contents

the

instruction)

instruction.

the

computer

address

the

contents

as

that

decoding,

instruction

a

\AlOrd

and add

register).

set

provides

the X register

is in

bit

position 9 of

determines

addressing

an

instruction

of

the

address

as

A 1 in

to

add

to form

an

if

is,

from

it

the

instruction

of

the

were

an

the

computer's

using

ADD

location

it

to

However,

instructions

and

and

memory.

whether

with

causes

field

the

14-bit

the

the

contents

effective

causes

location,

instruction

the

word

01000

01000

the

contents

if

the

for

transfering

the

the

instruc-

the

(bit

index

address.

the

accessed

address

specified

causes

(assume

instruction

for

in-

or

not

com-

posi-

address

bit

of

the

com-

without

logic

the

com-

it

of

the

5

Page 12

ADD

*01000

location

and

lator.

indirect

Indirect

one

level

If

the

01000,

adds

If

address

addressing

cycle

of

indirect

instruction

instruction)

index

register

struction

Exampl es:

The

octal

used in

tents

of.

the

"

Location

is

given,

decodes

the

contents

the

word in

bit,

time

to

addressing

also

calls

are

before

indirect

Indexing

instruction

examples

Contents

to

each

(or

any

added

and

the

computer

the

of

location

location

the

process

as

many

instruction

subsequent

for

indexing,

to

addressing

Indirect

code

for LOAD A

is

76.

Effect

address

01005

01000

of

decoding

levels

cycle

performed.

word

the

the

address

occurs.

Addressing

Parentheses

obtains

it

contains

to

also

has

as

specified

time,

treated

contents

field

register

denote

the

the

accumu-

a 1 in

is

reiterated.

for

of

the

word

in

(01005),

the

adds

each

as

an

of

the

in-

(L

DA),

"con-

A program

anyone

can

time;

use up to

however,

programmer-specified,

nate

sets

or

subsets

of

program to program,

same program. The

tors

is

without

than

64

900

Series

structions

monic

designations

example,

ADD) refers to a

computer,

routine

to-one

900

puter

A more

in

instruction

Series

in

detailed

Programmed

limit,

in

one

program.

maintain

through use

whi Ie

it

may

another.

Computer

the

series.

Operator

are

the

built-in

refer

relationship;

discussion

64

Programmed

since

Programmed

the

programmer

the

64

Programmed

or

from

section

total

number

but

it is

inconvenient

Other

compatibil

of

ity

Programmed

identical

designation

machine

to a Programmed

This

technique

can

be

executed

and

a list

subroutines

Operators

Operators

can

select

Operators

to

section

of

Programmed

to use more

computers

in

among symbolic

Operators.

in

all

computers.

"FLA"

(for FLOA TIN G

instruction

Operator

preserves

programs

are

written

on

any

of

standard

in

Appendix

of

Opera-

the

in

one

the

other

at

alter-

the

XDS

in-

Mne-

sub-

one-

for

com-

XDS

E.

are

from

For

one

X

register

01000

01001

01002

01003

02000

02001

02002

02003

00000001

00001001

00041002

00001003

00000002

076

276

07641000

27641000

PROGRAMMED OPERATORS

Programmed

a program by

the

some mnemonic form

The

computer

instructions

mined by

address

maintained.

location

address

Programmed

letter,

built-in

Operators

giving a single

interprets

and

each

at

location

By

00000,

of

the

Operator

mnemonic

machine

01000

01000

transfers

code.

00000

means

the

subroutine

call

ing

designations

instructions

(1000) = 00001001

( 1

000 + 1) = (1

00041002

( ( 1 000)) =

00041002~A

( ( 1

000

----.A

(1

+ 1)) =

001) =

001) =

((1

001 )) =

~A

(41002) = ((1002)) = (1003) =

00000002~A

permit

as

the

to a

The

of

so

indirect

subroutines

"calling"

built-in

codes

0100-0177

subroutine

computer

that

program

can

to be used in

instruction

machine

instructions.

as

uniquely

records

the

continuity

addressing through

gain

access

instruction.

subroutines

are

in

the

same

described

assigned

manner

in

Section

of

special

deter-

return

to

the

three-

as

2.

OVERFLOW

An

overflow

to

recognize

during

indicator

the

following

1. The

contained

2. A

position 0 of

3.

The MULTIPLY

-1 in

positions

contents

If

the

the

appropriate

contains

of

the

The

only

FLOW

skips

if

of

the

detector

erroneous

the

execution

on

the

control

conditions

result

of

within

left-shift

the

of

operation

effective

21

through 23

the

OVERFLOW

reset

instructions

OVERFLOW

instruction

indicator

is

OVERFLOW is

OVERFLOW

in

the

computer

arithmetic

of

a program. The OVERFLOW

panel

is

makes

operations

set

whenever

occur:

an

addition

or

subtraction

the A register.

changes

the

the A register.

STEP

instruction

memory

A reg

ister

indicator

instruction

to

reset

of

is

or

is

location,

the B register,

divided

set,

it

remains

is

executed.

test

and

indicator.

affected

OVERFLOW

indicator

reset.

by

the

TEST

Thus, if

can

be

state

(OVT),

desired,

ignored.

it

that

cannot

contents

executed

100 in

by 2 is

reset

of

the

which

possible

occur

any

of

of

bit

with

bit

and

the

zero.

set

untii

Section

the

state

OVER-

the

state

be

2

is

To

determine

causes

executing

dicator.

is

RETURN

(where $ is

next

location

whether a particular

overflow,

the

An

reset

instruction;

instruction

BRANCH

the

location

and

sets

the

then

that

(BRR).

of

the

OVERFLOW

program

OVERFLOW

test

the

may

be

used to

The

instruction

the

BRR)

"branches" to

instruction

indicator

before

OVERFLOW i

set

overflow

BRR

$, 4

the

indicator.

n-

6

Page 13

The

execution

interrupt

of

med

places

position a of

indicator.

(BRM)

bit

not

The

merges

the

location

cator.

instructions.

The XDS

three

1.

2.

3.

A program

MARK

automatically

subroutines

the

OVERFLOW

Operator

the

places

position a of

disturb

instruction

the

contents

and

Section 2 contains a description

910

kinds

Normal

eters

are

the A register

Interrupt

an

interrupt

Programmed

enters

PLACE

of

Programmed

automatically

indicator.

instruction,

status

of

the

location

The

the

the

OVERFLOW

contents

of

places

SUBROUTI·NE EXECUTION

Computer

of

subroutines:

closed

specified

subroutine

AND

stores

00000

instruction

status

the

effective

RETURN

of

bit

position a of

the

subroutine

Operator

a normal

BRANCH

the

Operator,

In

the

computer

OVERFLOW

and

MARK

of

the

OVERFLOW

memory

indicator.

BRANCH

the

OVERFLOW

the

result

in

makes

it

possible

where

in

appropriate

that

is

entered

subroutine

closed

(BRM)

contents

executing a Program-

resets

the

subroutine

of

closed,

preserves

automatically

indicator

the

PLACE

(BRR)

AND

location

automatically

indicator

effective

OVERFLOW

of

to

the

input

registers

as

instruction;

the

program

and

the

status

in

bit

OVERFLOW

BRANCH

indicator

memory

the

execute

the

via

and

with

indi-

branch

param-

such

result

a

BRM

counter

in

does

as

of

(P

register)

in

the

branch-to

mally

the

location

BRANCH

the

ister

Section

i

nstruc

Interrupt

by

automatically

to

be

ecution

a

fixed

location

address

BRM

tents

the

to

the

the

ferred

value

struction

the

BRANCH

indirect

the

the

clears

this

uses

(BRR)

main

program;

value

2, Branch

ti

ons.

subroutines

the

detection

entered.

to

be

location

normally

of

the

is

executed,

of

the P register

branch-to

branch-to

instruction

to

the

stored

to

interrupt

UNCONDITIONALLY

addressing

subroutine)

completion

the

interrupt

differs

the

BRR

and

the

status

location.

of

the

instruction

the

BRR

and

transfers

Group,

are

of

program-controlling

cause

the

An

interrupt

suspended

corresponding

contains a BRM

interrupt

it

automatically

and

location.

location

process

appropriate

from

P,

therefore,

which

program

is

serviced

(through

returns

of

the

subroutine.

from

from

the

norma I

(stored P value

of

the

The P

BRM

accompl

adds

control

for a

closed

appropriate

causes

and

control

servicing

the

OVERFLOW

The

BRM

+ 1. (When

is

completed,

BRM

without

control

by

the

the

control

the

to

active

closed

+ 1

OVERFLOW

register

instruction. A RETURN

ishes

one

to

to

that

description

subroutines,

interrupt

normal program

to

to

that

interrupt.

instruction

subroutine.

stores

then

an

and

disturbing

is

the

address

should

interrupt

(BRU)

branch-to

the

main

BRU

state.

subroutine

---..

P).

indicator

value

the

return

the

stored P reg-

location.

of

the

initiated

interrupts,

subroutine

be

transferred

with

When

the

current

indicator,

transfers

interrupt

control

of

return

subroutine).

instruction

location

program

indirect

Note

return

is

nor-

to

See

branch

that

ex-

The

the

the

con-

control

occurs,

is

trans-

P.

The

the

in-

after

with

of

at

also

that

that

to

in

A

7

Page 14

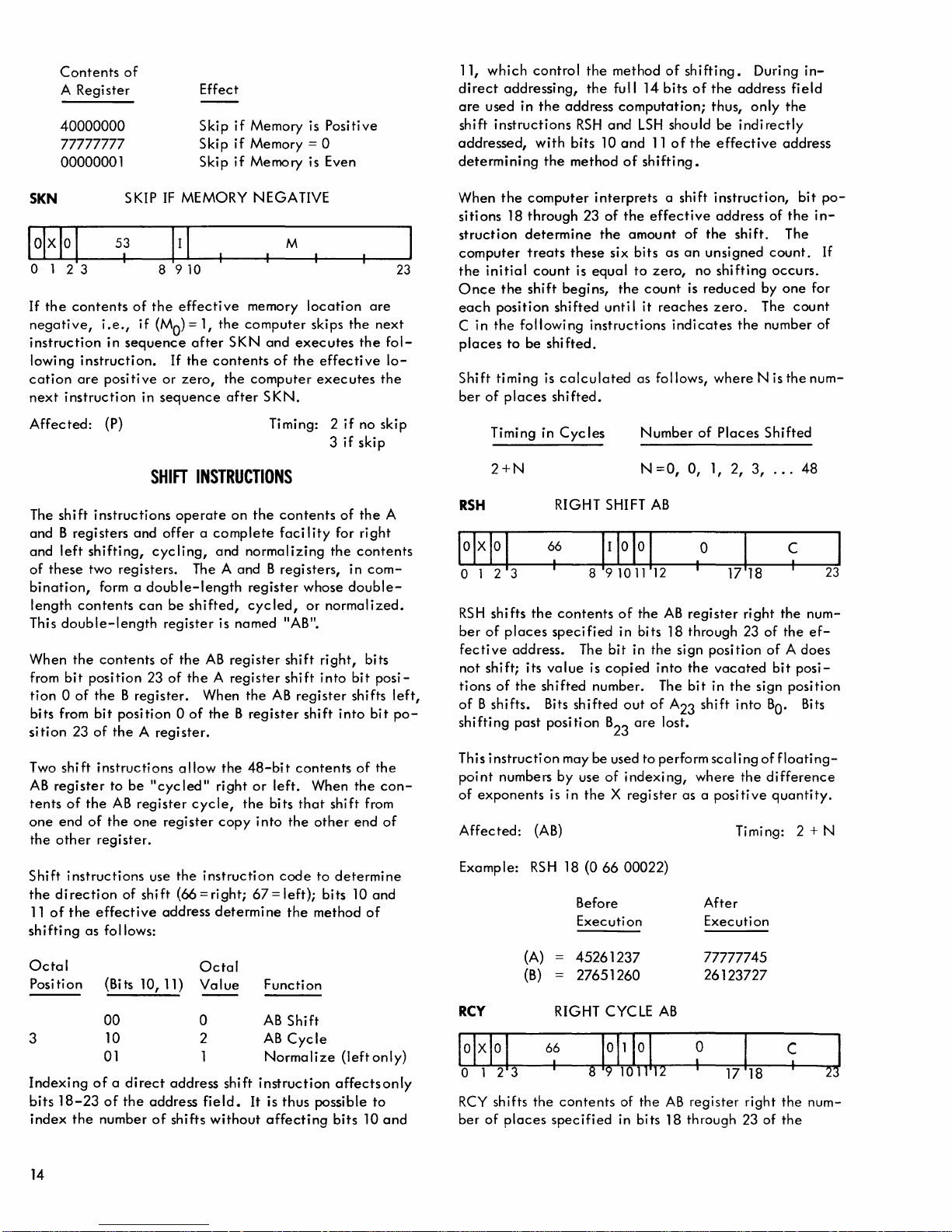

This

section

groups.

and

A-21,

A

companies

ing

identifies

ter

used

indicates

instruction,

cates

ory.

If

indexing

tion 9 of

addressing

instructions

field;

memory,

tion

The

criptions:

Lists

alphabetical

A-26,

diagram

each

diagram

X in

bit

with

that

bit

position 1 of

cannot

the

these

but

code

following

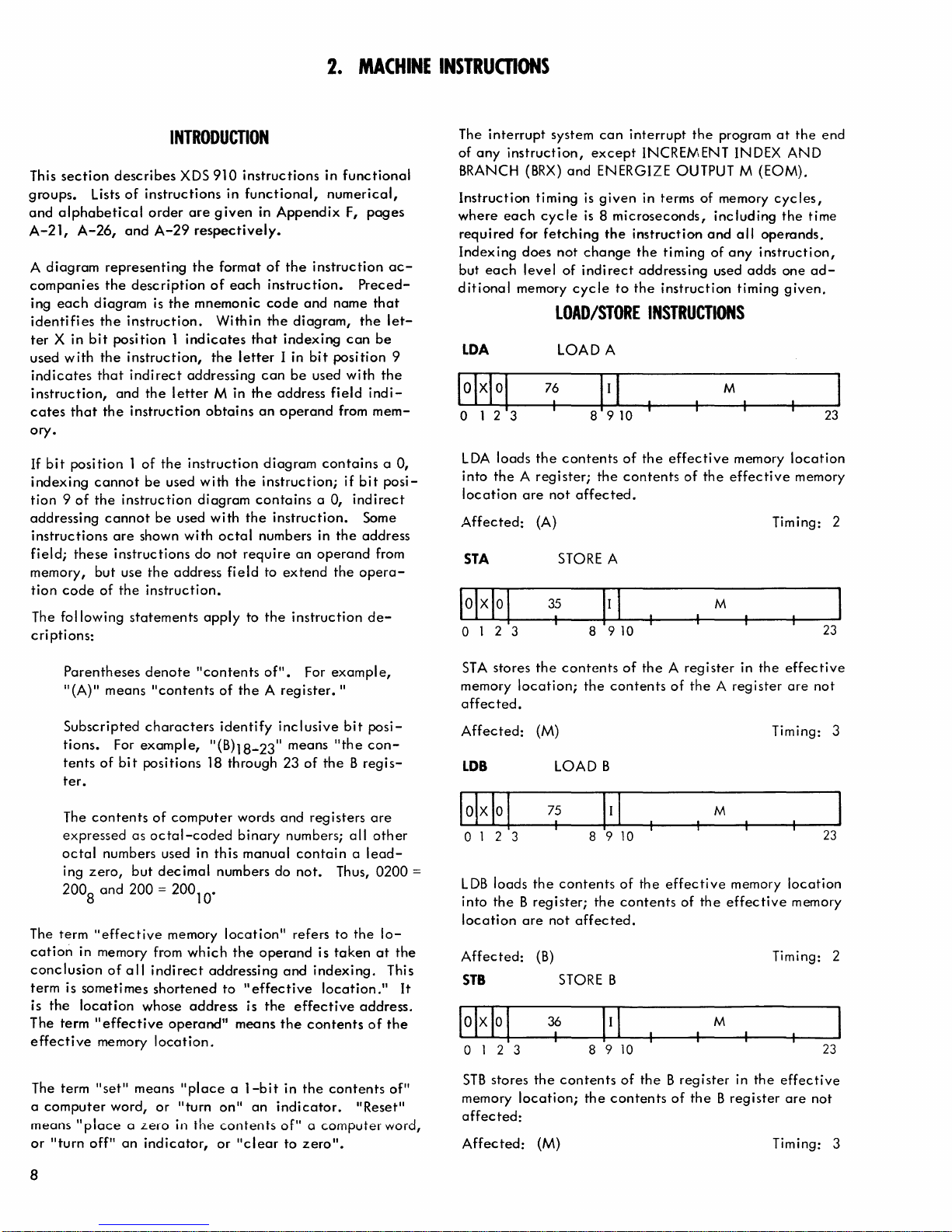

INTRODUCTION

describes

of

and

representing

the

description

the

instruction.

position 1 indicates

the

instruction,

that

indirect

and

the

instruction

instruction

cannot

are

instructions

use

of

the

statements

XDS

instructions

order

are

A-29

respectively.

the

is

the

mnemonic

addressing

the

letter

the

instruction

be

used with

diagram

be

used

shown

with

do

the

address

instruction.

apply

910

in

given

format

of

each

Within

the

letter

M in

obtains

the

with

octal

not

field

instructions

functional,

in

Appendix

of

the

instruction.

code

and

the

diagram,

that

indexing

I in

bit

can

be

the

address

an

operand

diagram

instruction;

contains

the

instruction.

numbers in

require

to

an

to

extend

the

instruction

2.

MACHINE

in

functional

numerical,

F,

pages

instruction

Preced-

name

that

the

can

be

position

used

with

the

field

indi-

from

mem-

contains a 0,

if

bit

a 0,

indirect

Some

the

address

operand

the

from

opera-

de-

ac-

let-

9

posi-

INSTRUCTIONS

The

interrupt

of

any

BRANCH

Instruction

where

required

Indexing

but

each

ditional

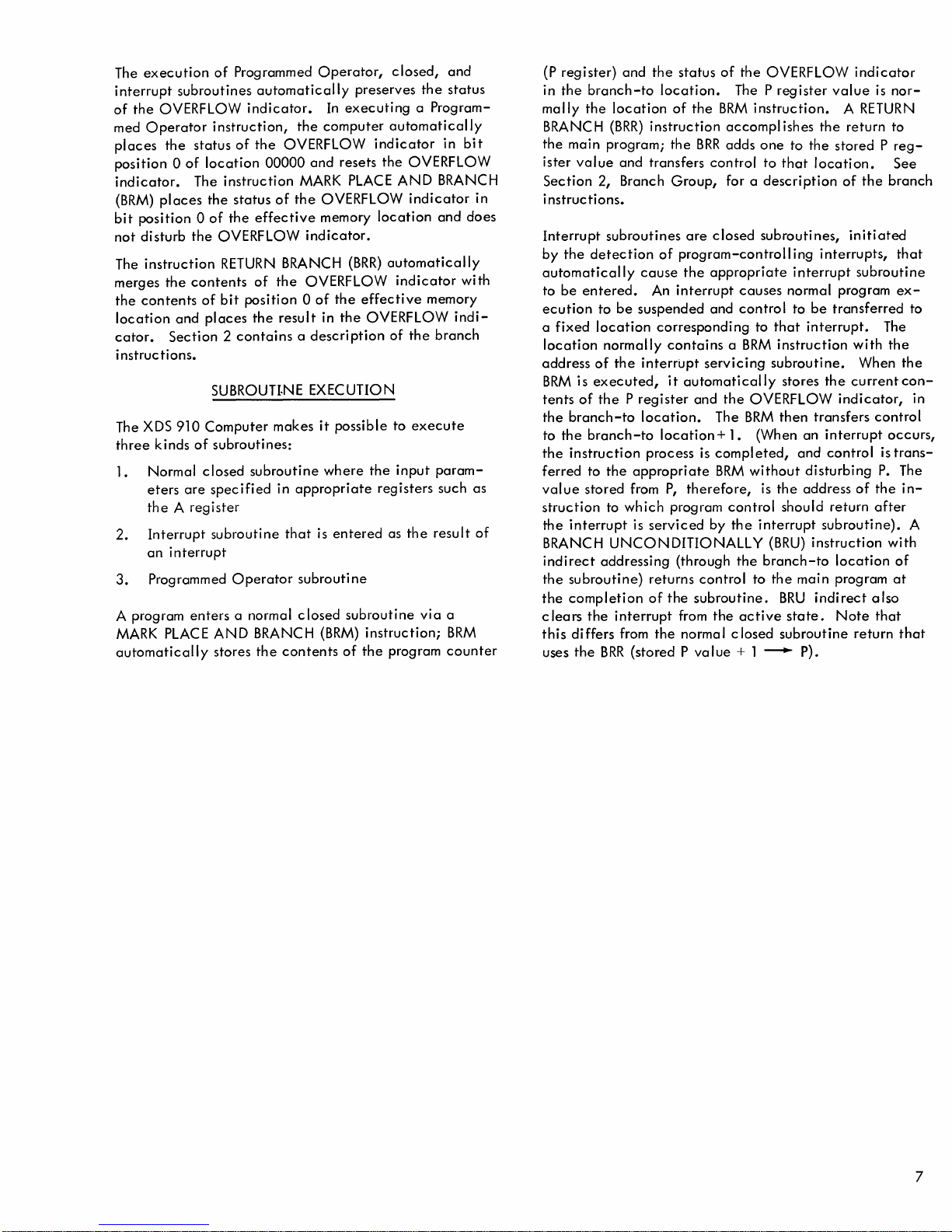

LOA

o 1 2 3

LOA

loads

into

the A register;

location

Affected:

STA

o 1 2 3

system

instruction,

(BRX)

timing

each

cycle

for

fetching

does

level

memory

except

and

is

is 8 microseconds,

not

change

of

indi

cycle

LOAD/STORE

LOAD A

76

I

the

contents

are

not

affected.

(A) Timing: 2

STORE A

8 9

can

interrupt

INCREMENT INDEX

ENERGIZE OUTPUT M (EOM).

given

in terms of memory

the

instruction

the

rect

addressing

to

the

the

program

including

and

timing

instruction

of

used

all

operands.

any

instruction,

adds

timing

at

the

AND

cycles,

the

one

given.

INSTRUCTIONS

M

of

the

the

contents

10

effective

of

the

M

memory

effective

location

memory

end

time

ad-

23

23

Parentheses

"(A)"

means

Subscripted

tions.

tents

ter.

The

expressed

octal

ing

2008 and

The term

cation

conclusion

term is sometimes

is

the

The term

effective

The term

a

computer

means

or

IIturn

For

of

bit

contents

as

numbers used in this

zero,

but

200 = 200

"effective

in memory from

of

all

location

"effective

memory

"set"

means

word,

"place

off"

a z.ero

an

denote

characters

example,

positions 18 through

whose

indicator,

"contents

"contents

"(Bh8-23"

of

computer

octal-coded

decimal

memory

indirect

shortened

operand

location.

or

numbers do

,

10

which

addressing

address

"place a l-bit

"turn

in

the

or

of

the A register."

identify

words

binary

manual

location"

the

operand

to

"effective

is

ll

means

on"

an

contents

"clear

of".

For

example,

inclusive

means

"the

23

of

the B regis-

and

registers

numbers;

contain a leadnot.

refers

to

is

taken

and

indexing.

location."

the

effective

the

contents

in

the

contents

indicator.

of" a computer

to

zeroll.

bit

all

Thus,

the

address.

II

posicon-

are

other

0200

lo-

at

the

This

of

the

of"

Reset"

word,

It

STA

stores

the

contents

memory

affected.

Affected:

LOB

location;

(M)

LOAD B

75

,

o 1 2 3

=

LOB

loads

into

the B register;

location

Affected:

STB

o 1 2 3

STB

stores

memory

affected:

Affected:

the

contents

are

not

affected.

(B)

STORE B

36

I

the

contents

location;

(M) Timing: 3

the

8 9

the

8910

the

of

the A register

contents

10

of

the

contents

of

the B register

contents

of

the A register

M

effective

of

the

M

of

the B register

in

the

Timing: 3

memory

effective

Timing: 2

in

the

effective

are

not

23

location

memory

23

effective

are

not

8

Page 15

LOX

LOAD

INDEX

MIN

MEMORY INCREMENT

o 1 2 3

L

DX

loads

memory

the

effective

Affected:

STX

o 1 2 3

STX

stores

ter

in

the

index

register

Affected:

EAX

o 1 2 3

EAX

copies

into

bit

ten

most

tents

of

71

I

the

entire

location

memory

(X)

STORE INDEX

37

I

the

entire

effective

are

(M)

COpy

REGISTER

77

I

the

address

positions

significant

the

effective

8 9 10

24-bit

into

the

index

location

contents

register;

are

8910

24-bit

contents

memory

not

EFFECTIVE ADDRESS

8 9

10

- 23

bits

affected.

10

of

the

of

the

of

the X register

memory

location;

effective

index

location

M

of

not

M

of

the

M

(X)

the

effective

the

contents

affected.

the

index

contents

INTO

memory

register;

and

are

not

23

of

Timing: 2

23

regis-

of

the

Timing: 3

INDEX

23

location

the

the

con-

affected.

o 1 2 3

MIN

increases

cation

Overflow

37777777

the

Affected:

by

location.

result

MOE

o 1 2 3

MDE

decreases

cation

same

change.

An

40000000.

Affected:

SUB

by

location.

overflow

61

I

8 9 10

the

contents

one,

and

places

The

contents

occurs

before

in

only

execution.

M.

(M),

Of

MEMORY DECREMENT

of

the

the

resulting

of

the A register

when

the

In

contents

this

60

I

8910

the

contents

one

and

places

The

contents

occurs

The

(M),

if

result

Of

SUBTRACT MEMORY FROM A

of

the

the

resulting

of

the A register

the

initial

contents

inmemoryinthiscaseis37777777.

M

effective

sum

do

case,

M

effective

difference

memory

in

the

not

change.

of

Mare

40000000

Timing: 3

memory

do

of

memory

Timing: 3

same

in

not

23

lo-

is

23

lo-

the

are

The

addressing

a

load

instruction,

contents

memory

executed

bit

into

Affected:

of

address

with

configuration

bit

positions

ADD

101+1

o 1 2 3

This

instruction

ory

location

the

result

in

the

sign

of

flow has

FLOW

Affected:

occurred

indicator.

(A),

process for this

except

the

effective

is

the

zeros

in

10

(X)

10-23

ARITHMETIC

ADD MEMORY TO A

55

I

that

.memory

operand.

in

bit

positions 1 and

the

address

-23

of

1 I I

the X register.

INSTRUCTIONS

8910

adds

the

contents

to

the

the

A.

If

result

and

Of

contents

both

in

of

numbers

the A register

the

computer

instruction

instead

location,

For

field

of

the A register

are

of

exampl

of

EAX

M

the

effective

of

the

is

opposite,

has

set

operates

obtaining

9,

the

effective

e,

if

EAX

the

actual

is

copied

Timing: 2

mem-

and

places

same

sign

the

OVER-

Timing: 2

as in

the

23

but

over-

54

I

the

contents

are

address

the

sign

overflow

Of

MUL

64

I

indicator

the

contents

8 9 10

of

and

of

the

same

have

of

the

has

occurred

indicator.

TIPL Y STEP

8910

extends

is

set,

of

the

places

been

result

indicator

the

is

o 1 2 3

SUB

subtracts

tion

from

reg i

ster.

If

both

of

the

effective

addition

opposite,

has

set

Affected:

the A register

numbers

but

an

the

OVERFLOW

(A),

MUS

1 2 3

The sign

the

OVERFLOW

zeros.

of A temporarily

left

if

the OVERFLOW

Then

effective

sign

in

two

two

the

the

compl

and

memory

M

memory

result

in

after

the

contents

emented

the A register

the

computer

Timing: 2

M

bit

positions

is

reset.

bits

extended

location

the

for

If

23

loca-

A

is

23

to

the

are

9

Page 16

determined

tracted

three

operation

ing

from

low-order

table:

B21

by

the

the

A reg ister,

bits

performed

B22

effective

of

the B register.

takes

place

B

23

address

based

Arithmetic

are

on

according

added

the

contents

The

arithmetic

to

Operation

to

the

or

sub-

of

the

follow-

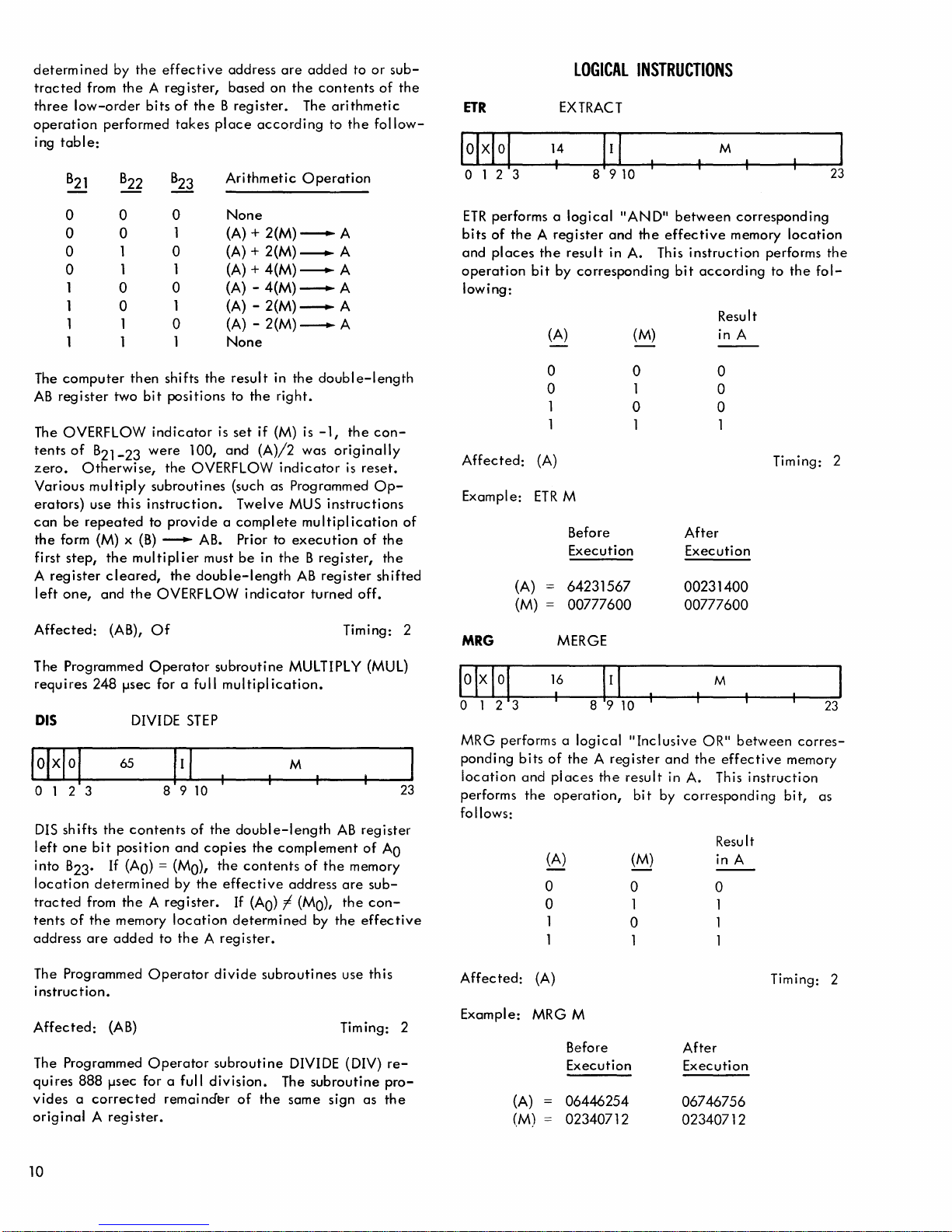

ETR

012

LOGICAL

EXTRACT

14

3

INSTRUCTIONS

M

23

0 0

0 0

0 1 0

0

1

1

1

1 1

The

computer

AB

register

The OVERFLOW

tents

of

zero.

Various

erators)

can

be

the

form (M) x

first

step,

A

register

left

one,

Affected:

The Programmed

requires

DIS

1

0

0

1

then

two

B21-23

Otherwise,

multiply

use

this

repeated

the

multipl

cleared,

and

the

(AB),

248

fJsec for a full

DIVIDE

65

o 1 2 3

DIS

shifts

the

contents

left

one

bit

position

into

B23.

If

(AO)

location

tracted

tents

address

of

determ

from

the A register.

the

memory

are

added

0

1 (A) + 2(M)

1

0

1

0

1

shifts

bit

positions

indicator

were

the

subroutines

instruction.

to

provide a complete

(B)

--+-

the

OVERFLOW

Of

Operator

8 9

and

= (MO),

ined

by

location

to

the A register.

None

(A) + 2(M)

(A) +

(A) - 4(M)

(A) - 2(M)

(A) - 2(M)

None

the

is

100,

and

OVERFLOW

AB. Prior to

ier

must

double-length

subroutine

multiplication.

STEP

10

of

the

copies

the

the

effective

---.

A

----.

A

4(M)

----.

A

---.

A

---.

A

---.

A

result

in

the

double-length

to

the

right.

set

if

(M) is

-1,

the

(A)/2

was

originally

indicator

(such as Programmed

Twelve

be

double-length

If

determined

MUS

execution

in

the B register,

AB

indicator

MULTIPLY (MUL)

M

the

complement

contents

address

(AO)

-I

(MO),

is

instructions

multiplication

register

turned

off.

Timing: 2

AB

of

the

memory

are

the

by

the

con-

reset.

Op-

of

of

the

the

shifted

23

register

of

AO

subcon-

effective

ETR

performs a

bits

of

the A register

and

places

operation

lowing:

the

bit

by

(A)

o

o

1

1

Affected:

Example:

MRG

o 1 2 3

MRG performs a

ponding

iocation

performs

follows:

(A)

(M)

bits

and

the

(A)

ETR

MERGE

16

I

of

piaces

operation,

(A)

0

0

1

1

logical

result

"AND"

and

the

in A. This

corresponding

(M)

o

1

o

1

M

Before

Execution

64231567

00777600

89

10

logical

the A register

"Inclusive

the

result

bit

(M)

0

1

0 1

1

between

effective

instruction

bit

according

Result

in A

o

o

o

1

After

Execution

00231400

00777600

M

OR"

and

the

in A. This

by

corresponding

Result

in A

0

1

corresponding

memory

between

effective

location

performs

to

Timing: 2

memory

instruction

bit,

the

corres-

the

fol-

23

as

The Programmed

i nstruc

tion.

Affected:

The Programmed

quires

888

vides a corrected

original A register.

10

Operator

(AB)

Operator

fJsec for a full

remainder

divide

subroutine

division.

of

the

subroutines

DIVIDE (DIV)

The

subroutine

same

use this

Timing: 2

sign

as

reprothe

Affected:

Example:

(A)

(M)

(A)

MRGM

Before

Execution

06446254

02340712

Timing: 2

After

Execution

06746756

02340712

Page 17

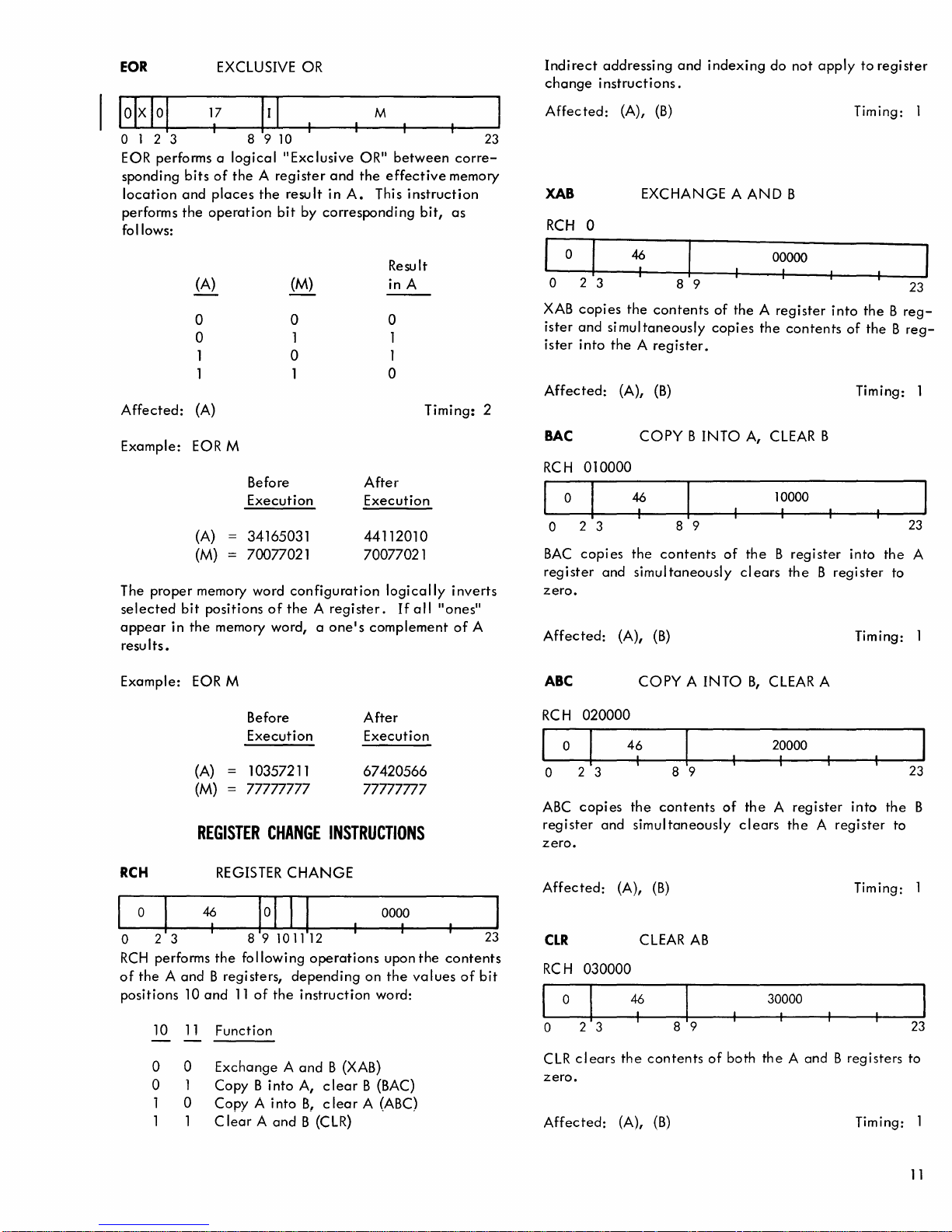

EOR

EXCLUSIVE

OR

Indirect

change

addressing

instructions.

and

indexing

do

not

apply

to

register

I

IOIXIOI

17

o 1 2 3 8 9

EOR performs a

sponding

location

performs

follows:

Affected:

Example:

The

selected

appear

resu

proper

in

Its.

bits

of

and

places

the

operation

(A)

0

0

1

1

(A)

EORM

(A)

(M)

memory word

bit

positions

the

memory word, a

I I I

10

logical

the A register

II

Exc lusive

the

result

bit

(M)

0

1

0

Before

Execution

34165031

70077021

configuration

of

the A register.

by

M

OR"

between

and

the

effective

in

A.

This

corresponding

Result

in A

o

1

1

o

After

Execution

44112010

70077021

logically

If

one's

complement

corre-

memory

instruction

bit,

as

Timing:

inverts

all

"ones"

of

A

23

2

Affected:

XAB

RCH

0

o 2 3

XAB

copies

ister

and

ister

into

Affected:

BAC

RCH

010000

o 2 3

BAC

copies

register

zero.

Affected:

(A),

(B)

EXCHANGE A AND

46

I

8 9

the

contents

si

mul

taneously

the A register.

(A),

(B)

COpy B INTO

46

I

8 9

the

contents

and

simultaneously

(A),

(B)

of

the A register

copies

the

A, CLEAR B

of

the B register

clears

B

00000

I

into

contents

10000

I

the B register

Timing: 1

the B reg-

of

the B reg-

Timing: 1

into

the

to

Timing: 1

23

23

A

Example:

RCH

023

RCH

performs

of

the A and

positions

10

o 0

o 1

1

1 1 C

EOR M

Before

Execution

(A)

(M)

10357211

77777777

REGISTER

REGISTER

46

I

89101112

the

following

B regi sters,

10

and

11

11

Function

Exchange A and

Copy B into

0

Copy A into

lear A and

CHANGE

CHANGE

depending

of

the

instruction

A,

B, c lear

B (CLR)

After

Execution

67420566

77777777

INSTRUCTIONS

0000

I

operations

B (XAB)

clear

upon

on

the

word:

B (BAC)

A (ABC)

va

the

lues

23

contents

of

bit

ABC

RCH

020000

023

ABC

copies

register

zero.

Affected:

CLR

RCH

030000

o 2 3

CLR

clears

zero.

Affected:

COpy A INTO

46

I

the

and

simultaneously

(A),

(B)

CLEAR

46

I

the

contents

(A),

(B)

8 9

contents

AB

B,

of

the A register

clears

of

both

CLEAR A

20000

I

into

the

the A register

to

Timing: 1

30000

the A and B registers

Timing:

23

B

23

to

11

Page 18

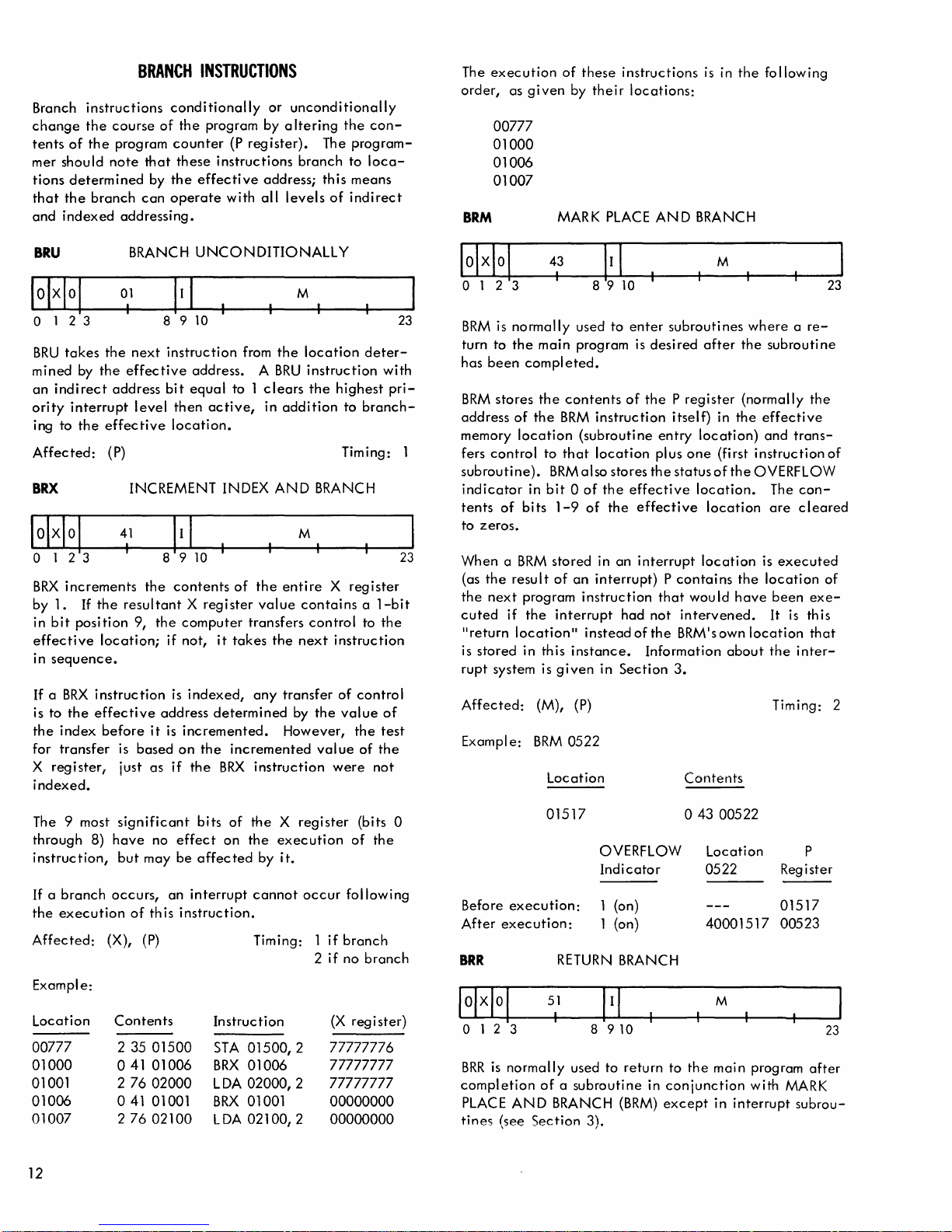

Branch

change

tents

mer

should

tions

that

the

and

indexed

instructions

the

course

of

the

program

note

determined

branch

addressing.

BRANCH

that

by

can

INSTRUCTIONS

conditionally

of

the

program by a

counter

these

the

effective

operate

or

(P

reg

ister).

instructions

address;

with

all

unconditionally

Itering

levels

The

branch

this

of

the

con-

program-

to

loca-

means

indirect

The

order,

BRM

execution

as

given

00777

01000

01006

01007

of

these

by

MARK

instructions

their

PLACE

locations:

AND

is

in

the

BRANCH

following

BRU

o 1 2 3

BRU

takes

mined

an

ority

Affected:

indirect

ing to

by

interrupt

the

BRX

o 1 2 3

BRX

increments

by

1.

If

in

bit

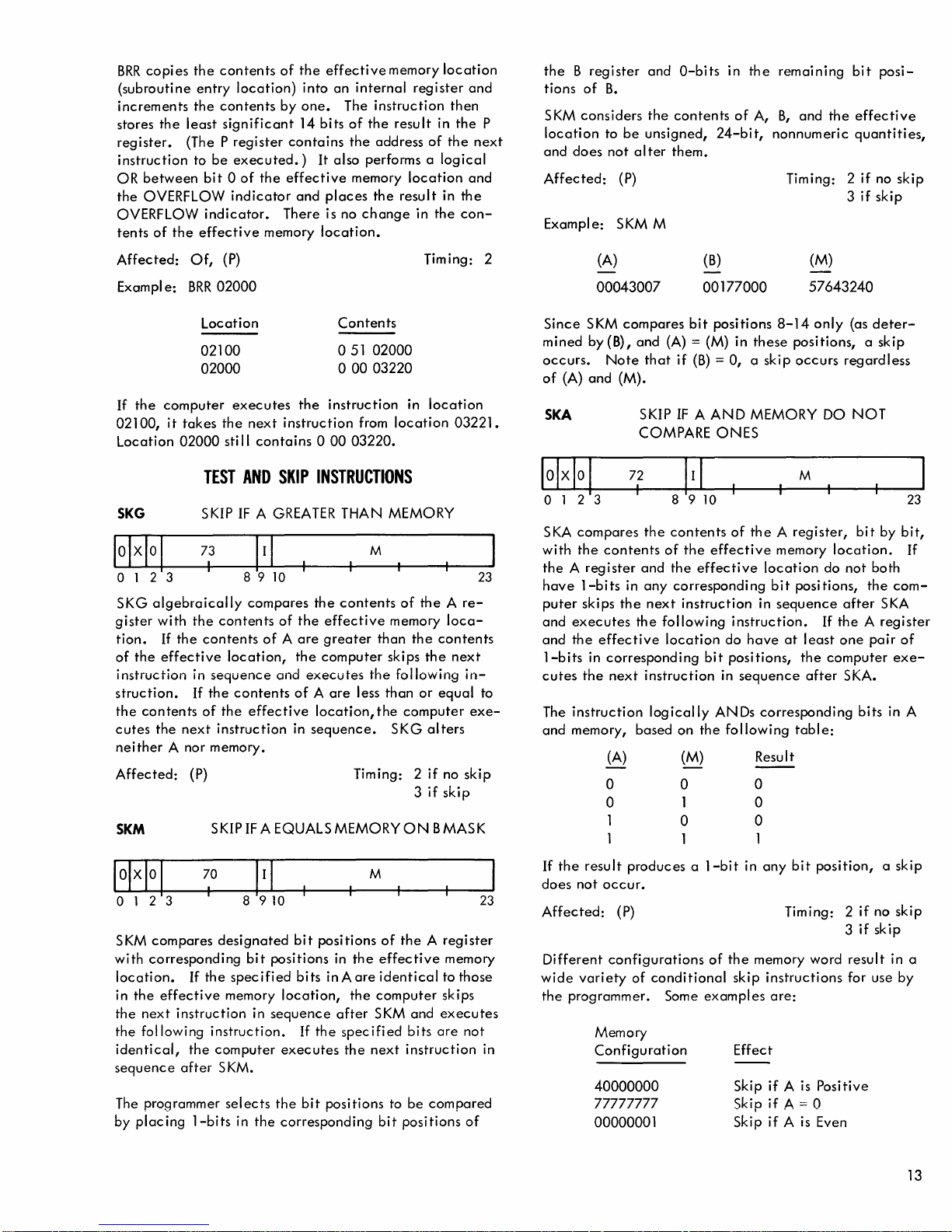

position