Page 1

SWA51, 5GHz Module Datasheet

General Description

The SWA51 module is a member of a family of

products representing a new level of system

integration offering customers fast time to

market with a point-to-point mono, or stereo,

wireless connection. These modules are

optimized for low-cost, high-quality and ease-ofuse.

The module incorporates Avnera’s proprietary

5GHz wireless audio protocol, designed from the

ground up specifically for audio. It features low

fixed latency, uncompressed CD quality mono or

stereo audio, superior interference immunity,

and inherent coexistence with WiFi.

The SWA51 module integrates all features

necessary to complete a wireless stereo or

mono link, including AV5100 Wireless Audio

Chip, printed diversity antennas, PA, shield can,

flash memory, interface connector and all

passive components. Just provide power and an

I2S interface and you are ready to create a

wireless audio link.

The module measures 26 x 47 x 3.3 mm and is

provided with a 24 pin FPC connector.

The module is certified to FCC and CE

standards.

Extended Range Mono/Stereo Wireless Audio System, based on the Avnera AV5100 IC

Features

Audio Interfaces

I2S Digital Input / Output interface with

>93dB end-to-end digit al audio path

Wireless Range (Typ)

> 50m Non Line Of Sight (NLOS) range

> 160m Line Of Sight (LOS) range

Frequency range: 5.15-5.25&5.725-5.825 GHz,

continuous dynamic channel selection

Forward error correction coding, error

detection, and audio-specific error

concealment

Dual printed PCB diversity antennas for

multipath and fading mitigation

Auto-search/synch and dynamic channel

selection

Low, fixed latency

24 pin FPC or pin header connector

Sample rate converter: Support for 32 - 96kHz

input sample rates

Customizable firmware for simple, low-cost,

sub-woofer amplifier implementations

Applications

Wireless Subwoofers

Stereo Wireless Rear Speakers

Soundbar / Audio Video Receiver / BluRay

Mono/Stereo Audio Channel Transmission

Ordering Options

SWA51 TX: Transmit module with digital audio

input

SWA51 RX: Receive module with digital audio

output

RF parts can-shielded, module meets FCC

part 15 rules for emissions and susceptibility.

General purpose over-the-air (OTA) serial

interface:

11 kbps, bi-directional, full duplex

Support for amplifier control data, meta-

data, and remote control commands

Different labels and P/Ns are used to

distinguish between TX and RX.

CONFIDENTIAL | PROVIDED UNDER NDA

Page 2

SWA51 Module Datasheet Rev 1.1

1 Functional Description

The SWA51 module is available in 2 variations; digital input transmitter module or digital output receiver

module.

There are three available I2S digital audio data inputs/outputs, each of these can be configured to operate as

either a master or a slave - depending on the application, the I2S ports can oper ate simultaneously as either

inputs or outputs. When configured as slaves, the I2S inputs/outputs can be inde pendently clocked by up to

two external masters. In addition, MCLK can be output from the module to provide a reference clock source to

an external ADC or DAC. MCLK can also be input to the module to provide a reference clock from an

external source.

The hardware for the audio input (transmit) a nd audio output (re ceive) versions of the module is id entical and

only the firmware loaded onto the module determines its function.

The highly integrated nature of the AV5100 transceiver IC results in few external components being required

for the SWA51 module design. 2 pr inted PCB antennas are u sed to achieve increased range, a nd to achieve

antenna spatial diversity. The extended-range RF path consists of the antennas, associated tuning

components, shield can, the RF switch, and two baluns, one connected to each of the RF input/output ports

on the AV5100 IC.

A 16MHz crystal oscillator generates the AV5100 fundamental system clock used as the basis for all RF and

digital audio clocks.

A 2Mb flash memory chip is used to store the module’s application firmware. The AV5100 is able to boot from

internal ROM upon first power up, which enables programming the flash chip with the application fir m ware . In

addition, Over-the-air Firmware upgrade capability can be enabled through the application firmware. The

module can be controlled from an external host device via the I2C Slave or the SPI Slave data interfaces. The

I2C master port allows the module to control other system audio devices such as a sub-woofer amplifier

system without having to add another MCU to the product design. Up to 9 additional GPIOs are available on

the SWA51 module (not including I2C and I2S signals) fo r implementing different UI features on the target

application. The resources mentioned above can be lever aged to implement low cost sub-woofer d esigns as

outlined below.

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 2 CONFIDENTIAL

Page 3

SWA51 Module Datasheet Rev 1.1

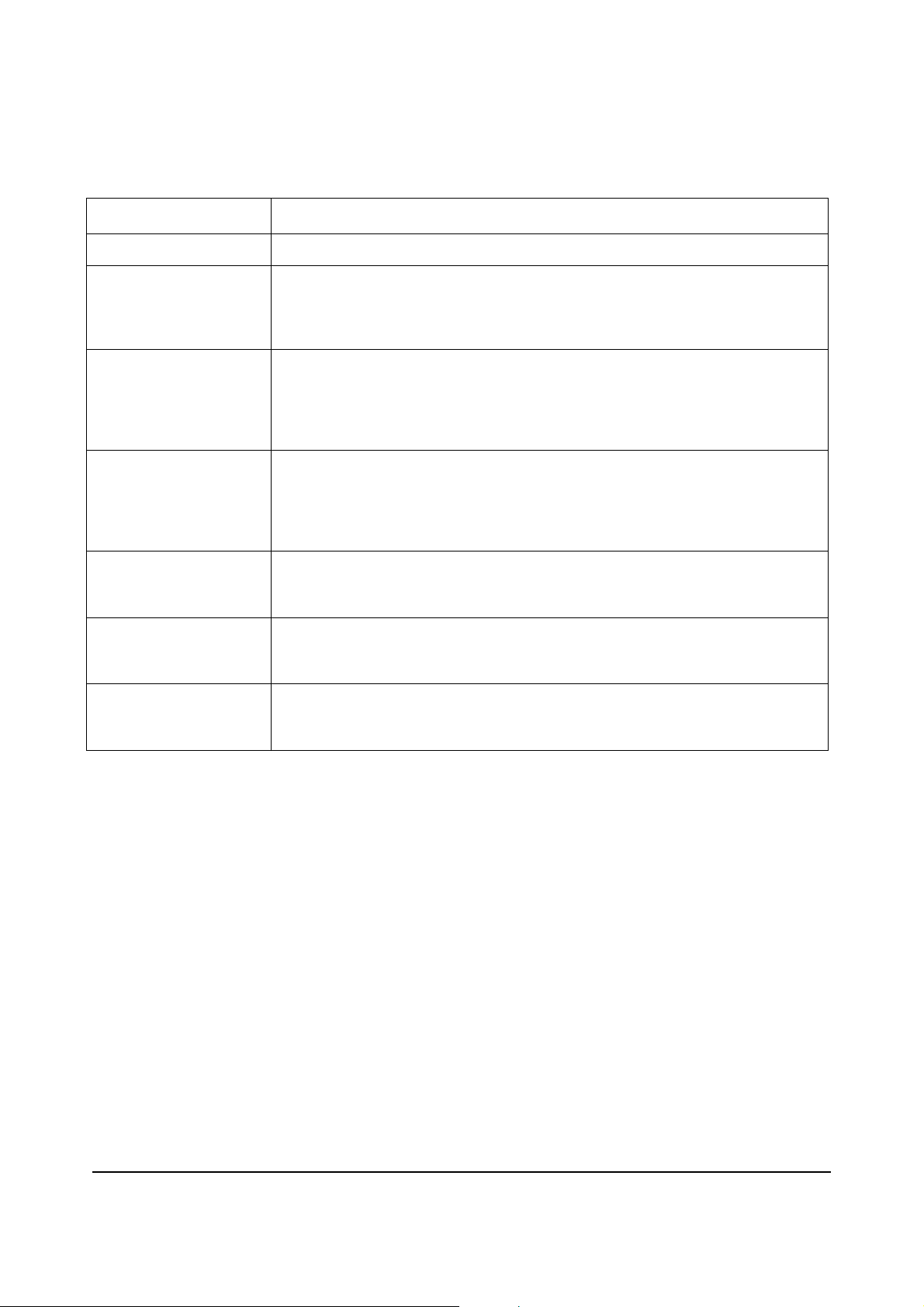

1.1 SWA51 Module Connections and Interfaces

Signal Type Description

+3.3V Supply

Reset

I2S In Port

I2S Out Port

I2C Slave Port

I2C Master Port

The SWA51 hardware is configured to accept a nominal +3.3V supply.

Active low reset input. This pin is driven from an open collector/drain device such

that it can be pulled to ground for the active r eset state b ut, when r eleased , mu st

go to a high impedance state. This pin should not be actively driven high, as the

AV5100 internal reset circuit will not operate correctly.

The I2S input port can be co nfigured as a master or slave. Conse quently BCLK

and LRCK can be either inputs or outputs. In addition, MCLK can be sourced by

the module on pin 16. Since the AV5100 IC contains a sample rate converter,

MCLK is not required to be supplied to the module when it is an I2S slave.

CMOS 3.3V logic levels are used for all I2S signals.

The I2S output port can be configured as a master or slave. Conseq uently BCLK

and LRCK can be either inputs or outputs. In addition, MCLK can be sourced by

the module on pin 16. Since the AV5100 IC contains a sample rate converter,

MCLK is not required to be supplied to the module when it is an I2S slave.

CMOS 3.3V logic levels are used for all I2S signals.

The I2C slave port can be used for external host com munication and for module

testing. It is assumed that external pull up resistors are connected at the I2C

master communicating with the module.

The I2C master port is used to communicate with external audio devices such as

a sub-woofer amplifier. It is assumed that external pull up resistors are included

on the application board.

GPIOs

3.3V CMOS logic level GPIOs available to connect to other devices, or to use as

UI supporting GPIOs for LED and button support. All supported GPIOs can be

configured as outputs or inputs with configurable pull-ups/pull-downs.

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 3 CONFIDENTIAL

Page 4

SWA51 Module Datasheet Rev 1.1

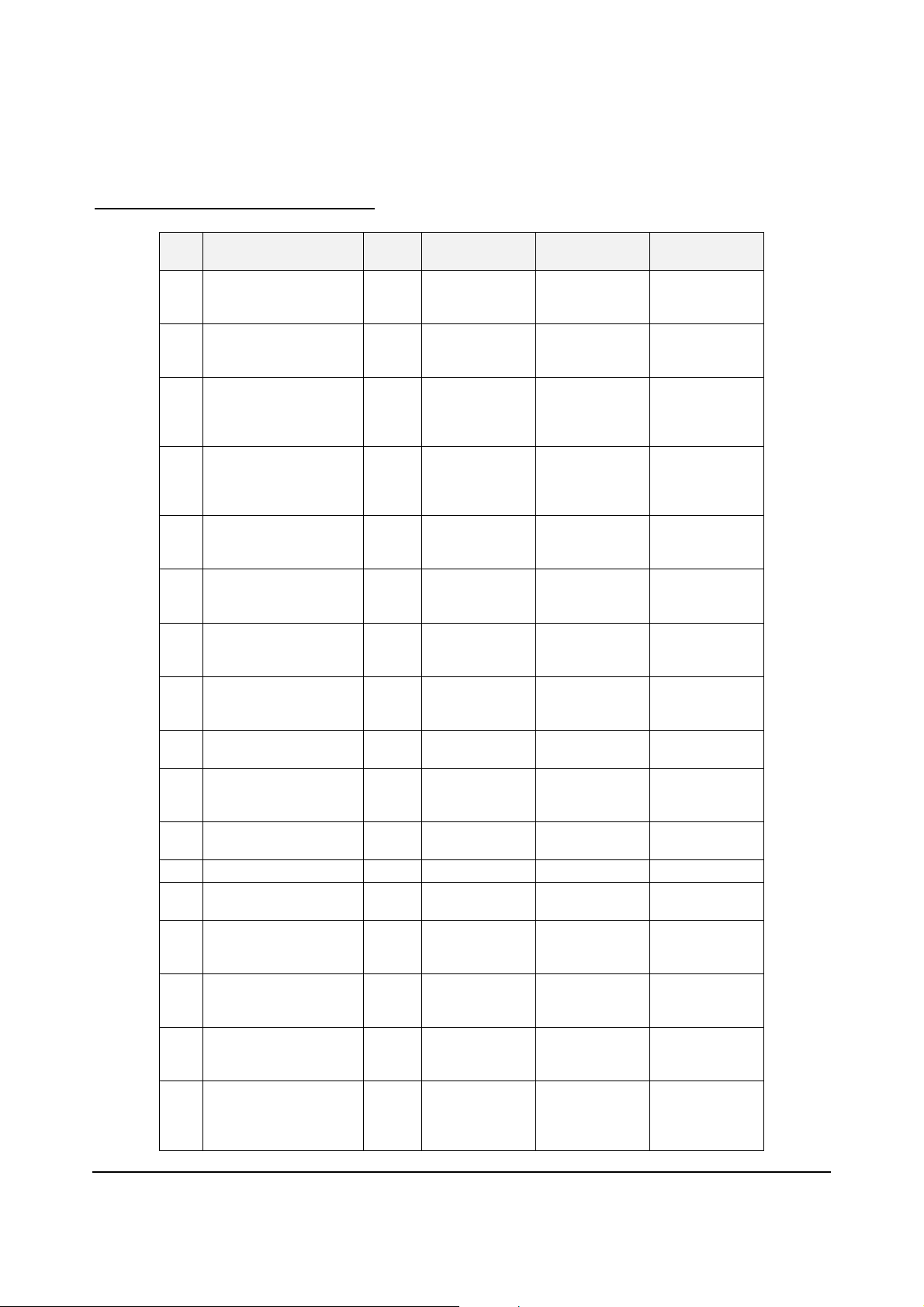

2 SWA51 Connector Information

Table 1: SWA51 Connector Information

No Pin Name

Pin

AV5100 Pin

Type

1 GPIO2/S_SSB

Digital

12

I/O

2 GPIO3/S_SCLK

Digital

11

I/O

3 GPIO4/S_SDA/S_MOSI

Digital

10

I/O

4

GPIO5/S_SCL/S_MISO

Digital

9

I/O

5 GPIO16/M_SDA

Digital

4

I/O

6 GPIO17/M_SCL

Digital

3

I/O

7 GPIO20/LINK_LED

Digital

56

I/O

8 GPIO21/PAIR

Digital

55

I/O

9 GPIO18/BCLK1

Digital

2

I/O

10 GPIO19/WCLK1

Digital

1

I/O

11 GPIO10/MCLK

Digital

53

I/O

12 GND GND Paddle (57) GND GND

13 GPIO11/BCLK0

Digital

52

I/O

14 GPIO12/WCLK0

Digital

51

I/O

15 GPIO13/ADAT0

Digital

50

I/O

16 GPIO14/ADAT1

Digital

49

I/O

17 GPIO15/ADAT2/CEN

Digital

48 or 38

I/O or

Digital

Input

SWA51-TX Pin

Description

GPIO or SPI

Slave Chip

Select

GPIO or SPI

Slave Serial

Clock

GPIO, I2C

Slave Serial

Data or SPI

Slave Data In

GPIO, I2C

Slave Serial

Clock or SPI

Slave Data Out

GPIO, I2C

Master Serial

Data

GPIO, I2C

Master Serial

Clock

GPIO, or

LINK_LED

Output

GPIO, or input

from PAIR

Button

GPIO or I2S

Port 1 Bit Clock

GPIO or I2S

Port 1 Word

Clock

GPIO or Master

Clock Out

GPIO or I2S

Port 0 Bit Clock

GPIO or I2S

Port 0 Word

Clock

GPIO or I2S

Port 0 Audio

Data

GPIO or I2S

Port 1 Audio

Data

GPIO, I2S Port

2 Audio Data or

chip enable

1)

(

SWA51-RX Pin

Description

GPIO or SPI

Slave Chip

Select

GPIO or SPI

Slave Serial

Clock

GPIO, I2C

Slave Serial

Data or SPI

Slave Data In

GPIO, I2C

Slave Serial

Clock or SPI

Slave Data Out

GPIO, I2C

Master Serial

Data

GPIO, I2C

Master Serial

Clock

GPIO, or

LINK_LED

Output

GPIO, or input

from PAIR

Button

GPIO or I2S

Port 1 Bit Clock

GPIO or I2S

Port 1 Word

Clock

GPIO or Master

Clock Out

GPIO or I2S

Port 0 Bit Clock

GPIO or I2S

Port 0 Word

Clock

GPIO or I2S

Port 0 Audio

Data

GPIO or I2S

Port 1 Audio

Data

GPIO, I2S Port

2 Audio Data or

chip enable

1)

(

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 4 CONFIDENTIAL

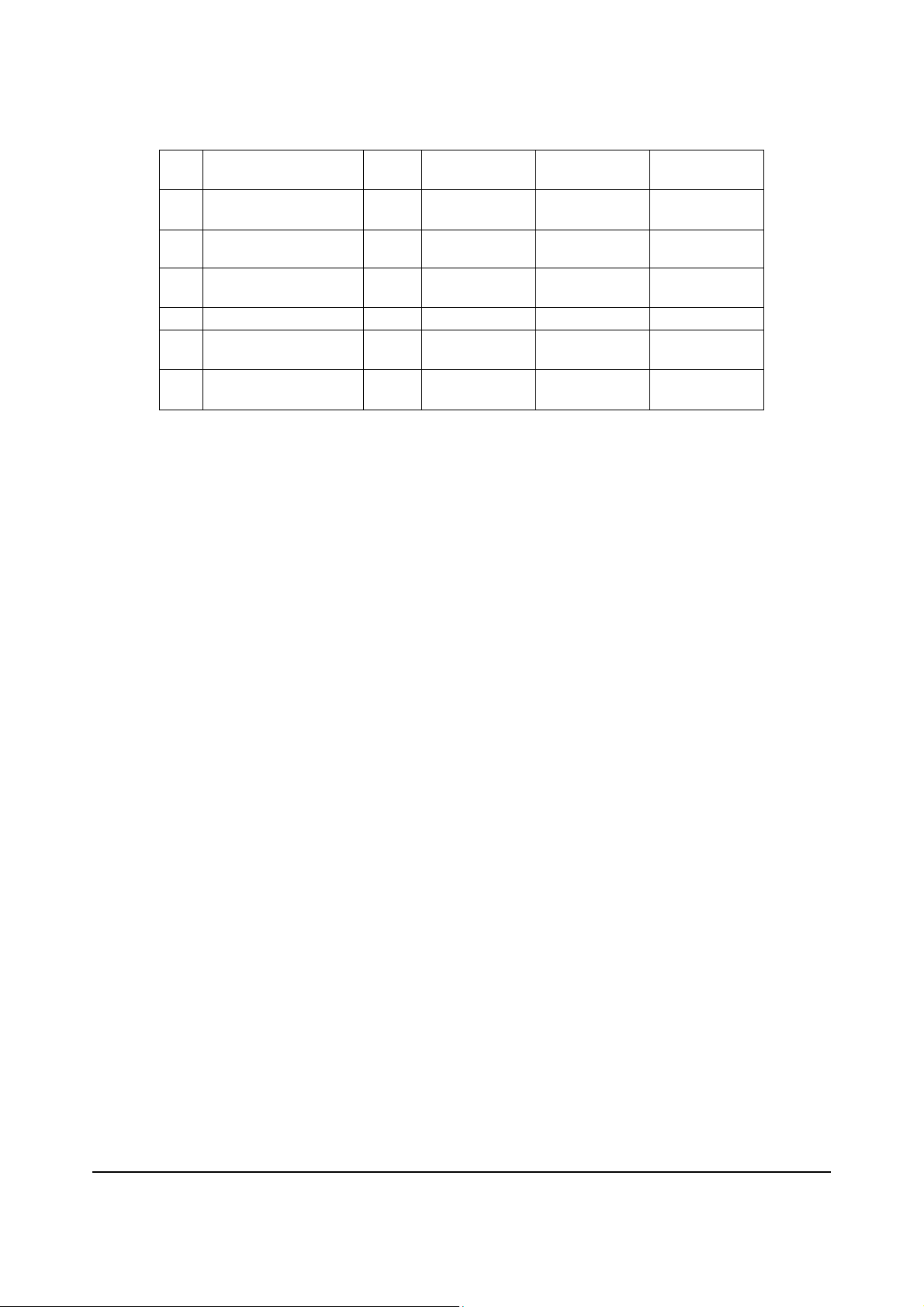

Page 5

SWA51 Module Datasheet Rev 1.1

18 GPIO22/D+

19 GPIO23/D-

20 GPIO24

Digital

I/O

Digital

I/O

Digital

47 or 43

46 or 42

41

GPIO or USB

Data Plus

)

(2

GPIO or USB

Data Minus

)

(3

GPIO

GPIO

)

(2

GPIO or USB

Data Plus

)

(2

GPIO or USB

Data Minus

)

(3

)

(2

I/O

21 RESETN_EXT

Digital

Input

37

RESET signal

active low

)

(4

RESET signal

active low

)

(4

22 GND GND Paddle (57) GND GND

23 VDD

24 VDD

Supply

Input

Supply

Input

31, 45, 54

31, 45, 54

+3.3Vinput

supplyvoltage

+3.3Vinput

supplyvoltage

+3.3Vinput

supplyvoltage

+3.3Vinput

supplyvoltage

Notes:

(1) Pin 17 is hardware configured as GPIO15/ADAT2 by default; utilizing this pin as a CEN requires a

different stuffing option.

(2) Utilizing pins 18 and 19 as USB D+ and D- requires the firmware to Tri-stat e GPIOs 22 and 23.

(3) Pin 20 (GPIO24) can be utilized to implement a “Data Waiting” interrupt signal for I2C and SPI Slave

data communication.

(4) Pin 21 (RESET_EXT) can be pulled to GND with a switch or an open drain/collector type device to

provide a hard reset signal to the AV5100. This pin is pulled up to VDDIO (3.3V) internally in the

AV5100 and should not be actively driven high.

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 5 CONFIDENTIAL

Page 6

SWA51 Module Datasheet Rev 1.1

3 Electrical, Audio and Timing Specifications

3.1 Absolute Maximum Ratings

Absolute Maximum Ratings (AMR) are stress ratings only. AMR corresponds to the maximum value that can be applied without leading to

instantaneous or very short-term unrecoverable hard failure (destructive breakdown). Stresses beyond those listed under AMR may

cause permanent damage to the device.

Functional operation of the device at these or any other conditions beyond those indicated under “Recommended Operating Range” is

not implied. Exposure to absolute-maximum-rated conditions for extended periods may adversely affect device reliability.

Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test

conditions specified.

CONDITION MIN MAX

+3.3V Supply Voltage Input -0.3V 4.0V

Input Voltage Range – Digital

Inputs

Input Voltage Range – Analog

Inputs

Operating Temperature -40ºC +60ºC

Storage Temperature -40ºC +70ºC

Static Discharge Voltage1 2kV ----

-0.3V 3.6V

-0.3V 3.6V

Notes:

1)HBM=ESDHumanBodyModel;C=100pF,R=1kΩ

3.2 Recommended Operating Range

PARAMETER MIN TYP MAX UNIT

VDD, +3.3V Supply pin voltage 3.0 3.3 3.6 V

Ambient Temperature (TA) 0 55 ºC

RESET pin hold time 10 msec

Power Supply Rise Time (to 3.0V) 0 10 msec

3.3 Electrical Characteristics – DC Characteristics

OperatingConditions:VDD=3.3V,TA=0°Cto+55°C,RFFreq=5150‐5250;5725‐5825MHz,measuredrelativetotheRFbalun

single‐endedI/O.TypicalspecificationsatT

A=25°C,VDD=3.3V

PARAMETER CONDITIONS MIN TYP MAX UNIT

Supply Current (IVDDA)

Shutdown (chip disabled)

Standby (also USB suspend)

RX mode (continuous RX)

Link mode ( for SWA51 TX)

TBD

TBD

89

110*a

1

2.5

uA

mA

mA

mA

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 6 CONFIDENTIAL

Page 7

SWA51 Module Datasheet Rev 1.1

Link mode ( for SWA51 RX)

TX mode (continuous TX); Po ut=+6dBm

70*a

150*a

mA

mA

CMOS I/O Logic Levels – 3.3V I/O

Input Voltage Logic Low, VIL

Input Voltage Logic High, VIH

VDDIO

V

0.6 V

‐0.6

Output Voltage Logic Low, VOL

Output Voltage Logic High, VOH

VDDIO

‐0.3

0.3 V

V

*a : This is DCRMS current consumption value. If customer want to implement OCP(over current protection) for SWA51,

please consult with WNC for proper setting and design.

3.4 Electrical Characteristics – RF PLL Characteristics

OperatingConditions:VDD=3.3V,TA=0°Cto+55°C,RFFreq=5150‐5250;5725‐5825MHz,measuredrelativetotheRFbalun

single‐endedI/O.TypicalspecificationsatT

A=25°C,VDD=3.3V

PARAMETER CONDITIONS MIN TYP MAX UNIT

RF Channel Frequency Range Band1(lower band) 5150 5250 MHz

Band4(Upper band) 5725 5825 MHz

RF Channel frequency resolution (raster) 1 MHz

RF I/O Impedance ANT0,ANT1 50 ohm

Crystal Oscillator Frequency External crystal 16 MHz

Crystal Accuracy Requirement External XTAL, -20°C to +70 °C +/-20 ppm

Electrical Characteristics – RF RX Characteristics

3.5

OperatingConditions:VDD=3.3V,TA=0°Cto+55°C,RFFreq=5150‐5250;5725‐5825MHz,measuredrelativetotheRFbalun

single‐endedI/O.TypicalspecificationsatT

A=25°C,VDD=3.3V

PARAMETER CONDITIONS MIN TYP MAX UNIT

RF Channel Frequency Range Band1(lower band) 5150 5250 MHz

Band4(Upper band) 5725 5825 MHz

RF I/O Impedance ANT0,ANT1 50 ohm

RX Sensitivity SSC (single sub-carrier) -89 *b dBm

Max input signal LNA = low gain mode, min IF gain -5 dBm

Out-of-band blocker level <5150 MHz, >5850 MHz

2400-2483.5 MHz

Spurious RF outputs 5150-5850 MHz

<5150 MHz

>5850 MHz

-45

dBm

-20

-55

dBm

-63

-63

dBm

dBm

dBm

*b : The sensitivity been defined with BER <= 0.002.

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 7 CONFIDENTIAL

Page 8

SWA51 Module Datasheet Rev 1.1

3.6 Electrical Characteristics – RF TX Characteristics

OperatingConditions:VDD=3.3V,TA=0°Cto+55°C,RFFreq=5150‐5250;5725‐5825MHz,measuredrelativetotheRFbalun

single‐endedI/O.TypicalspecificationsatT

A=25°C,VDD=3.3V

PARAMETER CONDITIONS MIN TYP MAX UNIT

RF Channel Frequency Range Band1(lower band) 5150 5250 MHz

Band4(Upper band) 5725 5825 MHz

RF I/O Impedance ANT0,ANT1 50 ohm

TX Output power(5150-5250MHz)

SSB&DSB (single side band & double

6 dBm

side band)

TX Output power(5725-5825MHz)

SSB&DSB (single side band & double

6 dBm

side band)

LO leakage -20 dBc

(1) Measured at the worst performing frequency

3.7 Electrical Characteristics – Audio C/CS

PARAMETER CONDITIONS MIN TYP MAX UNIT

Frequency Response (-3dB)

16 bit audio, 11KSps over-the-air

sample rate

16 bit audio, 14.8KSps over-theair sample rate

16 bit audio, 22KSps over-the-air

sample rate

16 bit audio, 29.6KSps over-theair sample rate

16 bit audio, 44KSps over-the-air

sample rate

20 5K Hz

20 6.5K Hz

20 10K Hz

20 13K Hz

20 20K Hz

Gain Flatness1 0dB Input / Output Gain ±0.2 dB

SNR I2S Input / Output 93

(1)

dB

THD+N 94 dB

Notes

1- 16-bit audio, all OTA sample rates. OTA 12-bit path for voice is possible, but will limit the SNR to 72dB.

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 8 CONFIDENTIAL

Page 9

SWA51 Module Datasheet Rev 1.1

3.8 AV5100 Rate Converter Characteristics

SRC Block Input Rates Output Rates SNR (dB) SRC BW (-3dB)

SRC 0

(Audio)

SRC 1

(LFE)

SRC 2

(Voice)

I2S

32-96K

USB

8k – 48K,

ECU (TX)

“11K”

“14.8k”

“22k”

“29.6k”

“44k”

I2S

32-96K

USB

8k – 48K,

ECU (TX)

“11K”

“14.8k”

“22k”

“29.6k”

“44k”

I2S

32-96K

USB

8k – 48K,

ECU (TX)

“14.8k”

I2S

Master: 48k

Slave: 44.1K-96K

ECU (TX)

“11K”

“14.8k”

“22k”

“29.6k”

“44k”

I2S

Master: 48k

Slave: 44.1K-96K

ECU (TX)

“11K”

“14.8k”

“22k”

“29.6k”

“44k”

I2S

Master: 48k

Slave: 44.1K-96K

USB

8k – 48K,

ECU (RX)

“14.8k”

All rates support

16bit, >93dB

All rates support

16bit, >93dB

All rates support

16bit, >93dB, but the

OTA 12bit path will limit

SNR to 72dB

Actual bandwidth is

dependent on the lower

of the input or output

rates.

Output BW vs OTA

“11k” = 5kHz

“14.8k” = 6.5kHz

“22k” = 10kHz

“29.6k” = 13kHz

“44k” = 20kHz

Actual bandwidth is

dependent on the lower

of the input or output

rates.

Output BW vs OTA

“11k” = 5kHz

“14.8k” = 6.5kHz

“22k” = 10kHz

“29.6k” = 13kHz

“44k” = 20kHz

Actual bandwidth is

dependent on the lower

of the input or output

rates.

Output BW vs OTA

“11k” = 5kHz

“14.8k” = 6.5kHz

“22k” = 10kHz

“29.6k” = 13kHz

“44k” = 20kHz

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 9 CONFIDENTIAL

Page 10

SWA51 Module Datasheet Rev 1.1

3.9 I

2

S Communication Interface Timing

Table 2: SWA51 I2S Timing

MIN TYP MAX UNIT NOTES

VL low voltage level -0.3V 0.0V 0.4V V

VH high voltage level 2.4V 3.3V 3.6V V

T clock period 325.5n s 1/3.072MHz

TLo clock low period 0.4T 0.6T

THi clock high period 0.4T 0.6T

TR rise time 50n s Note 1

TF fall time 50n s Note 1

TSu setup time 25n s

THd hold time 25n s

TOd output delay -25n 25n s

bit clocks/word clock 64

I2S protocol is “I2S Justified” as shown below.

Note 1: The timing specified for the rise and fall times represents the edge rates on the module itself. The rise

and fall times of the I2S signals are determined by ESD/EMI mitigat ion components on the modules, as well

as external loading, and will be higher than the specifie d num be rs

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 10 CONFIDENTIAL

Page 11

SWA51 Module Datasheet

Rev 1.1

I2C Master/Slave Communication Interface Timing (S_SCL, S_SDA)

3.10

The SWA51 has both I2C slave and master interfaces available with their respective pins S_SCL, S_SDA and

M_SCL, M_SDA. The interfaces operate in I2C fast-mode and can receive and transmit at up to 400 kbit/s.

Bytes are 8 bits long and are transferred with the most significant bit (MSB) first. Each byte has to be followed

by an acknowledge bit. The SWA51 will apply clock-stopping (by holding the clock lin e S_SCL LOW to force

the master into a wait state) if necessary due to internal high-priority tasks.

The slave/master interface can be used both for writing (e.g. sending commands) or reading (e.g. requesting

status). An additional GPIO pin on the SWA51 (Ex. GPIO24), can be used to notify the I2C master when a

pending message is ready to be sent.

The SWA51 slave interface responds to the 7-bit slave address 1000000 (0x40) as shown in Figure 1 below.

Figure 5: First Byte after the START Procedure

ELECTRICAL SPECIFICATIONS AND TIMING

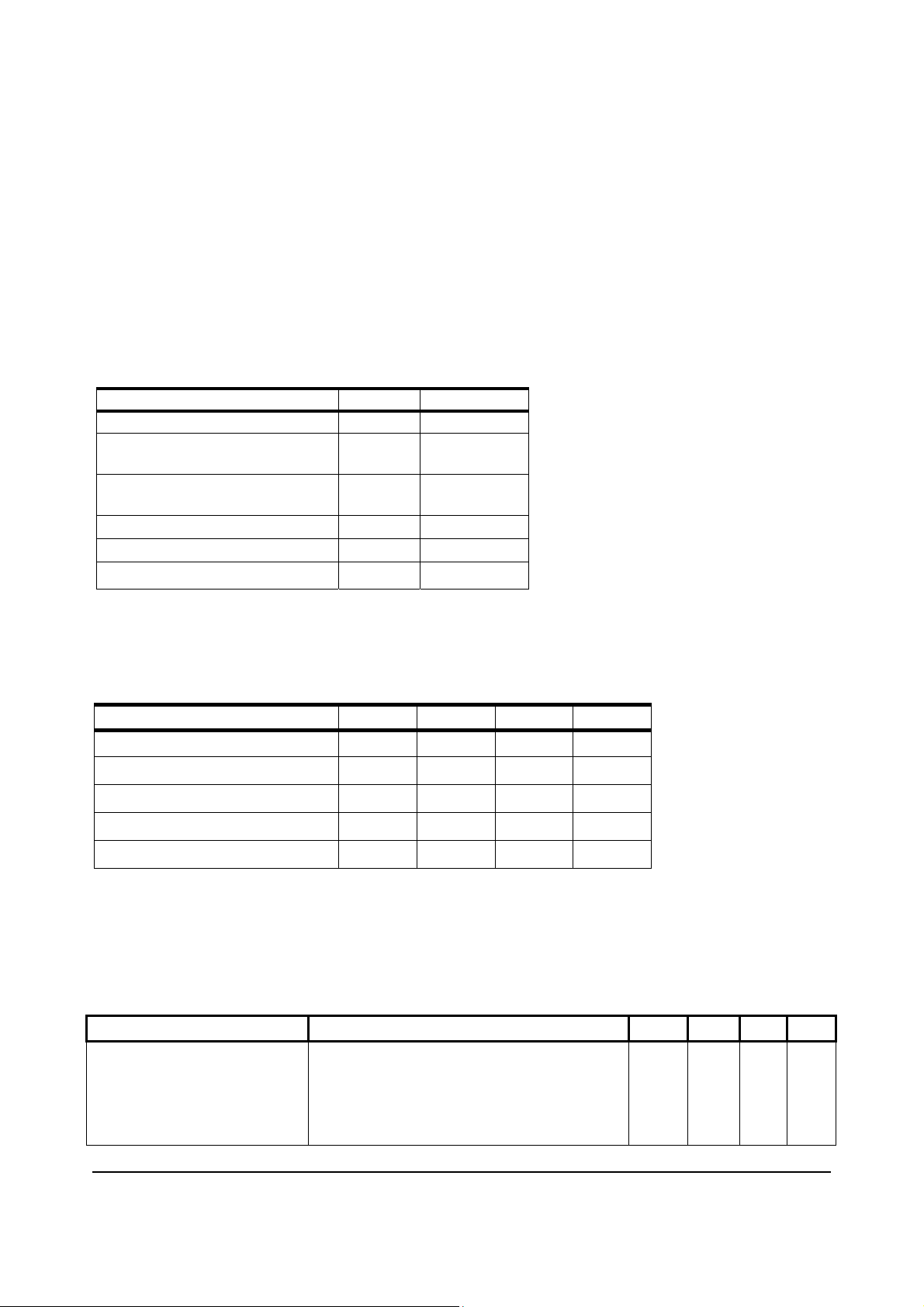

Table 3: Characteristics of the S_SDA and S_SCL I/Os

PARAMETER SYMBOL

LOW level input voltage

HIGH level input voltage V

LOW level output voltage (open drain or

open collector) at 1 mA sink current:

Output fall time from V

a bus capacitance from 10 pF to 400 pF

Pulse width of spikes which must be

suppress ed by the input filter

S_SCL clock frequency

LOW period of the S_SCL clock

HIGH period of the S_SCL clock

Data hold time t

Data set-up time

IHmin

to V

ILmax

with

V

IL

IH

V

OL

t

of

t

SP

0 50 ns

f

SCL

t

LOW

t

HIGH

HD;DAT

t

SU;DAT

FAST-MODE

MIN. MAX.

0.3

2.0

0.8

3.6

UNIT

V

V

0 0.4 V

0

0

1.3

0.6

100

100

250 ns

400

–

–

–

kHz

s

s

ns

– ns

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE

11

CONFIDENTIAL

Page 12

SWA51 Module Datasheet

Figure 6: Definition of Timing for F/S-Mode Devices on the I

2

C-Bus

Rev 1.1

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE

12

CONFIDENTIAL

Page 13

SWA51 Module Datasheet Rev 1.1

Ordering Information

Table 4: SWA51 Module Ordering Information

Module Part

Number

Option

Code

Description

SWA51 TX Digital Input , FPC Connector, integrated printed PCB

antennas

SWA51 RX Digital Output, FPC Connector, integrated printed PCB

antennas

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 13 CONFIDENTIAL

Page 14

SWA51 Module Datasheet Rev 1.1

FCC Statement:

Federal Communication Commission Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to

Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful

interference in a residential installation. This equipment generates, uses and can radiate radio frequency

energy and, if not installed and u sed in accordance with the instructions, may cause harmful interference to

radio communications. However, there is no guarantee that interference will not occur in a particular

installation. If this equipment does cause harmful interference to radio or television reception, which can be

determined by turning the equipment off and on, the user is encouraged to try to correct the interference by

one of the following measures:

● Reorient or relocate the receiving antenna.

● Increase the separation between the equipment and receiver.

● Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

● Consult the dealer or an experienced radio/TV technician for help.

FCC Caution: Any changes or modifications not expressly approved by the party responsible for

compliance could void the user’s authority to operate this equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1)

This device may not cause harmful interference, and (2) this device must accept any interference received,

including interference that may cause undesired operation.

This device and its antenna(s) must not be co-located with any other transmitters except in

accordance with FCC multi-transmitter product procedures.

Refering to the multi-transmitter policy, multiple-transmitter(s) and module(s) can be operated

simultaneously without C2P.

This device is restricted for indoor use

IMPORTANT NOTE:

FCC Radiation Exposure Statement:

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This

equipment should be installed and operated with minimum distance 20 cm between the radiator & your body.

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 14 CONFIDENTIAL

Page 15

SWA51 Module Datasheet Rev 1.1

IMPORTANT NOTE:

This module is intended for OEM integrator. The OEM integrator is responsible for the compliance to all the

rules that apply to the product into which this certified RF module is integrated.

Additional testing and certification may be necessary when multiple modules are used.

20 cm minimum distance has to be able to be maintained between the antenna and the users for the host this

module is integrated into. Under such configuration, the FCC radiation exposure limits set forth for an

population/uncontrolled environment can be satisfied.

Any changes or modifications not expressly approved by the manufacturer could void the user's authority to

operate this equipment.

USERS MANUAL OF THE END PRODUCT:

In the users manual of the end product, the end user has to be informed to keep at least 20 cm separation

with the antenna while this end product is installed and operated. The end user has to be informed that the

FCC radio-frequency exposure guidelines for an uncontrolled environment can be satisfied. The end user has

to also be informed that any changes or modifications not expressly approved by the manufacturer could void

the user's authority to operate this equip m ent. If the size of the end product is smaller than 8x10cm, then

additional FCC part 15.19 statement is required to be available in the users manual: This device complies with

Part 15 of FCC rules. Operation is subject to the following two conditions: (1) this device may not cause

harmful interference and (2) this device must accept any interference received, including interference that

may cause undesired operation.

LABEL OF THE END PRODUCT:

The final end product must be labeled in a visible area with the following " Contains TX FCC ID: NKR-SWA51

". This device complies with Part 15 of FCC rules. Operation is subject to the following two conditions: (1) this

device may not cause harmful interference and (2) this device must accept any interference received,

including interference that may cause undesired operation.

Responsible Party:

Contact name : Ted Su

Company : W-NeWeb Corporation

Address: 1525 McCarthy Blvd, Suite 206, Milpitas, CA 95035, U.S.A.

Tel: +1-408-457-6823

Fax: +1-408-457-6789

E-mail : Ted.Su@wnc.com.tw

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 15 CONFIDENTIAL

Page 16

SWA51 Module Datasheet Rev 1.1

IC Statement:

The device for operation in the band 5150–5250 MHz is only for indoor use to reduce the potential for harmful

interference to co-channel mobile satellite systems.

les dispositifs fonctionnant dans la bande 5150-5250 MHz sont réservés uniquement pour une

utilisation à l’intérieur afin de réduire les risques de brouillage préjudiciable aux systèmes de

satellites mobiles utilisant les mêmes canaux.

For indoor use only.

Pour une utilisation en intérieur uniquement.

This device complies with Industry Canada license-exempt RSS standard(s). Operation is subject to the

following two conditions: (1) this device may not cause interference, and (2) this device must accept any

interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio

exempts de licence. L'exploitation est autorisée aux deux conditions suivantes : (1) l'appareil ne doit

pas produire de brouillage, et (2) l'utilisateur de l'appareil doit accepter tout brouillage

radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

This device and its antenna(s) must not be co-located with any other transmitters except in

accordance with IC multi-transmitter product procedures.

Refering to the multi-transmitter policy, multiple-transmitter(s) and module(s) can be operated

simultaneously without reassessment permissive change.

Cet appareil et son antenne (s) ne doit pas être co-localisés ou fonctionnement en association avec une autre

antenne ou transmetteur.

IMPORTANT NOTE:

IC Radiation Exposure Statement:

This equipment complies with IC RSS-102 radiation exposure limits set forth for an uncontrolled environment.

This equipment should be installed and operated with minimum distance 20 cm between the radiator & your

body.

Cet équipement est conforme aux limites d'exposition aux rayonnements IC établies pour un

environnement non contrôlé. Cet équipement doit être installé et utilisé avec un minimum de 20cm

de distance entre la source de rayonnement et votre corps.

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 16 CONFIDENTIAL

Page 17

SWA51 Module Datasheet Rev 1.1

IMPORTANT NOTE:

This module is intended for OEM integrator. The OEM integrator is responsible for the compliance to all the

rules that apply to the product into which this certified RF module is integrated.

Additional testing and certification may be necessary when multiple modules are used.

20 cm minimum distance has to be able to be maintained between the antenna and the users for the host this

module is integrated into. Under such configuration, the IC RSS-102 radiation exposure limits set forth for an

population/uncontrolled environment can be satisfied.

Any changes or modifications not expressly approved by the manufacturer could void the user's authority to

operate this equipment.

USERS MANUAL OF THE END PRODUCT:

In the users manual of the end product, the end user has to be informed to keep at least 20 cm separation

with the antenna while this end product is installed and operated. The end user has to be informed that the IC

radio-frequency exposure guidelines for an uncontrolled environment can be satisfied. The end user has to

also be informed that any changes or modifications not expressly approved by the manufacturer could void

the user's authority to operate this equip m ent. Operation is subject to the following two conditions: (1) this

device may not cause harmful interference and (2) this device must accept any interference received,

including interference that may cause undesired operation.

LABEL OF THE END PRODUCT:

The final end product must be labeled in a visible area with the following " Contains IC: 4441A-SWA51 ".

The Host Model Number (HMN) must be indicated at any location on the exterior of the end product or

product packaging or product literature which shall be available with the end product or online.

Table for Filed Antenna

Ant Brand Model name Antenna Type Connector Band Gain(dBi)

0 WNC SWA51 Printed Antenna N/A B1 4.10

0 WNC SWA51 Printed Antenna N/A B4 3.39

1 WNC SWA51 Printed Antenna N/A B1 2.17

1 WNC SWA51 Printed Antenna N/A B4 3.50

CONTENTS SUBJECT TO CHANGE WITHOUT NOTICE 17 CONFIDENTIAL

Loading...

Loading...