Page 1

5

D D

4

3

2

1

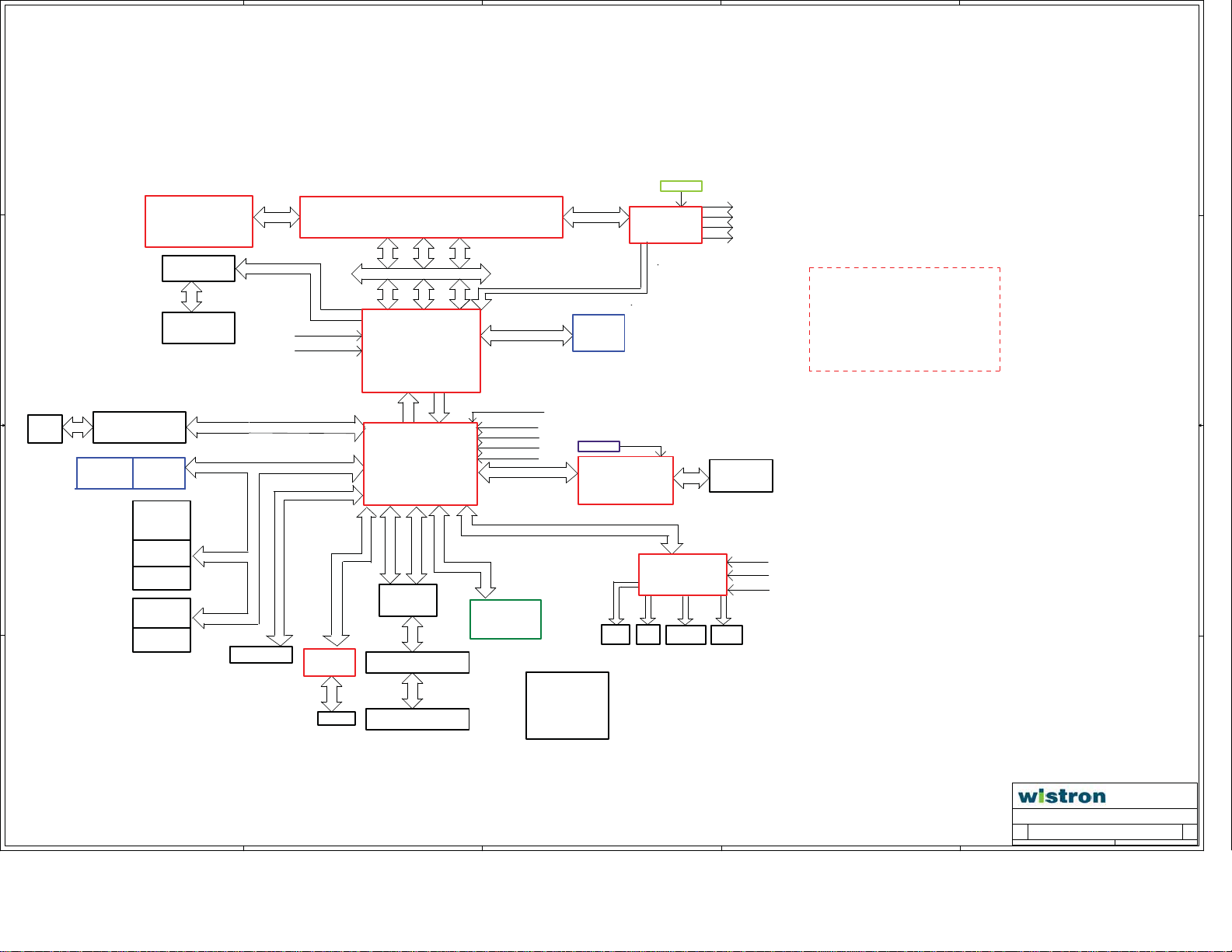

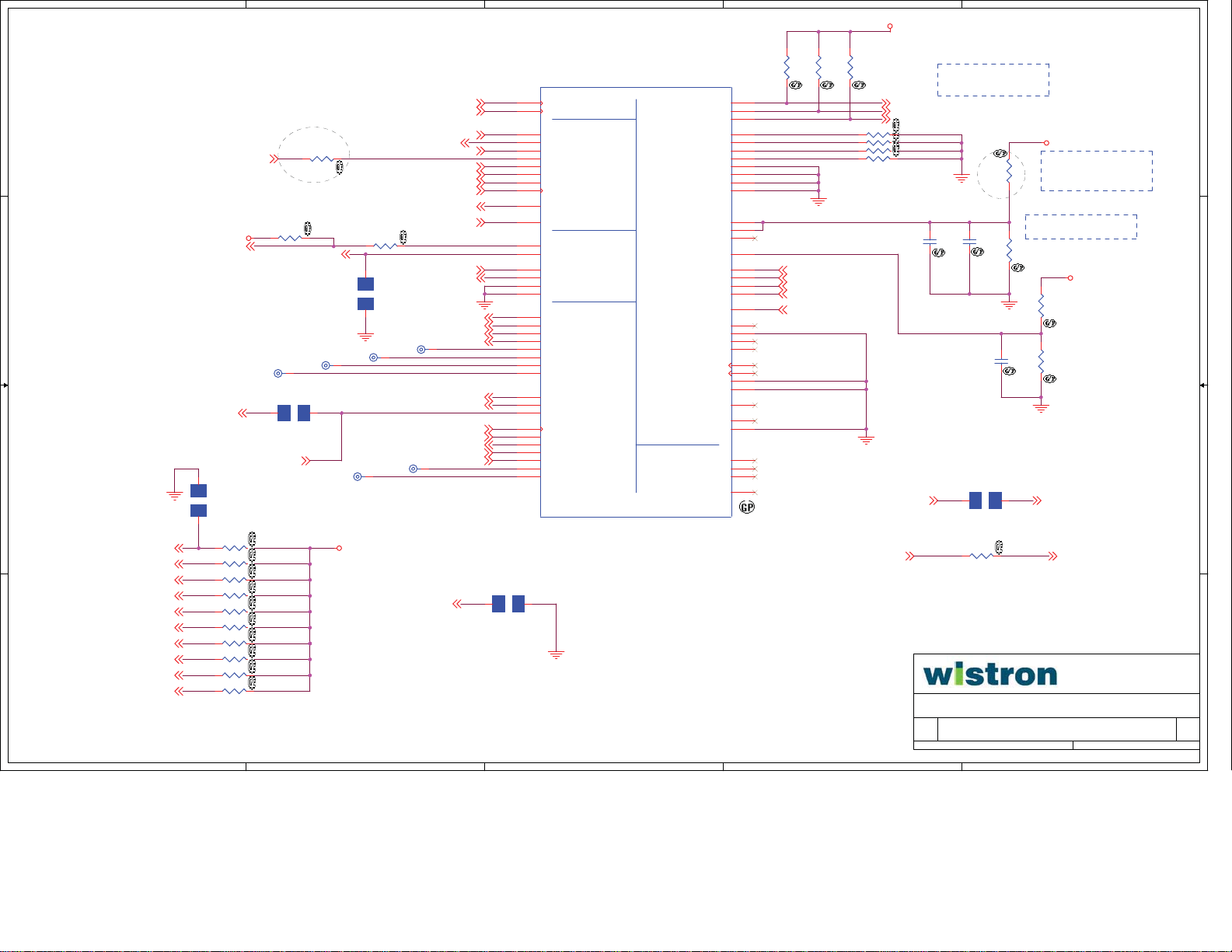

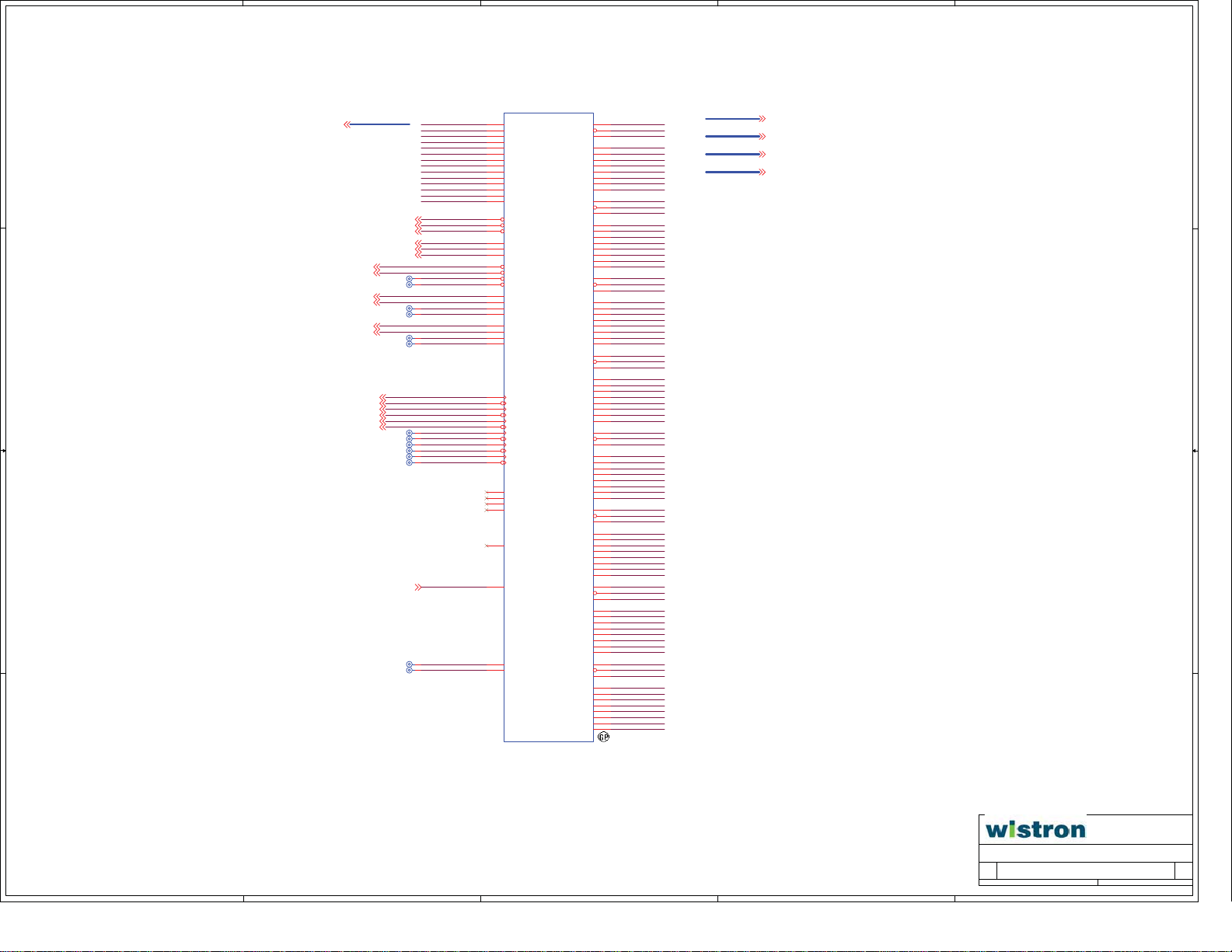

ATOM 230 +945GC + ICH7R

VRM 11.X

Intersil 6312

DEBUG BD

CONNECTOR

C C

NAND

Flash

B B

A A

Flash Controller

SM321

Front I/O Board

Front USB(SB

Port7)

VGA output

Keyboard/Mouse

COM Port

Front USB(SB

Port6)

REAR

LAN

Port-RJ45

connector

USB(SB Port 0)

USB(SB Port 1)

REAR

USB(SB Port 2)

USB(SB Port 3)

R,G,B

USB 2.0

PCI-E X4 SLOT

100MHz/100MHz#

DOT/DOT#

96MHz/96MHz#

(USB SB Port 4)

USB 2.0

PCI-E X4

88SE6111

E-SATA CN

BALL GRID ARRAY (BGA)

ATOM230

SOLDER DOWN PROCESSOR

CTRL

ADDR

ADDR

DATA

DATA

CTRL

Intel

LAKE PORT 945GC

GRAPHICS MEMORY

CONTROLLER HUB

DMI

DMI

100MHz/100MHz#

Intel

ICH7R

BP BD

HD*4

SPI

Control

Serial BIOS

Flash (SPI)

PCI-E

SATA X 4

SATA

Connector*4

Block Diagram

Channel A

DDR2

533/667

48MHz

33MHz

14.318MHz

32.768KHz

PCI-E

LPC Bus

Front IO Board

USB ConnectorX2

Power Indicator LED X1

System Health LED X1

Link Status LED X1

Reset Button Switch

X1

DIMM 0

25MHz

LAN

88E8071

Clock CK-410

SYSTEM

FAN

14.318MHz

100MHz/100MHz#

96MHz/96MHz#

Super

I/O

SMSC SCH5127

SYSTEM

Tmperature

FAN

Monitor

48MHz

33MHz

14.318MHz

REAR

LAN Port-RJ45

connector

33MHz

14.318MHz

32.768KHz

Voltage

Monitor

PAGE INDEX

Sheet 1

Sheet 2

Sheet 3

Sheet 4

Sheet 5

Sheet 7

Sheet 8

Sheet 9

Sheet 10

Sheet 11

Sheet 12

Sheet 13

Sheet 14

Sheet 15

Sheet 16

Sheet 17

Sheet 18

Sheet 19

Sheet 20

Sheet 21

Sheet 22

Sheet 23

Sheet 24

Sheet 25

BlOCK DIAGRAM & PAGE INDEX

REVISION HISTORY

POWER DISTRIBUTION

CLOCK DISTRIBUTION

PCB STACK_UP

RESET & PWRGD MAP

GPIO & IRQ & SMBUS SETTING

CPU 1 OF 3

CPU 2 OF 3

CPU 3 OF 3

CPU DECOUPLING CAPS

MCH PCIE/FSB/DMI 1 OF 6

MCH DDR2 A 2 OF 6

MCH DDR2 B 3 OF 6

MCH MISC 4 OF 6

MCH POWER 5 OF 6

MCH POWER 6 OF 6

MCH 2P5_DAC & PLL FILTERS

MCH DECOUPLING & COM P

MCH &DIMM VREF & COMP

MCH DCPL & VGA TERMINATION

240P CONN DDR2 CH A

DDR VTT TERMINATION

DDR VTT DECOUPLING

CK_410

Sheet 26

Sheet 27

Sheet 28

Sheet 29

Sheet 30

Sheet 31Sheet 6

Sheet 32

Sheet 33

Sheet 34

Sheet 35

Sheet 36

Sheet 37

Sheet 38

ICH7 SECTIONS 1&2 OF 6

ICH7 SECTION 3 OF 6

ICH7 SECTION 4 OF 6

ICH7 POWER 5&6 OF 6

MISC DECOUPLING

ICH PULL UP

SPI FLASH

SATA CONNECTOR

PCI TERMINATION

LAN 88E8071

USB CONN

E-SATA CONTROLLE R

SUPER I/O SMSC5127

FLASH CONTROLLER SMI321Sheet 39

Sheet 40

Sheet 41

Sheet 42

Sheet 43

Sheet 44

Sheet 45

Sheet 46

Sheet 47

PCIE & OTHER CONNECTOR

DEBUG BD CONNECTOR

FRONT IO BD CONNECTOR

ITP-XDP

POWER VCCP VREG CONTROLLER

POWER V_1P5_SFR & BATTERY

POWER DECOUPLING & STITCHING

POWER V_SM

Sheet 48 POWER 1P5 1P05 3P3_STB

Sheet 49 POWER VTT 5VDUAL 2P5_MCH

Sheet 50 GLUC LOGIC

<Variant Name>

Title

BlOCK DIAGRAM & PAGE INDEX

Size Document Number Rev

S15

A2

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

150Friday, December 12, 2008

-1

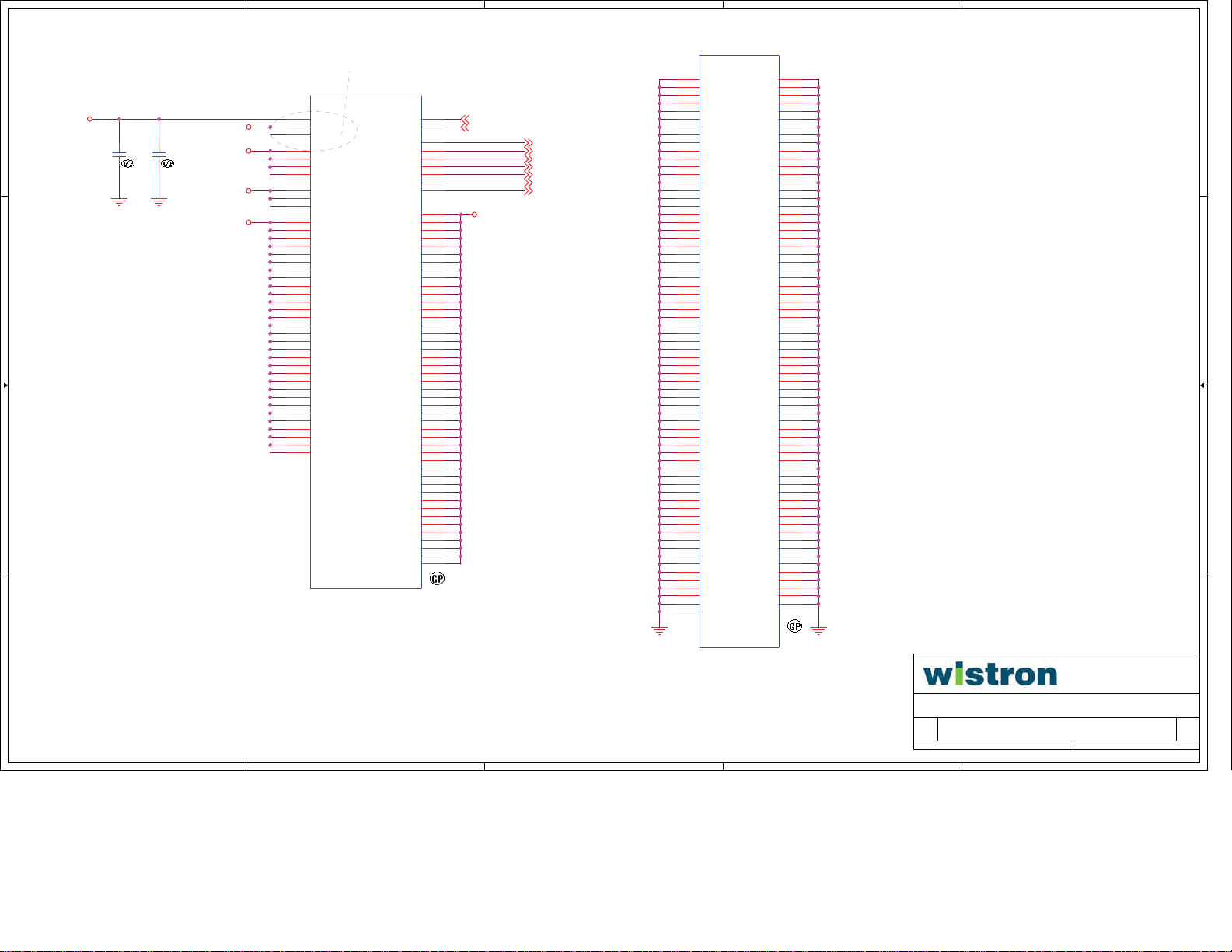

Page 2

5

Rev. History

4

3

2

1

RevDATE Description

0725 SA Add C493~C509 for EMI solution

0729 SA

D D

0730 SA

C C

0731

B B

0804

A A

0806 SA

0808 SA

R152,R154~R160 change to Dummy on page 27

R8 change to 0 ohm on page 9

R10 change to 1.2K ohm on page 9

R52,R54 change to Dummy on page 19

change R69,R70,R71 to 150 Ohm on page 21

change R69,R70,R71 to 150 Ohm on page 21

change R340,R342,R344 to 150 Ohm on page 41

change R340,R342,R344 to 150 Ohm on page 41

R129 to 33 ohm on page 25

R129 to 33 ohm on page 25

delete Net CK410_VDDPCI,and change to VDD_SRC_CLKA on page 25

delete Net CK410_VDDPCI,and change to VDD_SRC_CLKA on page 25

change R146 to DUMMY on page25

change R146 to DUMMY on page25

delete TP48,TP49 and add R610,R611 on page 26

delete TP48,TP49 and add R610,R611 on page 26

ADD R612,R613 on page 28

ADD R612,R613 on page 28

Change R392 value from 35.7k to 11k

Add C8 to reduce noise on current sense amplifier

Add R405(11.3KR)

Add C345 (1000PF)

Change R407 from 2.1K to 10KR

Change C343 from 15nF to 820PF

Change C341 from 180P to 100P

Change R385 from 10k to 16.9kR

Add R422 for power source filter

Delete R592 and R579

Change R575 from 2.1K to 3KR

Add C379, C387 (10uF) for V_SM

Add C389 and C390 (10uF) for V_1 P5 _C O R E

Change R593 from 10KR to 12KR

Change C477 from 4700pF to 10nF

Change R596 from 18KR to 24KR

Change R580 from 10KR to 15KR

Change C468 form 4700pF to 10nF

Change C583 from 18KR to 22KR

Change R391 to 470R

Delete TP122 and add R614, JP3 on page28

change R600 pin2 from net ICH_VRMPWRGD_PU to ICH_THRM_PU_N on page 38

SA

R194,R195,R196 mount 8.2K on page 32

R529 change from 560K to 15K on page 35

R526 change from 560K to 15K on page 36

R347 change from 560K to 15K on page 36

Delete TP119 and TP120, chagne net TP119 and TP 120 to ICH_GPIO38 and ICH_GPIO39 and pull high to VCC3 on

page28

delete R170 change to 10K on page 28

delete R287

delete C184

R176 change to Dummy,for VRM's power good already pull high

change C439 & R475 power source from VCC to V_5P0_STBY\G on page 50

Add D4 for Intel Recommend

R492,R495, C444change to Dummy

Add R617 and connector to ICH_VRMPWRGD_PU

TC3,TC4,TC5-SE560U2D5VM-GP EOL change to SE560U2D5VM-1-GP ON PAGE44

SA

change USBP8+,USBP8- to ICH7 port 7,change USB_FRONT1 and USB_FRONT2 to ICH port 4,5 ON PAGE26

delete net USB_OC4#_PULL_UP,USB_OC5#_PULL_UP,USB_OC_FRONT_67, CHANGE TO

USB_OC6#_PULL_UP,USB_OC7#_PULL_UP,USB_OC_FRONT_12 ON PAGE26

IND-1UH-64-GP change to IND-1UH-41-GP-U ON PAGE 48

U25 AT24C08AN-1-GP EOL change to AT24C08BN-SH-T-GP ON PAGE35

Add R226 Dummy, and connector to ICH_GPIO12 ON PAGE 28

R604 change to Dummy on page 38

Add R618 pull high to V_3P3_STBY\G on page38

Add C510 on page38

Change the U14 power source from V_SM to VCC3 on page 45

Change JR1 library,add L6,R623~R626

F6 ,F7 FUSE-1D5A6V-7GP EOL change to 69.50007.961

SA0811

change the SMI321 write protect from ICH_GPIO14 to ICH_GPIO6,because of power plane issue

Add R627

Add stitching caps C515,C516,C517,C518

change net RESET_BUTTON from SIO GP54 to ICH_GPIO10,Add SIO GP54 to TP138

Delete R551(pull high to VCC3)

SA0812

Add C519

5

V_SM

V_1P5_CORE

4

DATE Rev Description

0812 SA

0813 SA

0814

1002 1A Change V_SM controller source to 5VDUAL (P.47)

1014

1212

3

Delete net SDVO_CTRL_DATA,SDVO_CTRL_CLK,R325,R326

U47 change from AO4422-1-GP(N-MOS) to P2003EVG-GP(P-MOS),delete Q31,R608,delete net

VUSB_PU2

Add R628

Q29 OPEN for Intel recommend

SA

Q33 OPEN for Intel recommend

Q8 OPEN

Correct on Board flash USB interface

Add L7 to connect 1.2V power to E-SATA IC (P.37)

Correct U8 to CN10 trace name for Marvell 88SE6111

Add R232 R255 Dummy resistor to disconnect HDD Power control by SIO

Correct Front panel LAN LED control by LAN Active Pin (P.35)

Add C9 to reserve HDD Power control sequency function (P.40)

Correct LAN LED GIGA/100M connection

Change RAID LED and Backup LED to GPIO 27, 28

Add EMI Cap (C12) for 1D8V_LAN power (P.35)

Add EMI Cap (C10, C11) for CPU 12V power source (P.44)

Add EMI Cap (C13) for CK_PE_100M_PCIE_SLOT (P.25)

1B Remove U47, C492, C491, R609, R607, C490 Q32 and connect V_5_USB to 5VDUAL to

solve USB Vbus drop issue

Re-layout CN22 Pin 13 and Pin 15 for connect 5VDUAL to Front Board

change R391 to 820R to set current limit to 8A

Remove U6 R233 C214 to connect front LAN LED to LED_LAN_ACT directly no BOM change

1B

at -1A (20081023)

For wake up issue, remove R521 and put R521 to R522

Add C14 and R233 for separate LAN connector GND from System GND

-1B Add net 1_KBDAT,1_KBCLK pull high 10K,for reserved @PAGE41

1B

Delete C14 and R233 for EMI

1

Delete net 0

Add TC21 for reserved

2

<Variant Name>

Title

REVISION HISTORY

Size Document Number Rev

S15

A2

Date: Sheet of

1

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

250Friday, December 12, 2008

-1

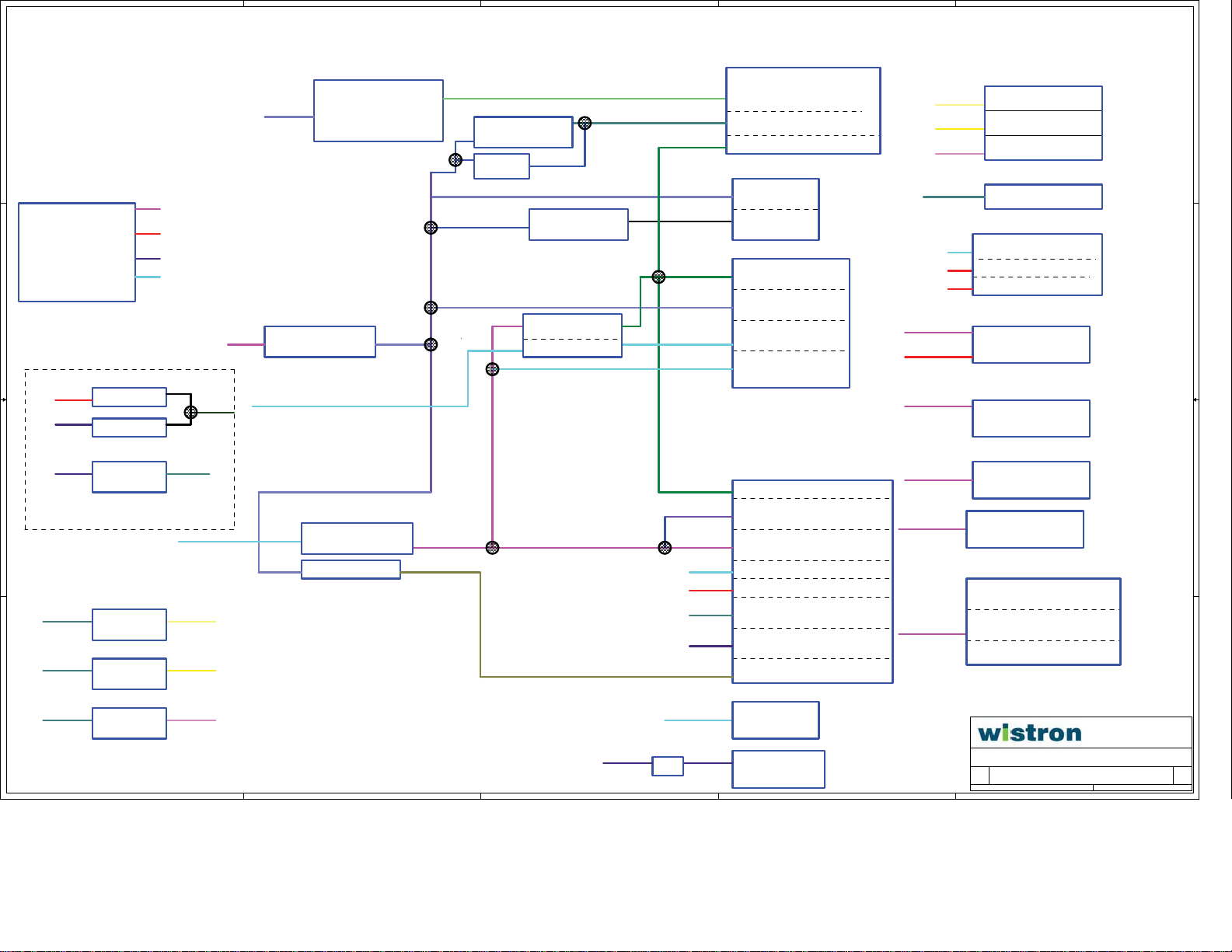

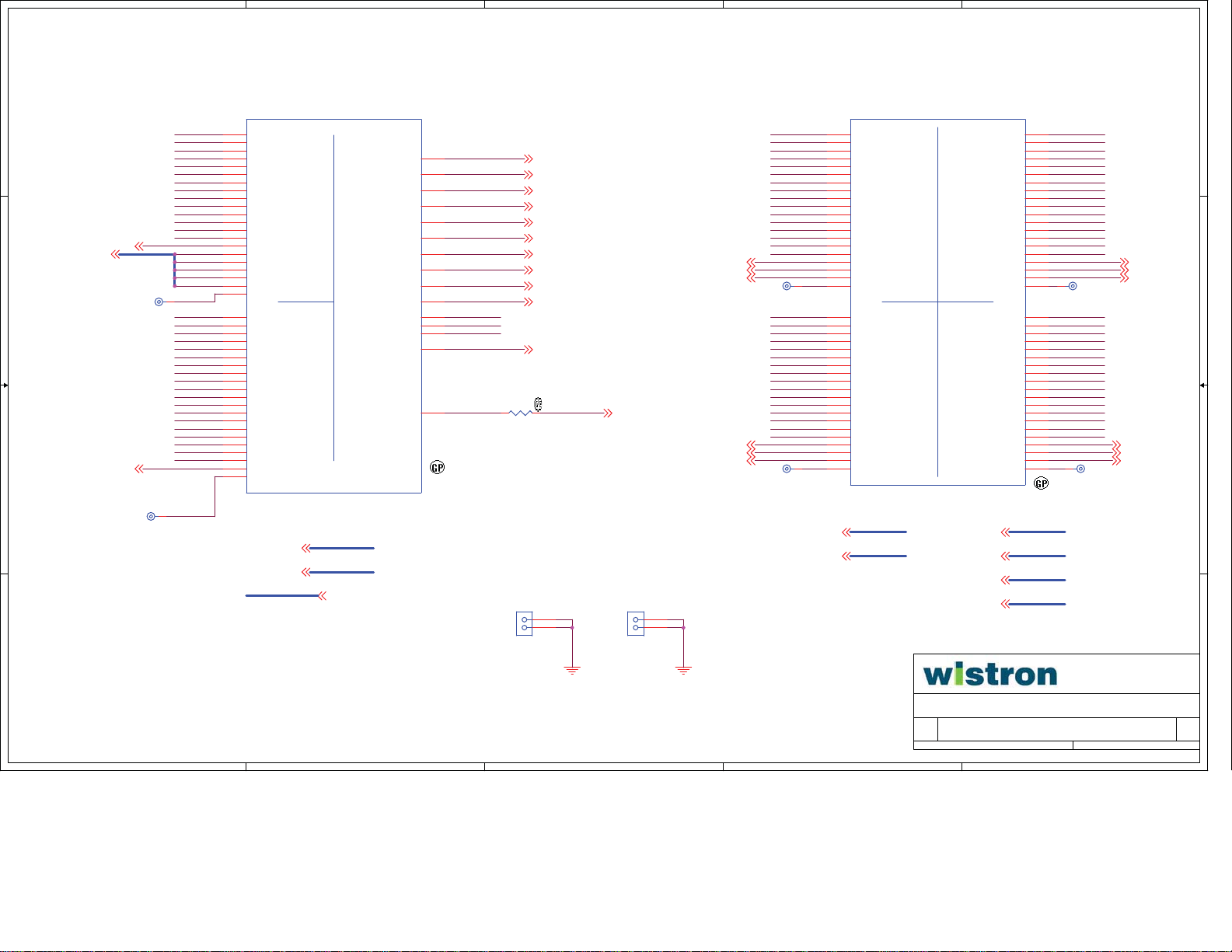

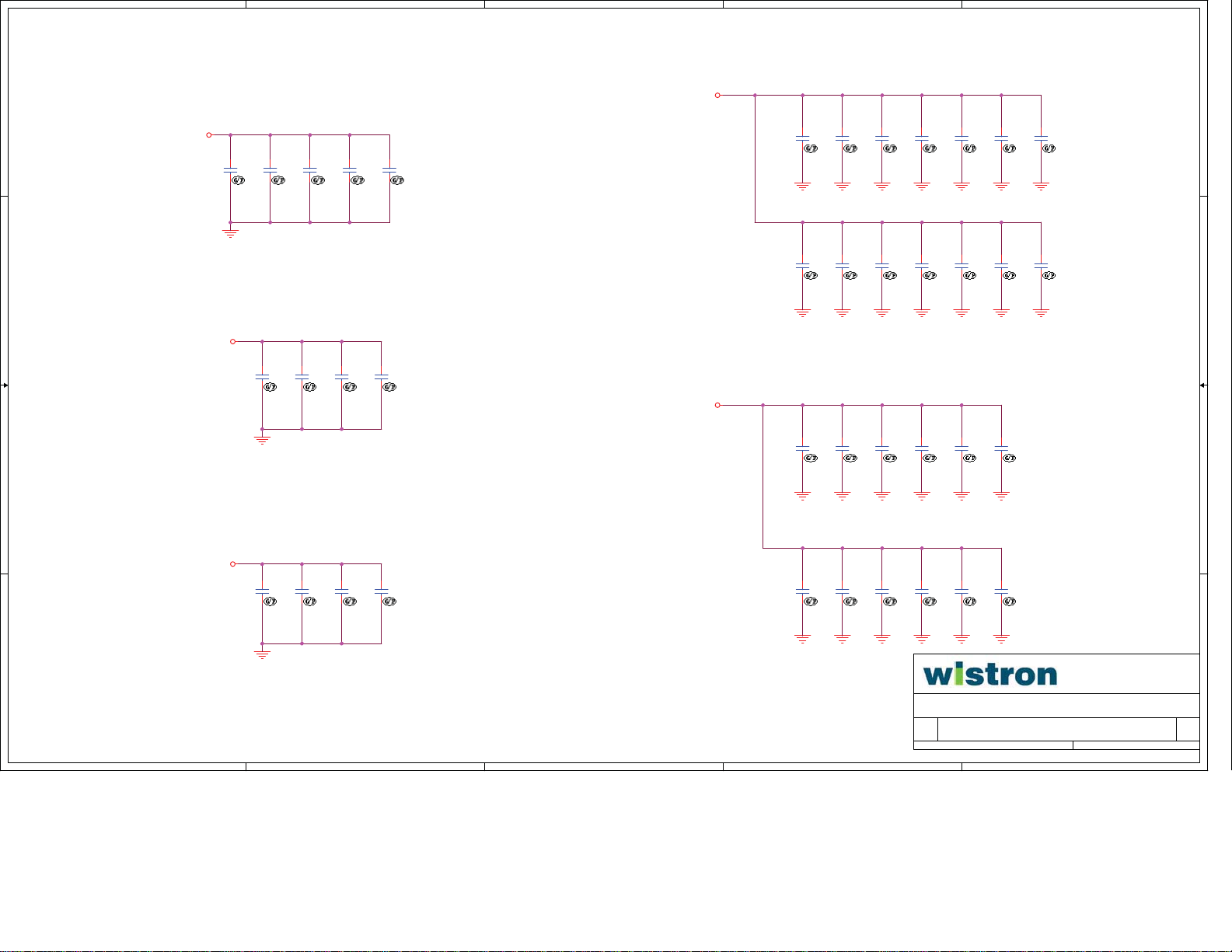

Page 3

5

4

3

2

1

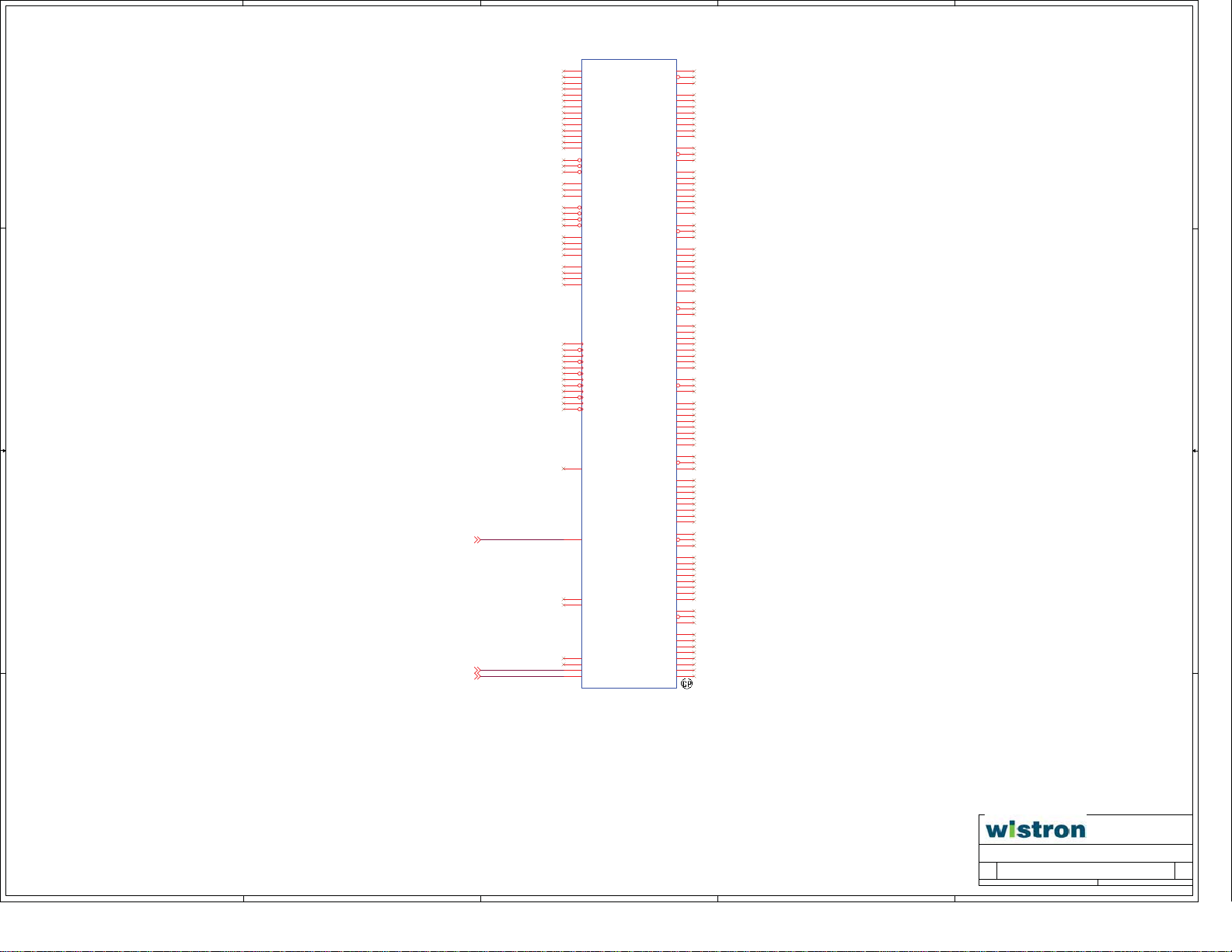

ATOM 230

VRM 11.X ON

D D

+12V

FDS6298-GP

VCC

V_5P0_STBY\G

VCC3

U42

Q59

V_3P3_STBY/G

5VDUAL

5VDUAL

ATX

POWER SUPPLY

C C

STBY/DUAL POWER

VCC

V_5P0_STBY\G

V_5P0_STBY\G

P2003EVG-GP

PMOS

V_12

ACPI Regulator

&Controller /

Switching

ISL6341

VCC3

BOARD/ISL6314

1.8V

V_SM

PWM

VCORE

APL1085

Linear

0 Ohm

(reserved)

V_1P5_CORE

1.5V

RT9199

Linear

V_SM 0.9V

LM358(Amplifer)(1/2)

Linear

LM358(Amplifer)(2/2)

LD1117DT

B B

ACPI Regulator

&Controller /

Switching

ISL6341

V_SM V_ICH_CORE

LM358(Amplifer)(2/2)

V_3P3_STBY/G

V_3P3_STBY/G

A A

V_3P3_STBY/G

LC

Filter

LAN

INTERNAL

Regulator

LAN

INTERNAL

Regulator

3D3V_LAN

1D8V_LAN

1D2V_LAN

1.5V

V_1P5_CORE

1.2V

V_5SB_DUAL

4A

0.13A

2.5A

V_5P0_STBY\G

V_1P5_SFR

V_FSB_VTT

V_FSB_VTT

V_2P5_MCH

V_1P5_CORE

V_FSB_VTT

V_1P5_CORE

V_1P5_COREVCC3

VCC3

V_3P3_STBY/G

V_ICH_CORE

V_3P3_STBY/G

V_5_USB

U47

5

4

3

Core:

0.65~1.2V

VCORE

Icc_max: 4A

S0, S1

VCCA : 1.5V +/- 0.075V

0.13A S0,S1

FSBVTT : 1.1V +/- 0.05V

2.5A S0,S1

DDR2

DIMM Channel 0

Core:1.8V+/-0.1V

V_SM

3A,S0,S1

400mA S3

V_SM_VTT

VTT:0.9V+/-0.2V

0.6A,S0,S1

420mA,S3(Vtt Up)

LAKE PORT 945GC

FSBVTT Host Termination

1.2V +/-0.06

0.9A(max) S0,S1

DDR2:1.8V +/- 0.1V

V_SM

4.1A(max) S0,S1

mA S3

DAC: 2.5V +/- 0.125V

0.1A

Core: 1.5V +/- 0.075V

15.5A S0, S1

ICH7R

FSBVTT 1.2V +/- 0.05V

14mA S0,S1

Internal Logic and I/O Buffer

1.5V +/- 0.075V

1.78A(max) S0,S1

PLL

1.5V +/- 0.075V

0.11A S0, S1

VCC3_3 3.3V +/- 0.165V

330mA(max) S0,S1

VCC

5VRef: 5.0V +/- 0.25V

6mA S0,S1

VCCSUS_3.3

3.3V +/- 0.165V

52mA S0,S1,S3,S5

VCCSUS_5

5.0V +/- 0.25V

10mA S0,S1,S3,S5

ICH7 Core(1.05V):

1.05V +/- 0.052V

0.86A S0, S1

CK-410

Clock Core&I/O:

3.3V+/-0.165V

500mA S0,S1

USB*4

USB and PS/2 cable

5V+/-0.25V

2A S0,S1

3D3V_LAN

1D8V_LAN

1D2V_LAN

V_3P3_STBY/G

VCC3

V_3P3_STBY/G

V_3P0_BAT_VREG

V_12

VCC

V_12

VCC

VCC3

VCC3

2

LAN 88E8071

VDD(3.3)

80mA

VDD(1.8)

150mA

VDD(1.2)

290mA

SPI

SPI Core:3.3V+/-0.3V

67mA S0,S1

SIO

LPC Super I/O

SMSC5127:3.3V

60mA(need ask vender)

60mA(need ask vender)

HDx4

12V

2*4=8A S0,S1

5V

2*4=8A S0,S1

SYSTEM FAN

12V

1.2A

LED

5V

100mA

SMI321

3.3V

400mA

E-SATA

1.5V

0.065A S0,S1

3.3V

0.205A S0,S1

1.2V

0.17A

<Variant Name>

Title

POWER DISTRIBUTION

Size Document Number Rev

S15

Custom

Date: Sheet

1

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

350Friday, December 12, 2008

of

-1

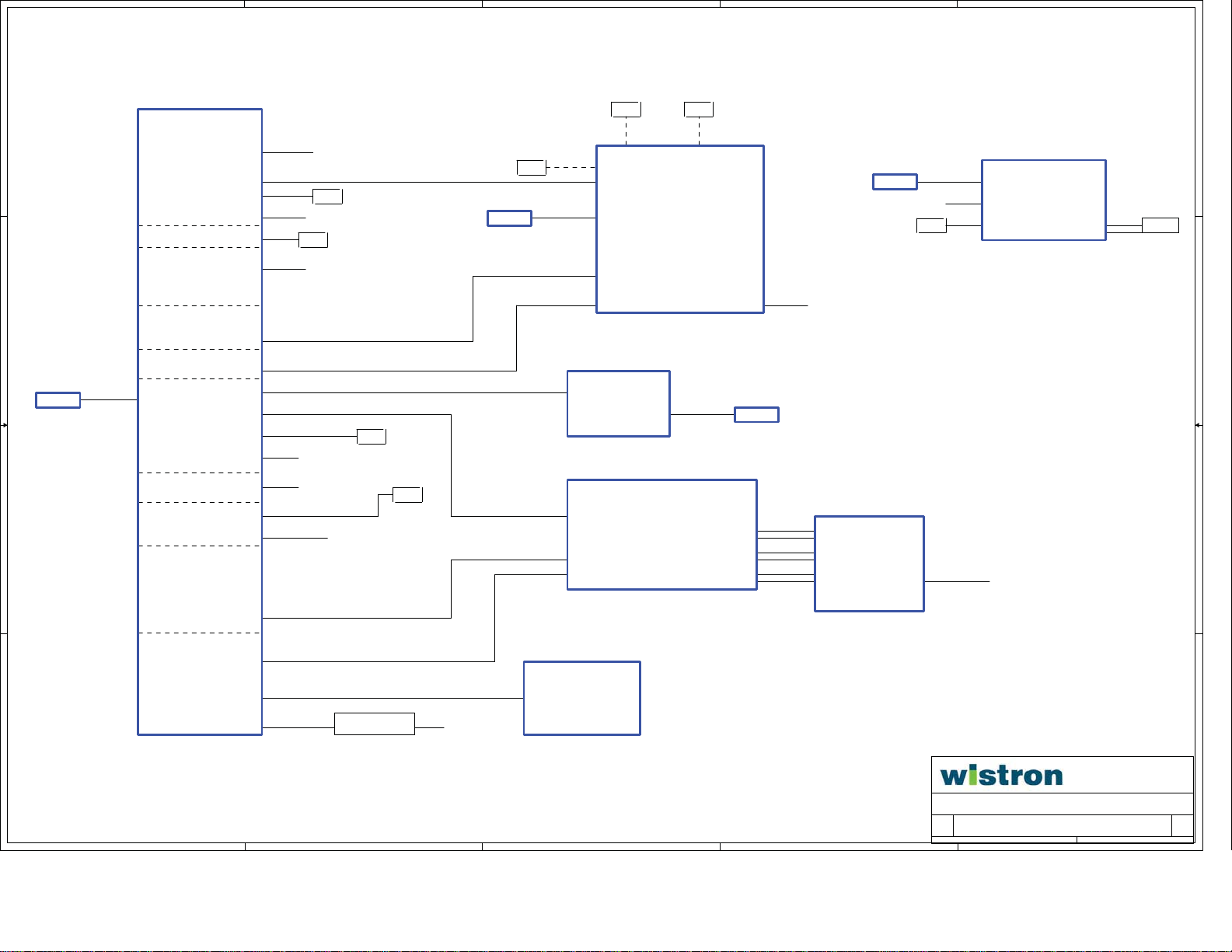

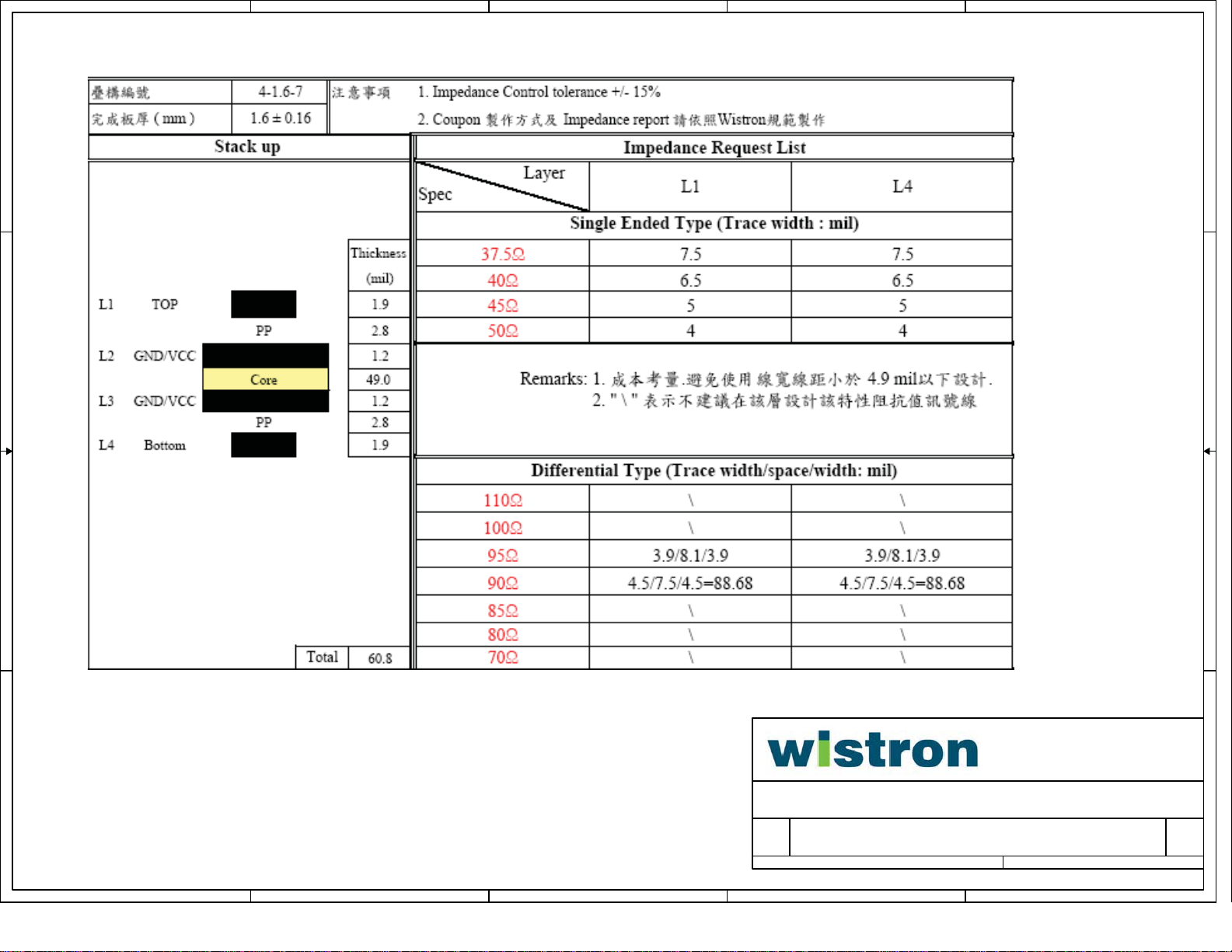

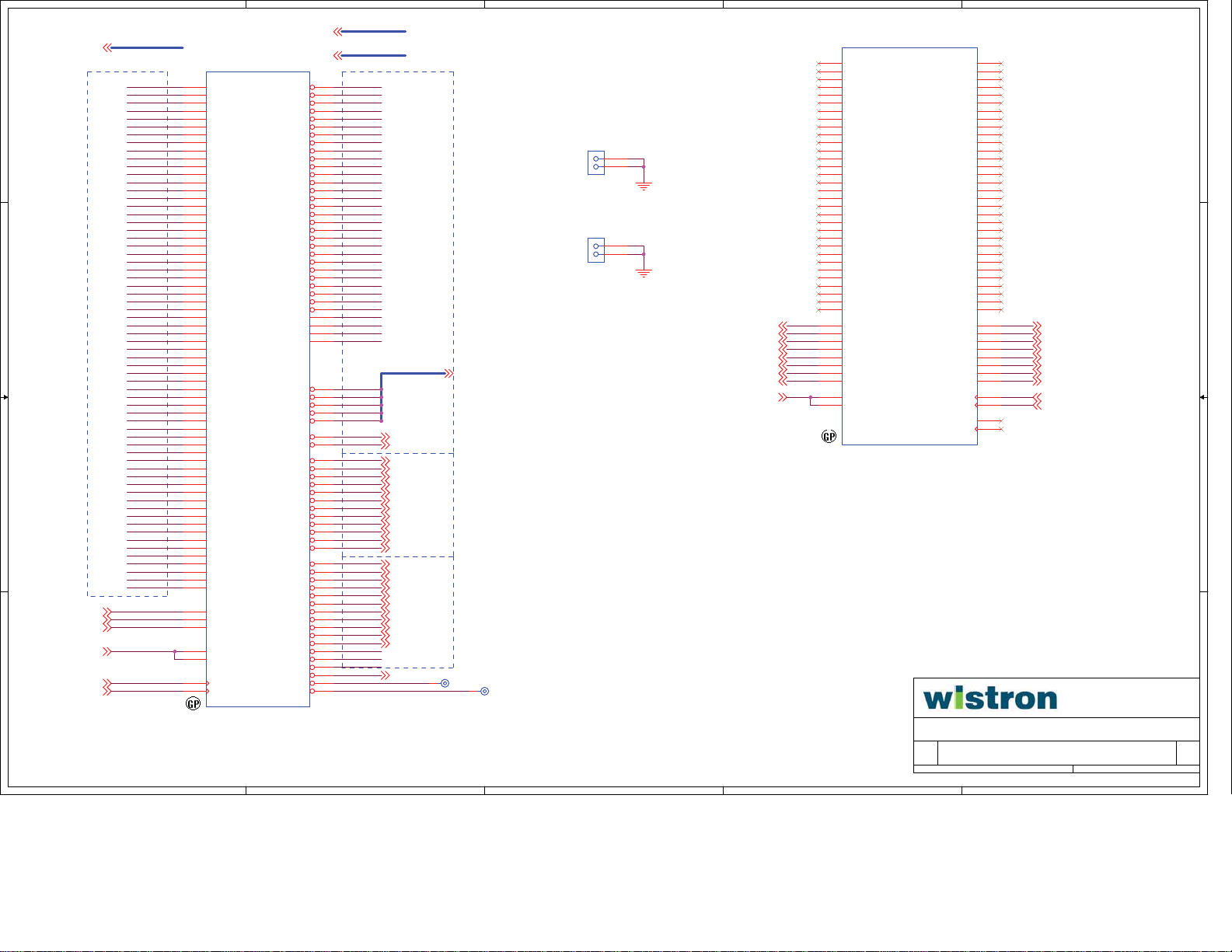

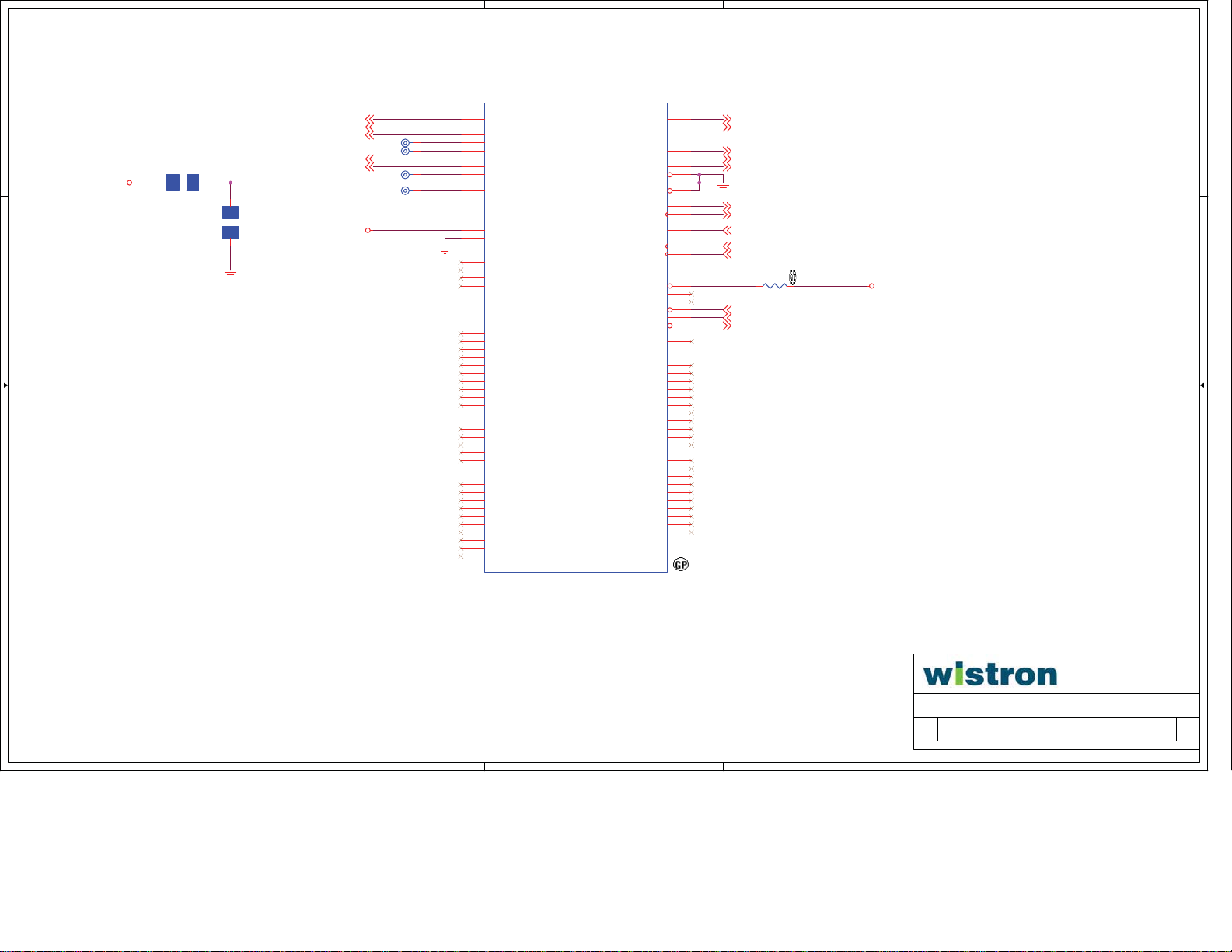

Page 4

5

http://hobi-elektronika.net/

4

3

2

1

D D

C C

Crystal

B B

14.318MHZ

3.3 VOLT

PCI CLOCK

24/48M SEL CLOCK

LAN CLOCK

USB CLOCK

SATA CLOCK PAIR

PEIE CLOCK PAIRS

SMBUS CLOCK

REF CLOCK

33MHZ

33MHZ

33MHZ

33MHZ

48MHZ

25MHZ

25MHZ

48MHZ

100MHZ

100MHZ

100MHZ

100MHZ

100MHZ

SCLK

14.318MHZ

14.318MHZ

SPARE

SIO

SPARE

SPARE

SIO

SPARE

ICH

ICH

Crystal

LAN

32.768KHZ

CK 410

CLK

14.318KHZ

LANCLK

PCICLK

RTCCLK

USBCLK

SATACLK

88E8071

PCIEREF

VOSCI

ICH7R

XTAL

GMCH

CLK

100MHZ

PCLK100

AC_BIT_CLK

25MHZ

Crystal

533MHz

Crystal

SPARE

DDR2 DIMM0

14.318MHZ

SCLK

CLK

33MHZ

SIO

SMSC5127

SCL

PCICLK

KBCLK

MCLK

MS/KB

ZCLK

DOT_96M

HOST

SCL

SCLK

96MHZ DREF

133MHZ CPU_CK

HOST CLOCK

PAIRS

133MHZ Z_CK0

CPU

XDP PORT

A A

5

SCL

4

SCLK

<Variant Name>

Title

CLOCK DISTRIBUTION

Size Document Number Rev

S15

A3

3

2

Date: Sheet

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

450Friday, December 12, 2008

1

-1

of

Page 5

5

D D

C C

4

3

2

1

B B

<Variant Name>

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

A A

Title

Hsichih, Taipei

PCB STACK_UP

Size Document Number Rev

S15

Date: Sheet of

5

4

3

2

550Friday, December 12, 2008

1

-1

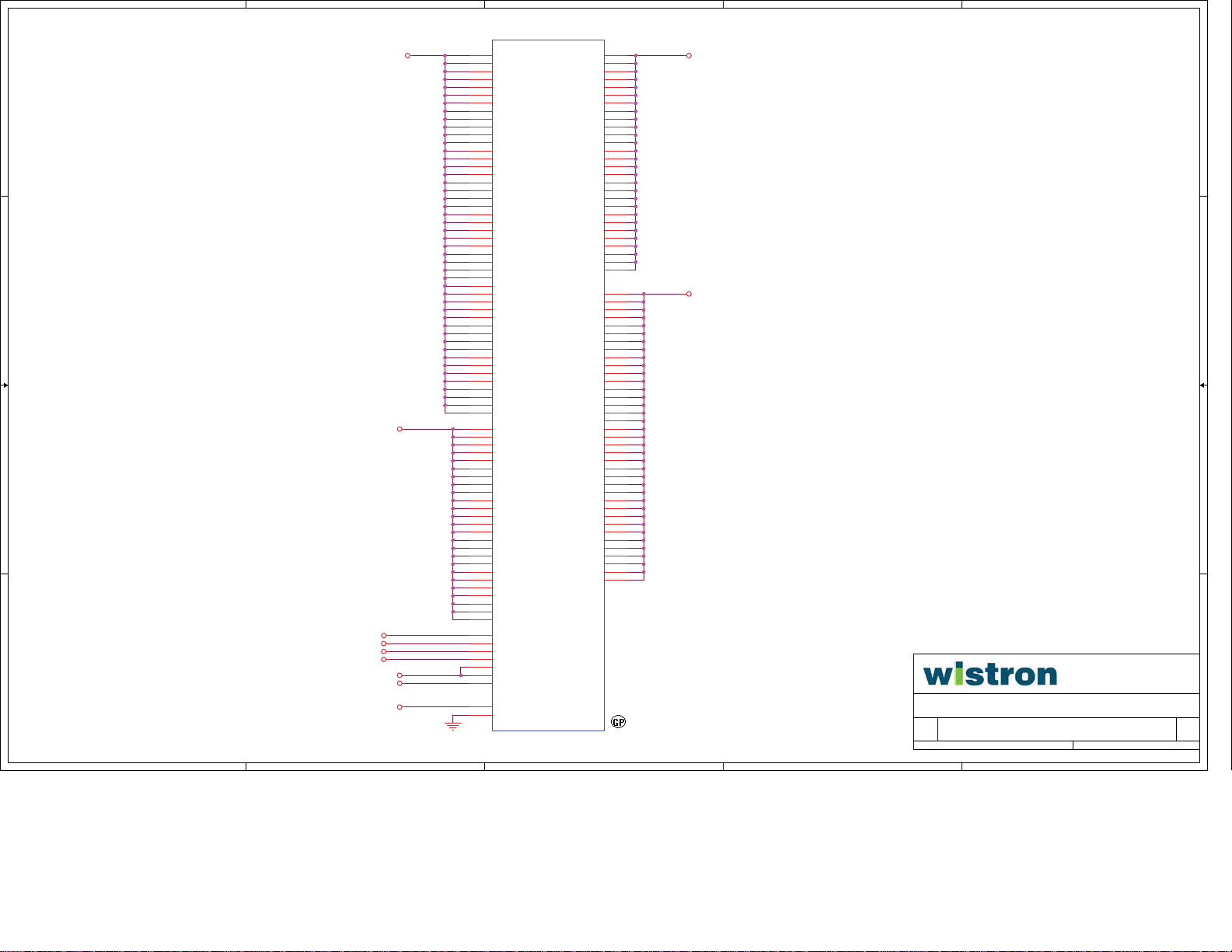

Page 6

5

http://hobi-elektronika.net/

4

3

2

1

V_FSB_VTT

PWRGOOD(V17)

D D

VRM

ISL6314

EN(17)

PG(1)

RESET_B(D15)

LAKEPORT

C C

HCPURST#(C30)

ATOM 230

PWROK(AJ9)

RSTIN#(AJ12)

DBR#(AC2)

ATX

PS_ON(16)

PWRGD_PS(8)

PWRGD_PS(84)

PS_ON#(92)

PWRGD_3V(84)

PCIRST~(25)

PB_OUT(99)

PB_IN(98)

POWER

BUTTON

PCIRST_OUT2(96)

PCIRST_OUT3(95)

SIO

SMSC5127

RSMRST~(100)

SLP_S3~(89)

SLP_S5~(88)

PCIEX4 SOLT

PERST#(A11)

PERST_N(53)

ESATA

CONTROLLER

B B

CMOS JUMP

A A

CPUPWRGD(AG24)

VRMPWRGD(AD22)

RCTRST#(AA3)

ACZ_RST#(R5)

ICH7R

RESET/POWER GOOD MAP

5

4

PWRBIN#(C23)

PWROK(AA4)

LAN_RST#(C19)

REMRST#(Y4)

SLP_S4#(D23)

SLP_S3#(B24)

3

Marvell LAN

PERSTn(5)PLTRST#(C26)

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Title

RESET & PWRGD MAP

Size Document Number Rev

S15

A3

2

Date: Sheet

<Variant Name>

Hsichih, Taipei

1

-1

of

650Friday, December 12, 2008

Page 7

5

4

3

2

1

ICH 7R

DURING

RESET

-----

-----

-----

-----

-----

-----

----- -----

-----

----- -----

IN

-----

-----

-----

IN

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

----- -----

----- -----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

Enable

Setting

DESCRIPTION

-----

-----

-----

-----

-----

-----

Write protect for onboard flash

-----

BACKUP DETECT

reserved function

-----

RESET_BUTTON

-----

System Management Interrupt from

Low

SIO

PME from SIO

Low

-----

Low

MODEL_SELECT JUMPER

-----

Boot BIOS Destination

-----

Selection (SPI)

-----

-----

SYS_STATUS LED to Front Panel

Low

-----

-----

-----

SYS_ERROR LED to Front Panel

Low

PWR_LED to Front Panel

Low

RAID_LED_CTRL to Front Panel

Low

-----

-----

Overcurrent Indicators

Overcurrent Indicators (NO UESD)

Overcurrent Indicators (NO UESD)

-----

-----

BACKUP_STATUS LED

RAID_LED_CTRL2 to Front Panel

-----

-----

-----

----- -----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

----------

Boot BIOS Destination

Selection (SPI)

NOTES

10K P/U TO VCC3 ON PAGE 28

8.2K P/U TO VCC3 ON PAGE 34

8.2K P/U TO VCC3 ON PAGE 34

8.2K P/U TO VCC3 ON PAGE 34

8.2K P/U TO VCC3 ON PAGE 34

10K P/U TO VCC3 ON PAGE 31

10K P/U TO VCC3 ON PAGE 31

10K P/U TO V_3P3_STBY\G ON PAGE 28

10K P/U TO V_3P3_STBY\G ON PAGE 28

10K P/U TO V_3P3_STBY\G ON PAGE 28RESET_BUTTON

10K P/U TO V_3P3_STBY\G ON PAGE 31

10K P/U TO V_3P3_STBY\G ON PAGE 28

10K P/U TO V_3P3_STBY\G ON PAGE 19

-----

10K P/D TO GND ON PAGE 26

PULL UP 4K7 TO VCC3 ON PAGE2 7

8.2K P/U TO VCC3 ON PAGE 34

connect to TP

USB OC protect ON PAGE26

8.2K P/U TO V_3P3_STBY\G ON PAGE 26

8.2K P/U TO V_3P3_STBY\G ON PAGE 26

connect to TP

connect to TP

PULL UP 4K7 TO VCC3 ON PAGE2 7

PULL UP 4K7 TO VCC3 ON PAGE2 7

PULL UP 10K TO VCC3 ON PAGE2 8

PULL UP 10K TO VCC3 ON PAGE2 8

10K P/U TO VCC3 ON PAGE 26

PIN NAME

GPIO0 MAIN GPI

GPIO1

GPIO2

GPIO3

D D

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO17

GPIO19

GPIO20 MAIN

C C

GPIO21

GPIO22

GPIO23 MAIN NO USED Native

GPIO24

GPIO25 RESUME

GPIO26

GPIO27 GPO

GPIO28

GPIO29

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

B B

GPIO38

GPIO39

GPIO40

GPIO41

GPIO42

GPIO43

GPIO44

GPIO45

GPIO46

GPIO47

GPIO48 MAIN

POWER

WELL

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAINGPIO18 connect to TPGPO

MAIN

MAIN

MAIN

RESUME SYS_ERROR

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

NA

NA

NA

NA

NA

NA

NA

NA

V_CPU_IOGPIO49

USAGE

NO_USED

NO_USED 8.2K P/U TO VCC3 ON PAGE 34

NO USED

NO USED

NO USED

NO USED

SMI321 Reset

NO USED

BACKUP_BUTTON

2 PIN JUMPER

SMB_ALERT_PU

SIO_SMI_N

PME_N

NO USED 10K P/U TO V_3P3_STBY\G ON PAGE 28

MODEL_SELECT

NO USED

Boot BIOS Destination

Selection (SPI)

NO_USED

NO_USED

SYS_STATUS GPO

NO_USED PULL UP 4K7 TO VCC3 ON PAGE2 7

NO_USED

PWR_LED

RAID_LED_CTRL

BACKUP_STATUS

RAID_LED_CTRL2

USB OC5USB OC6USB OC7NO_USED

NO_USED

NO_USED

NO USED

NO USED

NO USED

NO USED

Not implemented.

Not implemented.

Not implemented.

Not implemented.

Not implemented.

Not implemented.

Not implemented.

Not implemented.

Boot BIOS Destination

Selection (SPI)

H_PWRGD

(Multi-function)

Default

Type

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

Native

GPI

GPI

GPI

GPI

GPOMAINGPIO16

GPI

GPI

GPI

Native

GPO

GPO

GPO

GPO

Native

Native

Native

GPO

GPO

GPO

GPONO USED

GPI

GPI

GPI

GPI

NA

NA

NA

NA

NA

NA

NA

NA

Native

Native

PIN NAME

GP10

GP11 RESUME

GP15

GP16

GP17

GP20

GP22

GP37

GP40

GP41

GP50

GP51

GP52 HDD2_AMBER

GP53

GP54

GP55

GP56

GP57

GP60

GP10-GP17 are only an output and can not be configured as an input. GP60 and GP61

are OD output only.

SMSC5127

POWER

USAGE

WELL

MAIN OUT

RESUMEGP12 OUT

RESUMEGP13 ESATA_RST_N

RESUMEGP14

MAIN

RESUME

RESUME

MAIN

MAIN I/O

MAIN

MAIN

MAIN

MAIN

MAIN OUT

MAIN OUT

RESUME

RESUME

RESUME OUT

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUMEGP61

NO USED

HDD4_BLUE

PLTRST_SLOTS_N

HDD4_AMBER

NO USED

SIO_PROCHOT_N

FAN_CTL3

HWM_INT_N(reserve)

SIO_KDATGP21

SIO_KCLK

SIO_SMI_NGP27 OUT

SIO_MDATGP32

SIO_MCLKGP33

KBRST_NGP36

A20GATE

PWRGD_ICH_SIO

NO USED

SIO_PME_S3GP42

NO USED

HDD3_AMBER

HDD3_BLUE

HDD2_BLUE

NO USED

NO USED CONNECT TO TP

HDD1_AMBER

HDD1_BLUE

HDD3_PWR

HDD1_PWR

FLASH TYPE

GNT5#

GNT4#

1

0

1

1

Flash cycles routed to SPI

Flash cycles routed to PCI

0

1

Flash cycles routed to LPC

I/O Address : 0x02E

Enable

DURING

RESET

OUT

OUT

OUT

OUT

OUT Low

I/O

I/O

I/O

OUT

OUTGP43

I/O

I/O

I/O

I/O

I/O

Routing

DESCRIPTION NOTES

Setting

HDD4 ACT

Low

PCIE SLOT RESET

Low

ESATA_RST_N

HDD4 FAIL

Control VR THERMAL THROTTLE

High PUSH PULL

CIRCUITRY ON PAGE28

Low

Control of POWER V_LED

Control Thermal Alarm in

SB on Page19

Keyboard Data I/O

-----

Keyboard Clock I/O

-----

High

Mouse Data I/O

-----

Mouse Clock I/O

-----

Keyboard Reset

Low

Open-Drain Output

Control A20GATE IN ICH9

Low

reserved function

Low

----- -----

Power Management Event

High

Output.

Front Panel Reset

-----

HDD3 FAIL

-----

HDD3 ACT

HDD2 FAIL

-----

HDD2 ACT

-----

-----

HDD1 FAIL

-----

HDD1 ACT

-----

-----

-----

CONNECT TO TP

10K P/U TO V_3P3_STBY\G ON

PAGE 38

-----

10K PU on PAGE31

10K P/U TO 3P3_STBY\G ON PAGE 38

10K P/U TO VCC3 ON PAGE 38

10K P/U TO VCC3 ON PAGE 38

Reserved 1K P/U TO VCC3 ON

PAGE 28

10K P/U TO 3P3_STBY\G ON

PAGE 38

10K P/U TO 3P3_STBY\G ON PAGE 38

CONNECT TO TP

330R P/U TO VCC ON PAGE 40

330R P/U TO V_3SB ON PA GE 40

A A

<Variant Name>

Title

GPIO & IRQ & SMBUS SETTING

Size Document Number Rev

S15 -1

Custom

5

4

3

2

Date: Sheet

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

750Friday, December 12, 2008

1

of

Page 8

5

4

3

2

1

D D

H_A_N16

H_A_N15

H_A_N14

H_A_N13

H_A_N12

H_A_N11

H_A_N10

H_A_N9

H_A_N8

H_A_N7

H_A_N6

H_A_N5

H_A_N4

H_A_N3

TPAD28

H_ADSTB0_N

TP3

H_ADSTB1_N

H_REQ_N4

H_REQ_N3

H_REQ_N2

H_REQ_N1

H_REQ_N0

TP_AP_B2

1

H_A_N35

H_A_N34

H_A_N33

H_A_N32

H_A_N31

H_A_N30

H_A_N29

H_A_N28

H_A_N27

H_A_N26

H_A_N25

H_A_N24

H_A_N23

H_A_N22

H_A_N21

H_A_N20

H_A_N19

H_A_N18

H_A_N17

H_ADSTB0_N<12>

H_REQ_N[4..0]<12>

C C

H_ADSTB1_N<12>

B B

L21

K19

M20

L20

H21

M19

G20

N19

R20

N20

H20

P21

K20

R19

P20

G19

N21

D17

A14

B15

B14

A17

C16

B17

B16

C15

B18

D20

E20

C20

C18

C14

D19

A16

E21

F19

C19

B19

M18

J20

J19

J21

U1A

A_B16

A_B15

A_B14

A_B13

A_B12

A_B11

A_B10

A_B9

A_B8

A_B7

A_B6

A_B5

A_B4

A_B3

ADSTB_B0

REQ_B4

REQ_B3

REQ_B2

REQ_B1

REQ_B0

AP_B0

A_B35

A_B34

A_B33

A_B32

A_B31

A_B30

A_B29

A_B28

A_B27

A_B26

A_B25

A_B24

A_B23

A_B22

A_B21

A_B20

A_B19

A_B18

A_B17

ADSTB_B1

AP_B1

ADDR 0

ADDR 1

COMMON CLK

PAD-CPU437P-GP

TP_AP_B1

TP6

1

TPAD28

H_A_N[16..3]<12>

H_A_N[35..17]<12>

H_RS_N[2..0]

A A

5

H_A_N[16..3]

H_A_N[35..17]

H_RS_N[2..0] <12>

4

1 OF 5

ADS_B

BNR_B

BR0_B

BPRI_B

DBSY_B

DEFER_B

DRDY_B

HIT_B

HITM_B

LOCK_B

RS_B0

RS_B1

RS_B2

TRDY_B

RESET_B

H_ADS_N

V19

H_BNR_N

Y19

H_BREQ0_N

T20

H_BPRI_N

U21

H_DBSY_N

Y18

H_DEFER_N

T21

H_DRDY_N

T19

H_HIT_N

AA17

H_HITM_N

V20

H_LOCK_N

W20

H_RS_N0

W18

H_RS_N1

Y17

H_RS_N2

U20

H_TRDY_N

W19

H_CPURST_B_N H_CPURST_N

D15

R1

1 2

H_ADS_N <12>

H_BNR_N <12>

H_BREQ0_N <9,12>

H_BPRI_N <12>

H_DBSY_N <12>

H_DEFER_N <12>

H_DRDY_N <12>

H_HIT_N <12>

H_HITM_N <12>

H_LOCK_N <12>

H_TRDY_N <12>

0R2J-2-GP

CN1

1

2

FOX-CON2-3

H_CPURST_N <9,12,43>

CN2

1

2

FOX-CON2-3

3

H_D_N0

H_D_N1

H_D_N2

H_D_N3

H_D_N4

H_D_N5

H_D_N6

H_D_N7

H_D_N8

H_D_N9

H_D_N10

H_D_N11

H_D_N12

H_D_N13

H_D_N14

H_D_N15

H_DBI_N<0><12>

H_STBN_N<0><12>

H_STBP_N<0><12>

H_DBI_N<1><12>

H_STBN_N<1><12>

H_STBP_N<1><12>

H_DBI_N<0>

H_STBN_N<0>

H_STBP_N<0>

TP1

TPAD28

H_D_N16

H_D_N17

H_D_N18

H_D_N19

H_D_N20

H_D_N21

H_D_N22

H_D_N23

H_D_N24

H_D_N25

H_D_N26

H_D_N27

H_D_N28

H_D_N29

H_D_N30

H_D_N31

H_DBI_N<1>

H_STBN_N<1>

H_STBP_N<1>

TP4

TPAD28

Y11

D_B0

W10

D_B1

Y12

D_B2

AA14

D_B3

AA11

D_B4

W12

D_B5

AA16

D_B6

Y10

D_B7

Y9

D_B8

Y13

D_B9

W15

D_B10

AA13

D_B11

Y16

D_B12

W13

D_B13

AA9

D_B14

W9

D_B15

W16

DINV_B0

Y14

DSTBN_B0

Y15

AA5

AA6

AA8

W3

W7

W6

W2

W4

V9

Y8

U1

Y7

Y3

V3

U2

T3

V2

Y6

Y4

Y5

R4

DSTBP_B0

DP_B0

D_B16

D_B17

D_B18

D_B19

D_B20

D_B21

D_B22

D_B23

D_B24

D_B25

D_B26

D_B27

D_B28

D_B29

D_B30

D_B31

DINV_B1

DSTBN_B1

DSTBP_B1

DP_B1

1

1

DATA 2 DATA 3

DATA 0DATA 1

U1B

2 OF 5

D_B32

D_B33

D_B34

D_B35

D_B36

D_B37

D_B38

D_B39

D_B40

D_B41

D_B42

D_B43

D_B44

D_B45

D_B46

D_B47

DINV_B2

DSTBN_B2

DSTBP_B2

DP_B2

D_B48

D_B49

D_B50

D_B51

D_B52

D_B53

D_B54

D_B55

D_B56

D_B57

D_B58

D_B59

D_B60

D_B61

D_B62

D_B63

DINV_B3

DSTBN_B3

DSTBP_B3

DP_B3

R3

R2

P1

N1

M2

P2

J3

N3

G3

H2

N2

L2

M3

J2

H1

J1

L1

K2

K3

M4

C2

G2

F1

D3

B4

E1

A5

C3

A6

F2

C6

B6

B3

C4

C7

D2

C5

E2

F3

D4

H_D_N32

H_D_N33

H_D_N34

H_D_N35

H_D_N36

H_D_N37

H_D_N38

H_D_N39

H_D_N40

H_D_N41

H_D_N42

H_D_N43

H_D_N44

H_D_N45

H_D_N46

H_D_N47

H_DBI_N<2>

H_STBN_N<2>

H_STBP_N<2>

TP2

1

TPAD28

H_D_N48

H_D_N49

H_D_N50

H_D_N51

H_D_N52

H_D_N53

H_D_N54

H_D_N55

H_D_N56

H_D_N57

H_D_N58

H_D_N59

H_D_N60

H_D_N61

H_D_N62

H_D_N63

H_DBI_N<3>

H_STBN_N<3>

H_STBP_N<3>

1

TP5

TPAD28

H_DBI_N<2> <12>

H_STBN_N<2> <12>

H_STBP_N<2> <12>

H_DBI_N<3> <12>

H_STBN_N<3> <12>

H_STBP_N<3> <12>

PAD-CPU437P-GP

H_D_N[15..0]<12>

H_D_N[31..16]<12>

H_D_N[15..0]

H_D_N[31..16]

H_D_N[15..0]<12>

H_D_N[31..16]<12>

H_D_N[47..32]<12>

H_D_N[63..48]<12>

H_D_N[15..0]

H_D_N[31..16]

H_D_N[47..32]

H_D_N[63..48]

<Variant Name>

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Title

CPU 1 OF 3

Size Document Number Rev

S15

B

Date: Sheet

2

Hsichih, Taipei

850Friday, December 12, 2008

1

-1

of

Page 9

5

4

3

2

1

V_FSB_VTT

12

12

R2

U1C

H_INIT_N

V11

V12

U18

T16

V16

T15

R15

U17

R16

F16

V17

G17

H17

K17

H15

K18

V15

M17

N16

M16

L17

K16

M15

L16

J4

E4

E5

G4

F4

J18

J15

G6

H6

K4

K5

J16

BCLK0

BCLK1

A20M_B

FERR_B

IGNNE_B

INIT_B

LINT0

LINT1

SMI_B

STPCLK_B

IERR_B

PWRGOOD

PROCHOT_B

THERMTRIP_B

THRMDA

THRMDC

VSS

VSS

BPM_B0

BPM_B1

BPM_B2

BPM_B3

NC#G6

NC#H6

NC#K4

NC#K5

PRDY_B

PREQ_B

BR1_B

TCK

TDI

TDO

TMS

TRST_B

NC#M15

NC#L16

ASYNC

THERM

DEBUG

D D

SA-0729-R8 change to 0 ohm

H_SB_INIT_N<27>

R8 0R2J-2-GP

1 2

CK_H_CPU_DP<25>

CK_H_CPU_DN<25>

H_SB_A20M_N<27>

H_SB_FERR_N<27>

H_SB_IGNNE_N<27>

H_SB_INTR<27>

H_SB_NMI<27>

H_SB_SMI_N<27>

H_SB_STPCLK_N<27>

H_IERR_N

1

C3

TPAD28

1

TP11

TPAD28

TP7

R12

H_PWRGD<28,43>

H_TEMP_SRC_DP<38>

H_TEMP_RET_DN<38>

H_BPM4_PRDY_N<43>

H_BPM5_PREQ_N<43>

H_PROCHOT_B_N

H_BPM_N<0><43>

H_BPM_N<1><43>

H_BPM_N<2><43>

H_BPM_N<3><43>

1

H_TCK<43>

H_TDI<43>

H_TDO<43>

H_TMS<43>

H_TRST_N<43>

1

H_PROCHOT_N<38>

V_FSB_VTT

62R2J-GP

1 2

H_THERMTRIP_N

R11

22R2J-2-GP

1 2

12

C C

RESERVE FOR 1UF

TP10

TPAD28

1

TPAD28

R16 DUMMY-R2

FP_RST_N<28,31,43>

1 2

RESERVE FOR 0R

H_BR1_N

B B

12

R17

DUMMY-R2

RESERVE FOR 1KR

TP9

1

TP12

TPAD28

DUMMY-C2

TPAD28

TP8

3 OF 5

BSEL0

BSEL1

BSEL2

COMP0

COMP1

COMP2

COMP3

VSS

VSS

VSS

VSS

CMREF

GTLREF

NC#D6

EXTBGREF

SLP_B

DPRSTP_B

DPSLP_B

DPWR_B

FORCEPR_B

HFPLL

VSS

BINIT_B

MCERR_B

ACLKPH

DCLKPH

VSS

VSS

RSP_B

EDM

VSS

NC#A3

NC#C1

NC#C21

CORE_DET

J6

H5

G5

T1

T2

F20

F21

L5

N5

N4

P4

B7

A7

D6

M6

N18

R18

R17

U4

N15

N6

L15

T17

P17

U5

V5

P5

T5

T6

R6

A19

A3

C1

C21

A13

470R2J-2-GP

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_SB_CPUSLP_N <27>

H_DPRSTP_N

H_DPSLP_N

H_DPWR_N

H_FORCEPR

PAD-CPU437P-GP

H_DPWR_N

H_PWRGD<28,43>

H_BREQ0_N<8,12>

H_CPURST_N<8,12,43>

H_DPRSTP_N

H_SB_FERR_N<27>

H_DPSLP_N

A A

H_IERR_N

H_BR1_N

H_SB_THERMTRIP_N<27>

5

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R191KR2J-1-GP

R211KR2J-1-GP

V_FSB_VTT

R2251R2F-2-GP

R2351R2F-2-GP

R241KR2J-1-GP

H_PWRGD<28,43>

R251KR2J-1-GP

C5 DUMMY-C2

1 2

RESERVE FOR 1UF

R261KR2J-1-GP

R271KR2J-1-GP

R28150R2F-1-GP

R291KR2J-1-GP

4

3

12

R3

R4

470R2J-2-GP

470R2J-2-GP

R5 24D9R2F-L-GP

1 2

R6 49D9R2F-GP

1 2

R7 24D9R2F-L-GP

1 2

R9 49D9R2F-GP

1 2

H_GTLREF

H_EXTBGREF

H_PROCHOT_N<38> H_FORCEPR

2

COMP PIN MAX TRACE LENGTH

OF 500 MIL

H_FSBSEL0 <19,25>

H_FSBSEL1 <19,25>

H_FSBSEL2 <19,25>

SA-0729-R10 change to 1.2K

ohm

R10

V_FSB_VTT

GTLREF MAX TRACE LENGTH

OF 500 MIL AND 5 MIL

SPACING

1 2

1K2R2F-1-GP

PLACE NEAR GTLREF 'S PINS

12

C1

SC220P50V2JN-3GP

SC1U10V2KX-1GP

12

12

R13

C2

2KR2F-3-GP

12

C4

12

R14

1KR2J-1-GP

12

R15

2KR2F-3-GP

V_FSB_VTT

SC1U10V2KX-1GP

R18 DUMMY-R2

1 2

RESERVE FOR 0R

R20

1 2

H_SB_THERMTRIP_N <27>H_THERMTRIP_N

0R2J-2-GP

<Variant Name>

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Title

CPU 2 OF 3

Size Document Number Rev

S15

B

Date: Sheet

Hsichih, Taipei

950Friday, December 12, 2008

1

-1

of

Page 10

5

4

3

2

1

5 OF 5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

W14

W17

W21

W5

W8

Y1

A20

AA4

B21

E16

E8

F18

F7

H19

H4

K1

K7

L19

L4

L7

M1

P16

P19

P7

R1

T13

U16

U7

V14

V8

Y21

A2

AA3

B20

E15

E7

F17

F6

H18

H3

J9

K6

L18

L3

L6

L9

P15

P18

P6

P9

T12

U15

U6

V13

V7

Y20

AA20

B2

E6

F5

T11

V6

Y2

AA2

T10

AA19

AA18

CAPS FOR VCCP PLANE 11 *

(SC1U10V2KX-1GP) delete by JIM

20080714 for routing

CHECK PIN E14, DOES IT THE SAME WITH VTT ?

D D

V_1P5_SFR

12

12

C7

C6

SCD1U50V3KX-GP

SC10U6D3V3MX-GP

C C

B B

PLACE C6 CLOSE PIN D7

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

U1D

D7

VCCA

V10

VCCF

E14

VCCPC6_4

A9

VCCQ0_1

B9

VCCQ0_2

G14

VTT

H14

VTT

E13

VCCPC6_1

F14

VCCPC6_2

F13

VCCPC6_3

C9

VTT

D9

VTT

E9

VTT

G8

VTT

H8

VTT

J14

VTT

J8

VTT

K14

VTT

K8

VTT

L14

VTT

L8

VTT

M14

VTT

M8

VTT

N14

VTT

N8

VTT

P14

VTT

P8

VTT

R14

VTT

R8

VTT

T14

VTT

T8

VTT

F9

VTT

U14

VTT

U9

VTT

F8

VTT

U13

VTT

U8

VTT

U12

VTT

U11

VTT

U10

VTT

PAD-CPU437P-GP

4 OF 5

VCC_SENSE

VSS_SENSE

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

C13

VCC_SENSE_CPU_SKT <44>

D13

VSS_SENSE_CPU_SKT <44>

H_VID0

F15

H_VID1

D16

H_VID2

E18

H_VID3

G15

H_VID4

G16

H_VID5

E17

H_VID6

G18

A12

B12

C12

D12

E12

F12

G12

H12

J12

K12

L12

M12

N12

P12

R12

A11

B11

C11

D11

E11

F11

G11

H11

J11

K11

L11

M11

N11

P11

R11

A10

B10

C10

D10

E10

F10

G10

H10

J10

K10

L10

M10

N10

P10

R10

VCCP

H_VID0 <44>

H_VID1 <44>

H_VID2 <44>

H_VID3 <44>

H_VID4 <44>

H_VID5 <44>

H_VID6 <44>

A15

A18

AA10

AA12

AA15

AA7

B13

C17

D14

D18

D21

E19

G13

G21

H13

H16

J13

J17

K13

K15

K21

L13

M13

M21

N13

N17

P13

R13

R21

T18

U19

V18

V21

W11

U1E

VSS

VSS

A4

VSS

A8

VSS

VSS

VSS

VSS

VSS

B1

VSS

VSS

B5

VSS

B8

VSS

VSS

C8

VSS

D1

VSS

VSS

VSS

VSS

D5

VSS

D8

VSS

VSS

E3

VSS

G1

VSS

VSS

VSS

G7

VSS

G9

VSS

VSS

VSS

H7

VSS

H9

VSS

VSS

VSS

J5

VSS

J7

VSS

VSS

VSS

VSS

K9

VSS

VSS

VSS

VSS

M5

VSS

M7

VSS

M9

VSS

VSS

VSS

N7

VSS

N9

VSS

VSS

P3

VSS

VSS

VSS

R5

VSS

R7

VSS

R9

VSS

VSS

T4

VSS

T7

VSS

T9

VSS

VSS

U3

VSS

V1

VSS

VSS

VSS

V4

VSS

W1

VSS

VSS

A A

5

4

3

PAD-CPU437P-GP

2

<Variant Name>

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Title

CPU 3 OF 3

Size Document Number Rev

S15

B

Date: Sheet

Hsichih, Taipei

10 50Friday, December 12, 2008

1

of

-1

Page 11

5

4

3

2

1

BACKSIDE CAPS FOR V_FSB_VTT PLANE

D D

C C

TOP SIDE CAPS FOR V_FSB_VTT PLANE

V_FSB_VTT

12

C29

SC1U10V2KX-1GP

12

C30

SC1U10V2KX-1GP

12

C26

SC1U10V2KX-1GP

12

C27

SC1U10V2KX-1GP

12

C28

SC1U10V2KX-1GP

DECOUPLING FOR V_FSB_VTT

V_FSB_VTT

12

12

C38

C39

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

B B

12

C40

SC1U10V2KX-1GP

12

C41

V_FSB_VTT

VCCP

12

12

12

C22

12

C34

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C23

12

C35

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C19

12

C31

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C20

12

C32

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C21

12

C33

SC1U10V2KX-1GP

SC1U10V2KX-1GP

BACKSIDE CAPS FOR VCCP PLANE

12

12

C43

12

C44

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C42

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C45

12

C46

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C24

12

C36

12

C47

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C25

12

C37

DECOUPLING FOR VCCP

VCCP

A A

5

12

12

12

C48

C49

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C50

12

C51

SC1U10V2KX-1GP

4

3

12

12

C52

C53

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

2

12

12

12

C55

C54

SC1U10V2KX-1GP

SC1U10V2KX-1GP

<Variant Name>

Title

CPU DECOUPLING CAPS

Size Document Number Rev

S15

B

Date: Sheet

C56

12

C57

SC1U10V2KX-1GP

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

1

-1

of

11 50Friday, December 12, 2008

Page 12

5

H_D_N[63..0]<8>

D D

4X GTL+

C C

B B

HXSWING<19>

HXSCOMP<19>

HXRCOMP<19>

MCH_GTLREF0<19>

CK_H_MCH_DP<25>

CK_H_MCH_DN<25>

A A

H_D_N[63..0]

H_D_N0

H_D_N1

H_D_N2

H_D_N3

H_D_N4

H_D_N5

H_D_N6

H_D_N7

H_D_N8

H_D_N9

H_D_N10

H_D_N11

H_D_N12

H_D_N13

H_D_N14

H_D_N15

H_D_N16

H_D_N17

H_D_N18

H_D_N19

H_D_N20

H_D_N21

H_D_N22

H_D_N23

H_D_N24

H_D_N25

H_D_N26

H_D_N27

H_D_N28

H_D_N29

H_D_N30

H_D_N31

H_D_N32

H_D_N33

H_D_N34

H_D_N35

H_D_N36

H_D_N37

H_D_N38

H_D_N39

H_D_N40

H_D_N41

H_D_N42

H_D_N43

H_D_N44

H_D_N45

H_D_N46

H_D_N47

H_D_N48

H_D_N49

H_D_N50

H_D_N51

H_D_N52

H_D_N53

H_D_N54

H_D_N55

H_D_N56

H_D_N57

H_D_N58

H_D_N59

H_D_N60

H_D_N61

H_D_N62

H_D_N63

5

U2B

P41

HD0

M39

HD1

P42

HD2

M42

HD3

N41

HD4

M40

HD5

L40

HD6

M41

HD7

K42

HD8

G39

HD9

J41

HD10

G42

HD11

G40

HD12

G41

HD13

F40

HD14

F43

HD15

F37

HD16

E37

HD17

J35

HD18

D39

HD19

C41

HD20

B39

HD21

B40

HD22

H34

HD23

C37

HD24

J32

HD25

B35

HD26

J34

HD27

B34

HD28

F32

HD29

L32

HD30

J31

HD31

H31

HD32

M33

HD33

K31

HD34

M27

HD35

K29

HD36

F31

HD37

H29

HD38

F29

HD39

L27

HD40

M24

HD41

J26

HD42

K26

HD43

G26

HD44

H24

HD45

K24

HD46

F24

HD47

E31

HD48

A33

HD49

E40

HD50

D37

HD51

C39

HD52

D38

HD53

D33

HD54

C35

HD55

D34

HD56

C34

HD57

B31

HD58

C31

HD59

C32

HD60

D32

HD61

B30

HD62

D30

HD63

B27

HSWING

C27

HSCOMP

A28

HRCOMP

D27

HDVREF

D28

HACCVREF

M31

HCLKP

M29

HCLKN

LAKEPORT-1-GP

H_A_N[35..3]<8>

H_RS_N[2..0]<8>

2 OF 8

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

RESERVED#AA35

RESERVED#AA42

RESERVED#AA34

RESERVED#AA38

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HDSTBP#0

HDSTBN#0

HDINV#0

HDSTBP#1

HDSTBN#1

HDINV#1

HDSTBP#2

HDSTBN#2

HDINV#2

HDSTBP#3

HDSTBN#3

HDINV#3

HADS#

HTRDY#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HRS#0

HRS#1

HRS#2

HCPURST#

HPCREQ#

HEDRDY#

J39

K38

J42

K35

J37

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

AA37

V32

Y34

AA35

AA42

AA34

AA38

E41

D41

K36

G37

E42

M36

V35

K41

L43

K40

F35

G34

A38

J27

M26

E29

E34

B37

B32

W42

W40

V41

P40

W41

U41

U40

AA41

U39

D42

U42

T40

Y43

T43

C30

F38

Y40

4

H_A_N[35..3]

H_RS_N[2..0]

H_A_N3

H_A_N4

H_A_N5

H_A_N6

H_A_N7

H_A_N8

H_A_N9

H_A_N10

H_A_N11

H_A_N12

H_A_N13

H_A_N14

H_A_N15

H_A_N16

H_A_N17

H_A_N18

H_A_N19

H_A_N20

H_A_N21

H_A_N22

H_A_N23

H_A_N24

H_A_N25

H_A_N26

H_A_N27

H_A_N28

H_A_N29

H_A_N30

H_A_N31

H_A_N32

H_A_N33

H_A_N34

H_A_N35

H_REQ_N0

H_REQ_N1

H_REQ_N2

H_REQ_N3

H_REQ_N4

H_RS_N0

H_RS_N1

H_RS_N2

4

H_REQ_N[4..0]

H_ADSTB0_N <8>

H_ADSTB1_N <8>

H_STBP_N<0> <8>

H_STBN_N<0> <8>

H_DBI_N<0> <8>

H_STBP_N<1> <8>

H_STBN_N<1> <8>

H_DBI_N<1> <8>

H_STBP_N<2> <8>

H_STBN_N<2> <8>

H_DBI_N<2> <8>

H_STBP_N<3> <8>

H_STBN_N<3> <8>

H_DBI_N<3> <8>

H_ADS_N <8>

H_TRDY_N <8>

H_DRDY_N <8>

H_DEFER_N <8>

H_HITM_N <8>

H_HIT_N <8>

H_LOCK_N <8>

H_BREQ0_N <8,9>

H_BNR_N <8>

H_BPRI_N <8>

H_DBSY_N <8>

H_CPURST_N <8,9,43>

1

2X GTL+

H_REQ_N[4..0] <8>

4X GTL+

1X GTL+

TP13

TP14

TPAD28

1

TPAD28

3

CN3

1

2

FOX-CON2-3

CN4

1

2

FOX-CON2-3

3

2

U2A

D14

EXP_TXP0

C13

EXP_TXN0

A13

EXP_TXP1

B12

EXP_TXN1

A11

EXP_TXP2

B10

EXP_TXN2

C10

EXP_TXP3

C9

EXP_TXN3

A9

EXP_TXP4

B7

EXP_TXN4

D7

EXP_TXP5

D6

EXP_TXN5

A6

EXP_TXP6

B5

EXP_TXN6

E2

EXP_TXP7

F1

EXP_TXN7

G2

EXP_TXP8

J1

EXP_TXN8

J3

EXP_TXP9

K4

EXP_TXN9

L4

EXP_TXP10

M4

EXP_TXN10

M2

EXP_TXP11

N1

EXP_TXN11

P2

EXP_TXP12

T1

EXP_TXN12

T4

EXP_TXP13

U4

EXP_TXN13

U2

EXP_TXP14

V1

EXP_TXN14

V3

EXP_TXP15

W4

EXP_TXN15

W2

DMI_MT_IR_0_DP<26>

DMI_MT_IR_0_DN<26>

DMI_MT_IR_1_DP<26>

DMI_MT_IR_1_DN<26>

DMI_MT_IR_2_DP<26>

DMI_MT_IR_2_DN<26>

DMI_MT_IR_3_DP<26>

DMI_MT_IR_3_DN<26>

GRCOMP<19> CK_PE_100M_MCH_DP <25>

AA2

AB1

AA4

AB3

AC4

AC12

AC11

Y1

Y4

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

EXP_COMPO

EXP_COMPI

LAKEPORT-1-GP

1 OF 8

EXP_RXP0

EXP_RXN0

EXP_RXP1

EXP_RXN1

EXP_RXP2

EXP_RXN2

EXP_RXP3

EXP_RXN3

EXP_RXP4

EXP_RXN4

EXP_RXP5

EXP_RXN5

EXP_RXP6

EXP_RXN6

EXP_RXP7

EXP_RXN7

EXP_RXP8

EXP_RXN8

EXP_RXP9

EXP_RXN9

EXP_RXP10

EXP_RXN10

EXP_RXP11

EXP_RXN11

EXP_RXP12

EXP_RXN12

EXP_RXP13

EXP_RXN13

EXP_RXP14

EXP_RXN14

EXP_RXP15

EXP_RXN15

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

GCLKP

GCLKN

SDVO_CTRLDATA

SDVO_CTRLCLK

G12

F12

D11

D12

J13

H13

E10

F10

J9

H10

F7

F9

C4

D3

G6

J6

K9

K8

F4

G4

M6

M7

K2

L1

U11

U10

R8

R7

P4

N3

Y10

Y11

Y7

Y8

AA9

AA10

AA6

AA7

AC9

AC8

B14

B16

F15

E15

1

DMI_IT_MR_0_DP <26>

DMI_IT_MR_0_DN <26>

DMI_IT_MR_1_DP <26>

DMI_IT_MR_1_DN <26>

DMI_IT_MR_2_DP <26>

DMI_IT_MR_2_DN <26>

DMI_IT_MR_3_DP <26>

DMI_IT_MR_3_DN <26>

CK_PE_100M_MCH_DN <25>

Delete net SDVO_CTRL_DATA,SDVO_CTRL_CLK,R325,R326

<Variant Name>

Title

MCH PCIE/DMI 1 OF 6

Size Document Number Rev

S15

Custom

Date: Sheet

2

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

12 50Friday, December 12, 2008

1

-1

of

Page 13

5

D D

C C

B B

M_MAA_A[13..0]<22,23>

CK_M_166M_DDR0_A_DP<22>

CK_M_166M_DDR0_A_DN<22>

CK_M_166M_DDR1_A_DP<22>

CK_M_166M_DDR1_A_DN<22>

CK_M_166M_DDR2_A_DP<22>

CK_M_166M_DDR2_A_DN<22>

M_SCS_A_N0<22,23>

M_SCS_A_N1<22,23>

M_SCKE_A0<22,23>

M_SCKE_A1<22,23>

M_ODT_A0<22,23>

M_ODT_A1<22,23>

4

M_MAA_A[13..0]

M_WE_A_N<22,23>

M_CAS_A_N<22,23>

M_RAS_A_N<22,23>

M_SBS_A0<22,23>

M_SBS_A1<22,23>

M_SBS_A2<22,23>

TP18 TPAD28

MCH_VREF_A<14,20>

M_SCS_A_N0

M_SCS_A_N1

TP15 TPAD28

1

TP16 TPAD28

1

M_SCKE_A0

M_SCKE_A1

TP17 TPAD28

1

1

M_ODT_A0

M_ODT_A1

TP19 TPAD28

1

TP20 TPAD28

1

TP21 TPAD28

1

TP22 TPAD28

1

TP23 TPAD28

1

TP24 TPAD28

1

TP25 TPAD28

1

TP26 TPAD28

1

MCH_VREF_A

TP27 TPAD28

1

TP28 TPAD28

1

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_WE_A_N

M_CAS_A_N

M_RAS_A_N

M_SBS_A0

M_SBS_A1

M_SBS_A2

BA32

AW32

BB30

BA30

AY30

BA27

BC28

AY27

AY28

BB27

AY33

AW27

BB26

BC38

BB35

BA37

BA34

BC33

AY34

BA26

BB37

BA39

BA35

AY38

BB25

AY25

BC24

BA25

AW37

AY39

AY37

BB40

BB32

AY32

AK42

AK41

BA31

BB31

AH40

AH43

BC16

AY14

AW17

AW18

AK40

AL17

AK17

AY5

BB5

AY6

BA5

AM4

3 OF 8

U2C

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SWE_A#

SCAS_A#

SRAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A#0

SCS_A#1

SCS_A#2

SCS_A#3

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

SODT_A0

SODT_A1

SODT_A2

SODT_A3

SCLK_A0

SCLK_A#0

SCLK_A1

SCLK_A#1

SCLK_A2

SCLK_A#2

SCLK_A3

SCLK_A#3

SCLK_A4

SCLK_A#4

SCLK_A5

SCLK_A#5

RESERVED#BC16

RESERVED#AY14

RESERVED#AW17

RESERVED#AW18

RESERVED#AK40

SM_VREF_0

RSV_TP1

RSV_TP0

SDQS_A0

SDQS_A#0

SDM_A0

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDQS_A1

SDQS_A#1

SDM_A1

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQS_A2

SDQS_A#2

SDM_A2

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_A23

SDQS_A3

SDQS_A#3

SDM_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDQS_A#4

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDQS_A#5

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDQS_A#6

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDQS_A#7

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

3

AU4

AR2

AR3

AP3

AP2

AU3

AV4

AN1

AP4

AU5

AU2

BA3

BB4

AY2

AW3

AY3

BA7

BB7

AV1

AW4

BC6

AY7

AY11

BA10

BB10

AW12

AY10

BA12

BB12

BA9

BB9

BC11

AY12

AU18

AR18

AP18

AM20

AM18

AV20

AM21

AP17

AR17

AP20

AT20

AU35

AV35

AT34

AP32

AV34

AV38

AU39

AV32

AT32

AR34

AU37

AP42

AP40

AP39

AR41

AR42

AN43

AM40

AU41

AU42

AP41

AN40

AG42

AG41

AG40

AL41

AL42

AF39

AE40

AM41

AM42

AF41

AF42

AC42

AC41

AC40

AD40

AD43

AA39

AA40

AE42

AE41

AB41

AB42

M_DQS_A_DP0

M_DQS_A_DN0

M_DQM_A0

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DQS_A_DP1

M_DQS_A_DN1

M_DQM_A1

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DQS_A_DP2

M_DQS_A_DN2

M_DQM_A2

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DQS_A_DP3

M_DQS_A_DN3

M_DQM_A3

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DQS_A_DP4

M_DQS_A_DN4

M_DQM_A4

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DQS_A_DP5

M_DQS_A_DN5

M_DQM_A5

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DQS_A_DP6

M_DQS_A_DN6

M_DQM_A6

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DQS_A_DP7

M_DQS_A_DN7

M_DQM_A7

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

M_DQS_A_DP[7..0]

M_DQS_A_DN[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A_DP[7..0] <22>

M_DQS_A_DN[7..0] <22>

M_DQM_A[7..0] <22>

M_DATA_A[63..0] <22>

2

1

LAKEPORT-1-GP

A A

<Variant Name>

Title

MCH DDR2 A 2 OF 6

Size Document Number Rev

S15

C

Date: Sheet

5

4

3

2

1

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

of

13 50Friday, December 12, 2008

-1

Page 14

5

D D

C C

B B

4

MCH_VREF_A<13,20>

SMRCOMP_P<20>

SMRCOMP_N<20>

MCH_VREF_A

BB22

BB21

BA21

AY21

BC20

AY19

AY20

BA18

BA19

BB18

BA22

BB17

BA17

AW42

BB23

AY24

BA23

AW23

AY23

AY17

BA40

AW41

BA41

AW40

BA14

AY16

BA13

BB13

AY42

AV40

AV43

AU40

AM29

AM27

AL38

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

AL39

AK18

AK23

AV9

AW9

AM2

AM3

AJ8

AJ6

AL5

3

4 OF 8

U2D

SMA_B0

SMA_B1

SMA_B2

SMA_B3

SMA_B4

SMA_B5

SMA_B6

SMA_B7

SMA_B8

SMA_B9

SMA_B10

SMA_B11

SMA_B12

SMA_B13

SWE_B#

SCAS_B#

SRAS_B#

SBS_B0

SBS_B1

SBS_B2

SCS_B0#

SCS_B1#

SCS_B2#

SCS_B3#

SCKE_B0

SCKE_B1

SCKE_B2

SCKE_B3

SODT_B0

SODT_B1

SODT_B2

SODT_B3

SCLK_B0

SCLK_B#0

SCLK_B1

SCLK_B#1

SCLK_B2

SCLK_B#2

SCLK_B3

SCLK_B#3

SCLK_B4

SCLK_B#4

SCLK_B5

SCLK_B#5

RESERVED#AL39

SM_VREF_1

RSV_TP3

RSV_TP2

SM_OCDCOPM_1

SM_OCDCOPM_0

SM_RCOMP1

SM_RCOMP0

SDQS_B0

SDQS_B#0

SDM_B0

SDQ_B0

SDQ_B1

SDQ_B2

SDQ_B3

SDQ_B4

SDQ_B5

SDQ_B6

SDQ_B7

SDQS_B1

SDQS_B#1

SDM_B1

SDQ_B8

SDQ_B9

SDQ_B10

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_B14

SDQ_B15

SDQS_B2

SDQS_B#2

SDM_B2

SDQ_B16

SDQ_B17

SDQ_B18

SDQ_B19

SDQ_B20

SDQ_B21

SDQ_B22

SDQ_B23

SDQS_B3

SDQS_B#3

SDM_B3

SDQ_B24

SDQ_B25

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_B30

SDQ_B31

SDQS_B4

SDQS_B#4

SDM_B4

SDQ_B32

SDQ_B33

SDQ_B34

SDQ_B35

SDQ_B36

SDQ_B37

SDQ_B38

SDQ_B39

SDQS_B5

SDQS_B#5

SDM_B5

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQS_B6

SDQS_B#6

SDM_B6

SDQ_B48

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQS_B7

SDQS_B#7

SDM_B7

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

SDQ_B63

AM8

AM6

AL11

AL6

AL8

AP8

AP9

AJ11

AL9

AM10

AP6

AV7

AR9

AW7

AU7

AV6

AV12

AM11

AR5

AR7

AR12

AR10

AV13

AT13

AP13

AM15

AM13

AV15

AM17

AN12

AR13

AP15

AT15

AU23

AR23

AP23

AM24

AM23

AV24

AM26

AP21

AR21

AP24

AT24

AT29

AV29

AR29

AU27

AN29

AR31

AM31

AP27

AR27

AP31

AU31

AP36

AM35

AR38

AP35

AP37

AN32

AL35

AR35

AU38

AM38

AM34

AG34

AG32

AJ39

AL34

AJ34

AF32

AF34

AL31

AJ32

AG35

AD32

AD36

AD38

AD39

AC32

AD34

Y32

AA32

AF35

AF37

AC33

AC35

2

1

LAKEPORT-1-GP

A A

<Variant Name>

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Title

MCH DDR2 B 3 OF 6

Size Document Number Rev

S15

C

Date: Sheet

5

4

3

2

Hsichih, Taipei

-1

of

14 50Friday, December 12, 2008

1

Page 15

5

http://hobi-elektronika.net/

D D

R31

DUMMY-R2

V_FSB_VTT

C C

B B

1 2

R31 Reserved

for 1K

R32 Reserved

for 1K

12

R32

DUMMY-R2

V_1P5_CORE

SIGNAL NAMING CONVENTION

EXP : PCI EXPRESS

DMI : DIRECT MEDIA INTERFACE

MEM_TYPE<19>

EXP_SLR<19>

BSEL_0<19>

BSEL_1<19>

BSEL_2<19>

EXP_EN

4

TP29 TPAD28

TP30 TPAD28

TP31 TPAD28

TP32 TPAD28

3

U2E

5 OF 8

F21

BSEL0

H21

BSEL1

L20

H20

N21

M17

R27

U27

M15

BB2

BA2

AW26

AW2

AV27

AV26

AJ27

AG27

AG26

AG25

AJ24

AD30

AC34

AF31

AD31

U30

AA30

AC30

K18

L18

K21

L21

F20

L17

L15

E35

B42

B41

Y30

Y33

V31

BSEL2

ALLZTEST

XORTEST

RSV_TP5

EXP_SLR

RSV_TP4

EXP_EN

RSV_TP6

VCC

VSS

RESERVED#R27

RESERVED#U27

RESERVED#M15

RESERVED#L15

NC#BB2

NC#BA2

NC#AW26

NC#AW2

NC#AV27

NC#AV26

NC#E35

NC#B42

NC#B41

RESERVED#AJ27

RESERVED#AG27

RESERVED#AG26

RESERVED#AG25

RESERVED#AJ24

RESERVED#AD30

RESERVED#AC34

RESERVED#Y30

RESERVED#Y33

RESERVED#AF31

RESERVED#AD31

RESERVED#U30

RESERVED#V31

RESERVED#AA30

RESERVED#AC30

LAKEPORT-1-GP

DDC_DATA

DREFCLKP

DREFCLKN

RESERVED#M11

RESERVED#V30

ICH_SYNC#

RESERVED#A43

RESERVED#AK21

RESERVED#AJ23

RESERVED#AJ26

RESERVED#AL29

RESERVED#AL20

RESERVED#AJ21

RESERVED#AL26

RESERVED#AK27

RESERVED#AJ29

RESERVED#AG29

1

1

1

1

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREENB

BLUE#

DDC_CLK

IREF

EXTTS#

RSTIN#

PWROK

NC#BC43

NC#BC42

NC#BC2

NC#BC1NC#C42

NC#BB43

NC#BB1

NC#C2

NC#B43

NC#B3

NC#B2

NC#A42

D17

C17

F17

K17

H18

G17

J17

J18

N18

N20

A20

J15

H15

J20

M11

V30

AJ12

AJ9

M18

A43

BC43

BC42

BC2

BC1C42

BB43

BB1

C2

B43

B3

B2

A42

AK21

AJ23

AJ26

AL29

AL20

AJ21

AL26

AK27

AJ29

AG29

HSYNC <41>

VSYNC <41>

VGA_RED <21,41>

VGA_GREEN <21,41>

VGA_BLUE <21,41>

MCH_DDC_DATA <21,41>

MCH_DDC_CLK <21,41>

DACREFSET <21>

CK_96M_DREF_DP <25>

CK_96M_DREF_DN <25>

EXTTS_N

PLTRST_N <28,35,38>

PWRGD_3V <28,38>

ICH_SYNC_N <28>

R33

1 2

10KR2J-3-GP

2

V_2P5_MCH

1

ITP : ICH TRANSMIT POSITIVE

ITN : ICH TRANSMIT NEGATIVE

IRP : ICH RECEIVE POSITIVE

IRN : ICH RECEIVE NEGATIVE

MTP : MCH TRANSMIT POSITIVE

A A

MTN : MCH TRANSMIT NEGATIVE

MRP : MCH RECEIVE POSITIVE

MRN : MCH RECEIVE NEGATIVE

5

4

3

2

<Variant Name>

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Title

MCH MSIC 4 OF 6

Size Document Number Rev

S15

B

Date: Sheet

Hsichih, Taipei

15 50Friday, December 12, 2008

1

of

-1

Page 16

5

D D

C C

B B

VCCA_HPLL_MPLL

VCCA_HPLL_MPLL

A A

5

V_2P5_DAC_FILTERED

V_1P5_CORE

V_FSB_VTT

VCCA_DPLLB

VCCA_DPLLA

V_2P5_MCH

VCCA_GPLL

4

6 OF 8

U2F

N17

VCC

P17

VCC

AH4

VCC

AJ5

VCC

AK4

VCC

AF30

VCC

AK20

VCC

AK3

VCC

AK2

VCC

AJ14

VCC

AK14

VCC

AK15

VCC

AJ13

VCC

AH2

VCC

AH1

VCC

AG14

VCC

AG13

VCC

AG12

VCC

AG11

VCC

AG10

VCC

AG9

VCC

AG8

VCC

AG7

VCC

AG6

VCC

AG5

VCC

AG4

VCC

AG3

VCC

AG2

VCC

AF14

VCC

AF13

VCC

AF12

VCC

AF11

VCC

AF10

VCC

AF9

VCC

AF8

VCC

AF7

VCC

AF6

VCC

AD14

VCC

AC22

VCC

AB23

VCC

AB22

VCC

AB21

VCC

AA22

VCC

P21

VCC

P20

VCC

P18

VCC

F27

VTT

G23

VTT

H23

VTT

J23

VTT

K23

VTT

L23

VTT

M23

VTT

A24

VTT

N23

VTT

C26

VTT

D23

VTT

D24

VTT

D25

VTT

P23

VTT

F23

VTT

E27

VTT

E26

VTT

E24

VTT

E23

VTT

C25

VTT

C23

VTT

B26

VTT

B25

VTT

B24

VTT

B23

VTT

B19

VCCADPLLB

B20

VCCAMPLL

C21

VCCAHPLL

C19

VCCADPLLA

C18

VCCA_DAC

B18

VCCA_DAC

D19

VCC2

B17

VCCA_EXPPLL

A18

VSSA_DAC

LAKEPORT-1-GP

4

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

3

3

BC18

BC22

BC26

BC31

BC35

BC13

BB42

BB38

BB33

BB28

BB24

BB20

BB16

AY41

AW21

AW13

AV31

AV21

AW35

AW34

AW31

AW29

AW24

AW20

AW15

AV42

AV23

AV18

AD4

AD5

AD6

AD8

AD10

AD12

N5

N7

N9

N10

N12

R5

R10

AE2

R11

R13

U6

U7

U8

U13

V5

V6

V7

V9

AE3

V10

V13

Y13

AA5

AA13

AC5

AC6

AC13

AD1

AD2

AE4

N11

V_SM

V_1P5_CORE

2

1

<Variant Name>

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Title

MCH POWER 5 OF 6

Size Document Number Rev

S15

B

Date: Sheet

2

Hsichih, Taipei

16 50Friday, December 12, 2008

1

-1

of

Page 17

5

D D

U2H

G9G7G5

G38

G35

G32

G31G3G29

G27

G24

G21

G20

G18

G15

G13

G10F6F42

F34

AU15

F26F2F18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AU17

AU20

AU21

AU24

AU26

AU29

AU32

AU34

AU6

8 OF 8

Y9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT21

AT23

AT26

AT27

AT31

AU12

AU13

VSS

Y6

VSS

Y5

VSS

Y42

VSS

Y39

VSS

Y37

VSS

Y35

VSS

Y31

VSS

Y2

VSS

Y14

VSS

Y12

VSS

W3

VSS

V8

VSS

V43

VSS

V39

VSS

V38

VSS

V37

VSS

V36

VSS

V34

VSS

V2

VSS

V14

VSS

V12

VSS

V11

VSS

U9

AR39

U5

U38

U36

U33

U31

U3

U14

U12

T42

T2

R9

R6

R39

R37

R34

R31

R30

R14

R12

P30

P3

P29

P27

P26

P24

P15

P14

N8

N6

N43

N39

N36

N33

N31

N29

N27

N26

N24

N2

N15

N13

M9

M8

M5

M37

M35

M3

M21

M20

M13

M10

L42

L31

L29

L26

L24

L2

L13

L12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

LAKEPORT-1-GP

AR43

AR6

VSS

VSS

VSS

AT12

AT17

C C

B B

F13E9E7E4E32E3E21

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AU9

AV10

AV17

AV2

AV37

4

E20

E18

E17

E13

E12D5D21

D20D2D16

D10C7C5

C40C3C22

C14

C12

BC9

BB6

H12

H17

H26

H27

H32

J10

J12J2J21

J24

J29

J38

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS