OP ERA TIONS MAN UAL

LBC- 486Plus

LBC- 586Plus

Win Sys tems re serves the right to make changes in the cir cuitry

and speci fi ca tions at any time with out no tice.

Copy right 1997 by Win Sys tems. All Rights Re served.

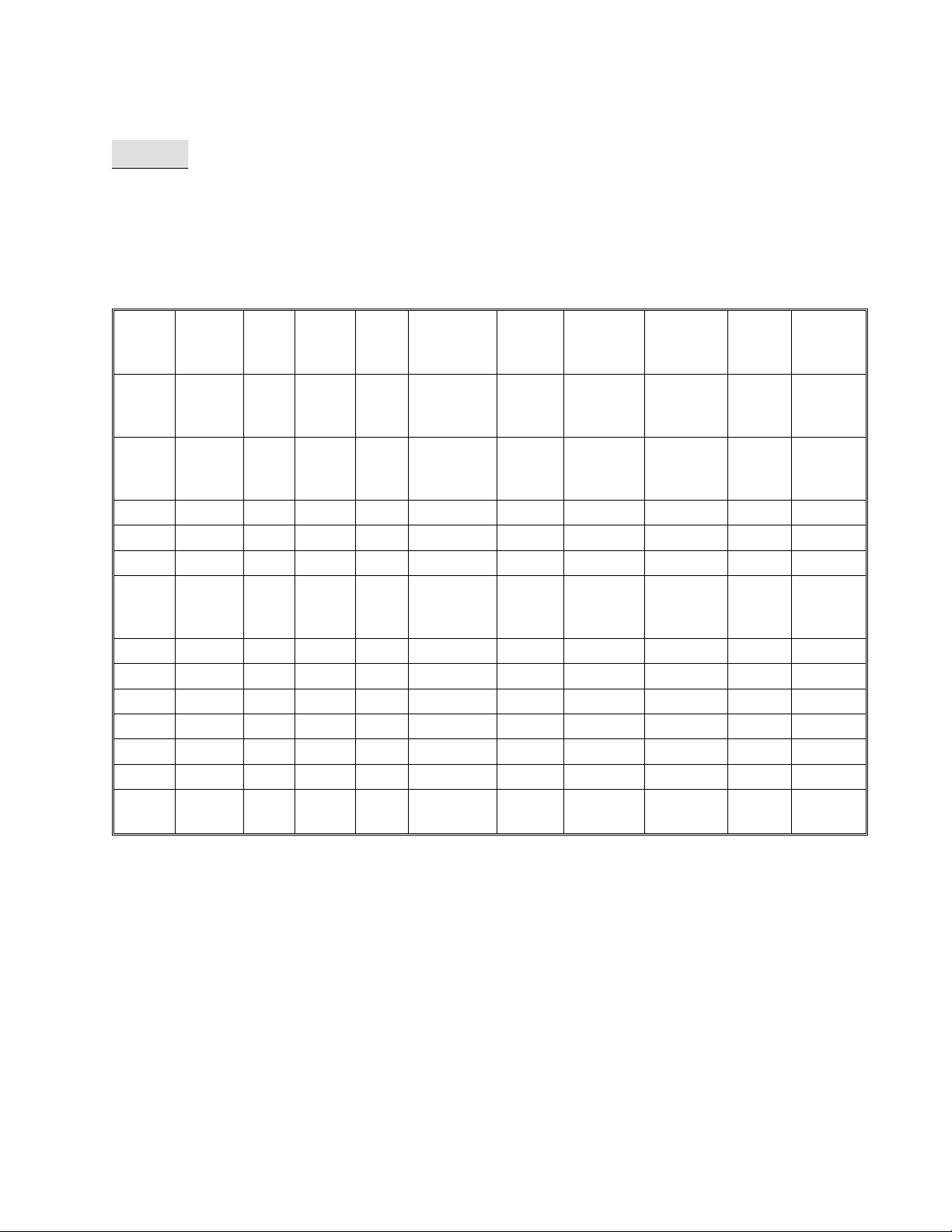

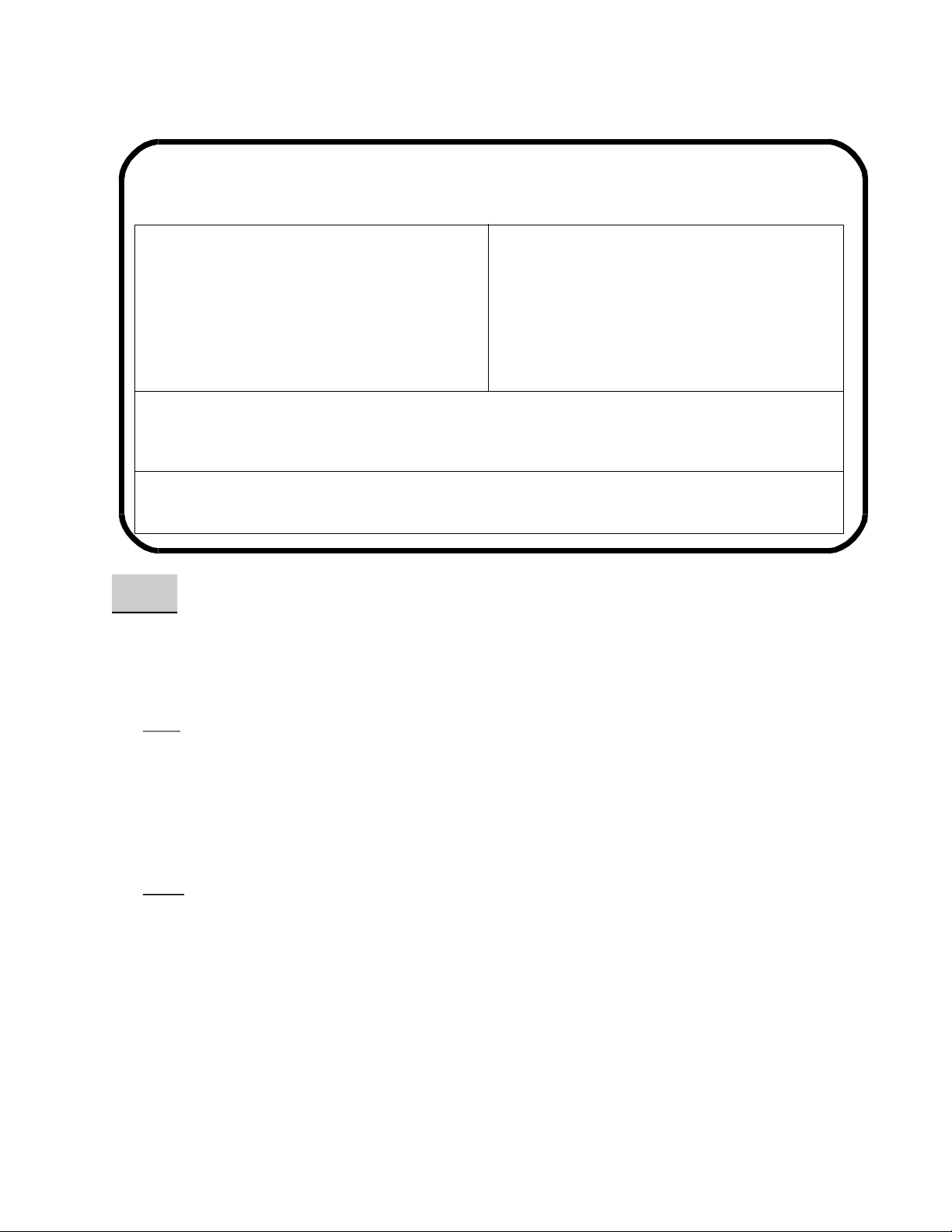

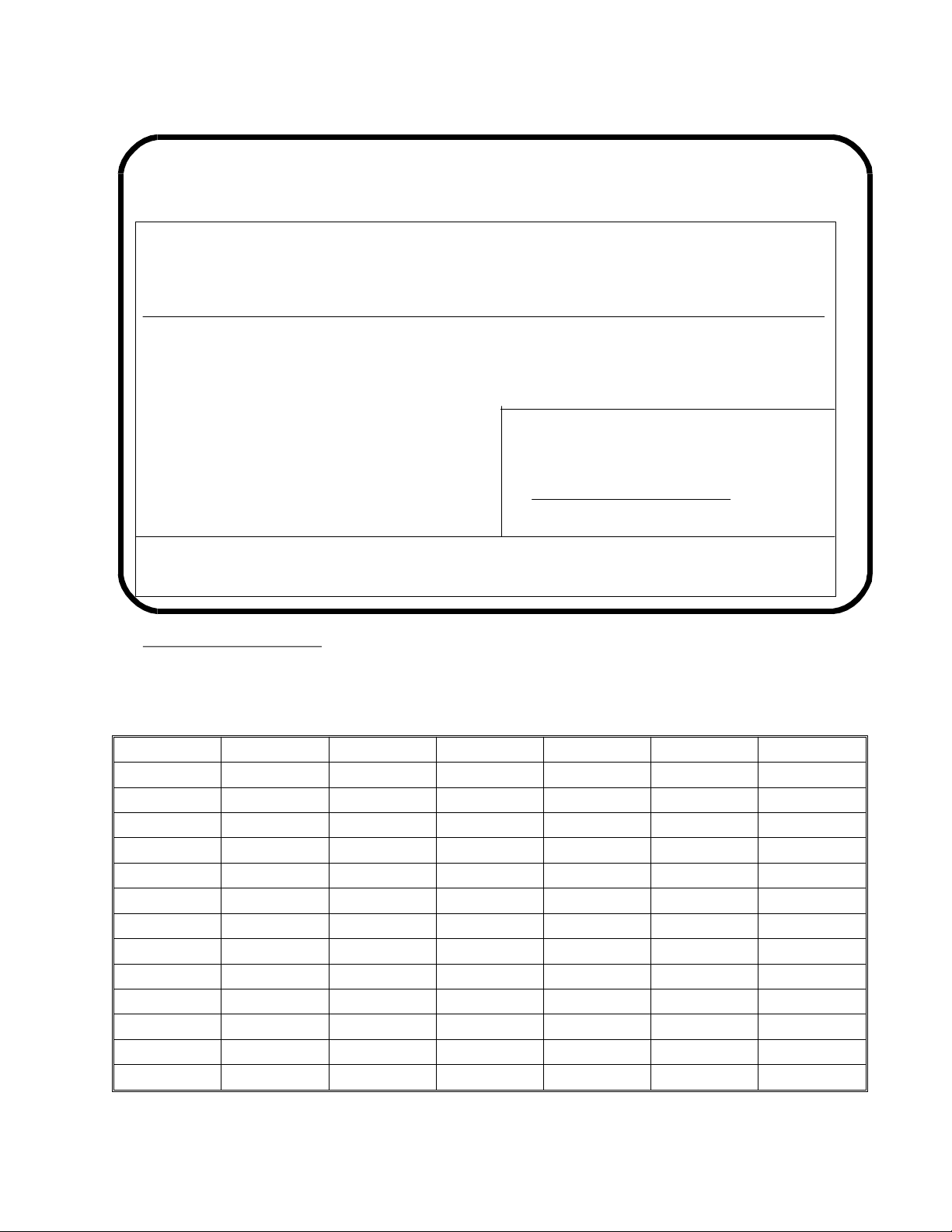

RE VI SION HIS TORY

P/N 403- 0259- 000

ECO Num ber Date Code Rev L evel

ORIGI NATED 970422 C

97- 36 970602 C1

97- 78 970829 C2

97- 105 971204 C3

98- 01 980107 C4

98- 18 980311 C5

98- 57 980807 C6

98- 86 980817 C7

99- 30 990609 D

99- 83 991206 E

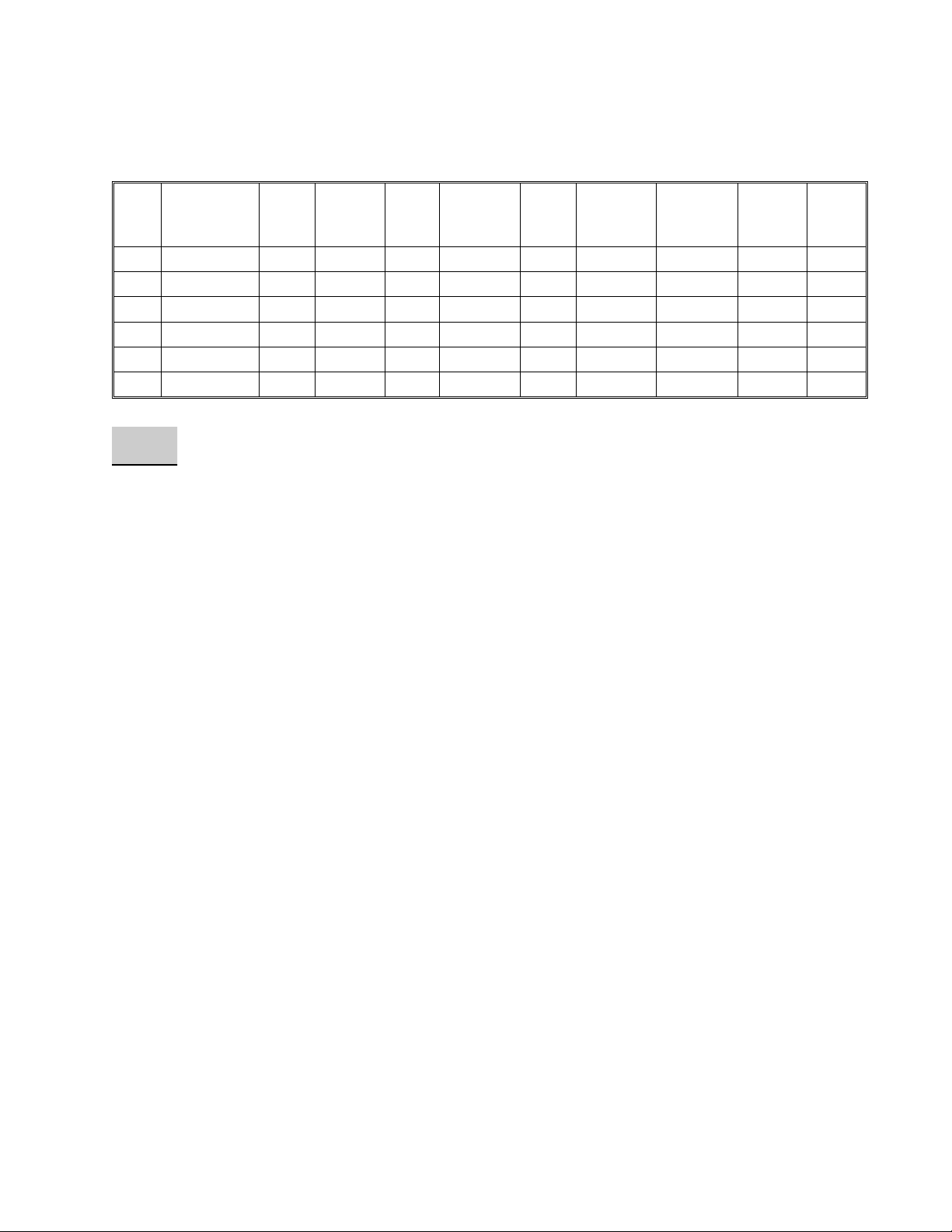

TA BLE OF CON TENTS

Sec tion Para graph Page

Num ber Ti tle Num ber

1 Gen eral In for ma tion

1.1 Fea tures 1-1

1.2 Gen eral De scrip tion 1-1

1.3 Speci fi ca tions 1-2

2 LBC- Plus Tech ni cal Ref er ence

2.1 In tro duc tion 2-1

2.2 ALI 1487/1489 Chipset 2-1

2.3 CPU Speed Se lec tion 2-2

2.4 PCI Clock Se lect 2-3

2.5 Mem ory In stal la tion 2-3

2.6 In ter rupt rout ing 2-4

2.7 Real Time Clock/Cal en dar 2-5

2.8 Key board In ter face 2-5

2.9 Se rial In ter face 2-6

2.10 Par al lel Printer Port 2-13

2.11 Speaker/Sound In ter face 2-14

2.12 PC/104 Bus In ter face 2-14

2.13 Floppy Disk In ter face 2-14

2.14 IDE Hard Disk In ter face 2-16

2.15 Watch dog Timer Con figu ra tion 2-16

2.16 Status LED 2-17

2.17 Bat tery Se lect Con trol 2-17

2.18 Power/Re set Con nec tion 2-18

2.19 Sili con Disk Con figu ra tion 2-18

2.20 Par al lel I/O 2-21

2.21 VGA Con figu ra tion 2-24

2.22 Eth er net Con figu ra tion 2-29

2.23 Multi I/O Con nec tor 2-41

2.24 Jumper/Con nec tor Sum mary 2-42

3 Award BIOS Con figu ra tion

3.1 Gen eral In for ma tion 3-1

3.2 En ter ing Setup 3-1

3.3 Setup Main Menu 3-1

3.4 Stan dard CMOS Setup 3-2

3.5 BIOS Fea tures Setup 3-6

3.6 Chipset Fea tures Setup 3-10

3.7 Load BIOS De faults 3-13

3.8 Load Setup De faults 3-13

3.9 Pass word Set ting 3-14

3.10 IDE HDD Auto De tec tion 3-14

3.11 Save & Exit Setup 3-14

3.12 Exit without Saving 3-14

4 LBC-Plus Silicon Disk Reference

4.1 Introduction 4-1

4.2 ROMDISK Usage 4-1

4.3 Bootable RAMDISK/FLASHDISK Usage 4-4

4.4 Non-Bootable RAMDISK Usage 4-5

4.5 Non-Bootable FLASHDISK Usage 4-7

4.6 DiskOnChip Usage 4-7

5 WS16C48 Programming Reference

5.1 Introduction 5-1

5.2 Function Definitions 5-1

5.3 Sample Programs 5-6

APPENDIX A I/O Port Map

APPENDIX B Interrupt Map

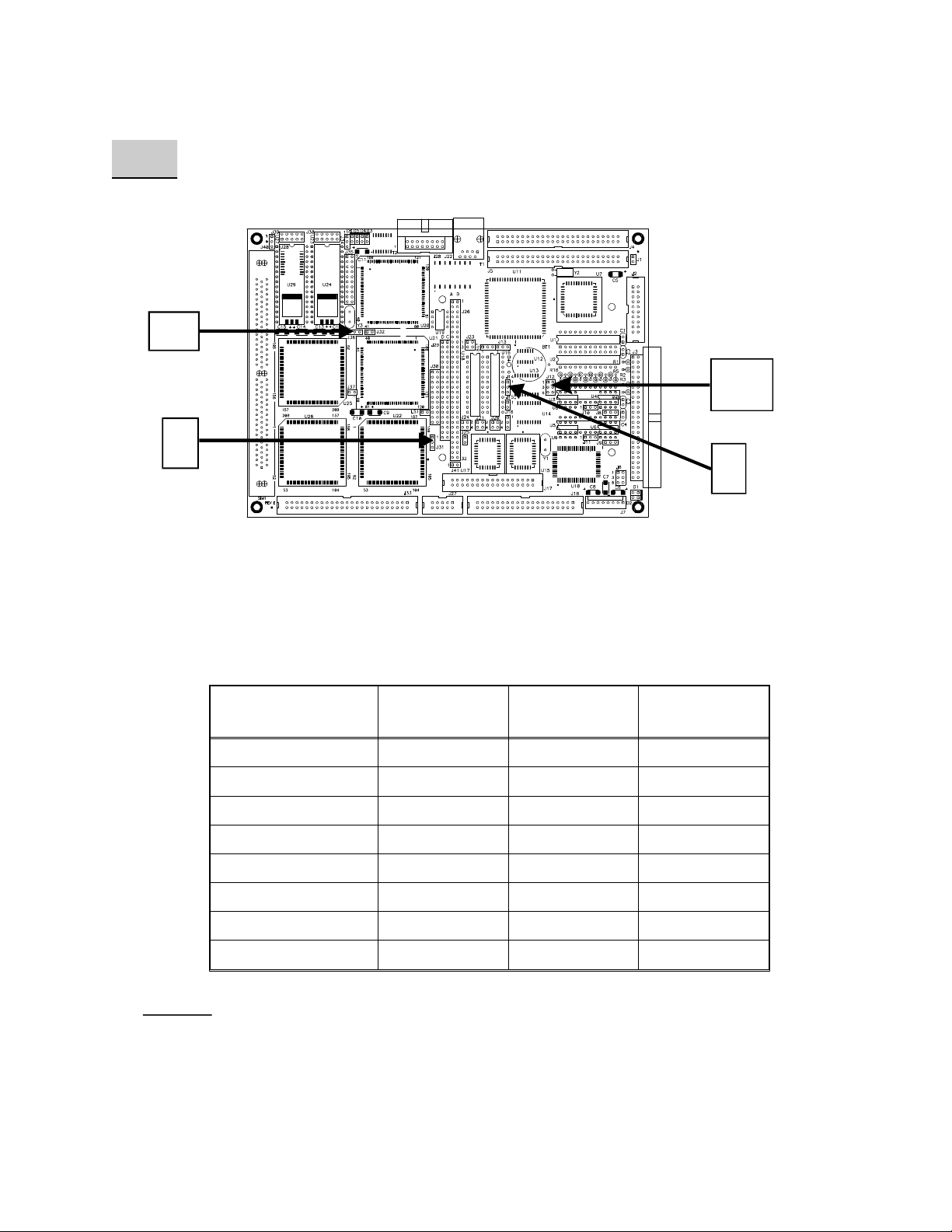

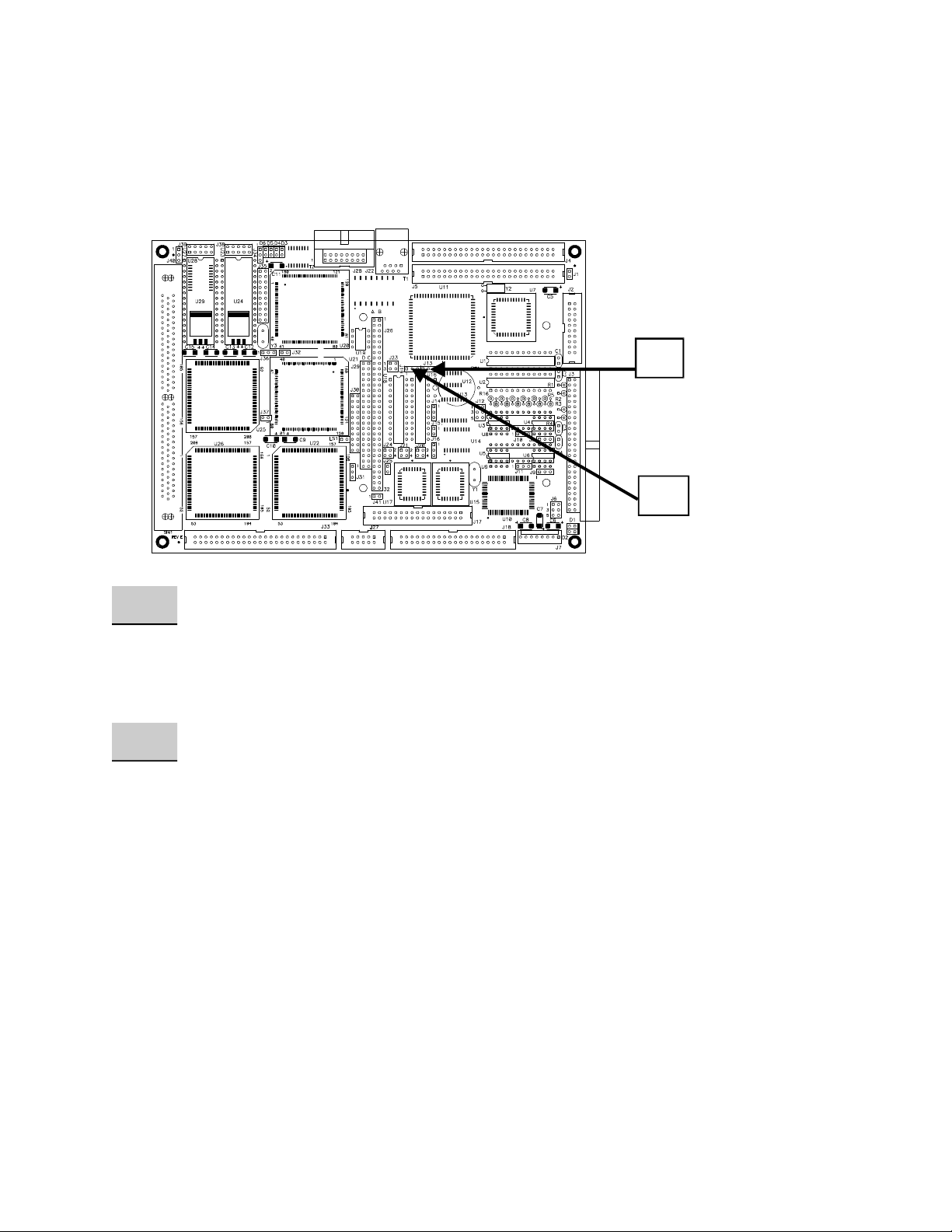

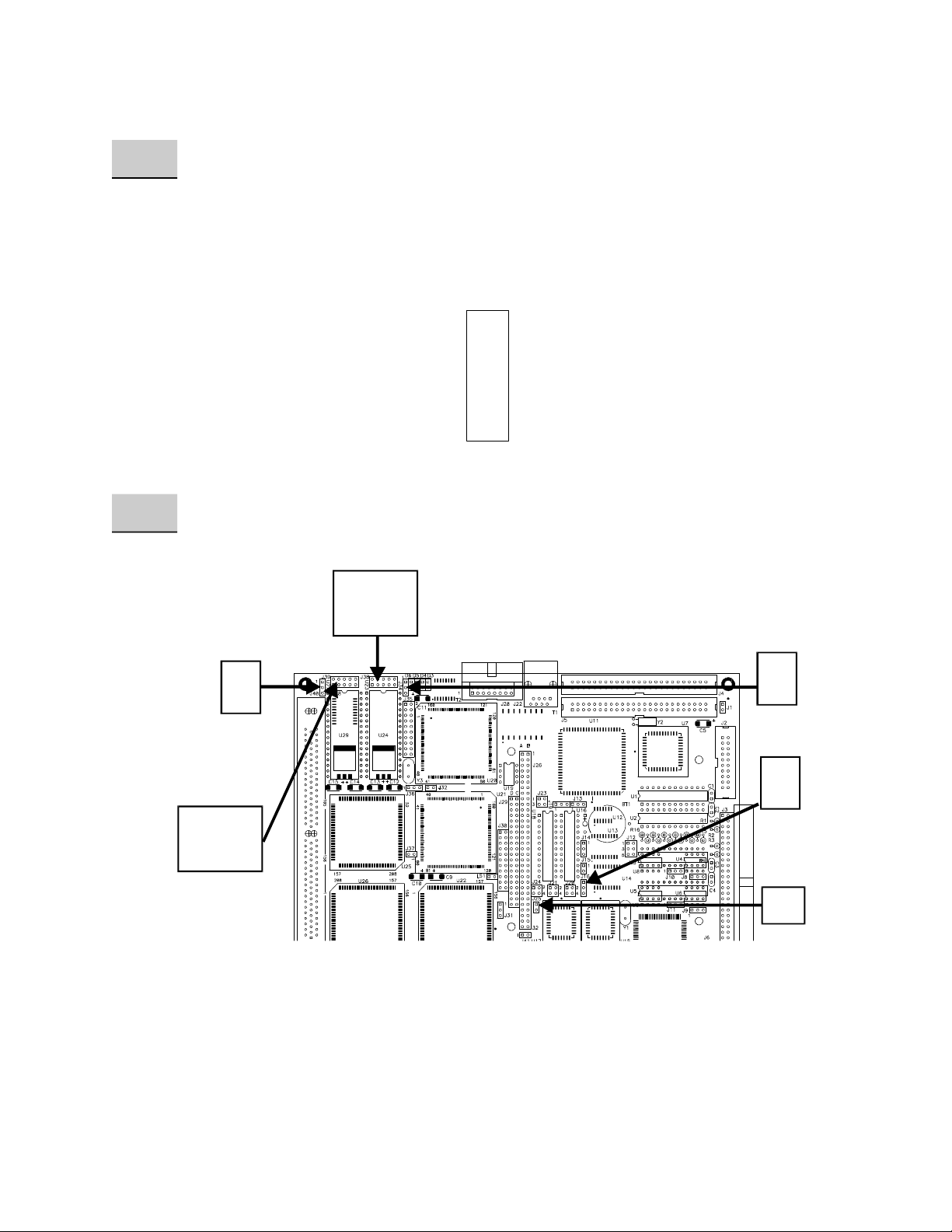

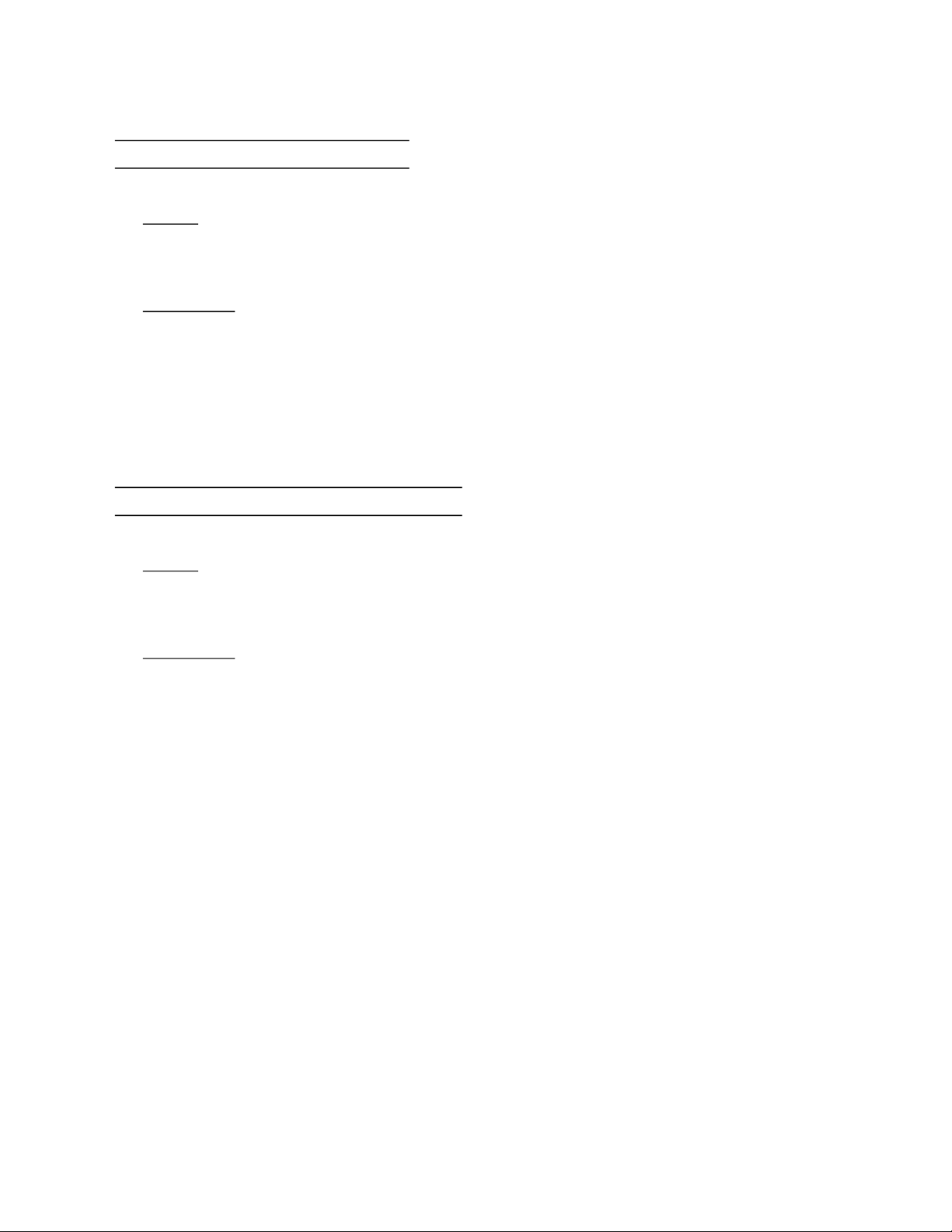

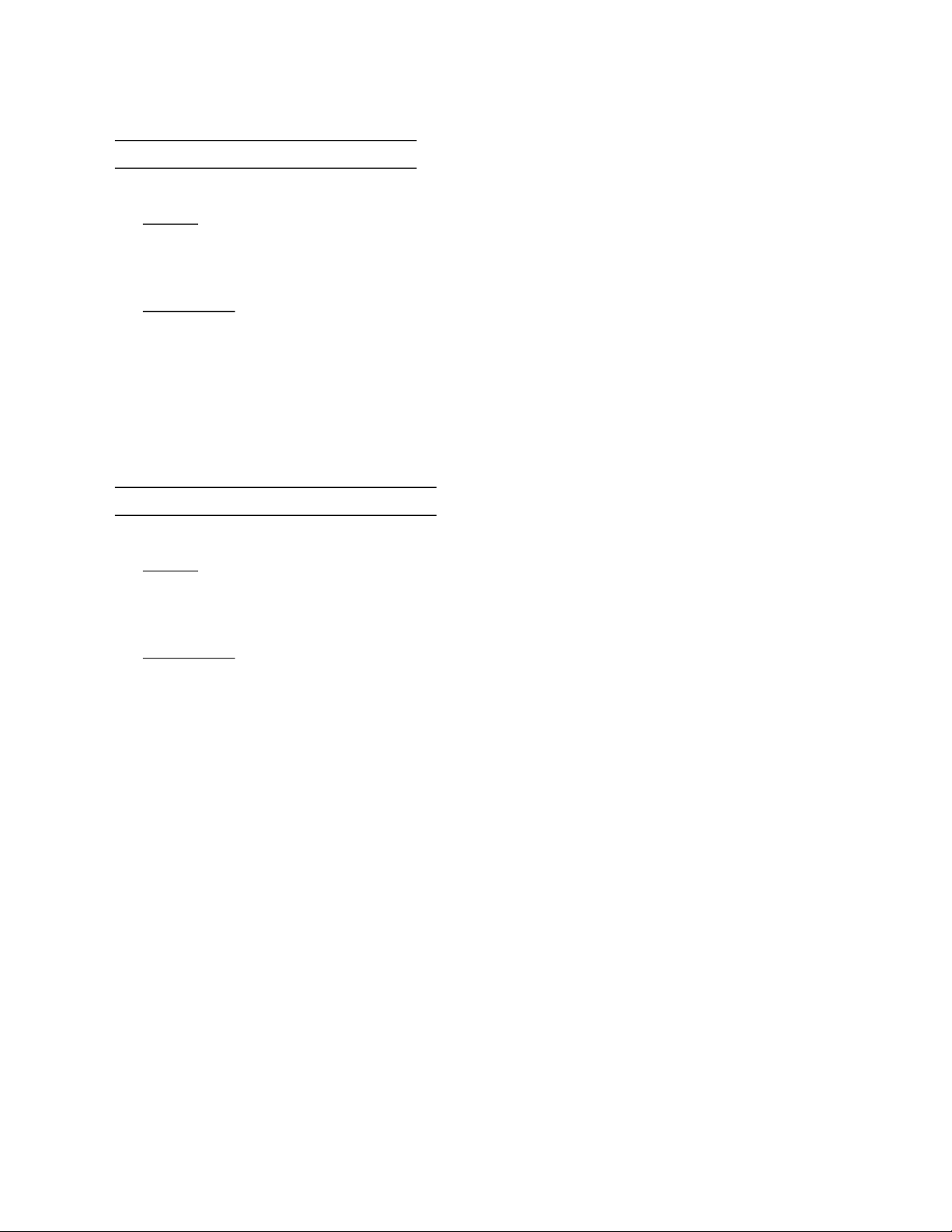

APPENDIX C Parts Placement Guide

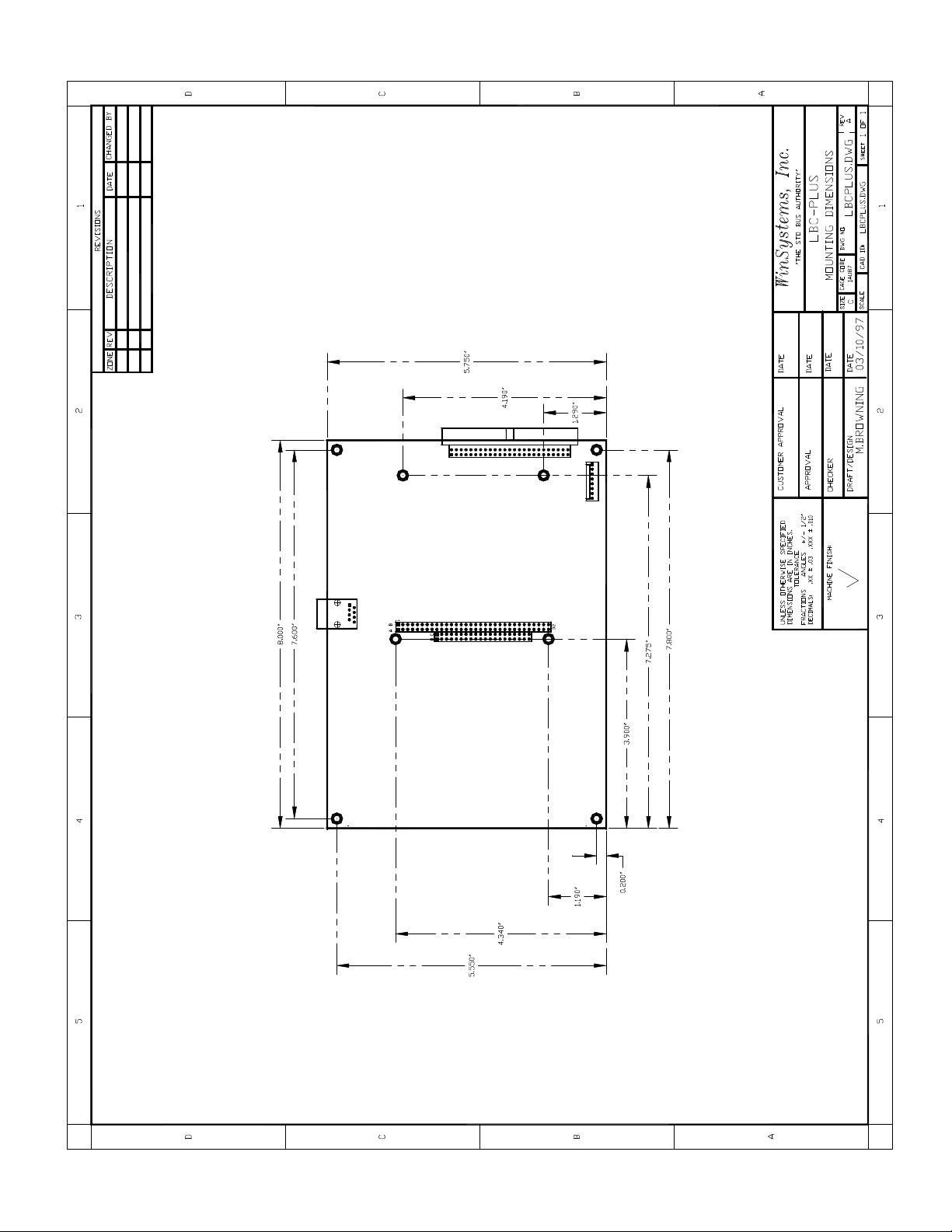

APPENDIX D LBC-Plus Mechanical Drawing

APPENDIX E WS16C48 I/O Routines and Sample Programs Listings

WARRANTY

1 Gen eral In for ma tion

1.1 Fea tures

n 486DX4 at 100MHz or 5X86 at 133 MHz

n 100% PC- AT Com pati ble

n Up to 32 Mbytes of user instal la ble FPM or EDO DRAM

n Op tional 256K L2 Cache

n Solid State Disk Sup port of up to 12MB

n PCI High- Resolution VGA con trol ler for CRT or Flat Panel us age

n PCI IDE Con trol ler

n NE2000 Com pati ble 10BaseT, AUI, Eth er net Con trol ler

n Four 16550 Com pati ble Se rial ports with op tional RS422, RS485, J1708 in ter faces

n Bi- directional Par al lel printer port sup ports EPP and ECP modes

n 48 Digi tal I/O lines with 24 line event sense ca pa bil ity

n Dual Floppy Disk in ter face

n 16- Bit PC/104 Ex pan sion Bus

n Watch dog Timer with Power- fail re set

1.2 Gen eral De scrip tion

The LBC- 486/586Plus is a small, high- performance, em beddable com puter sys tem on a sin gle

board. It in te grates a number of popu lar I/O op tions in clud ing VGA, Eth er net, Solid- State Disk, and

High- Density Par al lel I/O. Four PC com pati ble ser ial ports are stan dard, as are the floppy, hard disk,

and par al lel printer in ter faces. The LBC-Plus is popu lated with ei ther a 100 MHz AMD DX4 proc es sor

or the AMD 5x85 133 MHz proc es sor. Up to 32Mbytes of user instal la ble SIMM mem ory is sup ported. An op tional 256KB level two cache is also avail able. A full 16- bit PC/104 ex pan sion bus is

pro vided for fur ther ex pan sion to an en tire in dus try of add-on pe riph er als in clud ing so und and speech

mod ules, SCSI con trol lers, Ana log I/O mod ules, and lit er ally hun dreds of other op tions ava il able from

Win Sys tems and a va ri ety of ven dors sup port ing the PC/104 stan dard. An on board sili con di sk ar ray

sup ports disks up to 2 mega bytes in size and can util ize SRAM, PEROM or EPROM as the disk me dia .

Boot ca pa bil ity is pro vided on board and a set of utili ties and driv ers are pro vided to make the sili con

disk based sys tem very user friendly. Al ter nately, the M- Systems Disk On Chip FLASH mod ules ma y

be popu lated, sup port ing disk sizes rang ing from 1 Mega byte to 12 Mega bytes.

991206 OPERATIONS MANUAL LBC-Plus Page 1 - 1

WinSystems - "The Embedded Systems Authority"

1.3 Speci fi ca tions

1.3.1 Elec tri cal

Bus In ter face : PC/104 8- Bit or 16- Bit ex pan sion bus

Sys tem Clock : Jumper pro gram ma ble from 4MHz to 50MHz

In ter rupts : TTL Level in put

VCC : +5V +/- 5% at 2.0A typi cal with a 133MHz 5X86 proc es sor with 16M DRAM

1.8A typi cal with a 100MHz DX4 proc es sor and 16M DRAM

VCC1 : +12V +/-5% (Not re quired. PC/104 Ex pan sion, Flat- Panel, or AUI use only)

VCC2 : -12V +/-5% (Not required. PC/104 Ex pan sion or FLat- Panel use only)

1.3.2 Mem ory

Ad dress ing : 32 Mega byte ad dress ing

BIOS ROM : 128K OT PROM

Mem ory SIMM Socket : 72- pin Fast Page Mode or EDO DRAM in sizes from 1M to 32M

SSD Mem ory : Two 32- pin JE DEC stan dard sock ets sup port 4- Mbit SRAM, 4- Mbit PEROM,

4- Mbit EPROM, 8- Mbit EPROM, or one M- Systems 32- Pin DOC (Dis k On Chip) mod ule.

1.3.3 Me chani cal

Di men sions : 5.75 X 8.0 X 0.60 inches (with out PC/104 mod ules or ca bles)

PC- Board : FR4 Ep oxy Glass with 4 sig nal lay ers and 2 power planes with screened

com po nent leg end, and plated through holes.

Jump ers : 0.025" square posts on 0.10" cen ters

Con nec tors : Multi I/O : 50 pin RN type IDH- 50LP

COM3/COM4 : 20- pin RN type IDH- 20LP

Floppy Disk : 34 pin RN type IDH- 34- LP

Fixed Disk : 40 pin RN type IDH- 40- LP

Digi tal I/O : Two 50 pin RN type IDH- 50- LP

10BaseT : RJ45

Page 1 - 2 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

Eth er net AUI : 16 pin RN type IDH- 16- LP

CRT : 10 pin RN type IDH- 10- LP

Flat Panel : 50 pin RN type IDH- 50- LP

Power/Re set : 8 pin in- line Mo lex

PC/104 Bus : 64 Pin SAM TEC type ESQ- 132- 12- G-D

40 Pin SAM TEC type ESQ- 120- 12- G-D

1.3.4 En vi ron men tal :

Op er at ing Tem pera ture : -40 ° to +70° C

Non- condensing rela tive hu mid ity : 5% to 95%

991206 OPERATIONS MANUAL LBC-Plus Page 1 - 3

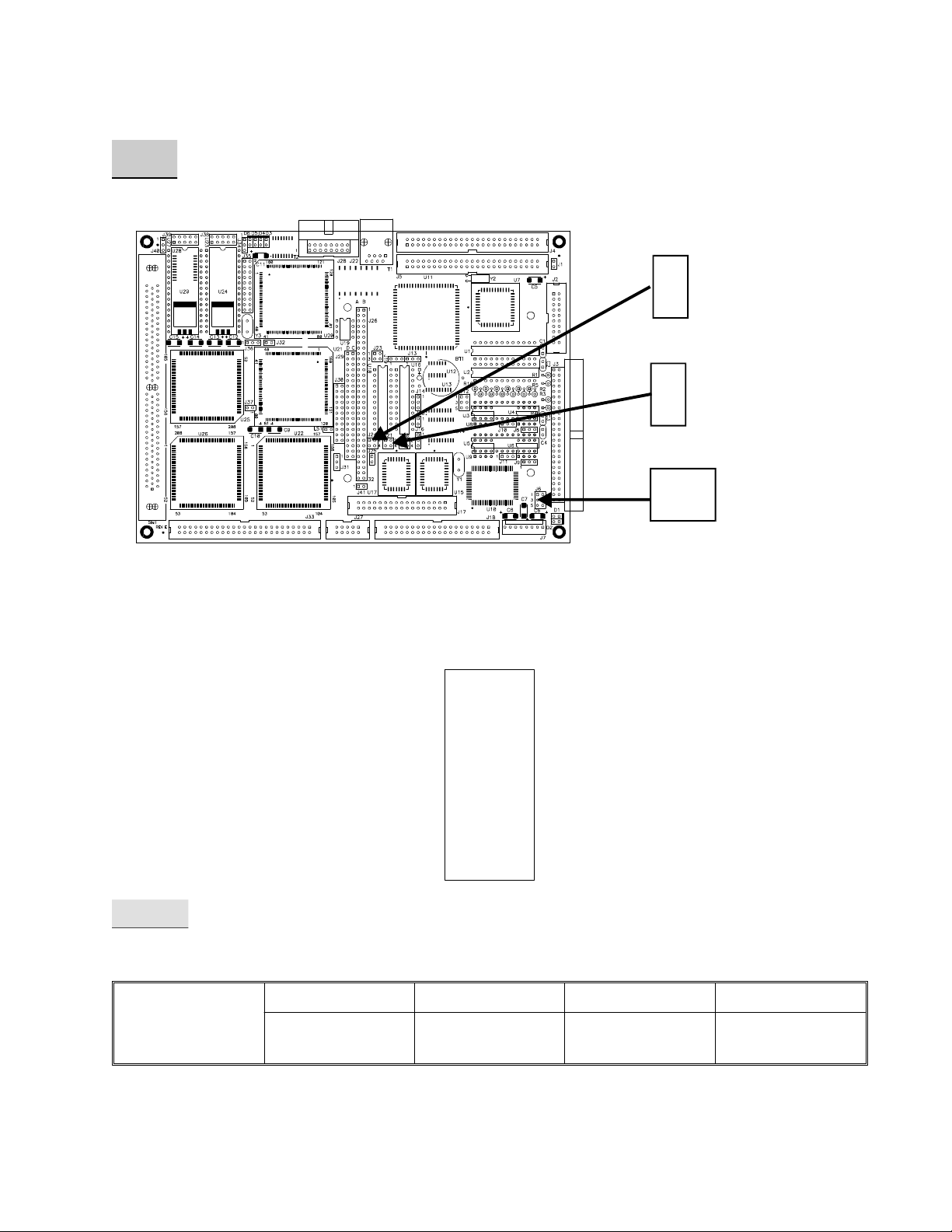

2 LBC- PLUS Tech ni cal Ref er ence

2.1 In tro duc tion

This sec tion of the man ual is in tended to pro vide suf fi cient in for ma tion re gard ing the c on figu ra tion

and us age of the LBC-Plus board. Win Sys tems main tains a Tech ni cal Sup port group to help an s wer

ques tions re gard ing con figu ra tion, us age, or pro gram ming of the board. For an swers to que s tions not

ade quately ad dressed in this man ual, con tact Tech ni cal Sup port at (817) 274- 7553 be tween 8 AM and

5PM Cen tral Time.

2.2 ALI 1487/1489 Chipset

The LBC-Plus util izes the ALI FINALI- 486 Chipset which pro vides a highly- integrated, high-

performance back bone for full PC/AT com pati bil ity. The Chipset con tains the logic for DRAM an d bus

state con trol as well as the stan dard com ple ment of 'AT' class pe riph er als, in clud ing :

8 DMA Chan nels com pati ble with PC/AT 8237A DMA con trol lers

15 in ter rupt in puts com pati ble with mas ter/slaved 8259 in ter rupt con trol lers

Three 8254 com pati ble timer/coun ter chan nels

A PC- AT com pati ble real time clock/cal en dar with CMOS RAM

A PCI BUS IDE in ter face

A PC/AT com pati ble key board in ter face

These func tional units are 100% PC/AT com pati ble and are sup ported by the AWARD BIOS and

setup. Us ers de sir ing to ac cess these in ter nal pe riph er als di rectly should ref er to any manu fac tur ers ge neric lit era ture on the equiva lent dis crete com po nent.

There are a number of in ter nal reg is ters within the Finali- 486 chipset that are used by the BI OS for

con trol and con figu ra tion. Ref er to the I/O map in Ap pen dix A for port us age to avoid con f licts when

add ing ex ter nal I/O de vices.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 1

WinSystems - "The Embedded Systems Authority"

2.3 CPU Speed Se lec tion

J36

1 2 3

o o o

J31

1 o

2 o

3 o

J12

1 o o 2

3 o o 4

5 o o 6

J14

1 o

2 o

3 o

The LBC- Plus uses a Crys tal con trolled fre quency syn the sizer to con trol the CPU clock rate. The

jumper block at J12 al lows for the se lec tion of any of 8 CPU base clock fre quen cies rang ing f rom 8

MHz to 100 MHz.

The ta ble be low gives all of the pos si ble CPU clock speeds avail able by jump er ing J12.

CPU

Speed

J12

1-2

J12

3-4

J12

5-6

8 Mhz ON ON ON

16 MHz ON ON OFF

33 MHz ON OFF ON

40 MHz ON OFF OFF

50 MHz OFF ON ON

66 MHz OFF ON OFF

80 MHz OFF OFF ON

100 MHz OFF OFF OFF

NOTE : The LBC- Plus board will be jumpered at the fac tory for the rated speed of the in stalled

proc es sor. Jump er ing J12 to any speed in ex cess of the rated speed may re sult in CPU over hea t ing,

misop era tion, and pos si ble de struc tion of the CPU. Fail ures of CPUs which have been op er at ed above

their rated speed or tem pera ture are not cov ered un der the Win Sys tems stan dard prod uct war ranty.

Page 2 - 2 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

2.3.1 Clock Mul ti plier Se lect

486DX4 and 5X86 proc es sors ac tu ally run at a mul ti ple of the base os cil la tor fre quency. T he

jumper block at J36 al lows se lec tion of the mul ti plier as shown here :

J36

1 2 3

o o o

3X

J36

1 2 3

o o o

2X - 486

4X - 5X86

2.4 PCI Clock Se lect

The PCI bus clock source must be se lected us ing jumper blocks at J14 and J31. The CPUCLK

source may be se lected any time the CPU base fre quency is less than or equal to 33MHz. For any C PU

base fre quency in ex cess of 33MHz the CPUCLK/2 se lec tion must be made.

J14 J14

1 o

2 o

3 o

J31

1 o

2 o

3 o

1 o

2 o

3 o

CPUCLK

CPUCLK/2

J31

1 o

2 o

3 o

2.5 Mem ory In stal la tion

The LBC-Plus util izes user instal la ble 72- pin stan dard SIMMs. SIMM mod ules should be a

minimum speed of 70nS and X32 ar chi tec ture is pre ferred as there is no sup port for the par ity bits pro vided by X36 bit mod ules. A sin gle SIMM socket is pro vided which can sup port DRAM sizes from

1MB to 32MB.

In stal la tion is ac com plished with power off by an gling the SIMM mod ule ap proxi mately 30 de grees from ver ti cal and in sert ing the fin gers into the con nec tor (It may be nec es sary to r e move any de vice in stalled in the U27 socket. ). The SIMM mod ule is keyed slightly off- center and can not be in serted

back wards with out ex treme force. Once the fin gers are in the socket, the mod ule is then ro tat ed to the

ver ti cal un til the re tain ing clips snap into place. Re moval is the re verse pro cess. Pull th e re tain ing clips

out ward and the SIMM mod ule, once re leased, should ro tate back to an ap pro pri ate re moval an gle.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 3

WinSystems - "The Embedded Systems Authority"

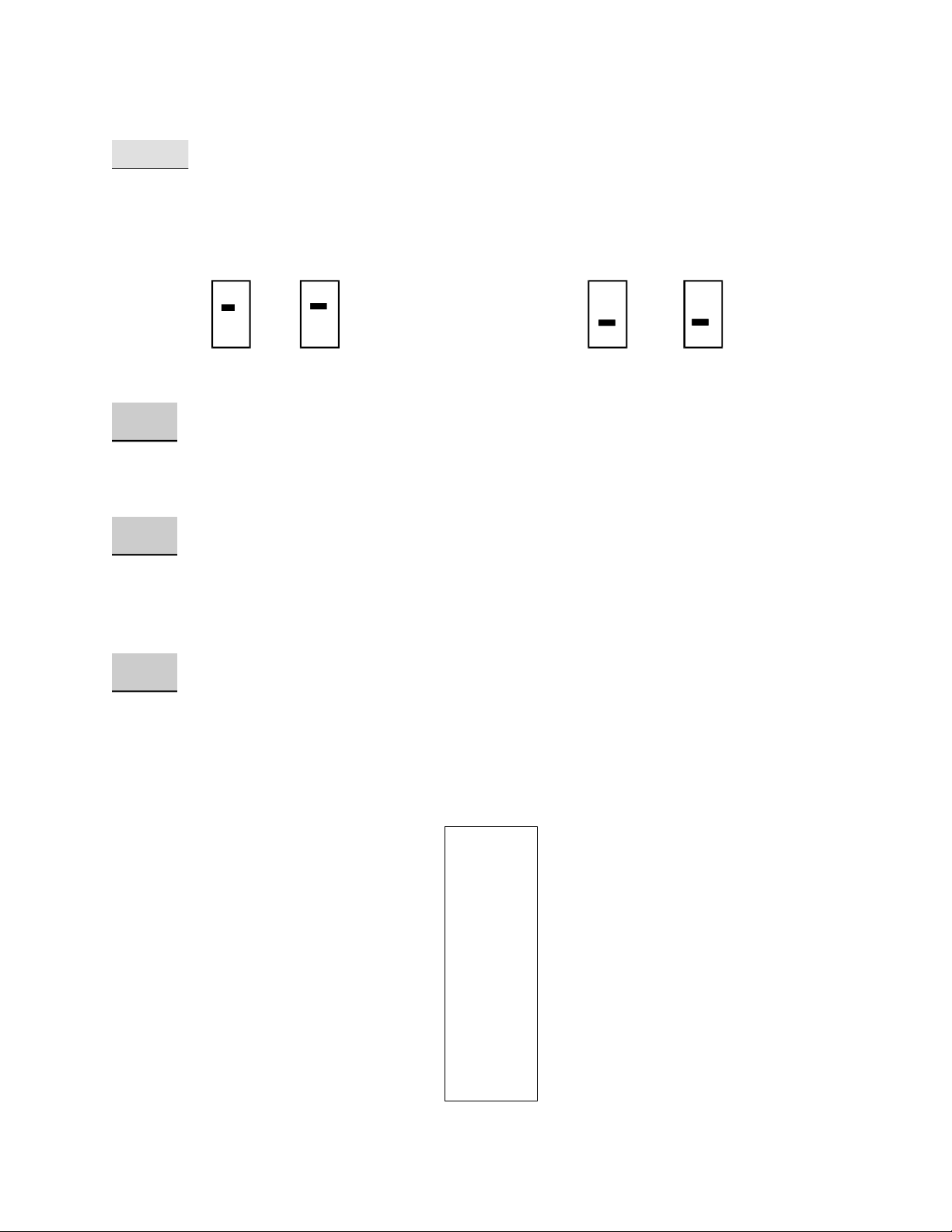

2.6 In ter rupt rout ing

J30

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

21 o o 22

All in ter rupts on the LBC-Plus are routed to their re spec tive PC/104 bus pins. On board pe riph er als,

se rial, par al lel, and disk are routed to their typi cal us age in ter rupts us ing the jumper bl ock at J30. This

block al lows dis con nect ing or re rout ing of the on board in ter rupts. The lay out for the J30 header and the

de fault jumper set tings are shown here.

J30

IDE

LPT

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

21 o o 22

IRQ9

IRQ10

IEQ11

IRQ12

IRQ15

IRQ14

IRQ7

IRQ6

IRQ5

IRQ4

IRQ3

COM4

ENET

COM3

COM4

WS16C48

FLOPPY

COM3

COM1

COM2

Page 2 - 4 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

2.7 Real Time Clock/Cal en dar

J13

1 2 3

o o o

The LBC- Plus con tains an on board Clock/Cal en dar within the ALI1487 chip. This clock is fully

com pati ble with the MC146818A used in the origi nal PC- AT com put ers. This clock has a number o f

fea tures in clud ing pe ri odic and alarm in ter rupt ca pa bili ties. In ad di tion to the time a nd date keep ing

func tions, the sys tem con figu ra tion is kept within the CMOS RAM con tained in the clock sec ti on. This

RAM holds all of the setup in for ma tion re gard ing hard and floppy disk types, video type, shad owing,

wait states, etc. Ref er to the sec tion on the AWARD BIOS Setup for what is con fig ured via the C MOS

RAM.

It may be come nec es sary at some time to make the CMOS RAM for get its cur rent con figu ra tion and

to start fresh with fac tory de faults. This may be ac com plished by re mov ing power from the boa rd . Then

re move the jumper from pins 1-2 on J13 and place on pins 2-3 for 30 seconds. Re place the jumper o n

J13 pins 1-2, power- up, and re con fig ure the CMOS set tings as de sired.

NOTE : J13 is the mas ter bat tery en able jumper. Re mov ing the jumper re moves bat tery power from

the en tire board in clud ing the SSD ar ray. Be sure that any data con tained in bat tery backed S RAM is

backed up bef ore re mov ing the bat tery jumper. J13 must be jumpered 2-3 in the clear po si tion if a bat tery is not installed.

2.8 Key board In ter face

The LBC-Plus con tains an on board PC- AT style key board con trol ler. Key board con nec tion is

made through the Multi-I/O con nec tor at J3. An adapter ca ble P/N CBL- 162-1 is avail able from W in Sys tems to make ready ac cess to all of the de vices ter mi nated at the Multi-I/O con nec tor. Us ers de sir ing

cus tom con nec tions should ref er to the Multi-I/O con nec tor pin defi ni tions given later in t his man ual.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 5

WinSystems - "The Embedded Systems Authority"

2.9 Se rial In ter face

U8

J10

U9

J11

U3

1 2 3

o o o

J8

U5

1 2 3

o o o

U4

1 2 3

o o o

U6

J9

The LBC-Plus pro vides four 16550 com pati ble RS- 232 se rial ports at the fol low ing ad dresses :

COM1 3F8H at IRQ 4

COM2 2F8H at IRQ 3

COM3 3E8H* at IRQ 5**

COM4 2E8H* at IRQ 9**

*COM ports 3 and 4 can be en abled or dis abled in di vidu ally via the jumper block at J23. When J 23

pins 1-2 are jumpered, COM3 is en abled. When J23 pins 3-4 are jumpered, COM4 is en abled.

**The in ter rupts are not dis con nected when COM3 or COM4 are dis abled. Use the in ter rupt rout ing block de scribed ear lier to dis con nect the de fault in ter rupts if de sired.

1 2 3

o o o

Page 2 - 6 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

The two pri mary se rial ports, COM1 and COM2 are con fig ur able for RS- 422, RS- 485 or J1708,

with the ad di tion of op tional driver ICs. The con figu ra tion op tions for each of the sup port ed modes are

shown on the fol low ing pages.

COM1 - RS- 232

COM1 DB9

J8 J10

1 2 3

o o o

1 2 3

o o o

U3 - In stalled

U4 - Not In stalled

U8 - Not In stalled

RX Data

TX Data

GND

CD

DTR

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

DSR

RTS

CTS

RI

COM2 - RS- 232

COM2 DB9

J9 J11

1 2 3

o o o

1 2 3

o o o

U5 - In stalled

U6 - Not In stalled

U9 - Not In stalled

RX Data

TX Data

DTR

GND

CD

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

DSR

RTS

CTS

RI

COM3/COM4 - RS- 232

COM3 and COM4 are RS- 232 only and are ter mi nated at J2. An adapter ca ble is avail able from

Win Sys tems ( P/N CBL- 173-1), which adapts J2 to two stan dard DB9M con nec tors. The pin defi ni tions for J2 are shown here :

J2

COM3 DCD

COM3 RX

COM3 TX

COM3 DTR

GND

COM4 DCD

COM4 RX

COM4 TX

COM4 DTR

GND

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 7

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

COM3 DSR

COM3 RTS

COM3 CTR

COM3 RI

N/C

COM4 DSR

COM4 RTS

COM4 CTS

COM4 RI

N.C

WinSystems - "The Embedded Systems Authority"

2.9.1 RS- 422 Mode Con figu ra tion

RS- 422 lev els are sup ported on both COM1 and COM2 with the in stal la tion of the op tional “Chi p

Kit”, Win Sys tems part number CK- 75176-2. This kit pro vides the driver ICs nec es sary for a sin gle

chan nel of RS- 422. If two chan nels of RS- 422 are re quired then two kits will be needed. RS- 42 2 is a 4 wire point-to-point full- duplex in ter face al low ing much longer ca ble runs than are pos si bl e with RS-

232. The dif fer en tial trans mit ter and re ceiver twisted pairs of fer a high de gree of noise im mu nity. RS 422 usu ally re quires the lines be ter mi nated at both ends. This ter mi na tion can be ac com p lished ei ther

on the ca ble or by in stall ing re sist ers on the board in lo ca tions re served for them. The me thod for de ter min ing the cor rect re sis tor val ues is be yond the scope of this docu ment but it is rec om men ded that trial

val ues of 100 ohms be used in all three lo ca tions at the re ceiver end. The fol low ing il lus t ra tion shows

the cor rect mode jump er ing, driver IC in stal la tion, I/O con nec tor pin defi ni tions, and te r mi na tion re sis tor lo ca tions for each of the chan nels when used in RS- 422 mode.

COM1 - RS- 422

COM1 DB9

J8 J10

1 2 3

o o o

VCC

R8

R9

R10

1 2 3

o o o

RX+

RX-

U3 - Not In stalled

U4 - In stalled

U8 - In stalled

RS- 422 NOTE : When used in RS- 422 mode,

the trans mit ter must be en abled by set ting the RTS

bit in the Mo dem Con trol Reg is ter (Bit1).

N/C

TX+

TX-

N/C

GND

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

RX+

RXN/C

N/C

Page 2 - 8 OPERATIONS MANUAL LBC-Plus 991206

COM2 - RS- 422

WinSystems - "The Embedded Systems Authority"

COM2 DB9

J9 J11

1 2 3

o o o

1 2 3

o o o

U5 - Not In stalled

U6 - In stalled

U9 - In stalled

N/C

TX+

TX-

N/C

GND

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

RX+

RXN/C

N/C

RS- 422 NOTE : When used in RS- 422 mode,

VCC

R7

RX+

R6

RX-

R3

the trans mit ter must be en abled by set ting the RTS

bit in the Mo dem Con trol Reg is ter (Bit1).

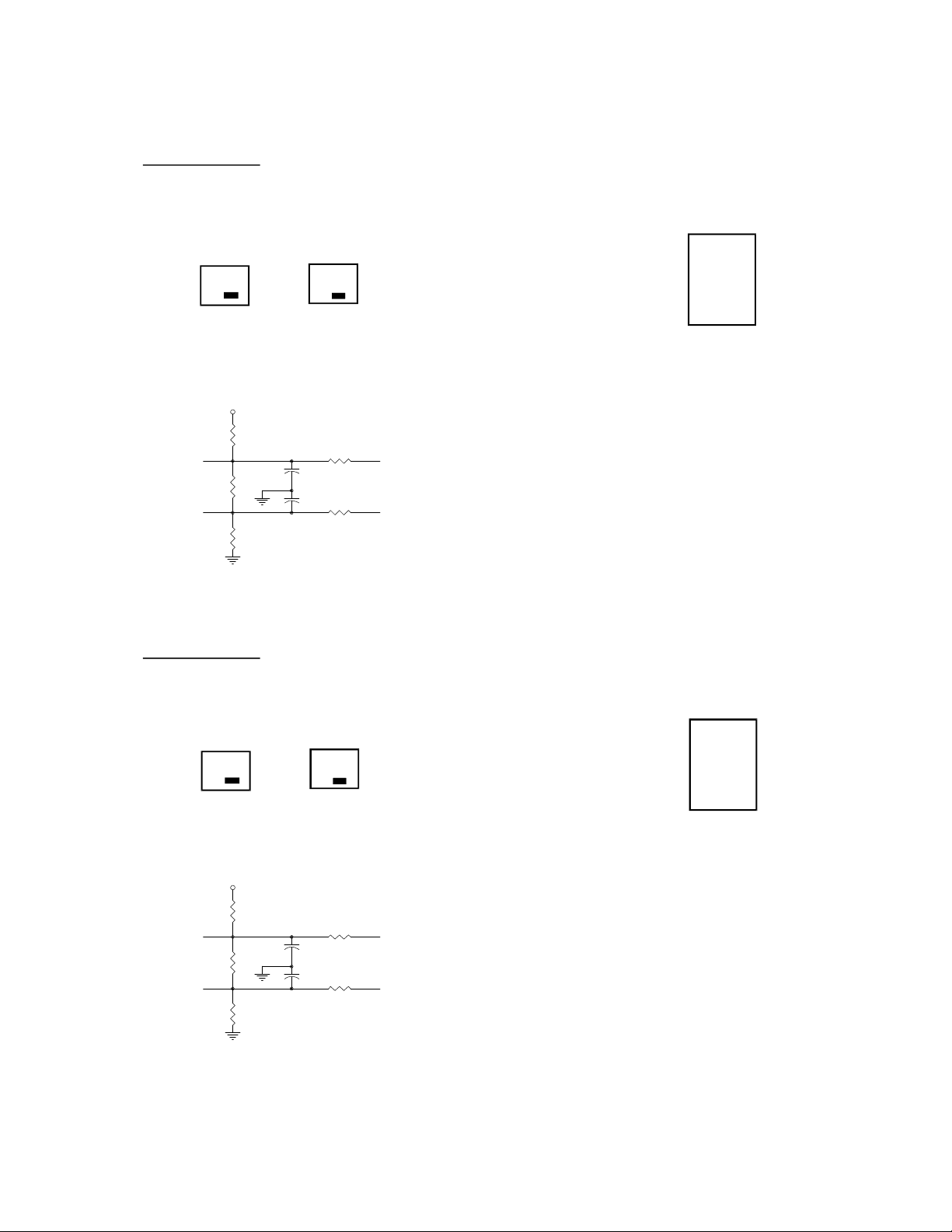

2.9.2 RS- 485 Mode Con figu ra tion

The RS- 485 Multi- drop in ter face is sup ported on both chan nels with the in stal la tion of the op tional

“Chip Kit”, Win Sys tems part number CK- 75176-2. A sin gle kit is suf fi cient to con fig ure both chan nels

for RS- 485. RS- 485 is a 2- wire multi- drop in ter face where only one sta tion at a time talks ( trans mits)

while all oth ers lis ten (re ceive). RS- 485 usu ally re quires the twisted pair be ter mi nated a t each end of

the run. The re quired ter mi na tion val ues are de pend ent upon a number of fac tors in clud ing : line im ped ance, line length, etc. A good trial value is 100 ohms in all three re sis tor lo ca tions. The fol low ing il lus tra tions show the cor rect jump er ing, driver IC in stal la tion, I/O con nec tor pin out, and te r mi na tion

re sis tor lo ca tions for each of the chan nels when used in RS- 485 mode.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 9

COM1 - RS- 485

WinSystems - "The Embedded Systems Authority"

COM1 DB9

J8 J10

1 2 3

o o o

VCC

R8

R9

R10

1 2 3

o o o

TX/RX-

TX/RX+

U3 - Not In stalled

U4 - In stalled

U8 - Not In stalled

N/C

TX/RX+

TX/RX-

N/C

GND

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

N/C

N/C

N/C

N/C

RS- 485 NOTE : Be cause RS- 485 uses a sin gle

twisted- pair, all trans mit ters are con nected in par al lel. Only one sta tion at a time may trans mit or have

its trans mit ter en abled. The trans mit ter En able/Dis able is con trolled in soft ware us ing bit 1 in the Mo dem Con trol Reg is ter (RTS). When RTS is set, the

trans mit ter is en abled, and when cleared (the nor mal

state) the trans mit ter is dis abled and the re ceiver is

en abled. Note that it is nec es sary to al low some

mini mal set tling time af ter ena bling the trans mit ter

bef ore trans mit ting the first char ac ter. Like wise, fol low ing a trans mis sion, it is nec es sary to be sure that

all char ac ters have been com pletely shifted out of

the UART (Check Bit 6 in the Line Status Reg is ter)

bef ore dis abling the trans mit ter to avoid chop ping

off the last char ac ter.

Page 2 - 10 OPERATIONS MANUAL LBC-Plus 991206

COM2 - RS- 485

WinSystems - "The Embedded Systems Authority"

COM2 DB9

J9 J11

1 2 3

o o o

VCC

R14

R15

R16

1 2 3

o o o

TX/RX-

TX/RX+

U5 - Not In stalled

U6 - In stalled

U9 - Not In stalled

N/C

TX/RX+

TX/RX-

N/C

GND

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

N/C

N/C

N/C

N/C

RS- 485 NOTE : Be cause RS- 485 uses a sin gle

twisted- pair, all trans mit ters are con nected in par al lel. Only one sta tion at a time may trans mit or have

its trans mit ter en abled. The trans mit ter En able/Dis able is con trolled in soft ware us ing bit 1 in the Mo dem Con trol Reg is ter (RTS). When RTS is set, the

trans mit ter is en abled, and when cleared (the nor mal

state) the trans mit ter is dis abled and the re ceiver is

en abled. Note that it is nec es sary to al low some

mini mal set tling time af ter ena bling the trans mit ter

bef ore trans mit ting the first char ac ter. Like wise, fol low ing a trans mis sion, it is nec es sary to be sure that

all char ac ters have been com pletely shifted out of

the UART (Check Bit 6 in the Line Status Reg is ter)

bef ore dis abling the trans mit ter to avoid chop ping

off the last char ac ter.

2.9.3 SAE J1708 Con figu ra tion

The So ci ety of Auto mo tive En gi neers (SAE) J1708 in ter face is a varia tion of the RS- 485 in ter face

which is used for “Se rial Data Com mu ni ca tions be tween Mi cro com puter Sys tems in Heavy Duty Ve hi cle Ap pli ca tions”. It is be yond the scope of this docu ment to go into de tail on the J1708 spe ci fi ca tion.

The LBC- Plus may be user con fig ured for J1708 by the ad di tion of the CK- 75176-2 “Chip Kit”. O ne

“Chip Kit” is suf fi cient to con fig ure both chan nels for J1708. The il lus tra tions that fol l ow show the cor rect jump er ing, driver IC in stal la tion, I/O con nec tor pin defi ni tions, and the ter mi na t ion net work de tails

for each of the chan nels when used in J1708 mode.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 11

COM1 - J1708

WinSystems - "The Embedded Systems Authority"

COM1 DB9

J8 J10

1 2 3

o o o

VCC

R11

4.7K

R12

Absent

R13

4.7K

COM2 - J1708

1 2 3

o o o

R1 470 OHM

C1 .0022 ufd

C2 .0022 ufd

R2 470 OHM

U3 - Not In stalled

U4 - In stalled

U8 - Not In stalled

TX/RX+

TX/RX-

N/C

TX/RX+

TX/RX-

N/C

GND

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

N/C

N/C

N/C

N/C

R14

4.7K

R15

Absent

R16

4.7K

J9 J11

1 2 3

o o o

VCC

1 2 3

o o o

R5 470 OHM

C4 .0022 ufd

C3 .0022 ufd

R4 470 OHM

U5 - Not In stalled

U6 - In stalled

U9 - Not In stalled

TX/RX+

TX/RX-

N/C

TX/RX+

TX/RX-

N/C

GND

COM2 DB9

1 o o 6

2 o o 7

3 o o 8

4 o o 9

5 o

N/C

N/C

N/C

N/C

Page 2 - 12 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

2.10 Par al lel Printer Port

J24

1 2

o o

o o

3 4

J21

1 2

o o

o o

3 4

J6

1 o o 2

3 o o 4

5 o o 6

The LBC- Plus sup ports a fully bi- directional par al lel printer port ca pa ble of EPP and ECP op era tions. The par al lel port is mapped at 278H and is ter mi nated at the Multi-I/O con nec tor J3. T he pin defi ni tions for the par al lel port DB25 con nec tor when us ing the CBL- 162-1 cable are shown be low :

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

ACK

PE

SLCT

1 o o 14

2 o o 15

3 o o 16

4 o o 17

5 o o 18

6 o o 19

7 o o 20

8 o o 21

9 o o 22

10 o o 23

11 o o 24

12 o o 25

13 o

AUTOFD

ERROR

INIT

SLIN

GND

GND

GND

GND

GND

GND

GND

GND

STROBE

BUSY

2.10.1 Par al lel Port Mode Se lec tion

The par al lel port mode is se lected via the jumper block at J6 per the fol low ing ta ble :

SPP Mode EPP Mode ECP Mode EPP/ECP Mode

J6

Jumpering

3-5

4-6

3-5

2-4

1-3

4-6

1-3

2-4

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 13

WinSystems - "The Embedded Systems Authority"

2.10.2 ECP DMA Con figu ra tion

When the par al lel port is used in an ECP con figu ra tion, the jumper blocks at J21 and J24 are u sed to

se lect the de sired DMA chan nel as shown here :

J21 J24

1 2

o o

o o

3 4

DMA Chan nel 1 DMA Chan nel 3

1 2

o o

o o

3 4

J21

1 2

o o

o o

3 4

J24

1 2

o o

o o

3 4

2.11 Speaker/Sound In ter face

The LBC- Plus util izes a high- impedance piezo type de vice for audio out put. BIOS beep codes, er ror sig nal ing, or user de fined tones can be pre sented via this de vice.

2.12 PC/104 Bus In ter face

The LBC- Plus sup ports I/O ex pan sion through the stan dard PC/104 con nec tors at J26 and J29. T he

LBC- Plus sup ports both 8- bit and 16- bit PC/104 mod ules. The PC/104 con nec tor pin defi ni tio ns are

pro vided on the fol low ing page for ref er ence pur poses.

2.13 Floppy Disk In ter face

The LBC- Plus sup ports up to 2 stan dard 3 1/2" or 5 1/4" PC com pati ble floppy disk drives. The

drives are con nected via the I/O con nec tor at J17. Note that the in ter con nect ca ble to the d rives is a stan dard floppy I/O ca ble used on desk- top PCs. The ca ble must have the twisted sec tion prior to t he drive A

po si tion. The pin defi ni tions for the J17 con nec tor are shown here :

J17

GND

1 o o 2

3 o o 4

GND

5 o o 6

GND

GND

7 o o 8

9 o o 10

GND

11 o o 12

GND

GND

13 o o 14

15 o o 16

GND

17 o o 18

GND

GND

19 o o 20

21 o o 22

GND

23 o o 24

GND

GND

25 o o 26

27 o o 28

GND

29 o o 30

GND

GND

31 o o 32

33 o o 34

GND

Page 2 - 14 OPERATIONS MANUAL LBC-Plus 991206

RPM/LC

N/C

N/C

INDEX

MTR0

DRV1

DRV0

MTR1

DIR

STEP

WDATA

WGATE

TRK0

WPRT

RDATA

HDSEL

DSKCHG

WinSystems - "The Embedded Systems Authority"

GND

RESET

+5V

IRQ9

-5V

DRQ2

-12V

0WS

+12V

GND

MEMW

MEMR

IOW

IOR

DACK3

DRQ3

DACK1

DRQ1

REFRESH

SYSCLK

IRQ7

IRQ6

IRQ5

IRQ4

IRQ3

DACK2

TC

BALE

+5V

OSC

GND

GND

J26

B1 o o A1

B2 o o A2

B3 o o A3

B4 o o A4

B5 o o A5

B6 o o A6

B7 o o A7

B8 o o A8

B9 o o A9

B10 o o A10

B11 o o A11

B12 o o A12

B13 o o A13

B14 o o A14

B15 o o A15

B16 o o A16

B17 o o A17

B18 o o A18

B19 o o A19

B20 o o A20

B21 o o A21

B22 o o A22

B23 o o A23

B24 o o A24

B25 o o A25

B26 o o A26

B27 o o A27

B28 o o A28

B29 o o A29

B30 o o A30

B31 o o A31

B32 o o A32

IOCHK

BD7

BD6

BD5

BD4

BD3

BD2

BD1

BD0

IOCHRDY

AEN

SA19

SA18

SA17

SA16

SA15

SA14

SA13

SA12

SA11

SA10

SA9

SA8

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

GND

GND

SBHE

LA23

LA22

LA21

LA20

LA19

LA18

LA17

MEMR

MEMW

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

KEY

J29

C0 o o D0

C1 o o D1

C2 o o D2

C3 o o D3

C4 o o D4

C5 o o D5

C6 o o D6

C7 o o D7

C8 o o D8

C9 o o D9

C10 o o D10

C11 o o D11

C12 o o D12

C13 o o D13

C14 o o D14

C15 o o D15

C16 o o D16

C17 o o D17

C18 o o D18

C19 o o D19

GND

MEMCS16

IOCS16

IRQ10

IRQ11

IRQ12

IRQ15

IRQ14

DACK0

DRQ0

DACK5

DRQ5

DACK6

DRQ6

DACK7

DRQ7

VCC

MASTER

GND

GND

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 15

WinSystems - "The Embedded Systems Authority"

2.14 IDE Hard Disk In ter face

The LBC-Plus sup ports stan dard IDE fixed disks through the I/O con nec tor at J18. A red ac tiv i ty

LED is pres ent at D1. The pin defi ni tions for J18 are shown here :

J18

D7

D6

D5

D4

D3

D2

D1

D0

GND

GND

IOW

IOR

N/C

N/C

A1

A0

N/C

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

21 o o 22

23 o o 24

25 o o 26

27 o o 28

29 o o 30

31 o o 32

33 o o 34

35 o o 36

37 o o 38

39 o o 40

GND

D8

D9

D10

D11

D12

D13

D14

D15

N/C

GND

GND

GND

ALE

GND

IOCS16

N/C

A2

HDCS1

GND

RESET

INTRQ

HDCS0

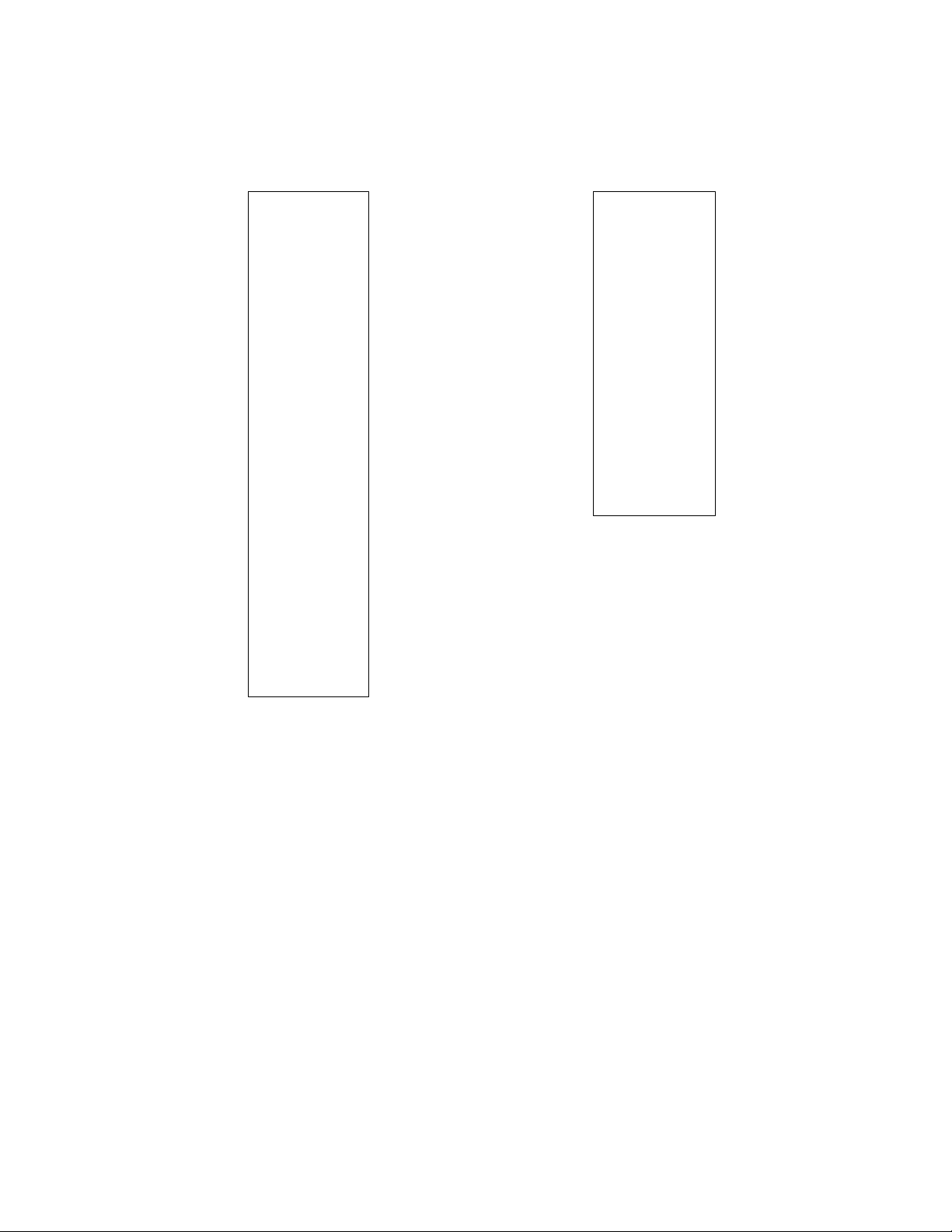

2.15 Watch dog Timer Con figu ra tion

The LBC- Plus board fea tures a power- on volt age de tect and power- down/power brown- out re set

cir cuit to pro tect mem ory and I/O from faulty CPU op era tion dur ing pe ri ods of il le gal vol t age lev els.

This su per vi sor cir cuitry also fea tures a watch dog timer which can be used to guard against s oft ware

lock ups. An in ter nal timer with a pe ri od of 1.5 sec onds will, when en abled, re set the CPU i f the watch dog has not been serv iced within the al lot ted time. There are three watch dog modes avail able o n the

LBC- Plus. With no jumper in stalled on J19, the watch dog is to tally dis abled and can never re s et the

CPU. When J19 is jumpered on pins 2-3, the watch dog cir cuit is per ma nently en abled and tim ing be gins im me di ate ly with power- on. This mode is NOT com pati ble with the AWARD BIOS or with MS DOS but is avail able for di rectly em bed ded code that takes the place of the BIOS. The watch do g must

be ac cessed every 1.5 sec onds or a re set will oc cur. Pet ting in this mode is ac com plished by writ ing to

I/O port 1EFH with any value.

An al ter nate mode of op era tion is via soft ware en able/dis able con trol. This mode is set by jump er ing J19 pins 1-2. In this mode the watch dog timer powers- up dis abled and must be en abled in sof t ware

bef ore tim ing will be gin. Ena bling is ac com plished by writ ing a 1 to I/O port 1EEH. Writ in g a 0 to I/O

port 1EEH will dis able the watch dog. Af ter ena bling, pet ting may be ac com plished by writ ing any

value to I/O port 1EFH at least every 1.5 sec onds or a re set will oc cur. This mode of op era tio n can be

used with the BIOS or DOS pro vided that the watch dog is dis abled bef ore mak ing any ex ten sive BIOS

or DOS calls, es pe cially video or Disk IO calls which could ex ceed the 1.5 sec onds al lowed. Th e draw -

Page 2 - 16 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

back to this mode is that a lockup dur ing the time the watch dog is dis abled will not al low for auto recovery and will re quire an ex ter nal re set.

J13

1 2 3

o o o

J19

1 2 3

o o o

2.16 Status LED

A green LED is popu lated on the board at D2 which can be used for any ap pli ca tion spe cific pur pose. The LED can be turned on in soft ware by writ ing a 1 to I/O port 1EDH. The LED can be turned off

by writ ing a 0 to 1EDH.

2.17 Bat tery Se lect Con trol

An on board 200mAh nomi nal ca pac ity, lith ium coin- cell bat tery is pro vided for the CMOS

Clock/Cal en dar and for bat tery backing- up Solid State Disk SRAMs. A mas ter bat tery en able j umper is

pro vided at J13. When J13 is jumpered pins 1-2, bat tery power is sup plied to the Clock/Cal en da r and to

the in di vid ual jumper blocks for bat tery backup of SSD SRAMs. When J13 is jumpered pins 2-3, th e

bat tery is to tally dis con nected and no cur rent will be drawn from it. Bat tery life is highly de pend ent

upon duty cy cle as there is no cur rent drawn from the bat tery when +5 volts is ap plied to the b oard. Both

stor age and op era tional tem pera tures play a promi nent fac tor in bat tery life. High tem pera tures will

shorten bat tery life sig nifi cantly. J13 must be jumpered 2-3 in the clear po si tion if a bat te ry is not

installed.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 17

WinSystems - "The Embedded Systems Authority"

2.18 Power/Re set Con nec tion

Power is sup plied to the LBC-Plus via the con nec tor at J7. The pin defi ni tions for J7 are give n be low. An op tional normally- open push- button- reset switch may also be con nected to J7 be tween P BRE SET* and ground.

J7

8 o

7 o

6 o

5 o

4 o

3 o

2 o

1 o

PBRESET*

GND

GND

GND

+5V

+5V

+12V

-12V

2.19 Sili con Disk Con figu ra tion

J38

2 4 6 8 10

o o o o o

o o o o o

1 3 5 7 9

J40

1 o

2 o

3 o

J34

1 o

2 o

3 o

J16

1 o

J39

2 4 6 8 10

o o o o o

o o o o o

1 3 5 7 9

2 o

3 o

J25

1 o

2 o

The LBC- Plus sup ports the use of EPROM, PEROM (Flash), SRAM, and the M- Systems Disk On Chip (DOC) de vices to be used as Solid State Disk (SSD) drives. Sec tion 4 of this man ual pro vi des the

nec es sary in for ma tion for the gen era tion and us age of the Sili con drives. This sec tion do cu ments the re quired hard ware con figu ra tions for the vari ous type of de vices. Two 32- pin JE DEC mem ory so ck ets at

U27 and U23 are used to con tain the RAM, ROM,Flash, or DOC de vices used for the disk. The sili co n

Page 2 - 18 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

disk ar ray is mem ory mapped into a 16k byte hole at seg ment E400H and has an I/O con trol reg i s ter at

1ECH.

2.19.1 Sili con Disk Mode

There are two ba sic modes of Sili con Disk op era tion on the LBC- Plus. The first uses the on boa rd

BIOS ex ten sion and sup ports the use of 512K or 1M EPROMS, 512K SRAMS, or 512K AT MEL Flash

De vices. The sec ond mode uses the M- Systems Disk On Chip de vice. The mode is con trolled via th e

jumper block at J25 as shown here :

J25

1 o

2 o

DOC Mode

J25

1 o

2 o

SSD Mode

NOTE : Jump er ing for DOC mode with EPROMs, RAMs, of Flash de vices in stalled ef fec tively

acts as a dis able to the Solid State Disk and simi larly when a DOC de vice is in stalled and the jumper is

se lected for stan dard de vices the DOC is dis abled.

IM POR TANT NOTE : To in sure Win dows 95 com pati bil ity, J25 must be jumpered 1-2.

2.19.2 De vice Size Se lec tion

The on board Solid State Disk ar ray sup ports ei ther 512K EPROMs, SRAMs or FLASH de vice or

1M EPROM de vices. The de vice size se lec tion is made at J16 as shown here :

J16

1 o

2 o

3 o

J16

1 o

2 o

3 o

512K or DOC Device

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 19

1M Devices

WinSystems - "The Embedded Systems Authority"

2.19.3 De vice Type Se lec tion

Each of the de vices in the ar ray has an in di vid ual de vice type jumper block at the de vice so cket. J39

sets the de vice type for U27 and J38 sets the de vice type for U23. The sup ported de vice type ju mp er ings

are shown here :

2 4 6 8 10

o o o o o

o o o o o

1 3 5 7 9

512K X 8

SRAM

2 4 6 8 10

o o o o o

o o o o o

1 3 5 7 9

512K X 8

EPROM

2 4 6 8 10

o o o o o

o o o o o

1 3 5 7 9

512K X 8

PEROM

2 4 6 8 10

o o o o o

o o o o o

1 3 5 7 9

1 MEG X 8

EPROM

2 4 6 8 10

o o o o o

o o o o o

1 3 5 7 9

DOC

DEVICE

2.19.4 Bat tery Backup Se lec tion

When us ing SRAM de vices and non vola tile op era tion is de sired, bat tery backup can be se lect ed on

a socket- by- socket ba sis. J40 for U27 and J34 for U23. The il lus tra tion be low shows the jump er ing for

bat tery backup or stan dard op era tion.

1 o

2 o

3 o

Bat tery Backup

Enabled

1 o

2 o

3 o

Bat tery Backup

Disabled

NOTE : Hav ing the jumper(s) se lected for bat tery backup when us ing other than low- power standby SRAMs (such as with EPROMs, or PEROMs) will re sult in the quick drain ing of the on board

bat tery.

2.19.5 Sili con Disk Notes

1. When in stall ing de vices, U27 is the first de vice in the ar ray and must al ways con tain the first de -

vice of a boota ble disk.

2. The Disk On Chip op tion must use the socket at U23. When a DOC is in stalled, U27 is avail abl e

as a Sec ondary Sili con Disk de vice. See sec tion 4.4 for more in for ma tion.

Page 2 - 20 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

2.20 Par al lel I/O

The LBC-Plus util izes the Win Sys tems WS16C48 ASIC high- density I/O chip mapped at a base

ad dress of 120H. The first 24 lines are ca pa ble of fully latched event sens ing with sense po la r ity be ing

soft ware pro gram ma ble. Two 50- pin con nec tors al low for easy mat ing with in dus try stan da rd I/O

racks.

J1

1 o

2 o

J15

1 o

2 o

2.20.1 Par al lel I/O En able

The par al lel fea tures of the LBC- Plus can be en abled or dis abled us ing the jumper block at J 15.

When J15 is jumpered the par al lel I/O is en abled at I/O ad dress 120H. When J15 is open the 16 a d dresses start ing at I/O ad dress 120H are free for use by other de vices.

2.20.2 Par al lel I/O Con nec tors

The 48 lines of par al lel I/O are ter mi nated through two 50- pin con nec tors at J4 and J5. The J4 con nec tor han dles I/O ports 0-2 while J5 han dles ports 3-5. The pin defi ni tions for J4 and J5 are shown on

the fol low ing page.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 21

WinSystems - "The Embedded Systems Authority"

Port 2 Bit 7

Port 2 Bit 6

Port 2 Bit 5

Port 2 Bit 4

Port 2 Bit 3

Port 2 Bit 2

Port 2 Bit 1

Port 2 Bit 0

Port 1 Bit 7

Port 1 Bit 6

Port 1 Bit 5

Port 1 Bit 4

Port 1 Bit 3

Port 1 Bit 2

Port 1 Bit 1

Port 1 Bit 0

Port 0 Bit 7

Port 0 Bit 6

Port 0 Bit 5

Port 0 Bit 4

Port 0 Bit 3

Port 0 Bit 2

Port 0 Bit 1

Port 0 Bit 0

+5V

J4

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

21 o o 22

23 o o 24

25 o o 26

27 o o 28

29 o o 30

31 o o 32

33 o o 34

35 o o 36

37 o o 38

39 o o 40

41 o o 42

43 o o 44

45 o o 46

47 o o 48

49 o o 50

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

Port 5 Bit 7

Port 5 Bit 6

Port 5 Bit 5

Port 5 Bit 4

Port 5 Bit 3

Port 5 Bit 2

Port 5 Bit 1

Port 5 Bit 0

Port 4 Bit 7

Port 4 Bit 6

Port 4 Bit 5

Port 4 Bit 4

Port 4 Bit 3

Port 4 Bit 2

Port 4 Bit 1

Port 4 Bit 0

Port 3 Bit 7

Port 3 Bit 6

Port 3 Bit 5

Port 3 Bit 4

Port 3 Bit 3

Port 3 Bit 2

Port 3 Bit 1

Port 3 Bit 0

+5V

J5

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

21 o o 22

23 o o 24

25 o o 26

27 o o 28

29 o o 30

31 o o 32

33 o o 34

35 o o 36

37 o o 38

39 o o 40

41 o o 42

43 o o 44

45 o o 46

47 o o 48

49 o o 50

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2.20.3 Par al lel I/O VCC En able

The I/O con nec tors can pro vide +5 volts to an I/O rack or for mis cel la ne ous pur poses by jum p er ing

J1. When J1 is jumpered +5 volts is pro vided at pin 49 of both J4 and J5. It the user's re spon s i bil ity to

limit cur rent to a safe value (less than 1A) to avoid dam ag ing the CPU board.

2.20.4 WS16C48 Reg is ter Defi ni tions

The LBC- Plus uses the Win Sys tems’ ex clu sive ASIC de vice, the WS16C48. This de vice pro vides

48 lines of digi tal I/O. There are 17 unique reg is ters within the WS16C48. The fol low ing ta b le sum ma rizes the reg is ters and the text that fol lows pro vides de tails on each of the in ter nal reg i s ters.

Page 2 - 22 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

I/O Ad dress

Offset

Page 0 Page 1 Page 2 Page 3

00H Port 0 I/O Port 0 I/O Port 0 I/O Port 0 I/O

01H Port 1 I/O Port 1 I/O Port 1 I/O Port 1 I/O

02H Port 2 I/O Port 2 I/O Port 2 I/O Port 2 I/O

03H Port 3 I/O Port 3 I/O Port 3 I/O Port 3 I/O

04H Port 4 I/O Port 4 I/O Port 4 I/O Port 4 I/O

05H Port 5 I/O Port 5 I/O Port 5 I/O Port 5 I/O

06H Int_Pending Int_Pending Int_Pending Int_Pending

07H Page/Lock Page/Lock Page/Lock Page/Lock

08H N/A Pol_0 Enab_0 Int_ID0

09H N/A Pol_1 Enab_1 Int_ID1

0AH N/A Pol_2 Enab_2 Int_ID2

Reg is ter De tails

Port 0-5 I/O - Each I/O bit in each of the 6 ports can be in di vidu ally pro grammed for in put or out -

put. Writ ing a '0' to a bit po si tion causes the cor re spond ing out put pin to go to a High- Im pedance state

(pulled high by ex ter nal 10K ohm re sis tors). This al lows it to be used as an in put. When used in the in put

mode, a read re flects the in verted state of the I/O pin, such that a high on the pin will read as a '0' in the

reg is ter. Writ ing a '1' to a bit po si tion causes the out put pin to sink cur rent (up to 12mA) , ef fec tively

pull ing it low.

INT_PEND ING - This read- only reg is ter re flects the com bined state of the INT_ID0 through

INT_ID2 reg is ters. When any of the lower 3 bits are set, it in di cates that an in ter rupt is pe nd ing on the

I/O port cor re spond ing to the bit po si tion(s) that are set. Read ing this reg is ter al lows a n In ter rupt Serv ice Rou tine to quickly de ter mine if any in ter rupts are pend ing and which I/O port has a pend ing in ter rupt.

PAGE/LOCK - This reg is ter serves two pur poses. The up per two bits se lect the reg is ter page in use

as shown here :

D7 D6 Page

0 0 Page 0

0 1 Page 1

1 0 Page 2

1 1 Page 3

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 23

WinSystems - "The Embedded Systems Authority"

Bits 5-0 al low for lock ing the I/O ports. A '1' writ ten to the I/O port po si tion will pro hibi t fur ther

writes to the cor re spond ing I/O port.

POL0- POL2 - These reg is ters are ac ces si ble when page 1 is se lected. They al low in ter rupt po lar ity

se lec tion on a port- by- port and bit- by- bit ba sis. Writ ing a '1' to a bit po si tion se lect s the ris ing edge de tec tion in ter rupts while writ ing a '0' to a bit po si tion se lects fal ling edge de tec tion i n ter rupts.

ENAB0- ENAB2 - These reg is ters are ac ces si ble when page 2 is se lected. They al low for port- by port and bit- by- bit ena bling of the edge de tec tion in ter rupts. When set to a '1' the edge d e tec tion in ter rupt is en abled for the cor re spond ing port and bit. When cleared to a '0' the bit's edge de tec tion in ter rupt

is dis abled. Note that this reg is ter can be used to in di vidu ally clear a pend ing in ter rupt by dis abling and

reena bling the pend ing in ter rupt.

INT_ID0 - INT_ID2 - These reg is ters are ac ces si ble when page 3 is se lected. They are used to

iden tify cur rently pend ing edge in ter rupts. A bit when read as a '1' in di cates that an edge of the po lar ity

pro grammed into the cor re spond ing po lar ity reg is ter has been rec og nized. Note that a writ e to this reg is ter (value ig nored) clears ALL of the pend ing in ter rupts in this reg is ter.

2.21 VGA Con figu ra tion

J20

1 2

o o

o o

3 4

Page 2 - 24 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

2.21.1 In tro duc tion

The LBC- Plus uses a third gen era tion CRT/Flat panel VGA con trol ler. It sup ports stan dard VGA

out put as well as a va ri ety of Flat Panel Dis plays us ing op tional Flat Panel Adapter (FPA) mo d ules. The

video on the LBC-Plus uses the Chips and Tech nolo gies 6554X se ries of high per form ance VGA co n trol lers. The C&T con trol ler sup ports stan dard and Super- VGA modes as well as Color and Mono chrome pan els with 8,9,12,15,16,18, and 24- bit in ter faces. Win Sys tems pro vides flat panel su p port

through a se ries of FPA (Flat Panel Adapter) mod ules. Con tact your Win Sys tems Ap pli ca tions En gi neer for the most cur rent list of avail able FPAs and sup ported pan els.

De tails re gard ing in ter fac ing to spe cific Flat Pan els is not pro vided in this man ual but should be ref er enced in the docu men ta tion ac com pa ny ing the FPA mod ule. At tempted con nec tion to any f lat panel

not di rectly sup ported by a Win Sys tems FPA mod ule is at the user's risk and ex treme care shou ld be ex er cised to avoid dam ag ing or de stroy ing the panel.

HAZ ARD WARN ING : LCD pan els can re quire a high volt age for the panel back light. This high frequency volt age can ex ceed 1000 volts and can pres ent a shock haz ard. Care should be taken w hen

wir ing or han dling the inverter out put. To avoid dan ger of shock and to avoid dam ag ing frag i le and ex pen sive pan els, make all con nec tion changes with power re moved.

2.21.2 VGA BIOS ROM Type Se lec tion

The LBC- Plus comes stan dard with a video BIOS ex pan sion ROM popu lated at U15. Vari ous

ROM sizes can be used to sup port a va ri ety of flat panel con figu ra tions each need ing its own BIOS im age. The FPA adapter mod ules, when con nected to J33, auto mati cally se lect the cor rect BIOS im age for

the panel fam ily the FPA sup ports. The fac tory will or di nar ily con fig ure the BIOS ROM for t he size

pro vided but the il lus tra tion be low shows the proper jump er ing of J20 for the sup ported RO M sizes.

J20

1 2

o o

o o

3 4

27C010

27C020

27C040

J20

1 2

o o

o o

3 4

27C080

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 25

WinSystems - "The Embedded Systems Authority"

2.21.3 CRT Out put Con nec tion

Video out put to a stan dard VGA moni tor is made via the con nec tor at J27. An adapter ca ble par t

number CBL- 207-1 is avail able from Win Sys tems to adapt from J27 to the stan dard DB15 VGA con nec tor. The pin defi ni tions for the J27 con nec tor are shown here :

J27

RED

GREEN

BLUE

HSYNC

VSYNC

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

GND

GND

GND

GND

GND

2.21.4 Flat Panel Out put Con nec tion

Con nec tion to all flat pan els is made via the 50- pin con nec tor at J33. This con nec tor is ca bled to the

ap pro pri ate FPA (Flat Panel Adapter) mod ule which then breaks out the nec es sary ca bling fo r at tach ment to the panel it self. The FPA mod ule also sup plies any spe cial con trols that may be needed for the

panel. Ref er to the FPA docu men ta tion for spe cific hook- up in struc tions. The pin defi ni ti ons for J33 are

shown here :

SW0

SW2

P23

P21

P19

GND

P17

P15

P13

GND

P11

P9

P7

GND

P5

P3

P1

GND

SHFCLK

FLM

ENVCC

ENVEE

PVS

+12V

VCC

J33

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

21 o o 22

23 o o 24

25 o o 26

27 o o 28

29 o o 30

31 o o 32

33 o o 34

35 o o 36

37 o o 38

39 o o 40

41 o o 42

43 o o 44

45 o o 46

47 o o 48

49 o o 50

SW1

SW3

P22

P20

P18

GND

P16

P14

P12

GND

P10

P8

P6

GND

P4

P2

P0

GND

LP

M

ENBKL

PHS

-12V

+12V

VCC

Page 2 - 26 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

2.21.5 Video Mode Ta bles

The LBC- Plus video sec tion sup ports a number of stan dard and ex tended VGA modes. The fol low ing ta bles ex tracted from the C&T 65540/65545 da ta book show the video modes along with the re quired amount of RAM.

Stan dard Video Modes - VGA Stan dard

Mode

(Hex)

0+, 1+ Text

2+, 3+ Text 16

7+ Text Mono

10 Planar 16 80 X 25 8 X 14 640 X 350 25.175 31.5 70 256KB A,B,C

11 Planar 2 80 X 30 8 X 16 640 X 480 25/175 31.5 60 256KB A,B,C

12 Planar 16 80 X 30 8 X 16 640 X 480 25.175 31.5 60 256KB A,B,C

13

Dis play

#

Mode

Col ors

16

4 Graph ics 4 40 X 25 8 X 8 320 X 200 25.175 31.5 70 256KB A,B,C

5 Graphics 4 40 X 25 8 X 8 320 X 200 15.175 31.5 70 256KB A,B,C

6 Graphics 2 80 X 25 8 X 8 640 X 200 25.175 31.5 70 256KB A,B,C

D Planar 16 40 X 25 8 X 8 320 X 200 25.175 31.5 70 256KB A,B,C

E Planar 16 80 X 25 8 X 8 640 X 200 25.175 31.5 70 256KB A,B,C

F Planar Mono 80 X 25 8 X 14 640 X 350 25.175 31.5 70 256KB A,B,C

Packed

Pixel

256 40 X 25 8 X 8 320 X 200 25.175 31.5 70 256KB A,B,C

Text

Dis play

40 X 25

40 X 25

40 X 25

80 X 25

80 X 25

80 X 25

80 X25

80 X 25

80 X 25

Font

Size

9 X 16

8 X 14

8 X 8

9 X 16

8 X 14

8 X 8

9 X 16

9 X 14

9 X 8

Pixel

Reso lu tion

360 X 400

320 X 350

320 X 200

720 X 400

640 X 350

620 X 200

720 X 400

720 X 350

720 X 350

Dot

Clock

(MHz)

28.322

25.175

25.175

28.322

25.175

25.175

28.322 31.5 70 256KB A,B,C

Hori zon tal

Fre quency

(KHz)

31.5 70 256KB A,B,C

31.5 70 256KB A,B,C

Ver ti cal

Fre quency

(Hz)

Video

Memory

CODE

CRT

CRT Codes

A - PS/2 Fixed Frequency analog CRT or equivalent (31.5/35.5 Khz Horizontal Frequency Specification )

B - Multi-Frequency CRT Monitor (37.5 Khz minimum Horizontal Frequency Specification) (NEC MultiSyn c 3D or equivalent)

C - Multi-Frequency High-Performance CRT Monitor (48.5 KHZ minimum Horizontal Frequency Specificati on) MultiSyc 5D or equivalent

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 27

WinSystems - "The Embedded Systems Authority"

Ex tended Reso lu tion Modes

Mode

#

(Hex)

Dis play

Mode

Col ors

Text

Dis play

Font

Size

Pixel

Reso lu tion

Dot

Clock

(MHz)

Hori zon tal

Fre quency

(KHz)

Ver ti cal

Fre quency

(Hz)

Video

Memory

CRT

CODE

20 4- Bit Linear 16 80 X 30 8 X 16 640 X 480 25.175 31.5 60 512KB A,B,C

22 4- Bit Linear 16 100 X 37 8 X 16 800 X 600 40.00 37.5 60 512KB B,C

24 4- Bit Linear 16 128 X 48 8 X 16

1024 X

768

65.00 48.5 60 512KB C

24I 44.90 35.5 43 512KB B,C

30 8- Bit Linear 256 80 X 30 8 X 16 640 X 480 25/175 31.5 60 512K A,B,C

32 8- Bit Linear 256 100 X 37 8 X 16 800 X 600 40.00 37.5 60 512KB B,C

34 8- Bit Linear 256 128 X 48 8 X 16

1024 X

768

65.00 48.5 60 1MB C

34I 44.90 35.5 43 1MB B,C

40 16- Bit Linear 32K 80 X 30 8 X 16 640 X 480 50.350 31.5 60 1MB A,B,C

41 16- Bit Linear 64K 80 X 30 8 X 16 640 X 480 50.350 31.5 60 1MB A,B,C

50 24- Bit Linear 16M 80 X 30 8 X 16 640 X 480 65.00 27.1 51.6 1MB B.C

60 Text 16 132 X 25 8 X 16

61 Text 16 132 X 50 8 X 16

1056 X

400

1056 X

400

40.00 30.5 68 256KB A,B,C

40.00 30.5 68 256KB A,B,C

6A,70 Planar 16 100 X 37 8 X 16 800 X 600 40.00 38.0 60 256KB B,C

72,75 Planar 16 128 X 48 8 X 16

1024 X

768

65.00 48.5 60 512KB C

72,75I 44.90 35.5 43 512KB B,C

78 Packed Pixel 16 80 X 25 8 X 16 640 X 400 25.175 31.5 70 256KB A,B,C

79 Packed Pixel 256 80 X 30 8 X 16 640 X 480 25.175 31.5 60 512KB A,B,C

7C Packed Pixel 256 100 X 37 8 X 16 800 X 600 40.00 37.5 60 512KB B,C

7E Packed Pixel 256 128 X 48 8 X 16

1024 X

768

65.00 48.5

60

1MB C

7EI Packed Pixel 44.90 35.5 43 1MB B,C

Support for the modes above is included directly in the BIOS. The ‘I’ in the mode # column indicate s “interlaced”

CRT Codes

A - PS/2 Fixed fre quency ana log CRT or equiva lent (31.5/35.5 Khz Hori zon tal Fre quency Speci f i ca tion)

B - Multi-Frequency CRT Monitor (37.5 Khz minimum Horizontal Frequency Specification) (NEC MultiSyn c 3D or equivalent)

C - Multi-Frequency High-Performance CRT Monitor (48.5 KHZ minimum Horizontal Frequency Specificati on) MultiSyc 5D or equivalent

Page 2 - 28 OPERATIONS MANUAL LBC-Plus 991206

High Re fresh Modes

WinSystems - "The Embedded Systems Authority"

Mode

#

(Hex)

12 Planar 16 80 X 30 8 X 16 640 X 480 31.50 37.5 75 256KB B,C

30 8- Bit Linear 256 80 X 30 8 X 16 640 X 480 31.50 37.5 75 256KB C

79 Packed Pixel 256 80 X 30 8 X 16 640 X 480 31.50 37.5 75 512KB C

6A,70 Planar 16 100 X 37 8 X 16 800 X 600 49.50 46.9 75 512KB C

32 8- Bit Linear 256 100 X 37 8 X 16 800 X 600 49.50 46.9 75 1MB C

7C Packed Pixel 256 100 X 37 8 X 16 800 X 600 49.50 46.9 75 1MB C

Dis play

Mode

Col ors

Text

Dis play

Font

Size

Pixel

Reso lu tion

Dot

Clock

(MHz)

Hori zon tal

Fre quency

(KHz)

Ver ti cal

Fre quency

(Hz)

Video

Memory

CRT

CODE

2.22 Eth er net Con figu ra tion

The Eth er net sec tion of the LBC- Plus uses the Na tional 83905 AT/LAN TIC Lo cal Area Net work

Twisted- Pair In ter face con trol ler. The AT/LAN TIC con trol ler is a CMOS/VLSI de vice used in the im ple men ta tion of CSMA/CD lo cal area net works. Sup ported net work in ter faces in clude 10BASE5 or

10BASE2 via an ex ter nal trans ceiver con nected to the AUI port, and twisted pair Eth er net (10B ASE-T)

us ing the on board trans ceiver. The AT/LAN TIC pro vides the Eth er net Me dia Ac cess Con trol ( MAC),

Encode- Decode (EN DEC) with an AUI in ter face, and 10BASE-T trans ceiver func tions in ac cor dan ce

with IEEE 802.3 stan dards.

This func tional block in cor po rates the re ceiver, trans mit ter, col li sion heart beat. loop b ack jab ber,

and link in teg rity blocks as de fined in the stan dard. The trans ceiver when com bined with the equali za tion re sis tors, trans mit/re ceive fil ters, and pulse trans form ers pro vide a com plete physi cal in ter face

from the AT/LAN TIC Con trol ler EN DEC mod ule and the twisted- pair me dium.

The in te grated EN DEC mod ule al lows the Man ches ter en cod ing and de cod ing via a dif fer en tial

trans ceiver and phase- lock- loop de coder at 10 Mbit/sec. Also in cluded are a col li sion de tec t trans la tor

and di ag nos tic loop back ca pa bil ity. The EN DEC mod ule in ter faces di rectly to the trans c eiver mod ule

and pro vides full IEEE com pli ant AUI (At tach ment Unit In ter face) for con nec tion to other m e dia trans ceiv ers.

The Me dia Ac cess Con trol (MAC) func tion is pro vided by the Net work In ter face Con trol (NIC)

mod ule which pro vides sim ple and ef fi cient packet trans mis sion and re cep tion con trol by m eans of off chip mem ory which can be ac cessed ei ther through an I/O port or mapped into the sys tem mem ory map.

An on board EPROM holds the Eth er net Ad dress and op tional con figu ra tion in for ma tion. This al lows for “jumper less” con figu ra tion us ing soft ware to con fig ure the board for its op er at ing mode, me dia type, I/O ad dress, in ter rupt, etc.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 29

WinSystems - "The Embedded Systems Authority"

J35

1 o o 2

3 o o 4

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

J32

1 2

o o

2.22.1 Jumpered vs. Jumper less Mode

The Eth er net sec tion can be con fig ured ei ther through the jumper block at J35 (de scribed lat er) or

via the con figu ra tion in for ma tion stored in the on board EE PROM. The source for the con figu ra tion in for ma tion is se lected via the jumper at J32 as shown here :

J32

1 2

o o

Jumpered Mode

Jumperless Mode

J32

1 2

o o

NOTE : The choice of “jumpered” or “jumper less” is to tally ex clu sive. This means that if

“jumper less” mode is se lected, all of the jump ers on J35 are ig nored and the con figu ra tion i n for ma tion

comes to tally from the EE PROM. Simi larly if “jumpered” mode is se lected the in for ma tion in t he EE PROM (ex cept for the Eth er net Ad dress) is ig nored.

IM POR TANT NOTE : In ter rupts must AL WAYS be jumpered manu ally via the jumper block at

J30 (Sec tion 1.6) which matches the “jumpered” or “jumper less” in ter rupt selection.

Page 2 - 30 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

The fol low ing sec tions de tail the J35 jump er ing when the “jumpered” mode is se lected.

2.22.2 I/O Port Se lec tion

The NE2000 sec tion of the LBC-Plus uses 32 con secu tive I/O ad dresses in the CPU’s I/O space.

The base ad dress is se lected us ing three pins on the J35 con figu ra tion jumper. The choices av ail able

are:

240H

280H

2C0H

300H

320H

340H

360H

None

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

300H

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

2C0H 320H 340H 360H

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

NONE 240H 280H

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

J35

.

.

11 o o 12

13 o o 14

15 o o 16

17 o o 18

19 o o 20

The proper jump er ing for each of these choices is shown in the fol low ing il lus tra tions.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 31

WinSystems - "The Embedded Systems Authority"

2.22.3 In ter rupt Se lec tion

The NE2000 sec tion needs an in ter rupt line for sig nal ing vari ous con di tions to the soft war e driver.

There are 8 pos si ble choices as shown here :

IRQ 3

IRQ 4

IRQ 5

IRQ 9

IRQ 10

IRQ 11

IRQ 12

IRQ 15

The proper jump er ing for the three rele vant jumper po si tions cor re spond ing to the avail abl e in ter rupt choices are shown here :

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ3

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ10

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ4

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ11

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ5

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ12

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ9

J35

.

.

5 o o 6

7 o o 8

9 o o 10

11 o o 12

13 o o 14

.

.

IRQ15

Page 2 - 32 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

2.22.4 I/O vs. Shared Mem ory Mode

The Eth er net buffer RAM can be ac cessed in ei ther of 2 ways. In the typi cal NE2000 com pati bl e

mode, the RAM is ac cessed through the NIC via I/O ports. An al ter nate ac cess scheme is avail ab le us ing the shared mem ory mode. In this mode it is soft ware com pati ble with the WD8013EBT from Stan dard Mi cro sys tems (for merly West ern Digi tal). In this mode a 32K win dow in the PC adapter sp ace is

used to ac cess packet mem ory. The ad dress of this win dow is con trolled by the driver. For NE20 00

com pati bil ity the I/O mode should be se lected. The jump er ing for each of the ac cess modes i s shown

be low :

J35

.

.

3 o o 4

5 o o 6

7 o o 8

.

.

I/O Mode

Shared Mem ory Mode

J35

.

.

3 o o 4

5 o o 6

7 o o 8

.

.

2.22.5 Me dia Type Se lec tion

The me dia type is also jumper se lecta ble via 2 pins on J35. The avail able choices are :

Twisted- pair 10BASE-T J22

Thin Eth er net Coax

AUI2 J28

Twisted- pair 10BASE-T Re duced Squelch

1

3

The J35 jump er ing for each of the op tions is shown be low.

J35

1 o o 2

3 o o 4

5 o o 6

.

10 BASE-T THIN ETHERNET

J35

1 o o 2

3 o o 4

5 o o 6

.

J35

1 o o 2

3 o o 4

5 o o 6

.

.

1

AUI Non- Spec 10 BASE-T

1 o o 2

3 o o 4

5 o o 6

.

.

J35

2

1

The thin Eth er net mode is not us able with the LBC- Plus. If thin Eth er net is re quired, it is nec es sary

to se lect the AUI mode and use an ex ter nal trans ceiver.

2

The AUI is con nected via J28. An adapter ca ble, WinSystems part number CBL- 147-1, is avail -

able which ter mi nates in a stan dard DB15 con nec tor.

3

The non- spec twisted- pair mode with re duced squelch lev els al lows the use of longer ca ble len gths

than speci fied in the twisted- pair speci fi ca tion, or the use of ca ble with higher losses.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 33

WinSystems - "The Embedded Systems Authority"

2.22.6 Com pati ble Vs. En hanced Mode

The NE2000 sec tion uses two 32K byte buffer RAMs on board. In com pati ble mode, only 8K of

each RAM (to tal of 16K) is ac ces si ble to the driver. When the En hanced mode is cho sen the ful l 32K is

avail able from each RAM. This en hanced mode is gen er ally sup ported by the sup plied AT/LAN TIC

driv ers but may not be us able with ge neric NE2000 soft ware or driv ers. When in doubt, choose t he

com pati ble mode. The J35 jump er ing for the com pati ble and en hanced modes are shown here :

J35

.

.

17 o o 18

19 o o 20

Com pati ble Mode

J35

.

.

17 o o 18

19 o o 20

En hanced Mode

2.22.7 Status LEDs

There are 4 LEDs in stalled on the LBC-Plus used to give a vis ual in di ca tion of Eth er net stat us. The

color, lo ca tion, and gen eral de scrip tion of each LED is given here :

D3 RED Col li sion

D4 GREEN Trans mit

D5 GREEN Re ceiver

D6 YEL LOW Link

2.22.8 Boot ROM Se lec tion

The LBC- Plus sup ports the use of the re mote boot fea ture avail able from NOVELL, QNX, and

some other op er at ing sys tems by al low ing pro vi sions for a user in stalled BIOS ex ten sion ROM into

U23. Only a 27C010 EPROM de vice is sup ported in this mode al though only 32K is avail able for th e

code. If the BIOS ex ten sion is sup plied in a smaller de vice it will have to be re pro grammed i nto a

27C010 de vice. In or der to use this BIOS ex ten sion, the board must be con fig ured for the DOC mode.

(See sec tion 2.19 for de tails). It is also pos si ble to se lect the ad dress where the BIOS ROM will ap pear

by con fig ur ing the SSD Socket Re lo ca tion op tion in the BIOS fea tures menu of CMOS Setup.

NOTE : The Eth er net BOOT ROM sup port and on board SSD sup port are mu tu ally ex clu sive, only

one or the other may be used. Con tact Win Sys tems for boards that sup port this fea ture.

Page 2 - 34 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

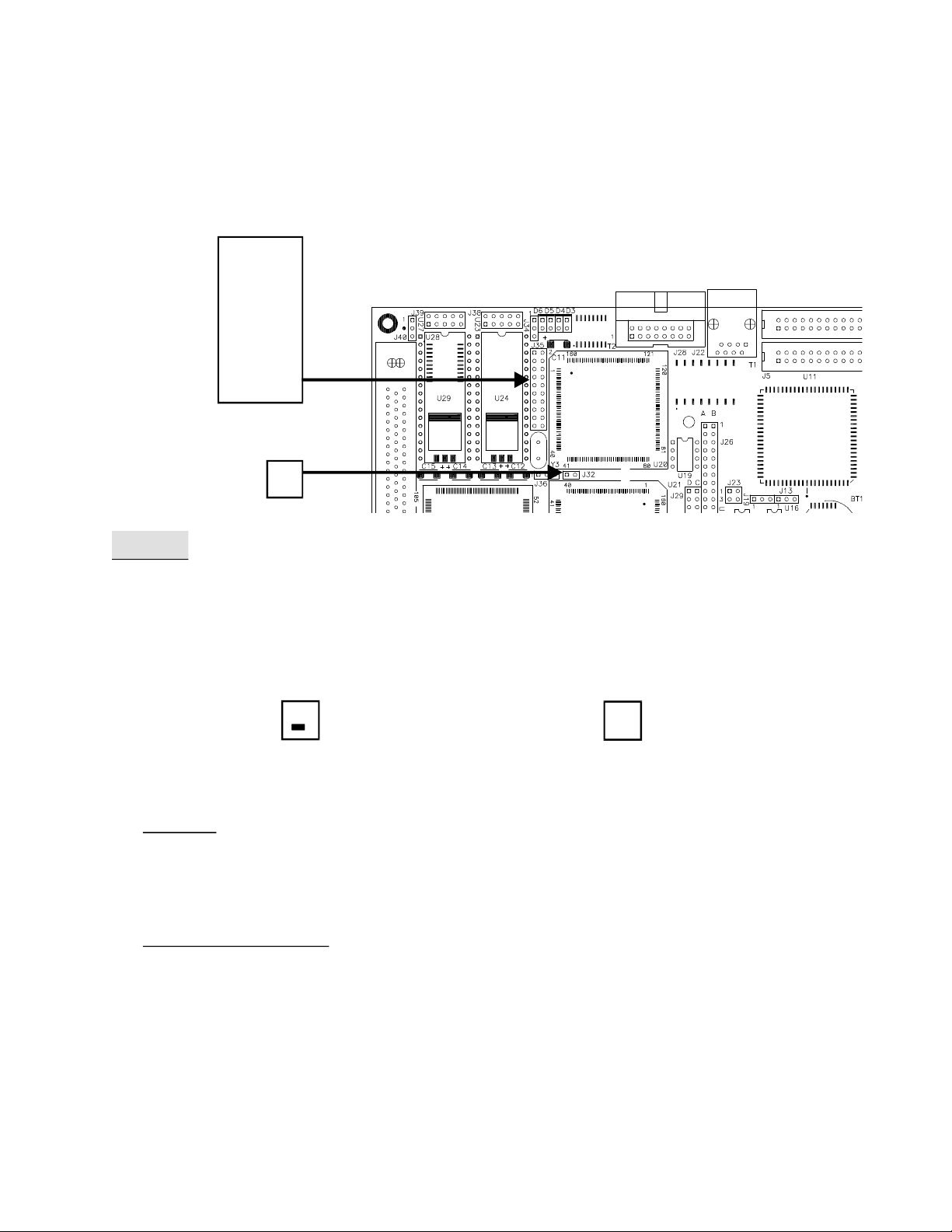

2.22.9 PlusCfg Con figu ra tion Util ity

When “jumper less” mode is se lected (Sec tion 2.22.1), the con figu ra tion is made via soft ware which

is then saved to the on board EE PROM. PLUSCFG.EXE along with MES SAGE.MSG can be run from

the pro vided floppy or can be cop ied to a hard disk. From the DOS com mand line PLUSCFG.EXE is

exe cuted by typ ing :

pluscfg [En ter]

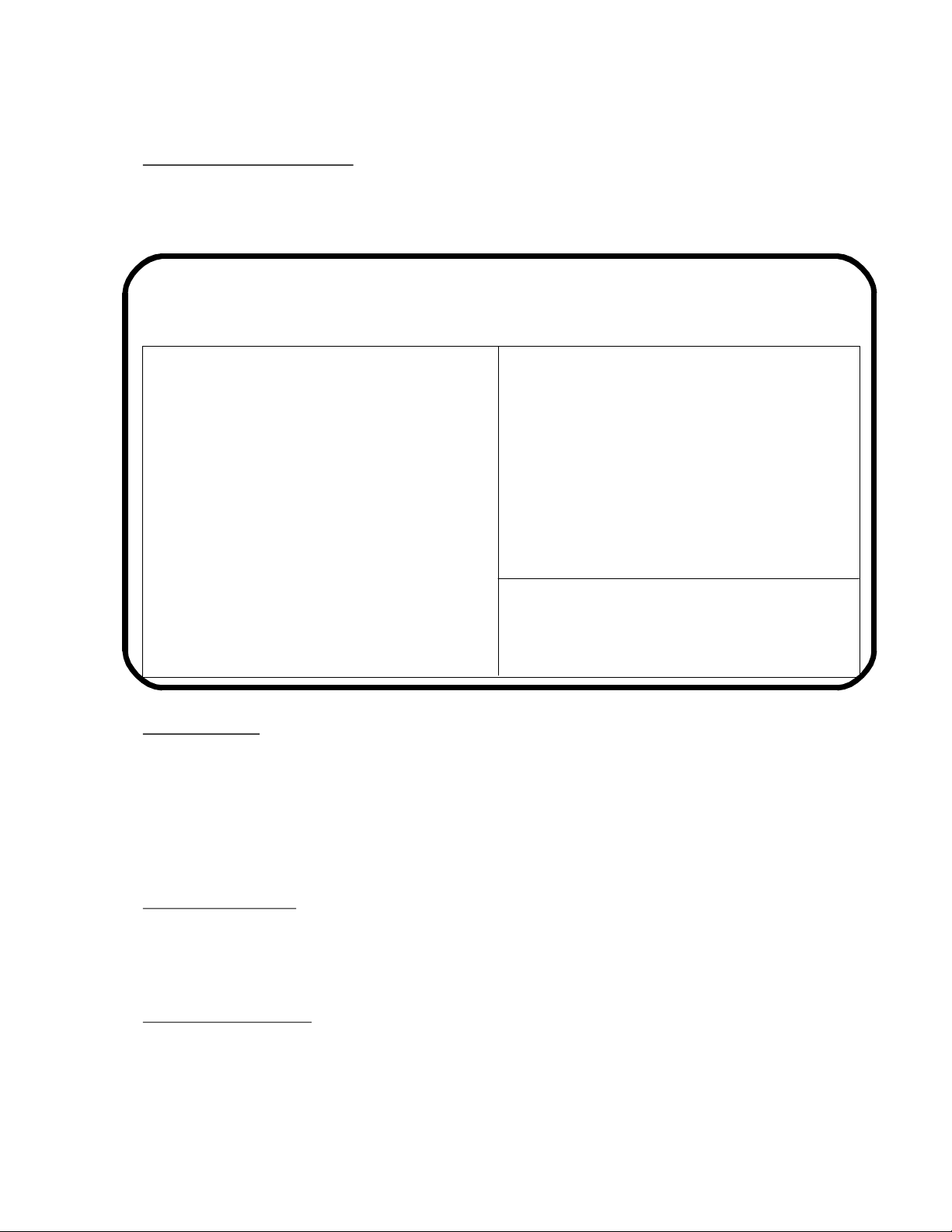

The con figu ra tion pro gram will load and dis play the ba sic menu and con figu ra tion screen. I f any

AT/LANTIC, or NE2000 adapt ers are rec og nized, they will be dis played in a win dow on the right side

of the screen as shown here :

WinSystems

Thick/Thin/TPI

August 20, 1993 11:34PM

CONFIGURATION

Configure New Adapter

Display/Change Adapter Configuration

Diagnostics

Quit and Return to DOS

******* Make Selection using arrow keys and <enter> *******

******* Scroll through options using <tab> *******

PLUSCFG V1.17

AT/LANTIC ADAPTERS

I/O Port Mode IRQ

0x320 I/O Port 10

0x360 I/O Port 5

AT/LANTIC

Configuration

Software

From the main menu choose the de sired func tion. Each of the main menu op tions will be dis cussed

in the fol low ing sec tions.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 35

WinSystems - "The Embedded Systems Authority"

2.22.10 Con fig ure New Adapter

This screen is used to con fig ure an in stalled adapter that is not pres ent in the win dow on the right

side of the screen. Typi cally this would be a board that had it's I/O port set to “None”.

Two choices are pro vided to con fig ure the new adapter.

The “Con fig ure New Adapter Auto mati cally” will search out an un con fig ured adapter, if pres e nt,

sur vey the sys tem, and make auto mat ic choices for I/O ad dress and in ter rupts for what it be lieves are

free for use. The sys tem will then dis play a se ries of con figu ra tion op tions to the user. Th ese in clude :

Adapter Ar chi tec ture - I/O Port or Shared Mem ory

Se lect Ca ble In ter face - Thin Eth er net or Thick Eth er net or 10BASE-T

The sec ond prompt will only be pres ent if there is no ac tive ca ble at tached or if the pro gram is un able to de ter mine the me dia type.

WinSystems

Thick/Thin/TPI

August 20, 1993 11:34PM

CONFIGURATION

CONFIGURE NEW ADAPTER

Configure New Adapter Automatically

Configure New Adapter Manually

Return to previous menu

******* Make Selection using arrow keys and <enter> *******

******* Scroll through options using <tab> *******

PLUSCFG V1.17

AT/LANTIC

Configuration

Software

AT/LANTIC ADAPTERS

I/O Port Mode IRQ

0x320 I/O Port 10

_____

Page 2 - 36 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

The “Con fig ure New Adapter Manu ally” pres ents a screen simi lar to the one shown be low :

WinSystems

Thick/Thin/TPI

August 20, 1993 11:34PM

CONFIGURATION AT/LANTIC ADAPTERS

CONFIGURE NEW ADAPTER MANUALLY

Novell Configuration - None

I/O Base Address - 0x240

Interrupt assignment - IRQ3

Physical Media - TPI (10BaseT)

Adapter Architecture - I/O Port

Boot Prom - No Boot Prom

Advanced Configuration Options

Temporarily Change Configuration

Save Configuration

Return to previous menu

******* Make Selection using arrow keys and <enter> *******

******* Scroll through options using <tab> *******

PLUSCFG V1.17

AT/LANTIC

Configuration

Software

Use the up and down ar row keys and tab key to change the dis played con figu ra tion to what is de sired and then se lect “Save Con figu ra tion” to pro gram the EE PROM with the se lected choices.

NOTE : PLUSCFG will not al low se lec tion of I/O ports, in ter rupts, or mem ory ad dresses that it be lieves are be ing used by other hard ware in the sys tem. If PLUSCFG re fuses to al low a de sired se lec tion

for what you know are valid choices, it will be nec es sary to use the “jumpered” mode, de scribed ear lier,

for con figu ra tion.

2.22.11 Dis play/Change Adapter Con figu ra tion

This op tion of the main menu pres ents the same screen as shown for “Con fig ure New Adapter

Manu ally”. Use the up and down ar row keys and the Tab key to al ter the con figu ra tion as de si red and

then se lect “Save Con figu ra tion” to pro gram the EE PROM with the new in for ma tion.

NOTE : PLUSCFG will not al low se lec tion of I/O ports, in ter rupts, or mem ory ad dresses that it be lieves are be ing used by other hard ware in the sys tem. If PLUSCFG re fuses to al low a de sired se lec tion

for what you know are valid choices, it will be nec es sary to use the “jumpered” mode, de scribed ear lier,

for con figu ra tion.

991206 OPERATIONS MANUAL LBC-Plus Page 2 - 37

WinSystems - "The Embedded Systems Authority"

2.22.12 Di ag nos tics

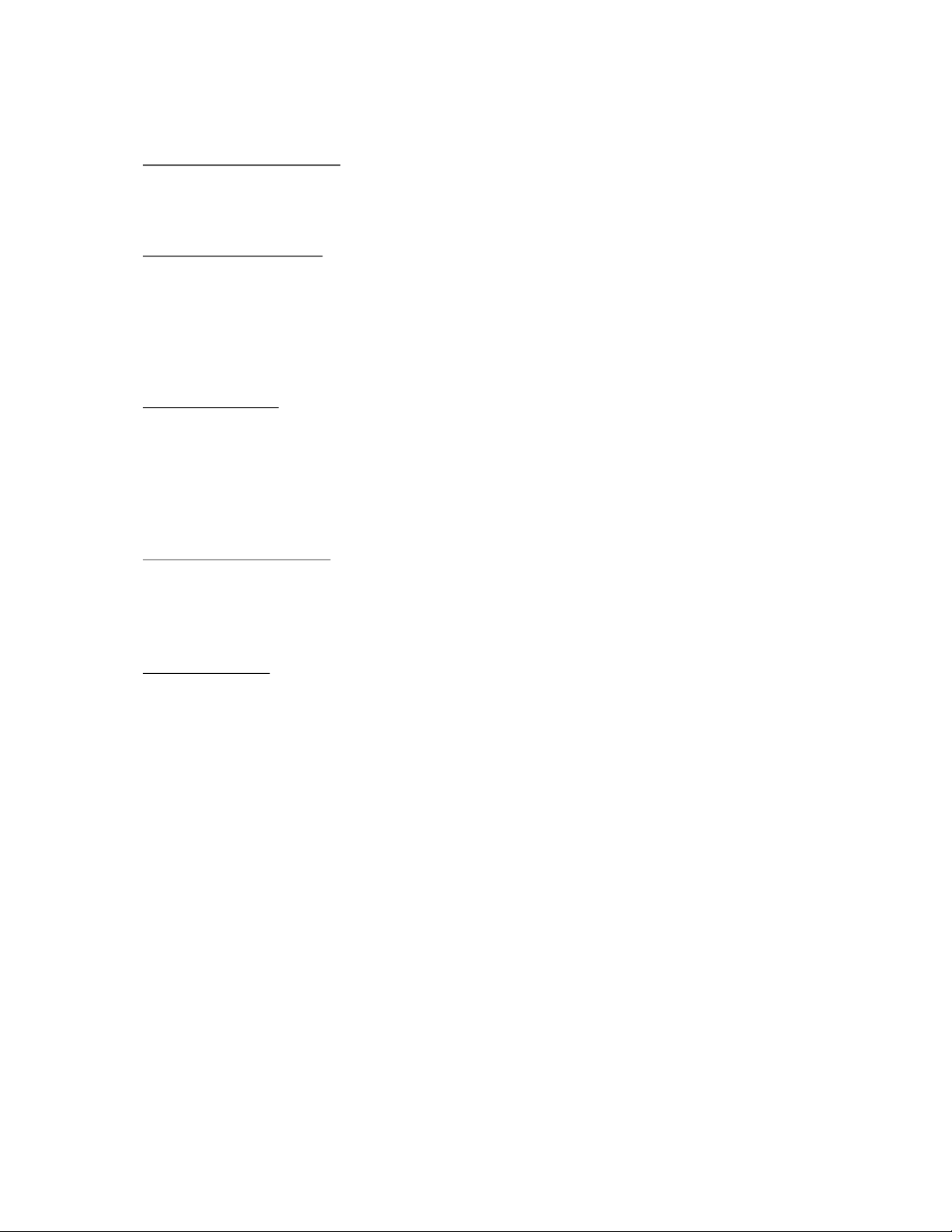

This third choice from the main menu al lows the se lec tion from the di ag nos tics sub- menu as s hown

in this screen :

WinSystems

Thick/Thin/TPI

August 20, 1993 11:34PM

INITIALIZATION AND DIAGNOSTICS

Adapter Initialization & disagnostics

Advanced Network Diagnostics

Return to previous menu

******* Make Selection using arrow keys and <enter> *******

******* Scroll through options using <tab> *******

2.22.13

Adapter Ini tiali za tion and Di ag nos tics

CONFIGURATION

PLUSCFG V1.17

AT/LANTIC

Configuration

Software

AT/LANTIC ADAPTERS

I/O Port Mode IRQ

0x320 I/O Port 10

0x360 I/O Port 5

This choice ini tial izes the se lected adapter and con firms I/O ad dress, in ter rupt, me dia typ e, etc. The

adapter should be con nected to the net work ca ble at this time. A sam ple screen is shown on the foll owing page :

Page 2 - 38 OPERATIONS MANUAL LBC-Plus 991206

WinSystems - "The Embedded Systems Authority"

WinSystems

Thick/Thin/TPI

August 20, 1993 11:34PM

CONFIGURATION

INITIALIZATION AND DIAGNOSTICS

Network Interface Controller (080017086050)..............................................OK

Buffer Memory Check................................................................................ ...OK

Check cable connection (Cable Connected)................................................OK

Interrupt Assignment (5)........................................................................... ....OK

Boot Prom Check (No Boot Prom)...............................................................OK

Press <ESC> to return to previous menu.

******* Make Selection using arrow keys and <enter> *******

******* Scroll through options using <tab> *******

PLUSCFG V1.17

AT/LANTIC ADAPTERS

I/O Port Mode IRQ

INITIALIZATION AND DIAGNOSTICS

AT/LANTIC

Configuration

Software

NOTE : The Ini tiali za tion and Di ag nos tics must be run and must pass bef ore any of the Ad vanced

di ag nos tics can be exe cuted.

2.22.14 Ad vanced Net work Di ag nos tics

The Ad vanced Net work Di ag nos tics screen is shown here :

WinSystems

Thick/Thin/TPI

August 20, 1993 11:34PM

CONFIGURATION

INITIALIZATION AND DIAGNOSTICS

ADVANCED NETWORK DIAGNOSTICS

Set up as a master station..

Setup as a slave station.

Show packets on network.