Page 1

5

A

4

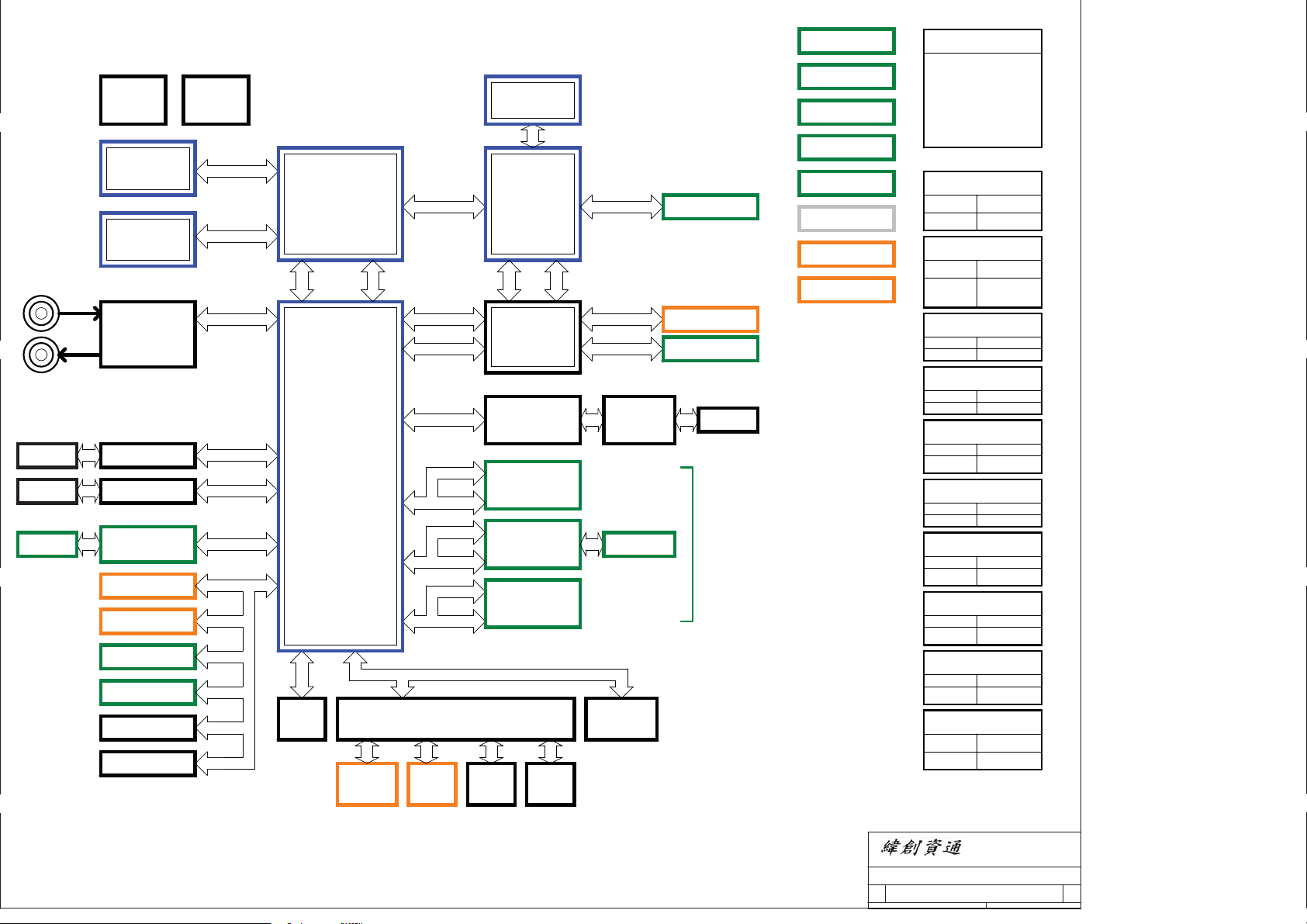

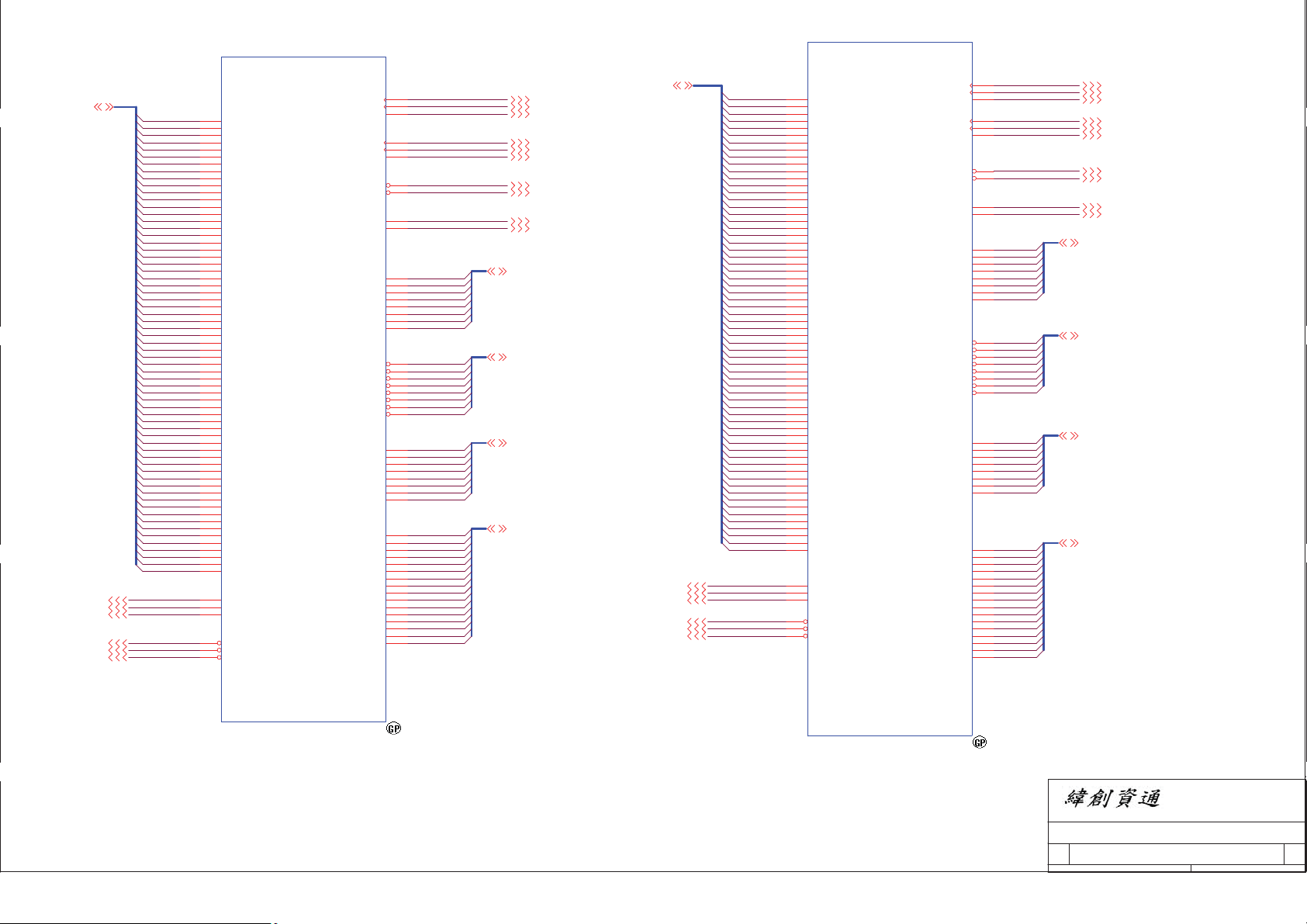

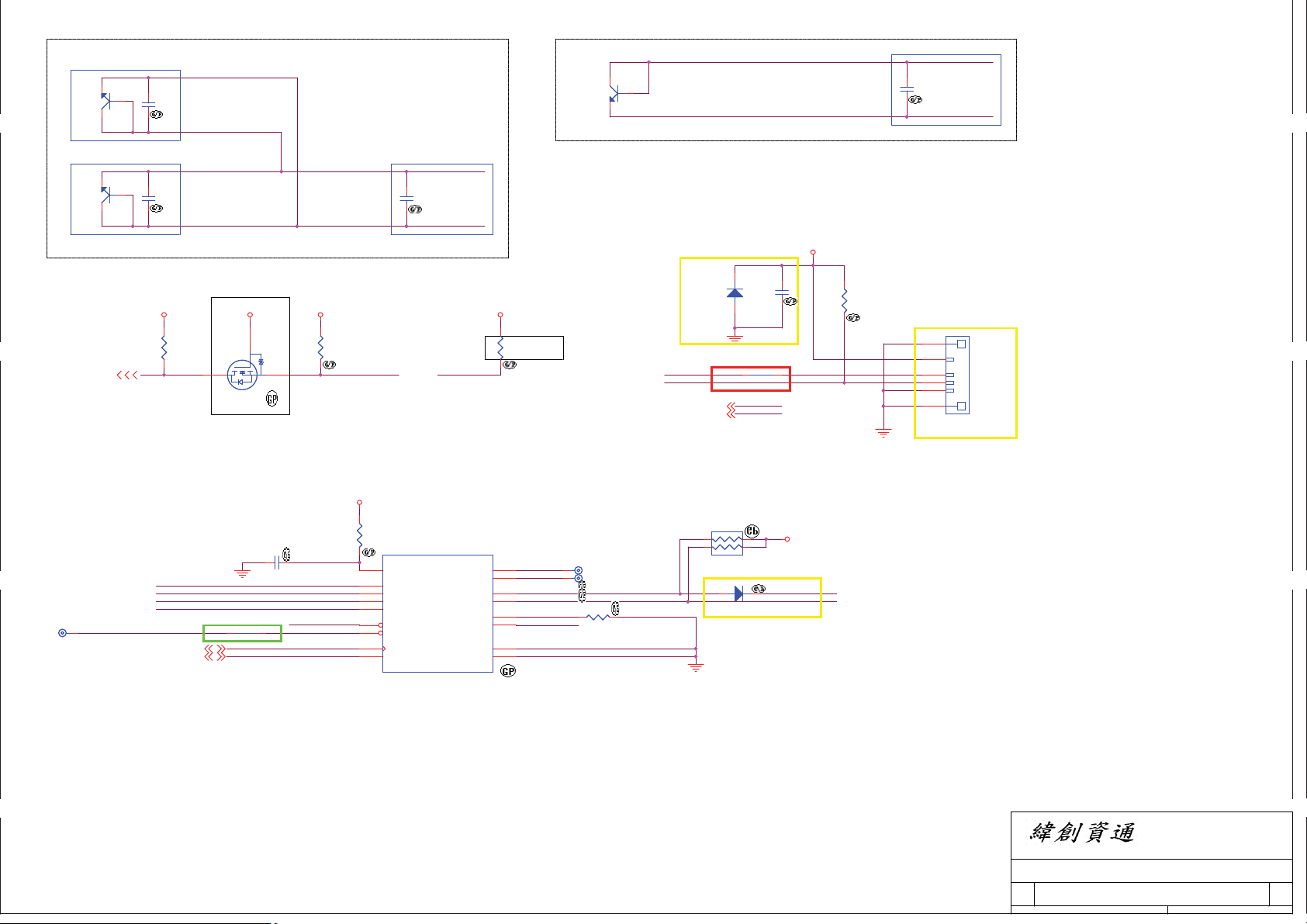

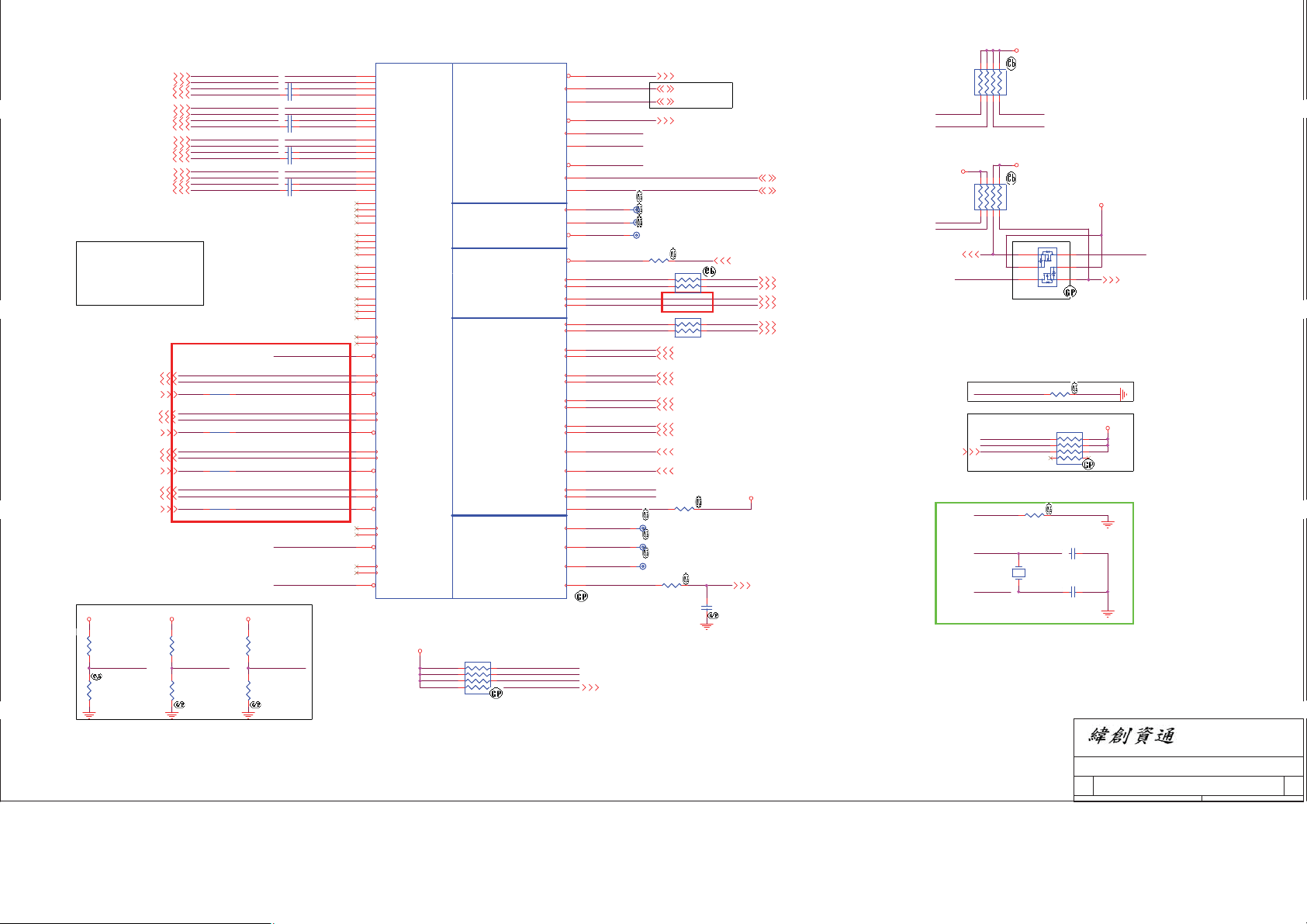

LA46 Switchable Graphics System Schematics

Clock GEN

CK505

11

12

3

Channel A

DDR3 800/1066

Intel CPU

Auburndale

(Dual Core)

Channel B

DDR3 800/1066

13

HDA Link

27

SATA Port 0

28

SATA Port 1

28

USB 2.0 port?

CH3

32

CH5

24

CH7

38

CH7

35

CH8

35

CH0

35

DDR3 800/1066MHz

4,5,6,7,8,9,10

AC97 2.3/Azalia Interface

14,15,16,17,18,19,20,21,22

EHCI#1

SPI

USB 2.0

SPI FLASH

4MB

38

Intel

PCH HM55

USB 2.0 (12 ports)

Serial ATA (4 ports)

PCI Express (8 ports)

ACPI 2.0

LPC I/F

PCI Rev 2.3

INT. RTC

Nuvoton NPCE781E

Multi-touch

Touchpad

DMI x4FDI

LPC Bus / 33MHz

KBC

38

D D

C C

Headphone out

SATA HDD

SATA ODD

B B

Mic in

5-in-1

Slot

USB BD

Thermal

Sensor

EMC2103

UNBUFFERED

DDR3 SODIMM

Socket1

204-PIN DDR3 SODIMM

UNBUFFERED

DDR3 SODIMM

Socket2

HD AUDIO CODEC

ALC269Q-VB-GR

SATA CONN

SATA CONN

I/O BD

MediaCard Reader

Realtek/5138

Bluetooth

Camera

Finger Printe r

USB 2.0

USB 2.0

USB 2.0

PCIe16XGen2

LVDS

RGB

PCI Express 8

USB 2.0 CH2

PCI Express 1

USB 2.0 CH4

PCI Express 3

USB 2.0 CH6

PCI Express 4

Int. KB

36

3

2

http://hobi-elektronika.net

Project Code: 91.4GV01.001

PCB(Raw Card): 09911-1

DDR3

512MB / 1GB

MUX

23,24,25

SPI Flash

128Kb

X4

57,58

36

38

LVDS

29

HDMI

LVDS

RGB

Transformer RJ45

30

SIM Slot

LPC Debug

Board Conn

36

HDMI CONN

HDMI BD

14'' WUXGA

(WSXGA) LCD

CRT CONN

CRT BD

I/O BD

31

26

24

25

30

VRAM

PortA

NVIDIA

N11M-GE

54,55,56,57,58,59

RGB

GLAN

AR8131

Mini PCI-E

WLAN Card

Mini PCI-E

WWAN Card

Express Card

G-Sensor

38

USB BD

I/O BD

CRT BD

Power BD

Finger Printer BD

HDMI BD

BT BD

AV BD

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

1

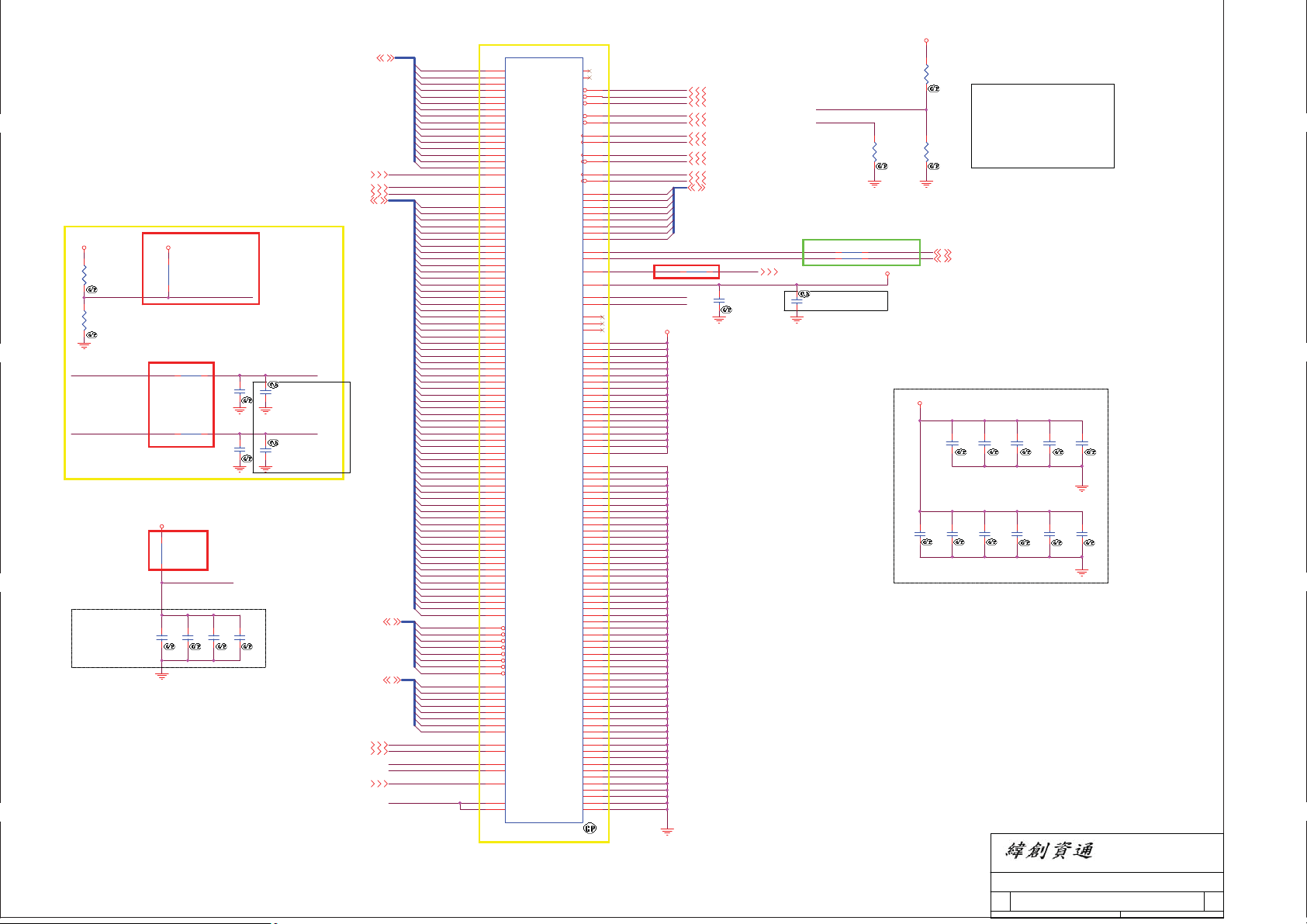

PCB LAYER

L1: Top

L2: GND

L3: Signal

L4: Signal

L5: VCC

L6: Signal

L7: GND

L8: Signal

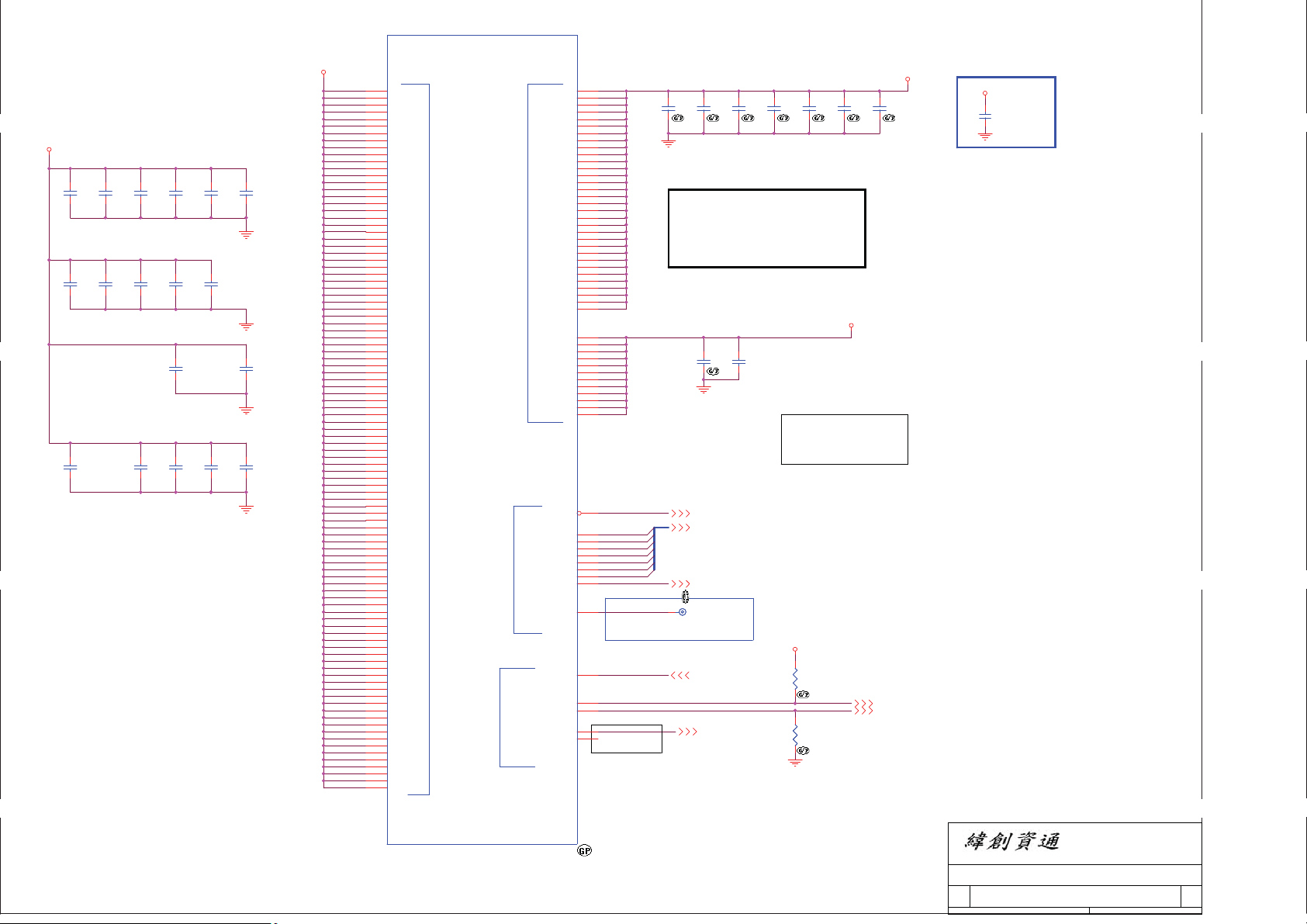

CPU DC/DC

ISL62882

INPUTS

DCBATOUT

SYSTEM DC/DC

TPS51123

INPUTS

SYSTEM DC/DC

RT8209E

DCBATOUT

SYSTEM DC/DC

RT8209E

INPUTS OUTPUTS

DCBATOUT

SYSTEM DC/DC

RT8209E

DCBATOUT

LDO

RT9025

INPUTS

LDO

RT9026

INPUTS

1D5V_S3 DDR_VREF_S3

SYSTEM DC/DC

ISL62881

DCBATOUT

SYSTEM DC/DC

ISL62872

DCBATOUT

CHARGER

BQ24745

INPUTS

DCBATOUT

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsic hih,

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsic hih,

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsic hih,

Taipei Hsien 221, Taiwan, R.O.C

Taipei Hsien 221, Taiwan, R.O.C

Taipei Hsien 221, Taiwan, R.O.C

01_Block Diagram

01_Block Diagram

01_Block Diagram

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

OUTPUTS

VCC_CORE

OUTPUTS

5V_AUX_S5

3D3V_AUX_S5

5V_S5DCBATOUT

3D3V_S5

OUTPUTSINPUTS

1D5V_S3

1D05V_S0

OUTPUTSINPUTS

1D05V_VTT

OUTPUTS

1D8V_S03D3V_S5

OUTPUTS

0D75_S0

OUTPUTSINPUTS

VCC_GFXCORE

OUTPUTSINPUTS

VGA_CORE_S0

OUTPUTS

BT+

38,39

158Wednesday,January 27,2010

158Wednesday,January 27,2010

158Wednesday,January 27,2010

40

41

41

42

43

43

44

45

46

A

-1

-1

-1

of

of

of

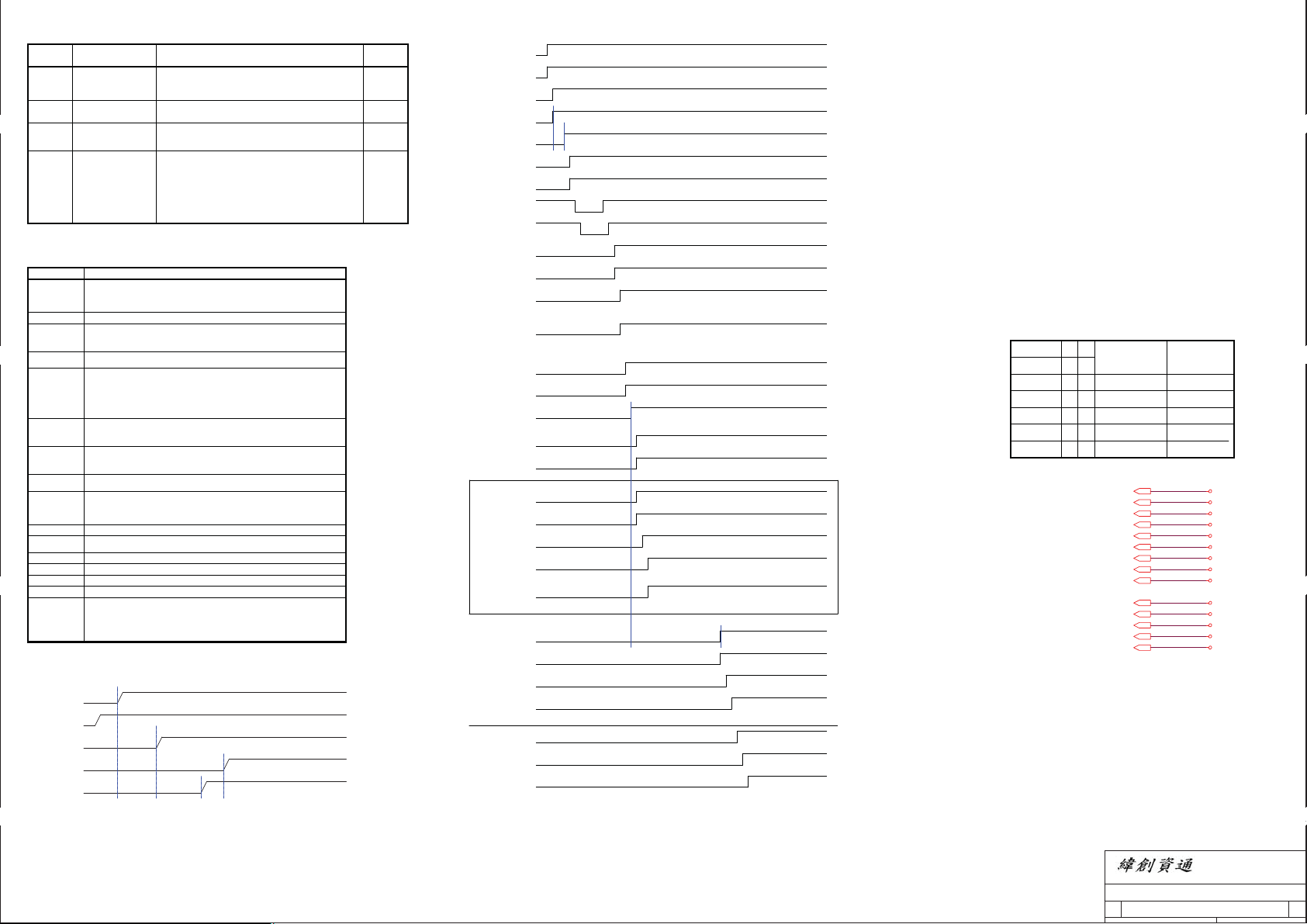

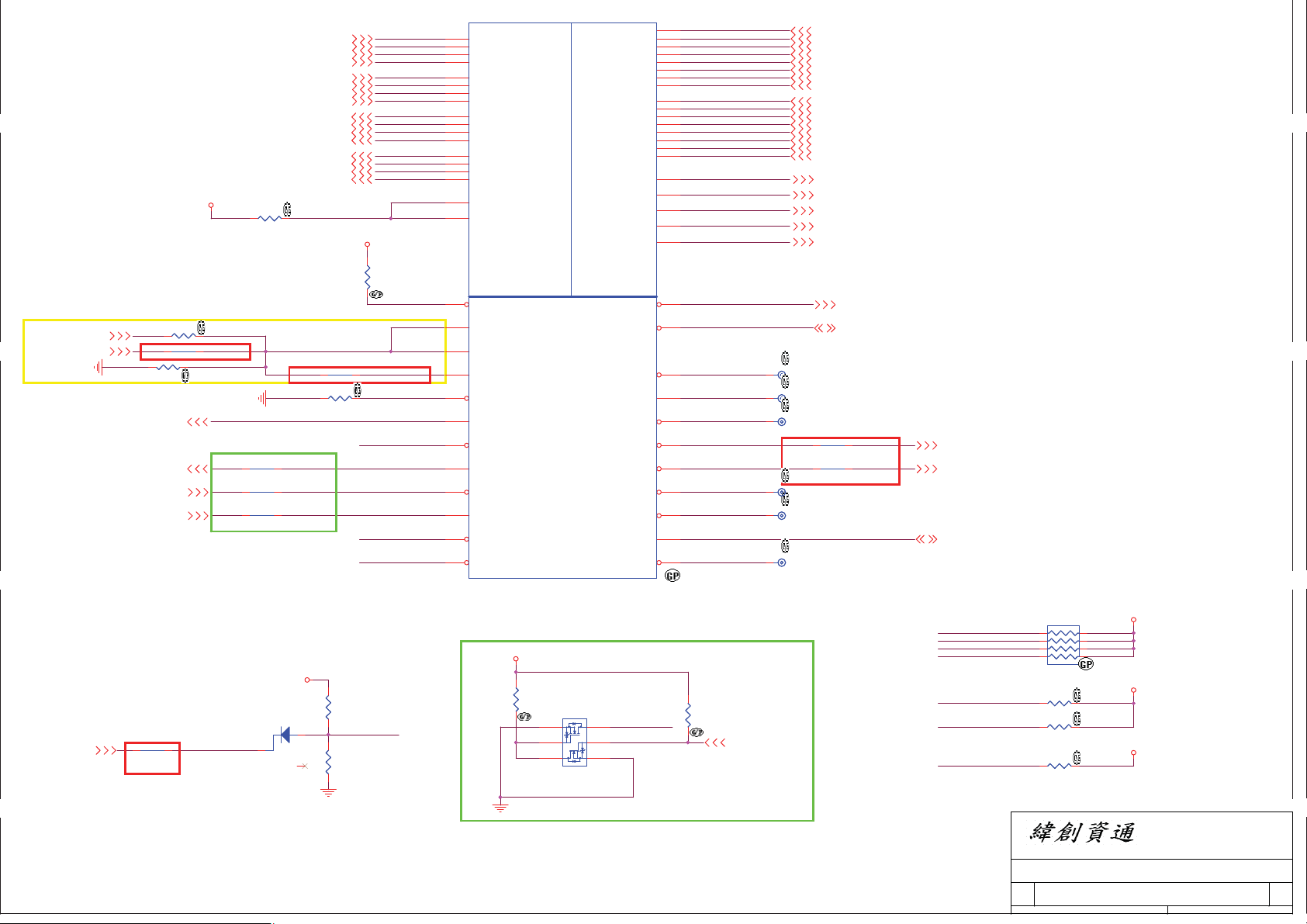

Page 2

5 4 3 2 1

A

A

f

y

f

y

f

y

Processor Strapping

Pin Name

Strap Description Configuration (Default value for each bit is

CFG[4] Disabled - No Physical Display Port attached to

DisplayPort

Presence

CFG[3]

PCI-Express Static

Lane Reversal1:0:

CFG[0]

CFG[7]

PCI-Express

Configuration

Select

Reserved Temporarily used

for early

Clarksfield

samples.

D

PCH Strapping

Name Schematics Notes

SPKR

INIT3_3V# Weak internal pull-down. Do not pull high.

GNT3#/

GPIO55

INTVRMEN

C

GNT0#,

GNT1#

GNT2#/

GPIO53

GPIO33

SPI_MOSI

NV_ALE

NC_CLE Weak internal pull-up. Do not pull low.

HAD_DOCK_EN#

/GPIO[33]

HDA_SDO Weak internal pull-down. Do not pull high.

HDA_SYNC

GPIO15

B

GPIO8

GPIO27

N11M-GE Power Sequence

VDD33

PEX_VDD

NVVDD

IFPAB_IOVDD

FBVDDQ

Reboot option at power-up

Internal weak Pull-down.

Default Mode:

Connect to Vcc3_3 with 8.2-k

No Reboot Mode with TCO Disabled:

- 10-k weak pull-up resistor.

Internal pull-up.

Default Mode:

(Connect to ground with 4.7-k weak

Low (0) = Top Block Swap Mode

pull-down resistor).

High (1) = Integrated VRM is enabled

Low (0) = Integrated VRM is disabled

Left both GNT0# and GNT1# floating. No pull up

Default (SPI):

required.

Connect GNT1# to ground with 1-k pull-down

Boot from PCI:

resistor. Leave GNT0# Floating.

Connect both GNT0# and GNT1# to ground with 1-k

Boot from LPC:

pull-down resistor.

Default - Internal pull-up.

= Configures DMI for ESI compatible operation (for servers

Low (0)

only. Not for mobile/desktops).

Do not pull low.

Default:

Connect to ground with 1-k

Disable ME in Manufacturing Mode:

pull-down resistor.

Connect to Vcc3_3 with 8.2-k weak pull-up resistor.

Enable iTPM:

Left floating, no pull-down required.

Disable iTPM:

Connect to Vcc3_3 with 8.2-k weak pull-up

Enable Danbury:

resistor.

Connect to ground with 4.7-k weak pull-down

Disable Danbury:

resistor.

Flash Descriptor Security will be overridden.

Low (0):

Flash Descriptor Security will be in effect.

High (1) :

Weak internal pull-down. Do not pull high.

Weak internal pull-down. Do not pull high.

Weak internal pull-up. Do not pull low.

Default = Do not connect (floating)

High(1) = Enables the internal VccVRM to have a clean supply for

analog rails. No need to use on-board filter circuit.

Low (0) = Disables the VccVRM. Need to use on-board filter

circuits for analog rails.

1 unless specified otherwise)

1:Embedded

Embedded DisplayPort.

Enabled - An external Display Port device is

0:

connected to the Embedded Display Port.

Normal Operation.

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

Single PCI-Express Graphics

1:

Bifurcation enabled

0:

-

Clarksfield (only for early samples pre-ES1)

Connect to GND with 3.01K Ohm/5% resistor

Only temporary for early CFD samples

Note:

(rPGA/BGA) [For details please refer to the WW33

MoW and sighting report].

For a common motherboard design (for AUB and CFD),

the pull-down resistor should be used. Does not

impact AUB functionality.

PEX_VDD c an ramp up any time

tNVVDD

tNV-IFPAB_IOVDD

tNV-FBVDDQ

Default

Value

1

1

1

0

http://hobi-elektronika.net

Sequence AC

AD+

3D3V_AUX_S5

5V_AUX_S5

S5_ENABLE (KBC)

5V_S5

3D3V_S5

RSMRST#_KBC

LAN_PWR_ON

3D3V_LAN_S5

KBC_PWRBTN#

PM_PWRBTN#

PM_SLP_S4#

1D5V_S3

DDR3_VREF_S3

PM_SLP_S3#

5V_S0

3D3V_S0

1D8V_S0

1D5V_S0

1D05V_S0

0D75V_S0

ALL_PWRGD

1D05V_VTT

VTT_PWRGD

(H_VTTPWRGD -->CPU, KBC)

GFX_VR_EN

VCC_GFXCORE

DIS: Before 1D05V_VTT

Platform

controlled

Sillicon

controlled

DGPU_PWR_EN#

3D3V_S0_NV

VGA_CORE_PWR

DGPU_PWROK

1D8V_S0_NV

FBVDD

1D05V_S0_NV

S0_PWR_GOOD

(IMVP_VR_EN)

VCC_CORE

VR_CLKEN#

CORE_PWRGD

(SYS_PWROK, PCH_PWROK)

PM_DRAM _PWRGD

H_PWRGD

PLT_RST#

>10ms

can power after power switch press

>99ms

PLANAR_ID[1..0]

KBC GPIn

PLANAR_IDn

31

1

0

0

1

11

23

0

0

1

0

DDR_VREF_S312,13,43

VCC_GFXCORE8,36,44

3D3V_S0_NV45,50,51,53,54,55

VGA_CORE_S045,50,51

1D8V_S0_NV50,54

FBVDD50,52,57,58

1D05V_S0_NV50,51,52,54,55

Planar IDVersion

LA46 - SA

LA46 - SB

VCC_CORE7,36,39

5V_S011,20,21,23,24,25,26,27,28,35,36,44,45,48,49

3D3V_S03,5,11,12,13,14,15,16,17,18,19,20,21,23,24,25,26,27,31,32,33,34,35,36,38,41,43,44,50

1D5V_S35,8,12,13,36,41,43,50

1D05V_S03,14,15,16,20,21,41,50

1D05V_VTT5,7,8,19,20,21,36,38,42

1D8V_S08,20,23,36,43

PlanarPCB Version

SA

SBLA46 - SB

SC

-1

VCC_CORE

5V_S0

3D3V_S0

1D5V_S3

1D05V_S0

1D05V_VTT

1D8V_S0

DDR_VREF_S3

VCC_GFXCORE

3D3V_S0_NV

VGA_CORE_S0

1D8V_S0_NV

FBVDD

1D05V_S0_NV

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai WuR d. , H s ichih,

21F,88,Sec.1,Hsin Tai WuR d. , H s ichih,

21F,88,Sec.1,Hsin Tai WuR d. , H s ichih,

Taipei Hsien221, Taiwan, R.O.C

Taipei Hsien221, Taiwan, R.O.C

Title

Title

Title

02_Reference

02_Reference

02_Reference

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA46 MB -1

A2

LA46 MB -1

A2

LA46 MB -1

A2

Date: Sheet

Date: Sheet

Date: Sheet

, January27, 2010

, January27, 2010

, January27, 2010

Taipei Hsien221, Taiwan, R.O.C

258Wednesda

258Wednesda

258Wednesda

o

o

o

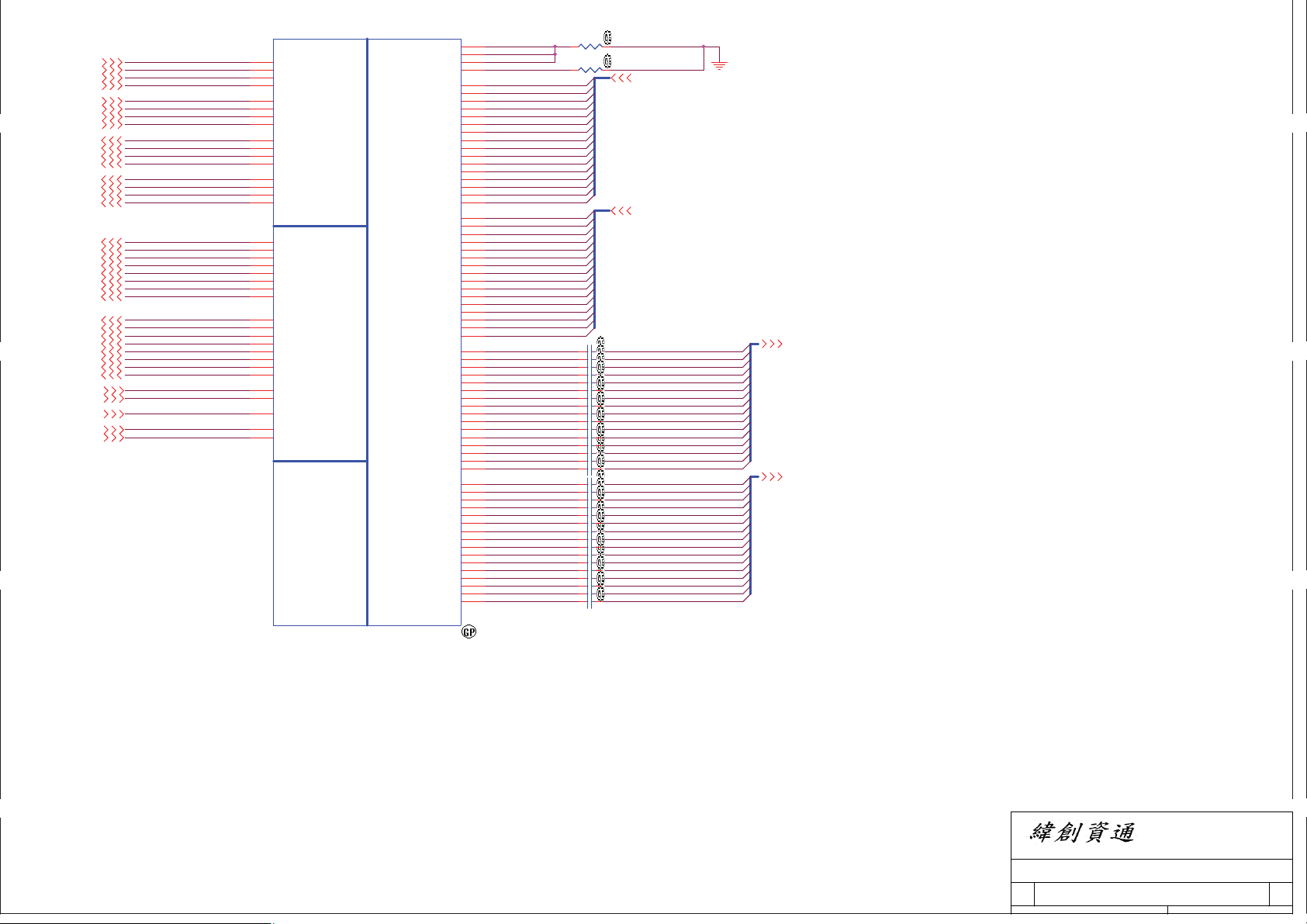

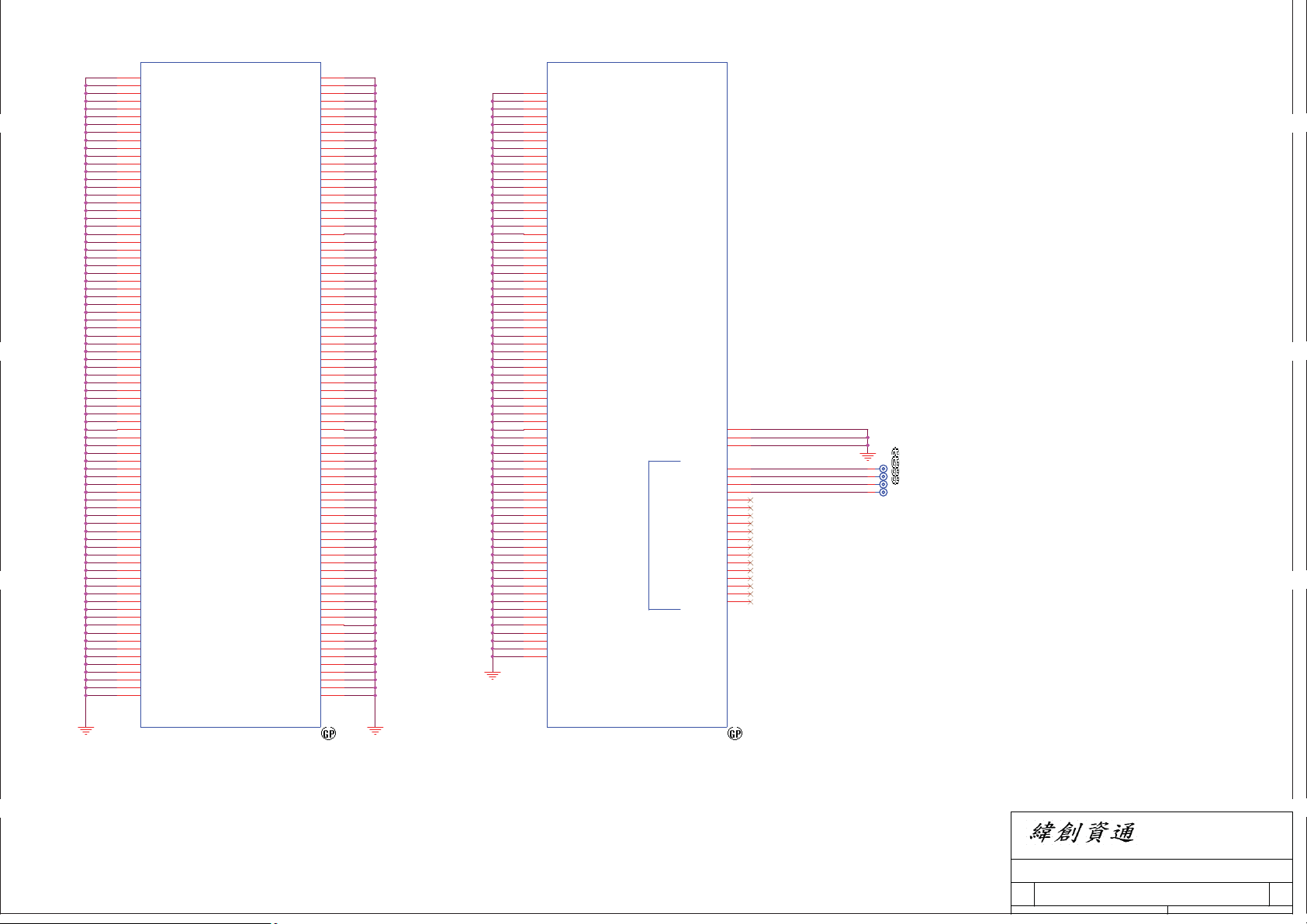

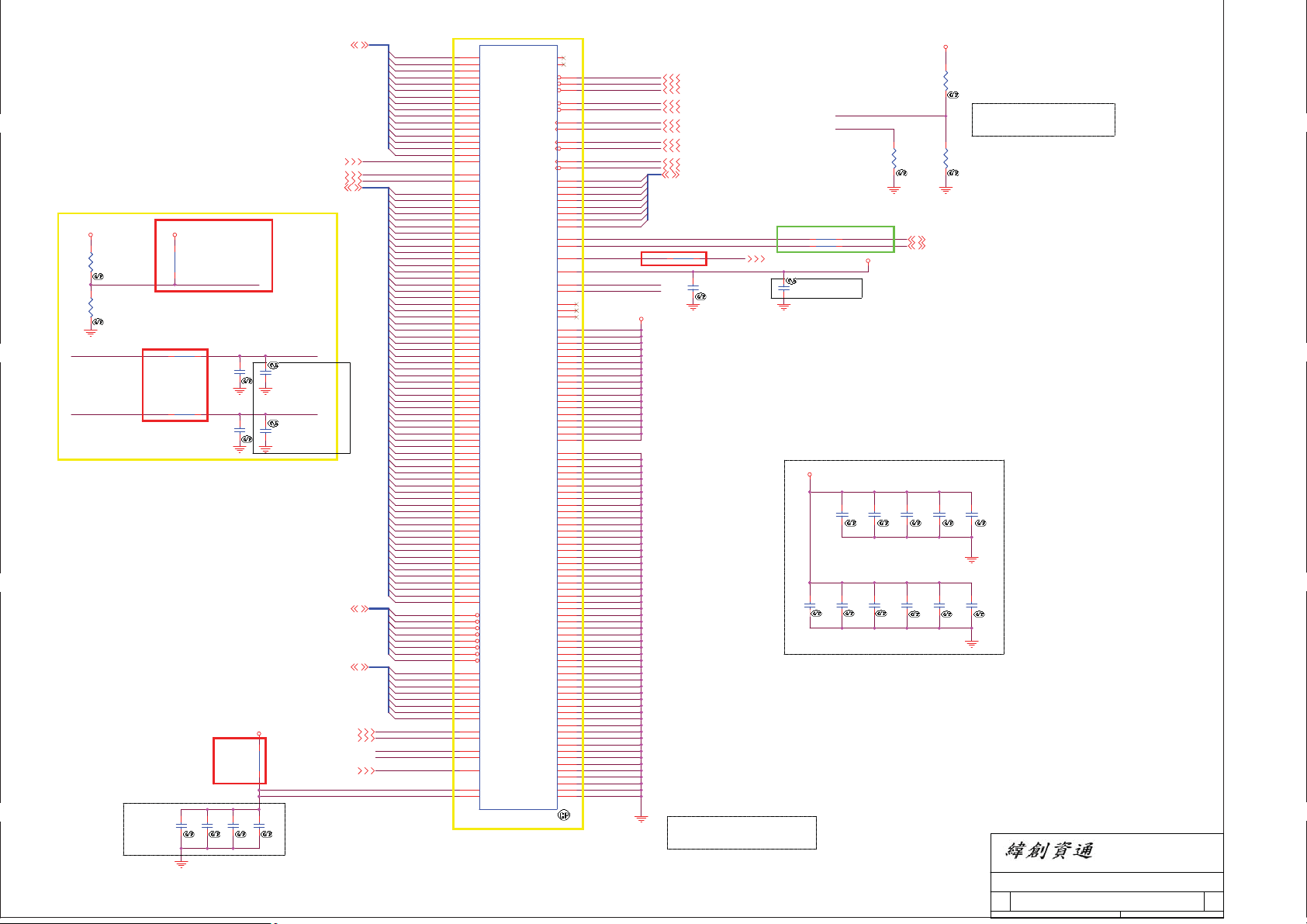

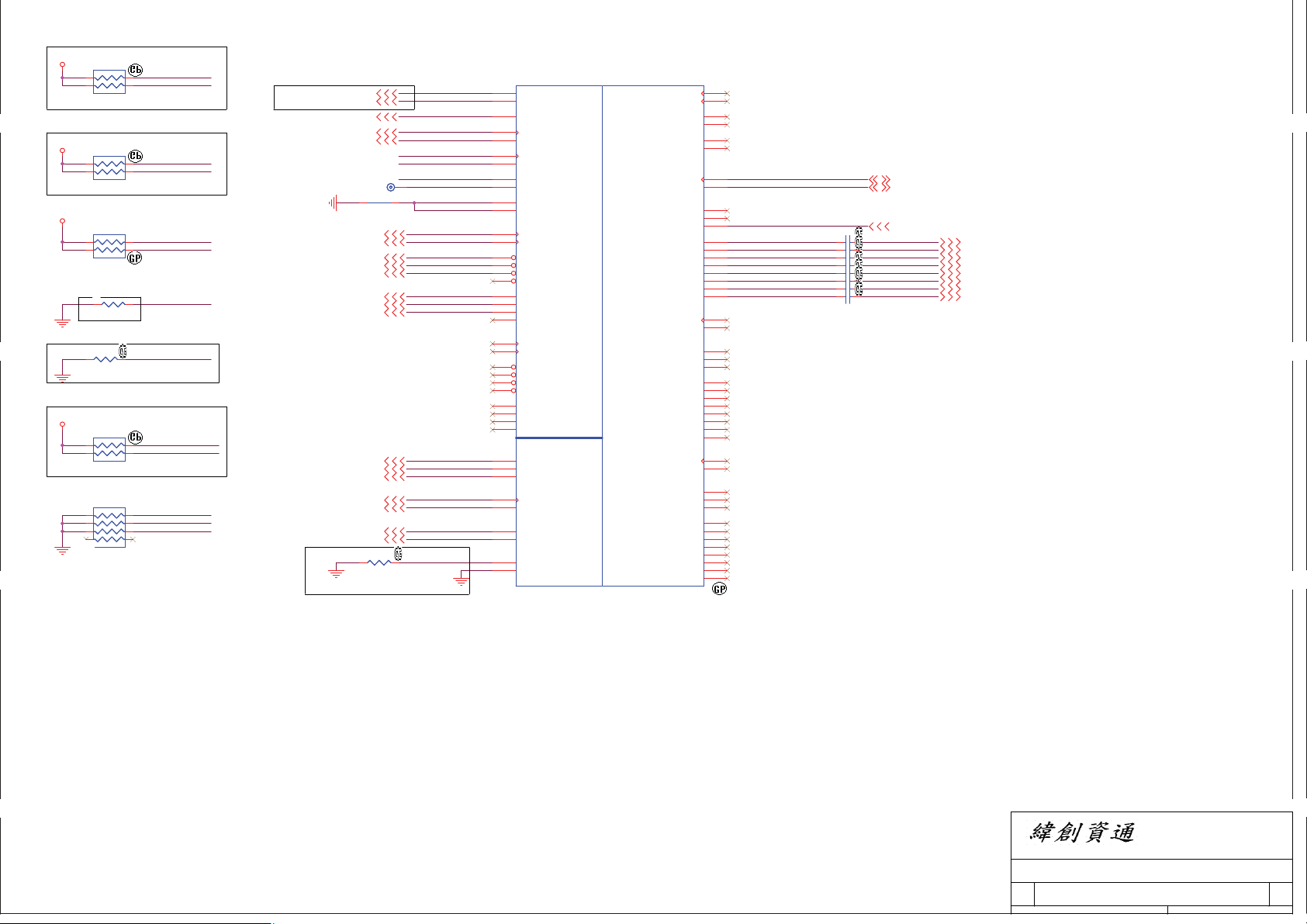

Page 3

5

A

1 2

R247

R247

0R0603-PAD

0R0603-PAD

-1 0107

12

12

C358

C358

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C347

C347

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

C348

C348

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_S0 3D3V_CK505

D D

C369

C369

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

4

http://hobi-elektronika.net

FOR CO-LAY SLG8LV595

1D5V_S0

12

C346

C346

SC47P50V2JN-3GP

SC47P50V2JN-3GP

12

12

C383

C383

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C349

C349

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_CK505

1 2

DY

DY

R264

R264

0R3J-0-U-GP

0R3J-0-U-GP

1D5V_S0_CK5051D5V_S0_CK505

12

R258

R258

0R3J-0-U-GP

0R3J-0-U-GP

3

1D05V_CK505

Low voltage I/O power

supply for outputs.

1D05V_S0

1 2

R268

R268

0R0603-PAD

0R0603-PAD

-1 0107

2

1D05V_CK505

12

C402

C402

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

12

C401

C401

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C376

C376

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C384

C384

SC47P50V2JN-3GP

SC47P50V2JN-3GP

1

5

15

VDD_DOT

VSS_SRC

VDD_27

VSS_DOT

2

18

VDD_SRC_IO

VDD_CPU_IO

CKPWRGD/PD#

REF_0/CPU_SEL

VSS_278VSS_SATA

9

27MHZ

27MHZ_SS

CPU_STOP#

XTAL_IN

XTAL_OUT

SDA

SCL

29

1

17

U27

U27

DREFCLK#15

DREFCLK15

CLKIN_DMI#15

CLKIN_DMI15

CLK_PCIE_SATA#15

C C

CLK_PCIE_SATA15

CLK_CPU_BCLK#15

CLK_CPU_BCLK15

-1 0111

1D05V_CK505 3D3V_CK505

R251

R251

2K2R2J-2-GP

2K2R2J-2-GP

DY

B B

DY

1 2

1 2

REF_0/CPU_SEL

R250

R250

10KR2J-3-GP

10KR2J-3-GP

FSC 0 1

SPEED

133MHz

(Default)

CK_PWRGD

VR_CLKEN#38

100MHz

SB-1015 change to 84.2N702.E31

4

3

14

13

11

10

22

23

19

20

SLG8SP585VTR-GP

SLG8SP585VTR-GP

2ND = 71.93197.003

2ND = 71.93197.003

1 2

G

S D

DOT_96#

DOT_96

SRC_2#

SRC_2

SRC_1/SATA#

SRC_1/SATA

CPU_0#

CPU_0

CPU_1#

CPU_1

10KR2J-3-GP

10KR2J-3-GP

R266

R266

Q21

Q21

2N7002A-7-GP

2N7002A-7-GP

24

33

VDD_CPU

GND

VDD_REF

VDD_SRC

VSS_CPU

VSS_REF

12

21

26

VGA 27M X1

Crystal

CLK GEN Mount

VGA_XIN1_L

6

OSC_SPREAD_L

7

CPU_STOP#

16

CK_PWRGD

25

REF_0/CPU_SEL

30

GEN_XTAL_IN

28

GEN_XTAL_OUT

27

31

32

3D3V_CK505

R255 10KR2J-3-GPR255 10KR2J-3-GP

3.3V LVTTL input for CPU_STOP#. Contains

internal pull-up resistor.

CL=20pF±0.2pF

C370

C370

SC10P50V2JN-4GP

SC10P50V2JN-4GP

1 2

1 2

C377

C377

SC12P50V2JN-3GP

SC12P50V2JN-3GP

R75RNT1

DYDY

Mount

DY

DY

4

FOR DIS

1 2

12

X4

X4

82.30005.A51

82.30005.A51

X-14D31818M-50GP

X-14D31818M-50GP

2ND = 82.30005.C51

2ND = 82.30005.C51

Mount

DY

RNT1

RNT1

1

SRN33J-5-GP-U

SRN33J-5-GP-U

23

R249 33R2J-2-GPR249 33R2J-2-GP

PCH_SMBDATA 12,13,15

PCH_SMBCLK 12,13,15

CPU_STOP#

GEN_XTAL_IN

GEN_XTAL_OUT

R79

Mount

DY

1 2

R80

C107

MountDYMount

DY

VGA_XIN1 55

OSC_SPREAD 55

DY

DY

Layout Notes:

C131

Mount

DY

CLK_ICH14 15

12

C351

C351

SC10P50V2JN-4GP

SC10P50V2JN-4GP

Make sure that the stubs to the

test points(CK_PWRGD, CLK_EN#,

GEN_XTAL_OUT) in the layout are as

short as possible on the high speed

signals.

SB BOM change to 82.30005.A51

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Title

Title

Title

03_Clock Generator SLG8SP585

03_Clock Generator SLG8SP585

03_Clock Generator SLG8SP585

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

358Tuesday,January 26, 2010

358Tuesday,January 26, 2010

358Tuesday,January 26, 2010

of

of

of

A

-1

-1

-1

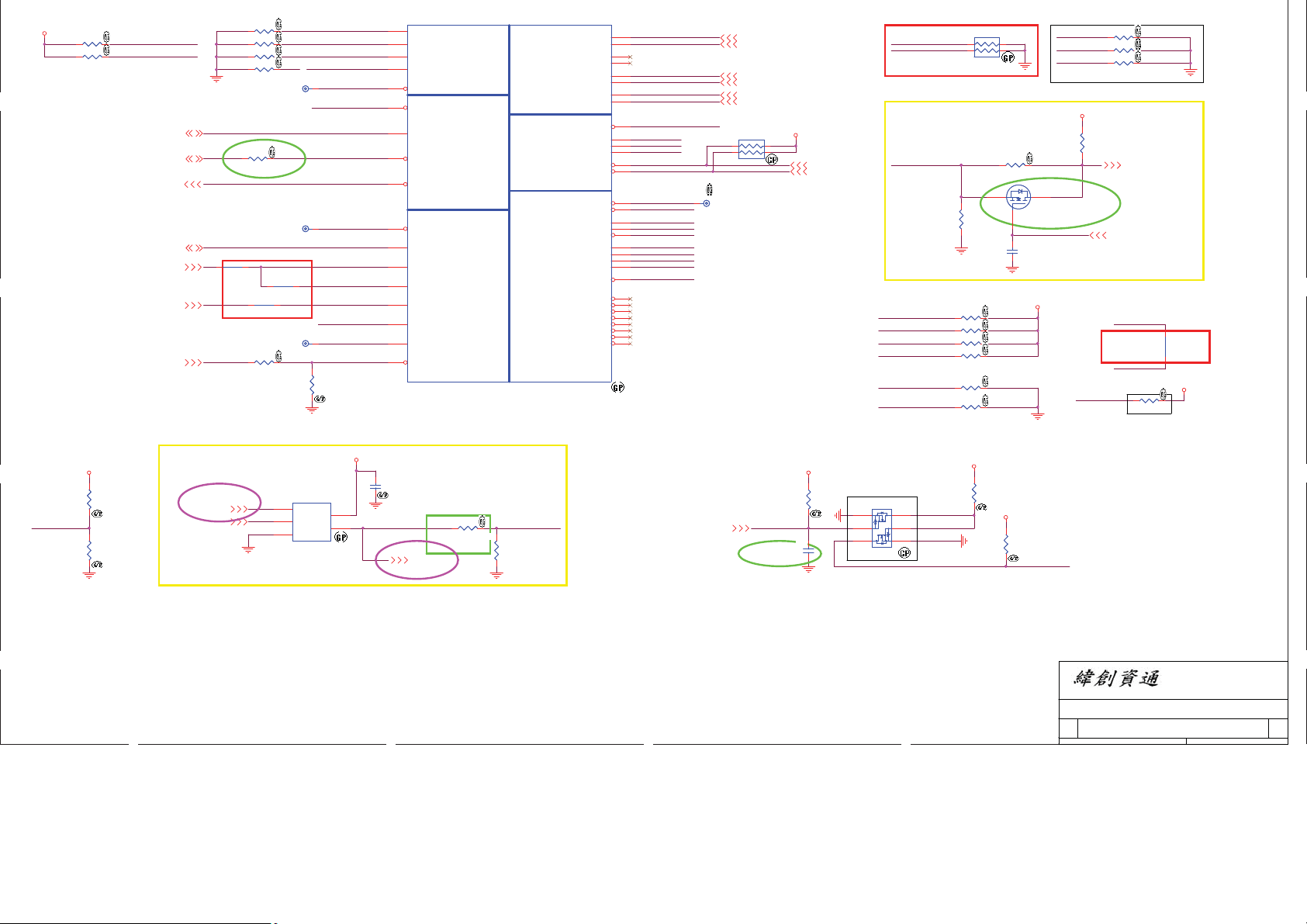

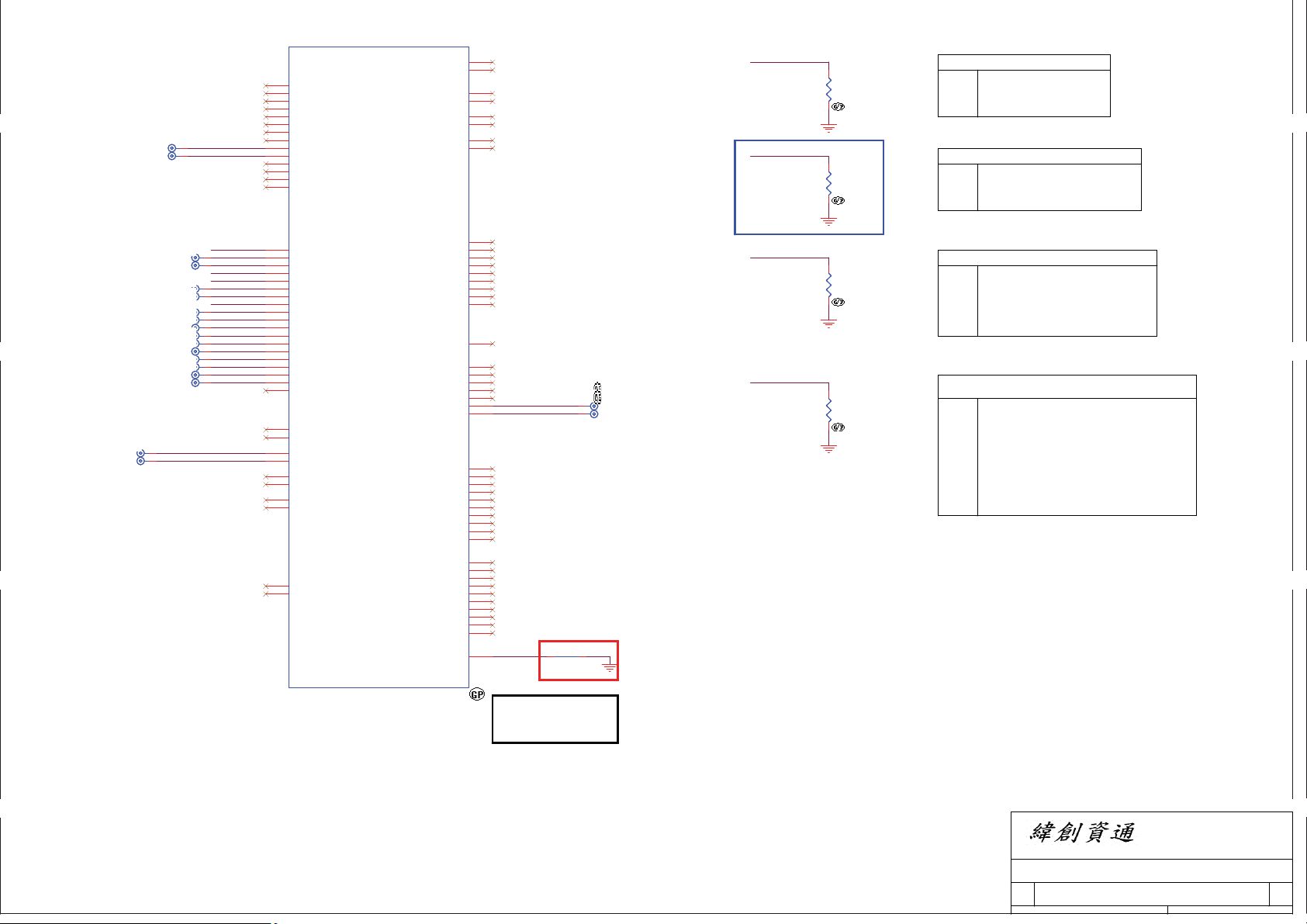

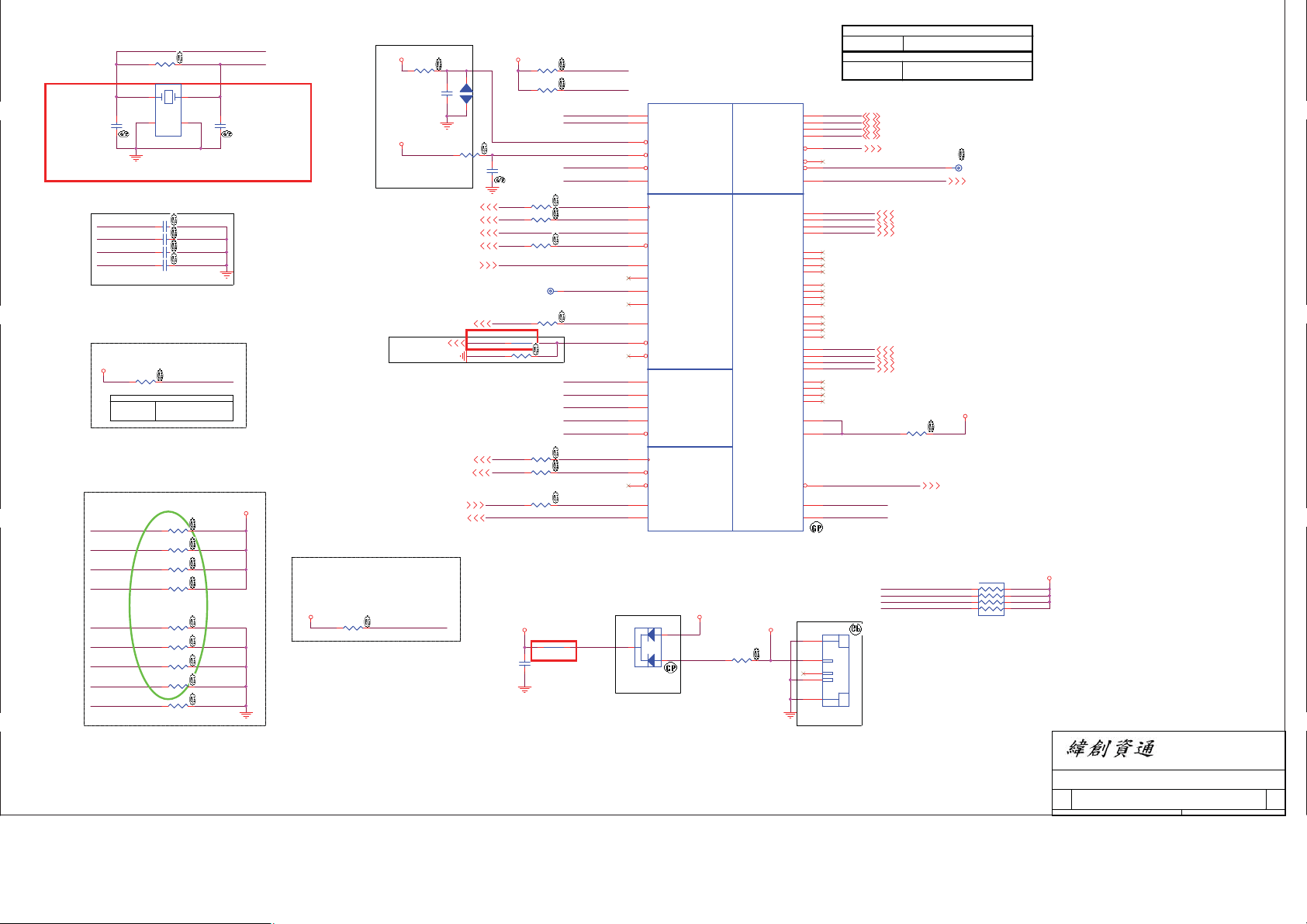

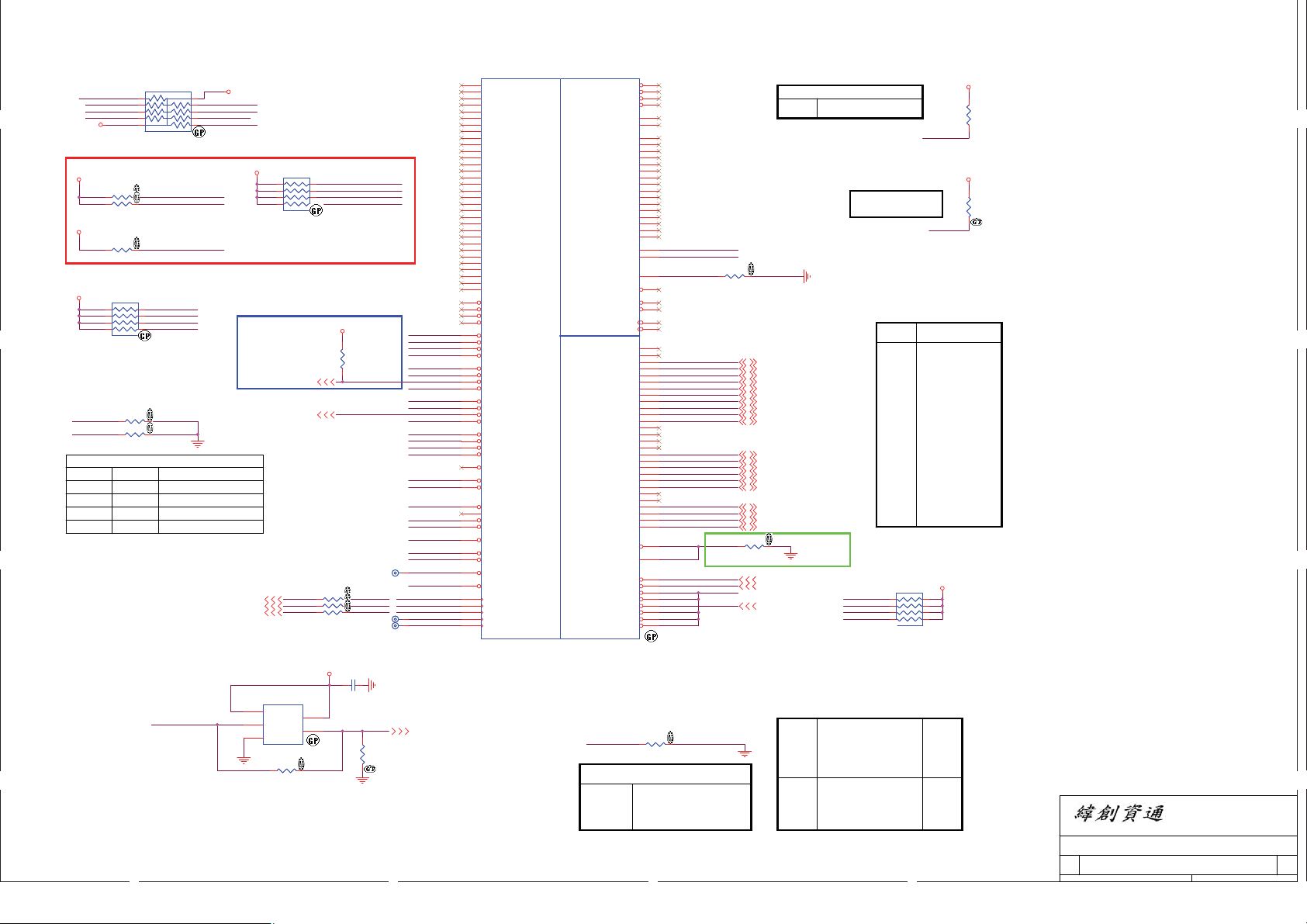

Page 4

5

A

CPU1A

CPU1A

DMI_TXN016

DMI_TXN116

DMI_TXN216

DMI_TXN316

DMI_TXP016

DMI_TXP116

DMI_TXP216

D D

C C

DMI_TXP316

DMI_RXN016

DMI_RXN116

DMI_RXN216

DMI_RXN316

DMI_RXP016

DMI_RXP116

DMI_RXP216

DMI_RXP316

FDI_TXN016

FDI_TXN116

FDI_TXN216

FDI_TXN316

FDI_TXN416

FDI_TXN516

FDI_TXN616

FDI_TXN716

FDI_TXP016

FDI_TXP116

FDI_TXP216

FDI_TXP316

FDI_TXP416

FDI_TXP516

FDI_TXP616

FDI_TXP716

FDI_FSYNC016

FDI_FSYNC116

FDI_INT16

FDI_LSYNC016

FDI_LSYNC116

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX0#

DMI_RX1#

DMI_RX2#

DMI_RX3#

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

DMI_TX0#

DMI_TX1#

DMI_TX2#

DMI_TX3#

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

FDI_TX0#

FDI_TX1#

FDI_TX2#

FDI_TX3#

FDI_TX4#

FDI_TX5#

FDI_TX6#

FDI_TX7#

FDI_TX0

FDI_TX1

FDI_TX2

FDI_TX3

FDI_TX4

FDI_TX5

FDI_TX6

FDI_TX7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

B B

4

1 OF 9

1 OF 9

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX0#

PEG_RX1#

PEG_RX2#

DMI

DMI

PEG_RX3#

PEG_RX4#

PEG_RX5#

AUBURNDALE

AUBURNDALE

PEG_RX6#

PEG_RX7#

PEG_RX8#

PEG_RX9#

PEG_RX10#

PEG_RX11#

PEG_RX12#

PEG_RX13#

PEG_RX14#

PEG_RX15#

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

Intel(R) FDI

Intel(R) FDI

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX0#

PEG_TX1#

PEG_TX2#

PEG_TX3#

PEG_TX4#

PEG_TX5#

PEG_TX6#

PEG_TX7#

PEG_TX8#

PEG_TX9#

PEG_TX10#

PEG_TX11#

PEG_TX12#

PEG_TX13#

PEG_TX14#

PEG_TX15#

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

http://hobi-elektronika.net

PEG_IRCOMP_R

B26

A26

B27

EXP_RBIAS

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

3

R500

R500

49D9R2F-GP

1 2

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

PEG_TXN15_L PEG_TXN15

PEG_TXN14_L PEG_TXN14

PEG_TXN13_L PEG_TXN13

PEG_TXN12_L PEG_TXN12

PEG_TXN11_L PEG_TXN11

PEG_TXN10_L PEG_TXN10

PEG_TXN9_L PEG_TXN9

PEG_TXN8_L PEG_TXN8

PEG_TXN7_L PEG_TXN7

PEG_TXN6_L PEG_TXN6

PEG_TXN5_L PEG_TXN5

PEG_TXN4_L PEG_TXN4

PEG_TXN3_L PEG_TXN3

PEG_TXN2_L PEG_TXN2

PEG_TXN1_L

PEG_TXN0_L PEG_TXN0

PEG_TXP15_L PEG_TXP15

PEG_TXP14_L PEG_TXP14

PEG_TXP13_L PEG_TXP13

PEG_TXP12_L PEG_TXP12

PEG_TXP11_L PEG_TXP11

PEG_TXP10_L PEG_TXP10

PEG_TXP9_L PEG_TXP9

PEG_TXP8_L PEG_TXP8

PEG_TXP7_L PEG_TXP7

PEG_TXP6_L PEG_TXP6

PEG_TXP5_L PEG_TXP5

PEG_TXP4_L PEG_TXP4

PEG_TXP3_L PEG_TXP3

PEG_TXP2_L PEG_TXP2

PEG_TXP1_L PEG_TXP1

PEG_TXP0_L PEG_TXP0

1 2

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

DIS

49D9R2F-GP

R498

R498

750R2F-GP

750R2F-GP

C632 SCD1U10V2KX-5GP

C632 SCD1U10V2KX-5GP

1 2

C628 SCD1U10V2KX-5GP

C628 SCD1U10V2KX-5GP

1 2

C630 SCD1U10V2KX-5GP

C630 SCD1U10V2KX-5GP

1 2

C342 SCD1U10V2KX-5GP

C342 SCD1U10V2KX-5GP

1 2

C343 SCD1U10V2KX-5GP

C343 SCD1U10V2KX-5GP

1 2

C340 SCD1U10V2KX-5GP

C340 SCD1U10V2KX-5GP

1 2

C338 SCD1U10V2KX-5GP

C338 SCD1U10V2KX-5GP

1 2

C345 SCD1U10V2KX-5GP

C345 SCD1U10V2KX-5GP

1 2

C335 SCD1U10V2KX-5GP

C335 SCD1U10V2KX-5GP

1 2

C316 SCD1U10V2KX-5GP

C316 SCD1U10V2KX-5GP

1 2

C312 SCD1U10V2KX-5GP

C312 SCD1U10V2KX-5GP

1 2

C294 SCD1U10V2KX-5GP

C294 SCD1U10V2KX-5GP

1 2

C270 SCD1U10V2KX-5GP

C270 SCD1U10V2KX-5GP

1 2

C272 SCD1U10V2KX-5GP

C272 SCD1U10V2KX-5GP

1 2

C260 SCD1U10V2KX-5GP

C260 SCD1U10V2KX-5GP

1 2

C258 SCD1U10V2KX-5GP

C258 SCD1U10V2KX-5GP

1 2

C633 SCD1U10V2KX-5GP

C633 SCD1U10V2KX-5GP

1 2

C629 SCD1U10V2KX-5GP

C629 SCD1U10V2KX-5GP

1 2

C631 SCD1U10V2KX-5GP

C631 SCD1U10V2KX-5GP

1 2

C341 SCD1U10V2KX-5GP

C341 SCD1U10V2KX-5GP

1 2

C344 SCD1U10V2KX-5GP

C344 SCD1U10V2KX-5GP

1 2

C339 SCD1U10V2KX-5GP

C339 SCD1U10V2KX-5GP

1 2

C337 SCD1U10V2KX-5GP

C337 SCD1U10V2KX-5GP

1 2

C336 SCD1U10V2KX-5GP

C336 SCD1U10V2KX-5GP

1 2

C332 SCD1U10V2KX-5GP

C332 SCD1U10V2KX-5GP

1 2

C320 SCD1U10V2KX-5GP

C320 SCD1U10V2KX-5GP

1 2

C302 SCD1U10V2KX-5GP

C302 SCD1U10V2KX-5GP

1 2

C277 SCD1U10V2KX-5GP

C277 SCD1U10V2KX-5GP

1 2

C268 SCD1U10V2KX-5GP

C268 SCD1U10V2KX-5GP

1 2

C276 SCD1U10V2KX-5GP

C276 SCD1U10V2KX-5GP

1 2

C263 SCD1U10V2KX-5GP

C263 SCD1U10V2KX-5GP

1 2

C252 SCD1U10V2KX-5GP

C252 SCD1U10V2KX-5GP

1 2

PEG_RXN[15..0] 51

PEG_RXP[15..0] 51

PEG_TXN1

PEG_TXN[15..0] 51

PEG_TXP[15..0] 51

2

1

AUBURUNF

AUBURUNF

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Title

Title

Title

04_CPU (1/7)-PEG / DMI / FDI

04_CPU (1/7)-PEG / DMI / FDI

04_CPU (1/7)-PEG / DMI / FDI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

458Tuesday,January 26, 2010

458Tuesday,January 26, 2010

458Tuesday,January 26, 2010

of

of

of

A

-1

-1

-1

Page 5

A

1D05V_VTT

D D

H_PROCHOT#

If using an optional glue

logic receiver, a series

resistor of 2.2 k ±5% is

needed.

C C

B B

1 2

R162 49D9R2F-GPR162 49D9R2F-GP

1 2

R207 68R2-GPR207 68R2-GP

1D5V_S3

12

S3

S3

DRAMPWROK

12

S3

S3

R125

R125

1K1R2F-GP

1K1R2F-GP

R120

R120

3KR2F-GP

3KR2F-GP

5

1 2

H_CATERR#

PROCHOT#

H_PECI19

H_PROCHOT#38

PM_THRMTRIP-A#19,36

130°C

H_PM_SYNC16

H_PWRGD19,36

PM_DRAM_PWRGD16

PLT_RST#18,29,31,33,35,51

R496 20R2F-GPR496 20R2F-GP

R497 20R2F-GPR497 20R2F-GP

R179 49D9R2F-GPR179 49D9R2F-GP

R499 49D9R2F-GPR499 49D9R2F-GP

R209 0R2J-2-GP

R209 0R2J-2-GP

1 2

R493

R493

0R0402-PAD

0R0402-PAD

-1 0107

R128

R128

PM_SLP_S3#16,31,33,36,41,42,43,44

VTT_PWRGD33,42

1 2

1 2

1 2

TP41TPAD14-GP TP41TPAD14-GP

SKTOCC# (Socket Occupied)

1 2

DY

DY

-1 0112

TP50TPAD14-GP TP50TPAD14-GP

1 2

1 2

R119 0R0402-PADR119 0R0402-PAD

TP53TPAD14-GP TP53TPAD14-GP

1 2

1K5R2F-2-GP

1K5R2F-2-GP

U58

U58

1

B

2

A

3

GND

74LVC1G08GW-1-GP

74LVC1G08GW-1-GP

S3_DY

S3_DY

1

1

R213

R213

0R0402-PAD

0R0402-PAD

1

12

R132

R132

750R2F-GP

750R2F-GP

VCC

Y

VCCPWRGOOD_1

VCCPWRGOOD_0

DRAMPWROK

H_VTTPWRGD

H_PWRGD_XDP

PLT_RST#_R

5

4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

SKTOCC#_R

H_CATERR#

PROCHOT#

H_CPURST#

3D3V_S5

CPU_VDDQ_PWRGDCPU_VDDQ_PWRGDCPU_VDDQ_PWRGDCPU_VDDQ_PWRGD

4

AT23

AT24

G16

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

12

C593

C593

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

S3_DY

S3_DY

CPU1B

CPU1B

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

AUBURUNF

AUBURUNF

SC 1130 change to 1.5Kohm

R486

R486

1 2

1K5R2F-2-GP

1K5R2F-2-GP

S3_DY

S3_DY

CPU_VDDQ_PWRGD 43

TDI

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

AP28

AT27

AT29

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

3

BCLK_CPU_P

BCLK_CPU_N

PEG_CLK_R

PEG_CLK#_R

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

DDR3_DRAMRST#_R

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_TDI_M

XDP_TDO_M

XDP_DBRESET#

1

VTT_PWRGD33,42

BCLK_CPU_P 19

BCLK_CPU_N 19

PEG_CLK_R 15

PEG_CLK#_R 15

DPLL_REF_SSCLK 15

DPLL_REF_SSCLK# 15

RN30

RN30

SRN10KJ-5-GP

SRN10KJ-5-GP

1

2 3

TP106 TPAD14-GPTP106 TPAD14-GP

-1 0114

1D05V_VTT

4

R494

R494

10KR2J-3-GP

10KR2J-3-GP

VTT_PWRGD H_VTTPWRGD_RDRAMPWROK

C617

C617

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

DY

DY

3D3V_S0

2 OF 9

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

CLOCKS

CLOCKS

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PM_EXT_TS0#

PM_EXT_TS1#

SA 0903

2 OF 9

BCLK

BCLK#

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

TDI_M

TDO_M

DBR#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

BPM6#

BPM7#

http://hobi-elektronika.net

MISC

MISC

AUBURNDALE

AUBURNDALE

THERMAL PWR MANAGEMENT

THERMAL PWR MANAGEMENT

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

R487

R487

750R2F-GP

750R2F-GP

S3_DY

S3_DY

1 2

PM_EXTTS#0_R 12

PM_EXTTS#1_R 13

12

Q51

Q51

1

2

3 4

DMN66D0LDW-7-GP

DMN66D0LDW-7-GP

1 2

SB 1015 change to 84.DMN66.03F

2

DPLL_REF_SSCLK#

DPLL_REF_SSCLK

-1 0112

SA 0901 : LC require to reserve

DDR3_DRAMRST#_R

100KR2J-1-GP

100KR2J-1-GP

XDP_TMS

XDP_TDI

XDP_PREQ#

XDP_TDO

XDP_TCLK

XDP_TRST#

6

5

1

2 3

SRN0J-6-GP

SRN0J-6-GP

DY

DY

12

R489

R489

S3_DY

S3_DY

1 2

DY

DY

R503 51R2J-2-GP

R503 51R2J-2-GP

1 2

DY

DY

R504 51R2J-2-GP

R504 51R2J-2-GP

1 2

DY

DY

R205 51R2J-2-GP

R205 51R2J-2-GP

1 2

R502 51R2J-2-GPR502 51R2J-2-GP

1 2

DY

DY

R215 51R2J-2-GP

R215 51R2J-2-GP

1 2

R501 51R2J-2-GPR501 51R2J-2-GP

3D3V_S5

12

R492

R492

100KR2J-1-GP

100KR2J-1-GP

RN77

RN77

4

1 2

R484 0R2J-2-GP

R484 0R2J-2-GP

S3

S3

S3_DY

S3_DY

BSS138LT1

BSS138LT1

2 3

S

S

1D05V_VTT

1

G

G

C601

C601

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1 2

S3_DY

S3_DY

1D05V_VTT

12

R495

R495

1KR2J-1-GP

1KR2J-1-GP

H_VTTPWRGD

D

D

2ND = 84.00138.G31

2ND = 84.00138.G31

Vgs(th)<=1.5V

SM_RCOMP_0

R90 100R2F-L1-GP-UR90 100R2F-L1-GP-U

SM_RCOMP_1

R91 24D9R2F-L-GPR91 24D9R2F-L-GP

SM_RCOMP_2

R92 130R2F-1-GPR92 130R2F-1-GP

1D5V_S3

R479

R479

1KR2J-1-GP

1KR2J-1-GP

S3_DY

S3_DY

1 2

Q49

Q49

XDP_DBRESET#

1 2

1 2

1 2

impedance compensation

DDR3_DRAMRST# 12,13

SC CHECK

RST_GATE 19

CPU JTAG

XDP_TDO_M

-1 0107

XDP_TDI_M

1 2

R203

R203

1KR2J-1-GP

1KR2J-1-GP

check list: 5k pu

1

12

R505

R505

0R0402-PAD

0R0402-PAD

3D3V_S0

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsic hih,

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsic hih,

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsic hih,

Taipei Hsien 221, Taiwan, R.O.C

Taipei Hsien 221, Taiwan, R.O.C

Title

Title

Title

05_CPU (2/7)-HOST

05_CPU (2/7)-HOST

05_CPU (2/7)-HOST

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

5

4

3

2

Taipei Hsien 221, Taiwan, R.O.C

1

of

558Tuesday, January26, 2010

of

558Tuesday, January26, 2010

of

558Tuesday, January26, 2010

A

-1

-1

-1

Page 6

5

A

A

CPU1C

CPU1C

3 OF 9

3 OF 9

4

http://hobi-elektronika.net

3

CPU1D

CPU1D

2

4 OF 9

4 OF 9

1

AA6

SA_CK0

M_A_DQ[63..0]12

D

C

B

M_A_BS012

M_A_BS112

M_A_BS212

M_A_CAS#12

M_A_RAS#12

M_A_WE#12

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

SA_DQ0

SA_DQ1

C7

SA_DQ2

A7

SA_DQ3

B10

SA_DQ4

SA_DQ5

E10

SA_DQ6

A8

SA_DQ7

D8

SA_DQ8

F10

SA_DQ9

E6

SA_DQ10

F7

SA_DQ11

E9

SA_DQ12

B7

SA_DQ13

E7

SA_DQ14

C6

SA_DQ15

SA_DQ16

G8

SA_DQ17

K7

SA_DQ18

J8

SA_DQ19

G7

SA_DQ20

SA_DQ21

J7

SA_DQ22

J10

SA_DQ23

L7

SA_DQ24

M6

SA_DQ25

M8

SA_DQ26

L9

SA_DQ27

L6

SA_DQ28

K8

SA_DQ29

N8

SA_DQ30

P9

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

AJ7

SA_DQ38

AJ6

SA_DQ39

SA_DQ40

AJ9

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

AL7

SA_DQ45

SA_DQ46

AL8

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

U7

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

AUBURNDALE

AUBURNDALE

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK0#

SA_CKE0

SA_CK1

SA_CK1#

SA_CKE1

SA_CS0#

SA_CS1#

SA_ODT0

SA_ODT1

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 12

M_CLK_DDR#0 12

M_CKE0 12

M_CLK_DDR1 12

M_CLK_DDR#1 12

M_CKE1 12

M_CS#0 12

M_CS#1 12

M_ODT0 12

M_ODT1 12

M_A_DM[7..0] 12

M_A_DQS#[7..0] 12

M_A_DQS[7..0] 12

M_A_A[15..0] 12

M_B_DQ[63..0]13

M_B_BS013

M_B_BS113

M_B_BS213

M_B_CAS#13

M_B_RAS#13

M_B_WE#13

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AG1

AG4

AG3

AM6

AM4

AM3

AR10

AT10

AF3

AJ3

AK1

AJ4

AH4

AK3

AK4

AN2

AK5

AK2

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AB1

AC5

AC6

B5

SB_DQ0

A5

SB_DQ1

C3

SB_DQ2

B3

SB_DQ3

E4

SB_DQ4

A6

SB_DQ5

A4

SB_DQ6

C4

SB_DQ7

D1

SB_DQ8

D2

SB_DQ9

F2

SB_DQ10

F1

SB_DQ11

C2

SB_DQ12

F5

SB_DQ13

F3

SB_DQ14

G4

SB_DQ15

H6

SB_DQ16

G2

SB_DQ17

J6

SB_DQ18

J3

SB_DQ19

G1

SB_DQ20

G5

SB_DQ21

J2

SB_DQ22

J1

SB_DQ23

J5

SB_DQ24

K2

SB_DQ25

L3

SB_DQ26

M1

SB_DQ27

K5

SB_DQ28

K4

SB_DQ29

M4

SB_DQ30

N5

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_BS0

W5

SB_BS1

R7

SB_BS2

SB_CAS#

Y7

SB_RAS#

SB_WE#

AUBURNDALE

AUBURNDALE

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_CK0

SB_CK0#

SB_CKE0

SB_CK1

SB_CK1#

SB_CKE1

SB_CS0#

SB_CS1#

SB_ODT0

SB_ODT1

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_CLK_DDR2 13

M_CLK_DDR#2 13

M_CKE2 13

M_CLK_DDR3 13

M_CLK_DDR#3 13

M_CKE3 13

M_CS#2 13

M_CS#3 13

M_ODT2 13

M_ODT3 13

M_B_DM[7..0] 13

M_B_DQS#[7..0] 13

M_B_DQS[7..0] 13

M_B_A[15..0] 13

AUBURUNF

AUBURUNF

5

4

3

AUBURUNF

AUBURUNF

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

TaipeiHsien221, Taiwan,R.O.C

TaipeiHsien221, Taiwan,R.O.C

Title

Title

Title

06_CPU (3/7)-MEM INTERFACE

06_CPU (3/7)-MEM INTERFACE

06_CPU (3/7)-MEM INTERFACE

Size DocumentNumber Rev

Size DocumentNumber Rev

Size DocumentNumber Rev

Custom

Custom

Custom

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

2

TaipeiHsien221, Taiwan,R.O.C

658Tuesday, January26, 2010

658Tuesday, January26, 2010

658Tuesday, January26, 2010

of

of

of

1

-1

-1

-1

Page 7

5

A

4

6 OF 9

CPU1F

CPU1F

http://hobi-elektronika.net

6 OF 9

3

2

1

PROCESSOR CORE POWER

48A -->Arrandale

D D

VCC_CORE

C238

C235

C235

C244

C244

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C240

C240

C618

C618

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C C

C242

C242

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C238

C236

C236

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C619

C619

C620

C620

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C267

C267

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C243

C243

C627

C627

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C239

C239

C237

C237

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C241

C241

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C251

C251

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C634

C634

C635

C635

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

B B

VCC_CORE

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AUBURUNF

AUBURUNF

AUBURNDALE

AUBURNDALE

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

POWER

POWER

VTT_SELECT

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

AH14

VTT0

AH12

VTT0

AH11

VTT0

AH10

VTT0

J14

VTT0

J13

VTT0

H14

VTT0

H12

VTT0

G14

VTT0

G13

VTT0

G12

VTT0

G11

VTT0

F14

VTT0

F13

VTT0

F12

VTT0

F11

VTT0

E14

VTT0

E12

VTT0

D14

VTT0

D13

VTT0

D12

VTT0

D11

VTT0

C14

VTT0

C13

VTT0

C12

VTT0

C11

VTT0

B14

VTT0

B12

VTT0

A14

VTT0

A13

VTT0

A12

VTT0

A11

VTT0

AF10

VTT0

AE10

VTT0

AC10

VTT0

AB10

VTT0

Y10

VTT0

W10

VTT0

U10

VTT0

T10

VTT0

J12

VTT0

J11

VTT0

J16

VTT0

J15

VTT0

AN33

PSI#

H_VID0

AK35

VID0

VID1

VID2

VID3

VID4

VID5

VID6

ISENSE

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

AN35

AJ34

AJ35

B15

A15

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_VTTVID1

SB 1019 remove test point

C621

C621

C616

C616

C613

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

ClarksfieldH_VTTVID1=Low, VTT = 1.1V

Arrandale H_VTTVID1= High, VTT=1.05V

1

C613

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

The decoupling capacitors , filter

recommendations and sens e resistors on the

CPU/PCH Railsare specific to the CRB

Implementation. Cust omers need to follow the

recommendations in the Calpella Platform

Design Guide.

C602

C602

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

PSI# 38

H_VID[6..0] 38

PM_DPRSLPVR 38

TP35 TPAD14-GPTP35 TPAD14-GP

IMVP_IMON 38

VTT_SENSE 42

1D05V_VTT

C604

C604

C603

C603

C605

C605

12

C218

C218

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

Please note that the VTT Rail

Values are Auburndale

VTT=1.05V; Clarksfield

VTT=1.1V

VCC_CORE

12

R238

R238

100R2F-L1-GP-U

100R2F-L1-GP-U

12

R232

R232

100R2F-L1-GP-U

100R2F-L1-GP-U

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

1D05V_VTT

C611

C611

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

VCC_SENSE 38

VSS_SENSE 38

SA 0917

1D05V_VTT

C636

C636

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

DY

DY

1 2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsichih,

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsichih,

21F,88,Sec.1,Hsin Tai Wu Rd.,Hsichih,

Taipei Hsien 221,Taiwan, R.O.C

Taipei Hsien 221,Taiwan, R.O.C

Title

Title

Title

07_CPU (4/7)-POWER

07_CPU (4/7)-POWER

07_CPU (4/7)-POWER

Size DocumentNumber Rev

Size DocumentNumber Rev

Size DocumentNumber Rev

Custom

Custom

Custom

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221,Taiwan, R.O.C

of

of

of

758Wednesday,January 27,2010

758Wednesday,January 27,2010

758Wednesday,January 27,2010

A

-1

-1

-1

Page 8

D D

A

C C

B B

VCC_GFXCORE

C216

C216

C614

C614

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

DY

DY

Please note that the VTT Rail

Values are Auburndale

VTT=1.05V; Clarksfield

VTT=1.1V

1D05V_VTT

TC7

TC7

ST220U2D5VBM-2GP

ST220U2D5VBM-2GP

C223

C223

5

C609

C609

C610

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

DY

DY

DY

DY

1D05V_VTT

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C607

C607

C610

C612

C612

18A

12

12

DY

DY

C210

C210

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C208

C208

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C233

C233

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C234

C234

12

12

C205

C205

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C608

C608

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C255

C255

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

4

CPU1G

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

H25

K26

H27

G28

G27

G26

F26

E26

E25

J24

J23

J27

J26

J25

CPU1G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

AUBURUNF

AUBURUNF

http://hobi-elektronika.net

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_VID0

GFX_VID1

AUBURNDALE

AUBURNDALE

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRAPHICS VIDs

GRAPHICS VIDs

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

7 OF 9

7 OF 9

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

3

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

12

C201

C201

C230

C230

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C211

C211

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C256

C256

VCC_AXG_SENSE 44

VSS_AXG_SENSE 44

GFX_VR_EN:

4.7-k pull-down to GND at PWM

GFX_VR_EN 44

GFX_DPRSLPVR 44

GFX_IMON 44

12

12

C202

C202

C203

C203

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

12

12

+V1.8S_VCCSFR

12

12

C259

C259

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C606

C606

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C209

C209

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C246

C246

12

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C204

C204

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

1D05V_VTT

1D05V_VTT

12

C247

C247

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

GFX_VID[6..0] 44

6A

12

12

C182

C182

C184

C184

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C381

C381

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

0.6A

1 2

0R0603-PAD

0R0603-PAD

2

C185

C185

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

R257

R257

-1 0110

12

C186

C186

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

1D8V_S0

1

SA 0901: LC require to reserve s3 reduce

power circuit

1D5V_CPU_VDDQ

1 2

S3

S3

R454 0R2J-2-GP

R454 0R2J-2-GP

1 2

S3

S3

R453 0R2J-2-GP

R453 0R2J-2-GP

1 2

S3

S3

R455 0R2J-2-GP

R455 0R2J-2-GP

1 2

S3

S3

R456 0R2J-2-GP

R456 0R2J-2-GP

1 2

S3

S3

R457 0R2J-2-GP

R457 0R2J-2-GP

U56

U56

S3_DY

S3_DY

S

S

1

S

S

2

S

S

3

GD

GD

4 5

AO4468-GP

AO4468-GP

84.04468.037

84.04468.037

2nd = 84.04800.D37

2nd = 84.04800.D37

U37_G

1 2

S3_DY

S3_DY

R459 0R2J-2-GP

R459 0R2J-2-GP

C570

C570

12

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

S3_DY

S3_DY

1D5V_CPU_VDDQ

R466

R466

200R2J-L1-GP

200R2J-L1-GP

S3_DY

S3_DY

1 2

Q64_D

Q45

Q45

2N7002A-7-GP

2N7002A-7-GP

S3_DY

S3_DY

G

-1 0114

S D

SA 0903: Place across the plane

D

D

8

D

D

7

D

D

6

ESD Protect

PM_SLP_S3 36

1D5V_S3

RUN_POWER_ON

SB 1022 Remove

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Title

Title

Title

08_CPU (5/7)-Graphic PWR

08_CPU (5/7)-Graphic PWR

08_CPU (5/7)-Graphic PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

858Wednesday,January27,2010

858Wednesday,January27,2010

858Wednesday,January27,2010

of

of

of

A

-1

-1

-1

Page 9

5

A

4

3

2

1

http://hobi-elektronika.net

9 OF 9

8 OF 9

CPU1H

CPU1H

AT20

VSS

AT17

VSS

AR31

VSS

AR28

VSS

AR26

VSS

AR24

VSS

AR23

D D

C C

B B

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AL9

AL6

AL3

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AJ8

AJ5

AJ2

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AUBURNDALE

AUBURNDALE

VSS

VSS

8 OF 9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

K27

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

G34

G31

G20

E35

E32

E29

E24

E21

E18

E13

E11

D33

D30

D26

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

A29

A27

A23

CPU1I

CPU1I

VSS

K9

VSS

K6

VSS

K3

VSS

J32

VSS

J30

VSS

J21

VSS

J19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H8

VSS

H5

VSS

H2

VSS

VSS

VSS

VSS

G9

VSS

G6

VSS

G3

VSS

F30

VSS

F27

VSS

F25

VSS

F22

VSS

F19

VSS

F16

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E8

VSS

E5

VSS

E2

VSS

VSS

VSS

VSS

D9

VSS

D6

VSS

D3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B8

VSS

B6

VSS

B4

VSS

VSS

VSS

VSS

A9

VSS

AUBURNDALE

AUBURNDALE

VSS

VSS

NCTF TEST PIN:

A35,AT1,AT35,B1,A3,A33,A34,AP1,AP35,

AR1,AR35,AT2,AT3,AT33,AT34,B35,C1,C35

NCTF TEST PIN:

A35,AT1,AT35,B1,A3,A33,A34,AP1,AP35,

AR1,AR35,AT2,AT3,AT33,AT34,B35,C1,C35

9 OF 9

VSS_NCTF#AR34

VSS_NCTF#B34

VSS_NCTF#B2

VSS_NCTF#B1

VSS_NCTF#A35

VSS_NCTF#AT1

VSS_NCTF#AT35

RSVD_NCTF#AT33

RSVD_NCTF#AT34

RSVD_NCTF#AP35

RSVD_NCTF#AR35

RSVD_NCTF#AT3

RSVD_NCTF#AR1

RSVD_NCTF#AP1

RSVD_NCTF#AT2

RSVD_NCTF#C1

RSVD_NCTF#A3

RSVD_NCTF#C35

RSVD_NCTF#B35

RSVD_NCTF#A34

RSVD_NCTF#A33

AR34

B34

B2

B1

A35

AT1

AT35

AT33

AT34

AP35

AR35

AT3

AR1

AP1

AT2

C1

A3

C35

B35

A34

A33

TP_MCP_VSS_NCTF6

TP_MCP_VSS_NCTF1

TP_MCP_VSS_NCTF2

TP_MCP_VSS_NCTF7

TP27 AFTE14P-GPTP27 AFTE14P-GP

1

TP63 AFTE14P-GPTP63 AFTE14P-GP

1

TP26 AFTE14P-GPTP26 AFTE14P-GP

1

TP64 AFTE14P-GPTP64 AFTE14P-GP

1

AUBURUNF

AUBURUNF

AUBURUNF

AUBURUNF

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Title

Title

Title

09_CPU (6/7)-VSS

09_CPU (6/7)-VSS

09_CPU (6/7)-VSS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

958Tuesday,January 26, 2010

958Tuesday,January 26, 2010

958Tuesday,January 26, 2010

of

of

of

A

-1

-1

-1

Page 10

5

A

CPU1E

CPU1E

AP25

RSVD#AP25

AL25

RSVD#AL25

AL24

RSVD#AL24

AL22

RSVD#AL22

AJ33

RSVD#AJ33

AG9

D D

H_RSVD9_R

1

TP37TPAD14-GP TP37TPAD14-GP

TP38TPAD14-GP TP38TPAD14-GP

H_RSVD10_R CFG3

1

M27

G25

G17

H17

E31

E30

L28

J17

RSVD#AG9

RSVD#M27

RSVD#L28

SA_DIMM_VREF#

SB_DIMM_VREF#

RSVD#G25

RSVD#G17

RSVD#E31

RSVD#E30

4

5 OF 9

5 OF 9

RSVD#AJ13

RSVD#AJ12

RSVD#AH25

RSVD#AK26

RSVD#AL26

RSVD_NCTF#AR2

AUBURNDALE

AUBURNDALE

RSVD#AJ26

RSVD#AJ27

3

http://hobi-elektronika.net

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

CFG0

2

12

R236

R236

3KR2F-GP

3KR2F-GP

DY

DY

12

R233

R233

3KR2F-GP

3KR2F-GP

PCI-Express Configuration Select

CFG0

1:Single PEG

0:Bifurcation enabled

CFG3 - PCI-Express Static Lane Reversal

CFG3

1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

1

KEY

RSVD#D15

RSVD#C15

VSS

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AR32

E15

F15

A2

D15

C15

RSVD64_R

AJ15

RSVD65_R

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

RSVD_VSS

AP34

1 2

0R0402-PAD

0R0402-PAD

VSS (AP34) can be left NC is

CRB implementation; EDS/DG

recommendation to GND.

R231

R231

1

1

TP36 TPAD14-GPTP36 TPAD14-GP

TP33 TPAD14-GPTP33 TPAD14-GP

-1 0114

CFG4

CFG7

12

R235

R235

3KR2F-GP

3KR2F-GP

DY

DY

12

R234

R234

3KR2F-GP

3KR2F-GP

DY

DY

CFG4 - DisplayPort Presence

CFG4

CFG7 Clarksfield (only for early samples pre-ES1) -

1:Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

CFG7(Reserved) - Temporarily used for early

Clarksfield samples.

Connect to GND with 3.01K Ohm/5% resistor.

Note: Only temporary for early CFD sample

(rPGA/BGA) [For details please refer to the

WW33 MoW and sightingreport].

For a common M/B design (for AUBand CFD),

the pull-down resistor shouble be used. Does

not impact AUB functionality.

CFG0

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

H16

B19

A19

A20

B20

AC9

AB9

U9

J29

J28

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

RSVD_TP#H16

RSVD#B19

RSVD#A19

RSVD#A20

RSVD#B20

RSVD#U9

T9

RSVD#T9

RSVD#AC9

RSVD#AB9

RSVD#J29

RSVD#J28

AUBURUNF

AUBURUNF

CFG1

1

TP51TPAD14-GP TP51TPAD14-GP

TP59TPAD14-GP TP59TPAD14-GP

TP58TPAD14-GP TP58TPAD14-GP

TP55TPAD14-GP TP55TPAD14-GP

TP61TPAD14-GP TP61TPAD14-GP

TP56TPAD14-GP TP56TPAD14-GP

TP49TPAD14-GP TP49TPAD14-GP

TP48TPAD14-GP TP48TPAD14-GP

C C

TP105TPAD14-GP TP105TPAD14-GP

TP104TPAD14-GP TP104TPAD14-GP

TP57TPAD14-GP TP57TPAD14-GP

TP60TPAD14-GP TP60TPAD14-GP

TP62TPAD14-GP TP62TPAD14-GP

TP52TPAD14-GP TP52TPAD14-GP

TP47TPAD14-GP TP47TPAD14-GP

TP54TPAD14-GP TP54TPAD14-GP

1

1

CFG2

1

CFG3

CFG4

CFG5

1

CFG6

1

CFG7

CFG8

1

CFG9

1

CFG10

1

CFG11

1

CFG12

1

CFG13

1

CFG14

1

CFG15

1

CFG16

1

CFG17

1

H_RSVD17_R

H_RSVD18_R

B B

RSVD#AL28

RSVD#AL29

RSVD#AP30

RSVD#AP32

RSVD#AL27

RSVD#AT31

RSVD#AT32

RSVD#AP33

RSVD#AR33

RSVD#AR32

RSVD_TP#E15

RSVD_TP#F15

RESERVED

RESERVED

RSVD#AJ15

RSVD#AH15

RSVD_TP#AA5

RSVD_TP#AA4

RSVD_TP#R8

RSVD_TP#AD3

RSVD_TP#AD2

RSVD_TP#AA2

RSVD_TP#AA1

RSVD_TP#R9

RSVD_TP#AG7

RSVD_TP#AE3

RSVD_TP#V4

RSVD_TP#V5

RSVD_TP#N2

RSVD_TP#AD5

RSVD_TP#AD7

RSVD_TP#W3

RSVD_TP#W2

RSVD_TP#N3

RSVD_TP#AE5

RSVD_TP#AD9

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

21F,88,Sec.1,Hsin Tai WuRd.,Hsichih,

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Taipei Hsien 221,Taiwan,R.O.C

Title

Title

Title

10_CPU (7/7)-RESERVED

10_CPU (7/7)-RESERVED

10_CPU (7/7)-RESERVED

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

LA46 MB DIS

LA46 MB DIS

LA46 MB DIS

Date: Sheet

Date: Sheet

Date: Sheet

10 58Tuesday,January 26, 2010

10 58Tuesday,January 26, 2010

10 58Tuesday,January 26, 2010

of

of

of

A

-1

-1

-1

Page 11

5

A

Close to PCH on top side.

SA 0905 change to 390p

3

E

D D

C

Q6

Q6

MMBT3904WT1G-GP

MMBT3904WT1G-GP

2

E

C

Q42

Q42

MMBT3904WT1G-GP

MMBT3904WT1G-GP

between CPU, VGA and DIMM on bottom side

C C

HW_THRMTRIP#33,36

B

B

3D3V_AUX_S5

12

C183

C183

SC390P50V2KX-GP

SC390P50V2KX-GP

12

C404

C404

SC390P50V2KX-GP

SC390P50V2KX-GP

DY

DY

R633

R633

10KR2J-3-GP

10KR2J-3-GP

1 2

2200p close to smsc2103 chip

3D3V_S0

G

Q25

Q25

2N7002A-7-GP

2N7002A-7-GP

3D3V_S0

12

R275

R275

10KR2J-3-GP

10KR2J-3-GP

SD

SYS_SHDN# FAN_PWM_CFAN_PWM

SB 1015 change to 84.2N702.E31

4

12

http://hobi-elektronika.net

T8

1

CPU backside or inside the socket

CPU TEMP:

REMOTE2-

C569

C569

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

REMOTE2+

3D3V_S0

12

R280

R280

6K8R2J-GP

6K8R2J-GP

SHDN_SEL

SHDN --> 2N3904 ON External diode

H_THERMDA and H_THERMDC routing 10mil trace width

and spacing. Locate Capacity near Thermal diode.

3

C

B

Q9

Q9

E

MMBT3904WT1G-GP

MMBT3904WT1G-GP

Close to connector

KA

D2

D2

1SS355PT-GP

1SS355PT-GP

DY

DY

R427

R427

1 2

0R0402-PAD

0R0402-PAD

FAN_TACH

FAN_PWM_C49

FAN_TACH49

C39

C39

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

SA 0905

-1 0107

2200p close to smsc2103 chip

5V_S0

12

R426

R426

10KR2J-3-GP

10KR2J-3-GP

2

H_THERMDA

12

C389

C389

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

H_THERMDC

SA 0823

FAN1

FAN1

5

1

2

3

4

6

ACES-CON4-GP-U1

ACES-CON4-GP-U1

20.F0714.004

20.F0714.004

1

4 WIRE PWM Fan Control circuit

3D3V_S0

12

R260

R260

68R2-GP

C388

C388

2103_VDD

1 2

SCD1U10V2KX-4GP

1 2

SCD1U10V2KX-4GP

SYS_SHDN# SHDN_SEL

THERM_SCI#_R

SMBC_THERM33,34,55

SMBD_THERM33,34,55

H_THERMDA

H_THERMDC

REMOTE2+

REMOTE2-

SC 1203

R272 0R0402-PADR272 0R0402-PAD

B B

1

TP66

TP66

TPAD14-GP

TPAD14-GP

THERM_SCI#

pin6, ALERT# OD

pin7, SYS_SHDN# OD

68R2-GP

U31

U31

3

VDD

2

DP1

1

DN1

16

DP2/DN3

15

ND2/DP3

7

SYS_SHDN#

6

ALERT#

9

SMCLK

8

SMDATA

EMC2103-2-AP-GP

EMC2103-2-AP-GP

GPIO1

GPIO2

TACH