Winbond Electronics W91521N, W91521AN, W91520N, W91520AN Datasheet

W91520N SERIES

TONE/PULSE DIALER WITH HANDFREE

AND HOLD FUNCTIONS

GENERAL DESCRIPTION

The W91520N series are Si-gate CMOS ICs that provide the necessary signals for tone or pulse

dialing. The W91520N series provide one-key redial, handfree dialing, hold, save, and redial

functions.

FEATURES

•

DTMF/pulse switchable dialer

•

Two by 32-digit redial and save memory

•

Pulse-to-tone (*/T) keypad for long distance call operation

•

Uses 5 × 5 keyboard

•

Easy operation with redial, flash, pause, and */T keypads

•

Pause, pulse-to-tone (*/T) can be stored as a digit in memory

• On-hook debounce time: 150 mS

•

Dialing rate (10 ppS, or 20 ppS) selectable by bonding option

•

Minimum tone output duration: 93 msec.

•

Minimum intertone pause: 93 msec.

•

Flash break time (73, 100, 300, 600 msec.) selectable by keypad; pause time is 1.0 sec.

•

On-chip power-on reset

•

Uses 3.579545 MHz crystal or ceramic resonator

•

Packaged in 18 or 20-pin plastic DIP

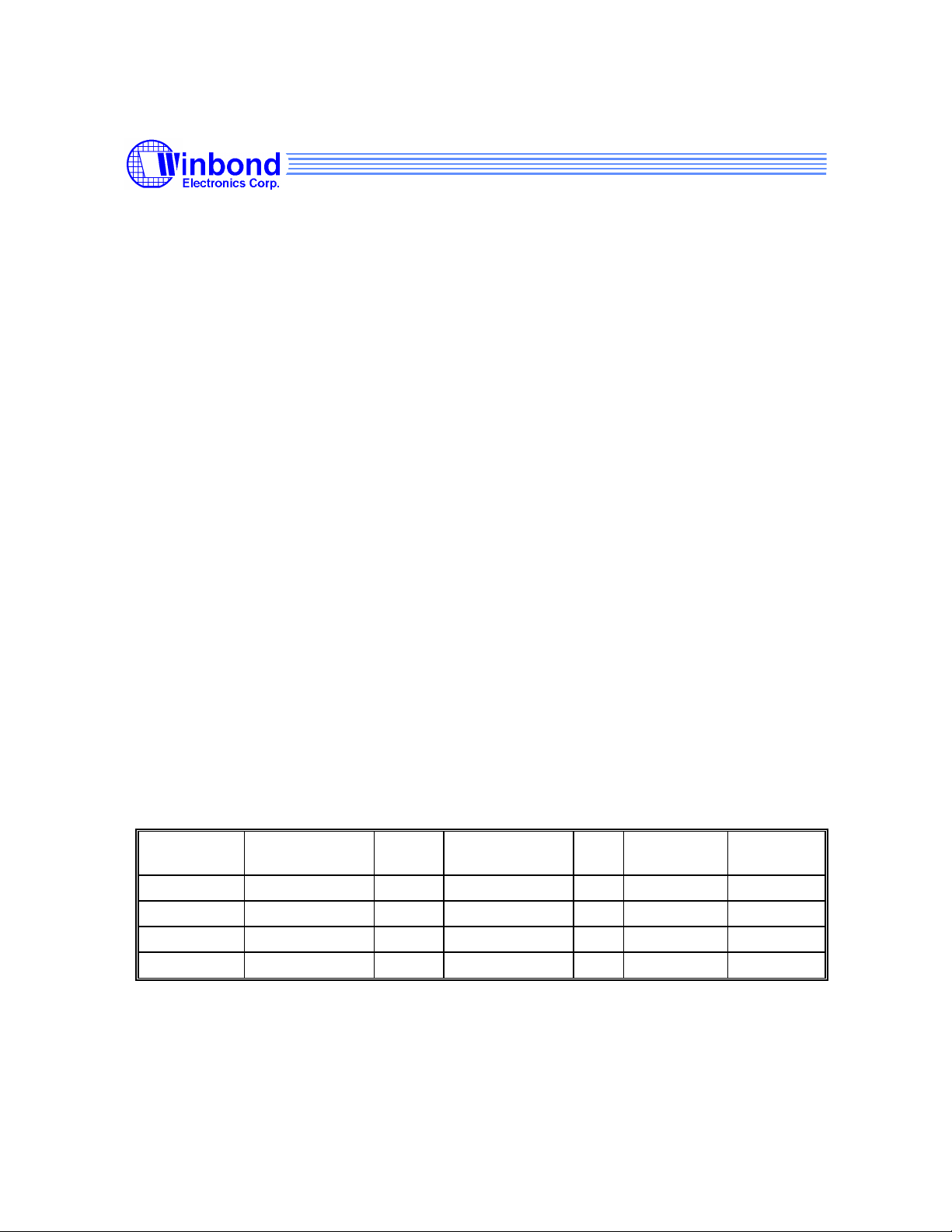

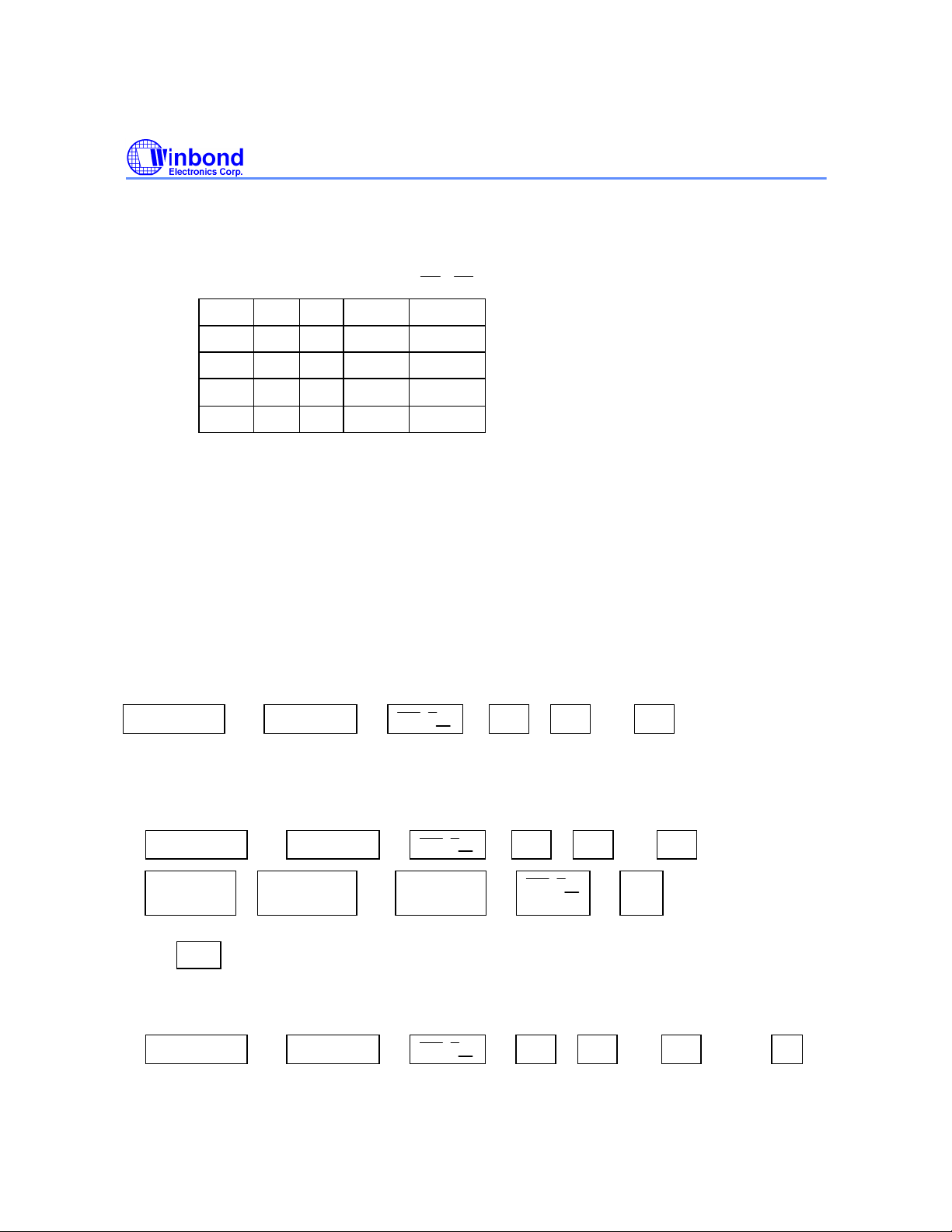

• The different dialers in the W91520N series are shown in the following table:

TYPE NO. REPLACEMENT

TYPE NO.

W91520N W91520 10 600/100/300/73 Pin - 18

W91521N W91521 20 600/100/300/73 Pin - 18

W91520AN W91520A 10 600/100/300/73 Pin Yes 20

W91521AN W91521A 20 600/100/300/73 Pin Yes 20

PULSE

(ppS)

FLASH

(mS)

M/B HANDFREE

DIALING

Publication Release Date: May 1997

- 1 - Revision A3

PACKAGE

(PINS)

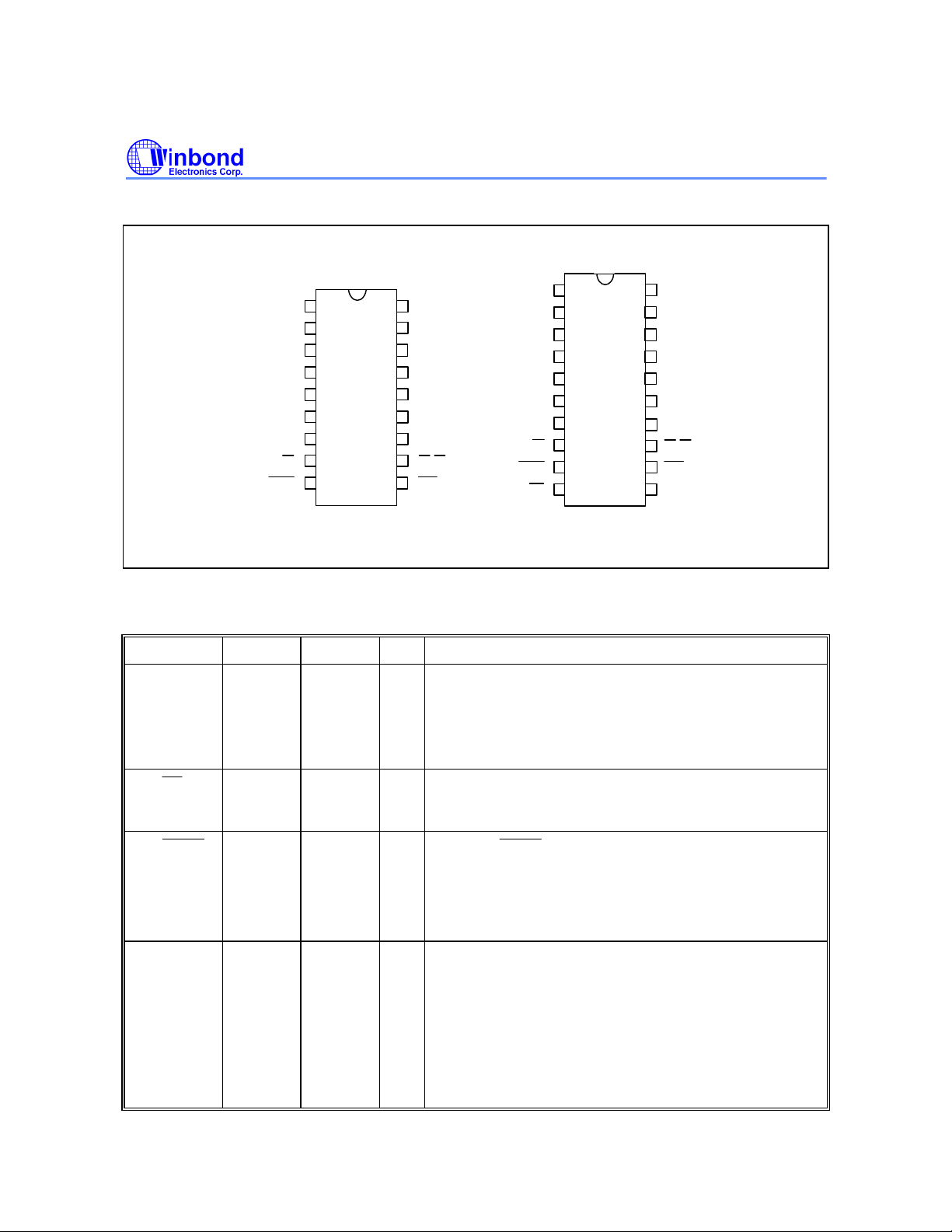

PIN CONFIGURATIONS

XT

MUTE

MUTE

C1

C2

C3

C4

H/P MUTE

SSV

XT

XT

T/P MUTE

W91520N SERIES

1

20

R4

R3

19

R2

18

R1

17

16

V

DD

MODE

15

14

DTMF

13

DP/C5

12

HKS

11

HFO

H/P MUTE

V

T/P MUTE

HFI

C1

2

C2

3

C3

C4

4

5

6

SS

7

XT

8

XT

9

10

1

2

3

4

5

6

7

8

9

18

R4

R3

17

R2

16

R1

15

14

V

DD

MODE

13

DTMF

12

11

DP/C5

10

HKS

W91520N/W91521N

W91520AN/W91521AN

PIN DESCRIPTION

SYMBOL 18-PIN 20-PIN I/O FUNCTION

ColumnRow

Inputs

XT,

T/P

1−4

&

15−18

1−4

&

17−20

7, 8 7, 8 I, O A built-in inverter provides oscillation with an

9 9 O

MODE 13 15 I Pulling mode pin to VSS places the dialer in tone

The keyboard inputs may be used with either a

standard 5 × 5 keyboard or an inexpensive single

I

contact (Form A) keyboard. Electronic input from a µC

can also be used. A valid key-in is defined as a single

row being connected to a single column.

inexpensive 3.579545 MHz crystal or ceramic

resonator.

The T/P

is a conventional CMOS N-channel

open drain output.

The output transistor is switched on during dialing

sequence, one-key redial break, and flash break time.

Otherwise, it is switched off.

mode.

Pulling mode pin to VDD places the dialer in pulse

mode (10 ppS; 20 ppS for W91521N/521AN, M/B =

40:60).

Floating mode pin places the dialer in pulse mode

(10 ppS; 20 ppS for W91521N/521AN, M/B =

33.3:66.7).

- 2 -

W91520N SERIES

HKS

HKS

HKS

HKS

DP/C5

R1R2R3

R4

C1

C2

C3

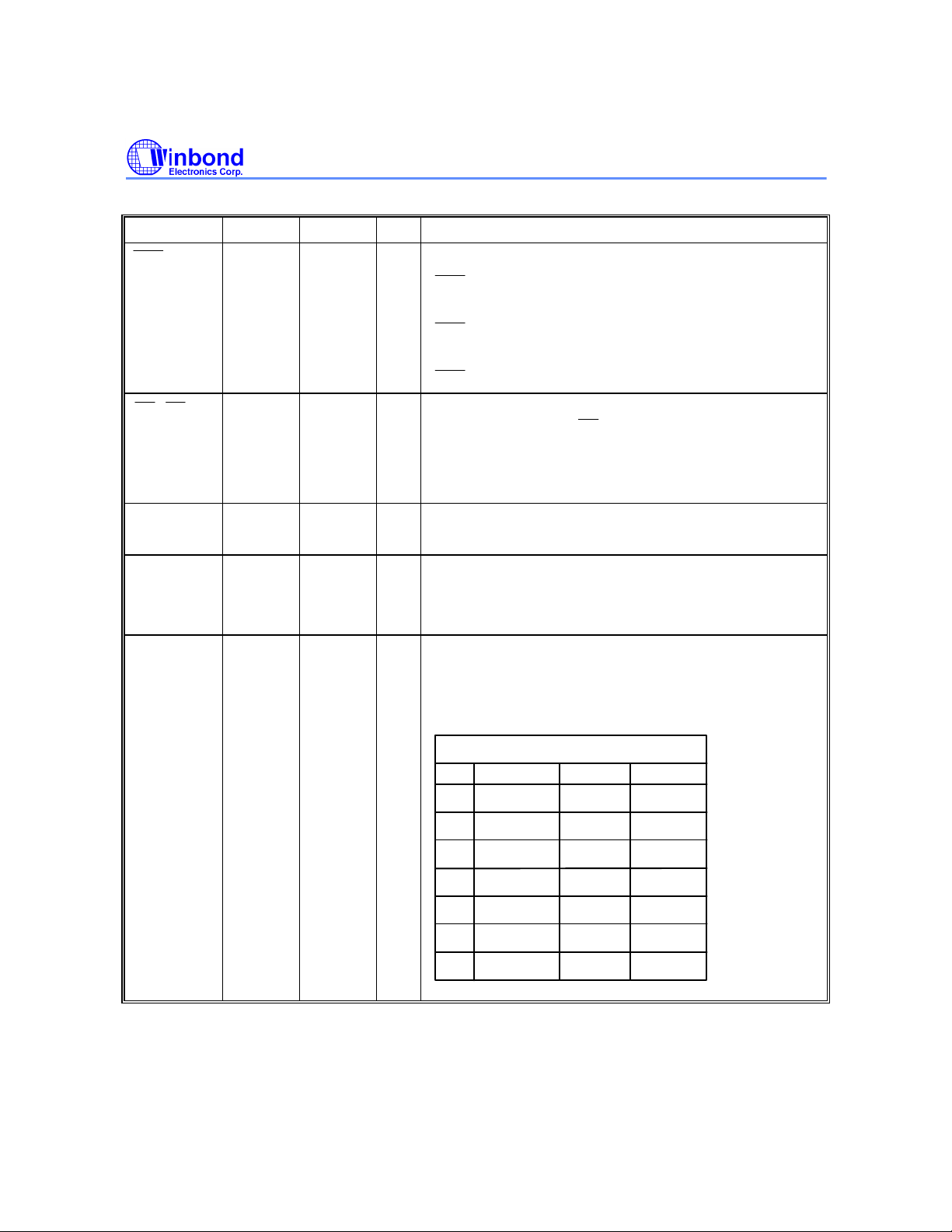

Pin Description, continued

SYMBOL 18-PIN 20-PIN I/O FUNCTION

10 12 I Hook switch input.

= VDD: On-hook state. Chip in sleeping mode, no

operation.

= VSS: Off-hook state. Chip is enabled for normal

operation.

pin is pulled to VDD by internal resistor.

11 13 O N-channel open drain dialing pulse output.

Flash key will cause DP to be active in either tone

mode or pulse mode.

The timing diagram for pulse mode is shown in Figure

1(a, b, c).

VDD, VSS 14, 6 16, 6 I Power input pins.

H/P MUTE 5 5 O The H/P MUTE is a conventional inverter output.

During pulse dialing, flash break, one-key redial break,

and hold period, this output is active high; otherwise, it

remains in low state.

DTMF 12 14 O In pulse mode, this pin remains in low state at all times.

In the tone mode, it will output a dual or single tone.

Detailed timing diagram for tone mode is shown in

Figure 2(a, b, c).

Output Frequency

Specified Actual Error %

697

770

852

941

1209

1336

1477

699

766

848

948

1216

1332

1472

+0.28

-0.52

-0.47

+0.74

+0.57

-0.30

-0.34

Publication Release Date: May 1997

- 3 - Revision A3

W91520N SERIES

HFI

HFI

HFO

HFI

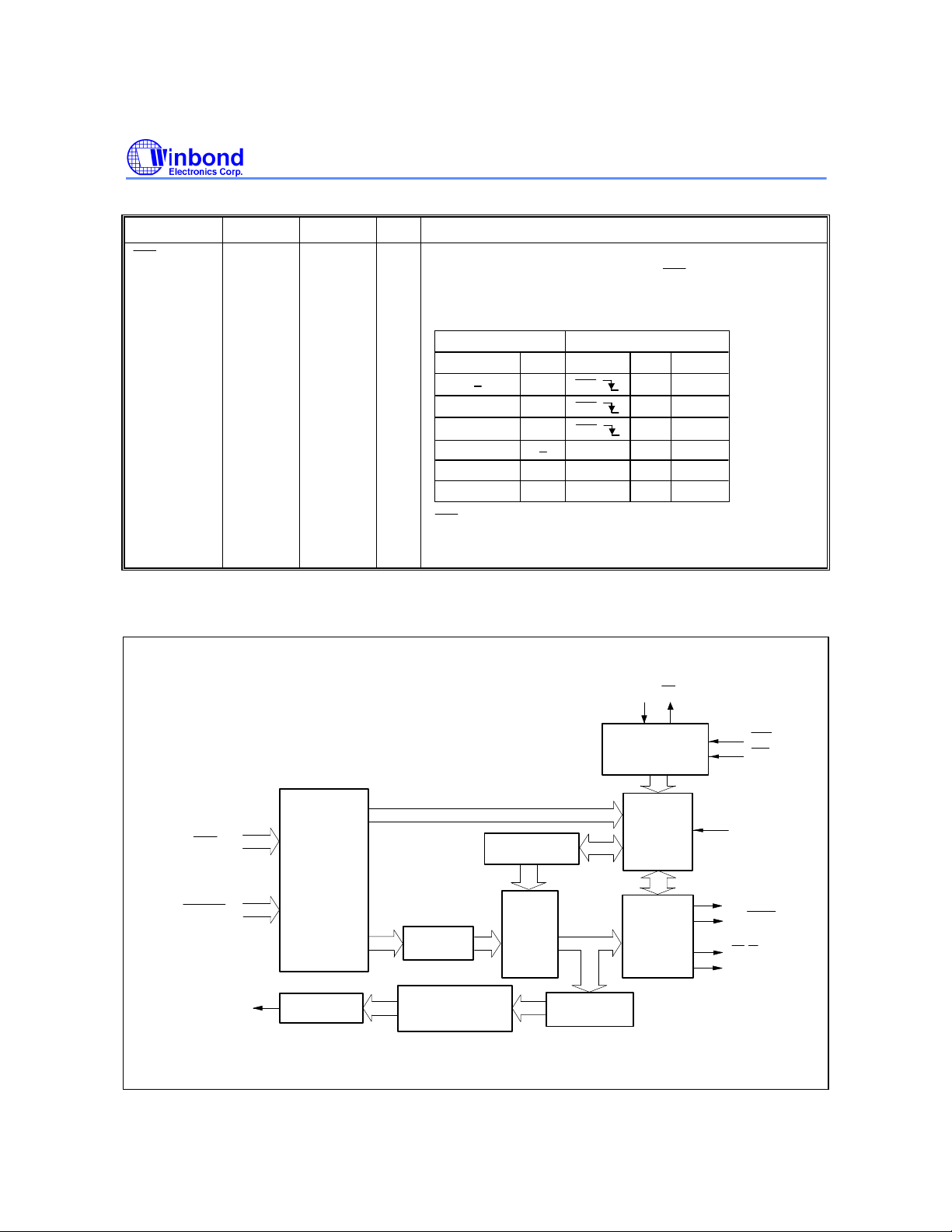

Pin Description, continued

SYMBOL 18-PIN 20-PIN I/O FUNCTION

, HFO

- 10, 11 I, O Handfree control pins. The handfree control state is

toggled on by a low pulse on the

status of the handfree control state is described in the

following table:

input pin. The

BLOCK DIAGRAM

CURRENT STATE

Hook SW. HFO

On Hook

Off Hook

Low

High

High

NEXT STATE

Input

HFI

HFI

HFI

High

Low No

Low Yes

Dialing

Yes

On Hook Off Hook Low Yes

Off Hook

Off Hook

Low

High

On Hook

On Hook

Low

No

High Yes

pin is pulled to VDD by an internal resistor.

Detailed timing diagrams are shown in Figure 3.

XT XT

SYSTEM CLOCK

GENERATOR

HKS

HFI

ROW

(R1 to R4, Vx)

COLUMN

(C1 to C4)

DTMF

KEYBOARD

INTERFACE

D/A

CONVERTER

LOCATION

LATCH

ROW & COLUMN

PROGRAMMABLE

COUNTER

- 4 -

READ/WRITE

COUNTER

RAM

DATA LATCH

& DECODER

CONTROL

LOGIC

PULSE

CONTROL

LOGIC

MODE

H/P MUTE

T/P MUTE

DP/C5

HFO

FUNCTIONAL DESCRIPTION

DPC5/

HFI

¡õ

HFI

¡õ

HFI

¡õ

HFI

¡õ

Keyboard Operation

C1 C2 C3 C4

1 2 3 SAVE R1

4 5 6 F1 R2

7 8 9 F2 H R3

W91520N SERIES

∗/T

0 # R/P1 R R4

R/P2 R F3 F4 VX

• R/P1, R/P2: Redial and pause function key; P1 is 3.6 sec. and P2 is 2.0 sec.

• ∗/T: ∗ in tone mode and P→T in pulse mode

• F1, ..., F4: Flash keys, flash break time of F1 = 600 mS, F2 = 100 mS, F3 = 300 mS, F4 = 73 mS

• H: Hold function key

• SAVE: Save function key

• R: One-key redial function

Notes:

D1, ..., Dn, D1', ..., Dn': 0, ..., 9, */T, #

R/P: R/P1 or R/P2.

Fn: F1, ..., F4

Normal Dialing

OFF HOOK (or ON HOOK &

1. D1, D2, ..., Dn will be dialed out.

2. Dialing length is unlimited, but redial is inhibited if length exceeds 32 digits in normal dialing.

), D1 , D2 , ..., Dn

Redialing

1. OFF HOOK (or ON HOOK &

ON

, OFF HOOK (or ON

HOOK

HOOK

), D1 , D2 , ..., Dn , Busy, Come

&

), R/P

a. The redial memory content will be dialed out.

b. The R/P key can execute the redial function only as the first key-in after off-hook; otherwise, it

executes pause function.

c. If redialing length exceeds 32 digits, the redialing function will be inhibited.

2. OFF HOOK (or ON HOOK &

), D1 , D2 , ..., Dn , Busy, R

a. The one-key redialing function timing diagram is shown in Figure 4.

Publication Release Date: May 1997

- 5 - Revision A3

Loading...

Loading...