Winbond Electronics W91473L, W91473DL, W91473D, W91473CL, W91473C Datasheet

...

W91473 SERIES

14-MEMORY TONE/PULSE SWITCHABLE DIALER

WITH HANDFREE AND LOCK FUNCTIONS

GENERAL DESCRIPTION

The W91473 series are Si-gate CMOS IC tone/pulse switchable dialers containing a 14-channel

automatic dialing memory, including a 16-digit × 3 emergency dialing memory and a 16-digit × 10

channel repertory memory that provides a 32-digit mercury memory. These dialers also provide flash,

clear, hold, lock, and one-key redial functions.

FEATURES

• DTMF/Pulse switchable dialer

• 32-digit LNB (last number buffer) memory

• 32-digit mercury memory

• 16-digit × 3 one-touch direct repertory memory

• 16-digit × 10 direct repertory memory

• Uses 7 × 5 keyboard

• Flash time: 98 mS, 305 mS, or 600 mS (selectable by keypad option)

• Minimum tone output duration: 93 mS

• Minimum intertone pause: 93 mS

• On-chip power-on reset

• Uses 3.579545 MHz crystal or ceramic resonator

• Packaged in 22, 24, or 28-pin plastic DIP

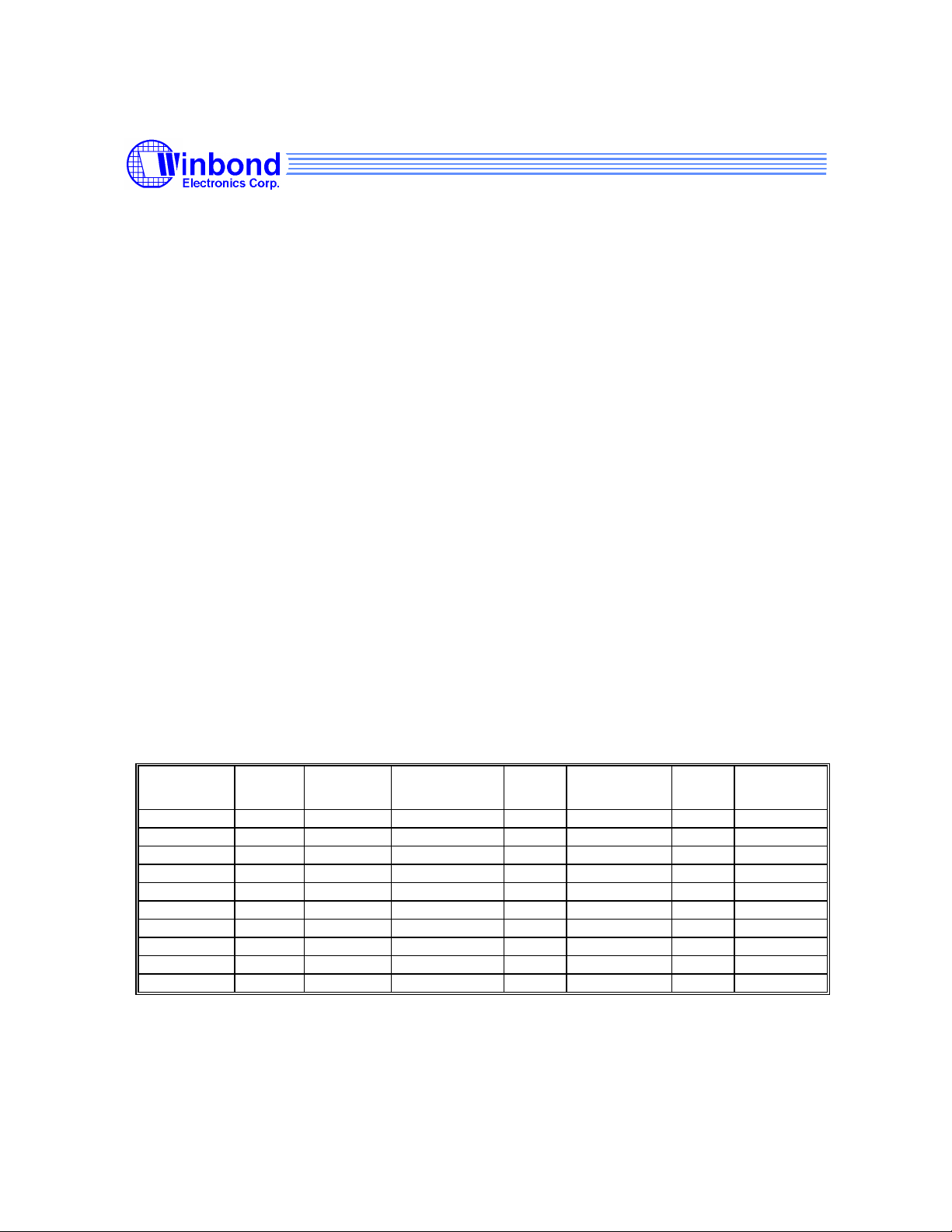

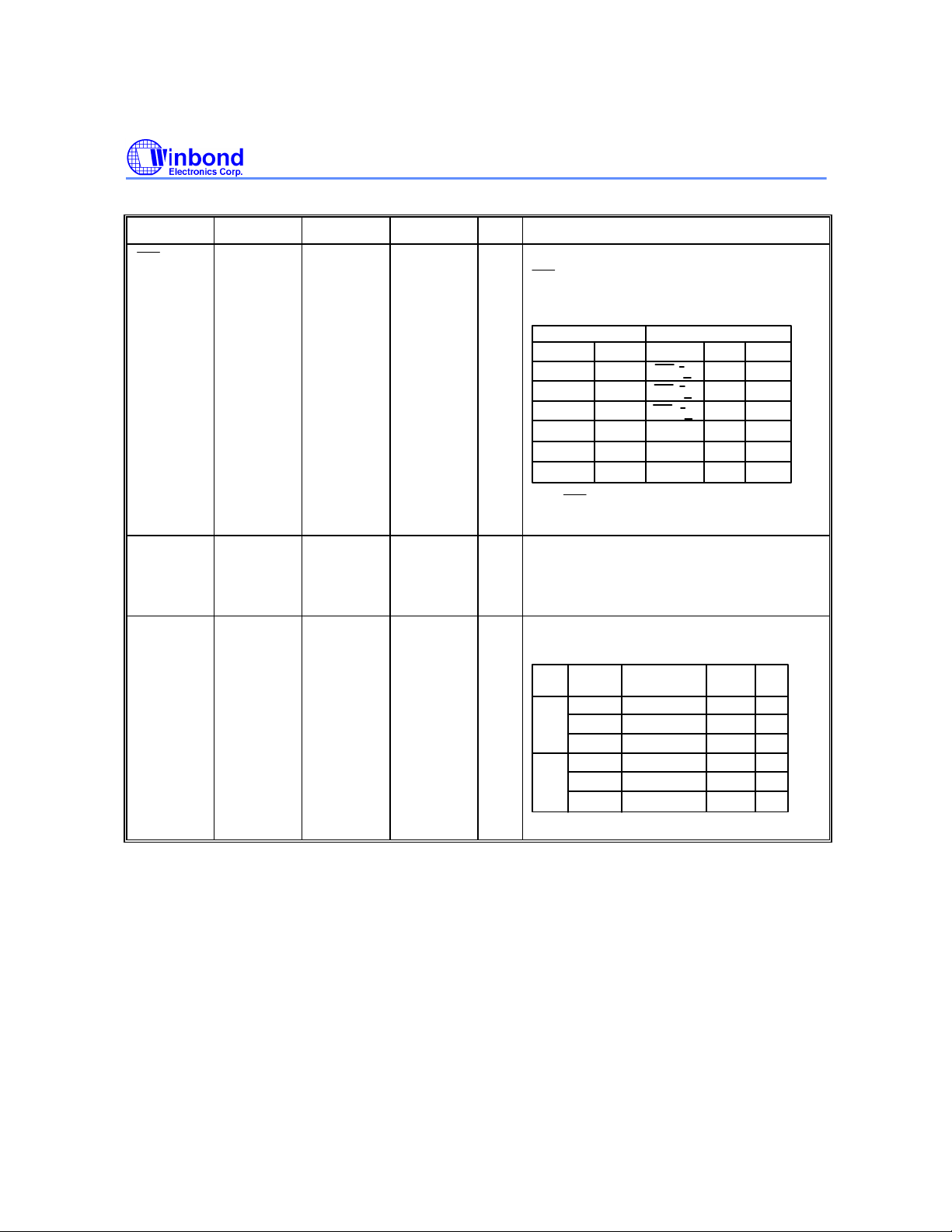

• The different dialers in the W91473 series are shown in the following table:

TYPE NO. PULSE

(ppS)

W91473 10 14 Yes Yes - - 22

W91473L 10 14 - - - Yes 22

W91473A 10 14 Yes Yes Yes - 24

W91473AL 10 14 - - Yes Yes 24

W91473B 10/20 14 Yes Yes Yes - 28

W91473BL 10/20 14 Yes Yes Yes Yes 28

W91473C 10/20 14 Save Memory Yes Yes - 28

W91473CL 10/20 14 Save Memory Yes Yes Yes 28

W91473D 10 14 Save Memory - - - 22

W91473DL 10 14 Save Memory - - Yes 22

MEMORY MERCURY

MEMORY

HOLD HANDFREE LOCK PACKAGE

Publication Release Date: February 1995

- 1 - Revision A3

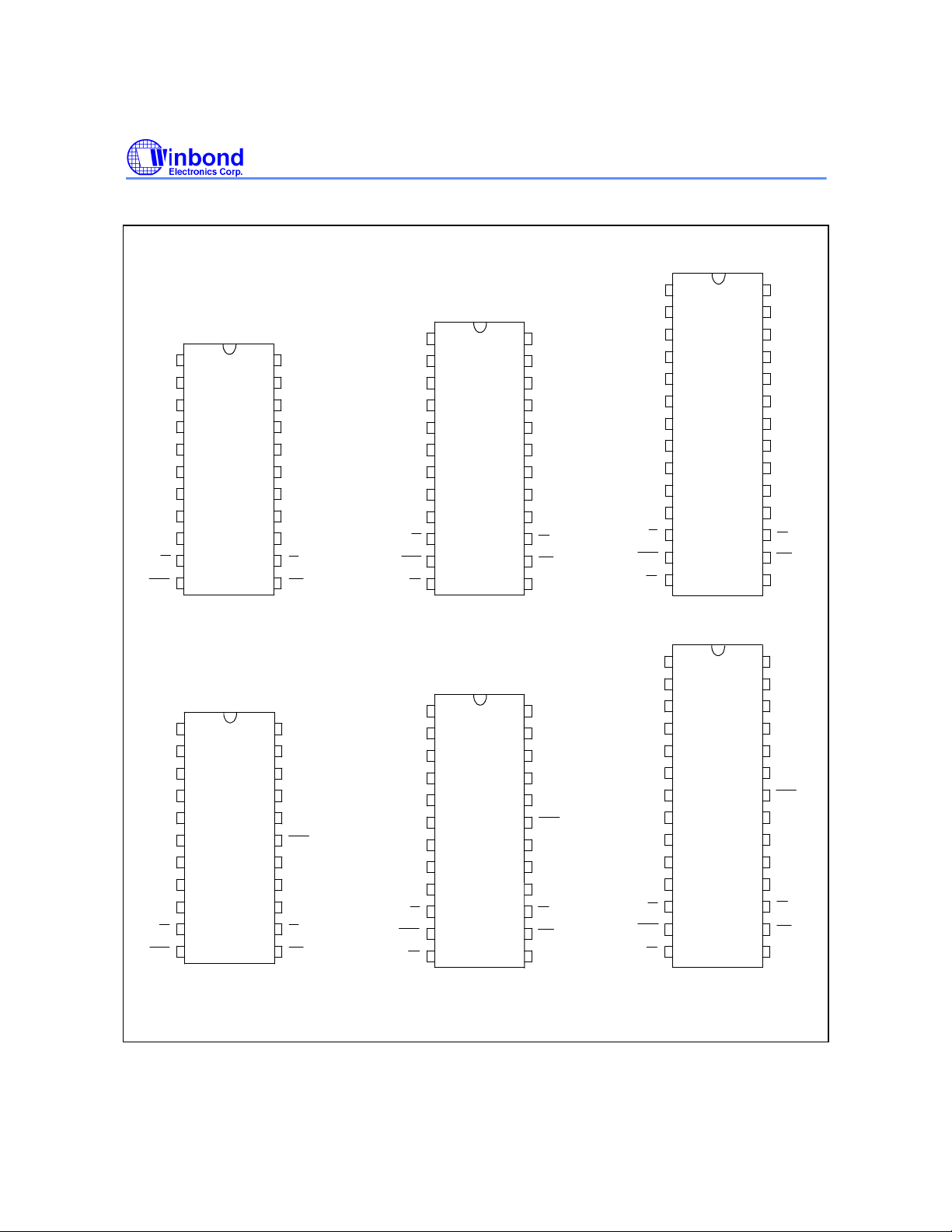

PIN CONFIGURATIONS

W91473 SERIES

T/P MUTE

T/P MUTE

1

2

C2

3

C3

4

C4

5 18

C5

C6

6

C7

7

V

8

SS

9 14

XT

10

XT

11

W91473/D

1

C1

2

C2

C3

3

4

C4

5 18

C5

C6C76

7

V

8

SS

9 14

XT

10

XT

11 12

W91473L/DL

22C1

21

20

19

17

16

15

13

12

22

21

20

19

17

16

15

13

R5

R4

R3

R2

R1

HPM MUTE

V

DD

MODE

DTMF

DP

HKS

R5

R4

R3

R2

R1

LOCK

V

DD

MODE

DTMF

DP

HKS

T/P MUTE

T/P MUTE

1

2

C2

3

V

T/P MUTE

HFI

V

T/P MUTE

HFI

C3

C4

4

5 24

C5

C6C76

7

8

NC

9

KT

10

SS

11

XT

12

XT

13

14 1516HFO

W91473B/C

1

C2

2

C3

3

4

C4

5 24

C5

C6C76

7

NC

8

KT

9 20

SS

10

11

XT

12 17

XT

13

14

1

2

C2

3

C3

4

C4

5 20

C5

C6C76

7

V

SS

8

XT

9

10

XT

11

12

HFI

W91473A

1

2

C2

3

C3

4

C4

5 20

C5

C6

C767

V

8

SS

9 16

XT

10

XT

11

12

HFI

R5

24C1

R4

23

22

R3

21

R2

R1

19

HPM MUTE

V

18

DD

MODE

17

16

DTMF

15

DP

14

HKS

13

HFO

24C1

R5

R4

23

R3

22

R2

21

R1

19

LOCK

V

18

DD

17

MODE

DTMF

15

DP

14

HKS

13

HFO

W91473AL W91473BL/CL

28C1

27

26

25

2223NC

21

20

19

18

17

28C1

27

26

25

23

22

21

19

18

16

15

R5

R4

R3

R2

R1

HPM MUTE

DRS

V

DD

MODE

DTMF

DP

HKS

R5

R4

R3

R2

R1

HPM MUTE

LOCK

DRS

V

DD

MODE

DTMF

DP

HKS

HFO

- 2 -

W91473 SERIES

XT

MUTE

MUTE

DP

HKS

HKS

HKS

HKS

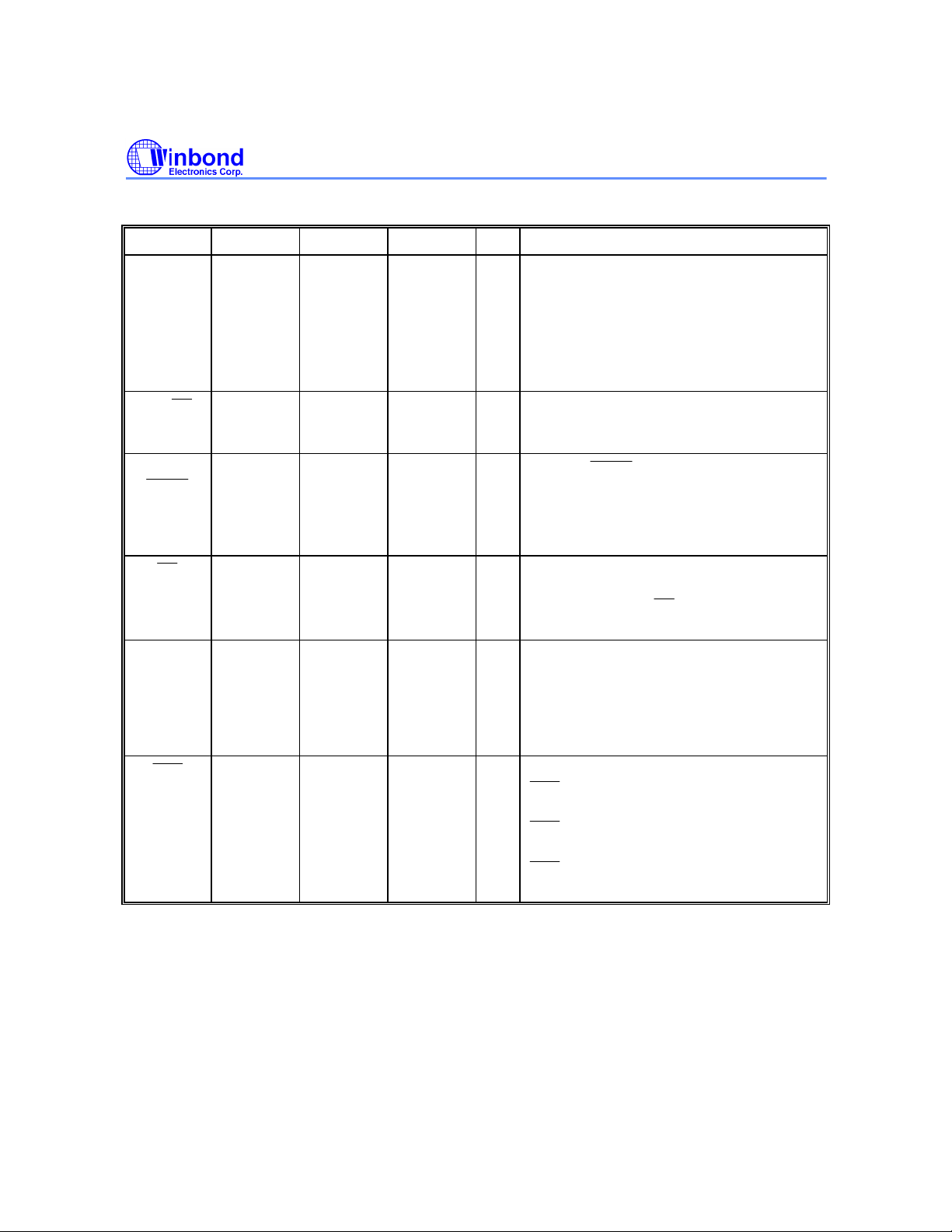

PIN DESCRIPTION

SYMBOL 22-PIN 24-PIN 28-PIN I/O FUNCTION

Column-

Row

Inputs

XT,

T/P

MODE 15 17 19 I Pulling mode pin to VSS places the dialer

1−7

&

18−22

9, 10 9, 10 11, 12 I, O A built-in inverter provides oscillation with

11 11 13 O

13 15 17 O N-channel open drain dialing pulse output

1−7

&

20−24

1−8

&

24−28

I The keyboard input may be used with

either the standard 7 × 5 keyboard or an

inexpensive single contact (form A)

keyboard. Electronic input with µC can

also be used.

A valid key entry is defined by a single

row being connected to a single column.

an inexpensive 3.579545 MHz crystal or

ceramic resonator.

The T/P

N-channel open drain output. The output

transistor is switched on during pulse and

tone mode dialing sequence and flash

break. Otherwise, it is switched off.

(Figure 1).

Flash key causes DP to go active when in

pulse mode and tone mode.

in tone mode.

Pulling mode pin to VDD places the dialer

in pulse mode (10 ppS, M/B = 2:3).

Leaving mode pin floating places the

dialer in pulse mode (10 ppS, M/B = 1:2).

is a conventional CMOS

12 14 16 I Hook switch input.

= 1: On-hook state. Chip in sleep

mode, no operation.

= 0: Off-hook state. Chip enabled for

normal operation.

pin is pulled to VDD by internal

resistor.

Publication Release Date: February 1995

- 3 - Revision A3

W91473 SERIES

LOCK

LOCK

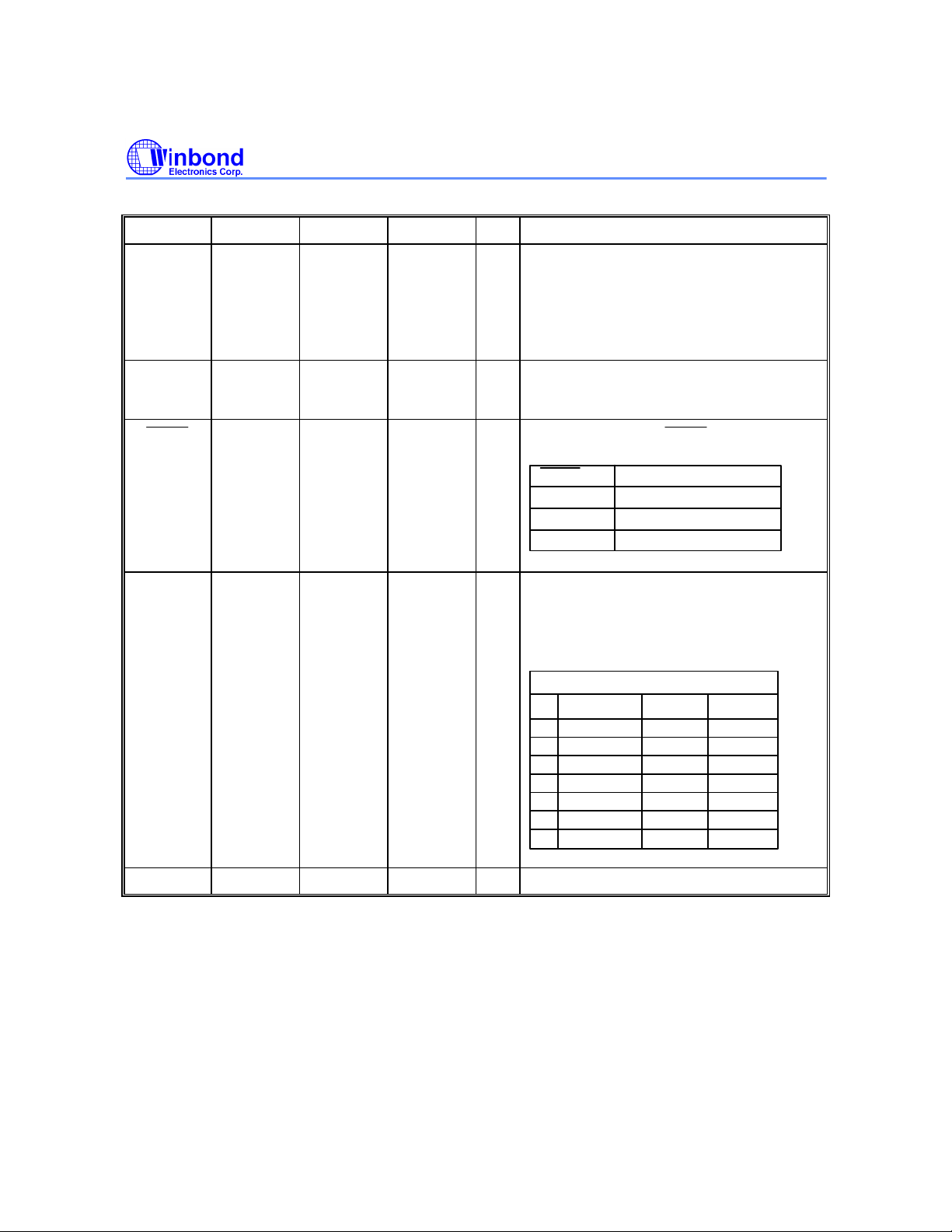

Pin Description, continued

SYMBOL 22-PIN 24-PIN 28-PIN I/O FUNCTION

HPM

MUTE

17

(only for

W91473/D

)

19

(only for

W91473A)

23 O The HPM MUTE is a conventional

inverter output.

During pulse dialing, flash, hold, and

mercury mute functions, this pin will

output an active high.

It remains in a low state at all other times.

NC - - 8, 22

(W91473

B/C)

17

(W91473L

/DL)

19

(W91473

AL)

22

(W91473

BL/CL)

- No connection.

I

The function of the

below:

LOCK PIN

V

DD

Floating

V

SS

pin is shown

FUNCTION

"0," " 9" dialing inhibited

Normal dialing

"0" dialing inhibited

DTMF 14 16 18 O In pulse mode, remains in low state at all

times. In tone mode, outputs a dual or

single tone.

Detailed timing diagram for tone mode is

shown in Figure 2.

OUTPUT FREQUENCY

Specified

R1

R2

R3

R4 941 948

C1

C2

C3 1477

697

770 766

852

1209

1336 1332 -0.30

Actual

699

848

1216

1472

Error %

+0.28

-0.52

-0.47

+0.74

+0.57

-0.34

VDD, VSS 16, 8 1, 8 20, 10 I Power input pins.

- 4 -

W91473 SERIES

HFI

HFI

HFI

Pin Description, continued

SYMBOL 22-PIN 24-PIN 28-PIN I/O FUNCTION

, HFO

- 12, 13 14, 15 I, O Handfree control pins. A low pulse on the

input pin toggles the handfree control

state. Status of the handfree control state

is listed in the following table:

CURRENT STATE

Hook Sw. HFO

- Low

On Hook

Off Hook

Off Hook

Off Hook

The

High Low No

High Low

- YesOff HookOn Hook

Low

High

pin is pulled to VDD by an

NEXT STATE

Input

¡õ

HFI

¡õ

HFI

¡õ

HFI

On Hook

On Hook

Dialing

HFO

High

Low

Low

High Yes

Yes

Yes

No

internal resistor.

KT - - 9 O Keytone signal output. The keytone will

be generated in all valid keys are pressed

in tone mode. Frequency is 600 Hz and

duration is 35 mS.

DRS - - 21 I Dial rate selection. This pin is pulled to

VDD by an internal resistor.

DRS

1

0

MODE

PIN

VDD

Floating

V

SS

V

DD

Floating

V

SS

TONE/PULSE

Pulse

Pulse

Tone

Pulse

Pulse

Tone

DIAL

RATE

10 ppS

10 ppS

10 ppS

20 ppS

-

M/B

2:3

1:2

1:2

1:2

-

Publication Release Date: February 1995

- 5 - Revision A3

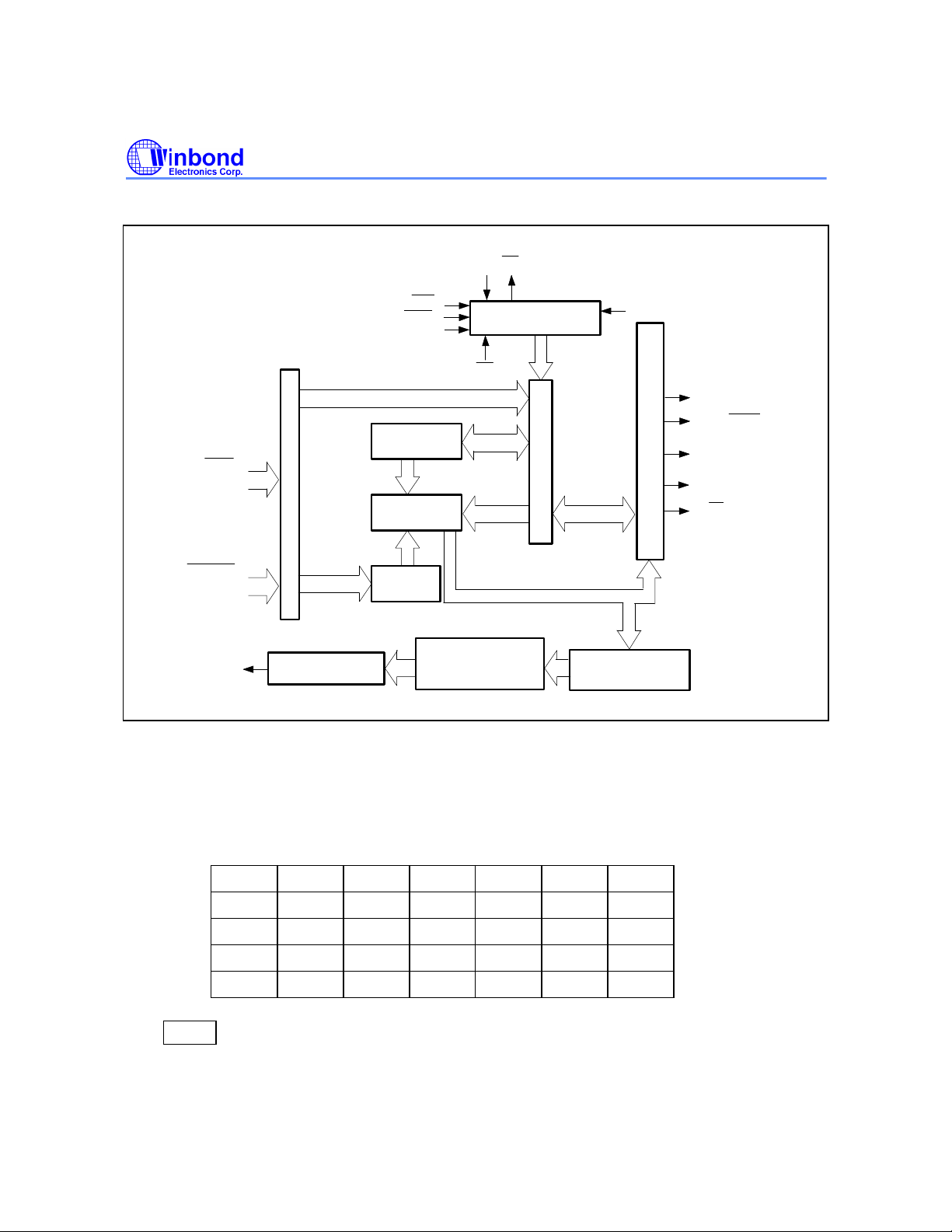

BLOCK DIAGRAM

XT

W91473 SERIES

XT

ROW

(R1 to R5)

COLUMN

(C1 to C7)

DTMF

K

E

Y

B

O

A

R

D

I

N

T

E

R

F

A

C

E

D/A CONVERTER

HKS

LOCK

MODE

READ/WRITE

COUNTER

RAM

LOCATION

LATCH

ROW & COLUMN

PROGRAMMABLE

COUNTER

SYSTEM CLOCK

GENERATOR

HFI

C

O

N

T

R

O

L

L

O

G

I

C

DRS

P

U

L

S

E

C

O

N

T

R

O

L

L

O

G

I

C

DATA LATCH

& DECODER

KT

T/P MUTE

HPM MUTE

HFO

DP

FUNCTIONAL DESCRIPTION

Keyboard Operation

C1 C2 C3 C4 C5 C6 C7

1 2 3 S M00 M05 EM1 R1

4 5 6 M01 M06 EM2 R2

7 8 9 CLR M02 M07 EM3 R3

*/T 0 # R/P M03 M08 H R4

F1 F2 F3 R M04 M09 *MER R5

Note: *MER location in W91473C/CL or W91473D/DL is SAVE memory.

• S:Store function key

- 6 -

Loading...

Loading...