Winbond Electronics W83781D Datasheet

W83781D

Winbond H/W

Monitoring IC

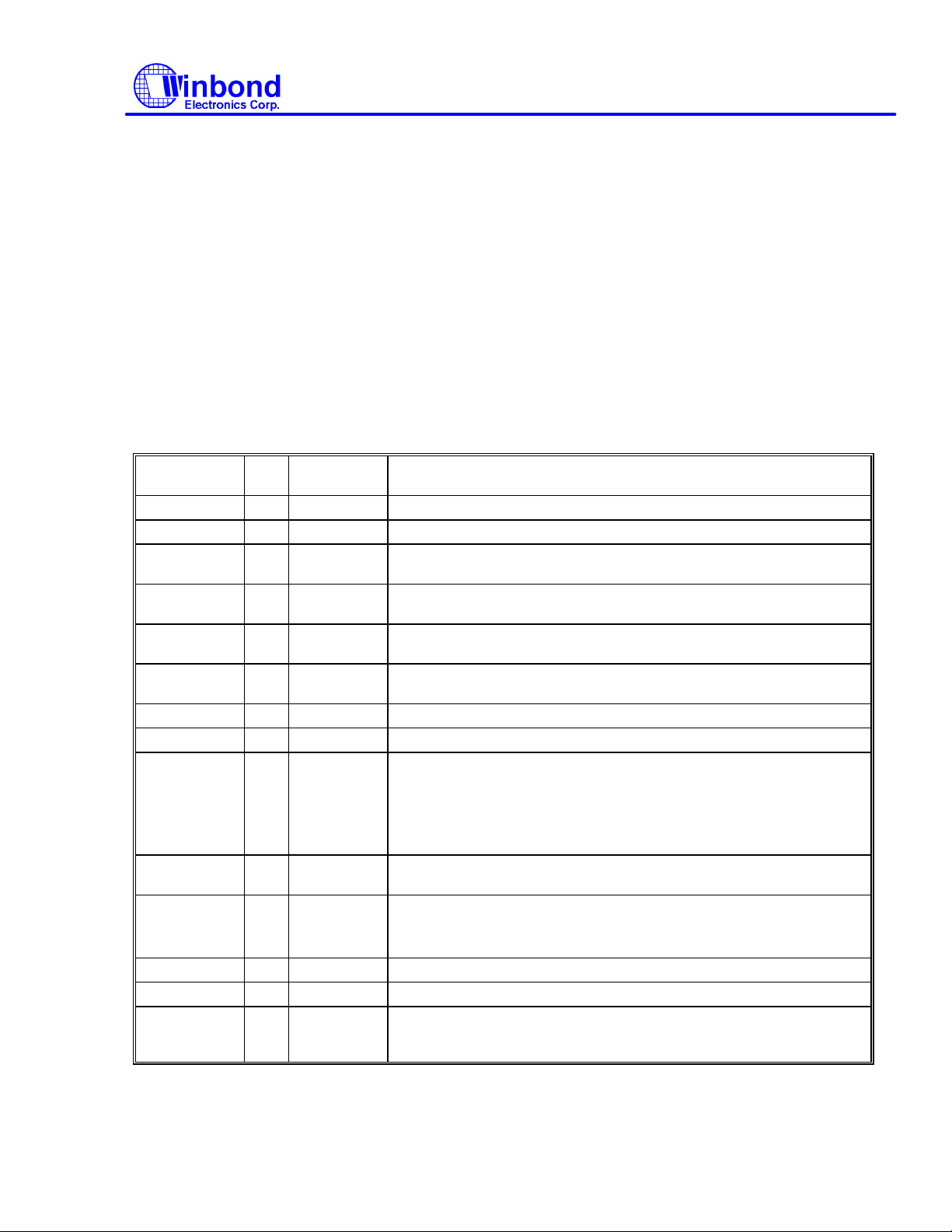

W83781D Data Sheet Revision History

Pages Dates Version Version

1

2

3

4

5

6

7

8

n.a. n.a. All the version before 0.60 are internal use.

n.a. 11/07/97 0.60 n.a. First published.

5 11/19/97 0.61 n.a. Pin 18-20: I/O Type ¡÷ I/O

4

5

6

33

37

40

43

48

12/17/97 0.62 n.a. Pin18-20:I/O Type ¡÷ Fan 1, Pin18:Fan1¡÷ Fan3

1/13/98 0.63 n.a. 8.24 index 55h(Bank 0) ¡÷ Winbond Test Register

on Web

Main Contents

12ts

Pin23: I/O Type ¡÷ OUT

Pin42: I/O Type ¡÷ OUT

8.30 index 52h(Bank 1) bit2 ¡÷ Reserve

8.37 index 52h(Bank 2) bit2 ¡÷ Reserve

9.2 I/O 12ts TTL DC Characteristics

Package QFT ¡÷ LQFP

8t

12

9

10

Please note that all data and specifications are subject to change without notice. All

the trade marks of products and companies mentioned in this data sheet belong to

their respective owners.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or

systems where malfunction of these products can reasonably be expected to result

in personal injury. Winbond customers using or selling these products for use in

such applications do so at their own risk and agree to fully indemnify Winbond for

any damages resulting from such improper use or sales.

W83781D

Monitoring IC

Winbond H/W

TABLE OF CONTENTS

1. GENERAL DESCRIPTION.......................................................................................................... 1

2. FEATURES.................................................................................................................................... 1

2.1 MONITORING ITEMS......................................................................................................................................... 1

2.2 ACTIONS ENABLING......................................................................................................................................... 2

2.3 GENERAL............................................................................................................................................................2

2.4 PACKAGE ............................................................................................................................................................ 2

3. KEY SPECIFICATIONS ..............................................................................................................2

4. BLOCK DIAGRAM ...................................................................................................................... 3

5. PIN CONFIGURATION ............................................................................................................... 4

6. PIN DESCRIPTION ...................................................................................................................... 5

7. FUNCTIONAL DESCRIPTION ................................................................................................... 7

7.1 GENERAL DESCRIPTION .................................................................................................................................. 7

7.1.1 The first serial bus access timing are shown as follow: .................................................................................. 9

7.1.2 The serial bus timing of the temperature 2 and 3 is shown as follow: ........................................................... 10

7.2 ANALOG INPUTS.............................................................................................................................................. 12

7.3 FAN INPUTS AND FAN CONTROL ................................................................................................................. 13

7.4 TEMPERATURE MEASUREMENT MACHINE................................................................................................ 14

8. CONTROL AND STATUS REGISTERS................................................................................... 16

8.1 ADDRESS REGISTER (PORT X5H).................................................................................................................. 16

8.2 DATA REGISTER (PORT X6H)......................................................................................................................... 19

8.3 CONFIGURATION REGISTER ¾- INDEX 40H (BANK 0)................................................................................19

8.4 INTERRUPT STATUS REGISTER 1¾ INDEX 41H (BANK 0).......................................................................... 20

8.5 INTERRUPT STATUS REGISTER 2 ¾ INDEX 42H (BANK 0)......................................................................... 21

Publication Release Date: Nov. 1997

- I - Version 0.60

W83781D

Monitoring IC

Winbond H/W

8.6 SMI# MASK REGISTER 1 ¾ INDEX 43H (BANK 0)........................................................................................ 21

8.7 SMI# MASK REGISTER 2 ¾ INDEX 44H (BANK 0)......................................................................................... 22

8.8 IRQ MASK REGISTER 2 ¾ INDEX 45H (BANK 0)........................................................................................... 22

8.9 IRQ MASK REGISTER 2 ¾ INDEX 46H (BANK 0)........................................................................................... 23

8.10 VID/FAN DIVISOR REGISTER ¾ INDEX 47H (BANK 0)...............................................................................23

8.11 SERIAL BUS ADDRESS REGISTER ¾ INDEX 48H (BANK 0)....................................................................... 24

8.12 VALUE RAM ¾ INDEX 20H- 3FH OR 60H – INDEX 7FH (AUTO-INCREMENT) (BANK 0)........................ 25

8.13 VOLTAGE ID (VID7-4) – INDEX 49H (BANK 0)...........................................................................................27

8.14 TEMPERATURE 2 AND TEMPERATURE 3 SERIAL BUS ADDRESS REGISTER INDEX 4AH (BANK 0). 28

8.15 PIN CONTROL REGISTER – INDEX 4BH (BANK 0)..................................................................................... 29

8.16 IRQ/OVT# PROPERTY SELECT – INDEX 4CH (BANK 0)...........................................................................30

8.17 FAN IN/OUT AND BEEP/GPO# CONTROL REGISTER -- INDEX 4DH (BANK 0) ....................................... 31

8.18 REGISTER 50H ~ 5FH BANK SELECT -- INDEX 4EH (NO AUTO INCREASE) (BANK 0).......................... 32

8.19 WINBOND VENDOR ID -- INDEX 4FH (NO AUTO INCREASE) (BANK 0) ................................................. 32

8.20 RESISTOR-TEMPERATURE TABLE REGISTER – INDEX 50H - 51H (BANK 0)......................................... 33

8.21 WINBOND TEST REGISTER 1 – INDEX 52H (BANK 0)............................................................................... 33

8.22 WINBOND TEST REGISTER 2 – INDEX 53H (BANK 0)............................................................................... 33

8.23 WINBOND TEST REGISTER 3 – INDEX 54H (BANK 0)............................................................................... 33

8.24 WINBOND TEST REGISTER 4 – INDEX 55H (BANK 0)............................................................................... 33

8.25 BEEP CONTROL REGISTER 1— INDEX 56H (BANK 0) (AUTO-INCREMENT)........................................... 34

8.26 BEEP CONTROL REGISTER 2— INDEX 57H (BANK 0) ( NO AUTO-INCREMENT).................................... 34

8.27 CHIP ID- INDEX 58H (BANK 0)...................................................................................................................... 35

8.28 TEMPERATURE SENSOR 2 TEMPERATURE REGISTER - INDEX 50H (BANK 1)..................................... 36

8.29 TEMPERATURE SENSOR 2 TEMPERATURE REGISTER - INDEX 51H (BANK 1)..................................... 36

8.30 TEMPERATURE SENSOR 2 CONFIGURATION REGISTER - INDEX 52H (BANK 1)................................. 37

8.31 TEMPERATURE SENSOR 2 HYSTERESIS (HIGH BYTE) REGISTER - INDEX 53H (BANK 1).................. 37

8.32 TEMPERATURE SENSOR 2 HYSTERESIS (LOW BYTE) REGISTER - INDEX54H (BANK 1).................... 38

8.33 TEMPERATURE SENSOR 2 OVER-TEMPERATURE(HIGH BYTE) REGISTER - INDEX 55H (BANK 1) .. 38

8.34 TEMPERATURE SENSOR 2 OVER-TEMPERATURE (LOW BYTE) REGISTER - INDEX 56H (BANK 1).. 39

8.35 TEMPERATURE SENSOR 3 TEMPERATURE REGISTER - INDEX 50H (BANK 2)..................................... 39

8.36 TEMPERATURE SENSOR 3 TEMPERATURE REGISTER - INDEX 51H (BANK 2)..................................... 40

Publication Release Date: Nov. 1997

- II - Version 0.60

W83781D

Monitoring IC

Winbond H/W

8.37 TEMPERATURE SENSOR 3 CONFIGURATION REGISTER - INDEX 52H (BANK 2)................................. 40

8.38 TEMPERATURE SENSOR 3 HYSTERESIS (HIGH BYTE) REGISTER - INDEX 53H (BANK 2).................. 41

8.39 TEMPERATURE SENSOR 3 HYSTERESIS (LOW BYTE) REGISTER - INDEX 54H (BANK 2)................... 41

8.40 TEMPERATURE SENSOR 3 OVER-TEMPERATURE (HIGH BYTE)REGISTER - INDEX 55H (BANK 2) .. 42

8.41 TEMPERATURE SENSOR 3 OVER-TEMPERATURE (LOW BYTE) REGISTER - INDEX 56H (BANK 2).. 42

9. SPECIFICATIONS...................................................................................................................... 43

9.1 ABSOLUTE MAXIMUM RATINGS .................................................................................................................. 43

9.2 DC CHARACTERISTICS................................................................................................................................... 43

9.2.1 AC Characteristics ...................................................................................................................................... 45

9.2.2 ISA Read/Write Interface Timing ................................................................................................................ 45

9.2.3 Serial Bus Timing Diagram......................................................................................................................... 46

10. HOW TO READ THE TOP MARKING.................................................................................. 47

11. PACKAGE DIMENTIONS....................................................................................................... 48

Publication Release Date: Nov. 1997

- III - Version 0.60

W83781D

PRELIMINARY

1. GENERAL DESCRIPTION

The W83781D is a hardware status monitoring IC for personal computers, server computers, or

microprocessor based systems. W83781D can be used to monitor several critical hardware

parameters of the system, including power supply voltages, fan speeds, and temperatures, which are

very important for a high-end computer system to work stable and properly. W83781D provides both

ISA and I2CTM serial bus interface.

A 8-bit analog-to-digital converter (ADC) was built inside W83781D. The W83781D can monitor 3

external thermistor temperature sensors, 5 positive analog voltage inputs, two inverting inputs (for

monitoring negative voltages), and also three fan tachometer outputs. There is also one input for

case open detection circuits.

With the application software, the users can read all the monitored parameters of system from time to

time. The application software could be the popular IntelTM LDCM (LANDesk Client Management) or

Winbonds application software. Also the users can set up the upper and lower limits of these

monitored parameters and to activate two programmable and maskable interrupts. An optional beep

tone could be used as warning signal when the monitored parameters is out of the preset range.

Additionally, 5 VID inputs are provided to read the VID of CPU (such as PentiumTM II) if applicable.

This is to provide the Vcore correction automatically. Also W83781D uniquely provides an optional

feature: early stage (before BIOS was load) beep warning. This is to detect if the fatal elements

present --- VcoreA, +3.3V voltage fail, and the system can not be boomed up.

2. FEATURES

2.1 Monitoring Items

• 3 thermal inputs from remote thermistors

• 5 positive voltage inputs (typical for +12V, +5V, +3.3V, VcoreA, VcoreB)

• 2 op amps for negative voltage monitoring (typical for -12V, -5V)

• 3 fan speed monitoring inputs

• Case open detection input

• WATCHDOG comparison of all monitored values

• Programmable hysteresis and setting points for all monitored items

-1- Publication Release Date : Nov. 1997

Revision 0.60

2.2 Actions Enabling

• Warning signal pop up in application software

• Beep tone warning

• Fan ON/OFF control

• Issue SMI#, IRQ to activate system protection

2.3 General

• ISA and I2CTM serial bus interface

• 5 VID input pins for CPU Vcore identification

• Initial power fault beep (for +3.3V, VcoreA)

• Master reset input to W83781D

• Independent power plane of digital Vcc and analog Vcc (input to IC)

• Intel LDCMTM compatible

W83781D

PRELIMINARY

• Winbond monitoring application software support

• Input clock rate optional for 24, 48, 14.318 MHz

2.4 Package

• 48-pin LQFP

3. KEY SPECIFICATIONS

• Voltage monitoring accuracy ±1% (Max)

• Monitoring Temperature Range and Accuracy

- 40°C to +120°C ± 3°C(Max)

• Supply Voltage 5V

• Supply Current Operating: 1 mA typ.

Shutdown: 10 µA typ.

• ADC Resolution 8 Bits

- 2 - Publication Release Date : Nov. 1997

Revision 0.60

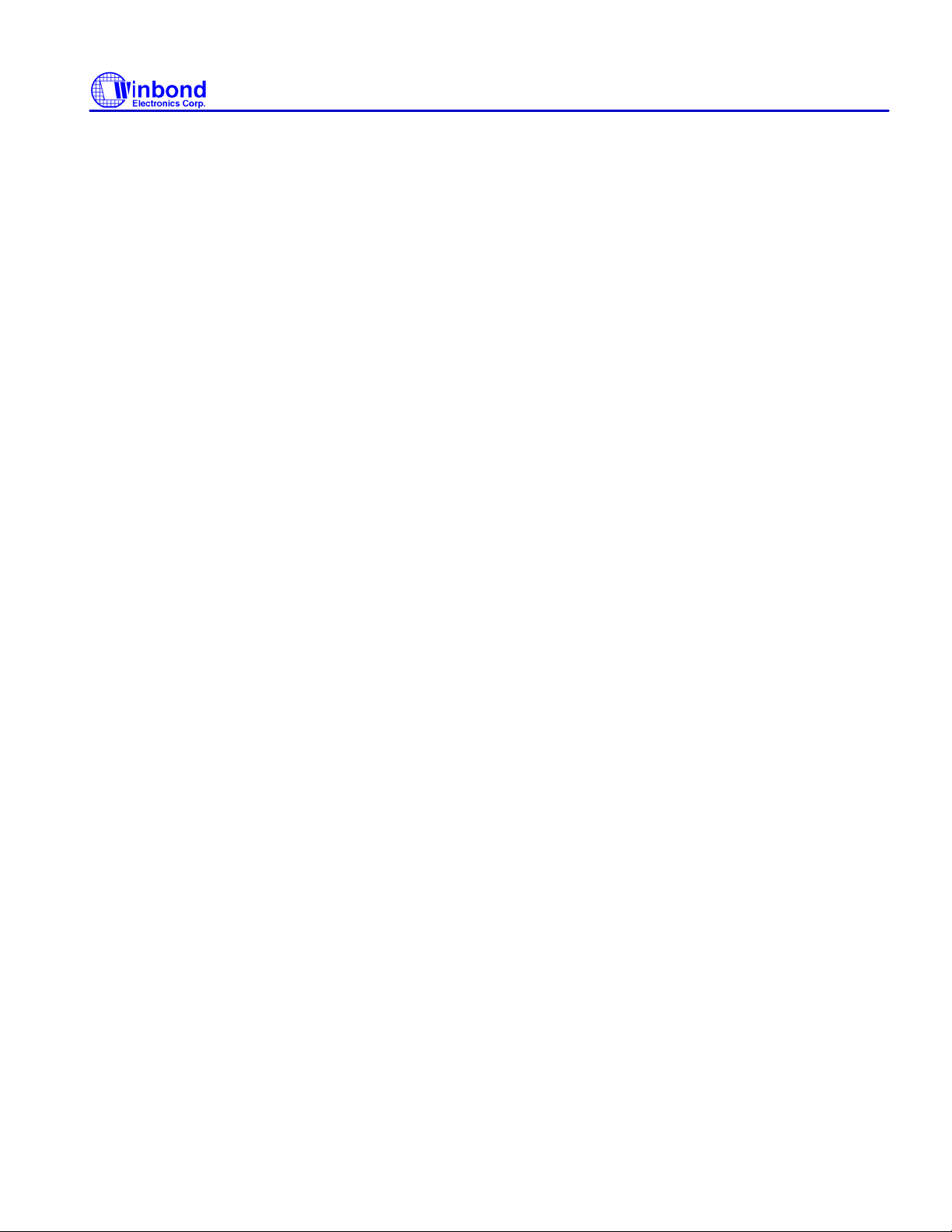

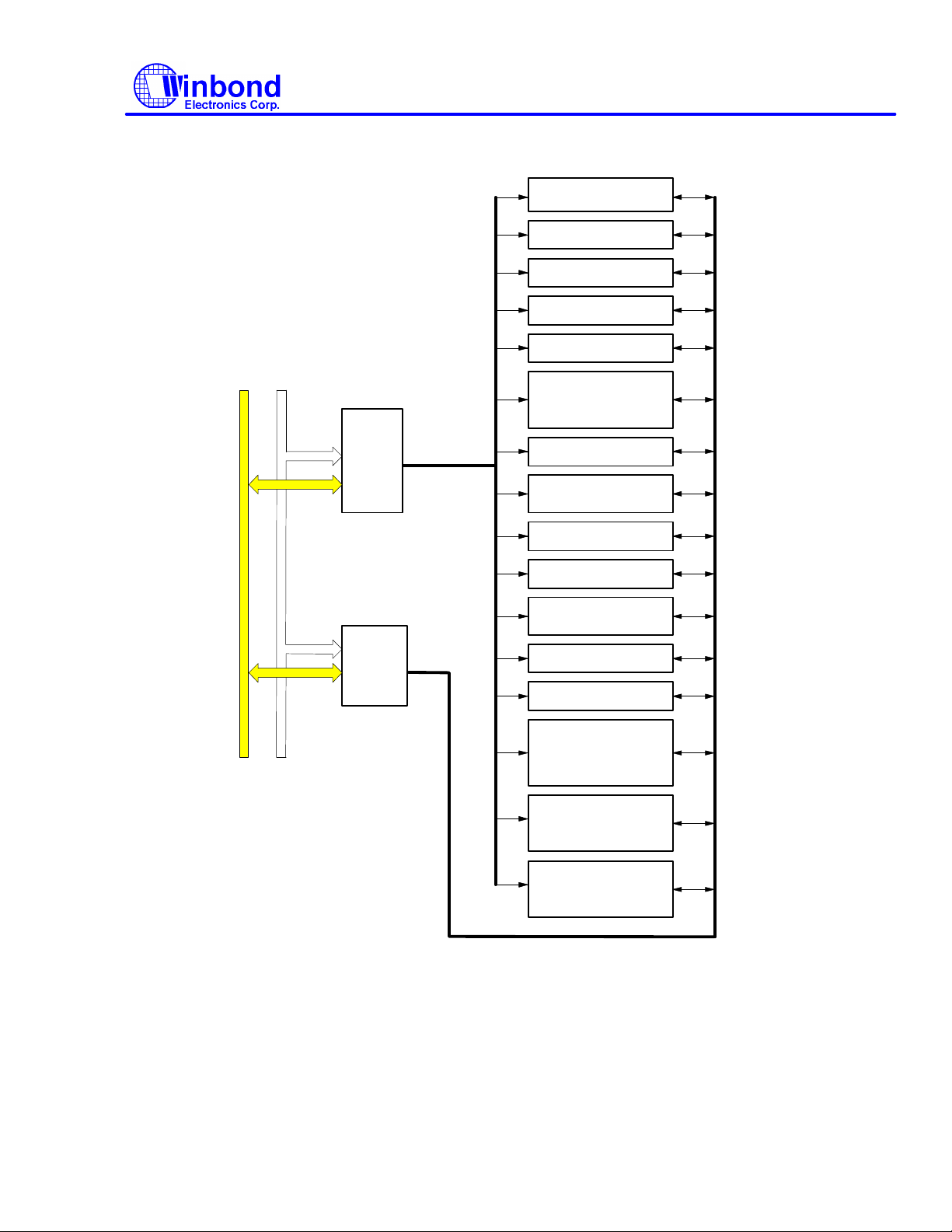

4. BLOCK DIAGRAM

IN0

:

:

:

IN6

VID0

:

VID4

VTIN3

:

VTIN1

:

:

:

:

8-Bit A/D

and Mux

16mV LSB

0~4.096V

Input

Configure

and

Control

Registers

Watch-Dog

and

Interrupt

Status

Registers

W83781D

PRELIMINARY

SMI#

IRQ

OVT#

FAN3

:

FAN1

CASEOPEN

MR

:

:

FAN

Speed

Counter

ISA/Serial Bus Interface

C

S

S

D

C

A

L

(Serial Bus) (ISA Bus Interface)

I

I

C

L

O

K

W

I

R

N

#

A

O

S

2

R

#

D

#

D

A

1

D

A

7

6

0

D

5

D4D3D

BEEP / GPO#

RSTOUT#

D

D

1

2

0

- 3 - Publication Release Date : Nov. 1997

Revision 0.60

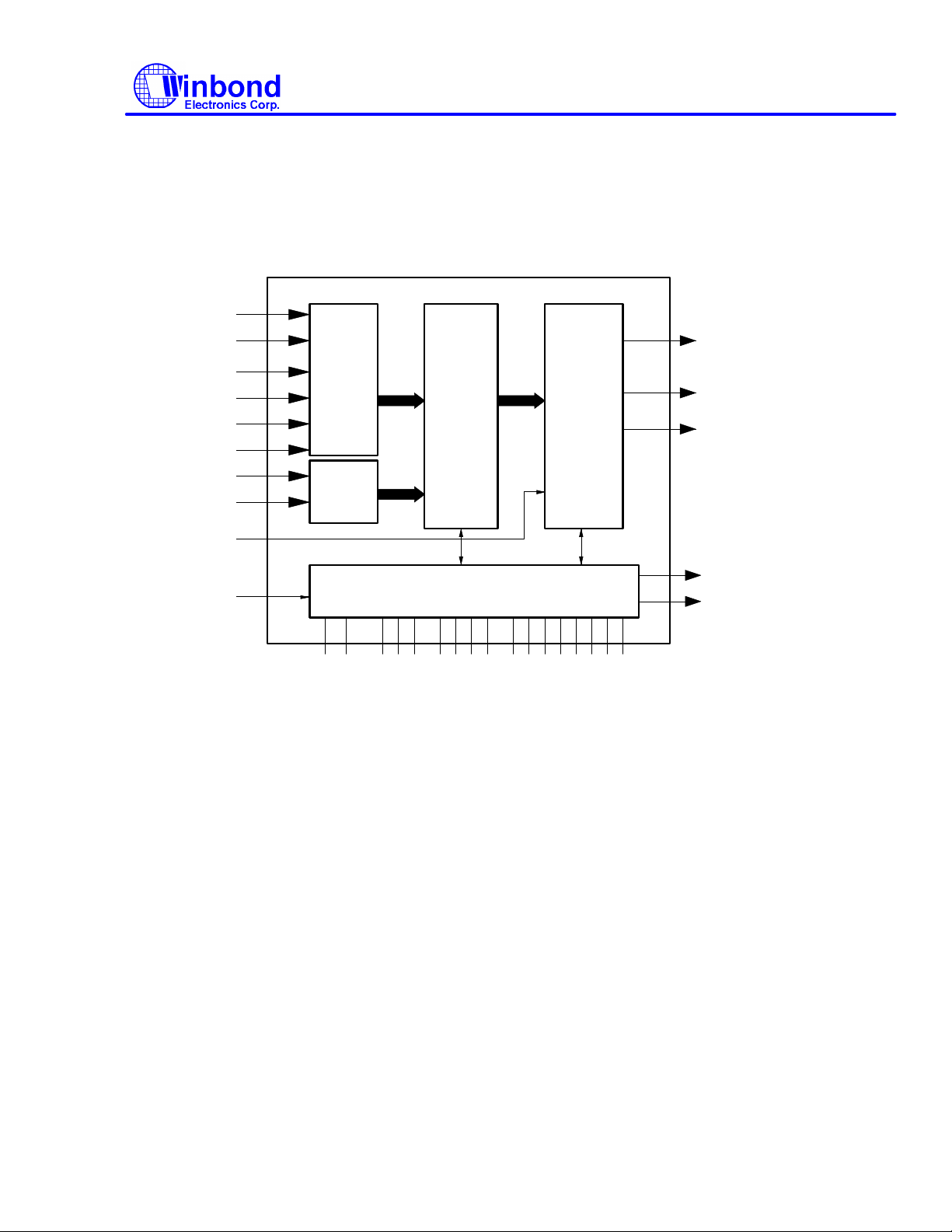

5. PIN CONFIGURATION

1

3

7

N

A

3

#

1

W83781D

PRELIMINARY

B

E

V

V

+

C

C

3.3

O

O

V

R

R

I

E

E

N

A

B

-

-

+

+

-

12

5

12

5

12

V

V

V

V

V

O

O

I

I

I

U

N

U

N

N

T

T

E

P

-

/

G

5

G

V

I

V

N

P

I

D

O

D

#

VREF

VTIN3

VTIN2

VTIN1

VID0

OVT#

IRQ

SMI#

A2

A1

A0

CS#

36

37

48

1

I

I

C

O

O

L

W

R

K

#

I

N

W83781D

D

D

D

D

D6D

4

2

5

25

24

VID2

RSTOUT#

SDA

C

S

L

FAN1 IN/OUT

FAN2 IN/OUT

FAN3 IN/OUT

VID4

CASEOPEN

MR

G ND D

13

12

V

D

D

I

0

D

CC

V

- 4 - Publication Release Date : Nov. 1997

Revision 0.60

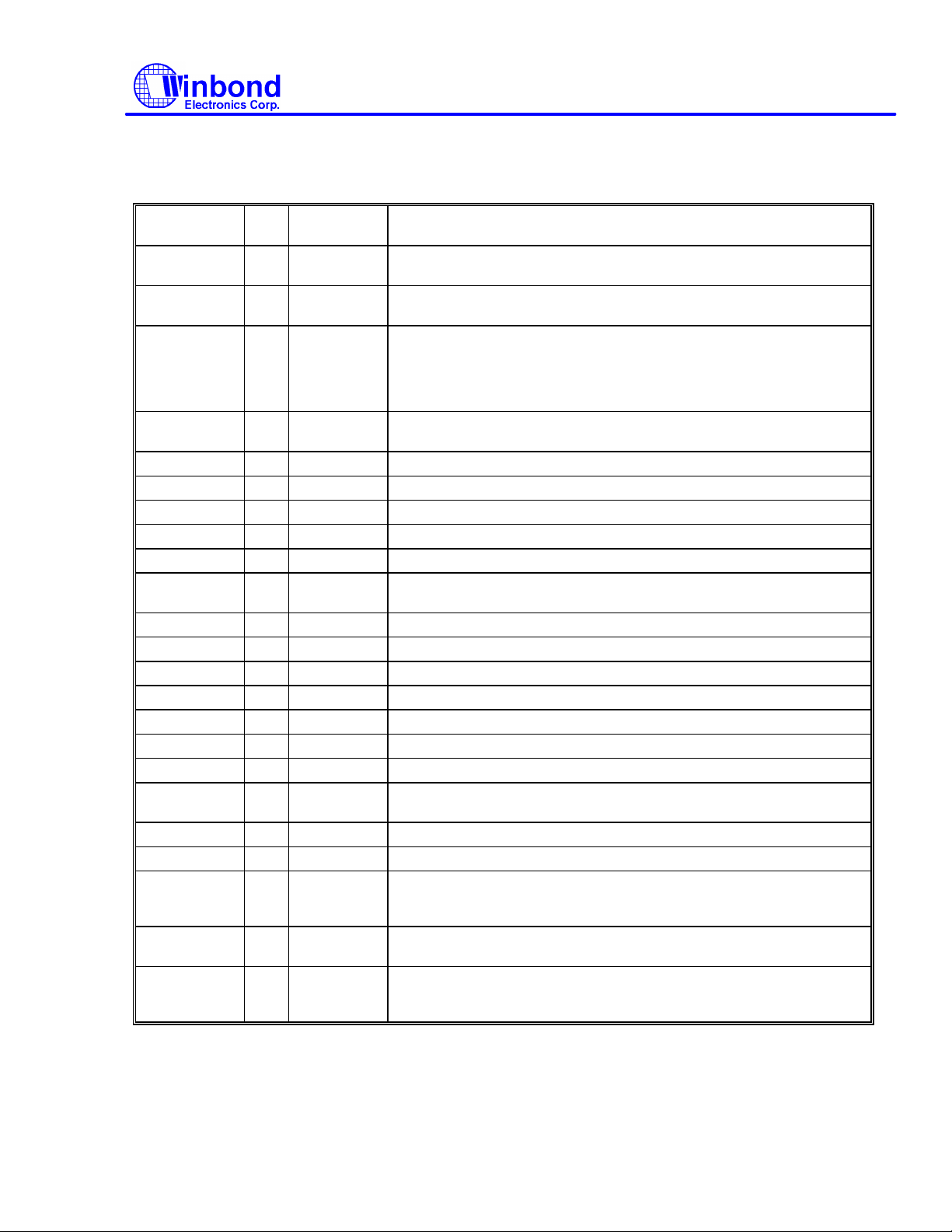

6. PIN DESCRIPTION

Pin

System clock input. Can select 48MHz or 24MHz or 14.318MHz.

The default is 24MHz.

4-

11

Bi-directional ISA bus Data lines. D0 corresponds to the low order

bit, with D7 the high order bit.

Voltage Supply readouts from P6.This value is read in the VID/Fan

Divisor Register.

+5V VCC power. Bypass with the parallel combination of 10µF

(electrolytic or tantalum) and 0.1µF (ceramic) bypass capacitors.

CASE OPEN. An active high input from an external circuit which

latches a Case Open event. This line can go high without any

clamping action intrusion regardless of the powered state of the

W83781D. The W83781D provides an internal open drain on this

line, controlled by Bit 7 of IRQ Mask Register 2, to provide a

minimum 20 ms reset of this line.

Voltage Supply readouts from P6.This value is read in the bit <0>

of Device ID Register.

18-

20

Fan on-off control output. These multifunctional pins can be

programmable input or output.

8 mA driver (open drain), active low output with a 20 ms minimum

pulse width. Available when enabled via Bit 7 in SMI# Mask

Register 2.

I/O

- TTL level bi-directional pin with 12 mA source-sink capability

12t

I/O

- TTL level and schmitt trigger

12ts

OUT

- TTL level output pin with 12 mA source-sink capability

12t

OUT8t - TTL level output pin with 8 mA source-sink capability

AOUT - Output pin(Analog)

OD8 - Open-drain output pin with 8 mA sink capability

OD12 - Open-drain output pin with 12 mA sink capability

OD48 - Open-drain output pin with 48 mA sink capability

INt - TTL level input pin

INts - TTL level input pin and schmitt trigger

AIN - Input pin(Analog)

W83781D

PRELIMINARY

Pin Name

Type Description

No.

IOR# 1 IN

IOW# 2 IN

CLKIN 3 IN

D7~D0

I/O

VID1 12 IN

ts

ts

t

12t

t

An active low standard ISA bus I/O Read Control.

An active low standard ISA bus I/O Write Control.

VCC (+5V) 13 POWER

GNDD 14 DGROUND Internally connected to all digital circuitry.

MR 15 IN

CASEOPEN 16 I/O

VID4 17 IN

FAN3-FAN1

I/O

ts

12t

t

12ts

Master reset input.

0V to +5V amplitude fan tachometer input /

IN/OUT

SCL 21 IN

SDA 22 I/O

ts

12ts

RSTOUT# 23 OUT

Serial Bus Clock.

Serial Bus bi-directional Data.

8t

- 5 - Publication Release Date : Nov. 1997

Revision 0.60

6. Pin Description , continued

Pin

Voltage Supply readouts from P6.This value is read in the VID/Fan

Divisor Register.

Voltage Supply readouts from P6.This value is read in the VID/Fan

Divisor Register.

Beep function or General purpose output (active low). This pin is

open drain driving 48 mA.

Internally connected to all analog circuitry. The ground reference

for all analog inputs.

This pin is Analog Vcc and connects internal monitor channel IN3

with fixed scale.

Voltage Supply readouts from P6.This value is read in the VID/Fan

Divisor Register.

System Management Interrupt (open drain). This output is enabled

when Bit 1 in the Configuration Register (CR40) is set to 1. The

default state is disabled.

45-

47

The three lowest order bits of the 16-bit ISA Address Bus. A0

corresponds to the lowest order bit.

Chip Select input from an external decoder which decodes high

order address bits on the ISA Address Bus. This is an active low

input.

W83781D

PRELIMINARY

Pin Name

Type Description

No.

VID2 24 IN

VID3 25 IN

BEEP/GPO# 26 OD

t

t

48

This multifunctional pin is programmable selected by CR4D bit 6.

GNDA 27 AGROUND

-5VIN 28 AIN Ground-referred inverting op amp input.

-5VOUT 29 AOUT Output of inverting op amp for Input 6.

-12VOUT 30 AOUT Output of inverting op amp for Input 5.

-12VIN 31 AIN Ground-referred inverting op amp input.

+12VIN 32 AIN 0V to 4.096V FSR Analog Inputs.

+5VIN 33 AIN

+3.3VIN 34 AIN 0V to 4.096V FSR Analog Inputs.

VCOREB 35 AIN 0V to 4.096V FSR Analog Inputs.

VCOREA 36 AIN 0V to 4.096V FSR Analog Inputs.

VREF 37 AOUT Reference Voltage.

VTIN3 38 AIN Thermistor 3 terminal input.

VTIN2 39 AIN Thermistor 2 terminal input.

VTIN1 40 AIN Thermistor 1 terminal input.

VID0 41 IN

t

OVT# 42 OD

IRQ 43 OUT

SMI# 44 OD

A2-A0

IN

CS# 48 IN

12

12t

12

t

t

Over temperature Shutdown Output.

Interrupt Request.

# Indicates Active Low("Not")

- 6 - Publication Release Date : Nov. 1997

Revision 0.60

W83781D

PRELIMINARY

7. FUNCTIONAL DESCRIPTION

7.1 General Description

The W83781D provides 5 analog positive inputs, 2 analog negative input, 3 fan speed monitors or fan

ON/OFF control, 3 thermistor voltage inputs, case open detection and beep function output when the

monitor value exceed the set limit value. When start the monitor function on the chip, the watch dog

machine monitor every function and store the value to registers. If the monitor value exceeds the limit

value, the interrupt status will be set to 1.

The W83781D provides two interface for microprocessor to read/write internal registers. The first

interface use ISA Bus to access which the ports of low byte (bit2~bit0) are defined in the port 5h and

6h. The high byte of these ports is decoded by Chip Select (CS#), the general decoded address is set

to port 295h and port 296h. These two ports are described as following:

Port 295h: W83781D Index register port.

Port 296h: Data port.

The register structure is showed as the diagram next page.

The second interface use Serial Bus. In the W83781D has three serial bus address. That is, the first

address defined at CR48 can read/write all registers excluding Bank 1 and Bank 2 temperature 2/3

registers, the second address defined at CR4A.bit2-0 only read/write temperature sensor 2 registers,

and the third address defined at CR4A.bit6-4 only can access (read/write) temperature sensor 3

registers.

- 7 - Publication Release Date : Nov. 1997

Revision 0.60

ISA

Data

Bus

ISA

Address

Bus

Port 5h

Index

Register

Port 6h

Data

Register

Configuration Register

40h

Interrupt Status Registers

41h, 42h

SMI# & IRQ Mask Registers

42h, 43, 44h, 45h

VID<3:0>/Fan Divisor Register

Temperature 2, 3 Serial

Bus Address

Fan IN/OUT and BEEP/GPO#

Control Register

Select Bank for 50h~5Fh Reg.

47h

Serial Bus Address

48h

Monitor Value Registers

20h~3Fh

and

60h~7Fh (auto-increment)

VID<4>/Device ID

49h

4Ah

Pin Control Register

4Bh

IRQ Polarity Select

4Ch

4Dh

4Eh

Winbond Vendor ID

4Fh

BANK 0

R-T Table Value

BEEP Control Register

Winbond Test Register

50h~58h

W83781D

PRELIMINARY

Temperature 2 Control/Staus

Registers

Temperature 3 Control/Staus

Registers

BANK 1

50h~56h

BANK 2

50h~56h

- 8 - Publication Release Date : Nov. 1997

Revision 0.60

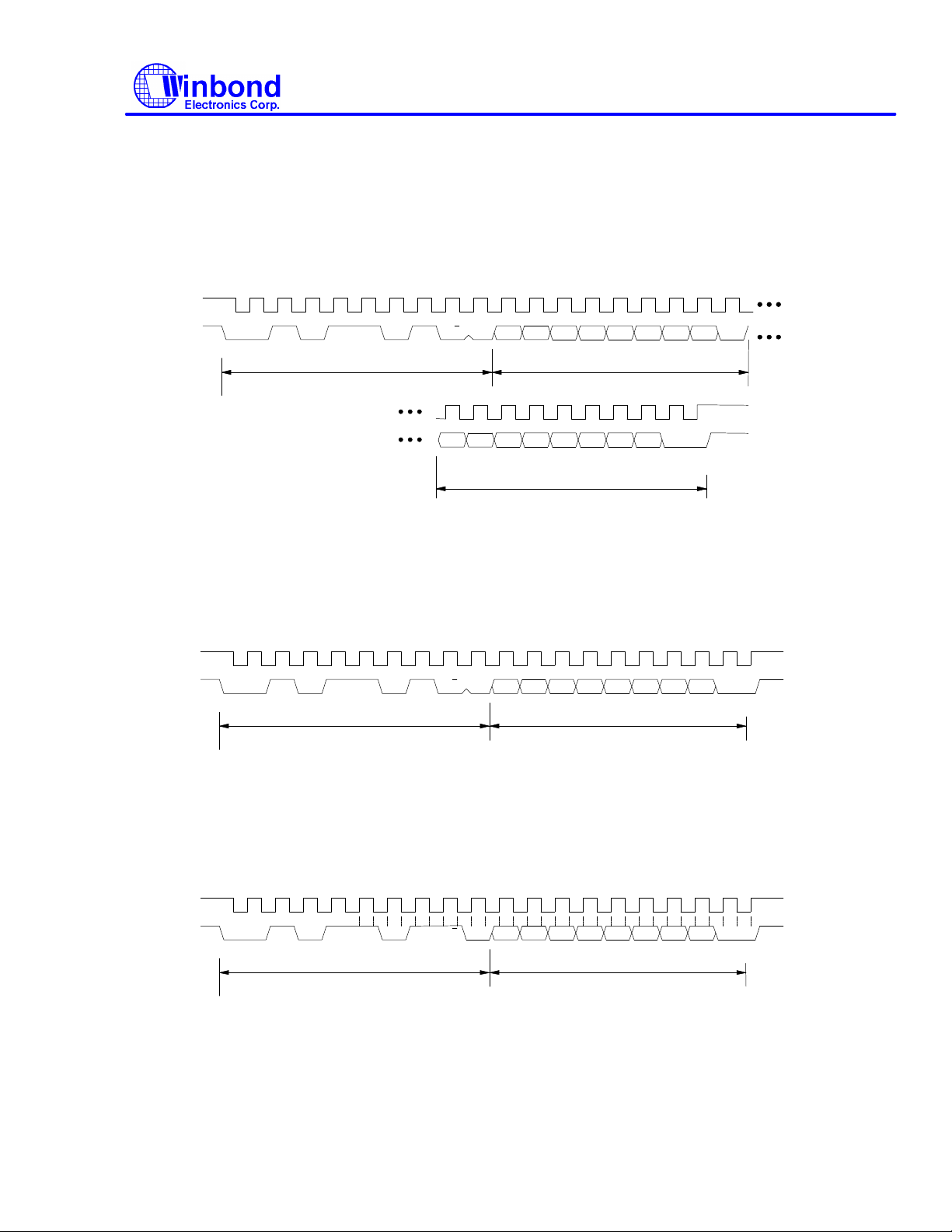

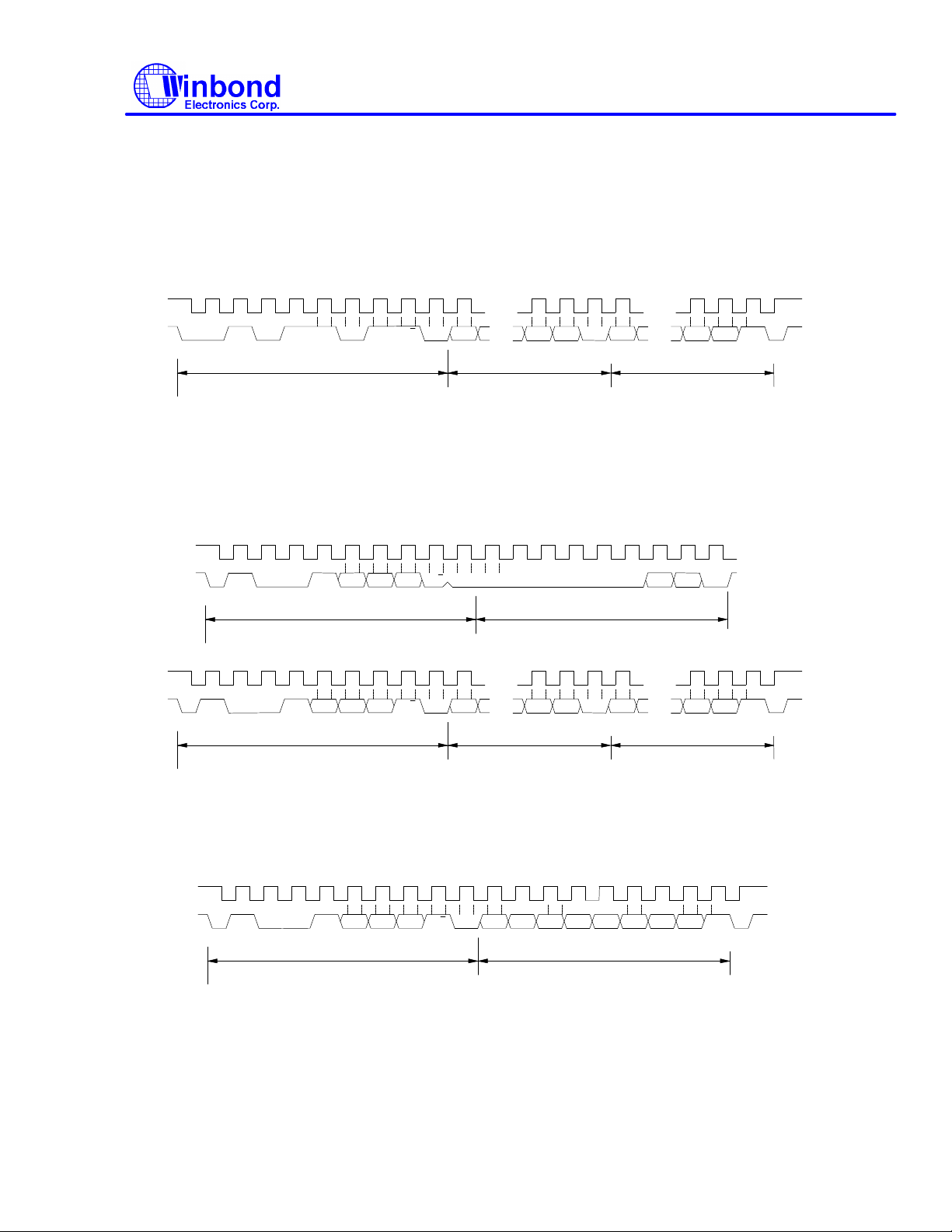

7.1.1 The first serial bus access timing are shown as follow:

(a) Serial bus write to internal address register followed by the data byte

W83781D

PRELIMINARY

0

7 8 0 7 8

SCL

SDA

0 1 0 1 1 0 1 D7 D6 D5 D4 D3 D2 D1 D0

Start By

Master

Frame 1

Serial Bus Address Byte

R/W

781D

Ack

0

SCL

(Continued)

SDA (Continued)

D7 D6 D5 D4 D3 D2 D1 D0

Serial Bus Write to Internal Address Register followed by the Data Byte

(b) Serial bus write to internal address register only

SCL

SDA

0

0 1 0 1 1 0 1 D7 D6 D5 D4 D3 D2 D1 D0

Start By

Master

Frame 1

Serial Bus Address Byte

Serial Bus Write to Internal Address Register Only

7 8 0 7 8

R/W

Ack

by

781D

0

Ack

by

Internal Index Register Byte

Frame 2

781D

by

7 8

Ack

Stop

by

by

781D

Frame 3

Data Byte

Internal Index Register Byte

Frame 2

Master

781D

Ack

Stop by

by

Master

(c) Serial bus read from a register with the internal address register prefer to desired location

SCL

SDA

0

0 1 0 1 1 0 1 D7 D6 D5 D4 D3 D2 D1 D0

Start By

Master

Frame 1

Serial Bus Address Byte

Serial Bus Write to Internal Address Register Only

7 8 0 7 8

R/W

Ack

781D

by

Internal Index Register Byte

Frame 2

0

Ack

by

Master

Stop by

Master

- 9 - Publication Release Date : Nov. 1997

Revision 0.60

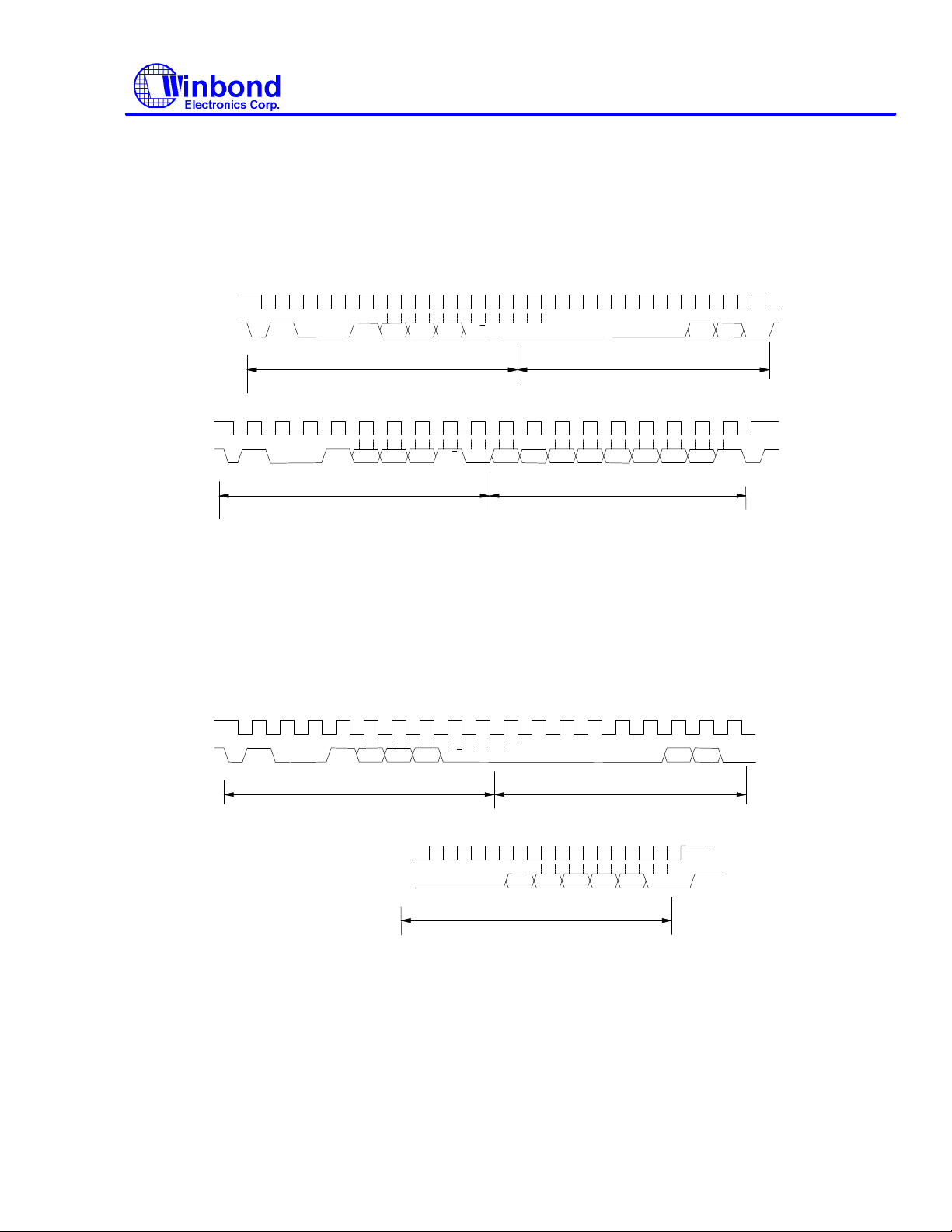

7.1.2 The serial bus timing of the temperature 2 and 3 is shown as follow:

W83781D

PRELIMINARY

(a) Typical 2-byte read from preset pointer location (Temp, TOS, T

SCL

SDA

0

0 1 0 1 1 0 1 D7 D1 D0

Start By

Master

Frame 1

Serial Bus Address Byte

7 8 0 7 8

R/W

Ack

by

781D

... ...

...

Frame 2

MSB Data Byte

)

HYST

0 7

D7 D1 D0

Ack

by

Master

...

LSB Data Byte

Frame 3

Typical 2-Byte Read From Preset Pointer Location

(b) Typical pointer set followed by immediate read for 2-byte register (Temp, TOS, T

4

Frame 2

Pointer Byte

D1 D0

0 7

SCL

SCL

SDA

0

1 0 0 1 A2 A1 A0 R/W

Start By

Master

0

Frame 1

Serial Bus Address Byte

7 8 0

0 0 0 0 0 0

Ack

by

781D

7 8 0 7 8

... ...

781D

Ack

by

HYST

Ack

by

Master

)

Stop by

Master

...

SDA

1 0 0 1 A2 A1 A0 R/W

Start By

Master

Frame 3

Serial Bus Address Byte

0

D7 D1 D0

Ack

by

781D

Frame 4

MSB Data Byte

Ack

by

Master

Typical Pointer Set Followed by Immediate Read for 2-Byte Register

(c) Typical read 1-byte from configuration register with preset pointer

SCL

SDA

0

1 0 0 1 A2 A1 A0 R/W D1D5 D4 D3D6

Start By

Master

Frame 1

Serial Bus Address Byte

Typical 1-Byte Read From Configuration With Reset Pointer

7 8 0

Ack

by

781D

D7 D2

Frame 2

Data Byte

- 10 - Publication Release Date : Nov. 1997

...

D7 D1 D0

Frame 5

LSB Data Byte

8

7

D0

No Ack

by

Master

No Ack

Master

Stop by

Master

Stop by

Master

by

Revision 0.60

(d) Typical pointer set followed by immediate read from configuration register

W83781D

PRELIMINARY

SCL

0

SDA

1 0 0 1 A2 A1 A0 R/W

Start By

Master

Frame 1

Serial Bus Address Byte

0

SCL (Cont..)

SDA (Cont..)

1 0 0 1 A2 A1 A0 R/W

Repea

Start

Master

By

Frame 3

Serial Bus Address Byte

Typical Pointor Set Followed by Immediate Read from Temp 2/3 Configuration Register

(e) Temperature 2/3 configuration register Write

SCL

0

7 8 0

7 8 0

Ack

by

781D

7 8 0

0 0 0 0 000

Ack

by

781D

D7 D5 D4

D6 D3

Frame 4

MSB Data Byte

4

Frame 2

Pointer Byte

D2 D1 D0

4

D1 D0

7

No Ack

Master

7 8

7 8

8

by

781D

Ack

by

Stop by

Master

...

...

SDA

1 0 0 1 A2 A1 A0 R/W

Start By

Master

Frame 1

Serial Bus Address Byte

SCL (Cont...)

SDA (Cont...)

Configuration Register Write

0 0 0 0 0 0 0

Ack

by

781D

0

Frame 2

Pointer Byte

7 8

D1 D0

781D

Ack

by

0 0 D4 D3 D2 D10 D0

Ack

Stop

by

Frame 3

Configuration Data Byte

781D

Master

by

- 11 - Publication Release Date : Nov. 1997

Revision 0.60

Loading...

Loading...