PCI TO ISA BRIDGE SET

W83628F & W83629D

PRELIMINARY

GENERAL DESCRIPTION

W83628F is a PCI-to-ISA bus conversion IC. W83629D is a condensed centralizer

IC for IRQ and DMA control. W83628F and W83629D together form a complete set

for the PCI-to-ISA bridge.

For the new generation Intel chipset Camino and Whitney, featuring LPC bus, there

is no support for ISA bus and slots. However the demand of ISA devices still exist.

For such case, W83628F plus W83629D are the best companion solution for the

non-ISA chipset. Also the packages of W83628F (128-QFP) and W83629D (48LQFP) had been chosen to be the most economic solution for save the M/B board

layout size and cost.

For the new generation chipset featuring LPC interface and support no ISA bus,

W83627HF/F (Winbond LPC I/O) together with the set of W83628F and W83629D

is the complete solution.

FEATURES

PCI to ISA Bridge

•

Full ISA Bus Support including ISA Masters

•

5V ISA and 3.3V PCI interfaces

•

PC/PCI DMA protocol for Software Transparent

•

IRQ Serializer for ISA Parallel IRQ transfer to Serial IRQ

•

Supports 3 fully ISA Compatible Slots without Buffering

•

PCI Bus at 25MHz, 33MHz and up to 40MHz

•

Supports Programmable ISA Bus Divide the PCI Bus Clock into 3 or 4

•

All ISA Signals can be Isolate

•

Supports Configuration registers for programming performance

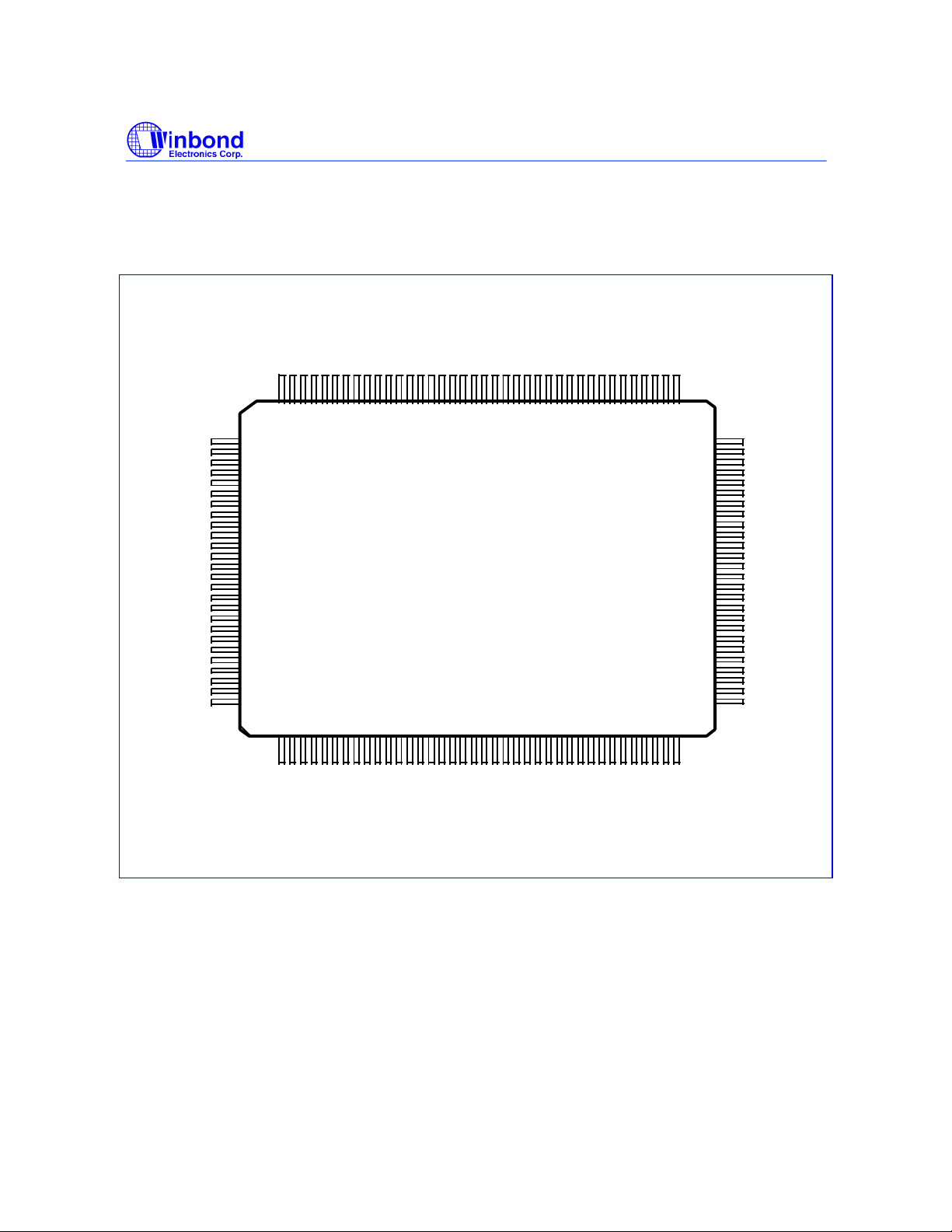

PACKAGE

•

128-pin PQFP for W83628F

•

48-pin LQFP for W83629D

Publication Release Date: Dec 1998

- 1 - Revision 0.32

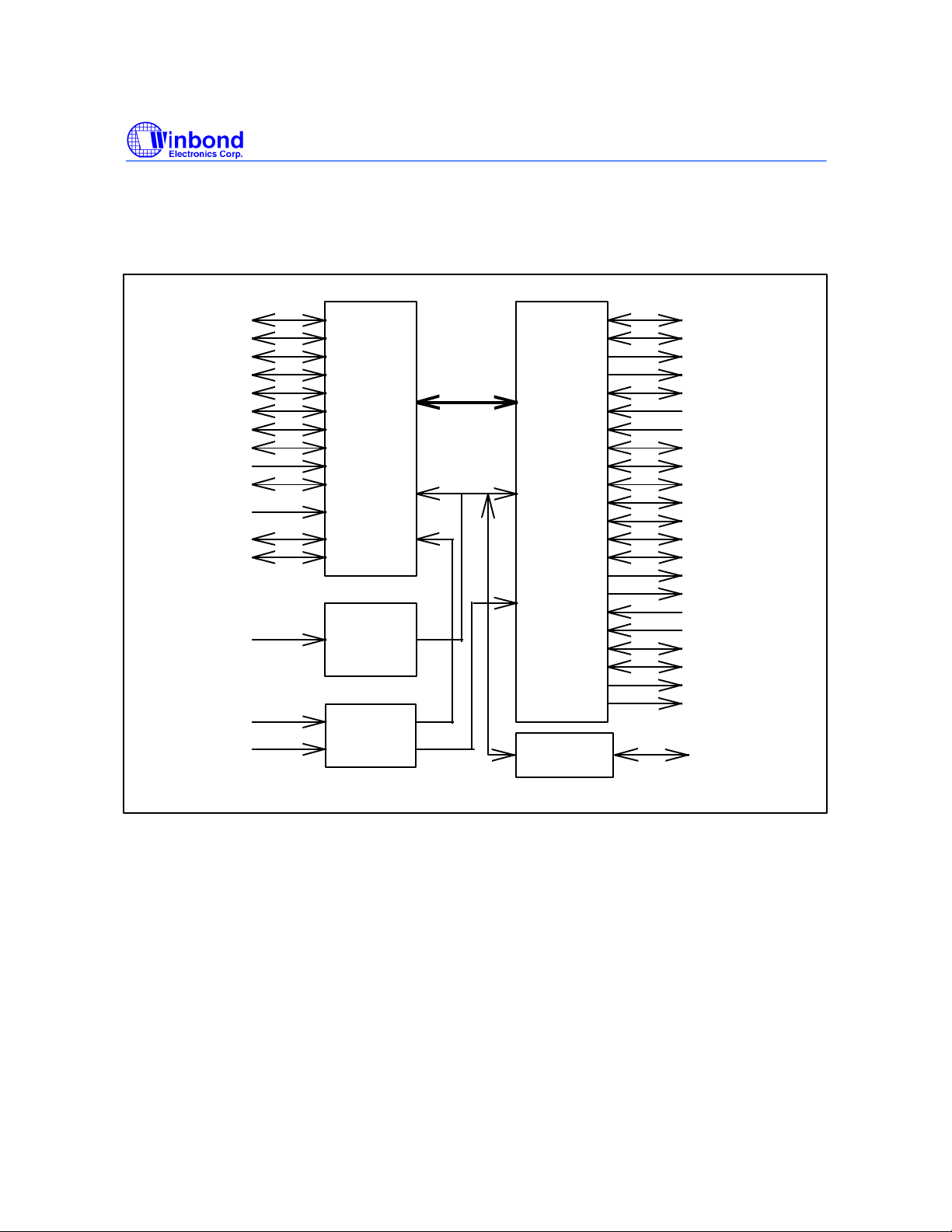

BLOCK DIAGRAM OF W83628F

PCI TO ISA BRIDGE SET

W83628F & W83629D

PRELIMINARY

AD[31:0]

C/BE[3:0]#

PAR

FRAME#

TRDY#

IRDY#

STOP#

DEVSEL#

IDSEL

SERR#

NOGO

PCIRST#

PCICLK

ISOLATE#

3.3V

5V

PCI

Interface

Signal

Isolation

Control

Power

SuppIy

SA[19:0]

SD[15:0]

BALE

AEN

IOCHRDY

IOCS16#

IOCHK#

ISA

Interface

Handshaking HS[2:0]

IOR#

IOW#

LA[23:17]

SBHE#

MEMCS16#

MEMR#

MEMW#

SMEMR#

SMEMW#

ZEROWS#

MASTER#

REFRESH#

ROMCS#

RSTDRV

SYSCLK

Publication Release Date: Jan 1999

- 2 - Revision 0.32

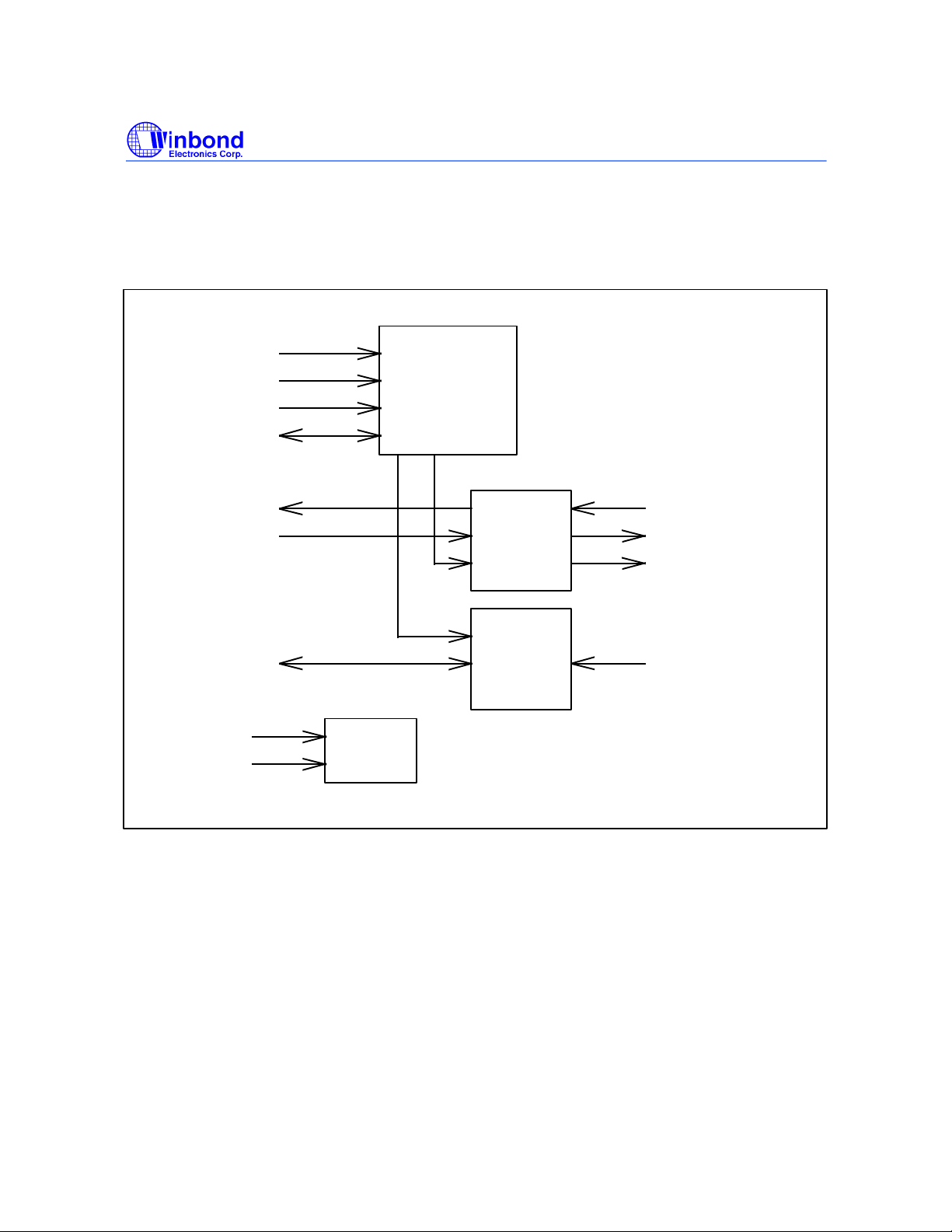

BLOCK DIAGRAM OF W83629D

PCI TO ISA BRIDGE SET

W83628F & W83629D

PRELIMINARY

PCIRST#

PCICLK

NOGO

HS[2:0]

ISAGNT#

3.3V

5V

Power

SuppIy

PCI Host &

Bridge Set

Handshaking

Logic

PCI/PCI

Interface

Serial

to

Parallel

IRQ

DREQ[7:5,3:0]ISAREQ#

DACK[7:5,3:0]#

TC

IRQ[15,14,12:9,7:3]SERIRQ

Publication Release Date: Jan 1999

- 3 - Revision 0.32

PIN CONFIGURATION FOR 628F

S

Y

S

S

S

S

S

S

S

S

S

C

A

A

V

D

C

6

C

A

D

L

1

1

1

7

K

9

8

7

S

G

A

A

A

A

N

1

1

1

1

D

6

5

4

3

PCI TO ISA BRIDGE SET

W83628F & W83629D

PRELIMINARY

R

I

E

P

S

F

R

C

R

O

R

S

I

O

S

S

S

A

A

A

S

S

S

V

S

S

S

S

S

S

1

1

1

A

A

A

C

A

A

2

1

0

7

9

6

C

5

8

S

A

A

A

A

A

4

3

2

1

0

L

E

N

T

R

A

U

S

O

H

G

#

O

A

D

C

S

T

D

R

S

T

E

0

V

#

#

#

G

A

A

A

A

N

D

D

D

D

D

4

1

2

3

SD5

SD4

IOCHK#

ZEROWS#

SD3

SD2

SD1

SD0

GND

HS2

HS1

HS0

VCC

IOCHRDY

SMEMR#

AEN

SMEMW#

IOR#

IOW#

BALE

MEMCS16#

IOCS16#

LA17

LA18

LA19

GND

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

1

1

1

9

0

0

0

9

2

1

0

1 2 345

L

L

L

V

A

A

A

C

2

2

2

C

0

1

2

9

897

L

A

2

3

M

E

M

R

#

L

A

2

2

678 9

969594939

1

0111213

M

S

S

S

E

D

D

D

M

8

9

1

W

0

#

9

1

2

908988878

685

8

8

38281807978

4

W83628F

S

D

1

1

S

S

D

D

1

1

2

3

1

415161718

S

D

1

4

1

222

2

920

324252627

1

M

S

G

A

A

A

A

S

A

B

N

D

S

H

D

1

T

E

5

E

#

R

#

A

D

D

D

D

D

3

3

2

2

2

1

0

9

8

7

7

757

3

V

C

C

282

C

/

B

E

3

#

I

D

S

E

L

7

473

271

9303132

A

A

D

D

2

2

3

2

A

D

2

1

776

A

A

A

D

D

D

2

2

2

6

5

4

7

069

3

3

A

D

2

0

6

6

6

6

867

5

64

3VCC

63

AD5

62

AD6

61

AD7

C/BE0#

60

59

AD8

58

AD9

57

AD10

56

AD11

55

AD12

54

AD13

53

AD14

52

AD15

51

C/BE1#

50

GND

49

PAR

48

PCLK_OUT

47

46

45

44

43

42

41

40

3

3

5

4

A

A

A

D

D

D

1

1

1

9

8

7

39

3

3

3

6

8

7

A

G

D

N

1

D

6

PCICLK

3VCC

SERR#

C/BE2#

DEVSEL#

TRDY#

IRDY#

FRAME#

STOP#

Publication Release Date: Jan 1999

- 4 - Revision 0.32

PIN CONFIGURATION FOR 629D

PCI TO ISA BRIDGE SET

W83628F & W83629D

PRELIMINARY

D

D

D

A

D

C

R

K

N

Q

C

7

A

A

D

D

C

R

R

K

Q

Q

6

7

5

#

6

#

D

C

A

D

D

K

G

5

N

#

D

V

C

R

R

C

K

Q

Q

C

3

3

2

NC

NC

NC

NOGO

ISAREQ#

ISAGNT#

GND

PCICLK

NC

SERIRQ

PCIRST#

3VCC

36

37

48

1

I

G

N

R

D

Q

3

W83629D

I

R

Q

4

V

I

I

I

I

C

R

R

R

R

D

Q

Q

Q

Q

C

5

6

7

9

I

I

I

R

R

R

Q

Q

Q

1

1

1

0 124

25

DACK2#

24

DRQ1

DACK1#

DRQ0

DACK0#

TC

GND

HS2

HS1

HS0

VCC

IRQ15

13

12

I

R

Q

1

Publication Release Date: Jan 1999

- 5 - Revision 0.32

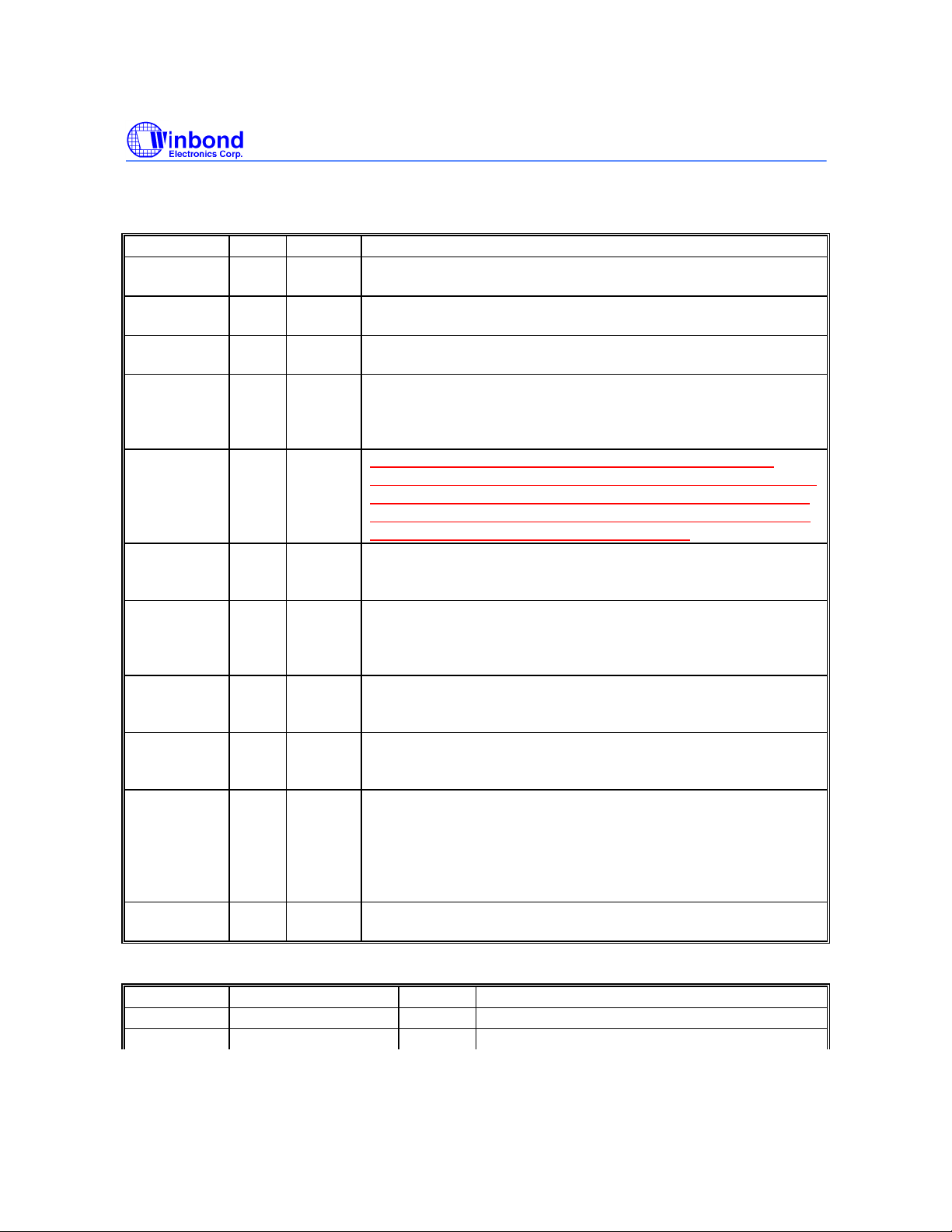

1. PIN DESCRIPTION

Note: Please refer to Section 13.2 DC CHARACTERISTICS for details.

I/O

- TTL level bi-directional pin with 12 mA source-sink capability

12t

I/O

- TTL level bi-directional pin with 24 mA source-sink capability

24t

I/O

- 3.3V TTL level bi-directional pin with 12 mA source-sink capability

12tp3

I/O

- 3.3V TTL level bi-directional pin with 24 mA source-sink capability

24tp3

I/OD

- TTL level bi-directional pin open drain output with 12 mA sink capability

12t

I/O

- TTL level bi-directional pin with 24 mA source-sink capability

24t

OUT

- TTL level output pin with 12 mA source-sink capability

12t

OUT

- TTL level output pin with 24 mA source-sink capability

24t

OUT

OUT

OD12 - Open-drain output pin with 12 mA sink capability

OD24 - Open-drain output pin with 24 mA sink capability

INcs - CMOS level Schmitt-trigger input pin

INt - TTL level input pin

INtd - TTL level input pin with internal pull down resistor

INts - TTL level Schmitt-trigger input pin

IN

- 3.3V TTL level output pin with 12 mA source-sink capability

12tp3

- 3.3V TTL level output pin with 24 mA source-sink capability

24tp3

- 3.3V TTL level Schmitt-trigger input pin

tsp3

PCI TO ISA BRIDGE SET

W83628F & W83629D

PRELIMINARY

1.1 W83628F PIN DESCRIPTION

1.1.1 PCI Interface

SYMBOL PIN I/O FUNCTION

AD[31:0] 19-26

30-37

52-59

61-63

66-70

C/BE[3:0]# 28,45

51,60

PCICLK 47 IN

PCLK_OUT 48

I/O

I/O

OUT

24tp3

24tp3

t

12t

PCI Bus Address and Data Signals. The standard PCI address

and data lines. Address is driven with FRAME# assertion, data is

driven or received in following clocks.

PCI Bus Command and Byte Enables. During the address

phase of a transaction C/BE[3:0]# define the bus command.

During the data phase C/BE[3:0]# are used as Byte Enables.

PCI Bus System Clock. PCICLK provides timing for all

transactions on the PCI bus. All other PCI signals are sampled

on the rising edge of PCICLK, and all timing parameters are

defined with respect to this edge.

PCI Bus System Clock DPLL Output. The PCLK_OUT can

reduce the PCICLK Loading and it produced from internal DPLL.

Publication Release Date: Jan 1999

- 6 - Revision 0.32

PCI TO ISA BRIDGE SET

W83628F & W83629D

1.1.1 PCI Interface, continued

SYMBOL PIN I/O FUNCTION

FRAME# 40

IDSEL 29 IN

STOP# 39

IRDY# 41

TRDY# 42

DEVSEL# 43

SERR# 45 OD

PAR 49

PCIRST# 71 IN

I/O

I/O

I/O

I/O

I/O

I/O

24tp3

t

12tp3

12tp3

12tp3

12tp3

12

12tp3

t

Frame Signal. FRAME# is driven by the current PCI bus master

to indicate the beginning and duration of an access.

Initialization Device Select. IDSEL is used as a chip select

during configuration read and write transactions. This signal

should be externally tied to one of the upper 21 address signals.

Bus Stop#. STOP# indicates the current target is requesting the

master to stop the current PCI bus transaction.

Initiator Ready. IRDY# indicates the initiating agent ability to

complete the current data phase of the PCI bus transaction.

Target Ready. TRDY# indicates the target agent’s ability to

complete the current data phase of the PCI bus transaction.

Device Select. W83628F drives DEVSEL# to indicate that it is

the target of the current PCI bus transaction. W83628F uses

subtractive decoding and the NOGO protocol to claim PCI

transactions.

System Error. SERR# can be pulsed active by any PCI agent

that detects a system error condition.

Parity Signal. W83628F generates even parity across AD[31:0]

and C/BE[3:0]#.

PCI Reset. W83628F receives PCIRST# as a reset from the PCI

Bus.

PRELIMINARY

1.1.2 Control Logic and Handshaking Signals

SYMBOL PIN I/O FUNCTION

HS[2:0]

112-

114

ISOLATE# 72 IN

NOGO 76 IN

I/O

Handshaking Signals. HS[2:0] connected to W83629D for PCI

12

to ISA SET handshaking signals.

HS1 is handshaking Signal 1, this pin weak pulled-down

during PCIRST# is asserted, and apply a pull-up

resistor(4.7Kohm) to this pin disables ISA bridge

subtraction decoder.

Isolation Control Input. Isolate# is an active low signal by user

t

programming to control the W83628F all output signals to

Isolation and Tri-state.

NOGO, This signal indicates which master initiated the current

t

transaction and also indicates whether or not the current bus

cycle is targeted for the ISA bus. This signal is a point-to-point

connection between PCI HOST Bridge and W83628F.

- 7 - Revision 0.32

Publication Release Date: Jan 1999

PCI TO ISA BRIDGE SET

W83628F & W83629D

1.1.3 ISA Interface Signals

SYMBOL PIN I/O FUNCTION

SA[19:17] 98-96 OUT

SA[16:0] 94-83

81-77

SD[15:0] 110-

107,

104,

103,

101,

100,

8-15

AEN 118 OUT

IOR# 120 I/O

IOW# 121 I/O

IOCHRDY 116 I/O

SYSCLK 99 OUT

RSTDRV 74 OUT

IOCS16# 124 IN

SBHE# 18 I/O

IOCHK# 105 IN

I/O

I/O

System Address Bus. These are the upper address lines that

24t

define the ISA’s byte granular address space (up to 1 Mbyte).

SA[19:17] are at an unknown state upon PCIRST#.

System Address Bus. These are the bi-directional lower

24t

address lines that define the ISA’s byte granular address space

(up to 1 Mbyte). SA[16:0] are at an unknown state upon

PCIRST#.

System Data. SD[15:0] provide the 16-bit data path for devices

24t

residing on the ISA Bus. The W83628F tri-states SD[15:0] during

PCIRST#.

Address Enable. AEN is asserted during DMA cycles. This

24t

signal is also driven high during W83628F initiated refresh

cycles. AEN is driven low upon PCIRST#.

I/O Read. IOR# is the command to an ISA I/O slave device that

24t

the slave may drive data on to the ISA data bus (SD[15:0]).

I/O Write. IOW# is the command to an ISA I/O slave device that

24t

the slave may latch data from the ISA data bus (SD[15:0]).

I/O Channel Ready. Resources on the ISA Bus negate

24t

IOCHRDY to indicate that additional time (wait states) is required

to complete the cycle.

ISA System Clock. SYSCLK is the reference clock for the ISA

24t

bus. The SYSCLK is generated by dividing PCICLK by 3 or 4.

Reset Drive. W83628F asserts RSTDRV to reset devices that

24t

reside on the ISA Bus. The W83628F asserts this signal while

the PCIRST# is asserted.

16-bit I/O Chip Select. This signal is driven by I/O devices on

t

the ISA Bus to indicate that they support 16-bit I/O bus cycles.

System Byte High Enable. SBHE# asserted indicates that a

24t

byte is being transferred on the upper byte (SD[15:8]) of the data

bus. SBHE# is at an unknown state upon PCIRST#.

I/O Channel Check. IOCHK# can be driven by any resource on

t

the ISA bus during on detection of an error.

PRELIMINARY

Publication Release Date: Jan 1999

- 8 - Revision 0.32

PCI TO ISA BRIDGE SET

24t

24t

t

24t

12

24t

t

24t

24t

24t

24

W83628F & W83629D

1.1.3 ISA Interface, continued

SYMBOL PIN I/O FUNCTION

MEMR# 6 I/O

MEMW# 7 I/O

MASTER# 17 IN

LA[23:17] 5-2

127-

125

ROMCS# 73 I/O

REFRESH# 75 I/O

ZEROWS# 106 IN

SMEMR# 117 OUT

SMEMW# 119 OUT

BALE 122 OUT

MEMCS16# 123 OD

I/O

Memory Read. MEMR# asserted indicates the current ISA bus

cycle is a memory read.

Memory Write. MEMW# asserted indicates the current ISA bus

cycle is a memory write.

MASTER#. This signal is used with a DREQ line by an ISA

master to gain control of the ISA Bus.

Unlatched Address. The LA[23:17] address lines are bidirectional. These address lines allow accesses to physical

memory on the ISA Bus up to 16 Mbytes. LA[23:17] are outputs

when the W83628F owns the ISA Bus.

ROMCS# ,this pin weak pulled-down during PCIRST is

asserted, and apply a pull-up resistor (4.7 Kohm) to this pin

enable positive decoder of BIOS address range (depend on

Configure register 70 , bit 3,2). When BIOS assress range is

enabled , the PIN is BIOS ROM CS# output.

Refresh. REFRESH# asserted indicates that a refresh cycle is in

progress, or that an ISA master is requesting W83628F to

generate a refresh cycle. Upon PCIRST#, this signal is tri-stated.

Zero Wait States. An ISA slave asserts ZEROWS# after its

address and command signals have been decoded to indicate

that the current cycle can be executed as an ISA zero wait state

cycle. ZEROWS# has no effect during 16-bit I/O cycles.

Standard Memory Read. SMEMR# asserted indicates the

current ISA bus cycle is a memory read cycle to an address

below 1 Mbyte.

Standard Memory Write. SMEMW# asserted indicates the

current ISA bus cycle is a memory write cycle to an address

below 1 Mbyte.

Bus Address Latch Enable. BALE is an active high signal

asserted by the W83628F to indicate that the address (SA[19:0],

LA[23:17]) and SBHE# signal lines are valid.

The LA[23:17] address lines are latched on the trailing edge of

BALE. BALE remains asserted throughout DMA and ISA master

cycles. BALE is driven low upon PCIRST#.

Memory Chip Select 16. MEMCS16# asserted indicates that the

memory slave supports 16-bit accesses.

PRELIMINARY

1.1.4 Power Signals

SYMBOL PIN I/O FUNCTION

VCC 1, 82, 102, 115 PWR

3VCC 27, 46, 64 PWR

5V Supply.

3.3V Supply.

Publication Release Date: Jan 1999

- 9 - Revision 0.32

Loading...

Loading...