Winbond Electronics W83194BR-39B Datasheet

W83194BR-39B

STEP-LESS 3-DIMM CLOCK

1.0 GENERAL DESCRIPTION

The W83194BR-39B is a Clock Synthesizer which provides all clocks required for high-speed RISC or

CISC microprocessor such as Intel Pentium II or Pentium III. W83194BR-39B provides 64 CPU/PCI

frequencies which are selectable with smooth transitions by hardware or software. W83194BR-39B

also provides 13 SDRAM clocks controlled by the none-delay buffer_in pin.

The W83194BR-39B provides step-less frequency programming by controlling the VCO freq. and the

programmable PCI clock output divisor ratio. A watch dog timer is quipped and when time out, the

RESET# pin will output 4ms pulse signal.

The W83194BR-39B accepts a 14.318 MHz reference crystal as its input. Spread spectrum built in at

±0.5% or ±0.25% to reduce EMI. Programmable stopping individual clock outputs and frequency

selection through I2C interface. The device meets the Pentium power-up stabilization, which requires

CPU and PCI clocks be stable within 2 ms after power-up. Using dual function pin for the slots(ISA,

PCI, CPU, DIMM) is not recommend.

2.0 PRODUCT FEATURES

• Supports Pentium II and !!! CPU with I2C.

• 2 CPU clocks (one free-running CPU clock)

• 13 SDRAM clocks for 3 DIMMs

• 6 PCI synchronous clocks

• One IOAPIC clock for multiprocessor support

• Optional single or mixed supply:

(Vddq1=Vddq2 = Vddq3 = Vddq4 = VddL1 =VddL2= 3.3V) or (Vddq1= Vddq2 = Vddq3=Vddq4 =

3.3V, VddL1 = VddL2 = 2.5V)

• < 250ps skew among CPU and SDRAM clocks

• < 250ps skew among PCI clocks

• < 5ns propagation delay SDRAM from buffer input

• Skew from CPU (earlier) to PCI clock 1 to 4ns, center 2.6ns.

• Smooth frequency switch with selections from 66 MHz to 200 MHz CPU

• Step-less frequency programming by controlling the VCO freq. and the clock output divisor ratio

• I2C 2-Wire serial interface and I2C read back

• ±0.25% or ±0.5% spread spectrum function to reduce EMI in freq. table mode

• Programmable spread spectrum in the M/N step-less mode

• Programmable registers to enable/stop each output and select modes

• MODE pin for power Management

• RESET# out when watch dog timer time out

• One 48 MHz for USB & one 24 MHz for super I/O

Publication Release Date: June 2000

- 1 - Revision 0.46

• 48-pin SSOP package

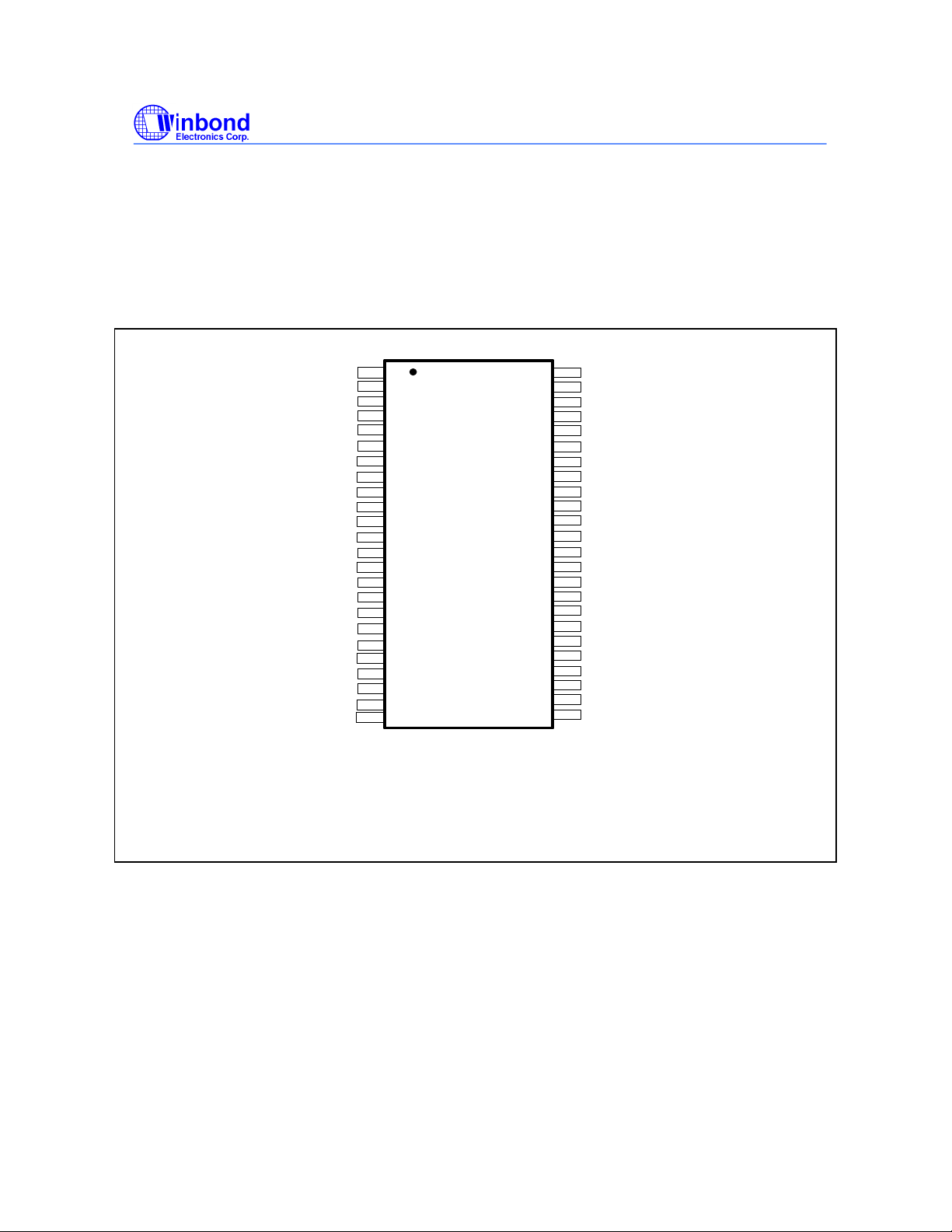

3.0 PIN CONFIGURATION

W83194BR-39B

PRELIMINARY

Vddq1

* PD#/REF0^

Vss

Xin

Xout

Vddq2

PCICLK_F/MODE0*

PCICLK0^/FS3&

Vss

PCICLK1^

PCICLK2^

PCICLK3^

PCICLK4

Vddq2

BUFFER IN

Vss

SDRAM11

SDRAM10

Vddq3

SDRAM 9

SDRAM 8

Vss

SDATA*

SDCLK*

* :internal 120K pull-high

&:Internal 120K pull-down

^ :1.5X strength

#: active low

$ :open drain

16

21

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

17

18

19

20

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

VddL1

IOAPIC

REF1/FS2*

Vss

CPUCLK_F

CPUCLK1

VddL2

RESET$

SDRAM12

Vss

SDRAM 0

SDRAM 1

Vddq3

SDRAM 2

SDRAM 3

Vss

SDRAM 4

SDRAM 5

Vddq3

SDRAM 6

SDRAM 7

Vddq4

48MHz/FS0*

24MHz/FS1*

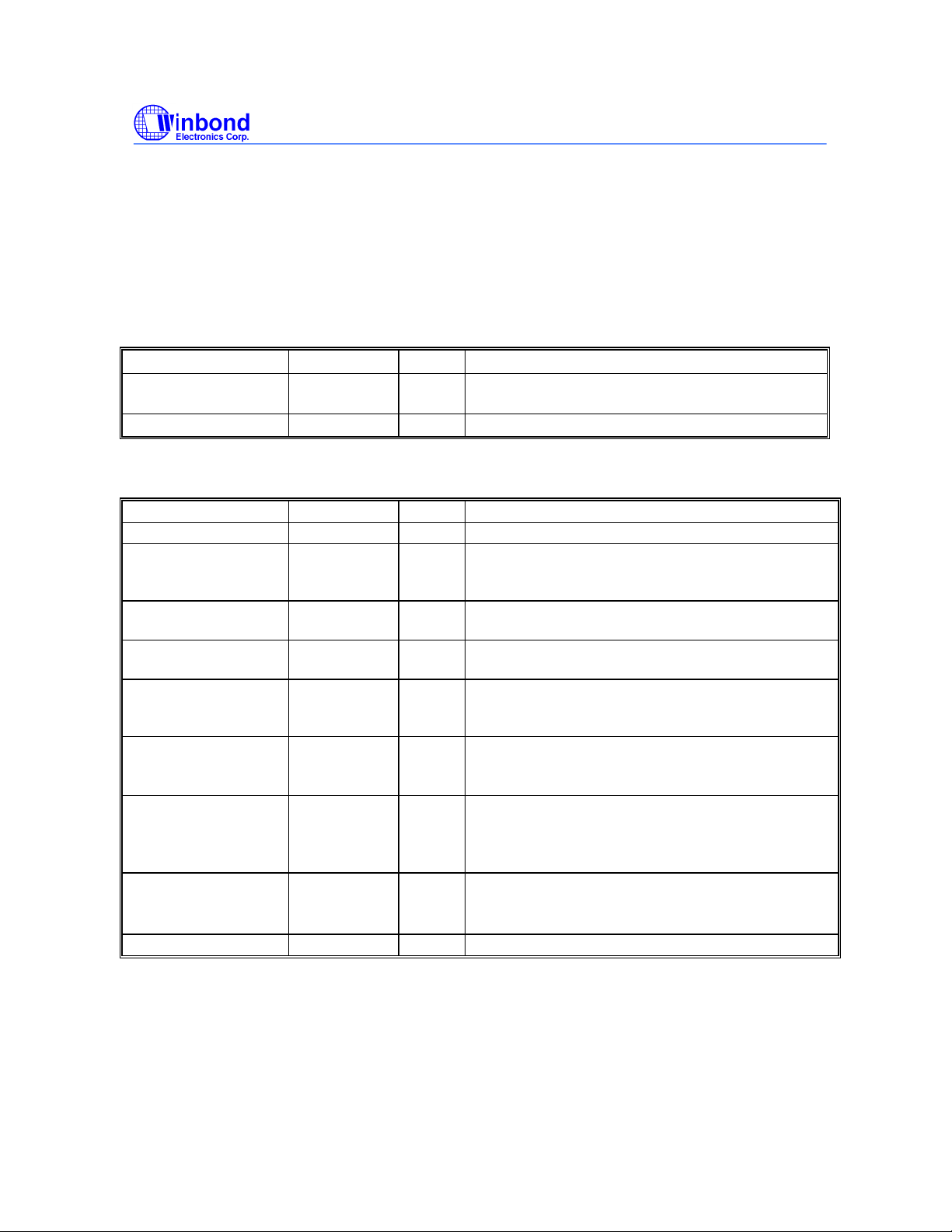

4.0 PIN DESCRIPTION

IN - Input

OUT - Output

I/O - Bi-directional Pin

# - Active Low

Publication Release Date: June 2000

- 2 - Revision 0.46

& - Internal 120KΩ pull-down

Latched Input. *Mode0=1, Pin 2 is REF0; *Mode0=0,

PCICLK0^/FS3&

* - Internal 120kΩ pull-up

4.1 Crystal I/O

SYMBOL PIN I/O FUNCTION

Xin 4 IN Crystal input with internal loading capacitors and

Xout 5 OUT Crystal output at 14.318MHz nominally.

4.2 CPU, SDRAM, PCI, IOAPIC Clock Outputs

SYMBOL PIN I/O FUNCTION

CPUCLK_F 44 OUT Free running CPU clock. Not affected by PD#

CPUCLK1 43 OUT Low skew (< 250ps) clock outputs for host

RESET# 41 OD RESET# (open drain, 4ms low active pulse when

IOAPIC 47 OUT High drive buffered output of the crystal, and is

SDRAM [ 0:12] 17,18,20,21,28

,29,31,32,34,

35,37,38,40

PCICLK_F/

*MODE0

PCICLK [1:3]^

PCICLK 4

BUFFER IN 15 IN Inputs to fanout for SDRAM outputs.

7 I/O Free running PCI clock during normal operation.

8 I/O Low skew (< 250ps) PCI clock outputs.

10,11,12,13 OUT Low skew (< 250ps) PCI clock outputs.

W83194BR-39B

PRELIMINARY

feedback resistors.

frequencies such as CPU, Chipset and Cache.

Powered by VddL2. Low if PD# is low.

Watch Dog time out)

powered by VddL1.

OUT SDRAM clock outputs. Fanout buffer outputs from

BUFFER IN pin.(Controlled by chipset)

Pin2 is PD#

Latched input for FS3 at initial power up for H/W

selecting the output frequency of CPU and PCI

clocks.

PCICLK 0:3 are double strength pins

PCICLK 4 is not.

Publication Release Date: June 2000

- 3 - Revision 0.46

W83194BR-39B

PRELIMINARY

4.3 I2C Control Interface

SYMBOL PIN I/O FUNCTION

SDATA* 23 I/O Serial data of I2C 2-wire control interface

SDCLK* 24 IN Serial clock of I2C 2-wire control interface

4.4 Fixed Frequency Outputs

SYMBOL PIN I/O FUNCTION

REF0^ / PD# 2 I/O 14.318MHz reference clock. This REF output is the

stronger buffer for ISA bus loads.(pin7 *Mode0=1)

Halt all clocks at logic 0 level, when input low (pin7

*Mode0=0)

REF1 / FS2* 46 I/O 14.318MHz reference clock.

Latched input for FS2 at initial power up for H/W

selecting the output frequency of CPU, SDRAM and

PCI clocks.

24MHz / FS1* 25 I/O 24MHz output clock.

Latched input for FS1 at initial power up for H/W

selecting the output frequency of CPU, SDRAM and

PCI clocks.

48MHz / FS0* 26 I/O 48MHz output for USB during normal operation.

Latched input for FS0 at initial power up for H/W

selecting the output frequency of CPU, SDRAM and

PCI clocks.

4.5 Power Pins

SYMBOL PIN FUNCTION

Vddq1 1 Power supply for Ref [0:1] crystal and core logic.

VddL1 48 Power supply for IOAPIC output, either 2.5V or 3.3V.

VddL2 42 Power supply for CPUCLK[0:3], either 2.5V or 3.3V.

Vddq2 6, 14 Power supply for PCICLK_F, PCICLK[0:4], 3.3V.

Vddq3 19, 30, 36 Power supply for SDRAM[0:12], and CPU PLL core,

nominal 3.3V.

Vddq4 27 Power for 24 & 48MHz output buffers and fixed PLL

core.

Vss 3,9,16,22,33,39,45 Circuit Ground.

Publication Release Date: June 2000

- 4 - Revision 0.46

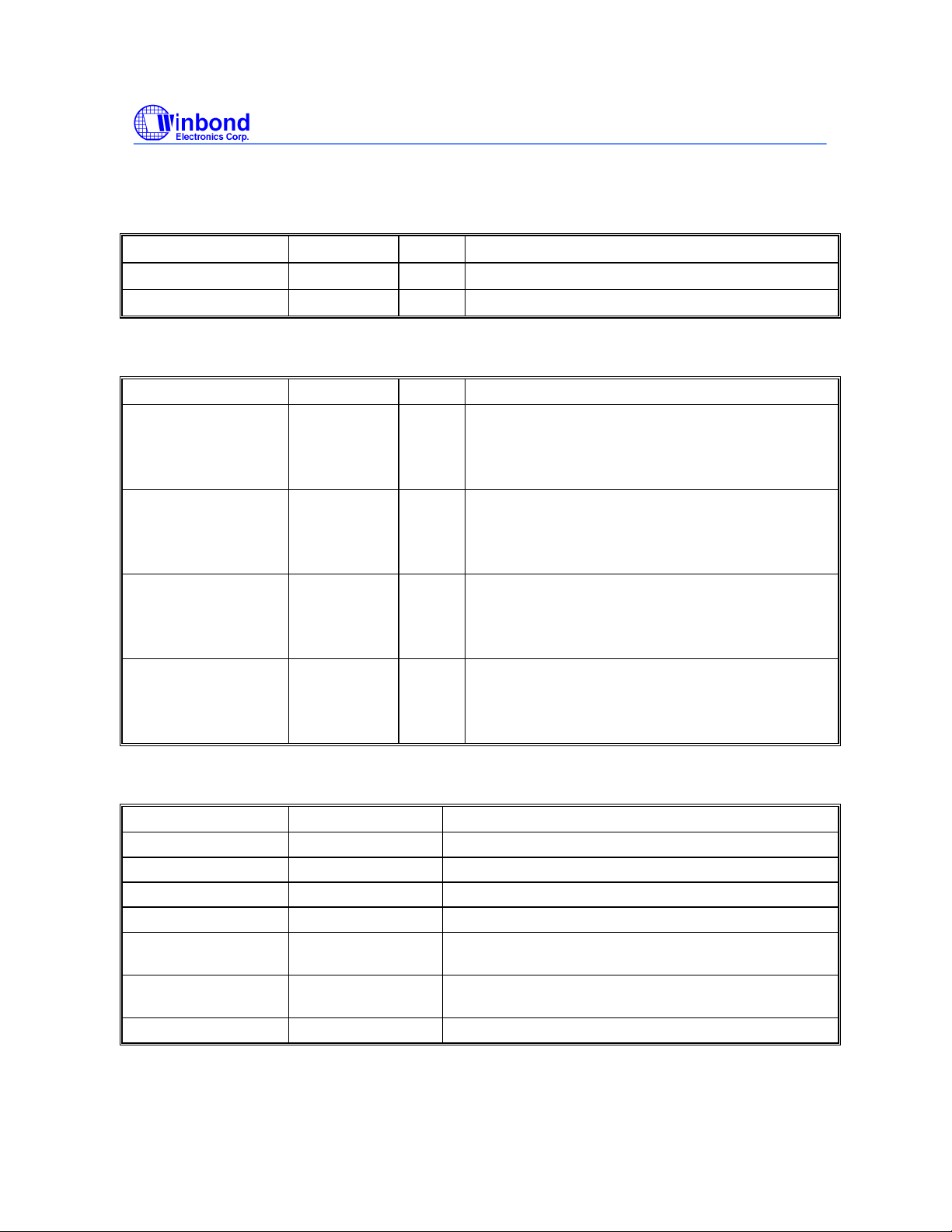

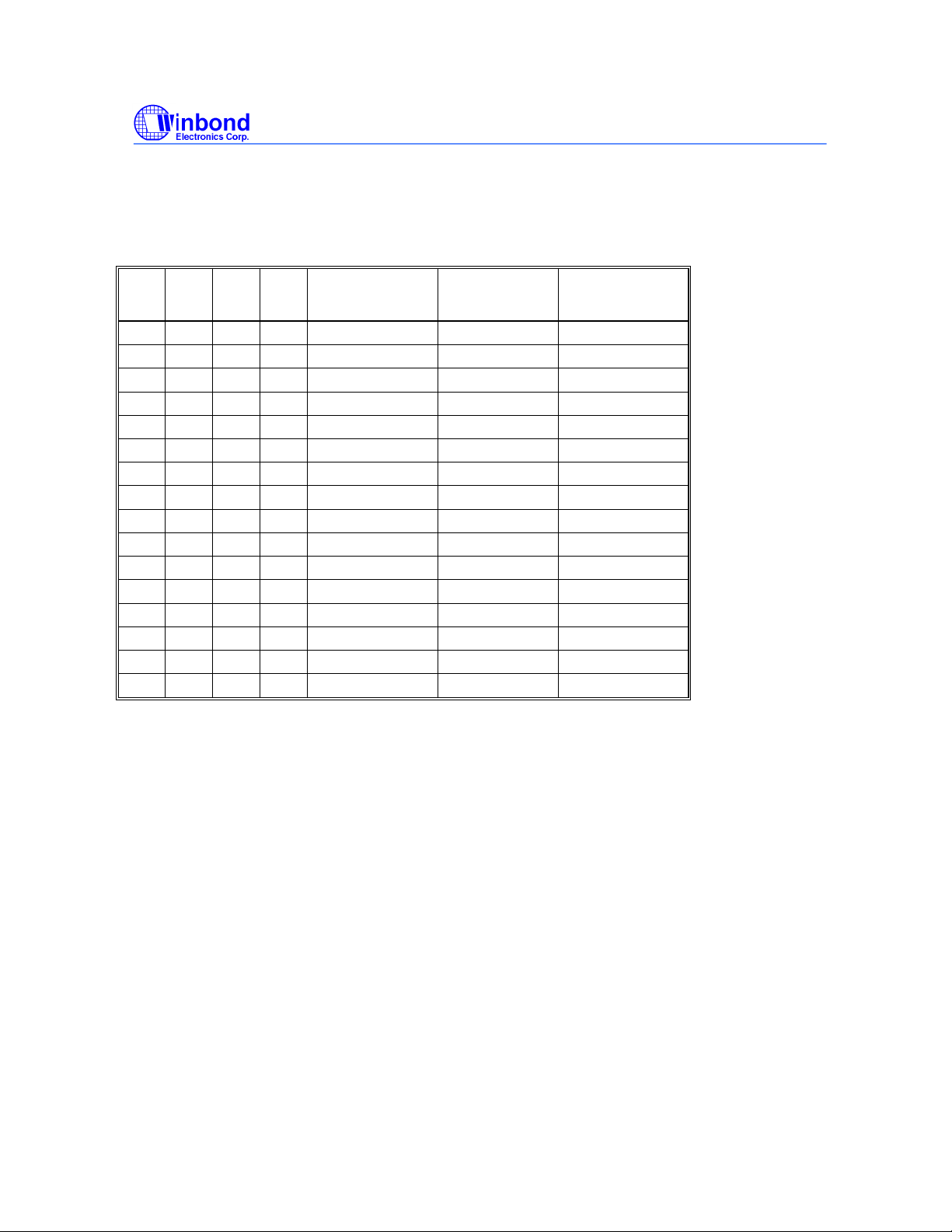

5.0 FREQUENCY BY HARDWARE

W83194BR-39B

PRELIMINARY

FS3 FS2 FS1 FS0

0 0 0 0 80.00 80.00 40.00

0 0 0 1 75.00 75.00 37.50

0 0 1 0 83.30 83.30 41.65

0 0 1 1 66.82 66.82 33.41

0 1 0 0 103.00 103.00 34.33

0 1 0 1 112.00 112.00 37.34

0 1 1 0 68.01 68.01 34.01

0 1 1 1 100.23 100.23 33.41

1 0 0 0 120.00 120.00 30.00

1 0 0 1 115.00 115.00 38.33

1 0 1 0 120.00 120.00 40.00

1 0 1 1 105.00 105.00 35.00

1 1 0 0 140.00 140.00 35.00

1 1 0 1 155.00 155.00 38.75

1 1 1 0 124.00 124.00 31.00

1 1 1 1 133.30 133.30 33.30

CPU(MHz) SDRAM(MHz)

PCI(MHz)

Publication Release Date: June 2000

- 5 - Revision 0.46

W83194BR-39B

PRELIMINARY

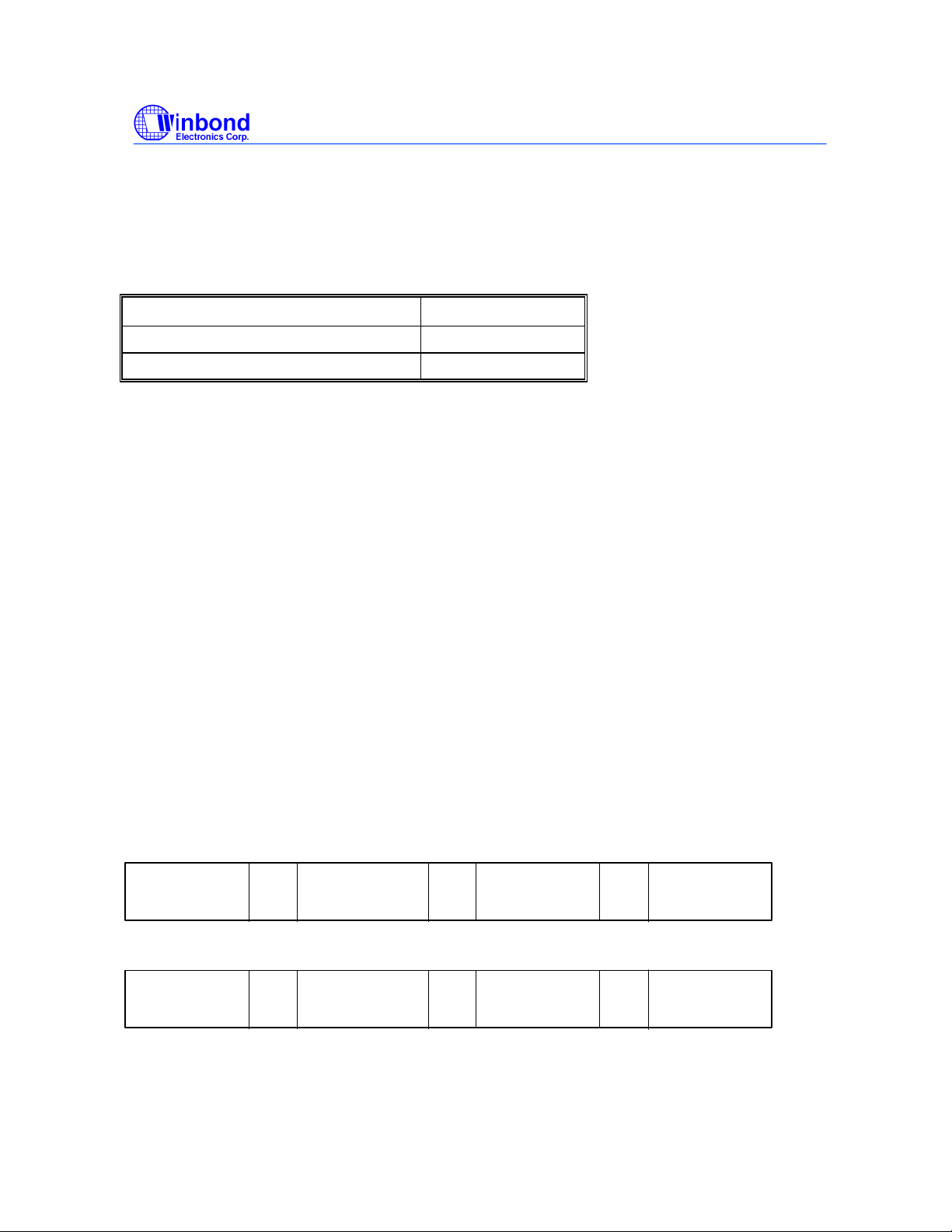

6.0 MODE PIN -POWER MANAGEMENT INPUT CONTROL

MODE0, Pin7 (Latched Input) PIN 2

0 PD# (Input)

1 REF0 (Output)

7.0 FUNCTION DESCRIPTION

7.1 2-WIRE I2C CONTROL INTERFACE

The clock generator is a slave I2C component which can be read back the data stored in the latches

for verification. All proceeding bytes must be sent to change one of the control bytes. The 2-wire

control interface allows each clock output individually enabled or disabled. On power up, the

W83194BR-39Binitializes with default register settings. Use of the 2-wire control interface is then

optional.

The SDATA signal only changes when the SDCLK signal is low, and is stable when SDCLK is high

during normal data transfer. There are only two exceptions. One is a high-to-low transition on

SDATA while SDCLK is high used to indicate the beginning of a data transfer cycle. The other is a

low-to-high transition on SDATA while SDCLK is high used to indicate the end of a data transfer

cycle. Data is always sent as complete 8-bit bytes followed by an acknowledge generated.

Byte writing starts with a “start” condition followed by 7-bit slave address and a write command bit

[1101 0010], command code checking [0000 0000], and byte count checking. After successful

reception of each byte, an “acknowledge“ (low) on the SDATA wire will be generated by the clock

chip. Controller can start to write to internal I2C registers after the string of data. The sequence

order is as follows:

Bytes sequence order for I2C controller :

Clock Address

A(6:0) & R/W

Set R/W to 1 when ?ead back”, the data sequence is as follows :

Clock Address

A(6:0) & R/W

Ack

Ack

8 bits dummy

Command code

Byte 0 Ack

Ack

8 bits dummy

Byte count

Byte 1

Ack

Ack

Byte0,1,2...

until Stop

Byte2, 3, 4...

until Stop

Publication Release Date: June 2000

- 6 - Revision 0.46

Loading...

Loading...