Winbond Electronics W83194BR-138 Datasheet

W83194BR-138

200MHZ CLOCK FOR SOLANO CHIPSET

1.0 GENERAL DESCRIPTION

The W83194BR-138 is a Clock Synthesizer for Intel 815 Solano chipset. W83194BR-138 provides all

clocks required for high-speed RISC or CISC microprocessor and also provides 64 different

frequencies of CPU, SDRAM, PCI, 3V66, IOAPIC clocks frequency setting. All clocks are externally

selectable with smooth transitions.

The W83194BR-138 provides I2C serial bus interface to program the registers to enable or disable

each clock outputs and provides 0.25% and 0.5% center type spread spectrum to reduce EMI.

The W83194BR-138 provides stepless frequency programming by controlling the VCO freq. and the

clock output divisor ratio. Also the skew of CPU, SDRAM and 3V66 clock outputs are programmable.

A watch dog timer is quipped and when time out, the RESET# pin will output 4ms pulse signal.

The W83194BR-138 accepts a 14.318 MHz reference crystal as its input and runs on a 3.3V supply.

High drive PCI and SDRAM CLOCK outputs typically provide greater than 1 V /ns slew rate into 30

pF loads. CPU CLOCK outputs typically provide better than 1 V /ns slew rate into 20 pF loads as

maintaining 50± 5% duty cycle. The fixed frequency outputs as REF, 24MHz, and 48 MHz provide

better than 0.5V /ns slew rate.

2.0PRODUCT FEATURES

• 2 CPU clocks

• 3 3V66 clocks

• 9 SDRAM clocks for 2 DIMMs

• 8 PCI synchronous clocks.

• Optional single or mixed supply:

(VDDR = VDDP=VDDS = VDD48 = VDD3 = 3.3V, VDDA=VDDC=2.5V)

• Skew form CPU to PCI clock -1 to 4 ns, center 2.6 ns

• Smooth frequency switch with selections from 66.8 to 200MHz

• I2C 2-Wire serial interface and I2C read back

• 0.25% or 0.5% center type spread spectrum

• Programmable registers to enable/stop each output and select modes

(mode as Tri-state or Normal )

• 48 MHz for USB

• 24 MHz for super I/O

• Packaged in 48-pin SSOP

Publication Release Date: May 2000

- 1 - Revision 0.37

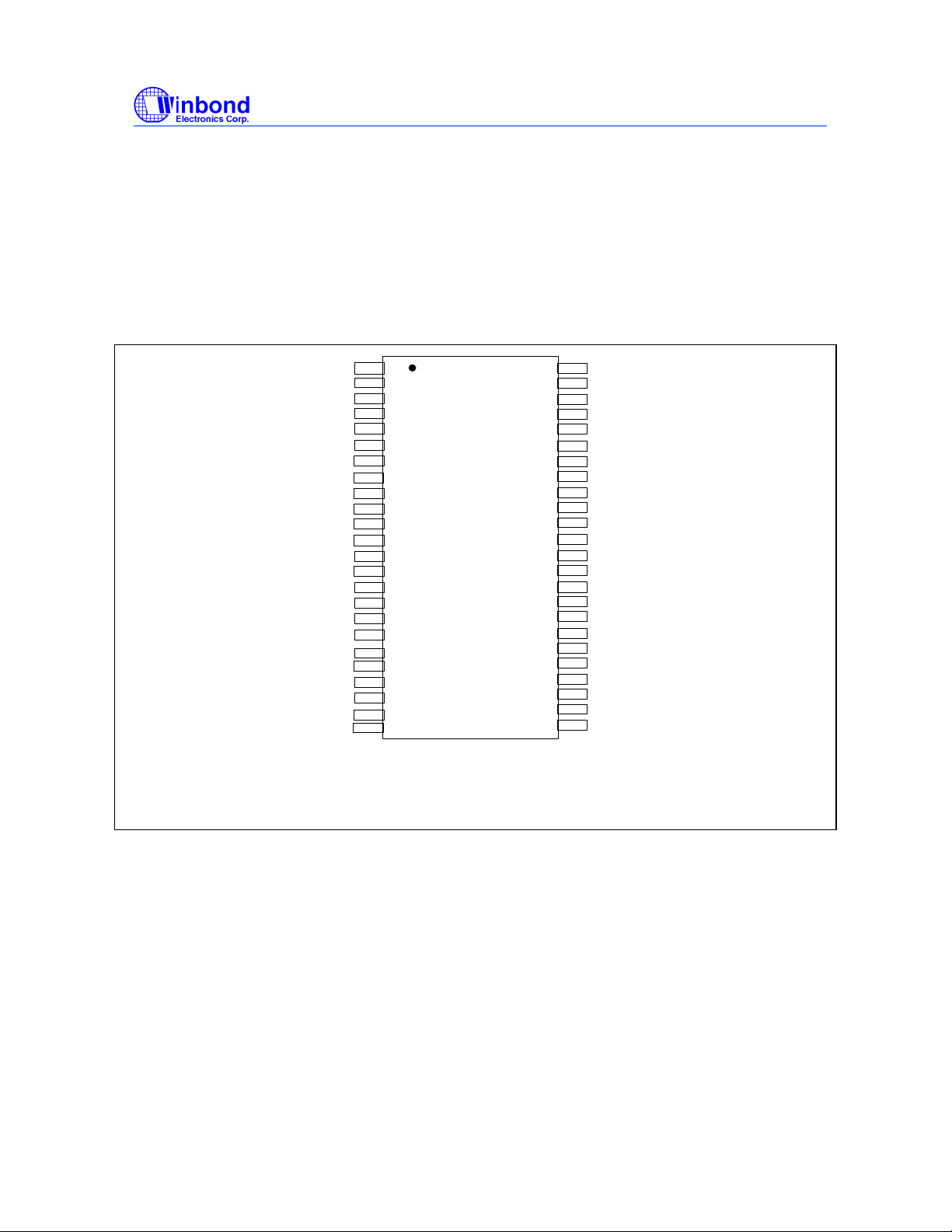

3.0 PIN CONFIGURATION

W83194BR-138

PRELIMINARY

REF1/*SEL24_48#

VDDR

Xin

Xout

VSS

VSS

3V66-0

3V66-1

3V66-2

VDD3

VDDP

PCICLK0/ FS0*

PCICLK1/ FS1&

PCICLK2/Mode1*

VSS

PCICLK3

PCICLK4

VDDP

PCICLK5

PCICLK6

VSS

PD*#/RESET$

SDCLK*

SDATA*

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

*: pull up

&: pull down

$: open drain

^:1.5X~2X driving strength

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

VddA

IOAPIC

VDDC

CPUCLK0

CPUCLK1

VSS

VSS

SDRAM 0

SDRAM 1

SDRAM 2

VDDS

SDRAM 3

SDRAM 4

SDRAM 5

VSS

SDRAM 6

SDRAM 7

SDRAM_F

VDDS

VSS

24_48MHz/ FS2&

48MHz-1/FS3*

48MHz-0/ FS4*

VDD48

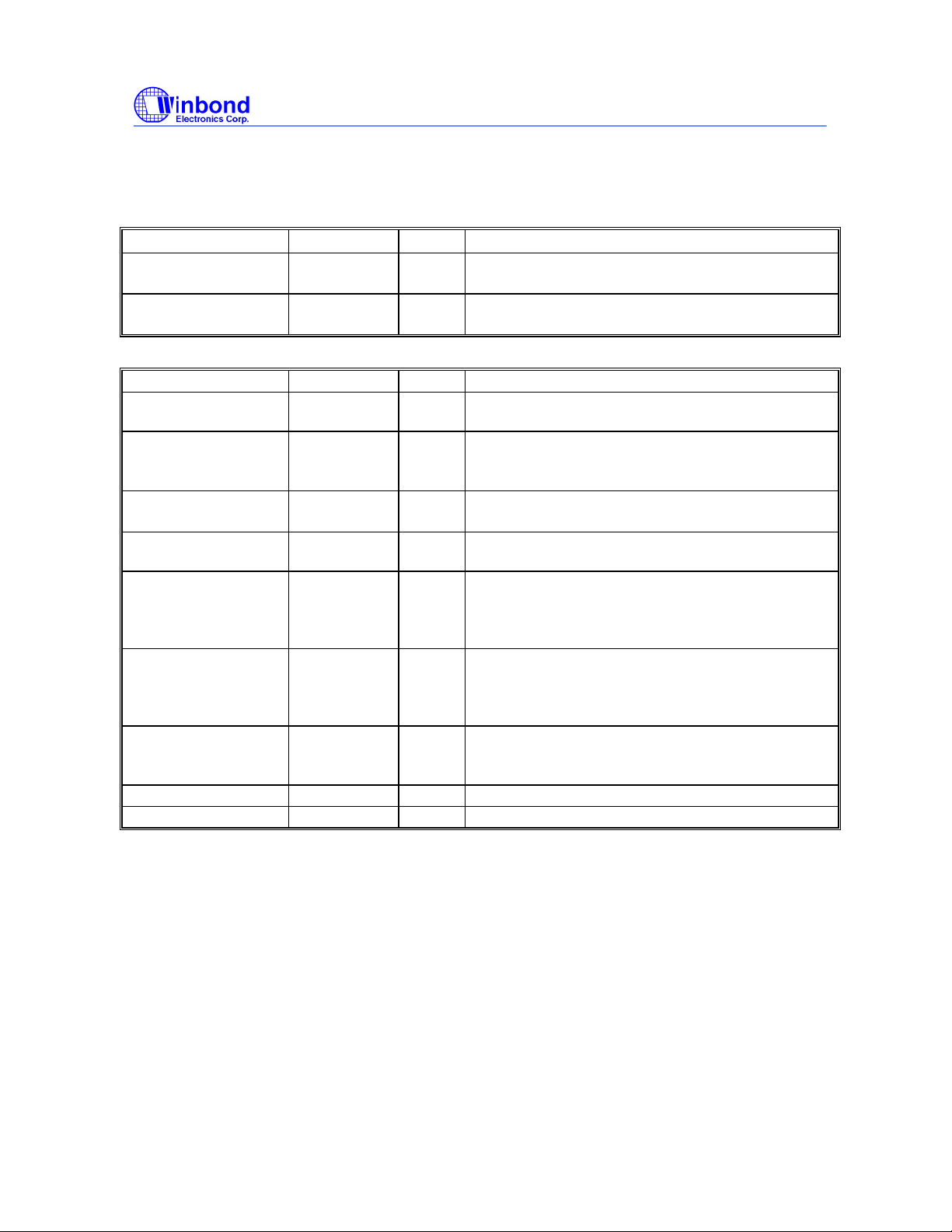

4.0 PIN DESCRIPTION

IN - Input

OUT - Output

I/O - Bi-directional Pin

# - Active Low

* - Internal 250kΩ pull-up

Publication Release Date: May 2000

- 2 - Revision 0.37

PCICLK1/ FS1&

4.1 Crystal I/O

Xin 3 IN Crystal input with internal loading capacitors(36pF)

Xout 4 OUT Crystal output at 14.318MHz nominally with internal

4.2 CPU, SDRAM, PCI, IOAPIC Clock Outputs

CPUCLK [0:1] 45,44 OUT Low skew (< 250ps) clock outputs for host

PD#/ RESET$ 22 I/OD If Mode1*=1, Power Down mode when driven low.

IOAPIC

SDRAM_F,

SDRAM[0:7]

PCICLK0/ *FS0 12 I/O 3.3V 33MHz PCI clock during normal operation.

PCICLK2/ Mode1*

PCICLK [ 3:6 ] 16,17,19,20 OUT Low skew (< 250ps) PCI clock outputs.

3V66 [0:2] 7,8,9 OUT 3.3V output clocks for the chipset.

W83194BR-138

SYMBOL PIN I/O FUNCTION

and feedback resistors.

loading capacitors(36pF).

SYMBOL PIN I/O FUNCTION

frequencies such as CPU and Chipset.

If Mode1*=0, 4ms pulse RESET# (open drain) when

Watch dog timer time out

47 OUT Clock outputs synchronous with PCI clock and

powered by VddA.

31,32,33,35,36

,37,39,40,41

13 I/O Low skew (< 250ps) PCI clock outputs.

15 I/O Low skew (< 250ps) PCI clock outputs.

OUT SDRAM clock outputs.

Latched input for FS0 at initial power up for H/W

selecting the output frequency of CPU, SDRAM and

PCI clocks(Default=1).

Latched input for FS1 at initial power up for H/W

selecting the output frequency of CPU, SDRAM and

PCI clocks(Default=0).

Latched input for Mode1* pin at initial power up for

the output PD#/RESET# output selection.

PRELIMINARY

Publication Release Date: May 2000

- 3 - Revision 0.37

W83194BR-138

wire control interface with internal

PRELIMINARY

4.3 I2C Control Interface

SYMBOL PIN I/O FUNCTION

*SDATA 24 I/O Serial data of I2C 2-

*SDCLK 23 IN Serial clock of I2C 2-wire control interface with

4.4 Fixed Frequency Outputs

SYMBOL PIN I/O FUNCTION

REF0 / *SEL24_48# 1 I/O 14.318MHz reference clock. This REF output is the

24_48MHz/FS2& 28 I/O 24MHz or 48MHz output clock. Default is 24MHz.

48MHz_0/ FS3* 27 I/O 48MHz / Latched input for FS3 at initial power up

48MHz_1/ FS4* 26 I/O 48MHz / Latched input for FS3 at initial power up

pull-up resistor.

internal pull-up resistor.

stronger buffer for ISA bus loads.

Latched input for SEL24_48 at initial power up for

H/W selecting the output frequency of 24_48MHz

(Default=1, 24MHz).

Latched input for FS2 at initial power up for H/W

selecting the output frequency of CPU, SDRAM and

PCI clocks(Default=0).

for H/W selecting the output frequency of CPU,

SDRAM and PCI clocks (Default=1).

for H/W selecting the output frequency of CPU,

SDRAM and PCI clocks (Default=1).

4.5 Power Pins

SYMBOL PIN FUNCTION

VddC,VddA 46,48 Power supply for CPU & IOAPIC, 2.5V or 3.3V.

Vdd48 25 Power supply for 48MHz output,3.3V.

Vdd3 10 Power supply for 3V_66 output, 3.3V.

VddP 11,18 Power supply for PCICLK, 3.3V.

VddR 2 Power supply for REF0, 3.3V.

VddS 30,38 Power supply for SDRAM_F,SDRAM[0:11], nominal

3.3V.

Vss 5,6,14,21,29,34,42,

43

Circuit Ground.

Publication Release Date: May 2000

- 4 - Revision 0.37

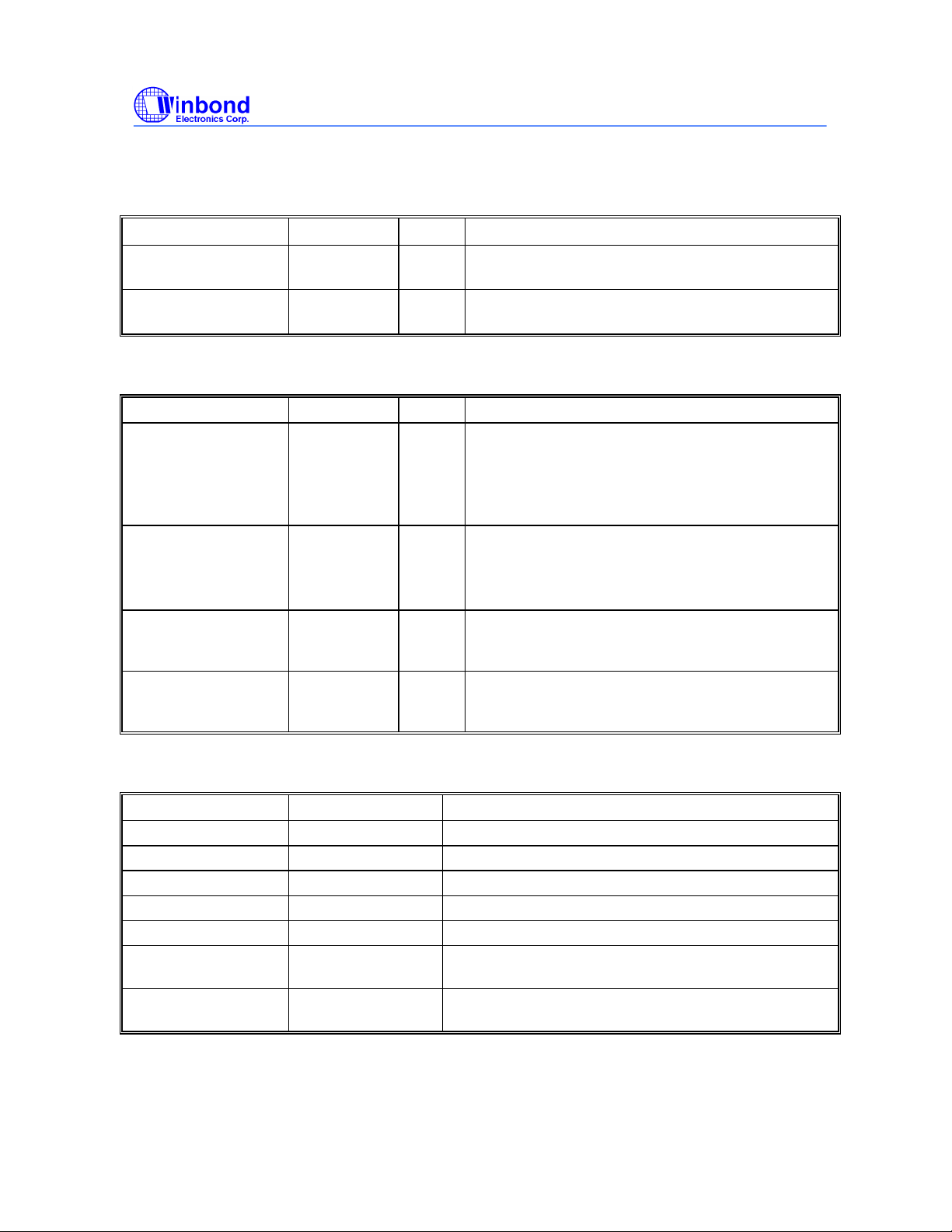

5.0 FREQUENCY SELECTION BY HARDWARE

W83194BR-138

PRELIMINARY

FS4 FS3 FS2 FS1 FS0

0 0 0 0 0 66.67 100.00 66.67 33.33 16.67

0 0 0 0 1 66.87 100.31 66.87 33.44 16.72

0 0 0 1 0 68.67 103.00 68.67 34.33 17.17

0 0 0 1 1 71.34 107.00 71.34 35.67 17.83

0 0 1 0 0 100.00 100.00 66.67 33.33 16.67

0 0 1 0 1 100.30 100.30 66.87 33.43 16.72

0 0 1 1 0 103.00 103.00 68.67 34.33 17.17

0 0 1 1 1 107.00 107.00 71.33 35.67 17.83

0 1 0 0 0 133.33 133.33 66.67 33.33 16.67

0 1 0 0 1 133.73 133.73 66.87 33.43 16.72

0 1 0 1 0 137.33 137.33 68.67 34.33 17.17

0 1 0 1 1 120.00 120.00 60.00 30.00 15.00

0 1 1 0 0 133.33 100.00 66.67 33.33 16.67

0 1 1 0 1 133.73 100.30 66.87 33.43 16.72

0 1 1 1 0 137.33 103.00 68.67 34.33 17.17

0 1 1 1 1 120.00 90.00 60.00 30.00 15.00

1 0 0 0 0 136.00 136.00 68.00 34.00 17.00

1 0 0 0 1 140.00 140.00 70.00 35.00 17.50

1 0 0 1 0 142.67 142.67 71.33 35.67 17.83

1 0 0 1 1 145.33 145.33 72.67 36.33 18.17

1 0 1 0 0 136.00 102.00 68.00 34.00 17.00

1 0 1 0 1 140.00 105.00 70.00 35.00 17.50

1 0 1 1 0 142.67 107.00 71.34 35.67 17.83

1 0 1 1 1 145.33 109.00 72.67 36.33 18.17

1 1 0 0 0 146.67 146.67 73.34 36.67 18.33

1 1 0 0 1 153.33 153.33 76.67 38.33 19.17

1 1 0 1 0 160.00 160.00 80.00 40.00 20.00

1 1 0 1 1 166.67 166.67 83.34 41.67 20.83

1 1 1 0 0 146.67 110.00 73.34 36.67 18.33

1 1 1 0 1 160.00 120.00 80.00 40.00 20.00

1 1 1 1 0 166.67 125.00 83.34 41.67 20.83

1 1 1 1 1 200.00 200.00 100.00 50.00 25.00

CPU(MHz)

SDRAM

(MHz)

3V66(MHz) PCI(MHz)

IOAPIC

(MHz)

Publication Release Date: May 2000

- 5 - Revision 0.37

Loading...

Loading...