Winbond Electronics W78E52BP-40, W78E52BP-24, W78E52BF-40, W78E52BF-24, W78E52B-40 Datasheet

...

Preliminary W78E52B

INT2

8-BIT MTP MICROCONTROLLER

GENERAL DESCRIPTION

The W78E52B is an 8-bit microcontroller which can accommodate a wider frequency range with low

power consumption. The instruction set for the W78E52B is fully compatible with the standard 8051.

The W78E52B contains an 8K bytes MTP ROM (Multiple-Time Programmable ROM); a 256 bytes

RAM; four 8-bit bi-directional and bit-addressable I/O ports; an additional 4-bit I/O port P4; three 16bit timer/counters; a hardware watchdog timer and a serial port. These peripherals are supported by

eight sources two-level interrupt capability. To facilitate programming and verification, the MTP-ROM

inside the W78E52B allows the program memory to be programmed and read electronically. Once

the code is confirmed, the user can protect the code for security.

The W78E52B microcontroller has two power reduction modes, idle mode and power-down mode,

both of which are software selectable. The idle mode turns off the processor clock but allows for

continued peripheral operation. The power-down mode stops the crystal oscillator for minimum power

consumption. The external clock can be stopped at any time and in any state without affecting the

processor.

FEATURES

• Fully static design 8-bit CMOS microcontroller

• Wide supply voltage of 4.5V to 5.5V

• 256 bytes of on-chip scratchpad RAM

• 8 KB electrically erasable/programmable MTP-ROM

• 64 KB program memory address space

• 64 KB data memory address space

• Four 8-bit bi-directional ports

•One extra 4-bit bit-addressable I/O port, additional

(available on 44-pin PLCC/QFP package)

• Three 16-bit timer/counters

• One full duplex serial port(UART)

• Watchdog Timer

• Eight sources, two-level interrupt capability

• EMI reduction mode

• Built-in power management

• Code protection mechanism

• Packages:

− DIP 40: W78E52B-24/40

− PLCC 44: W78E52BP-24/40

− PQFP 44: W78E52BF-24/40

- 1 - Revision A1

/ INT3

Publication Release Date: December 1998

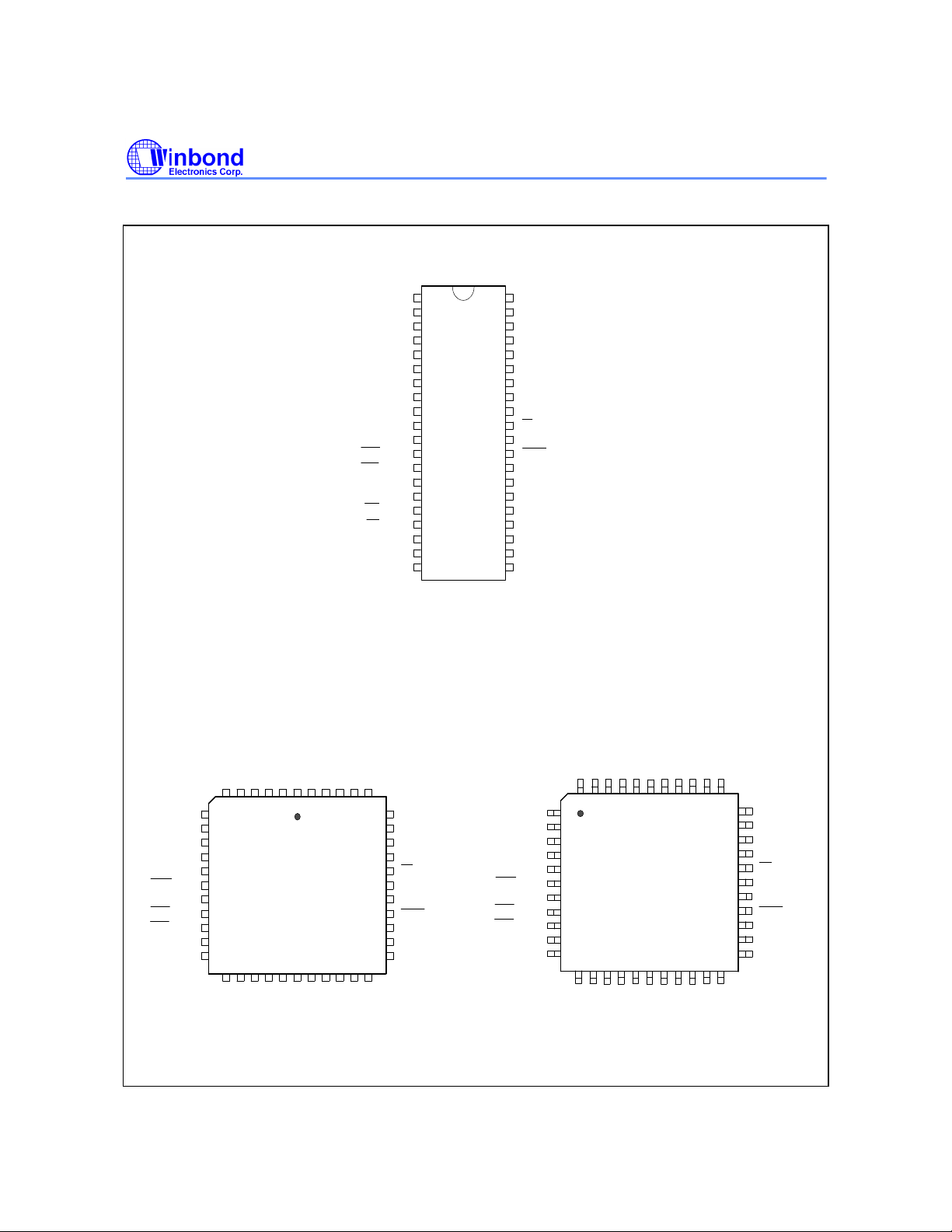

PIN CONFIGURATIONS

40-Pin DIP (W78E52B)

T2, P1.0

T2EX, P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RST

RXD, P3.0

TXD, P3.1

INT0, P3.2

INT1, P3.3

T0, P3.4

T1, P3.5

WR, P3.6

RD, P3.7

XTAL2

XTAL1

VSS

Preliminary W78E52B

VDD1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

P0.0, AD0

38

P0.1, AD1

37

P0.2, AD2

36

P0.3, AD3

35

P0.4, AD4

34

P0.5, AD5

33

P0.6, AD6

32

P0.7, AD7

31

EA

30

ALE

29

PSEN

28

P2.7, A15

27

P2.6, A14

26

P2.5, A13

25

P2.4, A12

24

P2.3, A11

23

P2.2, A10

22

P2.1, A9

21

P2.0, A8

44-Pin PLCC (W78E52BP)

/

T

I

2

N

T

E

T

2

X

3

,

,

,

P

P

P

P

P1.5

P1.6

P1.7

RST

RXD, P3.0

INT2, P4.3

TXD, P3.1

INT0, P3.2

INT1, P3.3

T0, P3.4

T1, P3.5

P

1

1

.

.

3

4

6 5 4 3

7

8

9

10

11

12

13

14

15

16

17

P

P

3

3

.

.

7

6

,

,

/

/

R

W

D

R

1

1

.

.

2

1

X

X

T

T

A

A

L

L

1

2

P

1

4

.

.

0

2

2 1 44 43 42

V

P

S

4

S

.

0

44-Pin QFP (W78E52BF)

/

T

I

2

A

A

A

A

D

D

D

D

3

2

1

0

,

,

,

,

P

P

P

P

V

D

D

P

2

.

0

,

A

8

0

0

0

0

.

.

.

.

3

1

2

0

40

41

P

P

P

2

2

2

.

.

.

3

2

1

,

,

,

A

A

A

1

1

9

1

0

P0.4, AD4

39

38

P0.5, AD5

37

P0.6, AD6

36

P0.7, AD7

35

EA

34

P4.1

33

ALE

32

PSEN

31

P2.7, A15

30

P2.6, A14

29

P2.5, A13

2827262524232221201918

P

2

.

4

,

A

1

2

P1.5

P1.6

P1.7

RST

RXD, P3.0

INT2, P4.3

TXD, P3.1

INT0, P3.2

INT1, P3.3

T0, P3.4

T1, P3.5

1

2

3

4

5

6

7

8

9

10

11

P

1

.

4

12

P

3

.

6

,

/

W

R

P

1

.

3

43 4241

P

3

.

7

,

/

R

D

E

X

,

P

P

1

1

.

.

2

1

X

X

T

T

A

A

L

L

1

2

N

T

T

2

3

,

,

P

P

1

V

4

.

D

.

0

D

2

40 39 38 37 36

V

P

P

S

2

4

S

.

.

0

0

,

A

8

A

A

A

A

D

D

D

D

3

2

1

0

,

,

,

,

P

P

P

P

0

0

0

0

.

.

.

.

3

1

2

0

34

3544

P

P

P

2

2

2

.

.

.

3

1

2

,

,

,

A

A

A

1

1

9

1

0

P0.4, AD4

33

32

P0.5, AD5

31

P0.6, AD6

30

P0.7, AD7

29

EA

28

P4.1

27

ALE

26

PSEN

25

P2.7, A15

24

P2.6, A14

23

P2.5, A13

22212019181716151413

P

2

.

4

,

A

1

2

- 2 -

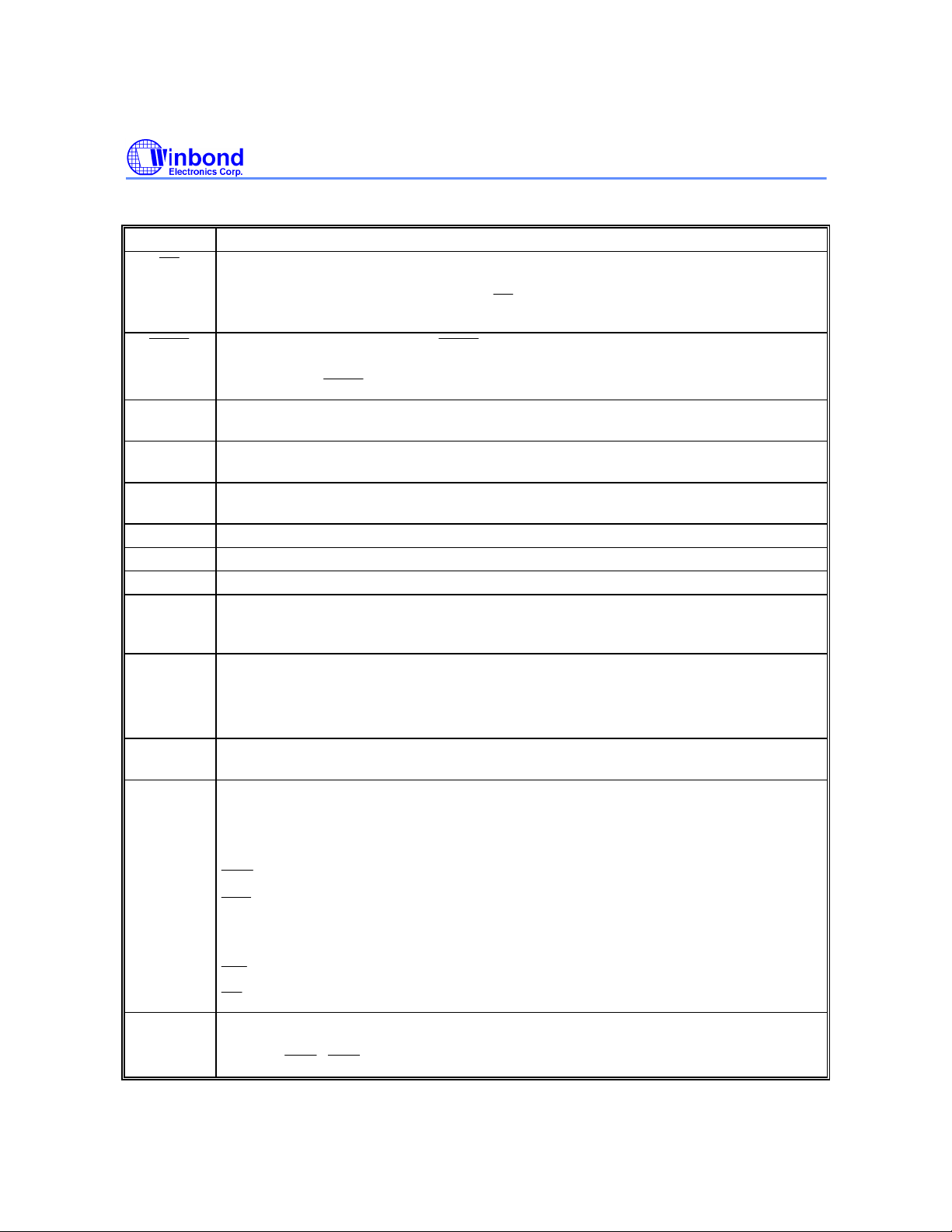

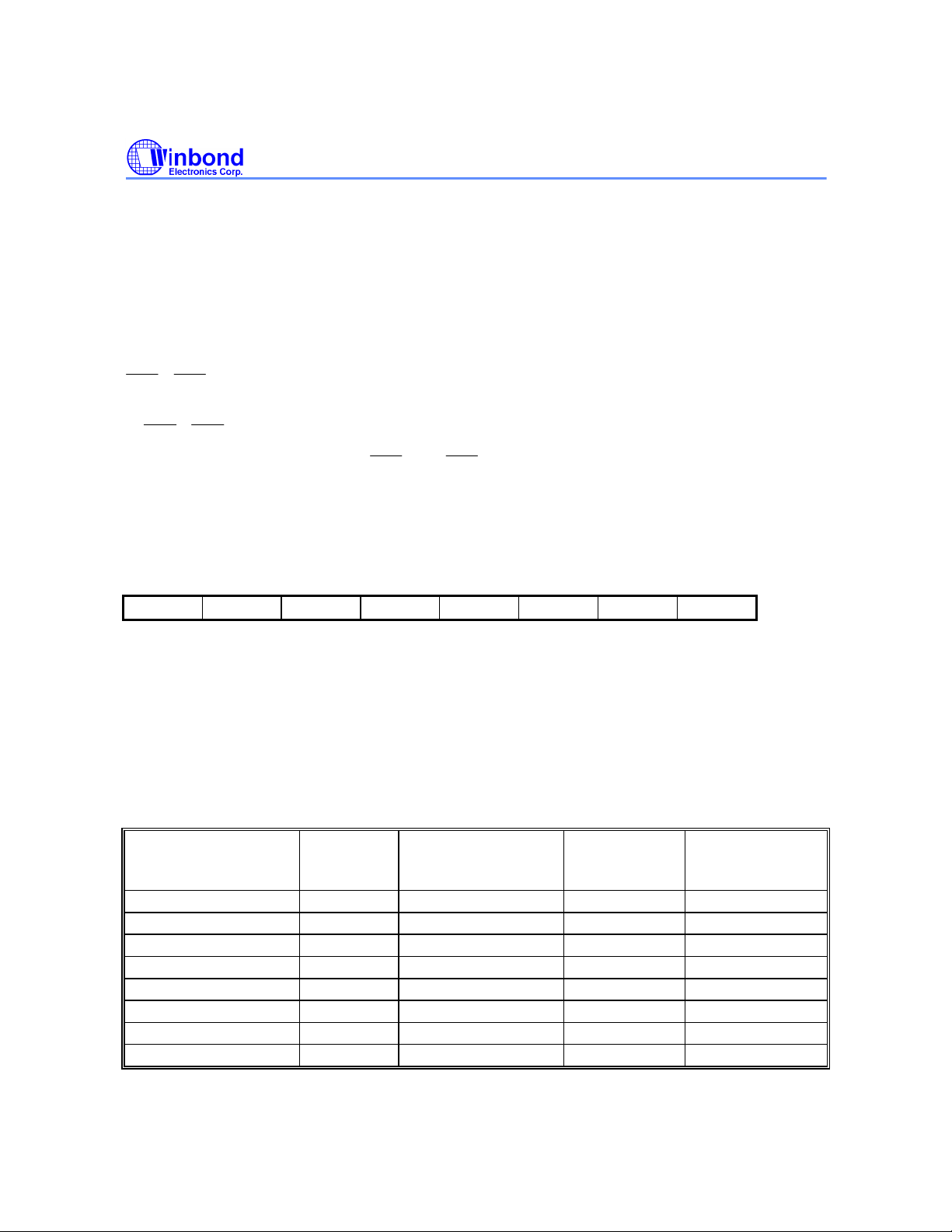

PIN DESCRIPTION

EA

PSEN

PSEN

PSEN

INT1

WR

RD

INT2

SYMBOL DESCRIPTIONS

EXTERNAL ACCESS ENABLE: This pin forces the processor to execute out of

external ROM. It should be kept high to access internal ROM. The ROM address and

data will not be presented on the bus if EA pin is high and the program counter is

within on-chip ROM area.

Preliminary W78E52B

ALE

RST

XTAL1

XTAL2

VSS

VDD

P0.0−P0.7

P1.0−P1.7

P2.0−P2.7

P3.0−P3.7

PROGRAM STORE ENABLE:

address/ data bus during fetch and MOVC operations. When internal ROM access is

performed, no

ADDRESS LATCH ENABLE: ALE is used to enable the address latch that separates

the address from the data on Port 0.

RESET: A high on this pin for two machine cycles while the oscillator is running resets

the device.

CRYSTAL1: This is the crystal oscillator input. This pin may be driven by an external

clock.

CRYSTAL2: This is the crystal oscillator output. It is the inversion of XTAL1.

GROUND: Ground potential

POWER SUPPLY: Supply voltage for operation.

PORT 0: Port 0 is a bi-directional I/O port which also provides a multiplexed low order

address/data bus during accesses to external memory. The pins of Port 0 can be

individually configured to open-drain or standard port with internal pull-ups.

PORT 1: Port 1 is a bi-directional I/O port with internal pull-ups. The bits have alternate

functions which are described below:

T2(P1.0): Timer/Counter 2 external count input

T2EX(P1.1): Timer/Counter 2 Reload/Capture control

PORT 2: Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides

the upper address bits for accesses to external memory.

PORT 3: Port 3 is a bi-directional I/O port with internal pull-ups. All bits have alternate

functions, which are described below:

RXD(P3.0) : Serial Port receiver input

TXD(P3.1) : Serial Port transmitter output

INT0 (P3.2) : External Interrupt 0

strobe signal outputs from this pin.

enables the external ROM data onto the Port 0

P4.0-P4.3

(P3.3) : External Interrupt 1

T0(P3.4) : Timer 0 External Input

T1(P3.5) : Timer 1 External Input

(P3.6) : External Data Memory Write Strobe

(P3.7) : External Data Memory Read Strobe

PORT 4: Another bit-addressable bidirectional I/O port P4. P4.3 and P4.2 are

alternative function pins. It can be used as general I/O port or external interrupt input

sources (

/INT3).

Publication Release Date: December 1998

- 3 - Revision A1

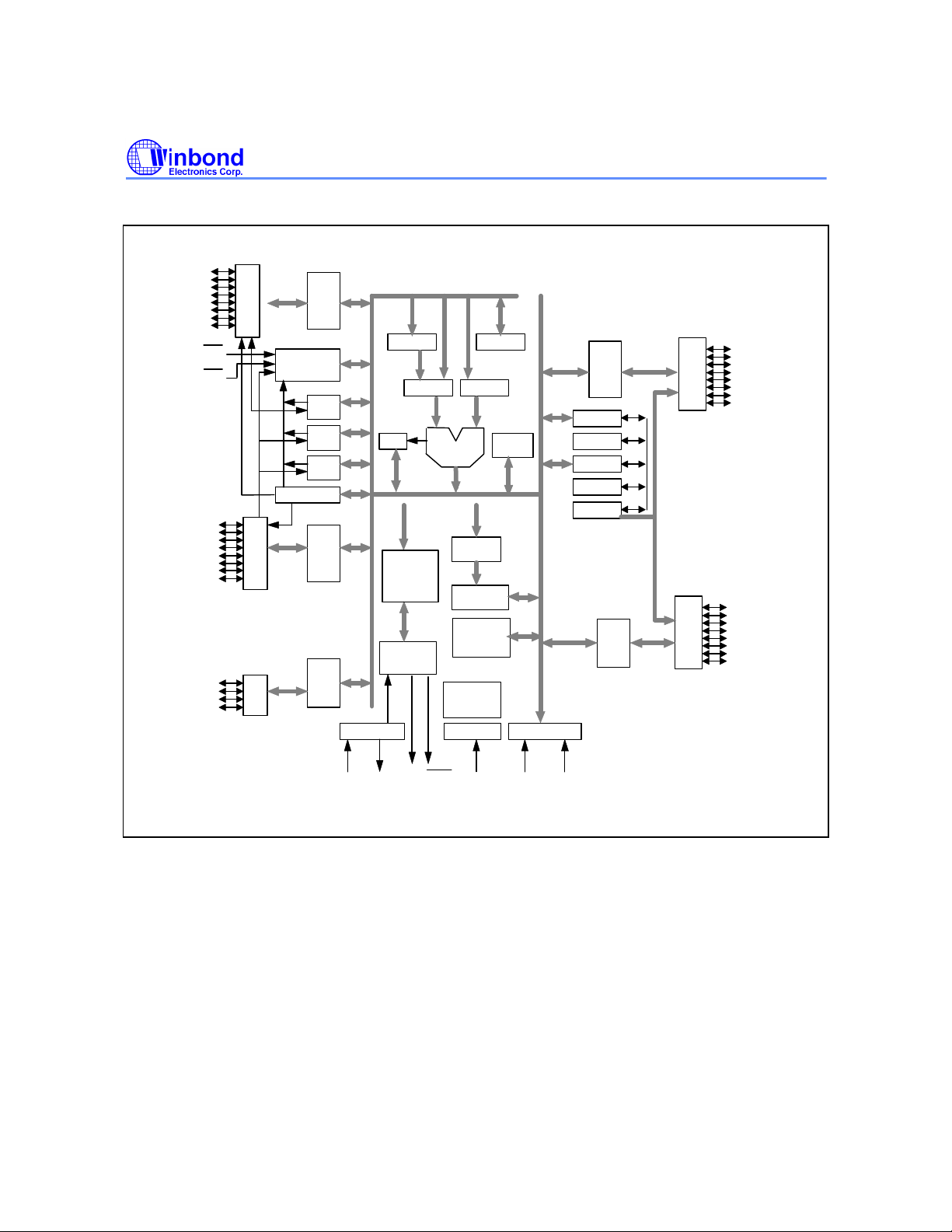

BLOCK DIAGRAM

Preliminary W78E52B

P1.0

~

P1.7

P3.0

~

P3.7

P4.0

~

P4.3

INT2

INT3

Port

1

Port

Port

Port 1

Latch

ACC

Interrupt

PSW

Instruction

Decoder

&

Sequencer

Bus & Clock

Controller

T1

ALU

Reset Block

Timer

2

Timer

0

Timer

1

UART

3

4

Port 3

Latch

Port 4

Latch

Oscillator

T2

SFR RAM

Address

256 bytes

RAM & SFR

ROM

Watchdog

Timer

B

Stack

Pointer

Power control

Port 0

Latch

DPTR

Temp Reg.

PC

Incrementor

Addr. Reg.

Port 2

Latch

Port

Port

2

P0.0

0

~

P0.7

P2.0

~

P2.7

XTAL1

XTAL2

PSENALE

RST

Vcc

Vss

FUNCTIONAL DESCRIPTION

The W78E52B architecture consists of a core controller surrounded by various registers, five general

purpose I/O ports, 256 bytes of RAM, three timer/counters, and a serial port. The processor supports

111 different opcodes and references both a 64K program address space and a 64K data storage

space.

Timers 0, 1, and 2

Timers 0, 1, and 2 each consist of two 8-bit data registers. These are called TL0 and TH0 for Timer 0,

TL1 and TH1 for Timer 1, and TL2 and TH2 for Timer 2. The TCON and TMOD registers provide

control functions for timers 0 and 1. The T2CON register provides control functions for Timer 2.

RCAP2H and RCAP2L are used as reload/capture registers for Timer 2.

- 4 -

Preliminary W78E52B

INT2

INT2

INT2

The operations of Timer 0 and Timer 1 are the same as in the W78C51. Timer 2 is a special feature

of the W78E54B: it is a 16-bit timer/counter that is configured and controlled by the T2CON register.

Like Timers 0 and 1, Timer 2 can operate as either an external event counter or as an internal timer,

depending on the setting of bit C/T2 in T2CON. Timer 2 has three operating modes: capture, autoreload, and baud rate generator. The clock speed at capture or auto-reload mode is the same as that

of Timers 0 and 1.

New Defined Peripheral

In order to be more suitable for I/O, an extra 4-bit bit-addressable port P4 and two external interrupt

, INT3 has been added to either the PLCC or QFP 44 pin package. And description follows:

1.

Two additional external interrupts,

interrupt 0 and 1 in the standard 80C52. The functions/status of these interrupts are

determined/shown by the bits in the XICON (External Interrupt Control) register. The XICON register

is bit-addressable but is not a standard register in the standard 80C52. Its address is at 0C0H. To

set/clear bits in the XICON register, one can use the "SETB (/CLR) bit" instruction. For example,

"SETB 0C2H" sets the EX2 bit of XICON.

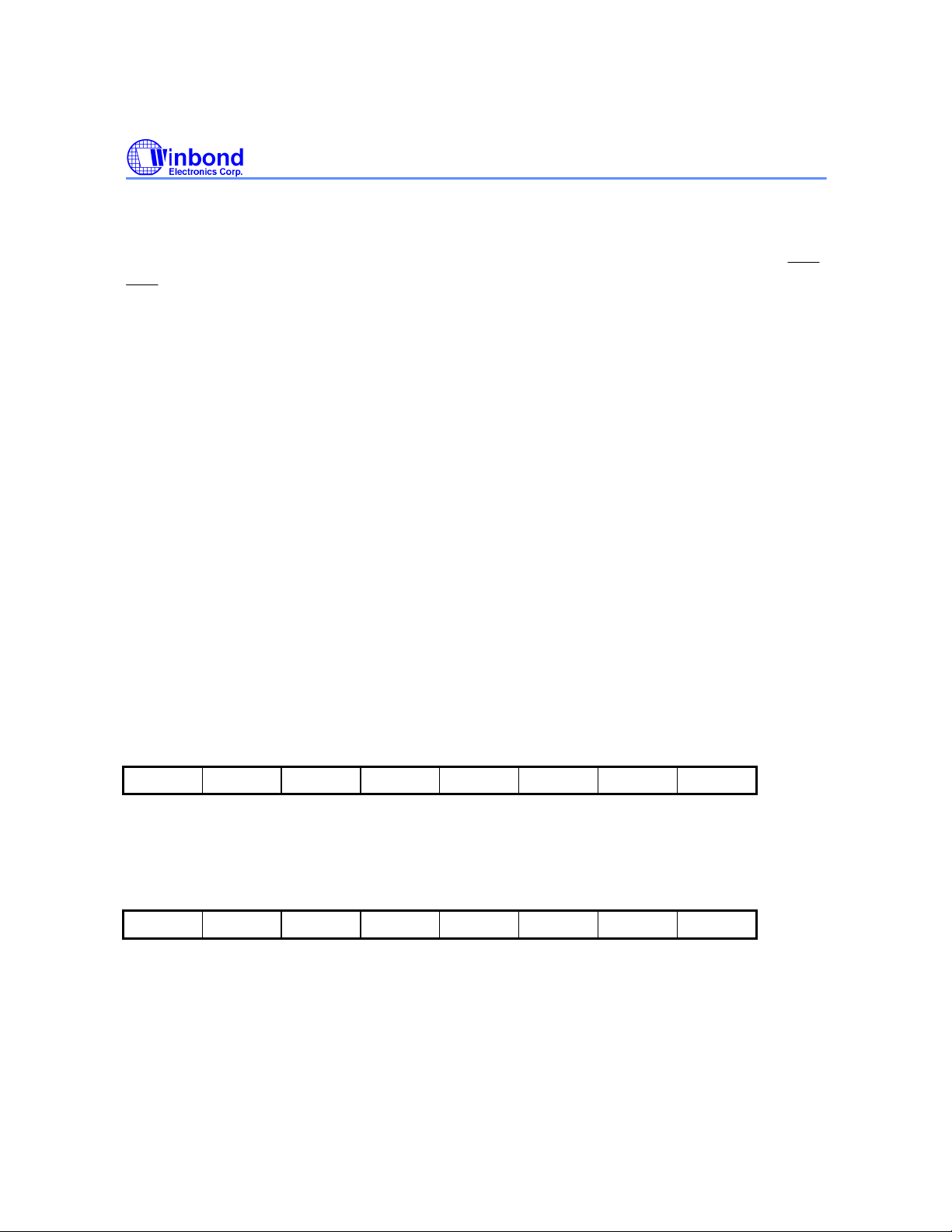

XICON - external interrupt control (C0H)

PX3: External interrupt 3 priority high if set

EX3: External interrupt 3 enable if set

IE3: If IT3 = 1, IE3 is set/cleared automatically by hardware when interrupt is detected/serviced

IT3: External interrupt 3 is falling-edge/low-level triggered when this bit is set/cleared by software

PX2: External interrupt 2 priority high if set

EX2: External interrupt 2 enable if set

IE2: If IT2 = 1, IE2 is set/cleared automatically by hardware when interrupt is detected/serviced

IT2: External interrupt 2 is falling-edge/low-level triggered when this bit is set/cleared by software

Eight-source interrupt informations:

External Interrupt 0 03H 0 (highest) IE.0 TCON.0

Timer/Counter 0 0BH 1 IE.1 External Interrupt 1 13H 2 IE.2 TCON.2

Timer/Counter 1 1BH 3 IE.3 Serial Port 23H 4 IE.4 Timer/Counter 2 2BH 5 IE.5 External Interrupt 2 33H 6 XICON.2 XICON.0

External Interrupt 3 3BH 7 (lowest) XICON.6 XICON.3

/ INT3

and INT3 , whose functions are similar to those of external

PX3 EX3 IE3 IT3 PX2 EX2 IE2 IT2

INTERRUPT

SOURCE

VECTOR

ADDRESS

POLLING

SEQUENCE WITHIN

PRIORITY LEVEL

ENABLE

REQUIRED

SETTINGS

INTERRUPT

EDGE/LEVEL

TYPE

Publication Release Date: December 1998

- 5 - Revision A1

Preliminary W78E52B

INT2

2. PORT4

Another bit-addressable port P4 is also available and only 4 bits (P4<3:0>) can be used. This port

address is located at 0D8H with the same function as that of port P1, except the P4.3 and P4.2 are

alternative function pins. It can be used as general I/O pins or external interrupt input sources (

INT3 ).

Example:

P4 REG 0D8H

MOV P4, #0AH ; Output data "A" through P4.0−P4.3.

MOV A, P4 ; Read P4 status to Accumulator.

SETB P4.0 ; Set bit P4.0

CLR P4.1 ; Clear bit P4.1

3. Reduce EMI Emission

Because of on-chip MTP-ROM, when a program is running in internal ROM space, the ALE will be

unused. The transition of ALE will cause noise, so it can be turned off to reduce the EMI emission if it

is useless. Turning off the ALE signal transition only requires setting the bit 0 of the AUXR SFR,

which is located at 08Eh. When ALE is turned off, it will be reactivated when the program accesses

external ROM/RAM data or jumps to execute an external ROM code. The ALE signal will turn off

again after it has been completely accessed or the program returns to internal ROM code space. The

AO bit in the AUXR register, when set, disables the ALE output. In order to reduce EMI emission from

oscillation circuitry, W78E52B allows user to diminish the gain of on-chip oscillator amplifiers by using

programmer to clear the B7 bit of security register. Once B7 is set to 0, a half of gain will be

decreased. Care must be taken if user attempts to diminish the gain of oscillator amplifier, reducing a

half of gain may affect the external crystal operating improperly at high frequency above 24MHz. The

value of R and C1,C2 may need some adjustment while running at lower gain.

,

***AUXR - Auxiliary register (8EH)

- - - - - - - AO

AO: Turn off ALE output.

4. Power-off Flag

***PCON - Power control (87H)

- -

POF: Power off flag. Bit is set by hardware when power on reset. It can be cleared by software

to determine chip reset is a warm boot or cold boot.

GF1, GF0: These two bits are general-purpose flag bits for the user.

PD: Power down mode bit. Set it to enter power down mode.

IDL: Idle mode bit. Set it to enter idle mode.

-

POF

GF1 GF0 PD IDL

- 6 -

Preliminary W78E52B

The power-off flag is located at PCON.4. This bit is set when VDD has been applied to the part. It can

be used to determine if a reset is a warm boot or a cold boot if it is subsequently reset by software.

Watchdog Timer

The Watchdog timer is a free-running timer which can be programmed by the user to serve as a

system monitor, a time-base generator or an event timer. It is basically a set of dividers that divide

the system clock. The divider output is selectable and determines the time-out interval. When the

time-out occurs a system reset can also be caused if it is enabled. The main use of the Watchdog

timer is as a system monitor. This is important in real-time control applications. In case of power

glitches or electro-magnetic interference, the processor may begin to execute errant code. If this is

left unchecked the entire system may crash. The watchdog time-out selection will result in different

time-out values depending on the clock speed. The Watchdog timer will de disabled on reset. In

general, software should restart the Watchdog timer to put it into a known state. The control bits that

support the Watchdog timer are discussed below.

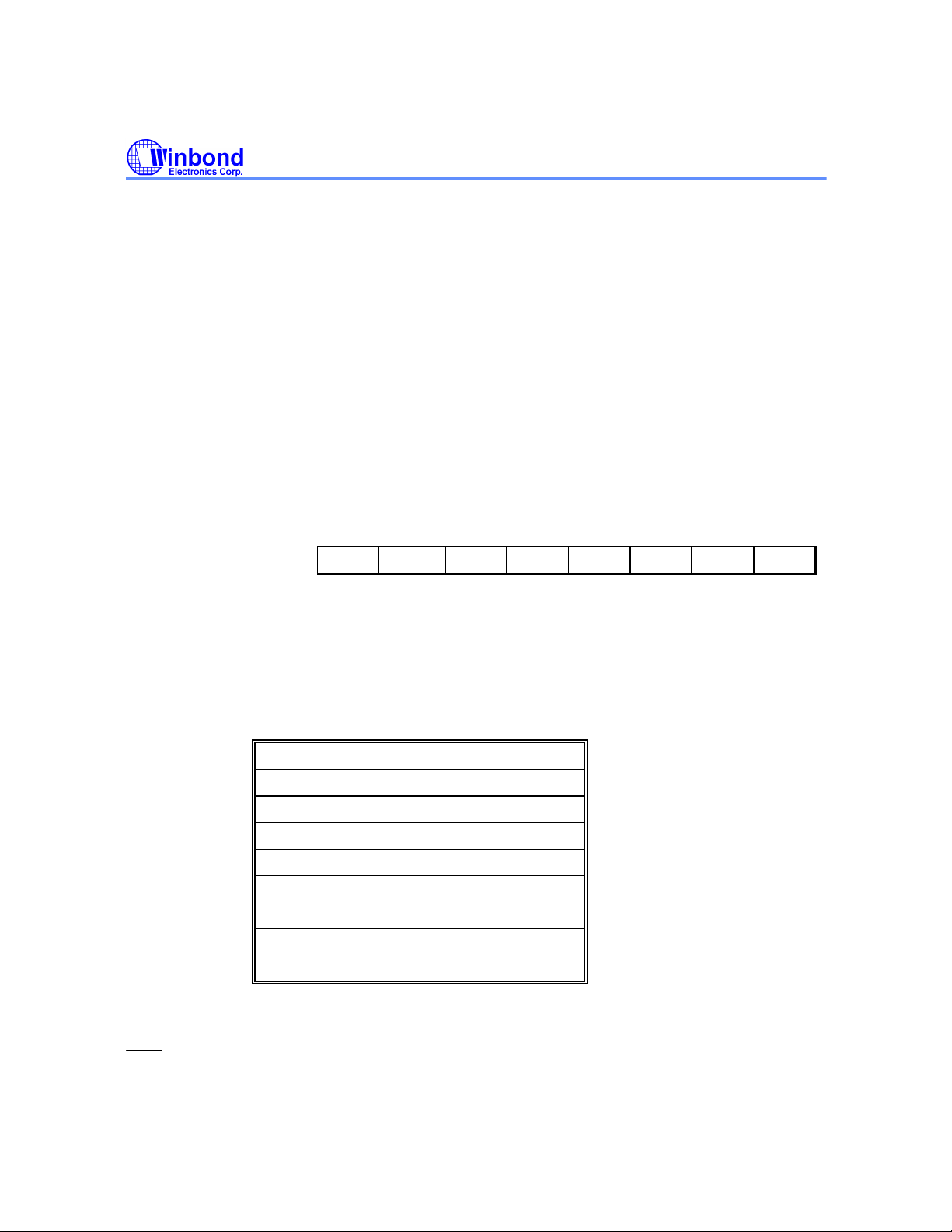

Watchdog Timer Control Register

Bit: 7 6 5 4 3 2 1 0

ENW CLRW WIDL - - PS2 PS1 PS0

Mnemonic: WDTC Address: 8FH

ENW : Enable watch-dog if set.

CLRW : Clear watch-dog timer and prescaler if set. This flag will be cleared automatically

WIDL : If this bit is set, watch-dog is enabled under IDLE mode. If cleared, watch-dog is disabled

under IDLE mode. Default is cleared.

PS2, PS1, PS0 : Watch-dog prescaler timer select. Prescaler is selected when set PS2~0 as follows:

PS2 PS1 PS0 PRESCALER SELECT

0 0 0 2

0 1 0 4

0 0 1 8

0 1 1 16

1 0 0 32

1 0 1 64

1 1 0 128

1 1 1 256

The time-out period is obtained using the following equation:

1

14

2 PRESCALER 1000 12 mS

× × × ×

OSC

Publication Release Date: December 1998

- 7 - Revision A1

Loading...

Loading...