Page 1

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 1

W90P710 Programming Guide

Revision 2.1

01/06/2006

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 2

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 2

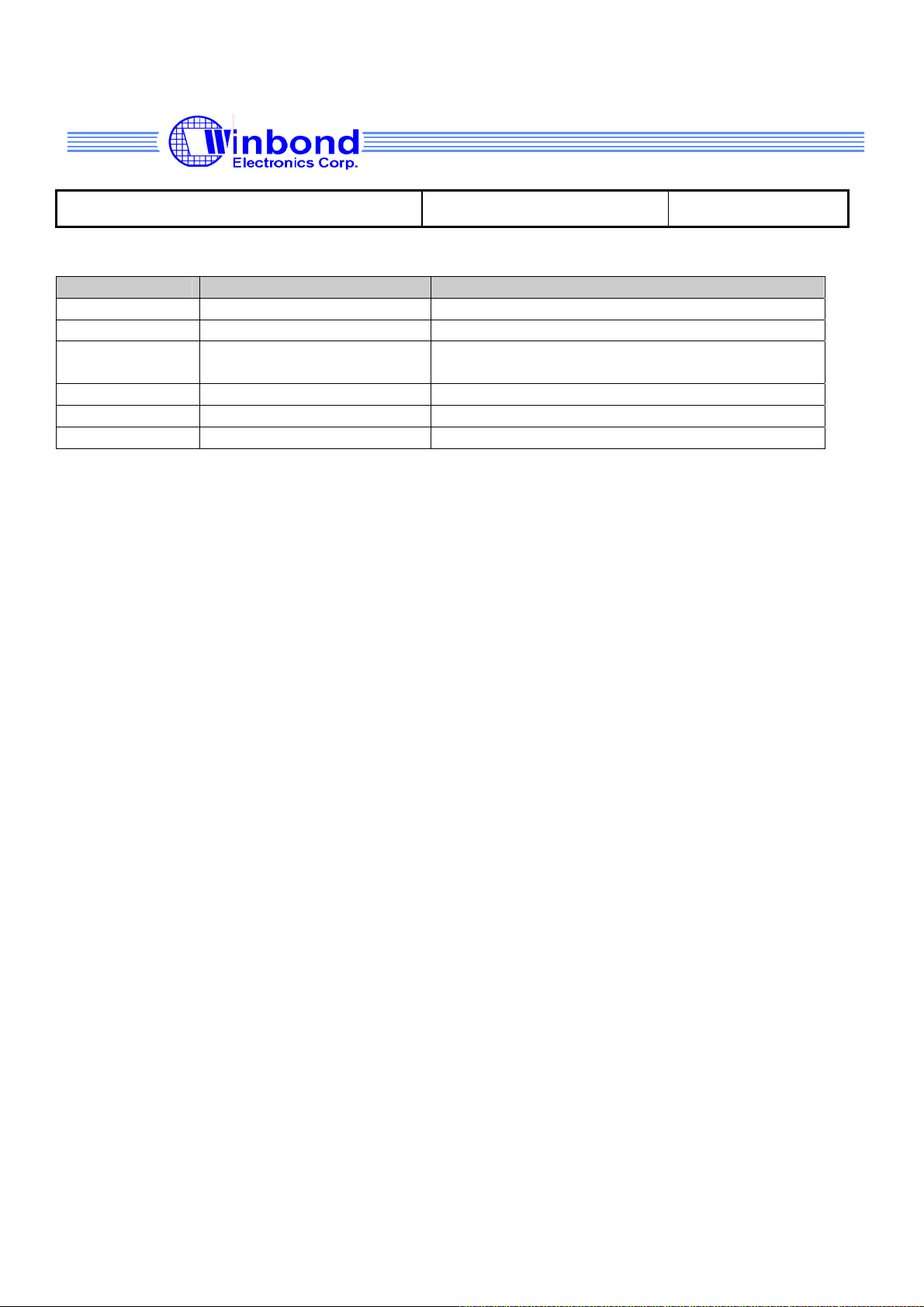

Revision History

Revision Date Comment

1.0 08/30/2005 Initial Version for W90P710

2.0 Major Revision

2.1 01/06/2006 Modify some contents and re-order the

sections

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 3

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 3

Table of Contents

1 Overview...................................................................................................................................... 15

1.1 Features ............................................................................................................................... 18

1.1.1 Architecture ................................................................................................................... 18

1.1.2 External Bus Interface ................................................................................................... 18

1.1.3 Instruction and Data Cache ........................................................................................... 18

1.1.4 Ethernet MAC Controller................................................................................................ 18

1.1.5 DMA Controller .............................................................................................................. 19

1.1.6 USB Host Controller ...................................................................................................... 19

1.1.7 USB Device Controller................................................................................................... 19

1.1.8 SDIO Host Controller..................................................................................................... 19

1.1.9 LCD Controller............................................................................................................... 20

1.1.10 2 Channel AC97/I2S Audio Codec Host Interface ......................................................... 21

1.1.11 UART............................................................................................................................. 21

1.1.12 Timers............................................................................................................................ 21

1.1.13 Advanced Interrupt Controller........................................................................................ 21

1.1.14 GPIO ............................................................................................................................. 22

1.1.15 Real Time Clock ............................................................................................................ 22

1.1.16 Smart Card Host Interface ............................................................................................. 22

1.1.17 I2C Master ..................................................................................................................... 23

1.1.18 Universal Serial Interface (USI) ..................................................................................... 23

1.1.19 4-Channel PWM ............................................................................................................ 23

1.1.20 Keypad Interface ........................................................................................................... 24

1.1.21 PS2 Host Interface Controller........................................................................................ 24

1.1.22 Power Management ...................................................................................................... 24

2 EBI (External Bus Interface) ........................................................................................................ 25

2.1 Overview............................................................................................................................... 25

2.2 Block Diagram ...................................................................................................................... 26

2.2.1 SDRAM interface........................................................................................................... 26

2.3 Registers .............................................................................................................................. 27

2.4 Functional Descriptions ........................................................................................................ 27

2.4.1 EBI Control Register (EBICON)..................................................................................... 27

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 4

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 4

2.4.2 ROM/Flash control register............................................................................................ 28

2.4.3 SDRAM configuration registers ..................................................................................... 29

2.4.4 External I/O control registers ......................................................................................... 30

2.4.5 A system memory initialization example flow chart........................................................ 30

2.4.6 REMAPPING ................................................................................................................. 32

3 Cache Controller.......................................................................................................................... 35

3.1 Overview............................................................................................................................... 35

3.2 Block Diagram ...................................................................................................................... 36

3.3 Registers .............................................................................................................................. 38

3.4 Functional Descriptions ........................................................................................................ 38

3.4.1 On-Chip RAM ................................................................................................................ 38

3.4.2 Non-Cacheable Area ..................................................................................................... 39

3.4.3 Cache Flushing.............................................................................................................. 39

3.4.4 Cache Enable and Disable ............................................................................................ 39

3.4.5 Cache Load and Lock.................................................................................................... 40

3.4.6 Cache Unlock ................................................................................................................ 41

4 EMC (Ethernet MAC Controller) .................................................................................................. 42

4.1 Overview............................................................................................................................... 42

4.2 Block Diagram ...................................................................................................................... 43

4.3 Registers .............................................................................................................................. 44

4.3.1 EMC Control registers .................................................................................................. 44

4.3.2 EMC Status Registers ................................................................................................... 45

4.4 Functional Descriptions ........................................................................................................

45

4.4.1 Initialize Rx Buffer Descriptors....................................................................................... 45

4.4.2 Initialize Tx Buffer Descriptors ....................................................................................... 48

4.4.3 MII ................................................................................................................................. 50

4.4.4 Control Frames.............................................................................................................. 52

4.4.5 Packet Processing......................................................................................................... 52

5 GDMA .......................................................................................................................................... 58

5.1 Overview............................................................................................................................... 58

5.2 Block Diagram ...................................................................................................................... 59

5.3 Registers .............................................................................................................................. 60

5.4 Functional Descriptions ........................................................................................................ 60

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 5

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 5

5.4.1 GDMA Configuration ..................................................................................................... 60

5.4.2 Transfer Count............................................................................................................... 62

5.4.3 Transfer Termination ..................................................................................................... 63

5.4.4 GDMA operation started by software............................................................................. 63

5.4.5 GDMA operation started by nXDREQ ........................................................................... 65

5.4.6 Fixed Address................................................................................................................ 66

5.4.7 Block Mode Transfer ..................................................................................................... 66

5.4.8 Single Mode Transfer .................................................................................................... 66

5.4.9 Demand Mode Transfer................................................................................................. 66

6 USB Host Controller..................................................................................................................... 68

6.1 Overview............................................................................................................................... 68

6.2 Registers Map....................................................................................................................... 69

6.3 Block Diagram ...................................................................................................................... 70

6.4 Data Structures..................................................................................................................... 71

6.4.1 Endpoint Descriptor (ED) Lists ...................................................................................... 72

6.4.2 Transfer Descriptor........................................................................................................ 73

6.4.3 Host Controller Communication Area ............................................................................ 75

6.5 Programming Note................................................................................................................76

6.5.1 Initialization.................................................................................................................... 76

6.5.2 USB States .................................................................................................................... 77

6.5.3 Add/Remove Endpoint Descriptors................................................................................ 78

6.5.4 Add/Remove Transfer Descriptors ................................................................................ 80

6.5.5 IRP Processing.............................................................................................................. 82

6.5.6 Interrupt Processing ...................................................................................................... 84

6.5.7 Done Queue Processing................................................................................................ 88

6.5.8 Root Hub ....................................................................................................................... 90

7 USB Device Controller ................................................................................................................. 94

7.1 Overview............................................................................................................................... 94

7.2 Block Diagram ...................................................................................................................... 95

7.3 Register Map ........................................................................................................................ 95

7.4 Functional descriptions .........................................................................................................97

7.4.1 Initialization.................................................................................................................... 97

7.4.2 Endpoint Configuration .................................................................................................. 98

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 6

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 6

7.4.3 Interrupt Service Routine............................................................................................... 98

7.4.4 Endpoint 0 Operation..................................................................................................... 99

7.4.5 Get Descriptor ............................................................................................................. 100

7.4.6 Endpoint A ~ C Operation............................................................................................ 101

7.4.7 Example....................................................................................................................... 102

8 SDIO Host Controller ................................................................................................................. 103

8.1 Overview............................................................................................................................. 103

8.2 Block Diagram .................................................................................................................... 103

8.3 Registers ............................................................................................................................ 104

8.4 SDIO Host Controller .......................................................................................................... 105

8.4.1 SDIO host controller Initialization Sequence................................................................ 105

8.4.2 Move data from SDRAM to SDIO host controller buffer .............................................. 106

8.4.3 Move data from SDIO host controller buffer to SDRAM .............................................. 106

8.5 SD Host Interface ............................................................................................................... 106

8.5.1 Send Command to SD/MMC Card .............................................................................. 106

8.5.2 Get Response from SD/MMC Card ............................................................................. 107

8.5.3 SD/MMC to Buffer Access ........................................................................................... 107

8.5.4 Buffer to SD/MMC Access ........................................................................................... 107

9 LCD Controller ........................................................................................................................... 108

9.1.1 Overview...................................................................................................................... 108

9.1.2 Programming Procedure.............................................................................................. 112

9.2 Initialization......................................................................................................................... 115

9.3

Configure LCD Controller ................................................................................................... 115

9.4 Configure LCD Interrupt...................................................................................................... 117

9.5 Configure LCD Timing Generation...................................................................................... 117

9.6 Configure OSD function...................................................................................................... 117

9.7 Configure TFT Palette Look-up Table................................................................................. 119

9.8 Configure Gray level dithered data duty pattern ................................................................. 120

9.9 Configure Video/ OSD scaling factor .................................................................................. 120

9.10 Configure the starting address and the stride of frame buffer and FIFO............................. 121

9.11 Configure how to show image on the panel........................................................................ 124

9.12 Enable FIFO ....................................................................................................................... 125

9.13 Enable LCD Controller........................................................................................................ 126

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 7

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 7

9.14 Check running state and process interrupt status............................................................... 126

10 Audio Controller...................................................................................................................... 128

10.1 Overview............................................................................................................................. 128

10.2 Block Diagram .................................................................................................................... 129

10.3 Registers ............................................................................................................................ 130

10.4 AC97 Interface.................................................................................................................... 130

10.4.1 Cold Reset External AC97 Codec ............................................................................... 132

10.4.2 Read AC97 Registers .................................................................................................. 132

10.4.3 Write AC97 Registers .................................................................................................. 134

10.4.4 AC97 Playback ............................................................................................................ 135

10.4.5 AC97 Record ............................................................................................................... 137

10.5 I2S Interface ....................................................................................................................... 138

10.5.1 I2S Play ....................................................................................................................... 138

10.5.2 I2S Record................................................................................................................... 140

11 UART ..................................................................................................................................... 142

11.1 Overview............................................................................................................................. 142

11.2 Registers ............................................................................................................................ 142

11.3 Functional Descriptions ...................................................................................................... 144

11.3.1 Baud Rate.................................................................................................................... 144

11.3.2 Initializations ................................................................................................................ 145

11.3.3 Polled I/O Functions .................................................................................................... 147

11.3.4

Interrupted I/O Functions ............................................................................................. 148

11.3.5 IrDA SIR ...................................................................................................................... 153

12 Timers .................................................................................................................................... 154

12.1 Overview............................................................................................................................. 154

12.2 Block Diagram .................................................................................................................... 155

12.3 Registers ............................................................................................................................ 155

12.4 Functional Descriptions ...................................................................................................... 156

12.4.1 Interrupt Frequency ..................................................................................................... 156

12.4.2 Initialization.................................................................................................................. 156

12.4.3 Timer Interrupt Service Routine................................................................................... 159

12.4.4 Watchdog Timer .......................................................................................................... 160

13 AIC (Advanced Interrupt Controller) ....................................................................................... 163

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 8

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 8

13.1 Overview............................................................................................................................. 163

13.2 Block Diagram .................................................................................................................... 164

13.3 Registers ............................................................................................................................ 165

13.4 Functional Descriptions ...................................................................................................... 167

13.4.1 Interrupt channel configuration .................................................................................... 167

13.4.2 Interrupt Masking ......................................................................................................... 167

13.4.3 Interrupt Clearing and Setting...................................................................................... 168

13.4.4 Software Priority Scheme ............................................................................................ 168

13.4.5 Hardware Priority Scheme........................................................................................... 171

14 General-Purpose Input/Output (GPIO) ................................................................................... 174

14.1 Overview............................................................................................................................. 174

14.2 Register Map ...................................................................................................................... 176

14.3 Functional Description ........................................................................................................ 177

14.3.1 Multiple Functin Setting ............................................................................................... 177

14.3.2 GPIO Output Mode ...................................................................................................... 178

14.3.3 GPIO Input Mode......................................................................................................... 179

15 Real Time Clock (RTC) .......................................................................................................... 181

15.1 Overview............................................................................................................................. 181

15.2 Block Diagram .................................................................................................................... 182

15.3 Register Map ...................................................................................................................... 182

15.4 Functional Description ........................................................................................................ 183

15.4.1 Initialization.................................................................................................................. 183

15.4.2 RTC Read/Write Enable .............................................................................................. 183

15.4.3 Frequency Compensation............................................................................................ 183

15.4.4 Application Note .......................................................................................................... 184

15.5 Programming Note.............................................................................................................. 185

15.5.2 Set Calendar and Time Alarm ..................................................................................... 187

15.5.3 Set tick interrupt........................................................................................................... 189

16 Smart Card Host Interface...................................................................................................... 191

16.1 Overview............................................................................................................................. 191

16.2 Registers ............................................................................................................................ 191

16.3 Functional Description ........................................................................................................ 193

16.3.1 Initialization Sequence................................................................................................. 193

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 9

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 9

16.3.2 Timers Usage .............................................................................................................. 194

16.3.3 Receiver FIFO Data Time-out...................................................................................... 196

16.3.4 Parity Error management............................................................................................. 197

2

17 I

C Synchronous Serial Interface Controller........................................................................... 199

17.1 Overview............................................................................................................................. 199

17.2 Block Diagram .................................................................................................................... 201

17.3 Register Map ...................................................................................................................... 201

17.4 Functional Description ........................................................................................................ 202

17.4.1 Prescale Frequency..................................................................................................... 202

17.4.2 Start and Stop Signal................................................................................................... 202

17.4.3 Slave Address Transfer ............................................................................................... 202

17.4.4 Data Transfer............................................................................................................... 203

17.4.5 Below list Some Examples of I2C Data Transaction.................................................... 203

18 Universal Serial Interface ....................................................................................................... 209

18.1 Overview............................................................................................................................. 209

18.2 Block Diagram .................................................................................................................... 210

18.3 Register Map ...................................................................................................................... 210

18.4 Functional Description ........................................................................................................ 211

18.4.1 Active Universal Serial Interface.................................................................................. 211

18.4.2 Initialize Universal Serial Interface............................................................................... 211

18.4.3 Universal Serial Interface Transmit/Receive................................................................ 212

19 Pulse Width Modulation (PWM) Timer ................................................................................... 213

19.1 Overview............................................................................................................................. 213

19.2 Block Diagram .................................................................................................................... 215

19.3 Register Map ...................................................................................................................... 215

19.4 Functional Description ........................................................................................................ 2

16

19.4.1 Prescaler and clock selector........................................................................................ 216

19.4.2 Basic PWM timer operation and double buffering reload automatically....................... 217

19.4.3 PWM Timer Start Procedure........................................................................................ 218

19.4.4 PWM Timer Stop Procedure........................................................................................ 220

20 Keypad Interface .................................................................................................................... 222

20.1 Overview............................................................................................................................. 222

20.2 Block Diagram .................................................................................................................... 223

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 10

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 10

20.3 Register Map ...................................................................................................................... 223

20.4 Functional Description ........................................................................................................ 223

20.4.1 KPI Interface Programming Flow................................................................................. 224

20.4.2 KPI Low Power Mode Configuration ............................................................................ 225

21 PS/2 Host Interface Controller................................................................................................ 227

21.1 Overview............................................................................................................................. 227

21.2 Scan Code Set.................................................................................................................... 227

21.3 Register Map ...................................................................................................................... 229

21.4 Functional Description ........................................................................................................ 229

21.4.1 Initialization.................................................................................................................. 229

21.4.2 Send Commands ......................................................................................................... 230

21.4.3 Read scan code and ASCII code................................................................................. 231

21.4.4 Interrupt Service Routine ............................................................................................. 232

21.4.5 Example....................................................................................................................... 235

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 11

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 11

Table of Figures

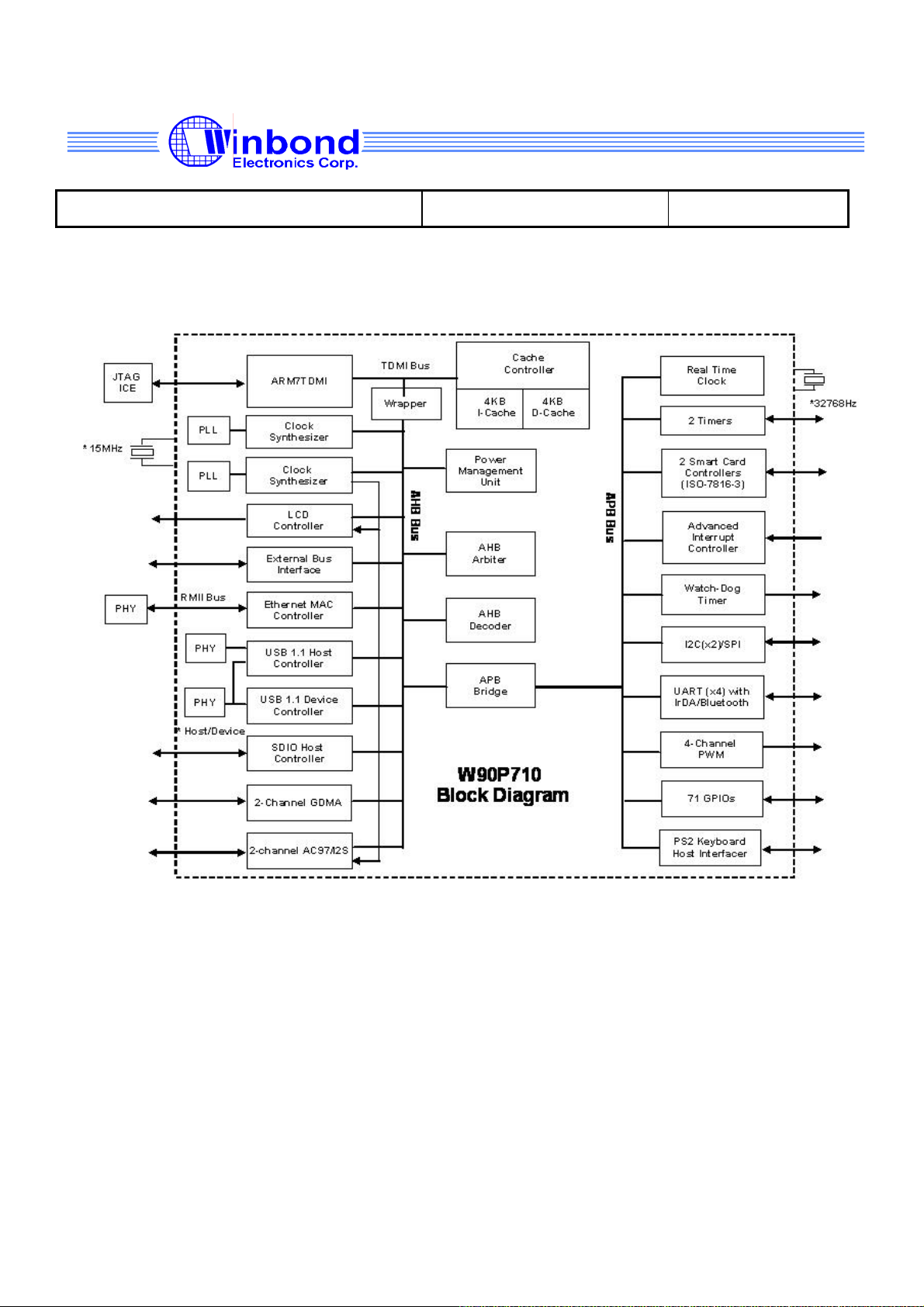

Figure 1-1 W90P710 Functional Block Diagram ................................................................................ 16

Figure 2-1 SDRAM Interface............................................................................................................... 26

Figure 2-2 System Memory Map Setting Flow .................................................................................... 30

Figure 3-1 Instruction Cache Organization Block Diagram ................................................................. 36

Figure 3-2 Data Cache Organization Block Diagram .......................................................................... 37

Figure 3-3 Cache Load and Lock........................................................................................................ 40

Figure 4-1 EMC Block Diagram .......................................................................................................... 43

Figure 4-2 Rx Descriptor Initialization ................................................................................................. 47

Figure 4-3 Tx Descriptor Initialization.................................................................................................. 49

Figure 4-4 Packet Transmission Flow................................................................................................. 53

Figure 4-5 Tx Interrupt Service Routine Flow...................................................................................... 55

Figure 4-6 Rx Interrupt Service Routine.............................................................................................. 57

Figure 5-1 GDMA Block Diagram........................................................................................................ 59

Figure 5-2 The bit-fields of the GDMA control register........................................................................ 61

Figure 5-3 GDMA operations .............................................................................................................. 62

Figure 5-4 Software GDMA Transfer................................................................................................... 64

Figure 6-1 Endpoint Descriptor Format............................................................................................... 72

Figure 6-2 General Transfer Descriptor Format .................................................................................. 74

Figure 6-3 Isochronous Transfer Descriptor Format ........................................................................... 74

Figure 6-4 Remove an Endpoint Descriptor ........................................................................................79

Figure 6-5 ED list and TD queue......................................................................................................... 80

Figure 7-1 USBD Controller Block Diagram ........................................................................................95

Figure 10-2 USBD Controller Block Diagram...................................................................................... 99

Figure 8-1 SDIO Host Block Diagram ............................................................................................... 103

Figure 9-1 LCD Controller Block Diagram......................................................................................... 108

Figure 9-2 Overall programming flow for LCD controller - 1.............................................................. 112

Figure 9-3 Overall programming flow for LCD controller - 2.............................................................. 114

Figure 9-4 The relationship between screen, valid window, and OSD window ................................. 117

Figure 9-5 An example to explain how to program the starting address and stride........................... 122

Figure 10-1 Block diagram of Audio Controlle................................................................................... 129

Figure 10-2 AC97 Playback Data in DMA Buffer .............................................................................. 135

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 12

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 12

Figure 10-3 AC97 Data in Record DMA buffer.................................................................................. 137

Figure 10-4 I2S Play Data in DMA buffer.......................................................................................... 139

Figure 10-5 I2S Record Data in DMA buffer ..................................................................................... 140

Figure 11-1 UART initialization ......................................................................................................... 145

Figure 11-2 Transmit data in polling mode........................................................................................ 147

Figure 11-3 Receive data in polling mode......................................................................................... 148

Figure 11-4 Output function in interrupt mode................................................................................... 149

Figure 11-5 Input functions in interrupt mode.................................................................................... 150

Figure 11-6 Interrupt Service Routine ............................................................................................... 152

Figure 11-7 IrDA Tx/Rx ..................................................................................................................... 153

Figure 12-1 Timer Block Diagram ..................................................................................................... 155

Figure 12-2 Timer Initialization Sequence......................................................................................... 158

Figure 12-3 Timer Interrupt Service Routine ..................................................................................... 159

Figure 12-4 Enable Watchdog Timer ................................................................................................ 161

Figure 12-5 Watchdog Timer ISR ..................................................................................................... 162

Figure 13-1 AIC block diagram ......................................................................................................... 164

Figure 13-2 Source Control Register ................................................................................................ 167

Figure 13-3 Sequential Priority Scheme............................................................................................ 170

Figure 13-4 Interrupt Service Routine with Vector ............................................................................ 172

Figure 13-5 Using hardware priority scheme .................................................................................... 173

Figure 15-1 RTC Block Diagram ....................................................................................................... 182

Figure 15-2 RTC Set Calendar and Time flow chart ......................................................................... 186

Figure 15-3 RTC Set Calendar and Time Alarm flow chart ............................................................... 188

Figure 15-4 RTC Set tick interrupt flow chart .................................................................................... 189

2

Figure 17-1 I

C Block Diagram ......................................................................................................... 201

Figure 18-1 Universal Serial InterfaceI Block Diagra ........................................................................ 210

Figure 19-1 PWM Block Diagram...................................................................................................... 215

Figure 19-2 PWM operation .............................................................................................................. 218

Figure 19-3 PWM Timer Start Procedure.......................................................................................... 219

Figure 19-4 PWM Timer Stop flow chart (method 1)......................................................................... 220

Figure 19-5 PWM Timer Stop flow chart (method 2)......................................................................... 221

Figure 20-1 Keypad Controller Block Diagram.................................................................................. 223

Figure 20-2 KPI Interface flowchart................................................................................................... 225

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 13

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 13

Figure 20-3 KPI set Wake-Up in system low power mode flowchart................................................. 226

Figure 21-1 Key map of PS/2 keyboard ............................................................................................ 227

Figure 21-2 Key map of extended keyboard & Numeric keypad ....................................................... 228

Figure 21-3 Make Code and Break Code.......................................................................................... 229

Figure 21-4 Example ISR.................................................................................................................. 233

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 14

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 14

List of Tables

Table 3-1 The size and start address of On-Chip RAM ...................................................................... 38

Table 6-1 HCCA (Host Controller Communication Area) .................................................................... 75

Table 9-1 LCD Controller Register Map............................................................................................ 110

Table 9-2 Register LCDCON Bit Map ............................................................................................... 115

Table 9-3 OSD Display Condition ..................................................................................................... 118

Table 9-4 entry of the TFT Look-up table.......................................................................................... 119

Table 9-5 STN 16-leve gray number & relative Time-based dithering .............................................. 120

Table 9-6 BSWP=0, HSWP=0 .......................................................................................................... 125

Table 9-7 BSWP=0, HSWP=1 .......................................................................................................... 125

Table 9-8 BSWP=0, HSWP=0 .......................................................................................................... 125

Table 9-9 BSWP=1, HSWP=0 .......................................................................................................... 126

Table 10-1 AC97 Output Frame........................................................................................................ 131

Table 10-2 AC97 Output Frame Data Format ................................................................................... 131

Table 10-3 AC97 Input Frame........................................................................................................... 131

Table 10-4 AC97 Input Frame Data Format...................................................................................... 132

Table 11-1 General Baud Rate Settings ........................................................................................... 145

Table 12-1 Timer Reference Setting Values ..................................................................................... 156

Table 13-1 AIC Register Definition.................................................................................................... 165

Table 14-1 GPIO Multiplexed Functions Table ................................................................................. 174

Table 21-1 Command register PS2CMD........................................................................................... 230

Table 21-2 Command table............................................................................................................... 230

Table 21-3 Register PS2SCANCODE .............................................................................................. 231

Table 21-4 Register PS2ASCII ......................................................................................................... 232

Table 21-5 Register PS2ST .............................................................................................................. 232

Table 21-6 LED Status byte .............................................................................................................. 235

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 15

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 15

1 Overview

The W90P710 16/32-bit RISC micro-controller is a cost-effective, high-performance micro-controller

solution for Ethernet-based system. An integrated Ethernet controller, the W90P710, is designed for

use in managed communication hubs and routers.

The W90P710 is built around an outstanding CPU core: on the 16/32 ARM7TDMI based RISC

processor designed by Advanced RISC Machines, Ltd. The ARM7TDMI core is a low power, general-

purpose integrated circuits. Its simple, elegant, and fully static design is particularly suitable for cost-

sensitive and power-sensitive applications.

The W90P710 offers a 4K-byte I-cache/SRAM, a 4K-byte D-cache/SRAM and one MACs of

Ethernet controller that reduces total system cost. A color LCD controller is built in to support black-and-

white/gray-level/color TFT and low cost STN LCD modules. Most of the on-chip function blocks have

been designed using an HDL synthesizer and the W90P710 has been fully verified in Winbond’s state-

of-the art ASIC test environment.

The other important peripheral functions include one USB host controller, one USB device

controller, one AC97/IIS codec controller, one SD/SDIO host controller, one 2-Channel GDMA, two

smartcard host controller, four independent UARTS, one Watchdog timer, two 24-bit timers with 8-bit

pre-scale, 71 programmable I/O ports, PS/2 keyboard controller and an advance interrupt controller.

The external bus interface (EBI) controller provides for SDRAM, ROM/SRAM, flash memory and I/O

devices. The System Manager includes an internal 32-bit system bus arbiter and a PLL clock controller.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 16

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 16

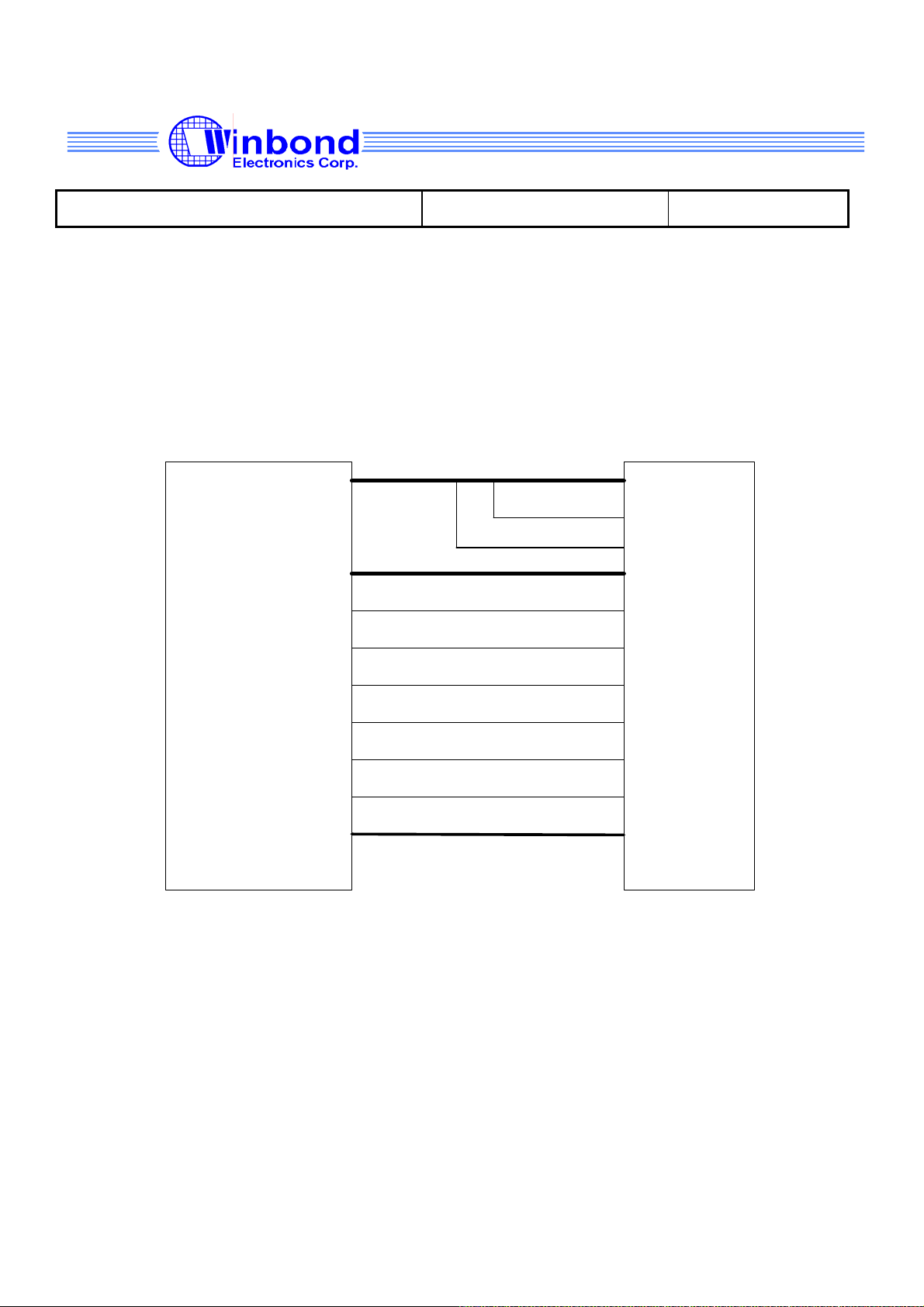

Figure 1-1 W90P710 Functional Block Diagram

On the following chapters, programming note of each chapter will be described in detailed.

• Chapter 2. External Bus Interface Controller

• Chapter 3. Cache Controller

• Chapter 4. Ethernet MAC Controller

• Chapter 5. GDMA

• Chapter 6. USB Host Controller

• Chapter 7. USB Device Controller

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 17

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 17

• Chapter 8. SDIO Host Controller

• Chapter 9. LCD Controller

• Chapter 10. Audio Controller

• Chapter 11. UART

• Chapter 12. Timers

• Chapter 13. Advance Interrupt Controller

• Chapter 14. GPIO

• Chapter 15. Real Time Clock

• Chapter 16. Smartcard Host Interface Controller

• Chapter 17. I2C Synchronous Serial Interface

• Chapter 18. Universal Serial Interface

• Chapter 19. PWM-Tmer

• Chapter 20. Keypad Interface

• Chapter 21. PS/2 Host Interface Controller

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 18

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 18

1.1 Features

1.1.1 Architecture

• Integrated system for POS (Point of Sale) and automatic data collection applications

• Fully 16/32-bit RISC architecture

• Little/Big-Endian mode supported

• Efficient and powerful ARM7TDMI core

• Cost-effective JTAG-based debug solution

1.1.2 External Bus Interface

• 8/16/32-bit external bus support for ROM/SRAM, flash memory, SDRAM and external I/Os

• Support for SDRAM

• Programmable access cycle (0-7 wait cycle)

• Four-word depth write buffer

• Cost-effective memory-to-peripheral DMA interface

1.1.3 Instruction an d Dat a Cache

• Two-way, Set-associative, 4K-byte I-cache and 4K-byte D-cache

• Support for LRU (Least Recently Used) Protocol

• Cache is configurable as an internal SRAM

• Support Cache Lock function

1.1.4 Ethernet MAC Controller

• DMA engine with burst mode

• MAC Tx/Rx buffers (256 bytes Tx, 256 bytes Rx)

• Data alignment logic

• Endian translation

• 100/10-Mbit per second operation

• Full compliance with IEEE standard 802.3

• RMII interface only

• Station Management Signaling

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 19

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 19

• On-Chip CAM (up to 16 destination addresses)

• Full-duplex mode with PAUSE feature

• Long/short packet modes

• PAD generation

1.1.5 DMA Controller

• 2-channel General DMA for memory-to-memory data transfers without CPU intervention

• Initialed by a software or external DMA request

• Increments or decrements a source or destination address in 8-bit, 16-bit or 32-bit data transfers

• 4-data burst mode

1.1.6 USB Host Controller

• USB 1.1 compliant

• Compatible with Open HCI 1.0 specification

• Supports low-speed and full speed devices

• Build-in DMA for real time data transfer

• Two on-chip USB transceivers with one optionally shared with USB Device Controller

1.1.7 USB Device Controller

• USB 1.1 compliant

• Support four USB pipes including one control pipe and 3 configurable pipes for rich USB

functions

• Support USB Mass Storage

• Support USB Virtual COM port with modem capability

• Support Full speed only

1.1.8 SDIO Host Controller

• Directly connect to Secure Digital (SD, MMC or SDIO) flash memory card

• Supports DMA function to accelerate the data transfer between the internal buffer,

external SDRAM, and flash memory card

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 20

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 20

• Two 512 bytes internal buffers are embedded inside of the controller

• No SPI mode

1.1.9 LCD Controller

• STN LCD Display

Supports Sync-type STN LCD

Supports 2 types of LCD panels: 4-bit single scan and 8-bit single scan display type

Supports 16 gray levels for Monochrome STN LCD panel

Supports 4096(12bpp) color for Color STN LCD panel

Virtual coloring method: Frame Rate Control (16-level)

Anti-flickering method: Time-based Dithering

• TFT LCD Display

Supports Sync-type TFT LCD and Sync-type High-color TFT LCD

Supports 8-bpp(RGB 332) palette color display

Supports 16-bpp(RGB 565) non-palette true color display

• TV Encoder

Supports 8-bit YCbCr data output format to connect with external TV Encoder

• LCD Prep ro ce ss ing

Image re-size

Horizontal/Vertical Down-Scaling

Horizontal/Vertical Up-Scaling

Image relocation

Horizontal /Vertical Cropping

Virtual Display

• LCD Postprocessing

Support for one OSD overlay

Support various OSD function

• Others

Color-look up table size 256x32 bit for TFT used

Dedicated DMA for block transfer mode

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 21

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 21

1.1.10 2 Channel AC97/I2S Audio Codec Host Interface

• AHB master port and an AHB slave port are offered in audio controller

• Always 8-beat incrementing burst

• Always bus lock when 8-beat incrementing burst

• When reach middle and end address of destination address, a DMA_IRQ is

requested to CPU automatically

1.1.11 UART

• Four UART (serial I/O) blocks with interrupt-based operation

• Support for 5-bit, 6-bit, 7-bit or 8-bit serial data transmit and receive

• Programmable baud rates

• 1, ½ or 2 stop bits

• Odd or even parity

• Break generation and detection

• Parity, overrun and framing error detection

• X16 clock mode

• Support for Bluetooth, IrDA and Micro-printer control

1.1.12 Timers

• Two programmable 24-bit timers with 8-bit pre-scalar

• One programmable 24-bit Watch-Dog timer

• One-short mode, period mode or toggle mode operation

1.1.13 Advanced Interrupt Controller

• 31 interrupt sources, including 4 external interrupt sources

• Programmable normal or fast interrupt mode (IRQ, FIQ)

• Programmable as either edge-triggered or level-sensitive for 4 external interrupt sources

• Programmable as either low-active or high-active for 4 external interrupt sources

• Priority methodology is encoded to allow for interrupt daisy-chaining

• Automatically mask out the lower priority interrupt during interrupt nesting

• Automatically clear the interrupt flag when the interrupt source is programmed to be edge-

triggered

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 22

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 22

1.1.14 GPIO

• 71 programmable I/O ports

• Pins individually configurable to input, output, or I/O mode for dedicated signals

• I/O ports Configurable for Multiple functions

1.1.15 Real Time Clock

• Time counter (second, minute, hour) and calendar counter (day, month, year)

• Alarm register (second, minute, hour, day, month, year)

• 12 or 24-hour mode selectable

• Recognize leap year automatically

• Day of the week counter

• Frequency compensate register (FCR)

• Beside FCR, all clock and alarm data expressed in BCD code

• Support tick time interrupt

1.1.16 Smart Card Host Interface

• ISO-7816 compliant

• PC/SC T=0, T=1 compliant

16-byte transmitter FIFO and 16-byte receiver FIFO

•

• FIFO threshold interrupt to optimize system performance

• Programmable transmission clock frequency

Versatile baud rate configuration

•

• UART-like register file structure

• Versatile 8-bit, 16-bit, 24-bit time-out counter for Ansswer To Reset (ATR) and

waiting times processing

• Parity error counter in reception mode and in transmission mode with automatic

re-transmission

• Automatic activation and deactivation sequence through an independence

sequencer

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 23

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 23

1.1.17 I2C Master

• Compatible with Philips I2C standard, support master mode only

• Support multi master operation

• Clock stretching and wait state generation

• Provide multi-byte transmit operation, up to 4 bytes can be transmitted in a single transfer

• Software programmable acknowledge bit

• Arbitration lost interrupt, with automatic transfer cancellation

• Start/Stop/Repeated Start/Acknowledge generation

• Start/Stop/Repeated Start detection

• Bus busy detection

• Supports 7 bit addressing mode

2

• Software mode I

C

1.1.18 Universal Serial Interface (USI)

• Support USI master mode only

• Full duplex synchronous serial data transfer

• Variable length of transfer word up to 32 bits

• Programmable data frame size from 4 to 16 bits

• Provide burst mode operation, transmit/receive can be executed up to four times in one transfer

• MSB or LSB first data transfer

• Rx and Tx on both rising or falling edge of serial clock independently

• 2 slave/device select lines

1.1.19 4-Channel PWM

• Four 16-bit timers

• Two 8-bit pre-scalars & Two 4-bit divider

• Programmable duty control of output waveform (PWM)

• Auto reload mode or one-shot pulse mode

• Dead zone generator

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 24

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 24

1.1.20 Keypad Interface

• Scan up to 16x8 with an external 4 to 16 decoder and 4x8 array without auxiliary component

• Programmable debounce time

• One or two keys scan with interrupt and three keys reset function.

• Support low power mode wakeup function

1.1.21 PS2 Host Interface Controller

• APB slave consisted of PS2 protocol.

• Connect IBM keyboard or bar-code reader through PS2 interface.

• Provide hardware scan code to ASCII translation

1.1.22 Power Management

• Programmable clock enables for individual peripheral

• IDLE mode to halt ARM Core and keep peripheral working

• Power-Down mode to stop all clocks included external crystal oscillator.

• Exit IDLE/Power-Down by interrupts

•

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 25

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 25

2 EBI (External Bus Interface)

2.1 Overview

W90P710 supports External Bus Interface (EBI), which controls the access to the external memory

(ROM/FLASH, SDRAM) and External I/O devices. The EBI has seven chip selects to select one

ROM/FLASH bank, two SDRAM banks, and four External I/O banks and 25-bit address bus. It supports

8-bit, 16-bit, and 32-bit external data bus width for each bank.

The EBI has the following functions :

z SDRAM controller

z EBI control register

z ROM/FLASH interface

z External I/O interface

The base addresses of SDRAM, ROM/FLASH, and External I/O are all programmable. Thus they

can be set in a specified address ranges in memory. The EBI also offer power-on setting to ensure

the system can be boot by from ROM/FLASH.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 26

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 26

2.2 Block Diagram

2.2.1 SDRAM interface

Figure 2-1 SDRAM Interface

A[21:0]

D[31:0]

MCLK

MCKE

nSCS[1:0]

nSRAS

nSCAS

nSWE

nSDQM[3:0]

W90P710

A[10:0]

A13

A14

nSCS0

nSDQM[3:0]

A[10:0]

BS0

BS1

DQ[[31:0]

CLK

CKE

nCS

nRAS

nCAS

nWE

DQM[3:0]

SDRAM

64Mb 512Kx4x32

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 27

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 27

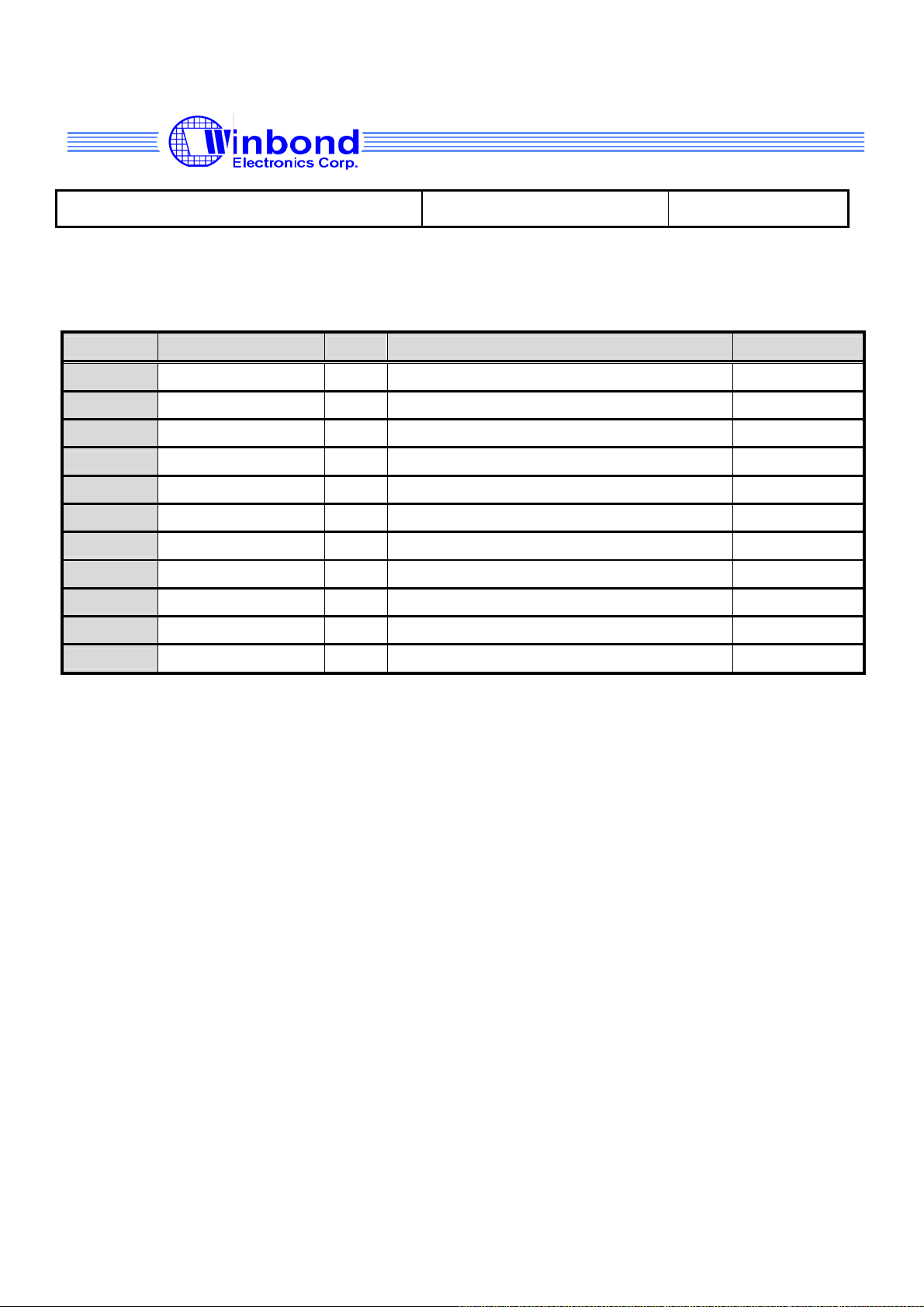

2.3 Registers

Register Address R/W Description Reset Value

EBICON 0xFFF0.1000 R/W

ROMCON 0xFFF0.1004 R/W

SDCONF0 0xFFF0.1008 R/W

SDCONF1 0xFFF0.100C R/W

SDTIME0 0xFFF0.1010 R/W

SDTIME1 0xFFF0.1014 R/W

EXT0CON 0xFFF0.1018 R/W

EXT1CON 0xFFF0.101C R/W

EXT2CON 0xFFF0.1020 R/W

EXT3CON 0xFFF0.1024 R/W

CKSKEW 0xFFF0.1F00 R/W

EBI control register

ROM/FLASH control register

SDRAM bank 0 configuration register

SDRAM bank 1 configuration register

SDRAM bank 0 timing control register

SDRAM bank 1 timing control register

External I/O 0 control register

External I/O 1 control register

External I/O 2 control register

External I/O 3 control register

Clock skew control register (for testing)

2.4 Functional Descriptions

2.4.1 EBI Control Register (E BICON)

0x0001.0000

0x0000.0XFC

0x0000.0800

0x0000.0800

0x0000.0000

0x0000.0000

0x0000.0000

0x0000.0000

0x0000.0000

0x0000.0000

0xXXXX.0038

The major function of EBICON is to control the SDRAM refreshing timing. This register can

control is used to set the refresh period, clock, and valid time of nWAIT signal. Additionally, the EBI

memory format configuration (Big, or Little Endian) can be known got by reading from the EBI control

register. The auto-refresh rate is controlled by the REFRAT , and SDRAM clock is controlled by

CLKEN.

There are two SDRAM refresh mode, auto-refresh mode and self-refresh mode. If SDRAM is

operated in auto-refresh mode, SDRAM controller refreshes SDRAM every by a period specified by

REFRAT. If SDRAM is in self-refresh mode, it is refreshed by SDRAM itself. Thus if SDRAM is

operated in self-refresh mode, the CLKEN and REFEN can be disabled to reduce save power

consumption. Another way to save reduce power consumption is just to disabling CLKEN, and

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 28

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 28

SDRAM controller still refreshed SDRAM by every each specified refresh period. In this case, SDRAM

is closed not functioning by disabling CLKEN to save for power saving, and but SDRAM controller still

refreshes it to prevent from data lost. In sum, SDRAM is operated as follows :

NORMAL MODE :

REFEN=1

REFMOD=0

CLKEN=1

REFRAT=(proper period)

POWER SAVING MODE 1 :

REFEN=1

REFMOD=0

CLKEN=1

REFRAT=(proper period)

POWER SAVING MODE 2 :

REFEN=0

REFMOD=1

CLKEN=0

REFRAT=(don’t care)

2.4.2 ROM/Flash control register

ROM/Flash control register is used to control the configuration of the boot ROM. In this register, the

size, base address, access type and access timing are specified. The base address of the boot ROM

can be set by BASADDR. Although the width of BASADDR is only 13 bits, the real start address of the

boot ROM is calculated as BASADDR << 18. Thus the range of the start address of the boot ROM is

from 0x0 to (2^13-1)*2^18. However, the system memory map should be concerned together when

setting the base address the base address setting should be checked to prevent from using

RESERVED memory address. The system memory map can be found in W90P710 spec data sheet.

After system reset, the EBI controller has uses the special power-on setting to ensure the boot

ROM to be bootable. These setting are as follows:

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 29

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 29

• The EBI controller is select to the boot ROM was selected by EBI controller after reset.

• The reset value of BASADDR of ROM/Flash control register is 0.

• The default size of the boot ROM is 256Kb256KB.

• The default value of tACC is the longest value. This value is supposed to suit support any kind of

ROM/Flash.

• The boot ROM/Flash data bus width is determined by the data bus signals D [13: 12] in power-

on setting. The external hardware has the responsibility to weak needs to do the pull-up, or pull-

down setting on the D [13: 12] according to the boot ROM/Flash types.

• PGMODE is set in normal ROM mode.

By the configurations shown above, the instruction fetch can be sure to be performed can be

fetched from the start of the boot ROM. However, if the boot ROM/Flash has more others functions, ex:

such as PGMODE, or more with larger size, the software has the responsibility to correct the setting

boot up program should configure the of ROM/Flash control register to let it work correctly after boot.

The ROM/Flash interface is designed for the boot ROM and it is supposed only to before read

operations. However, if a flash is attached to the ROM/Flash interface, it still can be written by the

writing programming command provided by of the flash. The ROM/Flash interface doesn’t hold the

writing command to the ROM/Flash. Thus the boot ROM/Flash is still programmable if the boot

ROM/Flash allows to be written. Thus, the attached Flash can be updated also by the programming

interface/sequence provided by the Flash.

2.4.3 SDRAM configuration registers

The SDRAM configuration registers enable software to set a number of operating parameters for

the SDRAM controller. There are two configuration registers SDCONF0, SDCONF1 for SDRAM bank 0,

bank 1 respectively. Each bank can have been set to different configurations. W90P710 also offers the

flexible timing control registers to control the generation and processing of the control signal and can

suit to control the timing of different speed type of SDRAMs. These timing control registers are

SDTIME0 and SDTIME1 for SDRAM bank 0, bank 1 respectively each.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 30

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 30

The configurations of SDCONF and SDTIME are dependent on the SDRAM types attached to the

EBI interface. Thus the software should have the information about the SDRAM attached to the EBI

interface before set the SDCONF and SDTIME according to the timing of SDRAM types. The SDRAM

components supported by W90P710 can be found in W90P710 spec data sheet.

The base address of SDRAM bank 0 and bank 1 are also programmable. By BASADDR of

SDCONF, the SDRAM bank can be place in a specific address location. BASADDR is 13 bits, and the

base address is calculated as BASADDR << 18. Thus the range of the base address each SDRAM

bank is from 0x0 to (2^13-1)*2^18. Whenever setting the SDCONF register, the MRSET bit should be

set. If this bit doesn’t set when setting SDCONF, the SDRAM controller won’t issue a mode register set

command to SDRAM and the setting will be invalid. The SDRAM controller offers auto pre-charge mode

of SDRAM for SDRAM bank0/1. If this mode is enabled, the SDRAM will issue a pre-charge command

to SDRAM when for each access.

2.4.4 External I/O cont rol registers

The W90P710 supports an external device control without glue logic. It is very cost effective

because provides address decoding and control signals timing logic are not needed. The control

registers can control special external I/O devices for providing the low cost external devices control

solution. For instance, if there is a SRAM is attached to the external I/O bank 0. Then the SRAM can be

access as memory after setting the external I/O control register of external I/O bank 0. By the way, the

flash ROM also can be attached to the external I/O. There are four external I/O banks relative to four

control registers called EXT0CON, EXT1CON, EXT2CON, and EXT3CON. The base address of each

external I/O bank can be set by BASADDR of external I/O control register. BASADDR is 13 bits and the

base address is calculated as BASADDR << 18.

2.4.5 A system memory initialization example flow chart

Figure 2-2 System Memory Map Setting Flow

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 31

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 31

Reset Go

Does the system have

been initialized?

Calculating the correct instruction fetch address

after remapping boot FLASH/ROM base addre ss

Calculating the correct instruction fetch address

after remapping boot FLASH/ROM base addre ss

Set the EBICON, ROMCON, SDCONF0,

SDCONF1, SDTIME0, and SDTIME1 at the sa me

time by store multiple instr u cti on.

Branch to the correct instructi on fet ch address

calculated before.

Execute boot software

Example:

EBICON = 0x000509C 1

ROMCON = 0xFFA00724 (base=0x7FD00000 size=256KB)

SDCONF0 = 0x000010ED (base=0x00000000 size=32MB )

SDCONF0 = 0x040010ED (base=0x02000000 size=32MB )

SDTIME0 = 0x000007FF

SDTIME0 = 0x000007FF

Boot FLASH/ROM 256KB

Before Initialization

0x7FFFFFFF

0x00040000

0x00000000

Boot FLASH/ROM 256KB

SDRAM BANK 1

SDRAM BANK 0

After Initialization

0x7FFFFFFF

0x7FD000000

0x04000000

0x02000000

0x00000000

Figure 2-4 is the boot flow of Boot Monitor with remapping. The flow chart shows that most of the

EBI control registers, EBICON, ROMCON, SDCONF, SDTIME should beware initialized as soon as

possible immediately after reset. Each value of these control register must be known before these

registers were configured. Because on doing of remapping, the control registers should be set by store

multiple instructions (STMIA). The store multiple instructions guarantee to complete the memory

initialization before next instruction execution. The system memory maps before initialization and after

initialization are shown as above, too. After system reset, the system can access the 256KB boot

FLASH/ROM. After the system initialization the memory map becomes the After Initialization of Figure

2-4.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed,

distributed or reproduced without permission from Winbond.

Table No.: 1200-0003-07-A

Page 32

NO: W90P710 Programming Guide VERSION: 2.1 PAGE: 32

2.4.6 REMAPPING

RAM is normally with faster access speed and wider than ROM. For this reason, it is better to store

for the vector table and interrupt handlers if the memory on system address at 0x0 is of RAM. However,

if RAM is located at address 0x0 on power-up, there is not a valid instruction in the reset vector (0x0)

entry. Therefore, you must allow ROM to be located at 0x0 during normal execution. The changeover

remapping from the reset to the normal memory map is normally caused by writing to a memory-

mapped register.

In W90P710 the memory remapping can be achieved by setting EBI control registers. The following

example is a MACRO, which achieves performs the remapping when booting. The program flow of this

example is as Figure 2-4.

In general, the memory remapping only needs to be preformed once at reset. Thus the reset value

of SDCONF0 is used to check if the system has been initialized. If the system memory needs to do