Winbond W83303AD, W83303AG Schematic [ru]

Advanced ACPI Controller

W83303AD/W83303AG

Winbond

W83303AD/W83303AG

W83303AD/W83303AG

W83303AD/AG

Data Sheet Revision History

Pages Dates Version

1 N.A. N.A.

2 N.A. 10/25/04 0.5 N.A. First published preliminary version.

3 N.A. 12/20/04 0.51 N.A.

4 12,13,14 1/09/06 0.52 N.A. Modified the application circuit.

5

6

7

8

Please note that all data and specifications are subject to change without notice. All the trademarks of

products and companies mentioned in this data sheet belong to their respective owners.

Version

on Web

Main Contents

All of the versions before 0.50 are for internal

use.

Add part no of W8303AG with Pb-free

package.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or

systems where malfunction of these products can reasonably be expected to result in

personal injury. Winbond customers using or selling these products for use in such

applications do so at their own risk and agree to fully indemnify Winbond for any

damages resulting from such improper use or sales.

W83303AD/W83303AG

1. GENERAL FUNCTION DESCRIPTION

y Provides Voltages

− 5V Active/Sleep (5VDUAL)

/5V

− Programmable 5V

− 3.3V Active/Sleep (3.3VDUAL)

− Programmable Dual-Channels RAM Active/Sleep (V

− Auto-detective 2.6V

− Two Programmable Linear Regulators and one Linear Regulator Ranging 1.2V~5.00V for

Over-Clocking Application

− 1.2V VCCVID for Intel® P4 CPU or FSB_VTT for Grandsdale

− 1.5V VPCI Voltage

y Supports VRGOOD signal for Intel® P4 CPU Power Good Control

y Supports RSMRST# Signal Control

y Provides Signals for ATX Power Supply PS_ON# Control

y I2C Interface

y Selectable I2C Address

y Internal Charge Pump Support Up to 9.5VSB

y Drive All N-Channel MOSFET

y Soft Start

y Under-Voltage Monitoring for 3VDUAL, VPCI and VRAM Channels

DL

/5VCC for USB Devices(5VUSB)

STR

STR

/1.8V

for DDR/DDRII Voltage

STR

) for DDR

STR

Publication Release Date: Jan. 9, 2006

- 1 - Revision 0.52

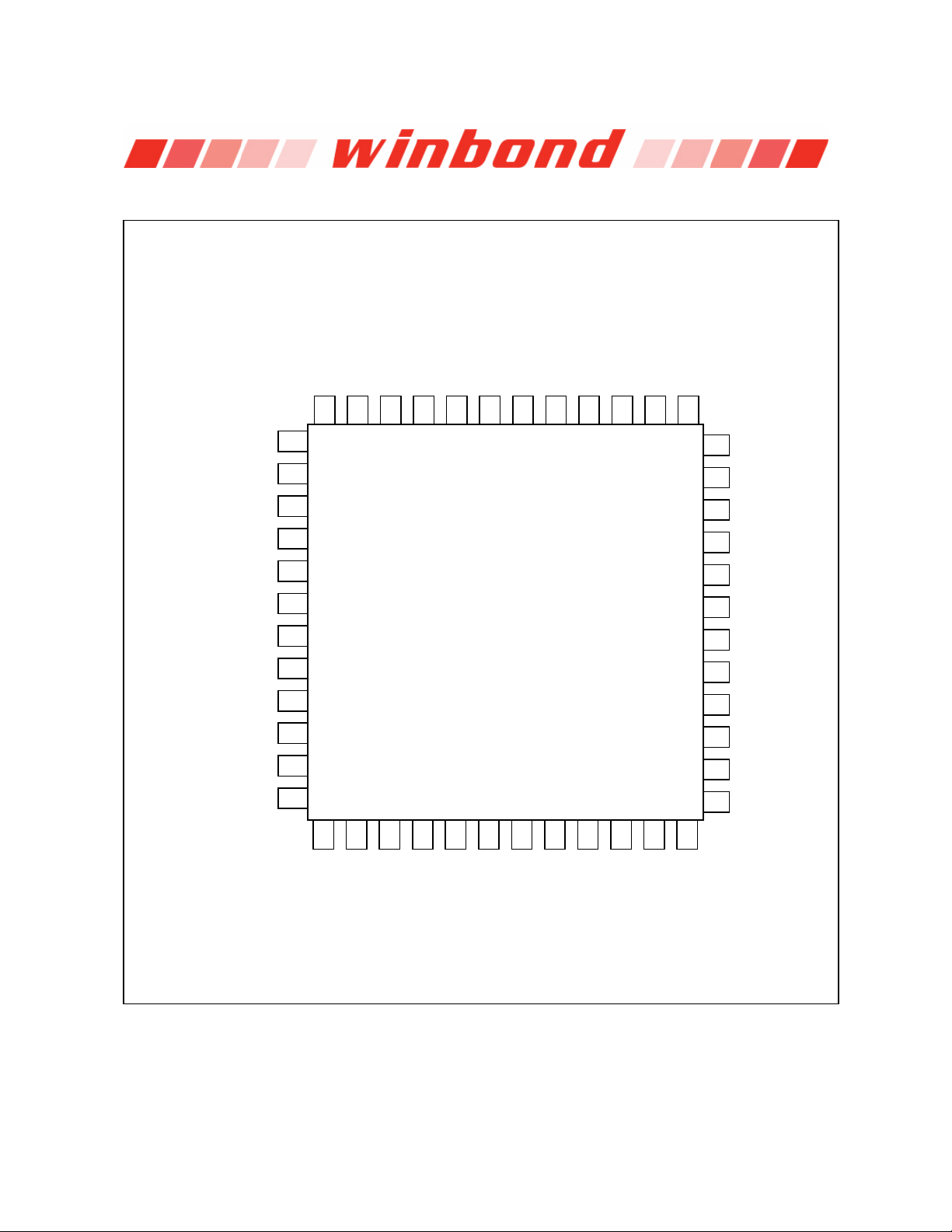

2. W83303AD/AG PIN-OUT

LR1_DRV

VCC

36 35 34 33 32 31 30 29 28 27 26 25

VPCI_SEN

VPCI_DRV

AGND

CHRPMP

C2

W83303AD/W83303AG

C1

5VSB

1.2V_DRV

1.2V_SEN

VRGOOD

LR1_SEN

LR2_DRV

LR2_SEN

DDRDET#

FAULT#

PS_IN#

PW_BUT#

PS_OUT#

DGND

PWR_OK

A0

D5VSB

37

38

39

RSMRST#

PWM_MODE

LR3_SEN

LR3_DR V

AGND

40

41

42

43

44

45

46

47

48

1 2 3 4 5 6 7 8 9 10 11 12

S3#

W83303AD/AG

S5#

I2C_CLK

I2C_DATA

5VUSB

5VSBDRV

AGND

24

VRAM_DRV1

23

I_SEN1

22

VRAM_SEN

21

VRAM_DRV2

20

I_SEN2

19

5VSB

18

ISET

17

SS

16

VCC3

15

3.3VSB_DRV

14

3.3V_SEN

13

3V/5VDRV

- 2 -

W83303AD/W83303AG

A

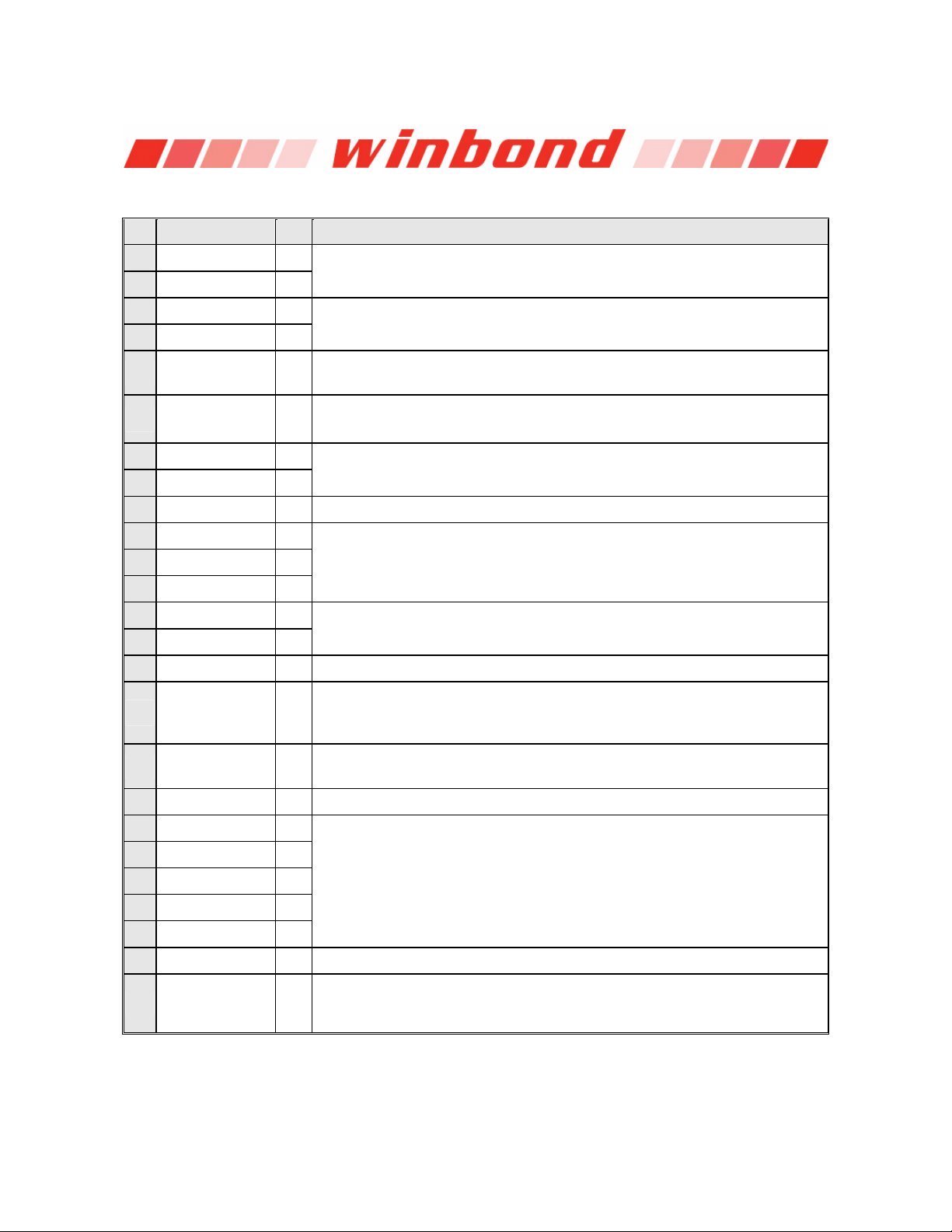

3. PIN DESCRIPTIONS

NO NAME I/O FUNCTION DESCRIPTION

1

2 S5# I

S3# I

SYSTEM ACPI CONTROL SIGNALS

3 I2C_DATA I/O

4 I2C_CLK I

5 RSMRST# OD

6 PWM_MODE I

7 LR3_SEN I

8 LR3_DRV O

9 AGND P Power ground

10 5VUSB O

11 5VSBDRV O

12 5VDRV O

13 3.3V_SEN I

14 3.3VSB_DRV O

15 VCC3 P Power 3.3Vcc

16 SS I

17 I

SET

I2C Interface, and the default ID value are defined as 5CH (0101 110X) as

well as 5EH (0101 111X), and X is used to control read/write.

A signal to indicate 3VDUAL power status. The signal will be issued after

82ms delay when the level of 3VDUAL higher than 2.8V

0=Internal RAM for Linear Mode;

1= external RAM for PWM Mode

Linear Regulators ranging form 1.2V to 5V and can be adjusted by

external resistors

Power switch for USB devises provides a programmable Voltage

(5VDUAL/5VSTR/ 5VCC) for USB devices. It can be set by register CR00

3.3VDUAL Voltage regulator

Soft-Start pin. Attach a capacitor to this pin to determine the soft-start rate;

and the slew-rate of SS is set by adjust the capacity of the external

capacitor.

ttached a specific external resistor to determine the internal reference

I

current.

18 5VSB P Power Pin

19 I_SEN2 I

20 VRAM_DRV2 O

21 VRAM_SEN I

22 I_SEN1 I

23 VRAM_DRV1 O

24 AGND P Power ground

25 VRGOOD OD

2 channels of V

design to balance the current on the channels. In which I_SEN1 & I_SEN2

pins should be connected together to 5VSB or 3VDUAL if only one

channel used. The DDR or DDRII determine by DDRDET#. If DDRDET#

=0 VRAM=DDR(2.6V) ; DDRDET#=1 VRAM=DDRII(1.8V).

The signal is applied for the Intel® Northwood CPU using; it’s a signal to

declare the CPU VID status.

output for DDR or DDRII with internal current sharing

STR

Publication Release Date: Jan. 9, 2006

- 3 - Revision 0.52

W83303AD/W83303AG

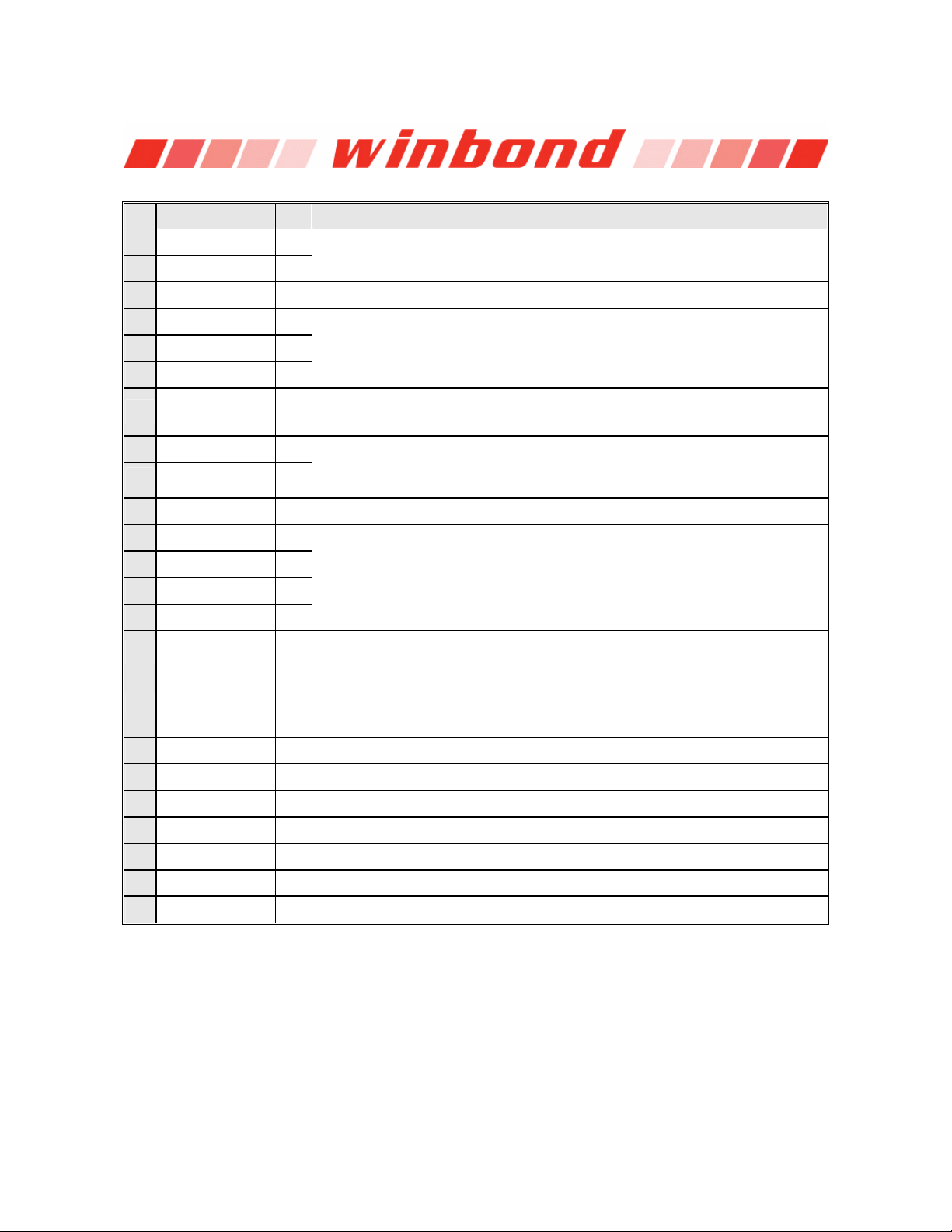

Pin Descriptions, continued

NO NAME I/O FUNCTION DESCRIPTION

26 1.2V_SEN I

27 1.2V_DRV O

28 5VSB P Power Pin

29 C1 I

30 C2 I

31 CHRPMP P

1.2V

Charge pump pins. It supports 10mA driving current and insures output

voltage 9V or above.

voltage regulator for Intel® P4 CPU application.

CC

32 AGND P

33 VPCI_DRV O

34 VPCI_SEN I

35 VCC P Power pin

36 LR1_DRV O

37 LR1_SEN I

38 LR2_DRV O

39 LR2_SEN I

40 DDRDET# I

41 FAULT# I

42 PS_IN# Power on signal. Low active.

43 PW_BUT# I System PW_BUT for power sequence monitoring.

44 PS_OUT# O Pin to control ATX power supply.

45 DGND P Power ground.

Power pin

1.5V Voltage Regulator for PCI Express. If this power plane won’t be

used, the VPCI_SEN must be connected to 3VDUAL to avoid the fault

trigger of LUV event.

Linear Regulators ranging form 1.2V to 5V and can be adjusted by

external resistors

A signal to indicate type of DDRRAM that plugged- in; low means 2.6V for

DDR and high means 1.8V for DDRII.

Fault event be monitored; the chip shut the ATX power supply down

directly by control the PS_ON# signal as long as the fault events are

triggered.

46 PWR_OK I Power good input signal of ATX power supply.

47 A0 I I2C address selecting pin.

48 D5VSB P Power pin.

*VRGOOD & TYPEDET# can endure 0-12V level voltage.

- 4 -

Loading...

Loading...