WCH CH347 User Manual

CH347 手册

1

高速 USB 转接芯片 CH347

手册

版本:1C

http://wch.cn

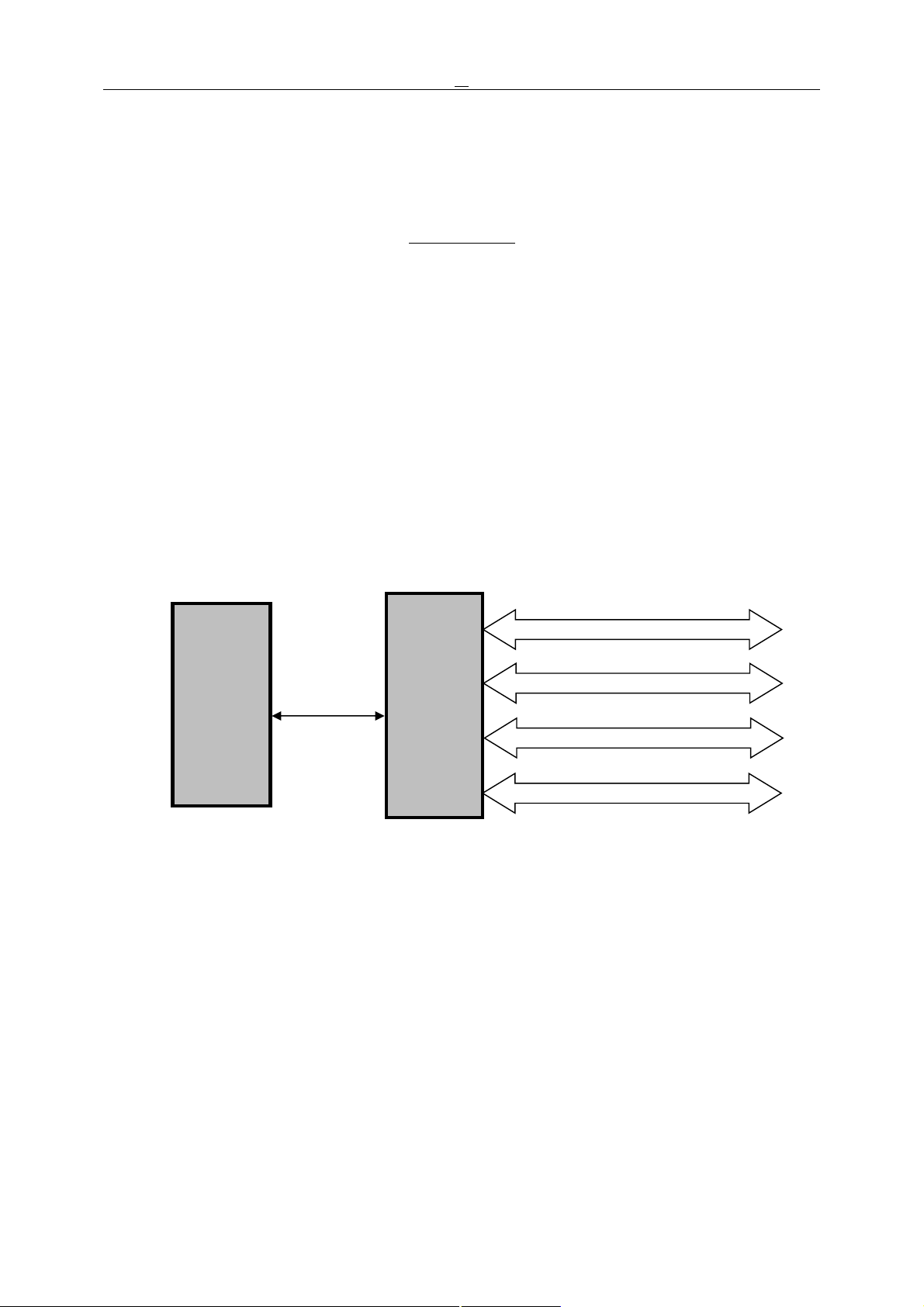

1、概述

CH347 是一款高速 USB 总线转接芯片,通过 USB 总线提供异步串口、I2C 同步串行接口、SPI 同

步串行接口和 JTAG 接口等。

在异步串口方式下,CH347 提供了 2 个高速串口,支持 RS485 串口收发使能控制、硬件流控和常

用的 MODEM 联络信号,用于为计算机扩展异步串口,或者将普通的串口设备或者 MCU 直接升级到 USB

总线。

在同步串行接口方式下,CH347 提供了 1 个 2 线 I2C 接口(SCL 线、SDA 线)和 1 个 4 线 SPI 接口

(SCS 线、SCK/CLK 线、MISO/SDI/DIN 线、MOSI/SDO/DOUT 线),用于为计算机扩展 2 线或 4 线同步串

行接口,操作 EEPROM、FLASH 和传感器等器件。

在 JTAG 接口方式下,CH347 提供了 1 个 JTAG 接口,支持 4/5/6 线接口(TMS 线、TCK 线、TDI 线、

TDO 线、TRST 线和 SRST 线),用于为计算机扩展 JTAG 接口,操作 CPU、DSP、FPGA 和 CPLD 等器件。

在 SWD 接口方式下,CH347 提供了 1 个 SWD 接口(SWDCLK 线,SWDIO 线),用于为计算机扩展 SWD

接口,操作 ARM MCU 和 CPU 等器件。

计算机

或

其它

USB 主机

USB

CH347

高速 USB

转接芯片

0#异步串口 UART/RS232/RS485

1#异步串口 UART/RS232/RS485

2 线 IIC 和 4 线 SPI 同步串口

JTAG 接口/SWD 接口

2、特点

2.1. 概述

l 480Mbps 高速 USB 设备接口,外围元器件只需晶振和电容。

l 内置 EEPROM,可 配置 工 作模 式、芯片 VID、PID、最大电流值、厂商和产品信息字符串等参数。

l 单一 3.3V 供电。

l CH347F 支持 I/O 独立供电,支持 3.3V、2.5V、1.8V 电源电压。

l 提供 TSSOP-20 和 QFN28 无铅封装,兼容 RoHS。

l 多种工作模式,适应高速 USB 转接应用需求。

2.2. 异步串口

l 内置固件,仿真标准串口,用于升级原串口外围设备,或者通过 USB 增加额外串口。

l 计算机端 Windows 操作系统下的串口应用程序完全兼容,无需修改。

CH347 手册

l 硬件全双工串口,内置独立的收发缓冲区,通讯波特率支持 1200bps~9Mbps。

l 串口支持 8 个数据位,支持奇校验、偶校验以及无校验,支持 1 或 2 停止位。

l 每个串口内置 12K 字节的接收 FIFO,4K 字节的发送 FIFO。

l 支持常用的 MODEM 联络信号 RTS、DTR、DCD、RI、DSR、CTS。

l 支持 CTS 和 RTS 硬件自动流控。

l 支持半双工,提供串口正在发送状态指示 TNOW,可用于控制 RS485 收发切换。

l 支持最多 8 路 GPIO 输入输出功能。

l 通过外加电平转换器件,支持 RS232、RS485、RS422 等接口。

2

2.3. I2C 同步串行接口

l 作为 Host/Master 主机模式。

l 提供 SCL 和 SDA 两根信号线,支持 5 种传输速度,传输频率可达 1MHz。

l 通过计算机 API 配合,可灵活操作 2 线接口的 A/D、D/A、EEPROM 和传感器等器件。

2.4. SPI 同步串行接口

l 作为 Host/Master 主机模式。

l 提供 SCS 线、SCK/CLK 线、MISO/SDI/DIN 线、MOSI/SDO/DOUT 四根信号线。

l 支持 2 根片选信号线,可分时操作 2 个 SPI 接口设备。

l 支持 8 位/16 位数据结构,支持 MSB 和 LSB 传输。

l 支持 SPI 模式 0/1/2/3,支持传输频率配置,传输频率可达 60MHz。

l 支持硬件 DMA 发送和接收。

l 通过计算机 API 配合,可灵活操作 4 线接口的 FLASH、MCU、传感器等器件。

2.5. JTAG 接口

l 作为 Host/Master 主机模式。

l JTAG 接口提供 TMS 线、TCK 线、TDI 线、TDO 线、TRST 线(可选)和 SRST 线(可选)。

l 支持高速 USB 数据传输。

l 通过计算机 API 配合,可灵活操作 CPU、DSP、FPGA、CPLD、MCU 等器件。

2.6. SWD 接口

l 作为 Host/Master 主机模式。

l SWD 接口提供 SWDCLK 线、SWDIO 线。

l 通过计算机 API 配合,可灵活操作 ARM MCU 和 CPU 等器件。

CH347 手册

3

3、封装

封装形式 塑体宽度 引脚间距 封装说明 订货型号

QFN28_4X4 4*4mm 0.4mm 15.7mil

TSSOP-20 4.4mm 173mil 0.65mm

25mil 薄小型 20 脚贴片 CH347T

四边无引线 28 脚 CH347F

注:CH347 的 USB 收发器按 USB2.0 全内置设计,UD+和 UD-引脚不能串接电阻,否则影响信号质量。

CH347F 的底板是 0#引脚 GND,是可选但建议的连接;其它 GND 是必要连接。

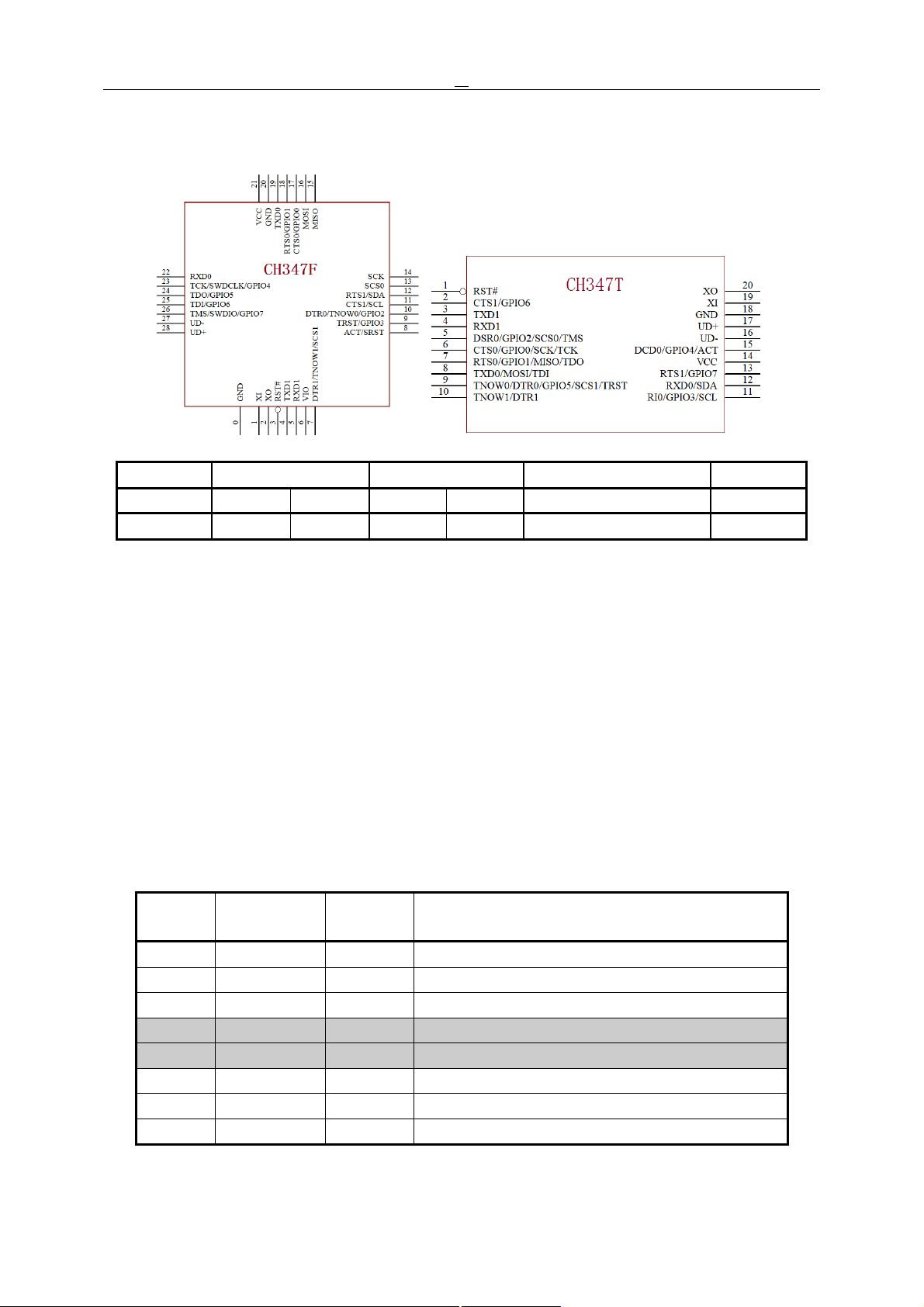

4、引脚

4.1. 一般说明

CH347 芯片具有多种工作模式,同一引脚在不同工作模式下的功能和定义可能不同。CH347T 芯片

在上电复位或外部复位时,检测配置引脚状态自动配置工作模式。

注:FT 表示引脚作为输入时耐受 5V 电压。

4.2. CH347F 引脚

标准的公共引脚

引脚号 引脚名称 类型 引脚说明

21 VCC 电源 电源调节器正电源输入端,需要外接退耦电容

0,20 GND 电源 公共接地端,需要连接 USB 总线的地线

3 RST# 输入 外部复位输入端,低电平有效,内置上拉电阻

28 UD+ USB 信号 直接连到 USB 总线的 D+数据线,不能额外串接电阻

27 UD- USB 信号 直接连到 USB 总线的 D-数据线,不能额外串接电阻

1 XI 输入 晶体振荡输入端

2 XO 输出 晶体振荡反相输出端

6 VIO 电源 I/O 端口电源输入端,需要外接退耦电容

CH347 手册

4

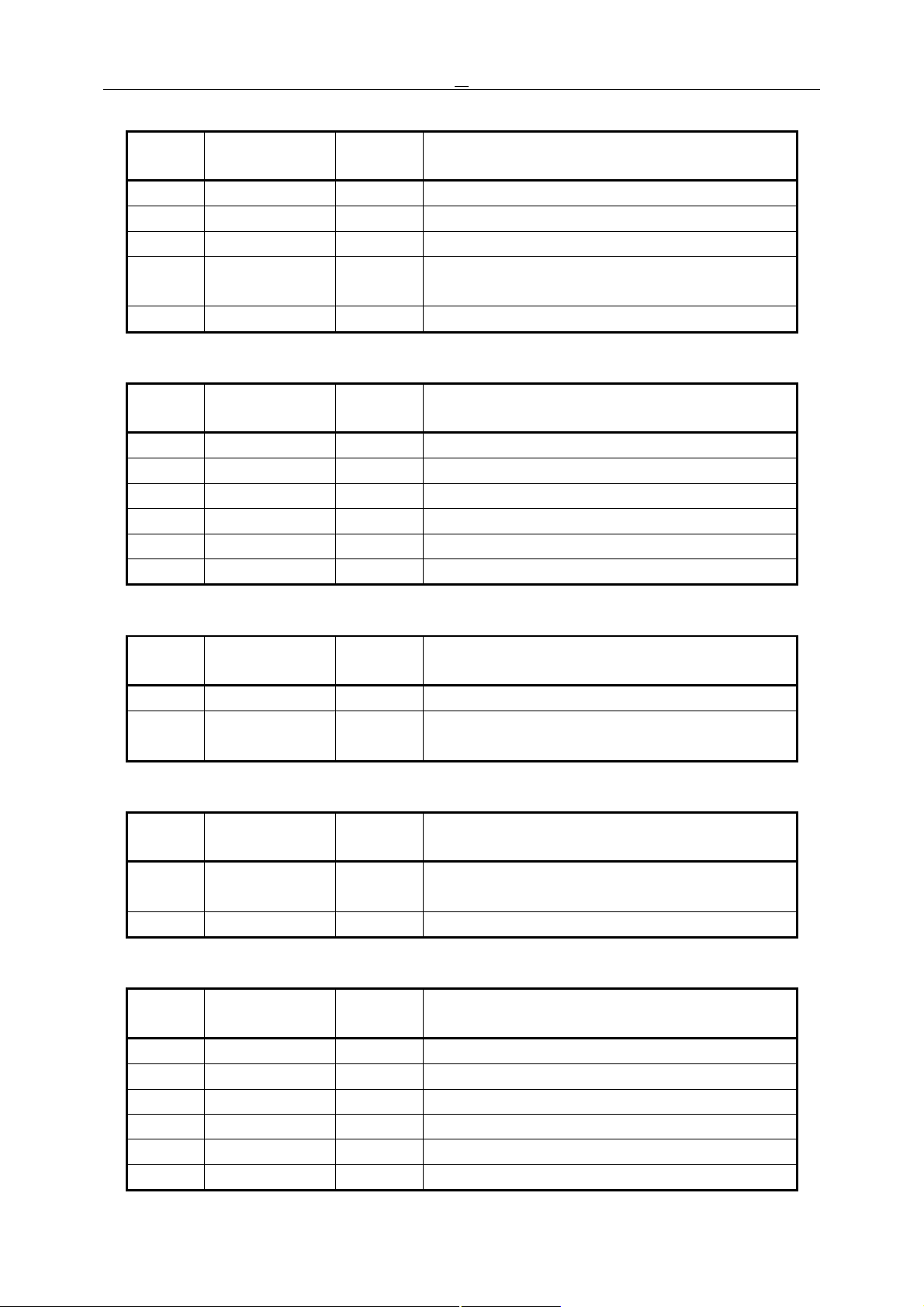

SPI 接口相关引脚

引脚号 引脚名称 类型 引脚说明

13 SCS0 输出 4 线串口的片选输出 0

7 SCS1 输出 4 线串口的片选输出 1

14 SCK 输出 4 线串口的时钟输出,别名 DCK

15 MISO 输入(FT)

4 线串口的数据输入,别名 DIN 或 SDI,

内置上拉电阻

16 MOSI 输出 4 线串口的数据输出,别名 DOUT 或 SDO

JTAG 接口相关引脚

引脚号 引脚名称 类型 引脚说明

25 TDI 输出 JTAG 接口的数据输出

24 TDO 输入(FT)

JTAG 接口的数据输入,内置上拉电阻

23 TCK 输出 JTAG 接口的时钟输出

26 TMS 输出 JTAG 接口的模式选择

9 TRST 输出 JTAG 接口的复位输出

8 SRST 输出 JTAG 接口的系统复位输出

SWD 接口相关引脚

引脚号 引脚名称 类型 引脚说明

23 SWDCLK 输出 SWD 接口的时钟引脚

26 SWDIO

输出

输入(FT)

SWD 接口的数据引脚

I2C 接口相关引脚

引脚号 引脚名称 类型 引脚说明

12 SDA

输出

输入(FT)

2 线串口的数据输入输出

11 SCL 输出 2 线串口的时钟输出

UART 接口相关引脚

引脚号 引脚名称 类型 引脚说明

19 TXD0 输出 UART0 的串行数据输出,空闲态为高电平

22 RXD0 输入(FT)

UART0 的串行数据输入,内置上拉电阻

4 TXD1 输出 UART1 的串行数据输出,空闲态为高电平

5 RXD1 输入 UART1 的串行数据输入,内置上拉电阻

17 CTS0 输入(FT) UART0 的 MODEM 输入信号,清除发送,低有效;

18 RTS0 输出 UART0 的 MODEM 输出信号,请求发送,低有效;

CH347 手册

5

上电期间,如果 RTS0 引脚检测到外接了

下拉电阻则禁用内部 EEPROM 中配置参数,

启用芯片自带默认参数

11 CTS1 输入(FT) UART1 的 MODEM 输入信号,清除发送,低有效;

12 RTS1 输出 UART1 的 MODEM 输出信号,请求发送,低有效;

UART0 的 MODEM 输出信号,数据终端就绪,低有效;

10 DTR0/TNOW0 输出

UART0 的 RS485 发送和接收控制引脚;

上电期间,如果 DTR0 引脚检测到外接了下拉电阻

则 DTR0 和 DTR1 分别切换为 TNOW0 和 TNOW1 功能

7 DTR1/TNOW1 输出

UART1 的 MODEM 输出信号,数据终端就绪,低有效;

UART1 的 RS485 发送和接收控制引脚

GPIO 相关引脚

引脚号 引脚名称 类型 引脚说明

17 GPIO0

18 GPIO1

10 GPIO2

9 GPIO3

23 GPIO4

24 GPIO5

25 GPIO6

26 GPIO7

输入(FT)

输出

输入(FT)

输出

输入

输出

输入

输出

输入(FT)

输出

输入(FT)

输出

输入(FT)

输出

输入(FT)

输出

通用 GPIO0,用于 IO 口输入或输出。

通用 GPIO1,用于 IO 口输入或输出。

通用 GPIO2,用于 IO 口输入或输出。

通用 GPIO3,用于 IO 口输入或输出。

通用 GPIO4,用于 IO 口输入或输出。

通用 GPIO5,用于 IO 口输入或输出。

通用 GPIO6,用于 IO 口输入或输出。

通用 GPIO7,用于 IO 口输入或输出。

注 1:CH347F 的第 17 和第 18 引脚的电源来自 VCC,为 3.3V 信号电平;其它引脚的电源来自 VIO,

为 VIO 相匹配的 3.3V/2.5/1.8V 信号电平。

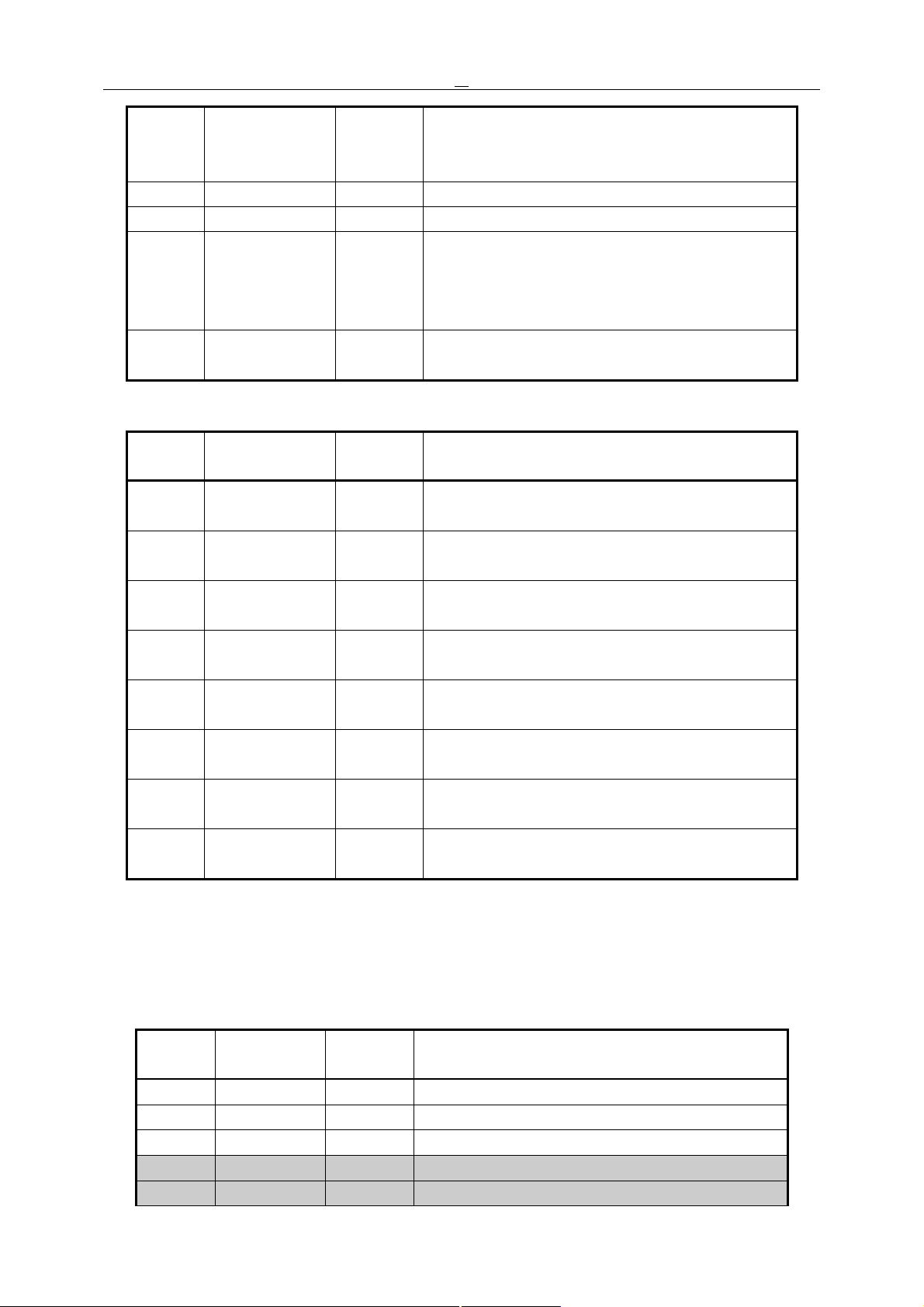

4.3. CH347T 引脚

标准的公共引脚

引脚号 引脚名称 类型 引脚说明

14 VCC 电源 电源调节器正电源输入端,需要外接退耦电容

18 GND 电源 公共接地端,需要连接 USB 总线的地线

1 RST# 输入 外部复位输入端,低电平有效,内置上拉电阻

17 UD+ USB 信号 直接连到 USB 总线的 D+数据线,不能额外串接电阻

16 UD- USB 信号 直接连到 USB 总线的 D-数据线,不能额外串接电阻

Loading...

Loading...