VMICPCI-7715

Single Board, All Rear I /O Pentium III® Socket 370

Processor-Based CompactPCI SBC

Product Manual

12090 South Memorial Parkway

Huntsville, Alabama 35803-3308, USA

(256) 880-0444

w (800) 322-3616 w Fax: (256) 882-0859

500-657715-000 Rev. A

COPYRIGHT AND TRADEMARKS

© Copyright 2000. The information in this document has been carefully checked and is believed to be entirely reliable.

While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no

responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC’s products to improve reliability,

performance, function , or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor

does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC’s Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, IOMax

MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus,

TESTCAL, “The Next Generation PLC”, The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic

Control(ler),

trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are

service marks of VMIC.

The I/O man figure, IOWorks, IOWorks man figure, UIOC, Visual IOWorks, the VMIC logo, and

registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX

are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarks, and Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers’ Group.

Other registered trademarks are the property of their respective owners.

VMEaccess

, VMEbus Access

(I/O man figure)

, VMEmanager, VMEmonitor

(IOWorks man figure)

, IOWorks Foundation, IOWorks Manager, IOWorks Server,

, VMEnet, VMEnet II, and

VMEprobe

WinUIOC

are

are

VMIC

All Rights Reserved

This document shall not be duplicated, nor its contents used for any

purpose, unless granted express written permission from VMIC.

Table of Contents

Overview

Organization of the Manual

References

Safety Summary

Safety Symbols Used In This Manual

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Chapter 1 - VMICPCI-7715 Features and Options

CompactPCI Features

VMICPCI-7715 Product Options

Chapter 2 - Installation and Setup

Unpacking Procedures

Hardware Setup

Installation

BIOS Setup

PMC Expansion Site Connectors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Chapter 3 - PC/AT Functions

CPU Socket

Physical Memory

Memory and Port Maps

Memory Map

I/O Port Map

PCI-to-PCI Bridge

PC/AT Interrupts

PCI Interrupts

I/O Ports

Video Graphics Adapter

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5

Ethernet Controller

10BaseT

100BaseTx

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Chapter 4 - Embedded PC/RTOS Features

DiskOnChip (Optional)

Installing the DiskOnChip

Configuring the DiskOnChip as the Boot Device

Using the DiskOnChip with Other Operating Systems

Watchdog Timer

Time of Day Registers

Time of Day Alarm Registers

Watchdog Alarm Registers

Command Register

Timers

Battery Backed SRAM

Smbus Multiplexer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

General

Timer Interrupt Status

Clearing the Interrupt

Timer Programming

Mode Definitions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Architecture

Writing

Reading

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Chapter 5 - Maintenance

Maintenance Prints

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Appendix A - Connector Pinouts

J1 Connector Pinout

J2 Connector Pinout

J4 Connector Pinout

J5 Connector Pinout

PMC J7 Connector Pinout

PMC J8 Connector Pinout

PMC J6 Connector Pinout

6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Appendix B - System Driver Software

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Driver Software Installation

Windows 2000

Windows 2000 82559ER Driver Installation

Windows NT (Version 4.0)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Appendix C - Phoenix BIOS

System BIOS Setup Utility

Help Window

Main Menu

QuickBoot

Setting The Time

Setting The Date

Legacy Diskette

Floppy Drive A

Floppy Drive B

Primary Master/Slave

Secondary Master

Keyboard Features

NumLock

Key Click

Keyboard Auto-Repeat Rate (Chars/Sec)

Keyboard Auto-Repeat Delay (sec)

Keyboard Test

System Memory

Extended Memory

Extended Memory

Console Redirection

Com Port Address

Baud Rate

Console Type

Flow Control

Console Connection

Console Redirection After P OST

Advanced Menu

Installed O/S

ACPI

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Reset Configuration Data

Cache Memory

I/O Device Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7

Large Disk Access Mode

Local Bus IDE Adapter

Advanced Chipset Control

Graphics Aperture

Enable Memory Gap

ECC Config

SERR

Power

Boot Menu

Exit Menu

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Exit Saving Changes

Exit Discarding Changes

Load Setup Defaults

Discard Changes

Save Changes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Appendix D - LANWorks BIOS

Boot Menus

First Boot Menu

Boot Menu

BIOS Features Setup

RPL

TCP/IP

Netware

PXE

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Appendix E - Device Configuration: I/O and Interrupt Control

BIOS Operations

BIOS Control Overview

Functional Overview

Data Book References

Device Address Definition

ISA Devices

PCI Devices

Device Interrupt Definition

PC/AT Interrupt Definition

ISA Device Interrupt Map

PCI Device Interrupt Map

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

. . . . . . . . . . . . . . . . . . . . 109

8

Appendix F - Sample C Software

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Directory CPU

CPU.C

** FILE: CPU.H

** FILE: FLAT.C

** FILE: FLAT.H

** FILE: PCI.C

** FILE: PCI.H

** FILE: UNIVERSE.H

Directory Smbus

FILE: Pci.h

** FILE: SCAN.H

Directory SRAM

**File: T_SRAM.C

Directory Timers

**File: CPU.H

**File: PCI.H

**File: PCI.C

**File: T_Timers.C

**File: Timer.C

Directory WATCHDOG

**File: Watchdog.H

**File: WDT0_RST.C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Index

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

9

10

List of Figures

Figure 1-1 VMICPCI-7715 Block Diagram

Figure 2-1 VMICPCI-7715 Board Jumper Locations

Figure 2-2 PCI Expansion Site

Figure 3-1 Connections for the PC Interrupt Logic Controller

Figure 4-1 Watchdog Alarm Block

Figure 4-2 Timer Interrupt Status Register Read/Steps

Figure 4-3 Timer Interrupt Status Register

Figure 4-4 Clearing the Timer Interrupt Status Register

Figure 4-5 82C54 Diagram

Figure 4-6 Internal Timer Diagram

Figure A-1 VMICPCI-7715 Connector Locations

Figure A-2 J1 Connector and Pinout

Figure A-3 J2 Connector and Pinout

Figure A-4 J4 Connector and Pinout

Figure A-5 J5 Connector and Pinout

Figure E-1 VMICPCI-7715 Block Diagram

Figure E-2 BIOS Default Connections for the PC Interrupt Logic Controller

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

. . . . . . . . . . . . . . . . . . . 117

11

12

List of Tables

Table 1-1 PC/AT I/O Features

Table 2-1 Board Connectors

Table 2-2 Watchdog Timer Select (User Configurable) - Jumper (E27)

Table 2-3 BIOS Mode Option - Resister (R409)

Table 2-4 Password Clear (User Configurable) - Jumper (E24)

Table 2-5 CMOS Battery Enable (User Configurable) - Jumper (E23)

Table 2-6 Watchdog Battery Enable (User Configurable) - Jumper (E22)

Table 2-7 Clock Select (User Configurable) - Jumper (E28)

Table 3-1 VMICPCI-7715, Interface Memory Address Map

Table 3-2 VMICPCI-7715 I/O Address Map

Table 3-3 PC/AT Hardware Interrupt Line Assignments

Table 3-4 PC/AT Interrupt Vector Table

Table 3-5 NMI Register Bit Descriptions

Table 3-6 Supported Graphics Video Resolutions

Table 4-1 Watchdog Registers

Table 4-2 Time of Day Alarm Registers

Table 4-3 I/O Address of the Control Word Register and Timers

Table 4-4 Control Word Format

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

. . . . . . . . . . . . . . . . . . . . . . . 33

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

. . . . . . . . . . . . . . . . . . . . . . 32

. . . . . . . . . . . . . . . . . . . . 33

Table 4-5 ST - Select Timer

Table 4-6 RW - Read/Write

Table 4-7 M - Mode

Table 4-8 BCD

Table 4-9 Read-Back Command Format

Table 4-10 Read-Back Command Description

Table 4-11 Status Byte

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

13

Table 4-12 Status Byte Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 4-13 LOAD Bit Operation

Table 4-14 Smbus Multiplexer Address

Table 4-15 LSB Control Bytes

Table A-1 PMC J7 Connector Pinout

Table A-2 PMC J8 Connector Pinout

Table A-3 PMC J6 Connector Pinout

Table E-1 ISA Device Mapping Configuration

Table E-2 PCI Device Mapping Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table E-3 Device PCI Interrupt Mapping by the BIOS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

14

Overview

Introduction

VMIC’s VMICPCI-7715 is a complete Pentium III Socket 370 processor-based

computer with the additional benefits of Eurocard construction and full compatibility

with the CompactPCI Specif ication Rev. 2.1. The VMICPCI-7715 w ith advan ced CPCI

interface and SDRAM which is dual-ported to the CPCI bus, is ideal for CPCI system

controller applications.

The single-slot CPU board functions as a standard PC/AT, executing a PC/AT-type

power-on self-test, then boots up Windows 98 SE, Windows NT or any other

PC/AT-compatible operating system. The PC/AT mode of the VMICPCI-7715 is

discussed in Chapter 3 of this manu al .

The VMICPCI-7715 also operates as a CPCI system slot SBC and interacts with other

CPCI modules via the on-board embedded bridge.

The VMICPCI-7715 also provides capabilities beyond the features of a typical PC/AT

compatible CPU, including a programma ble Watchdog Timer, nonvolatile SRAM,

Independent 16 Bit Timers and a bootable DiskOnChip system. These features make

the unit ideal for embedded applications. These nonstandard PC/AT functions are

discussed in Chapter 4 of this manual.

15

VMICPCI-7612 Product Manual

Organization of the Manual

This manual is composed of the following chapters and appendices:

Chapter 1 - VMICPCI-7715 Feat ures and Opti ons describes the features of the base

unit.

Chapter 2 - Installation and Setup describes unpacking, inspection, hardware jumper

settings, connector definitions, installation, system setup and operation of the

VMICPCI-7715.

Chapter 3 - PC/AT Functions describes the unit design in terms of the standard PC

memory and I/O maps, along with the standard interrupt architecture.

Chapter 4 - Embedded PC/RTOS Features describes the unit features that are beyond

standard PC/AT functions.

Chapter 5 - Maintenance provides information relative to the car e and maintena nce of

the unit.

Appendix A - Connector Pinouts illustrates and defines the connectors included in the

unit’s I/O ports.

Appendix B - Phoenix BIOS describes the menus and options associated with the

Phoenix BIOS.

Appendix C - Device Configuration: I/O and Interrupt Control provides the user with

the information needed to develop custom applications such as the revision of the

current BIOS configuration to a user-specific configuration.

Appendix D - LANWorks BIOS describes the menus and options associated with the

LANWorks BIOS.

Appendix E - Device Configuration: I /O and Interrupt Control provides the

information needed to develop custom applications such as revision of the current

BIOS configuration to a user-specific configuration.

Appendix F - Sample C Software provides example code to use with the

VMICPCI-7715

16

References

82443BX PCI and Memory Controller (PMC) 82443BX Data Bus Accelerator (DBX)

References

Some reference sources helpful in using or programming the VMICPCI-7715 include:

Pentium III Processors and Related Products

Intel Literature Sales

P.O. Box 7641

Mt. Prospect, IL 60056-7641

(800) 548-4752

www.intel.com

Intel 440BX PCIset

May 1996, Order Number 290549-001

Intel Corporation

P.O. Box 58119

Santa Clara, CA 95052-8119

(408) 765-8080

www.intel.com

Intel 21154 PCI-to-PCI Bridge

Intel Corporation

2200 Mission College Blvd.

P.O. Box 58119

Santa Clara, CA 95052-8119

PCI Special Interest Group

P.O. Box 14070

Portland, OR 97214

(800) 433-5177 (U.S.)

(503) 797-4207 (International)

FAX (503) 23 4-6762

www.pcisig.com

The following is useful information related to remote ethernet booting of the

VMICPCI-7715:

Microsoft Windows NT Server Resource Kit

Microsoft Corporation

ISBN: 1-57231-344-7

www.microsoft.com

Intel 82559 10/100 Mb/s Ethernet LAN Controller

Intel Corporation

2200 Mission College Blvd.

P.O. Box 58119

Santa Clara, CA 95052-8119

17

VMICPCI-7612 Product Manual

For additional information please refer to the following

Intel 82440BX AGP set: 82443BX Host Bridge/Controller

Intel Corporation

2200 Mission College Blvd.

P.O. Box 58119

Santa Clara, CA 95052-8119

Intel 82440BX PCIset ISA Bridge

82371EB PCI ISA IDE Xcellerator (PIIX4E)

2200 Mission College Blvd.

P.O. Box 58119

Santa Clara, CA 95052-8119

PCI Local Bus Specification, Rev. 2.1

PCI Special Interest Group

P.O. Box 14070

Portland, OR 97214

(800) 433-5177 (U.S.)

(503) 797-4207 (International)

(503) 234-6762 (FAX)

SMC FDC37C67X Enhanced Super I/O Controller

SMC Component Products Division

300 Kennedy Dr.

Hauppauge, NY 11788

(516) 435-6000

(516) 231-6004 (FAX)

ISA & EISA, Theory and Operation

Solari, Edward

Annabooks

15010 Avenue of Science, Suite 101

San Diego, CA 92128 USA

ISBN 0-929392 -15-9

DS 1384 Watchdog Timekeeping Controller

Dallas Semiconductor

4461 South Beltwood Pwky.

Dallas, TX 75244-3292

www.dalsemi.com

M-Systems Corporate Headquarters

USA Office

39899 Balentine Dr.

Suite 335

Newark, CA 94560

Tel: 510-413-5950

Fax: 510-413-5980

Email: info@m-sys.com

www.m-sys.com

18

Intel 69030AGP Video Controller

Intel Corporation

P.O. Box 58119

Santa Clara, CA 95052-8119

(408) 765-8080

www.intel.com

Phillips PCA9540 Smbus Multiplexer

Phillips Semiconductors

811 Eas t Arques Ave.

P.O. Box 3409

Sunnyvale, CA 94088-3409

1-800-234-7381

www.semiconductors.phillips.com

CMC Specification, P1386/Draft 2.0 from:

IEEE Standards Department

Copyrights and Permissions

445 Hoes Lanes, P.O. Box 1331

Piscataway, NJ 08855-13 31, USA

PMC Specification, P1386.1/Draft 2.0 from:

IEEE Standards Department

Copyrights and Permissions

445 Hoes Lanes, P.O. Box 1331

Piscataway, NJ 08855-13 31, USA

References

For a detailed description and specification of the CompactPCI bus, please refer to:

CompactPCI Specification PICMG 2.0 R2.1

PCI Industrial Computer Manufactures’ Group

301 Edgewater Place

Suite 220

Wakefield, MA 01880

(617) 224-1100

(617) 224-1239 (FAX)

www.picmg.org

19

VMICPCI-7612 Product Manual

Safety Summary

The following general safety precautions must be observed during all phases of the

operation, service and repair of this product. Failure to comply with these precautions

or with specific warnings elsewhere in this manual violates safety standards of

design, manufacture and intended use of this product.

VMIC assumes no liability for the customer’s failure to comply with these

requirements.

Ground the System

To minimize shock hazard, the chassis and system cabinet must be connected to an

electrical ground. A three-conductor AC power cable should be used. The power

cable must either be plugged into an approved three-contact electrical outlet or used

with a three-contact to two-contact adapter with the grounding wire (green) firmly

connected to an electrical ground (safety ground) at the power outlet.

Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of

any electrical system in such an environment constitutes a definite safety hazard.

Keep Away from Live Circuits

Operating personnel must not remove product covers. Component replacement and

internal adjustments must be made by qualified m aintenance personnel. Do not

replace components with power cable connected. Under certain conditions,

dangerous voltages may exist even with the power cable removed. To avoid injuries,

always disconnect power and discharge circuits before touching them.

Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person capable of

rendering first aid and resuscitation is present.

Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute

parts or perform any unauthorized modification to the product. Return the product to

VMIC for service and repair to ensure that safety features are maintained.

Dangerous Procedure Warnings

Warnings, such as the example below, pr ecede only potentially dangerous procedures

throughout this manual. Instructions contained in the warnings must be followed.

WARNING: Dangerous voltages, capable of causing death, are present in this system.

Use extreme caution when handling, testing and adjusting.

20

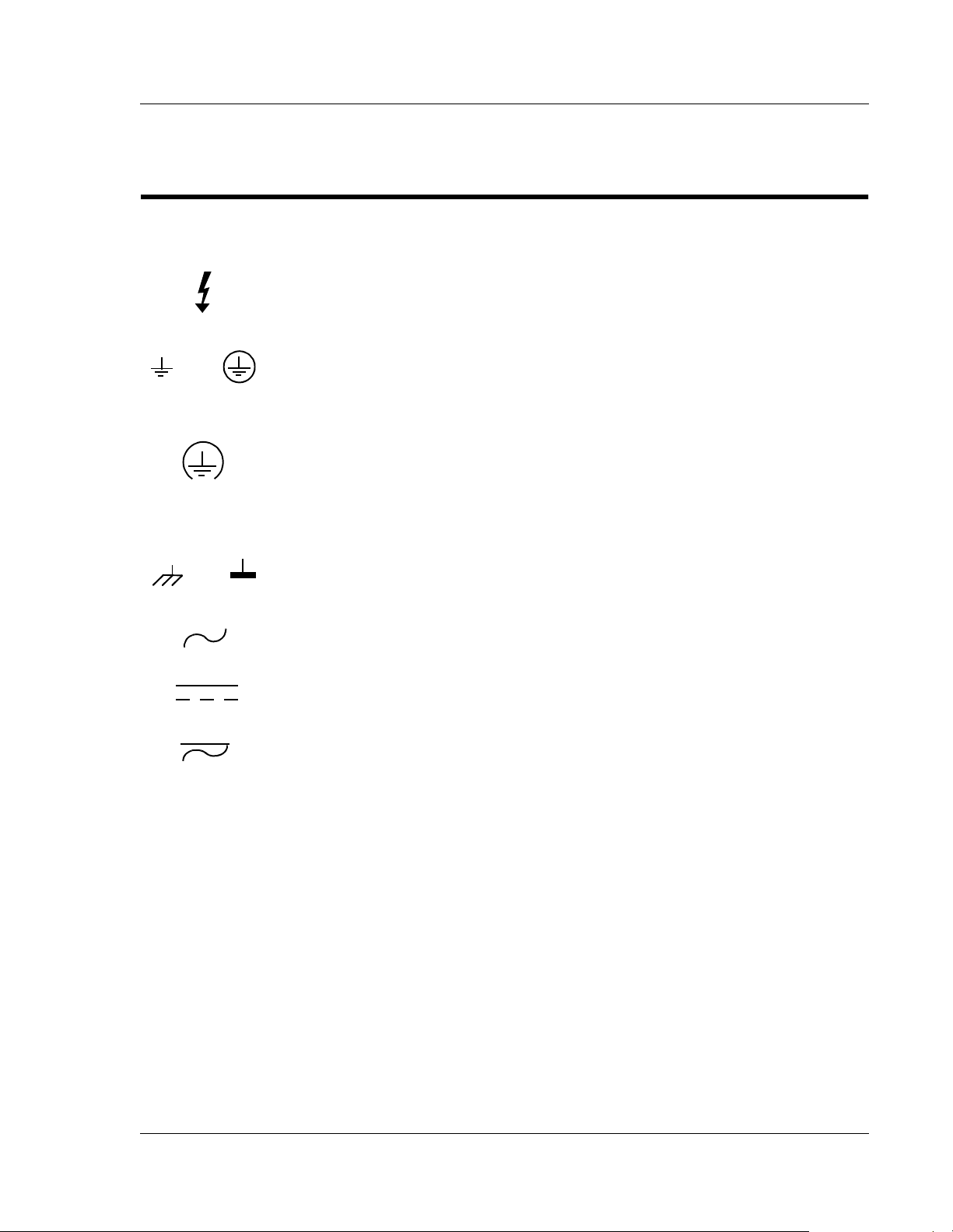

Safety Symbols Used In This Manual

OR

OR

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding

1000 V are so marked).

Protective conductor terminal. For protection against electrical shock in case of a fault.

Used with field wiring terminals to indicate the terminal which must be connected to

ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as

well as providing protection against electrical shock in case of a fault. Before

operating the equipment, terminal marked with this symbol must be connected to

ground in the manner described in the installation (operation) manual.

Frame or chassis terminal. A connection to the frame (ch assis) of the equipment which

normally includes all exposed metal structures.

Safety Symbols Used In This Manual

Alternating current (power line).

Direct current (power line).

Alternating or direct current (power line).

STOP informs the operator that the practice or procedure should not be performed.

Actions could result in injury or death to personnel, or could result in damage to or

destruction of part or all of the system.

WARNING denotes a hazard. It calls attention to a procedure, practice, or condition,

which, if not correctly performed or adhered to, could result in injury or death to

personnel.

CAUTION denotes a hazard. It calls attention to an operating procedure, practice or

condition, which, if not correctly performed or adhered to, could result in damage to

or destruction of part or all of the system.

NOTE denotes important information. It calls attention to a procedure, practice or

condition, which is essential to highlight.

21

VMICPCI-7612 Product Manual

22

VMICPCI-7715 Features and Options

Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

CompactPCI Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

CHAPTER

1

Introduction

The VMICPCI-7715 perfor ms all the functio ns of a st andar d IBM PC /AT motherboard

with the following features:

• Single-slot CompactPCI 6U Eurocard form factor

• Includes a high-performance Intel Pentium III Socket 370 processor

• Up to 512 Mbyte of Synchronous DRAM

• 64-bit PCI SVGA video graphics accelerator

- 4 Mbyte SGRAM Video Memory

- Resolutions up to 1280x1024x256 colors

• Batte ry-backed clock/calendar

• On-board support for a keyboard and mouse, speaker output, Ultra-IDE hard

drive and floppy drive through CPCI J5

• On-board Ethernet controller supporting 10baseT and 100baseTx interfaces

through CPCI J5

• 32k Nonvolatile SRAM

• Three independent 16 bit timers

• Software-controlled Watchdog Timer with reset

• Optional M-Systems DiskOnChip flash memory (24-288 Mbytes)

• PMC expansion site

• On-board support for custom (optional) L VDS DS90C363A T ransmitter through

CPCI J4

• Two serial ports available through CPCI J5

• Two USB ports through CPCI J5

• Smbus access via rear I/O J5 or CPCI J1 connectors

23

1

VMICPCI-7715 Product Manual

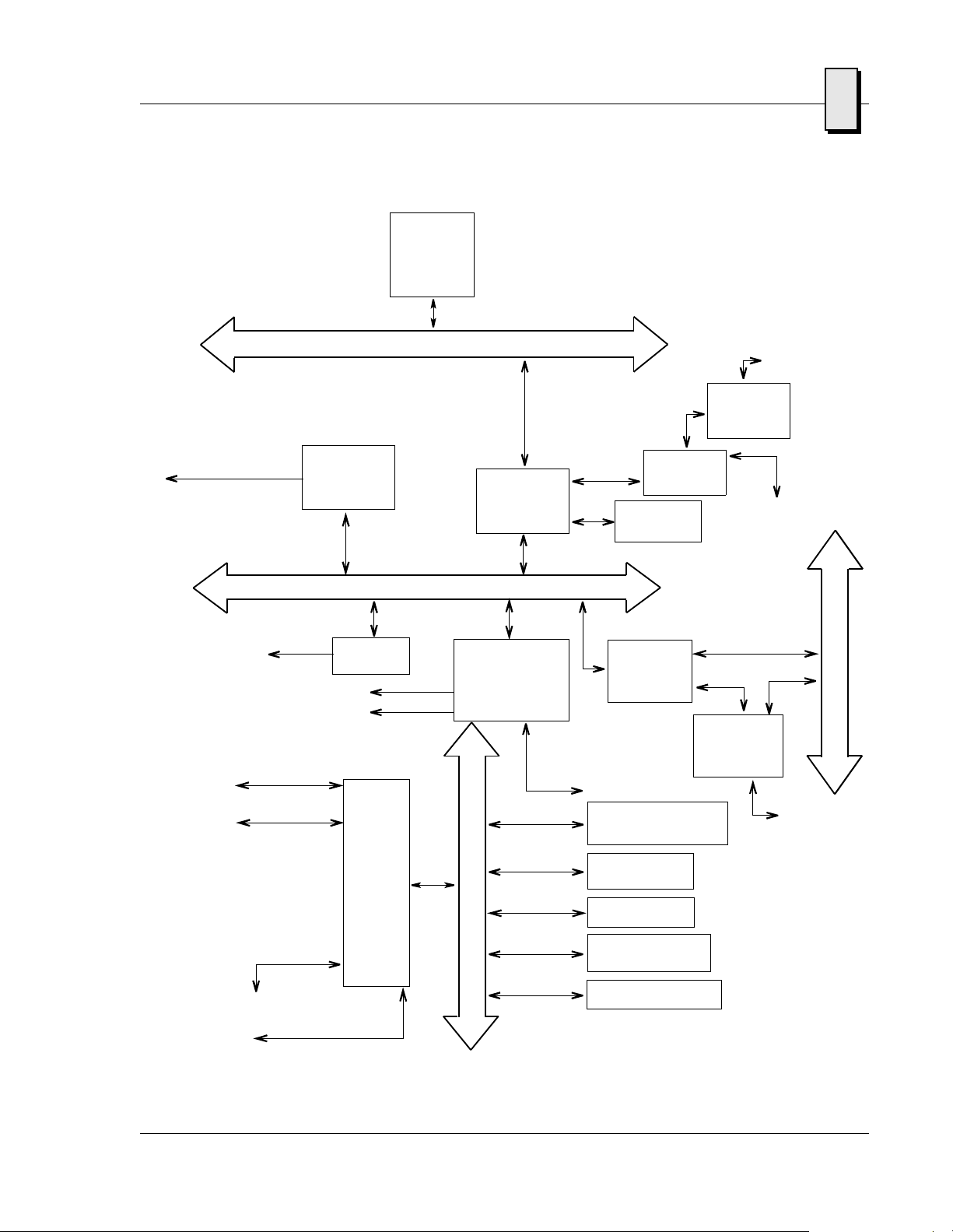

The VMICPCI-7715 supports standard PC/AT I/O features such as those listed in

Table 1-1. Figure 1-1 on page 25 s hows a block diagram of the VMICPCI-7715

emphasizing the I/O features.

Table 1-1 PC/AT I/O Features

I/O FEAT URE IDENTIFIER PHYSICAL ACCESS

Two Serial Ports

(16550-Compatible RS-232C)

Two USB Ports Throug h rear I/O J5

AT-Style Keyboard/Mouse

Controller

Super VGA Video Controller

with 4 Mbyte SGRAM

Ethernet, 10BaseT, 100BaseTx,

Novell NE-2000 Compatible

Floppy Disk Controller

(two drives maximum)

Ultra IDE Fixed Disk Controller

(two drives maximum)

Smbus Port Through rear I/O J5 or CPCI J1

Flat Panel LVDS Transmission

I/O

PMC I/O, 64 bit Through rear I/O J4

Drives A, B Through rear I/O J5

Drives C, D Through rear I/O J5

Throug h rear I/O J5

Throug h rear I/O J5

Throug h rear I/O J4

Throug h rear I/O J5

Throug h rear I/O J4

24

Pentium III

Processor

1

10BaseT/100Base Tx

J5

J5

J5

PMC I/O

J4

COM Port 1

COM Port 2

Floppy Drive

J5

Ethernet

Controller

Intel 82559ER

PMC Site

J5

J5

SUPER

I/O

with

RTC

FDC37C67X

Host bus

PCI bus

USB Port 0

USB Port 1

SMC

North Bridge

System

Controller

82443BX

South Bridge

PCI-to-ISA, IDE

Accelerator

Intel 82371EB (PIIX4E)

EIDE

Hard

Drive

I

S

A

b

u

s

AGP

Graphics

C&T 69030

SDRAM

PCI-to-PCI

Bridge

Intel 21154

J5

DiskOnChip

Socket

Optional

16 Bit Timers

82C54

Flash BIOS

Watchdog Timer

DS1384

Non Volatile SRAM

J4

LVDS

Trans

Custom Option

DS90C363A

Smbus

MUX

Philips PCA9540

J4

SVGA

J5

C

o

m

p

P

C

b

u

a

c

t

I

s

PS/2 Keyboard / Mouse

J5

Figure 1-1 VMICPCI-7715 Block D iag ram

25

1

VMICPCI-7715 Product Manual

CompactPCI Features

In addition to its PC/AT functions, the VMICPCI-7715 has the following CompactPCI

features:

• Single-slot, 6U height CPCI board

• Complies with Revision 2.1 of the PCI Local Bus Specification

• Complies with Revision 1.1 of the PCI-to-PCI Bridge Architecture Specification

(J1 pin B17 and C17 are used for Smbus Clock and Data respectively. J1 pin B17

and C17 are NOT used for SDONE and SB0# respectively.)

• Complies with Revision 2.1 of the CompactPCI Specification

• Implements delayed transactions for all PCI configuration, I/O and memory

read commands-up to three transactions simultaneously in each direction

• Allows 152 bytes of buffering (data and address) for upstream posted memory

write commands and 88 bytes of buffering for downstream posted memory

write commands - up to nine upstream and five downstream posted write

transactions simultaneously

• Allows 152 bytes of read data buffering upstream and 72 bytes of read data

buffering downstream

• Provides concurrent primary and secondary bus operation to isolate traffic

• Provides enhanced address decoding

• Includes addressing and VGA palette snooping support

• Supports PCI transaction forwarding for the following commands

- All I/O and memory commands

- Type 1 to Type 1 configuration commands

- Type 1 to Type 0 configuration commands (downstream only)

- All Type 1 to specia l cycle configuration commands

• Includes downstream lock support

• Supports both 5 and 3.3 V signaling environments

The VMICPCI-7715 is a versatile single-board solution for CPCI con trol with fam iliar

PC/AT operation.

VMICPCI-7715 Product Options

VMIC’s VMICPCI-7715 is built around three fundamental hardware configurations.

These configurations involve processor performance, the D iskOnChip, and SDRAM

memory size. These options are subject to change based on emerging technologies and

availability of vendor configurations.

The options and current details available with the VMICPCI-7715 are defined in the

device specification sheet available from your VMIC representative.

26

CompactPCI Features 1

27

1

VMICPCI-7715 Product Manual

28

Installation and Setup

Contents

Unpacking Procedures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Hardware Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

CHAPTER

2

Introduction

This chapter describes the configurable hardware resister settings, rear I/O

definitions, installation, system setup and operation of the VMICPCI-7715.

Unpacking Procedures

Any precautions found in the shipping container should be observed. All items

should be carefully unpacked and thoroughly inspected for damage that might have

occurred during shipment. All claims arising from shipping damage sho uld be f iled

with the carrier and a complete report sent to VMIC Customer Service along with a

request for advice concerning the disposition of the damaged item(s).

CAUTION: Some of the components assembled on VMIC’s products may be sensitive

to electrostatic discharge, and damage may occur on boards that are subjected to a

high energy electrostatic field. When the board is placed on a bench for configuring,

etc., it is suggested that conductive material be inserted under the board to provide a

conductive shunt. Unused boards should be stored in the same protective boxes in

which they were shipped.

29

2

VMICPCI-7715 Product Manual

Hardware Setup

The VMICPCI-7715 is factory populated with user-specified options as part of the

VMICPCI-7715 ordering information. The CPU speed, SDRAM and DiskOnChip size

are not user-upgradable. To change these options, contact customer service to receive

a Return Material Authorization (RMA).

VMIC Customer Service is available at: 1-800-240-7782.

Or E-mail us at customer.s ervice@vmic.com

The VMICPCI-7715 is tested for system operation and shipped with factory-installed

configurable jumpers. The physical location of the jumpers for the SBC are illustrated

in Figure 2-1 on page 31. The definitions of the SBC board jumpers are included in

Table 2-2 through Table 2-6.

CAUTION: All jumpers are factory configured and should not be modified by the

user. There are four exceptions: the Password Clear (E24), the Watchdog Timer (E27),

Battery jumpers (E22 and E23) and Timer Clock Select (E28).

Modifying any other jumper will void the Warranty and may damage the unit. The

default jumper condition of the VMICPCI-7715 is expressed in Table 2-1 through

Table 2-5 with bold text in the table cells.

30

Located On

Reverse Side

Hardware Setup

2

Figure 2-1 VMICPCI-7715 Board Jumper Locations

31

2

VMICPCI-7715 Product Manual

Table 2-1 Board Connectors

Connector Function

CPCI J5 PS/2 Keyboard and Mouse, Smbus,

USB0 1, Ethernet, COM1, COM2, Floppy

Drive, IDE Harddrive

CPCI J4 PMC I/O, VGA Video, LVDS Video

.

Table 2-2 Watchdog Timer Select (User Configurable) - Jumper (E27)

Select Jumper Position

Watchdog Timer

RESET 1-2

NMI 2-3

No RESET or NMI Out

Table 2-3 BIOS Mode Option - Resister (R409)

Select Resister Position

No Boot Block Programming Out

Boot Block Programming In

NOTE: The VMICPCI-7715’s BIOS has the capability (Default: Disabled) of password

protecting casual access to the unit’s CMOS set-up screens. The Password Clear

jumper (E24) allows for a means to clear the password feature, which might be

necessary in the case of a forgotten password.

To clear the CMOS:

1. Turn off power to the unit.

2. Install a jumper at E24.

32

3. Power up the unit.

4. Turn off the power to the unit and remove jumper E24.

When power is re-applied to the unit, the CMOS will be cleared.

Table 2-4 Password Clear (User Configurable) - Jumper (E24)

Jumper Position

Normal Out

Clear CMOS/Password In

Table 2-5 CMOS Battery Enable (User Configurable) - Jumper (E23)

Jumper Position

CMOS Battery Disabled Out

CMOS Battery Enabled In

Hardware Setup

2

Table 2-6 Watchdog Battery Enable (User Configurable) - Jumper (E22)

Jumper Position

Watchdog Battery Disa bled Out

W atchdog Batte ry Enabled In

Table 2-7 Clock Select (User Configurable) - Jumper (E28)

Jumper Pos ition

1 MHz Out

2 MHz In

33

2

VMICPCI-7715 Product Manual

Installation

The VMICPCI-7715 conforms to the CompactPCI physical specification for a 6U

board. The VMICPCI-7715 is a system slot only board. It can be plugged directly into

any standard chassis accepting this type of board. The following pictures illustrate the

symbols used to identify the slots in a standard CPCI chassis.

This symbol identifies the System Controller slot

This symbol identifies peripheral slot

CAUTION: Do not install or remove the board while power is applied.

The following steps describe the VMIC recommended method for installation and

powerup of the VMICPCI-7715:

1. Make sure power to the equipment is off.

2. If a PMC module such as VMIC’s VMIPMC-7441 is to be used, connect it to the

VMICPCI-7715 prior to board installation. Refer to the Product Manual for that

particular board for configuration and setup.

3. The VMICPCI-7715 must be installed in the designated system slot of the CompactPCI backplane.

NOTE: The VMICPCI-7715 requires forced air cooling. It is advisable to install blank

panels over any exposed slots. This will allow for better ai r flow o ver the board.

4. Insert the VMICPCI-7715 into the CompactPCI ch assis system slot. While

ensuring that the board is properly aligned and oriented in the supporting boar d

guides, slide the board smoothly forward against the mating connector. Use the

ejector handles to firmly seat the board.

5. The VMICPCI-7715 features a DiskOnChip resident on the board. Refer to

Chapter 4 for set up details.

6. If an external drive module is installed, the BIOS Setup program must be run to

configure the drive types. See Appendix B to properly configure the system.

7. If a drive module is present, install the operating system according to the

manufacturer’s instructions.

34

8. A keyboard/mouse are required if the system has not been previously configured.

BIOS Setup

The VMICPCI-7715 has an on-board BIOS Setup program that controls many

configuration options. These options are saved in a special nonvolatile,

battery-backed memory chip and are collectively referred to as the board’s “CMOS

configuration.” The CMOS configura tion controls many details concerning the

behavior of the hardware from the moment power is applied.

The VMICPCI-7715 is shipped from the factory with no hard drives configured in

CMOS. The BIOS Setup program must be run to configure the specific drives

attached.

Details of the VMICPCI-7715 BIOS setup program are included in Appendix C.

PMC Expansion Site Co nnecto rs

The VMICPCI-7715 supplies PMC expansion site connectors for adding a PMC

expansion board. This expansion capability allows third-party devices to be used with

the VMICPCI-7715, as shown in Figure 2-2.

Installation

2

VMICPCI-7715

*There are 64 bits connected to the PMC I/O through J4

Figure 2-2 PCI Expansion Site

PCI

PMC I/O*

CompactPCI

PMC Expansion

Site

Power

Only

35

2

VMICPCI-7715 Product Manual

36

PC/AT Functions

Contents

CPU Socket. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Physical Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Memory and Port Maps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

PC/AT Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

PCI Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

I/O Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Video Graphics Adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Ethernet Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

CHAPTER

3

Introduction

The VMICPCI-7715 provides a complete Pentium III processor-based Single Board

Computer (SBC). The design includes a high-speed microprocessor with current

technology memory .

Because the design is PC/AT compatible, it retains standard PC memory and I/O

maps along with standard interrupt architecture. Furthermore, the VMICPCI-7715

includes a PCI-compatible video adapter and Ethernet controller.

The following sections describe in detail the PC/AT functions of the VMICPCI-7715.

37

3

VMICPCI-7715 Product Manual

CPU Socket

The VMICPCI-7715 CPU socket is factory populated with a high-speed Pentium

III processor. The CPU type or speed, SDRAM size and DiskOnChip size are

user-specified as part of the VMICPCI-7 715 o r dering information. The options are not

user-upgradable.

To change CPU type or speeds, SDRAM size or DiskOnChip size contact VMIC

customer service to obtain a Return Material Authorization (RMA).

VMIC Customer Service is available at: 1-800-240-7782.

Or E-mail us at customer.s ervice@vmi c.com

Physical Memory

The VMICPCI-7715 provides 512 Mbytes of Synchronous DRAM (SDRAM) as

on-board system memory. Memory can be accessed as bytes, words or longwords.

All RAM on the VMICPCI-7715 is dual-ported to the CompactPCI bus through the

PCI-to-PCI bridge. The memory is addressable by the local processor, as well as the

CompactPCI bus slave interface by another CompactPCI master. Caution must be

used when sharing memory between the local processor and the CompactPCI bus to

prevent a CompactPCI bus master from overwriting the local processor’s operating

system.

The VMICPCI-7715 includes the system BIOS, and video BIOS in a single flash

memory device.

The VMICPCI-7715 is also a vail able wi th an opti onal MS yst ems D iskO nChip f lash up

to 288 Mbytes.

38

Memory and Port Maps

Memory Map

The memory map for the VMICPCI-7715 is shown in Table 3-1. All systems share this

same memory map, although a VMICPCI-7715 with less than the full 512 Mbyte of

SDRAM does not fill the entire space reserved for On-Board Extended Memory.

Table 3-1 VMICPCI-7715, Interface Memory Address Map

Memory and Port Maps

3

MODE

PROTECTED MODE

REAL MODE

* This space can be used to set up protected mode PCI-to-CompactPCI bus windows (also referred

to as PCI slave images).

** This space can be allocated as shared memory (for example, between the processor-based CPU

and CompactPCI bus Master). Note, that if a PMC board is loaded, the expansion BIOS may be

placed in this area.

MEMORY ADDRESS

RANGE

$FFFF 0000 - $FFFF FFFF 64 Kbyte ROM BIOS Image

$0400 0000 - $FFFE FFFF 3.9 Gbyte Unused *

$0010 0000 - $0FFF FFFF 255 Mbyte Reserved for **

$E0000 - $FFFF F 138 Kbytes ROM BIOS

$D8010 - $DFFFF 32Kbytes

$D800E - $D800F 2 Kbyte Board ID

$D8000 - $D800D 14 bytes RTC/Watchdog Timer Control

$C8000 - $D7FFF 64 Kbyte LANWorks BIOS

$C0000 - $C7F FF 32 Kbyte Video ROM

$A0000 - $BFFFF 128 Kbyte Video RAM

$00000 - $9FFFF 640 Kbyte User RAM/DOS RAM

SIZE DESCRIPTION

On-Board Extended Memory

(not filled on all systems)

Non-volatile SRAM

minus 16 bytes

Registers

I/O Port Map

The Pentium III processor-based CPU includes special input/output instructions that

access I/O peripherals residing in I/O addressing space (separate and distinct from

memory addressing space). Locations in I/O address space are referred to as ports.

When the CPU decodes and executes an I/O instruction, it produces a 16-bit I/O

address on lines A00 to A15 and identifies the I/O cycle to the processor’s M/I/O

control line. Thus, the CPU includes an independent 64 Kbyte I/O address space,

which is accessible as bytes, words or longwords.

39

3

VMICPCI-7715 Product Manual

Standard PC/AT hardware circuitry reserves only 1,024 bytes of I/O addressing

space from I/O $000 to $3FF for peripherals. All standard PC I/O peripherals such as

serial and parallel ports, hard and floppy drive controllers, video system, real-time

clock, system timers, and interrupt controllers are addressed in this region of I/O

space. The BIOS initializes and configures all these registers properly; adjusting these

I/O ports directly is not normally necessar y.

The assigned and user-available I/O addresses are summarized in the I/O Address

Map, Table 3-2.

Table 3-2 VMICPCI-7715 I/O Address Map

I/O ADDRESS

RANGE

$000 - $00F 16 DMA Controller 1

$010 - $01F 16 Reserved

$020 - $021 2 Master Interrupt Controller

$022 - $03F 30 Reserved

$040 - $043 4 Programmable Timer

$044 - $05F 30 Reserved

$060 - $064 5 Keyboard, Speaker, Eqpt. Configuration

$065 - $06F 11 Reserved

$070 - $071 2 Real-Time Clock, NMI Mask

$072 - $07F 14 Reserved

$080 - $08F 16 DMA Page Registers

$090 - $091 2 Reserved

SIZE IN

BYTES

HW DEVICE PC/AT FUNCTION

(Intel 8237A Compatible)

(Intel 8259A Compatible)

(Intel 8254 Compatible)

(Intel 8042 Compatible)

40

$092 1 Alt. Gate A20/Fast Reset Register

$093 1 Reserved

$094 1 Super VGA Chip POS102 Access Control Register

$095 - $09F 11 Reserved

$0A0 - $0A1 2 Slave Interrupt Controller

(Intel 8259A Compatible)

$0A2 - $0BF 30 Reserved

$0C0 - $0DF 32 DMA Controller 2

(Intel 8237A Compatible)

Memory and Port Maps

Table 3-2 VMICPCI-7715 I/O Address Map (Continued)

3

I/O ADDRESS

RANGE

$0E0 - $16F 142 Reserved

$170 - $177 8 PIIX4E Secondary Hard Disk Controller

$178 - $1EF 120 User I/O

$1F0 - $1F7 8 PIIX4E Primary Hard Disk Controller

$1F8 - $277 128 User I/O

$278 - $27F 8 Super I/O Chip* LPT2 Para llel I/O*

$280 - $2E7 104 Reserved

$2E8 - $2EE 7 UART* COM4 Serial I/O*

$2EF - $2F7 9 User I/O

$2F8 - $2FE 7 Super-I /O C hip COM2 Serial I/O (16550 Compatible)

$2FF - $36F 113 Reserved

$370 - $377 8 Super-I/O Chip Secondary Floppy Disk Controller

$378 - $37F 8 Super-I/O Chip LPT1 Para llel I/O

$380 - $3E7 108 Reserved

$3E8 - $3EE 7 UART* COM3 Serial I/O*

SIZE IN

BYTES

HW DEVICE PC/AT FUNCTION

$3F0 - $3F7 8 Super-I/O Chip Primary Floppy Disk Controller

$3F8 - $3FE 7 Super-I /O Chip COM1 Serial I/O (16550 Compatible)

$3FF - $4FF Reserved

$500 - $503 4 82C54 Timer Programmable Internal Timer

$504 - $CFF Reserved

* While these I/O ports are reserved for the listed functions, they are not implemented on

the VMICPCI-7715. They are listed here to make the user aware of the standard

PC/AT usage of these ports.

PCI-to-PCI Bridge

The VMICPCI-7715 uses the Intel 21154 PCI-to-PCI bridge to interface between the

primary PCI bus of the unit and the CompactPCI (CPCI) bus. The CompactPCI bus

appears as a secondary PCI bus, and all devices in the seven peripheral slots of the

CPCI chassis are auto detected by the BIOS and respond to normal PCI accesses.

41

3

VMICPCI-7715 Product Manual

PC/AT Interrupts

In addition to an I/O port address, an I/O device has a separate hardware interrupt

line assignment. Assigned to each interrupt line is a corresponding interrupt vector in

the 256-vector interrupt table at $00000 to $003FF in memory. The 16 maskable

interrupts and the single Non-Maskable Interrupt (NMI) are listed in Table 3-3 along

with their functions. Table 3-4 on page 43 details the vectors in the interrupt vector

table. The interrupt number in HEX and decimal are also defined for real and

protected mode in Table 3-4.

The interrupt hardware implementation on the VMICPCI-7715 is standard for

computers built around the PC/AT architecture, which evolved fr om the IBM PC/XT.

In the IBM PC/XT computers, only eight interrupt request lines exist, numbered fr o m

IRQ0 to IRQ7 at the PIC. The IBM PC/AT computer added eight more IRQx lines,

numbered IRQ8 to IRQ15, by cascading a second slave PIC into the original master

PIC. IRQ2 at the master PIC was committed as the cascade input from the slave PIC.

This architecture is represented in Figure 3-1 on page 47.

To ma intain backward compatibility with PC/XT systems, IBM chose to use the new

IRQ9 input on the slave PIC to operate as the old IRQ2 interrupt line on the PC/XT

Expansion Bus. Thus, in AT systems, the IRQ9 interrupt line connects to the old IRQ2

pin (pin B4) on the AT Expansion Bus (or ISA bus).

Table 3-3 PC/AT Hardware Interrupt Line Assignments

IRQ AT FUNCTION COMMENTS

NMI Parity Errors

(Must be enabled in BIOS Setup)

0 System Timer Set by BIOS Setup

1 Keyboard Set by BIOS Setup

2 Duplexed to IRQ9

3 COM2/COM4

4 COM1/COM3

5 General Purpose Timer Assigned to On-Board Timer

6 Floppy Controller

7 Not Assigned Determined by BIOS

8 Real-Time Clock

9USB

Used by VMICPCI-7715

CompactPCI bus Interface

42

PC/AT Interrupts

Table 3-3 PC/AT Hardware Interrupt Line Assignments (Continued)

IRQ AT FUNCTION COMMENTS

10 Not Assigned Determined by BIOS

11 Not Assigned Determined by BIOS

12 Mouse

13 Math Coprocessor

14 AT Hard Drive

15 Not Assigned Determined by BIOS

Table 3-4 PC/AT Interrupt Vector Table

3

INTERRUPT NO.

HEX DEC

00 0 Divide Error Same as Real Mode

01 1 Debug Single Ste p Same as Real Mode

02 2 NMI Memory Parity Error Same as Real Mode

03 3 Debug Breakpoint Same as Real Mode

04 4 ALU Overflow Same as Real Mode

05 5 Print Screen Array Bounds Check

06 6 Invalid OpCode

07 7 Device Not A v ailable

08 8 IRQ0 Timer Tick Double Exception Detected

09 9 IRQ1 Keyb oar d Input Coprocessor Segment Overrun

0A 10 IRQ2 BIOS Reserved Invalid Task State Segment

0B 11 IRQ3 COM2 Serial I/O Segment Not Present

0C 12 IRQ4 COM1 Serial I/O Stack Segment Overrun

IRQ

LINE

REAL MODE PROTECTED MODE

(Must be enabled in BIOS Setup)

0D 13 IRQ5

0E 14 IRQ6 Floppy Disk Controller Page Fault

0F 15 IRQ7 Assigned by BIOS

43

3

VMICPCI-7715 Product Manual

Table 3-4 PC/AT Interrupt Vector Table (Continued)

INTERRUPT NO.

HEX DEC

10 16 BIOS Video I/O Coprocessor Error

11 17 Eqpt Configuration Check Same as Real Mode

12 18 Memory Size Check Same as Real Mode

13 19 XT Floppy/Hard Drive Same as Real Mod e

14 20 BIOS Comm I/O Same as Real Mode

15 21 BIOS Cassette Tape I/O Same as Real Mode

16 22 BIOS Keyboard I/O Same as Real Mode

17 23 BIOS Printer I/O Same as Real Mode

18 24 ROM BASIC Entry Point Same as Real Mode

19 25 Bootstrap Loader Same as Real M ode

1A 26 IRQ8 Real-Time Clock Same as Real Mode

1B 27 Control/Break Handler Same as Real Mode

1C 28 Timer Control Same as Real Mode

IRQ

LINE

REAL MODE PROTECTED MODE

1D 29 Video Parameter Table Pntr Same as Real Mode

1E 30 Floppy Parm Table Pntr Same as Real Mode

1F 31 Video Graphics Table Pntr Same as Real Mode

20 32 DOS Terminate Program Same as Real Mode

21 33 DOS Function Entry Point Same as Real Mode

22 34 DOS Terminate Handler Same as Real Mode

23 35 DOS Control/Break Handler Same as Real Mod e

24 36 DOS Critic al Error Handler Same as Real Mode

25 37 DOS Absolute Disk Read Same as Real Mode

26 38 DOS Absolute Disk Write Same as Real Mode

27 39 DOS Program Terminate,

Stay Resident

28 40 DOS Keyboard Idle Loop Same as Real Mod e

29 41 DOS CON Dev. Raw Output Same as Real Mode

Same as Real Mode

44

Table 3-4 PC/AT Interrupt Vector Table (Continued)

PC/AT Interrupts

3

INTERRUPT NO.

HEX DEC

2A 42 DOS 3.x+ Network Comm Same as Real Mode

2B 43 DOS Internal Use Same as Real Mode

2C 44 DOS Internal Use Same as Re al Mode

2D 45 DOS Internal Use Same as Real Mode

2E 46 DOS Internal Use Same as Real Mode

2F 47 DOS Print Spooler Driver Same as Real Mode

30-60 48-9 6 R eserved by DOS Same as Real Mo de

61-66 97-1 02 User Available Same as Real Mode

67-70 103- 112 Reserved by DOS Same as Real Mode

71 113 IRQ 9 USB

72 114 IRQ10 Assigned by BIOS

73 115 IRQ11 Assigned by BIOS

74 116 IRQ12 Mouse

IRQ

LINE

REAL MODE PROTECTED MODE

75 117 IRQ13 Math Coprocessor

76 118 IRQ14 AT Hard Drive

77 119 IRQ15 Assigned by BIOS

78-7F 120-127 Reserved by DOS Same as Real M ode

80-F0 128-240 Reserved for BASIC Same as Real Mode

F1-FF 241-255 Reserved by DOS Same as Real Mo de

45

3

VMICPCI-7715 Product Manual

PCI Interrupts

Interrupts on Peripheral Component Interconnect (PCI) Local Bus are optional and

defined as “level sensitive,” asserted low (negative true), using open drain output

drivers. The assertion and de-assertion of an interrupt line, INTx#, is asynchronous to

CLK. A device asserts its INTx# line when requesting attention from its device driver.

Once the INTx# signal is asserted, it remains asserted until the device driver clears the

pending request. When the request is cleared, the device de-asserts its INTx# signal.

PCI defines one interrupt line for a single function device, and up to four interrupt

lines for a multifunction device or connector. For a single function device, only INTA#

may be used while the other three interrupt lines have no meaning. Figure 3-1 on

page 47 depicts the VMICPCI-7715 interrupt logic pertaining to CompactPCI bus

operations and the PCI expansion site.

Any function on a multifunction device can be connected to any of the INTx# lines.

The Interrupt Pin register defines which INTx# line the function uses to request an

interrupt. If a device implements a single INTx# line, it is called INTA#; if it

implements two lines, they are called INTA# and INTB#; and so forth. For a

multifunction device, all functions may use the same INTx# line, or each may have its

own (up to a maximum of four functions), or a ny combination thereof. A single

function can not generate an interrupt request on more than one INTx# line.

Table 3-5 NMI Register Bit Descriptions

Status Control Register

(I/O Address $061, Read/Write, Read Only)

SERR# NMI Source Status (Read Only) - This bit is set to 1 if a system board agent