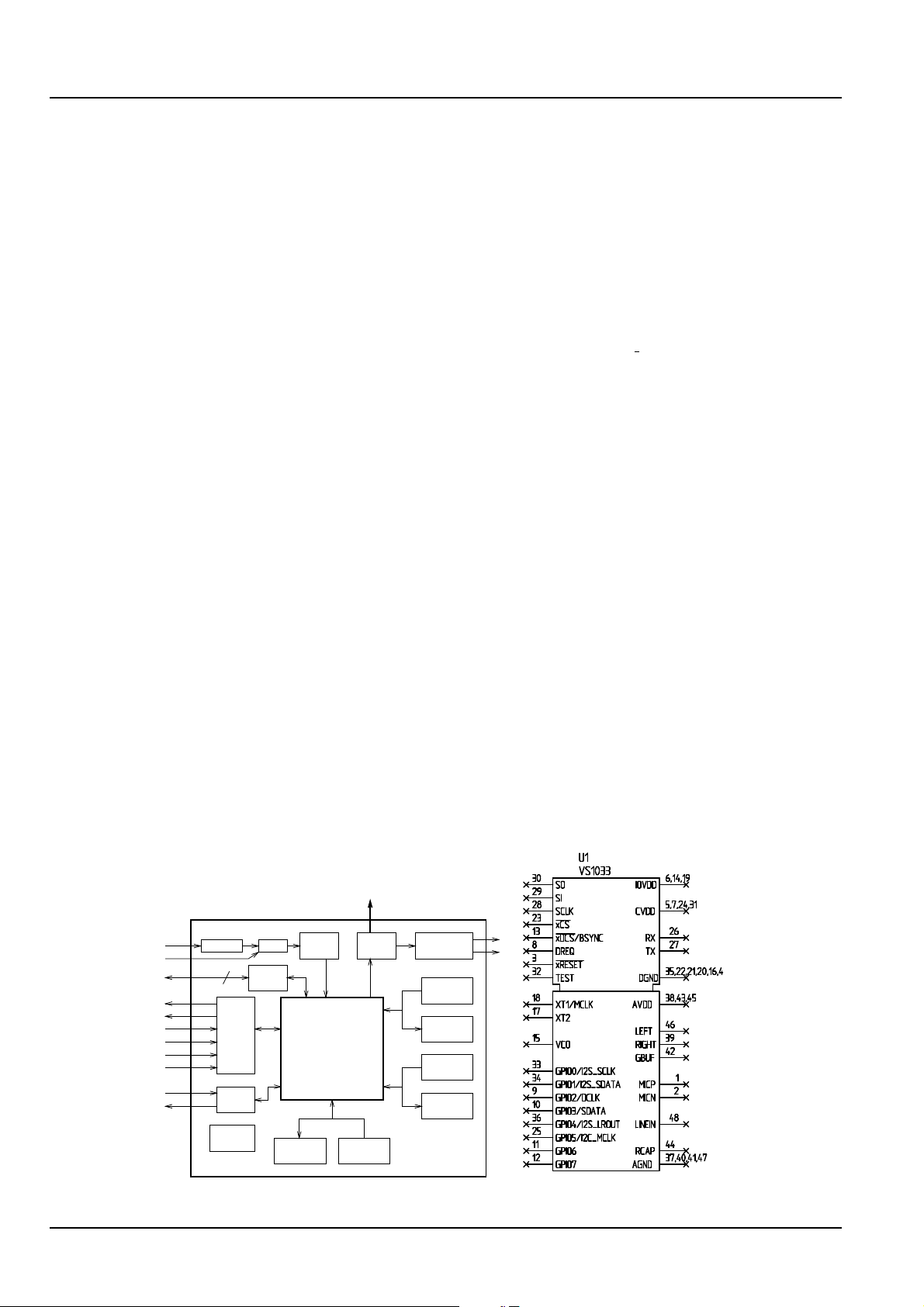

VLSI VS1033C, VS1033 Datasheet

VS1033c PRELIMINARY

Instruction

RAM

Instruction

ROM

Stereo

DAC

Mono

ADC

L

R

UART

Serial

Data/

Control

Interface

Stereo Ear−

phone Driver

DREQ

SO

SI

SCLK

XCS

RX

TX

audio

output

X ROM

X RAM

Y ROM

Y RAM

GPIO

GPIO

VSDSP

4

XDCS

MIC AMP

Clock

multiplier

MUX

line

audio

mic

audio

8

I2S

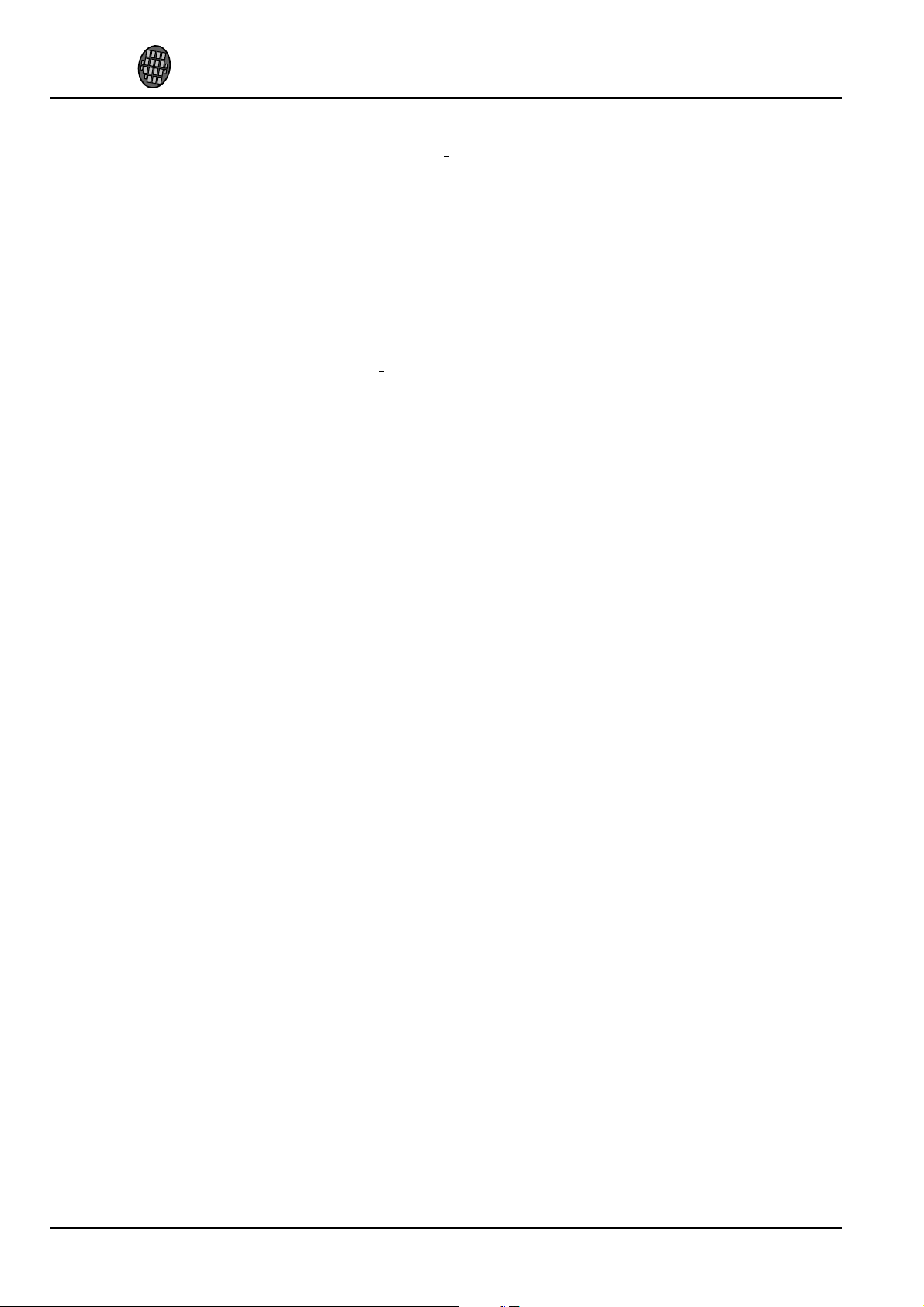

VS1033

VS1033 - MP3/AAC/WMA/MIDI

AUDIO CODEC

VS1033C

Features

• Decodes MPEG 1 & 2 audio layer III (CBR

+VBR +ABR); layers I & II optional;

MPEG4/2 AAC-LC-2.0.0.0 (+PNS);

WMA 4.0/4.1/7/8/9allprofiles (5-384 kbps);

WAV (PCM + IMA ADPCM);

General MIDI / SP-MIDI format 0 files

• Encodes IMA ADPCM from microphone

or line input

• Streaming support for MP3 and WAV

• EarSpeaker Spatial Processing

• Bass and treble controls

• Operates with a single clock 12..13 MHz

• Can also be used with 24..26 MHz clocks

• Internal PLL clock multiplier

• Low-power operation

• High-quality on-chip stereo DAC with no

phase error between channels

• Stereo earphone driver capable of driving a

30Ω load

• Quiet power-on and power-off

• I2S interface for external DAC

• Separate operating voltages for analog,

digital and I/O

• 5.5 KiB On-chip RAM for user code / data

• Serial control and data interfaces

• Can be used as a slave co-processor

• SPI flash boot for special applications

• UART for debugging purposes

• New functions may be added with software

and 8 GPIO pins

• Lead-free RoHS-compliantpackage(Green)

Description

VS1033 is a single-chip MP3/AAC/WMA/MIDI

audio decoder and ADPCM encoder. It contains

a high-performance, proprietary low-power DSP

processor core VS DSP4, working data memory,

5 KiB instruction RAM and 0.5 KiB data RAM

for user applications, serial control and input data

interfaces, upto 8 general purpose I/O pins, an

UART, as well as a high-quality variable-samplerate mono ADC and stereo DAC, followed by an

earphone amplifier and a common voltage buffer.

VS1033 receives its input bitstream through a serial input bus, which itlistenstoasasystemslave.

The input stream is decoded and passed through a

digital volume control to an 18-bit oversampling,

multi-bit, sigma-delta DAC. The decoding is controlled via a serial control bus. In addition to the

basic decoding, it is possible to add application

specific features,likeDSP effects, to theuserRAM

memory.

EarSpeaker spatial processing provides more natural sound in headphone listening conditions. It

widens the stereo image and positions the sound

sources outside the listener’s head.

Version 0.91, 2007-02-12 1

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

CONTENTS

Contents

1 Licenses 9

2 Disclaimer 9

3 Definitions 9

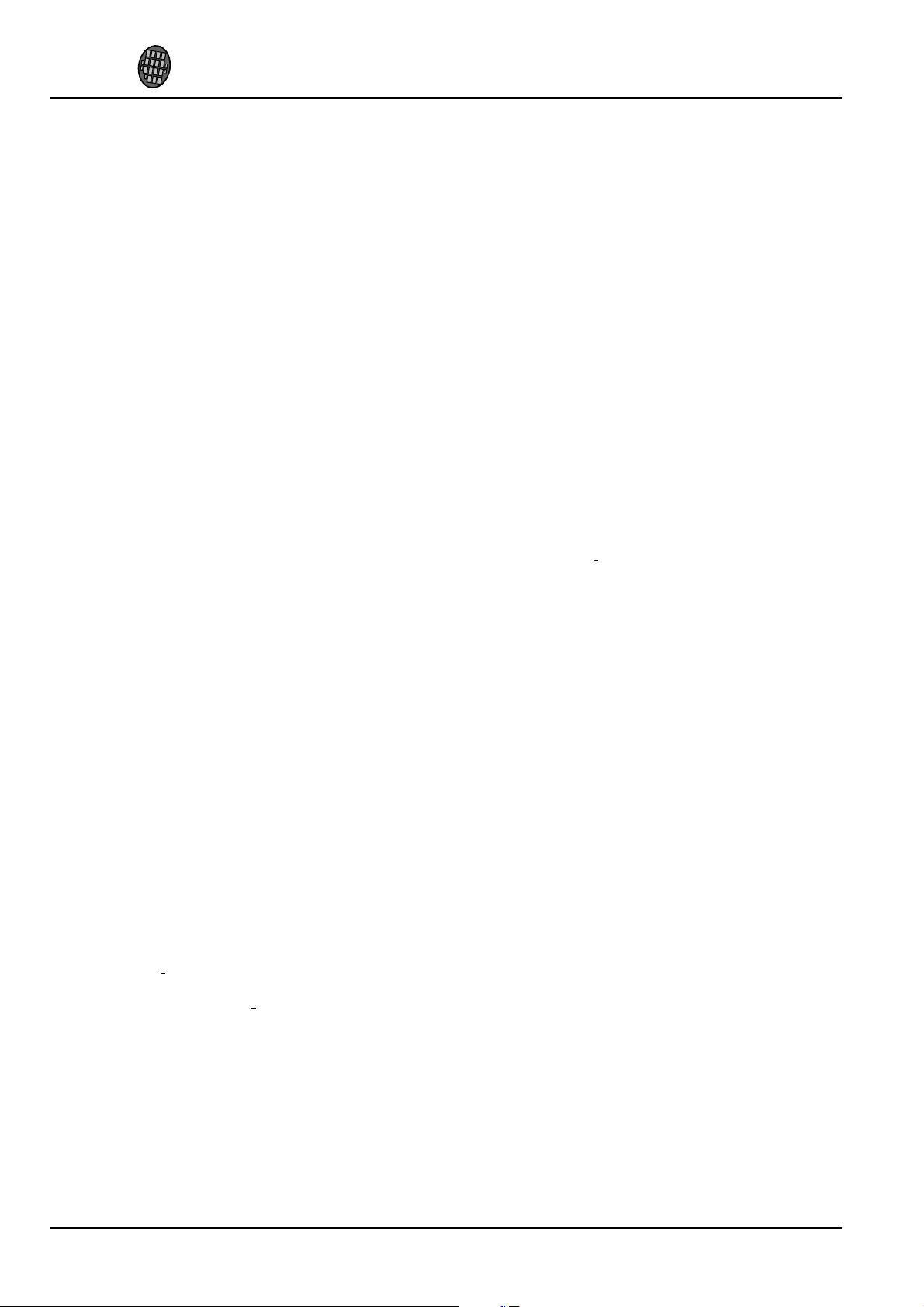

4 Characteristics & Specifications 10

4.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.3 Analog Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.4 Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.5 Digital Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.6 Switching Characteristics - Boot Initialization . . . . . . . . . . . . . . . . . . . . . . . 12

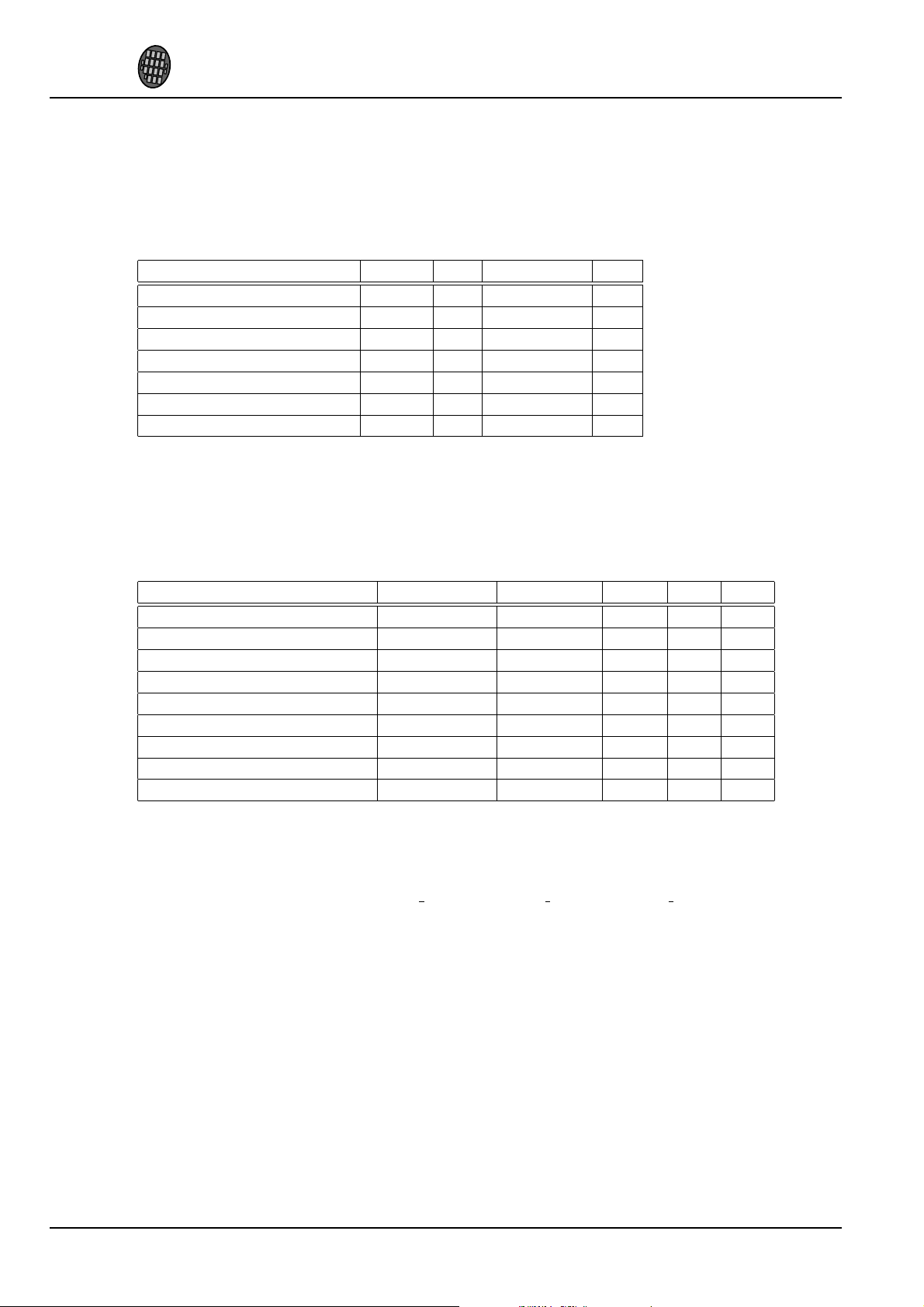

5 Packages and Pin Descriptions 13

5.1 Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.1.1 LQFP-48 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.1.2 BGA-49 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.2 LQFP-48 and BGA-49 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . 14

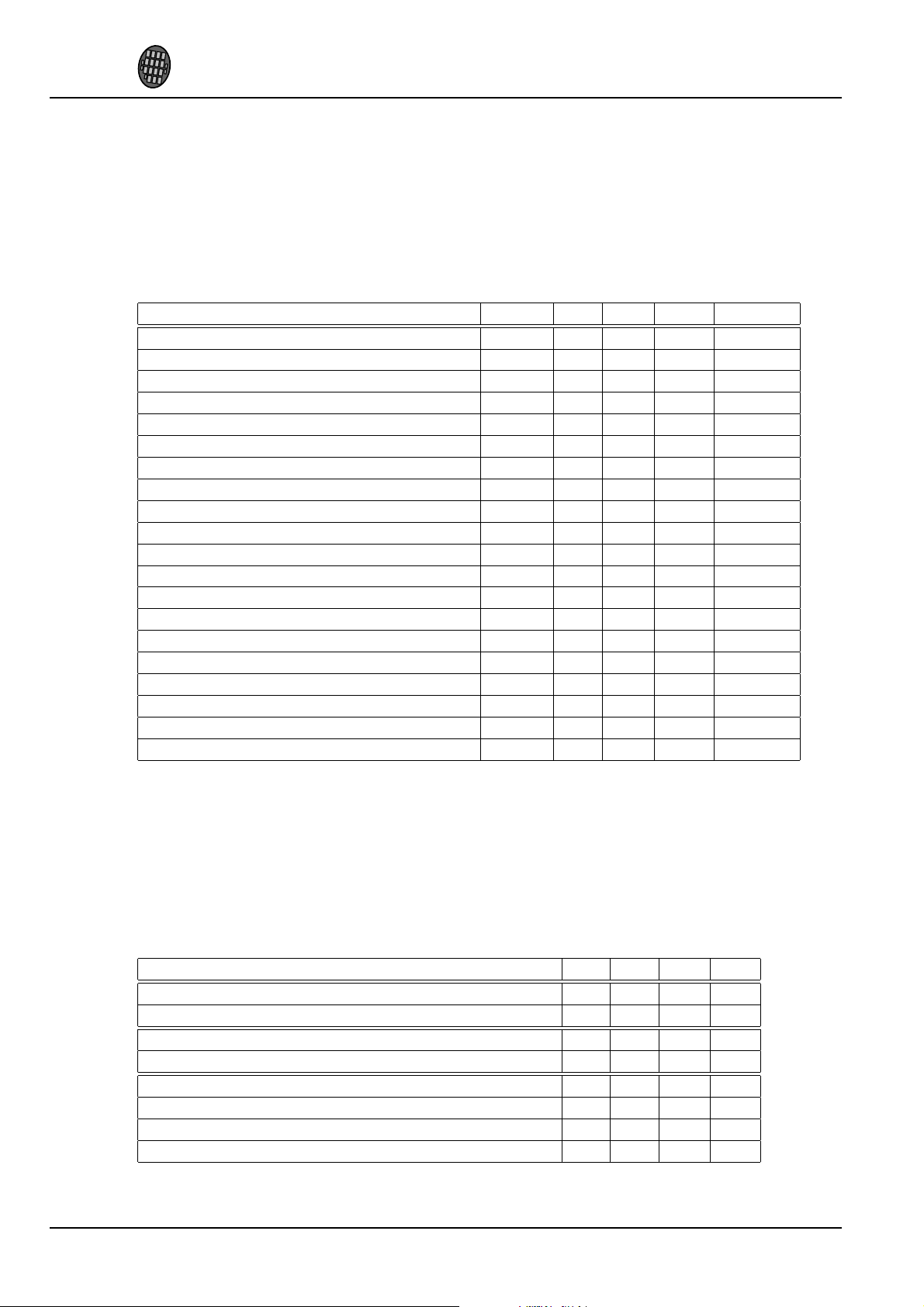

6 Connection Diagram, LQFP-48 16

7 SPI Buses 17

7.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Version 0.91, 2007-02-12 2

7.2 SPI Bus Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

7.2.1 VS1002 Native Modes (New Mode) . . . . . . . . . . . . . . . . . . . . . . . . 17

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

7.2.2 VS1001 Compatibility Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

7.3 Data Request Pin DREQ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

7.4 Serial Protocol for Serial Data Interface (SDI) . . . . . . . . . . . . . . . . . . . . . . . 18

7.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

7.4.2 SDI in VS1002 Native Modes (New Mode) . . . . . . . . . . . . . . . . . . . . 18

7.4.3 SDI in VS1001 Compatibility Mode . . . . . . . . . . . . . . . . . . . . . . . . 19

7.4.4 Passive SDI Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

7.5 Serial Protocol for Serial Command Interface (SCI) . . . . . . . . . . . . . . . . . . . . 19

7.5.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

CONTENTS

7.5.2 SCI Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.5.3 SCI Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.6 SPI Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

7.7 SPI Examples with SM SDINEW and SM SDISHARED set . . . . . . . . . . . . . . . 22

7.7.1 Two SCI Writes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.7.2 Two SDI Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.7.3 SCI Operation in Middle of Two SDI Bytes . . . . . . . . . . . . . . . . . . . . 23

8 Functional Description 24

8.1 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

8.2 Supported Audio Codecs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

8.2.1 Supported MP3 (MPEG layer III) Formats . . . . . . . . . . . . . . . . . . . . 24

Version 0.91, 2007-02-12 3

8.2.2 Supported MP1 (MPEG layer I) Formats . . . . . . . . . . . . . . . . . . . . . 25

8.2.3 Supported MP2 (MPEG layer II) Formats . . . . . . . . . . . . . . . . . . . . . 25

8.2.4 Supported AAC (ISO/IEC 13818-7) Formats . . . . . . . . . . . . . . . . . . . 26

8.2.5 Supported WMA Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

8.2.6 Supported RIFF WAV Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

8.2.7 Supported MIDI Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.3 Data Flow of VS1033 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

8.4 EarSpeaker Spatial Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

8.5 Serial Data Interface (SDI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

8.6 Serial Control Interface (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

8.7 SCI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

8.7.1 SCI MODE (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

8.7.2 SCI STATUS (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

CONTENTS

8.7.3 SCI BASS (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

8.7.4 SCI CLOCKF (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

8.7.5 SCI DECODE TIME (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.7.6 SCI AUDATA (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.7.7 SCI WRAM (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.7.8 SCI WRAMADDR (W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.7.9 SCI HDAT0 and SCI HDAT1 (R) . . . . . . . . . . . . . . . . . . . . . . . . . 40

8.7.10 SCI AIADDR (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

8.7.11 SCI VOL (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

8.7.12 SCI AICTRL[x] (RW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

9 Operation 43

Version 0.91, 2007-02-12 4

9.1 Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.2 Hardware Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.3 Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.4 ADPCM Recording . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

9.4.1 Activating ADPCM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

9.4.2 Reading IMA ADPCM Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

9.4.3 Adding a RIFF Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

9.4.4 Playing ADPCM Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9.4.5 Sample Rate Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9.4.6 Example Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9.5 SPI Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

9.6 Play/Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

9.7 Feeding PCM data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

CONTENTS

9.8 Extra Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.8.1 Common Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

9.8.2 WMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

9.8.3 AAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

9.8.4 Midi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

9.9 Fast Forward / Rewind . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

9.9.1 MP3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

9.9.2 AAC - ADTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

9.9.3 AAC - ADIF, MP4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

9.9.4 WMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

9.9.5 Midi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

9.10 SDI Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Version 0.91, 2007-02-12 5

9.10.1 Sine Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

9.10.2 Pin Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

9.10.3 Memory Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

9.10.4 SCI Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

10 VS1033 Registers 57

10.1 Who Needs to Read This Chapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

10.2 The Processor Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

10.3 VS1033 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

10.4 SCI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

10.5 Serial Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

10.6 DAC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

CONTENTS

10.7 GPIO Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

10.8 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

10.9 A/D Modulator Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

10.10Watchdog v1.0 2002-08-26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

10.10.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

10.11UART v1.1 2004-10-09 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

10.11.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

10.11.2 Status UARTx STATUS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

10.11.3 Data UARTx DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.11.4 Data High UARTx DATAH . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.11.5 Divider UARTx DIV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.11.6 Interrupts and Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Version 0.91, 2007-02-12 6

10.12Timers v1.0 2002-04-23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

10.12.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

10.12.2 Configuration TIMER CONFIG . . . . . . . . . . . . . . . . . . . . . . . . . . 66

10.12.3 Configuration TIMER ENABLE . . . . . . . . . . . . . . . . . . . . . . . . . . 67

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

10.12.4 Timer X Startvalue TIMER Tx[L/H] . . . . . . . . . . . . . . . . . . . . . . . 67

10.12.5 Timer X Counter TIMER TxCNT[L/H] . . . . . . . . . . . . . . . . . . . . . . 67

10.12.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

10.13I2S DAC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

10.13.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

10.13.2 Configuration I2S CONFIG . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

10.14System Vector Tags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

10.14.1 AudioInt, 0x20 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

10.14.2 SciInt, 0x21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

CONTENTS

10.14.3 DataInt, 0x22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

10.14.4 ModuInt, 0x23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

10.14.5 TxInt, 0x24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

10.14.6 RxInt, 0x25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

10.14.7 Timer0Int, 0x26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

10.14.8 Timer1Int, 0x27 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

10.14.9 UserCodec, 0x0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

10.15System Vector Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

10.15.1 WriteIRam(), 0x2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

10.15.2 ReadIRam(), 0x4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

10.15.3 DataBytes(), 0x6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

10.15.4 GetDataByte(), 0x8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

11 Document VersionChanges 73

Version 0.91, 2007-02-12 7

10.15.5 GetDataWords(), 0xa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

11.1 Version 0.91 for VS1033c, 2007-02-12 . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

11.2 Version 0.9 for VS1033c, 2006-08-15 . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

11.3 Version 0.8 for VS1033b, 2006-05-19 . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

11.4 Version 0.6 for VS1033a, 2006-01-05 . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

11.5 Version 0.5, 2005-10-21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

12 Contact Information 74

LIST OF FIGURES

List of Figures

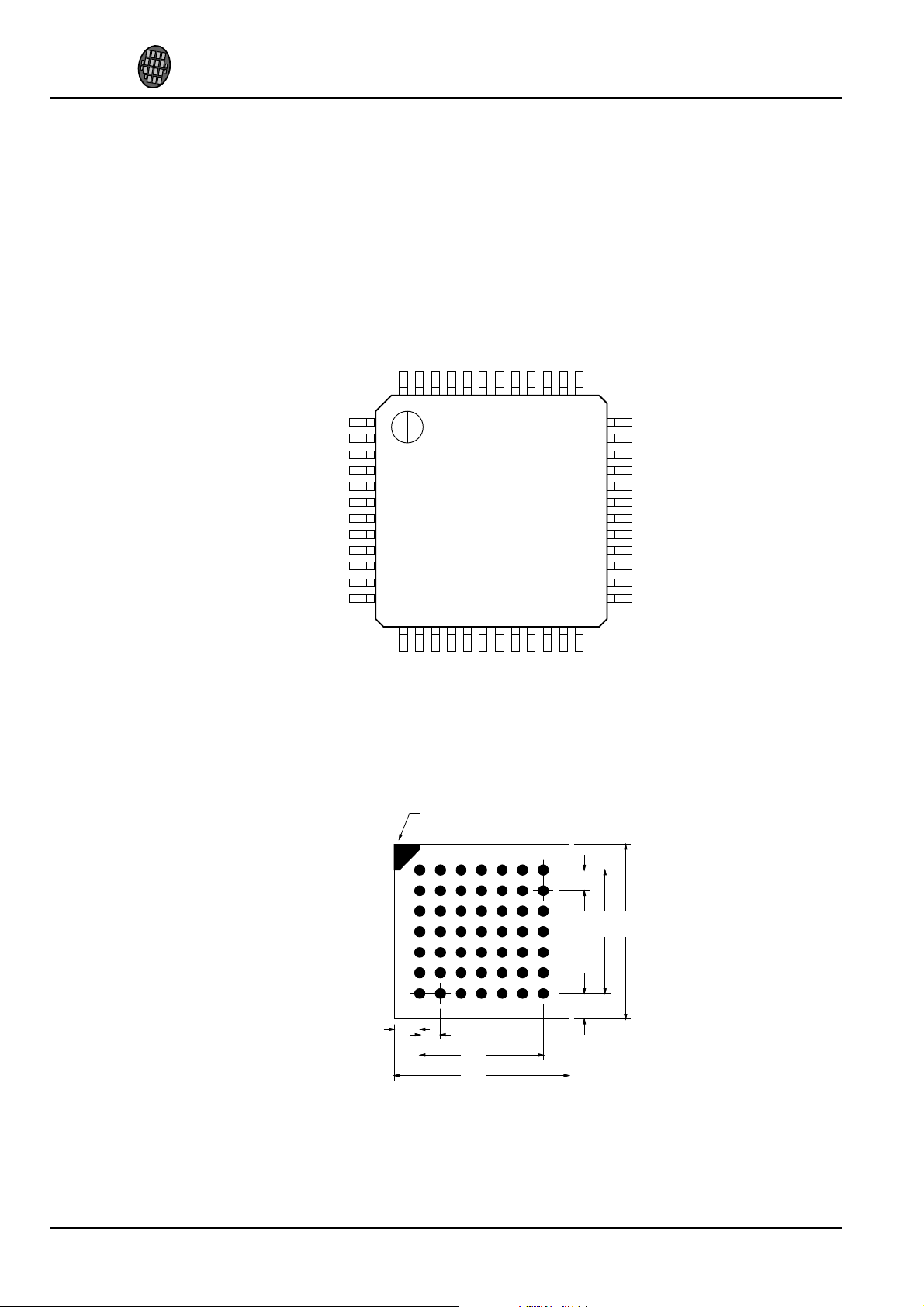

1 Pin Configuration, LQFP-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2 Pin Configuration, BGA-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

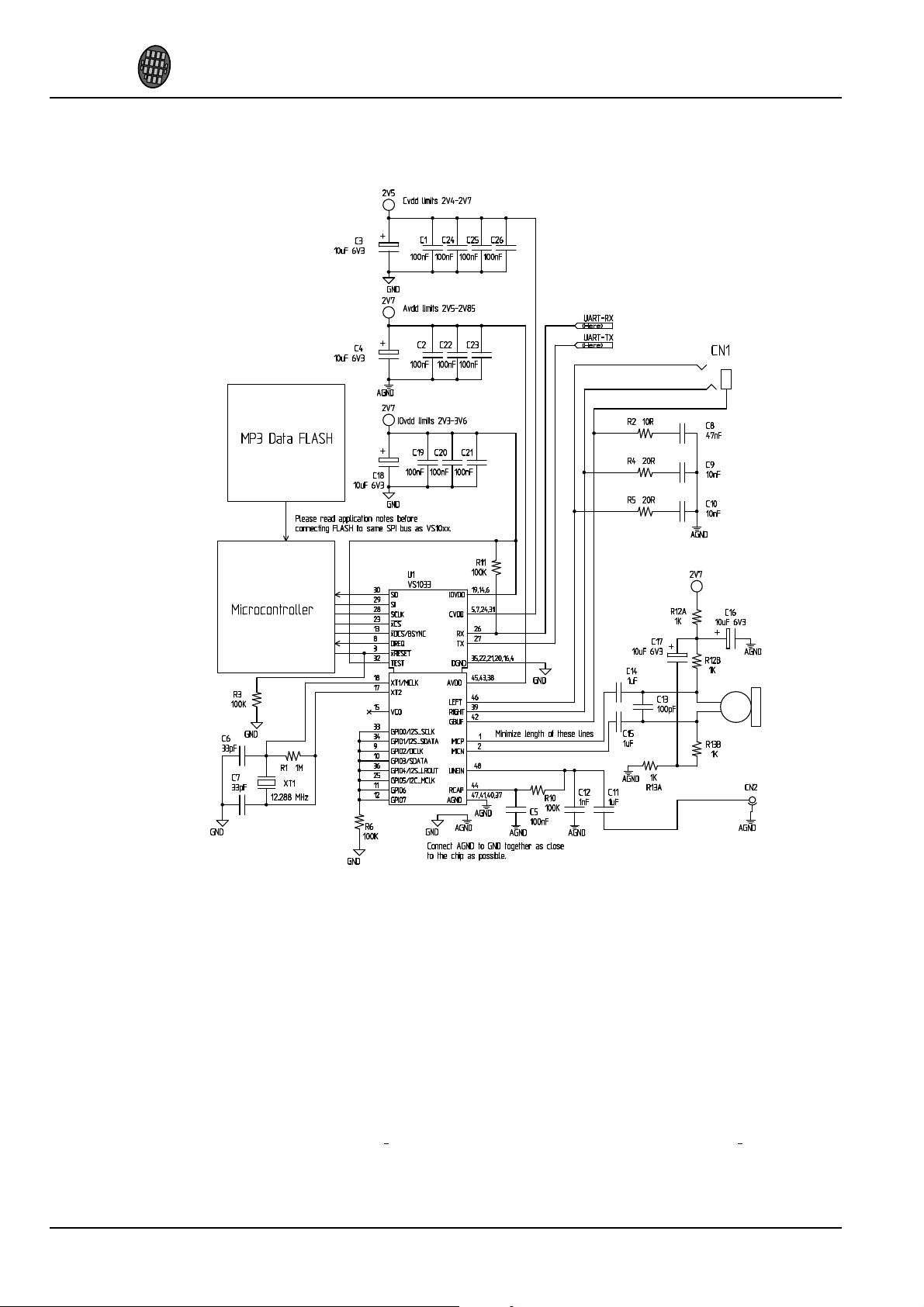

3 Typical Connection Diagram Using LQFP-48. . . . . . . . . . . . . . . . . . . . . . . . 16

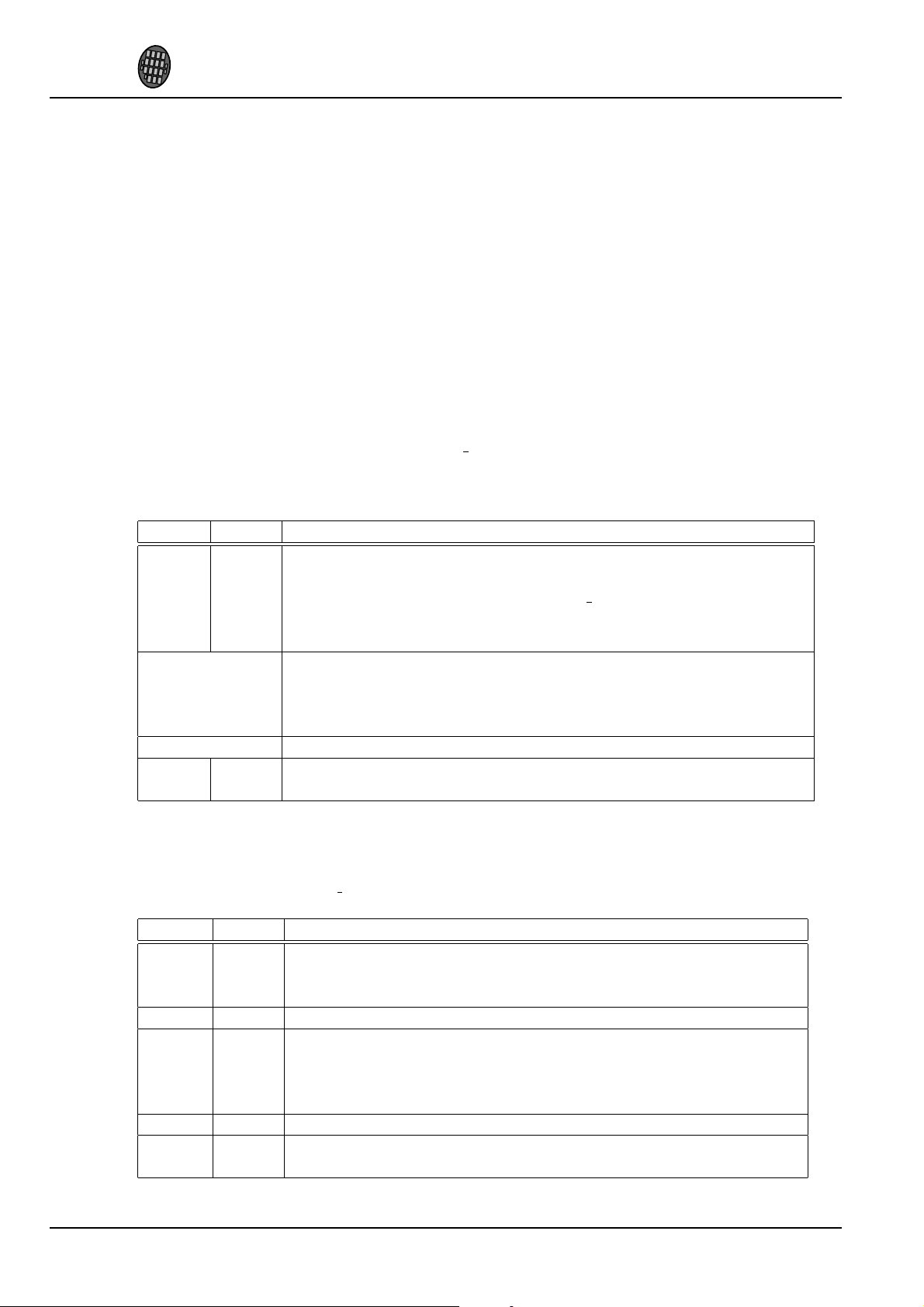

4 BSYNC Signal - one byte transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5 BSYNC Signal - two byte transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

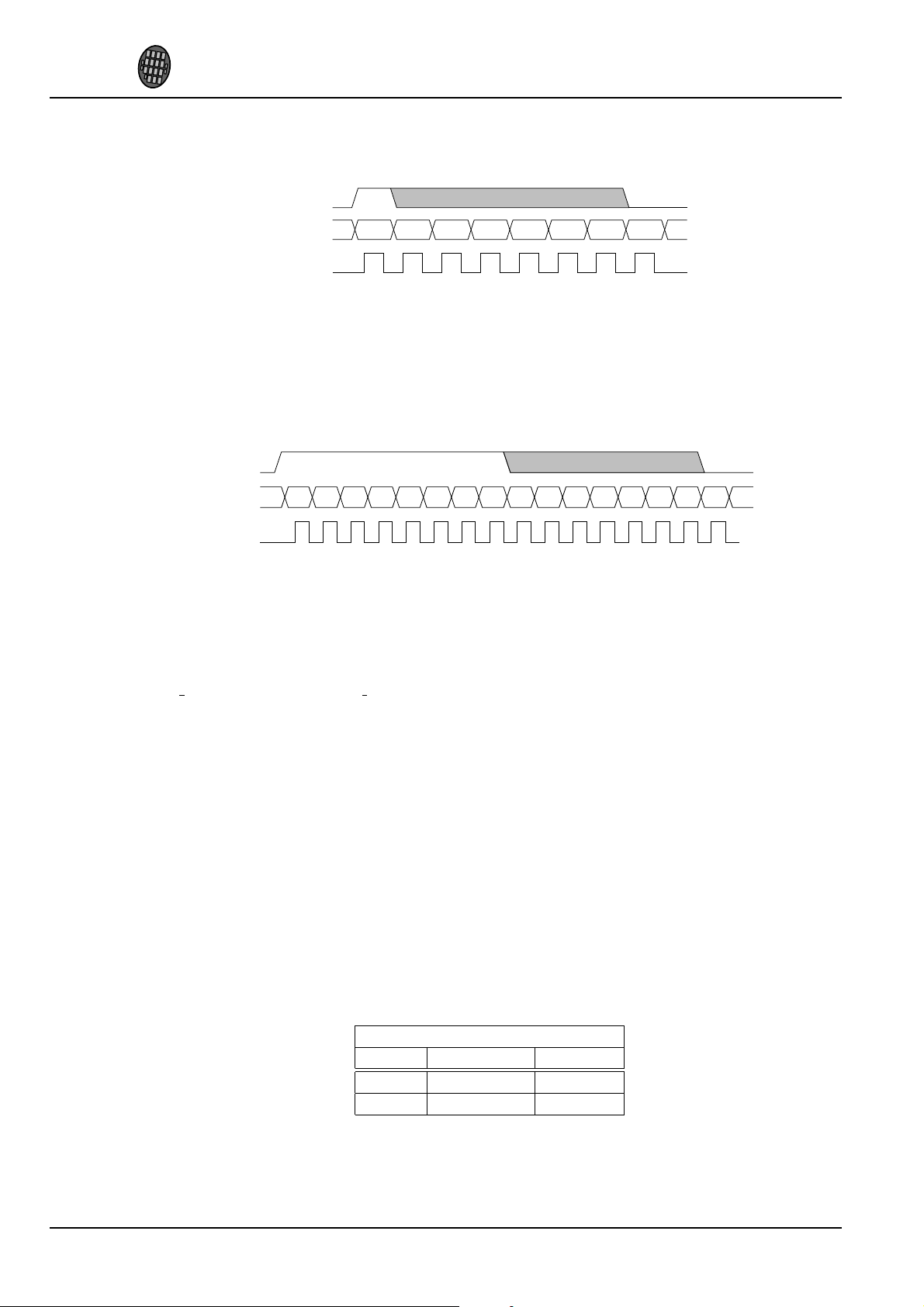

6 SCI Word Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7 SCI Word Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

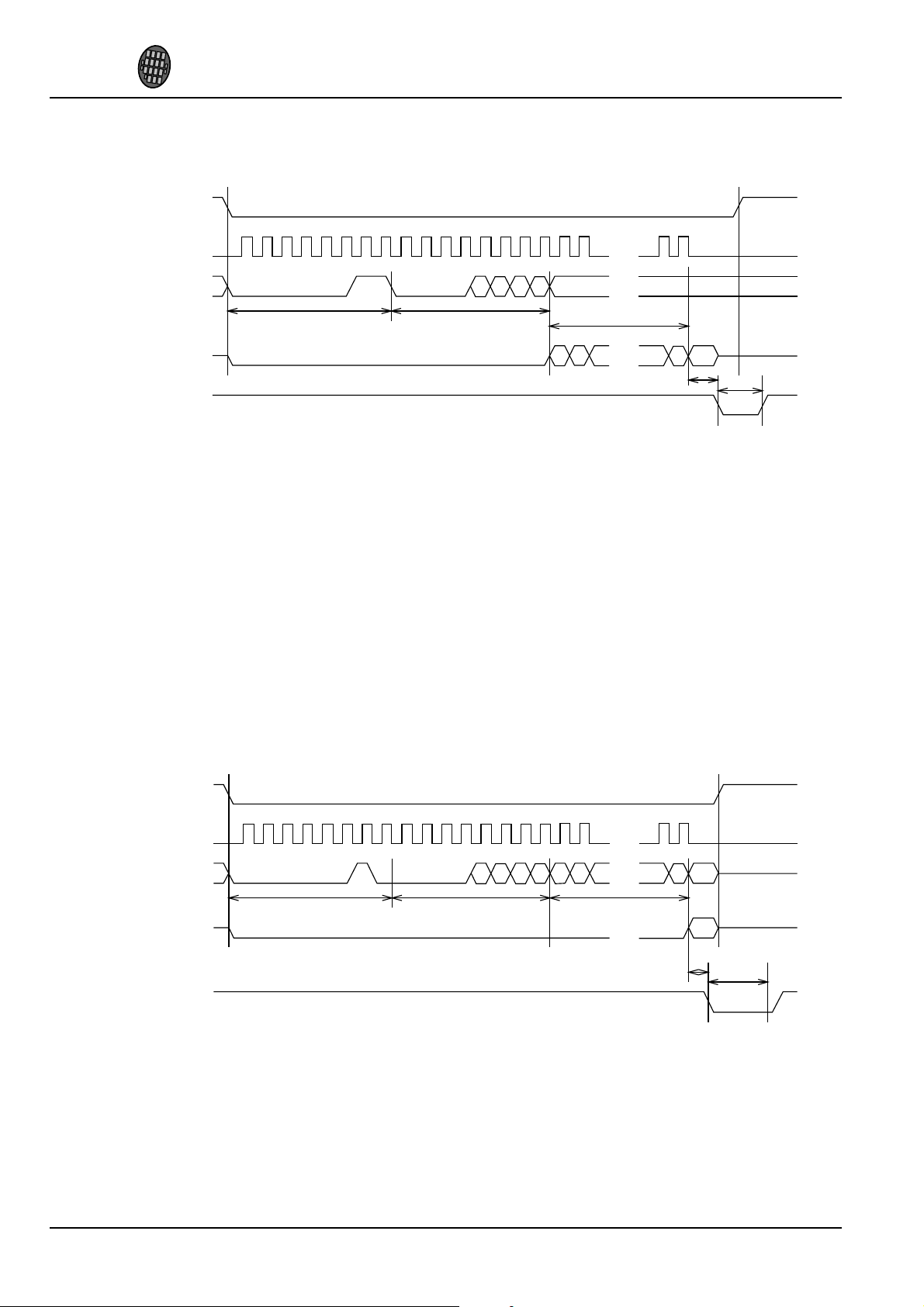

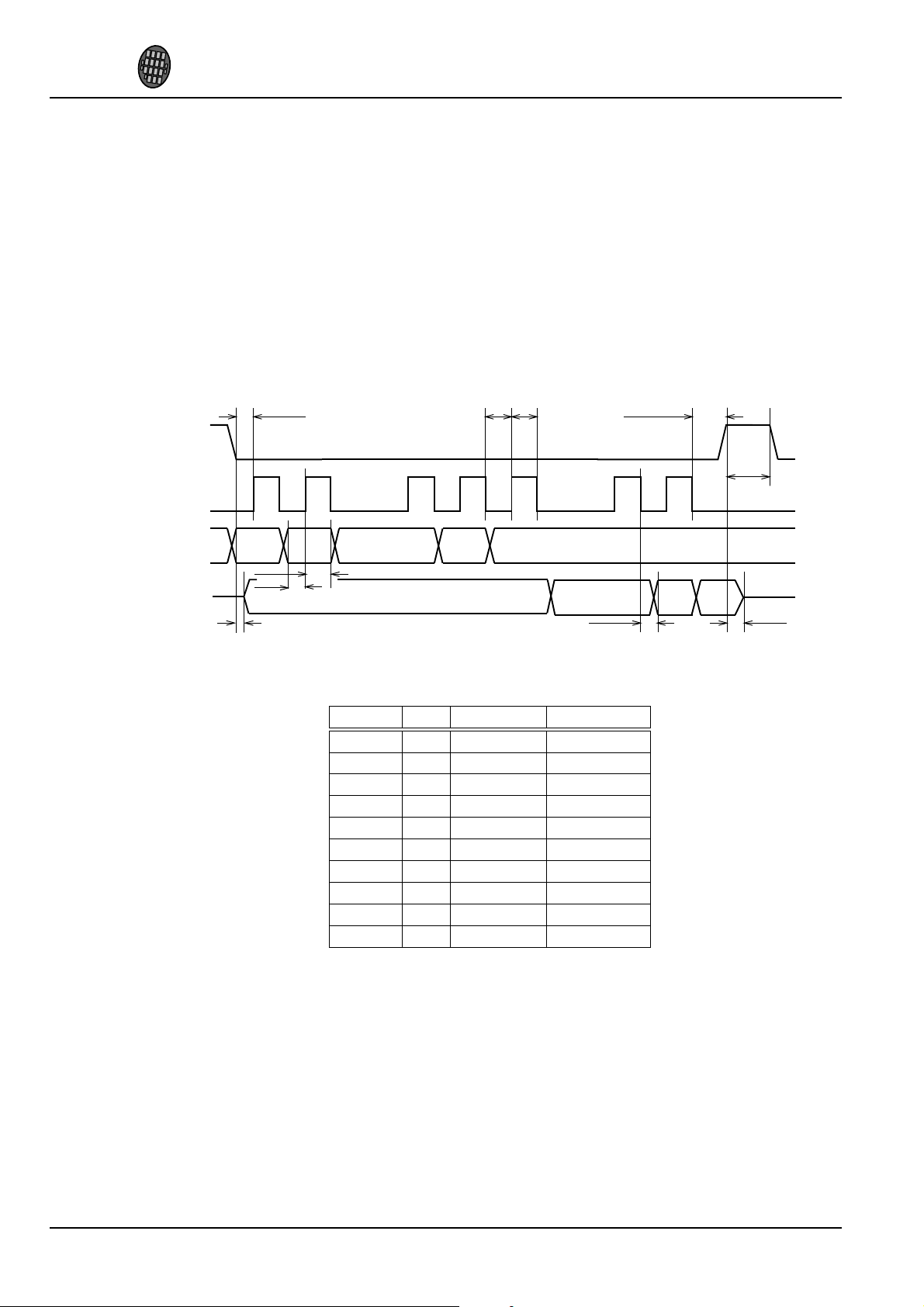

8 SPI Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

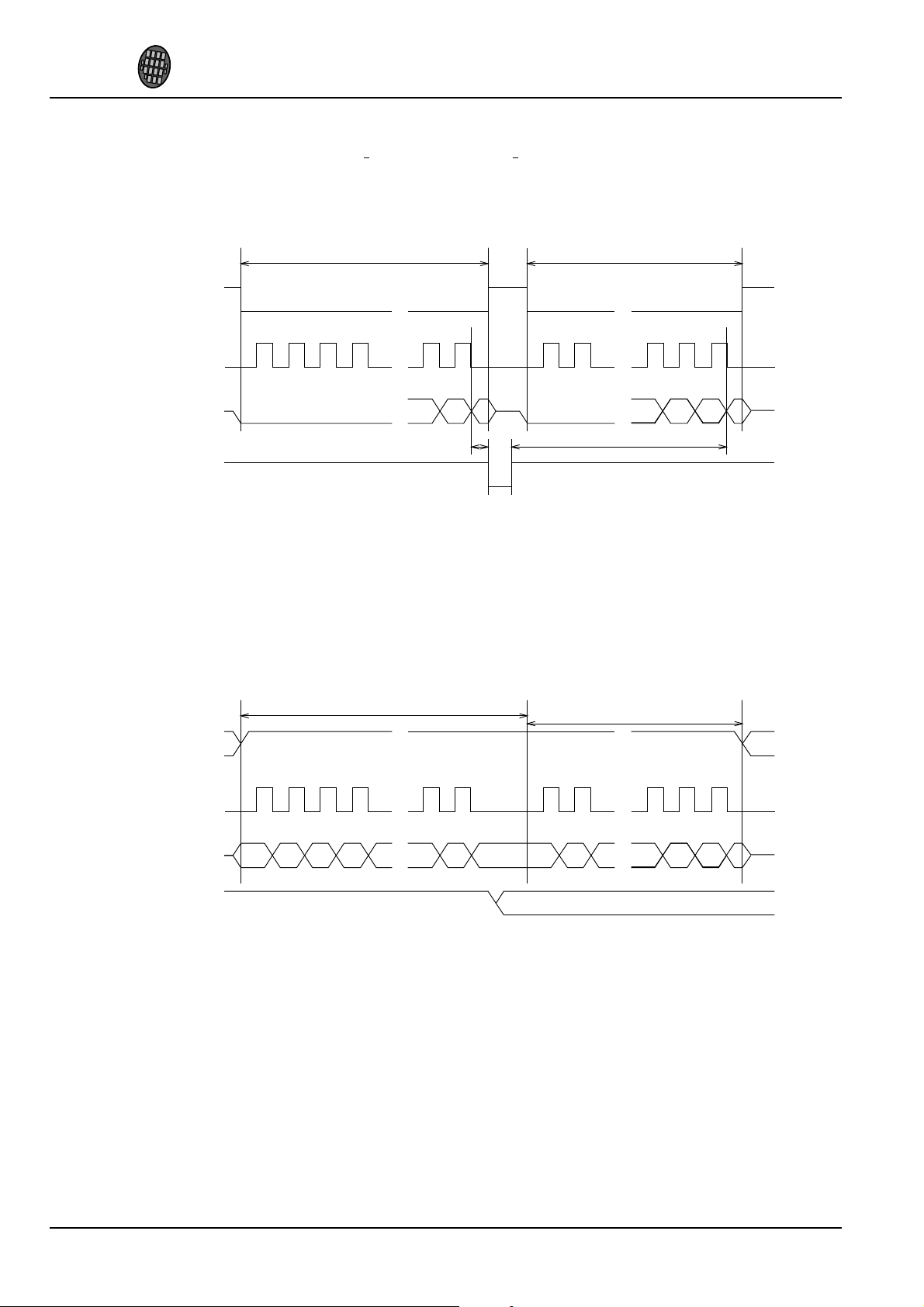

9 Two SCI Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

10 Two SDI Bytes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

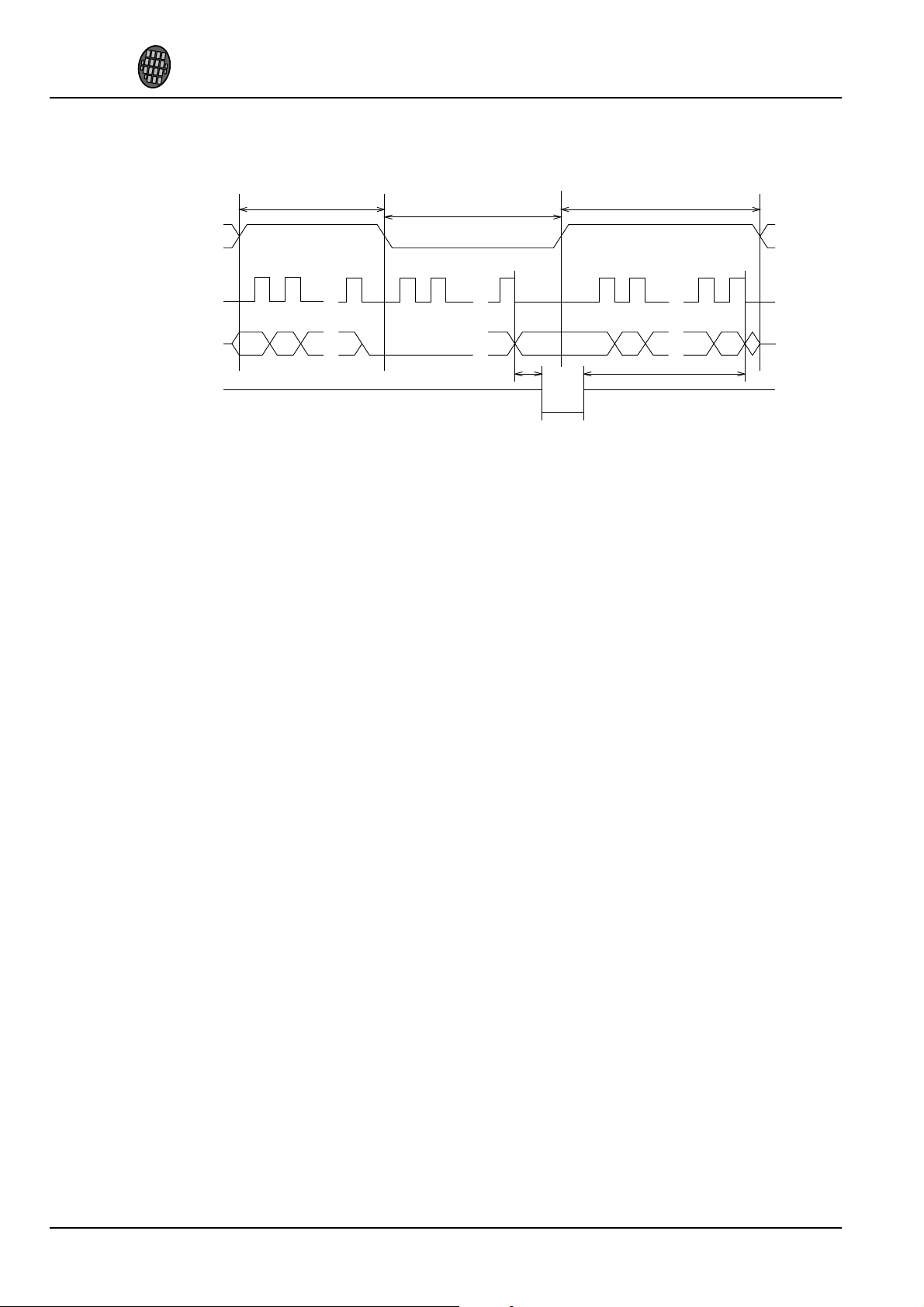

11 Two SDI Bytes Separated By an SCI Operation. . . . . . . . . . . . . . . . . . . . . . . 23

12 Data Flow of VS1033. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

13 EarSpeaker externalized sound sources vs. normal inside-the-head sound . . . . . . . . . 32

Version 0.91, 2007-02-12 8

14 ADPCM Frequency Responses with 8kHz sample rate. . . . . . . . . . . . . . . . . . . 36

15 User’s Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

16 RS232 Serial Interface Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

17 I2S Interface, 192 kHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

1. LICENSES

1 Licenses

MPEG Layer-3 audio decoding technology licensed from Fraunhofer IIS and Thomson.

Note: if you enable Layer I and Layer II decoding, you are liable for any patent issues that may

arise from using these formats. Joint licensing of MPEG 1.0 / 2.0 Layer III does not cover all patents

pertaining to layers I and II.

VS1033 contains WMA decoding technology from Microsoft.

This product is protected by certain intellectual property rights of Microsoft and cannot be used

or further distributed without a license from Microsoft.

VS1033 contains AAC technology (ISO/IEC 13818-7) which cannot be used without a proper license

from Via Licensing Corporation or individual patent holders.

To the best of our knowledge, if the end product does not play a specific format that otherwise would

require a customer license: MPEG 1.0/2.0 layers I and II, WMA, or AAC, the respective license should

not be required. Decoding of MPEG layers I and II are disabled by default, and WMA and AAC format

exclusion can be easily performed based on the contents of the SCI HDAT1 register.

2 Disclaimer

This is a

preliminary

datasheet. All properties and figures are subject to change.

3 Definitions

B Byte, 8 bits.

b Bit.

Ki “Kibi” = 210= 1024 (IEC 60027-2).

Mi “Mebi” = 220= 1048576 (IEC 60027-2).

VS DSP VLSI Solution’s DSP core.

W Word. In VS DSP, instruction words are 32-bit and data words are 16-bit wide.

Version 0.91, 2007-02-12 9

VLSI

Solution

y

VS1033c PRELIMINARY

4. CHARACTERISTICS&SPECIFICATIONS

4 Characteristics & Specifications

4.1 Absolute Maximum Ratings

Parameter Symbol Min Max Unit

Analog Positive Supply AVDD -0.3 3.6 V

Digital Positive Supply CVDD -0.3 2.7 V

I/O Positive Supply IOVDD -0.3 3.6 V

Current at Any Digital Output ±50 mA

Voltage at Any Digital Input -0.3 IOVDD+0.31V

Operating Temperature -40 +85

Storage Temperature -65 +150

1

Must not exceed 3.6 V

◦

◦

VS1033C

C

C

4.2 Recommended Operating Conditions

Parameter Symbol Min Typ Max Unit

Ambient Operating Temperature -40 +85◦C

Analog and Digital Ground

Positive Analog AVDD 2.5 2.8 3.6 V

Positive Digital CVDD 2.4 2.5 2.7 V

I/O Voltage IOVDD CVDD-0.6V 2.8 3.6 V

Input Clock Frequency

Internal Clock Frequency CLKI 12 36.864 55.3 MHz

Internal Clock Multiplier

Master Clock Duty Cycle 40 50 60 %

1

Must be connected together as close the device as possible for latch-up immunity.

2

The maximum sample rate that can be played with correct speed is XTALI/256.

Thus, XTALI must be at least 12.288 MHz to be able to play 48 kHz at correct speed.

3

Reset value is 1.0×. Recommended SC MULT=3.0×, SC ADD=1.0× (SCI CLOCKF=0x9000).

1

2

3

AGND DGND 0.0 V

XTALI 12 12.288 13 MHz

1.0× 3.0× 4.5×

Version 0.91, 2007-02-12 10

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

4. CHARACTERISTICS&SPECIFICATIONS

4.3 Analog Characteristics

Unless otherwisenoted: AVDD=2.5..2.85V, CVDD=2.4..2.7V, IOVDD=CVDD-0.6V..3.6V,TA=-40..+85◦C,

XTALI=12..13MHz, Internal Clock Multiplier 3.5×. DAC tested with 1307.894 Hz full-scale output

sinewave, measurement bandwidth 20..20000 Hz, analog output load: LEFT to GBUF 30Ω, RIGHT to

GBUF 30Ω. Microphone test amplitude 50 mVpp, fs=1 kHz, Line input test amplitude 1.1 V, fs=1 kHz.

Parameter Symbol Min Typ Max Unit

DAC Resolution 18 bits

Total Harmonic Distortion THD 0.1 0.3 %

Dynamic Range (DAC unmuted, A-weighted) IDR 90 dB

S/N Ratio (full scale signal) SNR 70 dB

Interchannel Isolation (Cross Talk) 50 75 dB

Interchannel Isolation (Cross Talk), with GBUF 40 dB

Interchannel Gain Mismatch -0.5 0.5 dB

Frequency Response -0.1 0.1 dB

Full Scale Output Voltage (Peak-to-peak) 1.3 1.5

Deviation from Linear Phase 5

Analog Output Load Resistance AOLR 16 30

Analog Output Load Capacitance 100 pF

Microphone input amplifier gain MICG 26 dB

Microphone input amplitude 50 1403mVpp AC

Microphone Total Harmonic Distortion MTHD 0.02 0.10 %

Microphone S/N Ratio MSNR 50 62 dB

Line input amplitude 2200 28003mVpp AC

Line input Total Harmonic Distortion LTHD 0.06 0.10 %

Line input S/N Ratio LSNR 60 68 dB

Line and Microphone input impedances 100 kΩ

1

2

1.7 Vpp

◦

Ω

1

3.0 volts can be achieved with +-to-+ wiring for mono difference sound.

2

AOLR may be much lower, but below Typical distortion performance may be compromised.

3

Above typical amplitude the Harmonic Distortion increases.

4.4 Power Consumption

Tested with an MPEG 1.0 Layer-3 128 kbps sample and generated sine. Output at full volume. Internal

clock multiplier 3.0×.

Parameter Min Typ Max Unit

Power Supply Consumption AVDD, Reset 0.6 5.0 µA

Power Supply Consumption CVDD = 2.5V, Reset 3.7 50.0 µA

Power Supply Consumption AVDD, sine test, 30Ω + GBUF 36.9 mA

Power Supply Consumption CVDD = 2.5V, sine test 8.2 mA

Power Supply Consumption AVDD, no load 7.0 mA

Power Supply Consumption AVDD, output load 30Ω 10.9 mA

Power Supply Consumption AVDD, 30Ω + GBUF 16.1 mA

Power Supply Consumption CVDD = 2.5V 14 mA

Version 0.91, 2007-02-12 11

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

4. CHARACTERISTICS&SPECIFICATIONS

4.5 Digital Characteristics

Parameter Symbol Min Typ Max Unit

High-Level Input Voltage 0.7×IOVDD IOVDD+0.31V

Low-Level Input Voltage -0.2 0.3×IOVDD V

High-Level Output Voltage at IO= -2.0 mA 0.7×IOVDD V

Low-Level Output Voltage at IO= 2.0 mA 0.3×IOVDD V

Input Leakage Current -1.0 1.0 µA

SPI Input Clock Frequency

2

CLK I

6

MHz

Rise time of all output pins, load = 50 pF 50 ns

1

Must not exceed 3.6V

2

Value for SCI reads. SCI and SDI writes allow

CLK I

4

.

4.6 Switching Characteristics - Boot Initialization

Parameter Symbol Min Max Unit

XRESET active time 2 XTALI

XRESET inactive to software ready 20000 500001XTALI

Power on reset, rise time to CVDD 10 V/s

1

DREQ rises when initialization is complete. You should not send any data or commands before that.

Version 0.91, 2007-02-12 12

VLSI

Solution

y

VS1033C

1

48

A

B

C

D

E

F

G

1 2

3

4 5

6 7

TOP VIEW

0.80 TYP

4.80

7.00

1.10 REF

0.80 TYP

1.10 REF

4.80

7.00

A1 BALL PAD CORNER

VS1033c PRELIMINARY

5. PACKAGES AND PIN DESCRIPTIONS

5 Packages and Pin Descriptions

5.1 Packages

Both LPQFP-48 and BGA-49 are lead (Pb) free and also RoHS compliant packages. RoHS is a short

name of Directive 2002/95/EC on the restriction of the use of certain hazardous substances in electrical

and electronic equipment.

5.1.1 LQFP-48

Figure 1: Pin Configuration, LQFP-48.

LQFP-48 package dimensions are at http://www.vlsi.fi/ .

5.1.2 BGA-49

BGA-49 package dimensions are at http://www.vlsi.fi/ .

Figure 2: Pin Configuration, BGA-49.

Version 0.91, 2007-02-12 13

VLSI

Solution

y

VS1033c PRELIMINARY

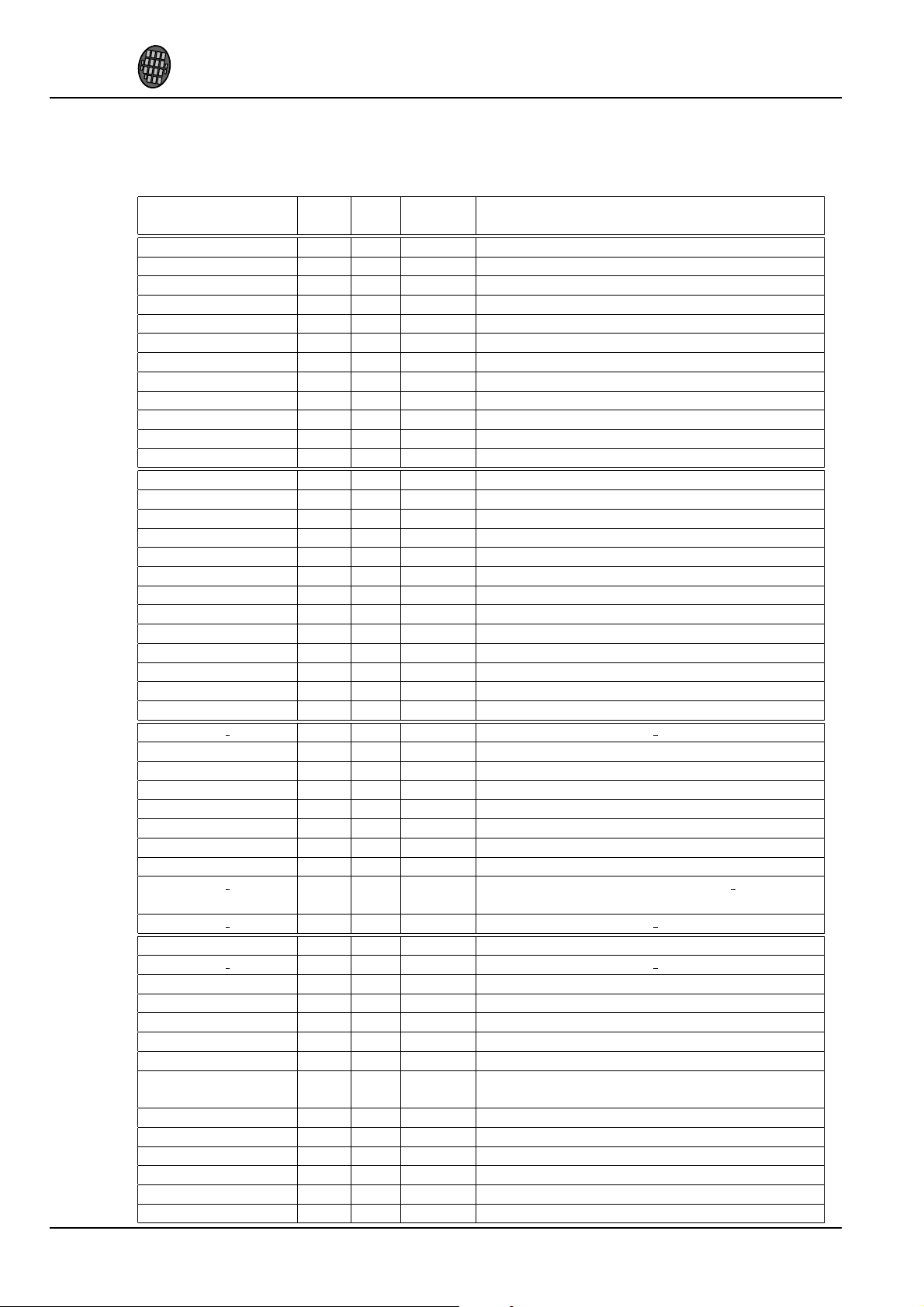

5.2 LQFP-48 and BGA-49 Pin Descriptions

VS1033C

5. PACKAGES AND PIN DESCRIPTIONS

Pin Name LQFP

Pin

MICP 1 C3 AI Positive differential microphone input, self-biasing

MICN 2 C2 AI Negative differential microphone input, self-biasing

XRESET 3 B1 DI Active low asynchronous reset, schmitt-trigger input

DGND0 4 D2 DGND Core & I/O ground

CVDD0 5 C1 CPWR Core power supply

IOVDD0 6 D3 IOPWR I/O power supply

CVDD1 7 D1 CPWR Core power supply

DREQ 8 E2 DO Data request, input bus

GPIO2 / DCLK

GPIO3 / SDATA

GPIO6 11 F1 DIO General purpose IO 6

GPIO7 12 G1 DIO General purpose IO 7

XDCS / BSYNC

IOVDD1 14 F3 IOPWR I/O power supply

VCO 15 G2 DO For testing only (Clock VCO output)

DGND1 16 F4 DGND Core & I/O ground

XTALO 17 G3 AO Crystal output

XTALI 18 E4 AI Crystal input

IOVDD2 19 G4 IOPWR I/O power supply

IOVDD3 F5 IOPWR I/O power supply

DGND2 20 DGND Core & I/O ground

DGND3 21 G5 DGND Core & I/O ground

DGND4 22 F6 DGND Core & I/O ground

XCS 23 G6 DI Chip select input (active low)

CVDD2 24 G7 CPWR Core power supply

GPIO5 / I2S MCLK

RX 26 E6 DI UART receive, connect to IOVDD if not used

TX 27 F7 DO UART transmit

SCLK 28 D6 DI Clock for serial bus

SI 29 E7 DI Serial input

SO 30 D5 DO3 Serial output

CVDD3 31 D7 CPWR Core power supply

TEST 32 C6 DI Reserved for test, connect to IOVDD

GPIO0 / I2S SCLK

GPIO1 / I2S SDATA334 B6 DIO General purpose IO 1 / I2S SDATA

GND 35 B7 DGND I/O Ground

GPIO4 / I2S LROUT336 A7 DIO General purpose IO 4 / I2S LROUT

AGND0 37 C5 APWR Analog ground, low-noise reference

AVDD0 38 B5 APWR Analog power supply

RIGHT 39 A6 AO Right channel output

AGND1 40 B4 APWR Analog ground

AGND2 41 A5 APWR Analog ground

GBUF 42 C4 AO Common buffer for headphones, do NOT connect to

AVDD1 43 A4 APWR Analog power supply

RCAP 44 B3 AIO Filtering capacitance for reference

AVDD2 45 A3 APWR Analog power supply

LEFT 46 B2 AO Left channel output

AGND3 47 A2 APWR Analog ground

LINEIN 48 A1 AI Line input

1

1

1

9 E1 DIO General purpose IO 2 / serial input data bus clock

10 F2 DIO General purpose IO 3 / serial data input

13 E3 DI Data chip select / byte sync

3

25 E5 DIO General purpose IO 5 / I2S MCLK

3

33 C7 DIO General purpose IO 0 (SPIBOOT) / I2S SCLK

BGA

Ball

Pin

Type

Function

use 100 kΩ pull-down resistor

ground!

2

Version 0.91, 2007-02-12 14

VLSI

Solution

y

VS1033c PRELIMINARY

1

First pin function is active in New Mode, latter in Compatibility Mode.

2

Unless pull-down resistor is used, SPI Boot is tried. See Chapter 9.5 for details.

3

If I2S CF ENA is ’0’ the pins are used for GPIO. See Chapter 10.13 for details.

5. PACKAGES AND PIN DESCRIPTIONS

Pin types:

VS1033C

Type Description

DI Digital input, CMOS Input Pad

DO Digital output, CMOS Input Pad

DIO Digital input/output

DO3 Digital output, CMOS Tri-stated OutputPad

AI Analog input

In BGA-49, D4 is a no-connect ball.

Type Description

AO Analog output

AIO Analog input/output

APWR Analog power supply pin

DGND Core or I/O ground pin

CPWR Core power supply pin

IOPWR I/O power supply pin

Version 0.91, 2007-02-12 15

VLSI

Solution

y

VS1033c PRELIMINARY

6 Connection Diagram, LQFP-48

VS1033C

6. CONNECTION DIAGRAM, LQFP-48

Figure 3: Typical Connection Diagram Using LQFP-48.

The common buffer GBUF can be used for common voltage (1.24 V) for earphones. This will eliminate

the need for large isolation capacitors on line outputs, and thus the audio output pins from VS1033 may

be connected directly to the earphone connector.

GBUF must NOT be connected to ground in any circumstance. If GBUF is not used, LEFT and RIGHT

must be provided with coupling capacitors. See application notes for details.

Unused GPIO pins should have a pull-down resistor.

If UART is not used, RX should be connected to IOVDD and TX be unconnected.

Do not connect any external load to XTALO.

Note: This connection assumes SM SDINEW is active (see Chapter 8.7.1). If also SM SDISHARE is

used, xDCS should be tied low or high (see Chapter 7.2.1).

Version 0.91, 2007-02-12 16

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

7. SPI BUSES

7 SPI Buses

7.1 General

The SPI Bus - that was originally used in some Motorola devices - has been used for both VS1033’s

Serial Data Interface SDI (Chapters 7.4 and 8.5) and Serial Control Interface SCI (Chapters 7.5 and 8.6).

7.2 SPI Bus Pin Descriptions

7.2.1 VS1002 Native Modes (New Mode)

These modes are active on VS1033 when SM SDINEW is set to 1 (default at startup). DCLK and

SDATA are not used for data transfer and they can be used as general-purpose I/O pins (GPIO2 and

GPIO3). BSYNC function changes to data interface chip select (XDCS).

SDI Pin SCI Pin Description

XDCS XCS Active low chip select input. A high level forces the serial interface into

standby mode, ending the current operation. A high level also forces serial

output (SO) to high impedance state. If SM SDISHARE is 1, pin

XDCS is not used, but the signal is generated internally by inverting

XCS.

SCK Serial clock input. The serial clock is also used internally as the master

clock for the register interface.

SCK can be gated or continuous. In either case, the first rising clock edge

after XCS has gone low marks the first bit to be written.

SI Serial input. If a chip select is active, SI is sampled on the rising CLK edge.

- SO Serial output. In reads, data is shifted out on the falling SCK edge.

In writes SO is at a high impedance state.

7.2.2 VS1001 Compatibility Mode

This mode is active when SM SDINEW is set to 0. In this mode, DCLK, SDATA and BSYNC are active.

SDI Pin SCI Pin Description

- XCS Active low chip select input. A high level forces the serial interface into

standby mode, ending the current operation. A high level also forces serial

output (SO) to high impedance state.

BSYNC - SDI data is synchronized with a rising edge of BSYNC.

DCLK SCK Serial clock input. The serial clock is also used internally as the master

SDATA SI Serial input. SI is sampled on the rising SCK edge, if XCS is low.

- SO Serial output. In reads, data is shifted out on the falling SCK edge.

clock for the register interface.

SCK can be gated or continuous. In either case, the first rising clock edge

after XCS has gone low marks the first bit to be written.

In writes SO is at a high impedance state.

Version 0.91, 2007-02-12 17

VLSI

Solution

y

VS1033C

VS1033c PRELIMINARY

7. SPI BUSES

7.3 Data Request Pin DREQ

The DREQ pin/signal is used to signal if VS1033’s 2048-byte FIFO is capable of receiving data. If

DREQ is high, VS1033 can take at least 32 bytes of SDI data or one SCI command. DREQ is turned low

when the stream buffer is too full and for the duration of a SCI command.

Because of the 32-byte safety area, the sender may send upto 32 bytes of SDI data at a time without

checking the status of DREQ, making controlling VS1033 easier for low-speed microcontrollers.

Note: DREQ may turn low or high at any time, even during a byte transmission. Thus, DREQ should

only be used to decide whether to send more bytes. It does not need to abort a transmission that has

already started.

Note: In VS10XX products upto VS1002, DREQ was only used for SDI. In VS1003 and VS1033 DREQ

is also used to tell the status of SCI.

There are cases when you still want to send SCI commands when DREQ is low. Because DREQ is

shared between SDI and SCI, you can not determine if a SCI command has been executed if SDI is not

ready to receive. In this case you need a long enough delay after every SCI command to make certain

none of them is missed. The SCI Registers table in section 8.7 gives the worst-case handling time for

each SCI register write.

7.4 Serial Protocol for Serial Data Interface (SDI)

7.4.1 General

The serial data interface operates in slavemodesoDCLK signal must be generated by an externalcircuit.

Data (SDATA signal) can be clocked in at either the rising or falling edge of DCLK (Chapter 8.7).

VS1033 assumes its data input to be byte-sychronized. SDI bytes may be transmitted either MSb or LSb

first, depending of contents of SCI MODE (Chapter 8.7.1).

The firmware is able to accept the maximum bitrate the SDI supports.

7.4.2 SDI in VS1002 Native Modes (New Mode)

In VS1002native modes(SM NEWMODE is 1), byte synchronizationisachieved by XDCS.Thestateof

XDCS may not change while a data byte transfer is in progress. To always maintain data synchronization

even if there may be glitches in the boards using VS1033, it is recommended to turn XDCS every now

and then, for instance once after every flash data block or a few kilobytes, just to keep sure the host and

VS1033 are in sync.

If SM SDISHARE is 1, the XDCS signal is internally generated by inverting the XCS input.

For new designs, using VS1002 native modes are recommended.

Version 0.91, 2007-02-12 18

VLSI

Solution

y

VS1033C

BSYNC

SDATA

DCLK

D7 D6 D5 D4 D3 D2 D1 D0

BSYNC

SDATA

DCLK

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

VS1033c PRELIMINARY

7. SPI BUSES

7.4.3 SDI in VS1001 Compatibility Mode

Figure 4: BSYNC Signal - one byte transfer.

When VS1033 is running in VS1001 compatibility mode, a BSYNC signal must be generated to ensure

correct bit-alignment of the input bitstream. The first DCLK sampling edge (rising or falling, depending

on selected polarity), during which the BSYNC is high, marks the first bit of a byte (LSB, if LSB-first

order is used, MSB, if MSB-first orderisused). If BSYNC is ’1’ when the last bit is received,thereceiver

stays active and next 8 bits are also received.

7.4.4 Passive SDI Mode

If SM NEWMODE is 0 and SM SDISHARE is 1, the operation is otherwise like the VS1001 compatibility mode, but bits are only received while the BSYNC signal is ’1’. Rising edge of BSYNC is still

used for synchronization.

7.5 Serial Protocol for Serial Command Interface (SCI)

7.5.1 General

The serial bus protocol for the Serial Command Interface SCI (Chapter 8.6) consists of an instruction

byte, address byte and one 16-bit data word. Each read or write operation can read or write a single

register. Data bits are read at the rising edge, so the user should update data at the falling edge. Bytes

are always send MSb first. XCS should be low for the full duration of the operation, but you can have

pauses between bits if needed.

The operation is specified by an 8-bit instruction opcode. The supported instructions are read and write.

See table below.

Figure 5: BSYNC Signal - two byte transfer.

Instruction

Name Opcode Operation

READ 0b0000 0011 Read data

WRITE 0b0000 0010 Write data

Note: VS1033 sets DREQ low after each SCI operation. The duration depends on the operation. It is not

allowed to start a new SCI/SDI operation before DREQ is high again.

Version 0.91, 2007-02-12 19

VLSI

Solution

y

7.5.2 SCI Read

0 1 2 3 4 5 6 7 8 9 10 11 12 13 30 3114 15 16 17

0 0 0 0 0 0 1 1 0 0 0 0

3 2 1 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

15 14 1 0

X

instruction (read) address

data out

XCS

SCK

SI

SO

don’t care don’t care

DREQ

execution

0 1 2 3 4 5 6 7 8 9 10 11 12 13 30 3114 15 16 17

0 0 0 0 0 0 1 0 0 0 0

3 2 1 0

1 0

X

address

XCS

SCK

SI

15 14

data out

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0SO

0 0 0 0

X

0

instruction (write)

DREQ

execution

VS1033c PRELIMINARY

Figure 6: SCI Word Read

VS1033C

7. SPI BUSES

VS1033 registers are read from using the following sequence, as shown in Figure 6. First, XCS line is

pulled low to select the device. Then the READ opcode (0x3) is transmitted via the SI line followed by

an 8-bit word address. After the address has been read in, any further data on SI is ignored by the chip.

The 16-bit data corresponding to the received address will be shifted out onto the SO line.

XCS should be driven high after data has been shifted out.

DREQ is driven low for a short while when in a read operation by the chip. This is a very short time and

doesn’t require special user attention.

7.5.3 SCI Write

Version 0.91, 2007-02-12 20

Figure 7: SCI Word Write

VS1033 registers are written from using the following sequence, as shown in Figure 7. First, XCS line

is pulled low to select the device. Then the WRITE opcode (0x2) is transmitted via the SI line followed

by an 8-bit word address.

VLSI

Solution

y

VS1033C

XCS

SCK

SI

SO

0 1 1514 16

tXCSS

tXCSH

tWL tWH

tH

tSU

tV

tZ

tDIS

tXCS

30

31

VS1033c PRELIMINARY

7. SPI BUSES

After the word has been shifted in and the last clock has been sent, XCS should be pulled high to end the

WRITE sequence.

After the last bit has been sent, DREQ is driven low for the duration of the register update, marked “execution” in the figure. The time varies depending on the register and its contents (see table in Chapter 8.7

for details). If the maximum time is longer than what it takes from the microcontroller to feed the next

SCI command or SDI byte, it is not allowed to finish a new SCI/SDI operation before DREQ has risen

up again.

7.6 SPI Timing Diagram

Figure 8: SPI Timing Diagram.

Symbol Min Max Unit

tXCSS 5 ns

tSU -26 ns

tH 2 CLKI cycles

tZ 0 ns

tWL 2 CLKI cycles

tWH 2 CLKI cycles

tV 2 (+ 25ns1) CLKI cycles

tXCSH -26 ns

tXCS 2 CLKI cycles

tDIS 10 ns

1

25ns is when pin loaded with 100pF capacitance. The time is shorter with lower capacitance.

Note: As tWL and tWH, as well as tH require at least 2 clock cycles, the maximum speed for the SPI

bus that can easily be used is 1/6 of VS1033’s internal clock speed CLKI. Slightly higher speed can be

achieved with very careful timing tuning. For details, see Application Notes for VS10XX.

Note: Although the timing is derived from the internal clock CLKI, the system always starts up in 1.0×

mode, thus CLKI=XTALI.

Note: Negative numbers mean that the signal can change in different order from what is shown in the

diagram.

Version 0.91, 2007-02-12 21

VLSI

Solution

y

VS1033c PRELIMINARY

0

1 2 3 30 31

1 0 1 0

0 0 0 0 0 0

X X

XCS

SCK

SI

2

32 33 61 62 63

SCI Write 1

SCI Write 2

DREQ

DREQ up before finishing next SCI write

1 2 3

XCS

SCK

SI

7 6 5 4 3 1 0 7 6 5 2 1 0

X

SDI Byte 1

SDI Byte 2

0 6 7 8 9 13 14 15

DREQ

7.7 SPI Examples with SM SDINEW and SM SDISHARED set

7.7.1 Two SCI Writes

VS1033C

7. SPI BUSES

Figure 9: Two SCI Operations.

Figure 9 shows two consecutive SCI operations. Note that xCS must be raised to inactive state between

the writes. Also DREQ must be respected as shown in the figure.

7.7.2 Two SDI Bytes

Figure 10: Two SDI Bytes.

SDI data is synchronized with a raising edge of xCS as shown in Figure 10. However, every byte doesn’t

need separate synchronization.

Version 0.91, 2007-02-12 22

VLSI

Solution

y

VS1033C

0

1

XCS

SCK

SI

7

7 6 5 1

0 0

0 7 6 5 1 0

SDI Byte

SCI Operation

SDI Byte

8 9 39 40 41 46 47

X

DREQ high before end of next transfer

VS1033c PRELIMINARY

7. SPI BUSES

7.7.3 SCI Operation in Middle of Two SDI Bytes

Figure 11: Two SDI Bytes Separated By an SCI Operation.

Figure 11 shows how an SCI operation is embedded in between SDI operations. xCS edges are used to

synchronize both SDI and SCI. Remember to respect DREQ as shown in the figure.

Version 0.91, 2007-02-12 23

Loading...

Loading...