VITESSE VSC9680 Datasheet

www.vitesse.com

Product Brief

2048 Channel HDLC/ATM Controller

TimeStream

Product

Family

Telecom Division

VSC9680

General Description

Designed to meet the challenges of

high bandwidth telecommunication line

aggregation devices, and offering an

industry-leading 2048 channels, the

VSC9680 is the HDLC controller and

A TM cell delineation device in Vitesse’

TimeStream™ product family.

Unique Scalable Time-sliced

Architecture

The VSC9680 uses a unique, patent

pending, scalable time-sliced state

machine architecture for performing

packet and cell delineation functions

that increase density and throughput for

a combined full duplex aggregate

throughput of up to 135 Mbps.

The VSC9680 provides more channels

with higher throughput than any currently available controller device. It includes a scatter/gather DMA engine,

32/64-bit 33/66 MHz PCI V2.1 compliant bus for system configuration and

HDLC packet transfers, and a Utopia

Level 2 compliant bus for ATM cell

transfers.

Lower Costs, Smaller Board

Space

The VSC9680 can perform HDLC

packet and ATM cell delineation for up

to 2048 logical channels with the lowest power consumption per channel.

This device can interface directly with

up to 28 T1 or 32 E1 framers, 3

unchannelized DS3 or HSSI channels,

16 xDSL channels, up to 2048 DS0

channels via a H.100 bus, and up to 84

T1 or 63 E1 framers via a proprietary

interface, which eliminates glue logic

requirements, resulting in lower cost

and smaller board space.

Features:

• 2048 full duplex HDLC channels

• 3 full duplex DS3 or HSSI

channels

• 16 HDSL and 8 ADSL channels

• 28 T1 or 32 E1 channels

• Up to 84 T1 or 63 E1 channels

via a proprietary interface to the

VSC967x Framer product family

• Combined throughput up to

135 Mbps

• Delineates HDLC packets or ATM

cells per logical channel

• Flexible and powerful mapping of

DS0 physical to logical channels

• HDLC flag insertion, bit stuffing,

CRC-16/32 generation for each

transmit channel

• HDLC flag detection, bit de-

stuffing and CRC-16/32 calculation for each receive channel

• Detects a valid ATM cell by

framing to the HEC in the receive

direction, and inserts an HEC

value for each ATM cell in the

transmit direction.

• 2048 channel scatter gather DMA

engine transfers packets to and

from host memory using a flexible

descriptor structure

• External ZBT SRAM allows large

burst transfers providing efficient

PCI bus utilization.

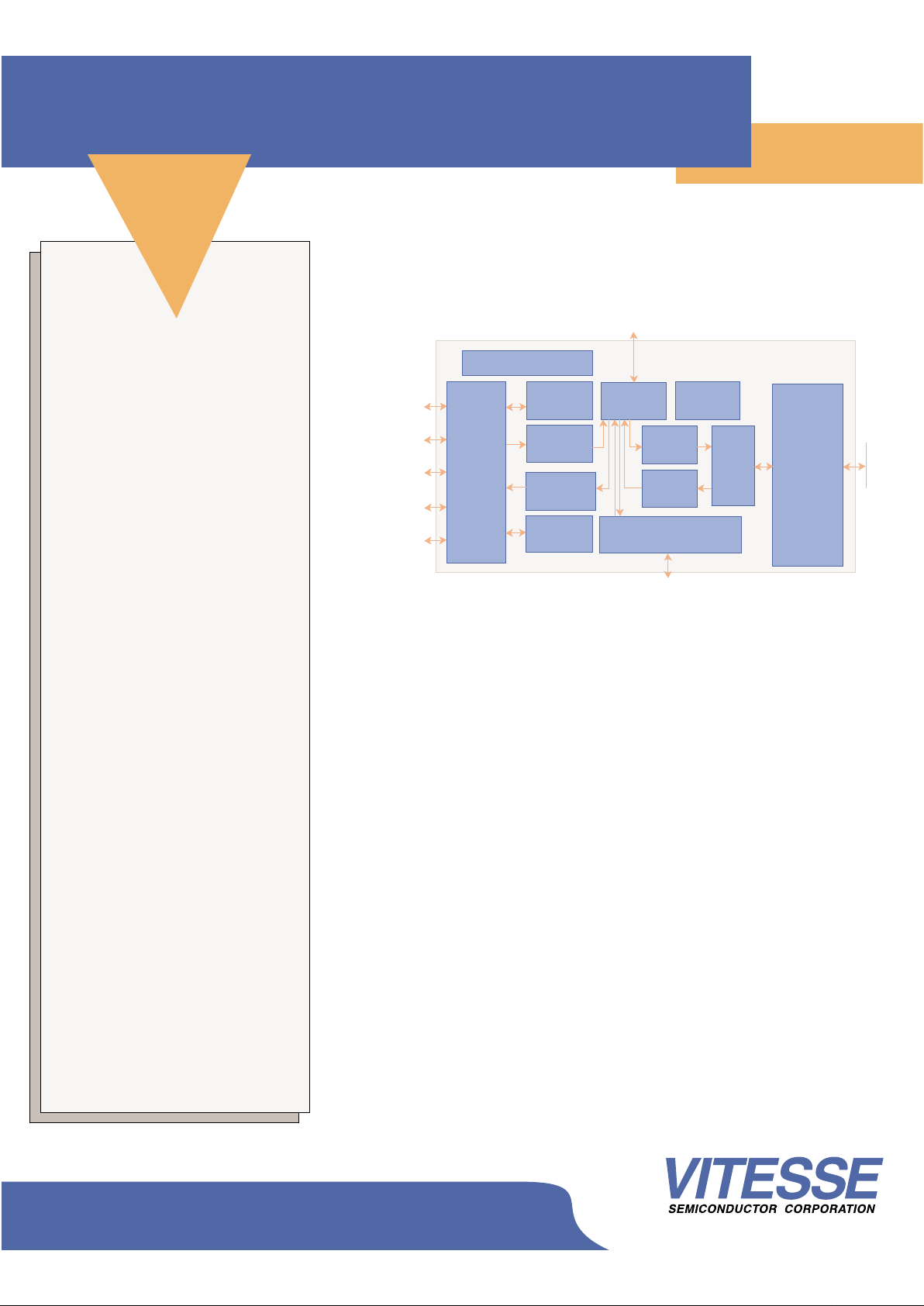

VSC9680 Block Diagram

3 TDMe I/F

H.100 Bus I/F

16 xDSL I/F

unchannelized

Utopia

Level 2

ZBT RAM Interface

28 T1 Framers I/F

32 E1 Framers I/F

PCI

Bus

3 T3/HSSI I/F

unchannelized

Scan +

JTAG

RAM

Interface

Utopia

Interface

32/64-bit

33/66MHz

PCI 2.1

System

Interface

Serial

Bus

Interface

Receive

DMA

Engine

Transmit

DMA

Engine

Arbiter

Clock/Reset Control

Transmit

Channel

Mapping

Transmit

Packet/Cell

Engine

Receive

Packet/Cell

Engine

Receive

Channel

Mapping

For more information on Vitesse Products visit the Vitesse web site

at www.vitesse.com or contact Vitesse Sales at (800) VITESSE or

sales@vitesse.com

© Copyright 2000 Vitesse Semiconductor Corporation

and the Vitesse logo

are all registered trademarks

of Vitesse Semiconductor Corp;oration

www.vitesse.com

Product Brief

TimeStream

Product

Family

2048 Channel HDLC/ATM Controller

VSC9680

Features Continued:

• 32/64-bit 33/66 MHz PCI V2.1

compliant bus interface for system

configuration and packet transfers

• Utopia Level 2 compliant bus in-

terface for ATM cell transfers

• Seamless interface to Vitesse’

VSC9670 and VSC9675 Framers

• IEEE 1 149.1 JT AG boundary scan

• 3.3V CMOS with 5V tolerant I/O

• 388-pin PBGA Packaging

Applications:

• ATM & Frame Relay Switches

• Universal Access Concentrators

• xDSL Access Multiplexors

• Routers

• Wireless Base Station Controllers

Standards:

• ATM Forum af-phy-0039 Utopia

Level 2, version 1.0, 6/95

• ECTF H.100 Hardware Compat-

ibility Specification: CT Bus revision 1.0

• PCI Local Bus Specification, Rev .

2.1, 6/95

• ITU-T Recommendation Q.921,

ISDN User-Network InterfaceData Link Layer Specification,

3/93

• ITU-T Recommendation I.432,

B-ISDN User-Network InterfacePhysical Layer Specification, 3/93

HDLC PACKETS

The VSC9680 performs HDLC flag insertion/ detection, bit stuffing/de-stuffing and CRC-16/32 generation/detection for each transmit and receive channel. On the receive side, packet length

violation, abort sequence detection,

and octet alignment violation are

checked and reported. The packets are

then transferred to host memory via a

scatter-gather DMA controller. On the

transmit side, packets are aborted in

case of underflows, and idle flags are

transmitted between packets.

ATM CELLS

In the receive path, the VSC9680

searches for cell boundaries by framing to the Header Error Check (HEC).

The cell engine then transfers the A T M

cells to an external SAR via a Utopia

Level 2 interface. Abnormal cases are

detected and reported. In the transmit

path, the VSC9680 calculates and inserts an HEC value for the header. Idle

cells are transmitted when there are no

more valid cells to be transmitted.

The VSC9680 uses an efficient scatter-gather DMA engine that minimizes

PCI bus access while transferring packets to and from host memory . External

ZBT SRAM for intermediate FIFO storage improves PCI bus utilization by allowing large burst transfers. The scatter / gather feature allows packet data

to be placed anywhere within a specified address space.

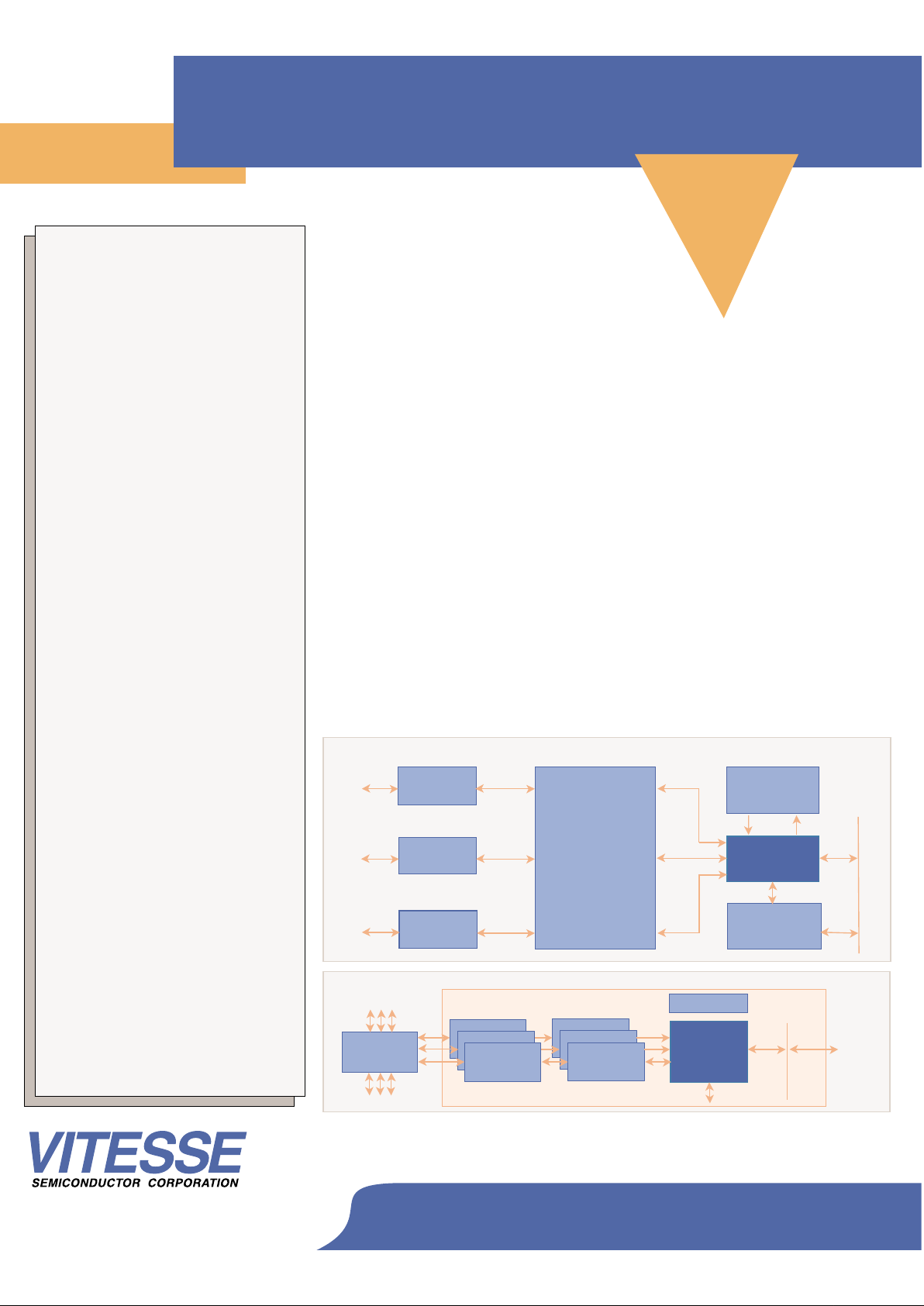

Application Diagrams

VSC9675

VSC9680

HLDC

VSC9680

HDLC/ATM

mode

Voice

Splitter LIU

SRAM

Terminating multiple T3 lines for Frame Relay and ATM using VSC9680 and VSC9675

UTOPIA L2

45 MHz

SRAM

ATM SAR

T3

LIU

T3

LIU

T3

LIU

PCI 32/64

33/66

MHZ

VSC9680 in a DSLAM product

Voice

Processing

Data

Network

PSTN

UTOPIA L2

PCI 32/64

33/66 MHZ

DSLAM

Line Driver

Hybrid

xDSL

DSP

Loading...

Loading...