VITESSE VSC9184 Datasheet

www.vitesse.com

Product Brief

Pointer Processor and Frame Aligner

TimeStream

Product

Family

Telecom Division

VSC9184

Product Description

The VSC9184 is a bi-directional STS48/STM-16, quad STS-12/STM-4 or

quad STS-3/STM-1 Pointer Processor

& Frame Aligner. Section and line termination is performed on line inputs and

outputs in addition to partial path overhead monitoring. Pointer processing is

performed to the STS-1/AU-3 level and

automatically accommodates any valid

combination of concatenated tributaries up to an STS-48c/AU-4-16c. Work-

ing and protection backplane interfaces

are built onto the device with integrated

retiming and deskew, allowing direct

connection to other Timestream devices. This device can be used in

SONET/SDH applications such as

large TSI switches, digital crossconnects and add/drop as well as in

DWDM terminal multiplexer applications.

Features & Benefits:

• Bi-directional STS-48/STM-16,

Quad STS-12/STM-4, or Quad

STS-3/STM-1 Section and Line

Termination Device with Integrated Pointer Processing

• Optional STS-3|12/STM-1|4 to

STS-48/STM-16 Combiner Mode

for Terminal Multiplexer Applications

• Interfaces with other Vitesse

Pointer Processor, TSI, and Backplane ICs

Line Interface

• Terminates and Generates

SONET/SDH Section/Line Overhead

• Serial Ports allow SONET/SDH

Transport Overhead Observation

and Modification

• Designed to Work with VSC8115

155/622 Mhz CDR and VSC8144

2.5G Transceiver

2.5G Pointer Processor

• Performs B3 Path Error Monitor-

ing for all STS-1 Tributaries

• Automatically Accommodates any

Combination of STS-1, STS-3c,

STS-12c, STS-48c Tributaries

and SDH equivalents.

• Extensive Support for Loopback,

Line and Source Timing Configurations.

For more information on Vitesse Products visit the Vitesse web site

at www.vitesse.com or contact Vitesse Sales at (800) VITESSE or

sales@vitesse.com

© Copyright 2000 Vitesse Semiconductor Corporation

and the Vitesse logo

are all registered trademarks

of Vitesse Semiconductor Corp;oration

www.vitesse.com

Product Brief

TimeStream

Product

Family

Pointer Processor and Frame Aligner

VSC9184

TSI Switch

• On Board 48x96 and 96x48 TSI

with STS-1/AU-3 Granularity and

Hitless Reconfiguration

• TSI Can Be Used as First and Third

Layer of Large Switch Architecture

for Collapsed Clos Configuration

Integrated Backplane

• Uses Standard STS-12 Signaling

on Backplane with B1 Byte for BER

Monitoring

• Built in Retiming and Deskew of

STS-12 Backplane Interface up to

+/- 3 Bytes

• Working and Protection 4 x 622.08

Mb/s L VDS STS-12/STM-4 Backplane Interface

Other

• IEEE 1 149.1 JTAG Test Port

• Eight General Purpose I/O Ports

• Thermally Enhanced 474-pin

CBGA Package

• 3.3V I/O and 2.5V Core Power

Supplies

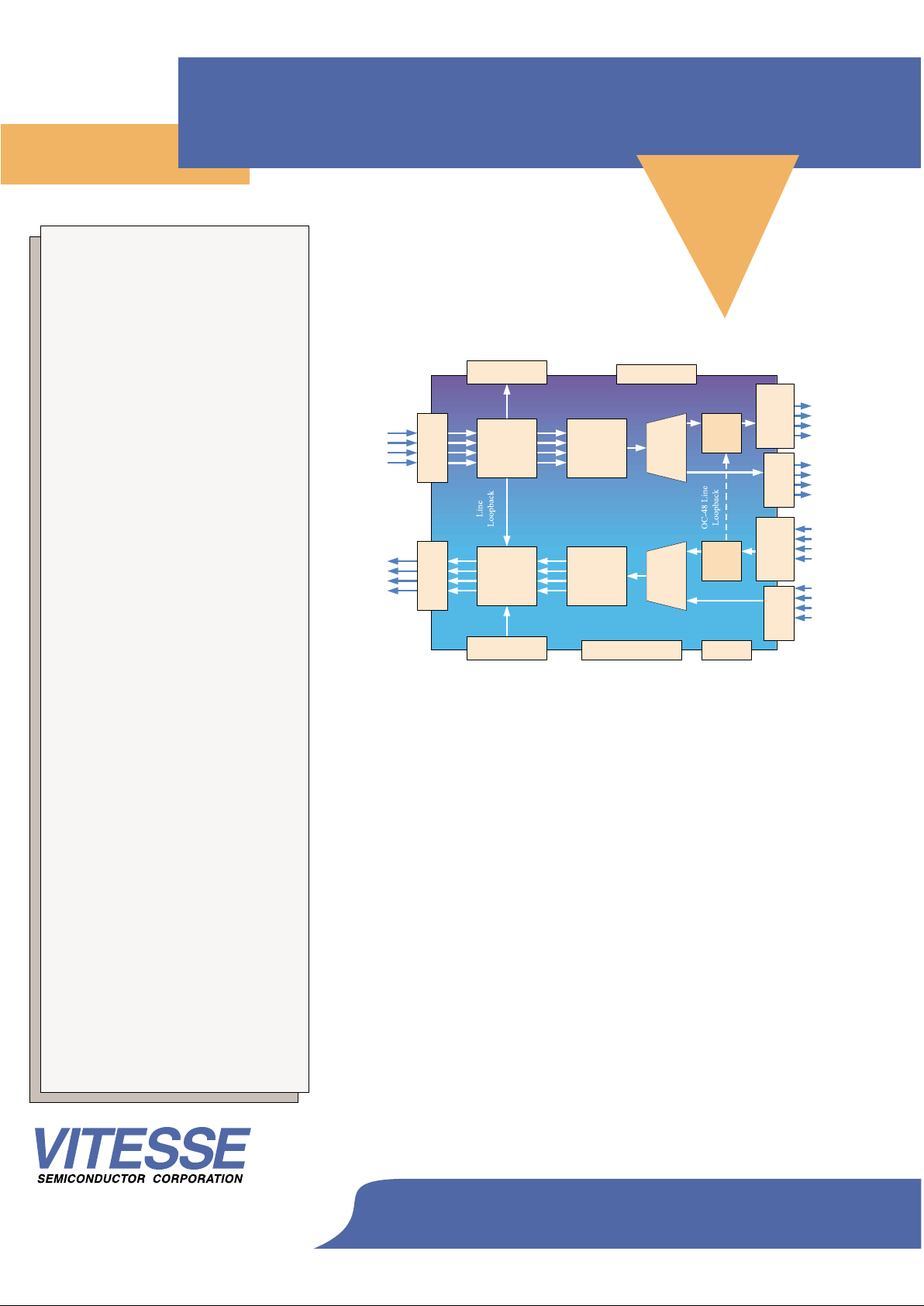

VSC9184 Architectures

Two modes of operation are available: SONET/SDH line interface(s) to working

and protection STS-12 backplane (ADM mode), or multiple OC-3/12 SONET/

SDH line interface(s) to OC-48 line interface (Combiner mode).

ADM Mode: The VSC9184 can interface with one or multiple VSC9182 40G TSI

Switch devices as a line interface solution for large SONET/SDH crossconnects,

providing OC-48 client services or soft programmable quad OC-3/12 services.

Both working and protection ports are provided for interfacing redundant switch

fabrics, and the on board TSI can act as the first and third layer of a collapsed

Clos architecture. The VSC9184 can also interface to other VSC9184 devices

or the VSC9186 10G Pointer Processor and Frame Aligner for small ADM aggregation applications.

Combiner Mode: Four soft programmable OC-3/12 ports can be combined into

an outgoing OC-48. Section and Line Termination, path B3 error monitoring and

serial TOH access is supported on all five interfaces.

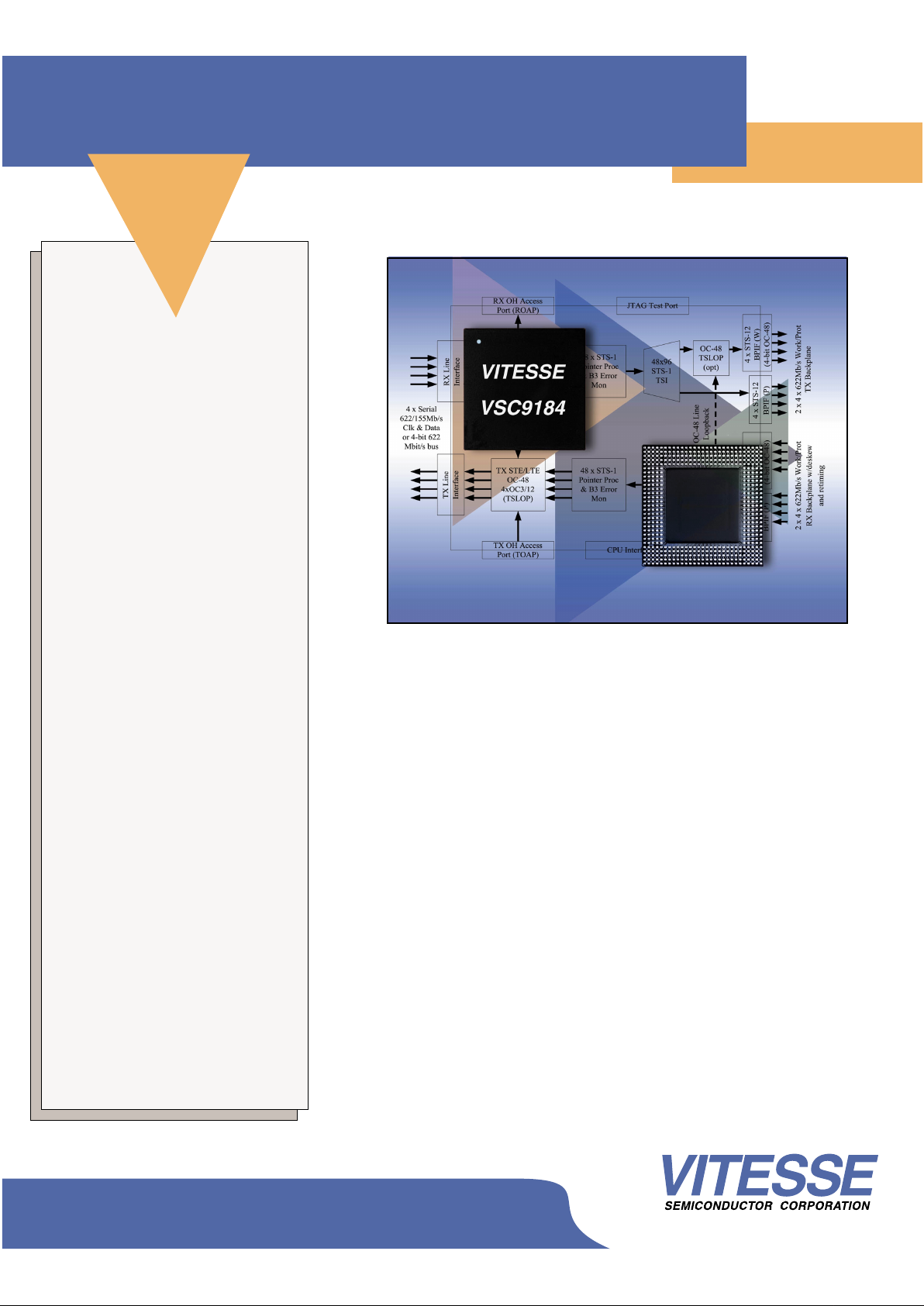

VSC9184 Block Diagram

RX Line

Interface

TX Line

Interface

4 x Serial

622/155Mb/s

Clk & Data

or 4-bit 622

Mbit/s bus

RX STE/LTE

1xOC-48

4xOC3/12

(RSLOP)

TX STE/LTE

OC-48

4xOC3/12

(TSLOP)

RX OH Access

Port (ROAP)

TX OH Access

Port (TOAP)

48 x STS-1

Pointer Proc

& B3 Error

Mon

48 x STS-1

Pointer Proc

& B3 Error

Mon

48x96

STS-1

TSI

OC-48

TSLOP

(opt)

96x48

STS-1

TSI

4 x STS-12

BPIF (W)

(4-bit OC-48)

4 x STS-12

BPIF (P)

4 x STS-12

BPIF (P)

OC-48

RSLOP

(opt)

CPU Interface

2 x 4 x 622Mb/s Work/Prot

TX Backplane

2 x 4 x 622Mb/s Work/Prot

RX Backplane w/deskew

and retiming

4 x STS-12

BPIF (W)

(4-bit OC-48)

GPIO

JTAG Test Port

Loading...

Loading...