VITESSE VSC9182 Datasheet

40G STS-1 Time Slot Interchange

TimeStream

Product

Family

Features & Benefits:

Interconnection Matrix

• Time & Space Switches any STS-

(n) [n= 1, 3c, 12c] Signal of an Incoming STS-12 into any Byte

Position of any STS-12 Output

• Single Stage Non-blocking Struc-

ture of the Switch Allows for

Multicast and Full Broadcast

• Hitless Switching: Programming is

Queued and Takes Effect After

user Intervention During the Next

Frame Boundary

VSC9182

Product Brief

• Unequipped or AIS Signals can be

Substituted into any of the Outgoing STS-1 Timeslots.

• Provides a Capability to Read out

the Switch Configuration (address

map)

Input Backplane Interface

• Serial 622.08 Mb/s Differential

L VDS STS-12/STM-4 Inputs

• Receives 64 Serial 622.08 Mb/s

STS-12/STM-4 Signals.

• Input Signals are Presumed

Frequency Synchronous and

Frame aligned to Within +/- 3

Time Slots of the System

SYNC Input

• Provides On-chip Data Recovery

De-skewing Functionality to Bitalign, Byte-align and Frame-align

all Incoming STS-12s (Within the

above Tolerance) to the Local

Clock

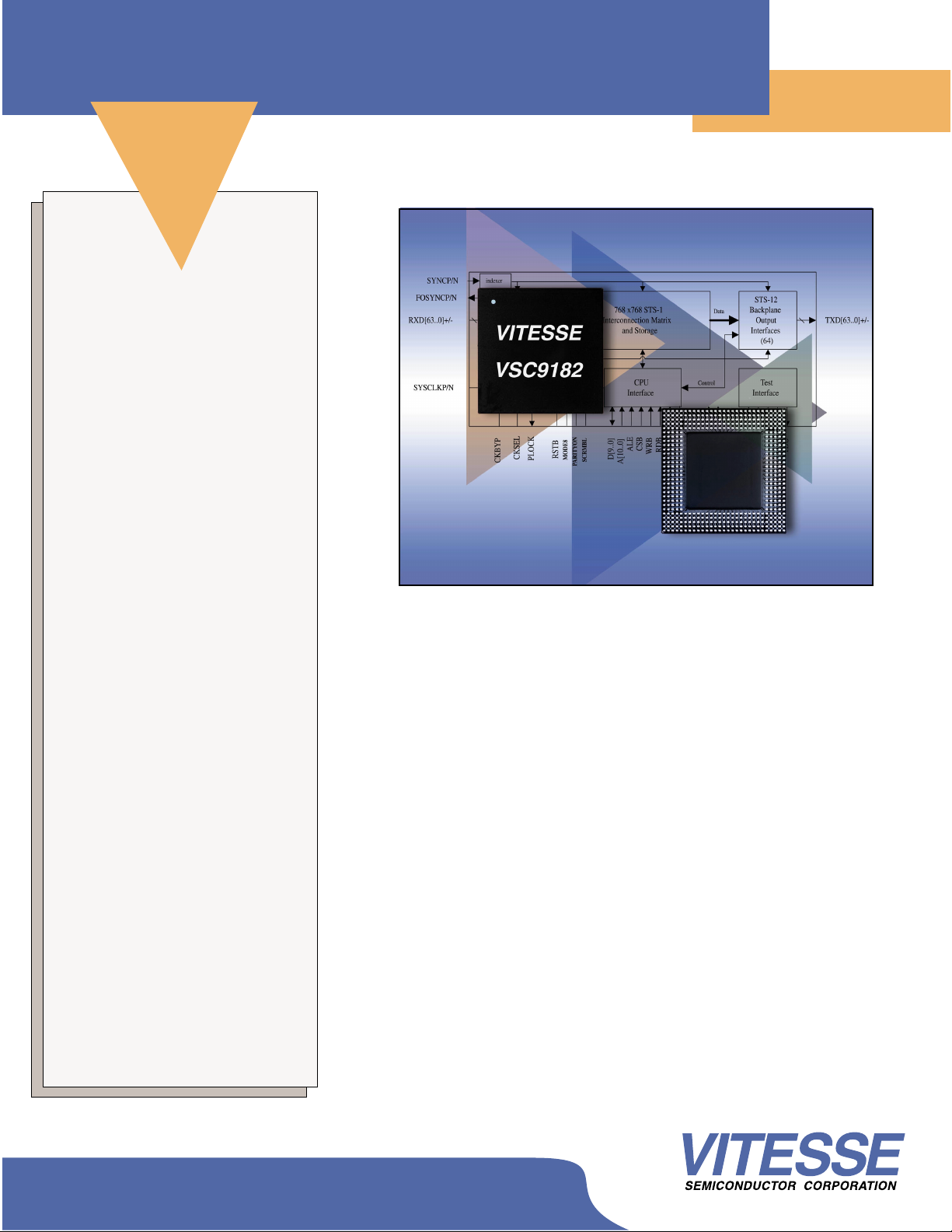

Product Description

The VSC9182 is a 64x64 STS-12/STM4 Time Slot Interchange Switch IC. A

single device provides 40G of nonblocking STS-1 connectivity (768x768

STS-1) with support for concatenated

tributaries. All STS-12/STM-4 inputs

and outputs are differential serial signals running at 622 Mb/s for efficiency

in switch card and system backplane

design. Backplane BER monitoring and

deskew are integrated, and the connection matrix can be hitlessly

reconfigured. Path AIS or UNEQ can

be optionally inserted into all 768 outgoing STS-1 tributaries. A standard

asynchronous CPU interface with event

interrupts is also supported.

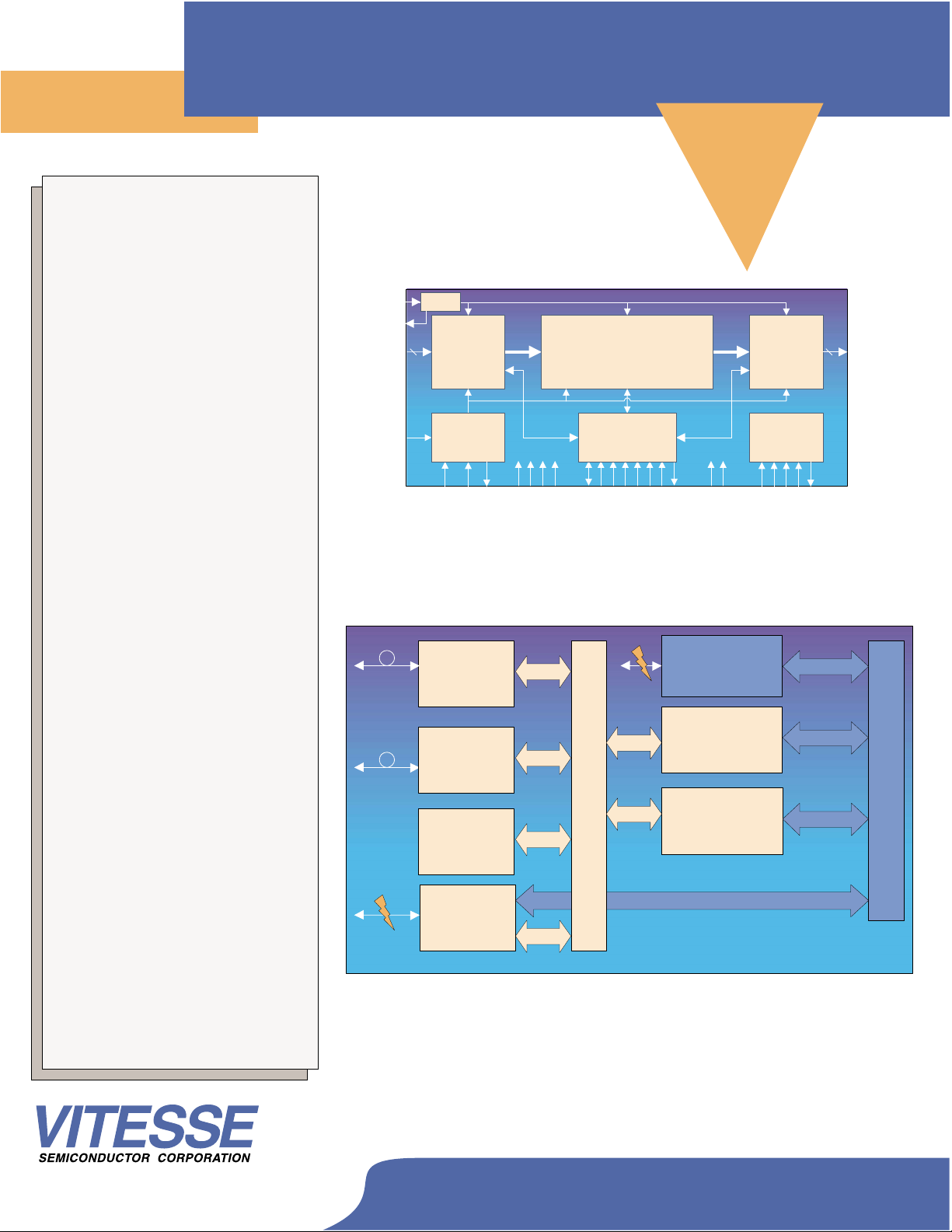

VSC9182 Architectures

A single VSC9182 provides sufficient

connectivity for a 16x16 OC-48 STS-1

grooming solution. Four VSC9182’s in

conjunction with the VSC9184 2.5G

Pointer Processor & Frame Aligner provide a solution for a 64x64 OC-48

grooming solution with support for OC12 and OC-3 tributaries. Multiple

VSC9182 devices can be used in a

three layer Clos architecture to construct larger switches, up to 1024 OC48 ports.. The VSC9182 is designed to

interface directly with the VSC9184 and

VSC9186 2.5G and 10G Pointer Processor & Frame Aligners and VSC9180

2.5G Backplane Transceiver.

www.vitesse.com

Telecom Division

40G STS-1 Time Slot Interchange

INTB

TXD[63..0]+/-RXD[63..0]+/-

SYSCLKP/N

SYNCP/N

D[9..0]

A[10..0]

ALE

CSB

WRB

RDB

RSTB

CKSEL

SCRMBL

TDO

TDI

TCK

TMS

TRSTB

CKBYP

PLOCK

PARITYON

MODE8

CONFIG

IDDQ2

IDDQ1

FOSYNCP/N

STS-12

Backplane

Input

Interfaces

(64)

STS-12

Backplane

Output

Interfaces

(64)

768 x768 STS-1

Interconnection Matrix

and Storage

Test

Interface

Clock

Synthesis

PLL

indexer

CPU

Interface

Clock

ControlControl

Data Data

Product Brief

Input Backplane Interface Cont.

• Flags Out-of-frame (OOF), Loss-

of-signal (LOS) and Parity Errors

• Checks B1 Parity of Incoming Data

• Inserts Unequipped or AIS When

Channel is in OOF, LOS or

Unprovisioned State and Inhibits

Alarms

• Optionally De-scrambles Incoming

SONET Data

Output Backplane Interface

• Serial 622.08 Mb/s Differential

L VDS STS-12/STM-4 Outputs

VSC9182

TimeStream

Product

Family

VSC9182 Block Diagram

• Optionally Inserts Byte-interleaved

Parity into B1 Byte of Following

Frame

• Optionally Scrambles Outgoing

SONET Data

• Optionally Inserts AIS or Un-

equipped on a Per-channel,

Per-time-slot Basis

CPU Interface

• Generic Microprocessor (CPU)

Interface used for Device Configuration and Status Checking

• 10-bit Data Bus and 1 1-bit Address

Bus

• Interrupt Output Pin to Signal

Status Changes of Internal Alarms

Test Interface

• IEEE P1149.1 Test Access Port

Controls External Boundary Scan

www.vitesse.com

TimeStream Diagram

SONET/SDH

Pointer Processors

PHY’s & Analog

SONET/SDH

Pointer Processors

PHY’s & Analog

VT/TU (T1/E1)

Grooming Unit

T1/E1/DS-3 Term

DS-0/DS-1/DS-3

HDLC & M13

For more information on Vitesse Products visit the Vitesse web site

at www.vitesse.com or contact Vitesse Sales at (800) VITESSE or

sales@vitesse.com

4 x OC-48

1 x OC-192

4 x OC-3

4 x OC-12

1 x OC-48

DS-3

T1/E1

Ethernet

TDM

TDM

TDM

TDM

STS-1 level SONET Time Slot Interchange (TSI)

TDM

TDM

© Copyright 2000 Vitesse Semiconductor Corporation

PHY, MAC,

uP

Packet

SONET/SDH Framer

(STS3c - STS48c)

Packet/Cell uP

SONET/SDH Framer

(STS-48c - STS-768c)

Packet/Cell uP

CSIX

and the Vitesse logo

of Vitesse Semiconductor Corp;oration

CSIX

CSIX

CSIX

are all registered trademarks

Layer 2/3/4 Packet/Cell Switch Fabric

Loading...

Loading...