VITESSE VSC837UG Datasheet

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

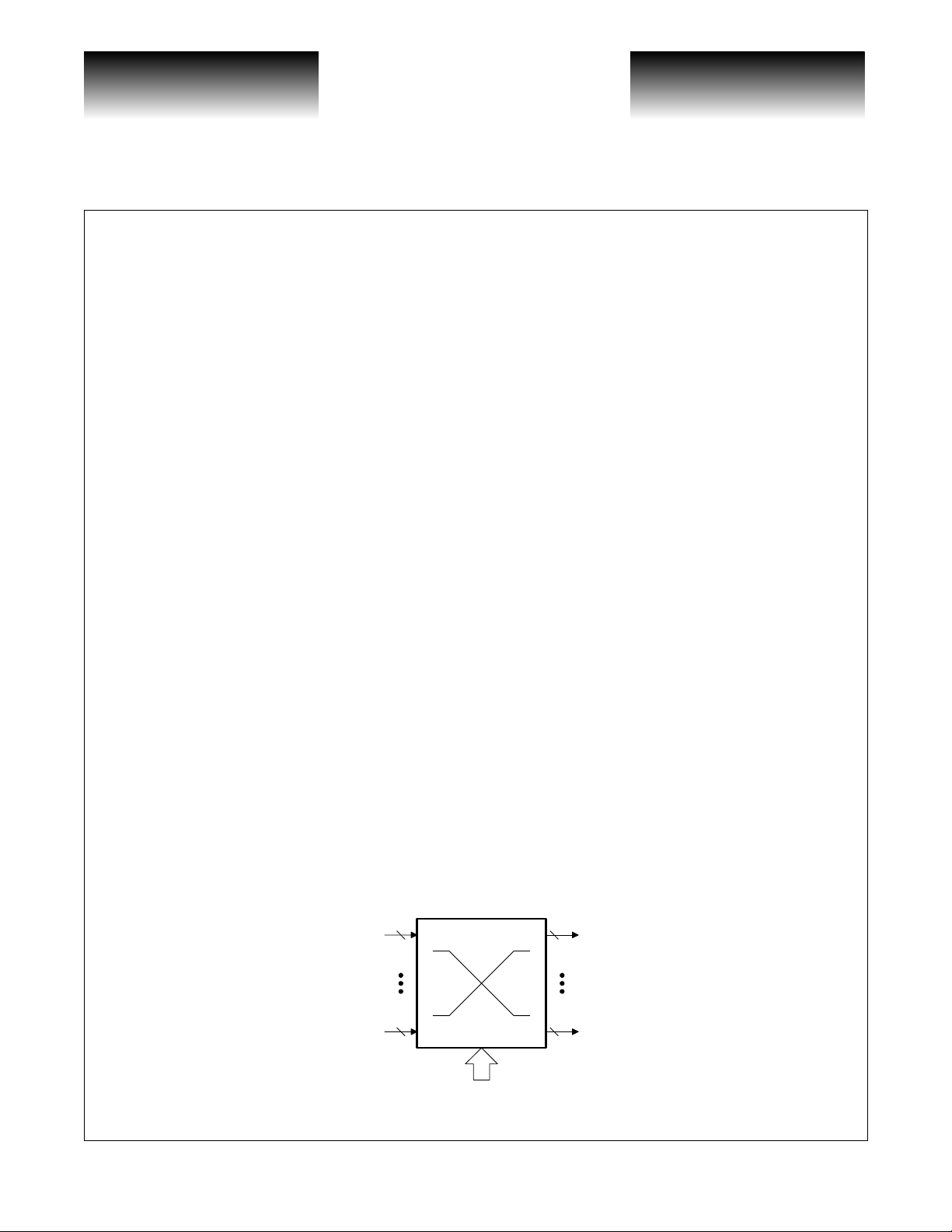

VSC837

68x68 Crosspoint Switch

Features

• 68 Input by 68 Output Crosspoint Switch

• 3.2Gb/s NRZ Data Bandwidth

• 66MHz Multi-Mode Programming Port

• TTL/2.5V CMOS Control I/O (3.3V tolerant)

• Programmable On-Chip I/O Termination

• Input Signal Activity (ISA) Monitoring Function

• Integrated Signal Equalization (ISE) for

Deterministic Jitter Reduction

• Single 2.5V Supply

• Differential CML Output Driver

• 11W typ/14W max (low drive mode)

13W typ/16 W max (high drive mode)

• Hard and Soft Power-Down for Unused Channels

• High Performance 37.5mm, 480 TBGA Package

General Description

The VSC837 is a monolithic 68x68 asynchronous crosspoint switc h, designed to carry broadband data

streams. The non-blocking switch core is programmed through a triple-mode port interface that allows random

access programming of each input/output port. A high degree of signal integr ity is maintained thr oughout the

chip via fully differential signal paths.

The crosspoint function is based on a multiplexer array architecture. Each data output is driven by a 68:1

multiplexer th at can be prog rammed to one and onl y o ne of its 68 inp uts. The s ignal path is u nregis tered and

fully asynchronous, so there are no restrictions on the phase, frequency, or signal pattern at each input.

Each high-speed output is a fully differential switched current driver with switchable on-die terminations

for maximum signal integrity. Data inputs are terminated on die through 100

plement inputs (see Input Termination section for further detail).

A triple-mode programming interface is provided that allows programming commands to be sent as serial

data or one of two forms of para llel da ta. The input -ref erred mode (b urst mode) allows an input por t to be rout ed

to all outputs in only 4 program cycles. Core program ming can be random for each port addre ss, or multiple

program assignments can be queued and issued simultaneously. The programming may be initialized to a

“straight-through” configuration (A0 to Y0, A1 to Y1, etc.) using the INITB pin.

An activity monitor is provided to allow in-system diagnostics. The activity monitor can observe any highspeed input via an internal 69th multiplexe r.

Unused channels may be powered down to allow efficient use of the switch in appl ications that requi re only

a subset of the channels. Power-down can be accomplished in har dware, via ded icated power pins for pairs of

input and output channels, or in software by programming individual unused outputs with a disable code.

Ω resistors between true and com-

3.2Gb/s

VSC837 Block Diagram

2 2

A0

2

A67

µ

P

control

G52309-0, Rev 3.0 Page 1

02/16/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Y0

2

Y67

VITESSE

SEMICONDUCTOR CORPORATION

3.2Gb/s

68x68 Crosspoint Switch

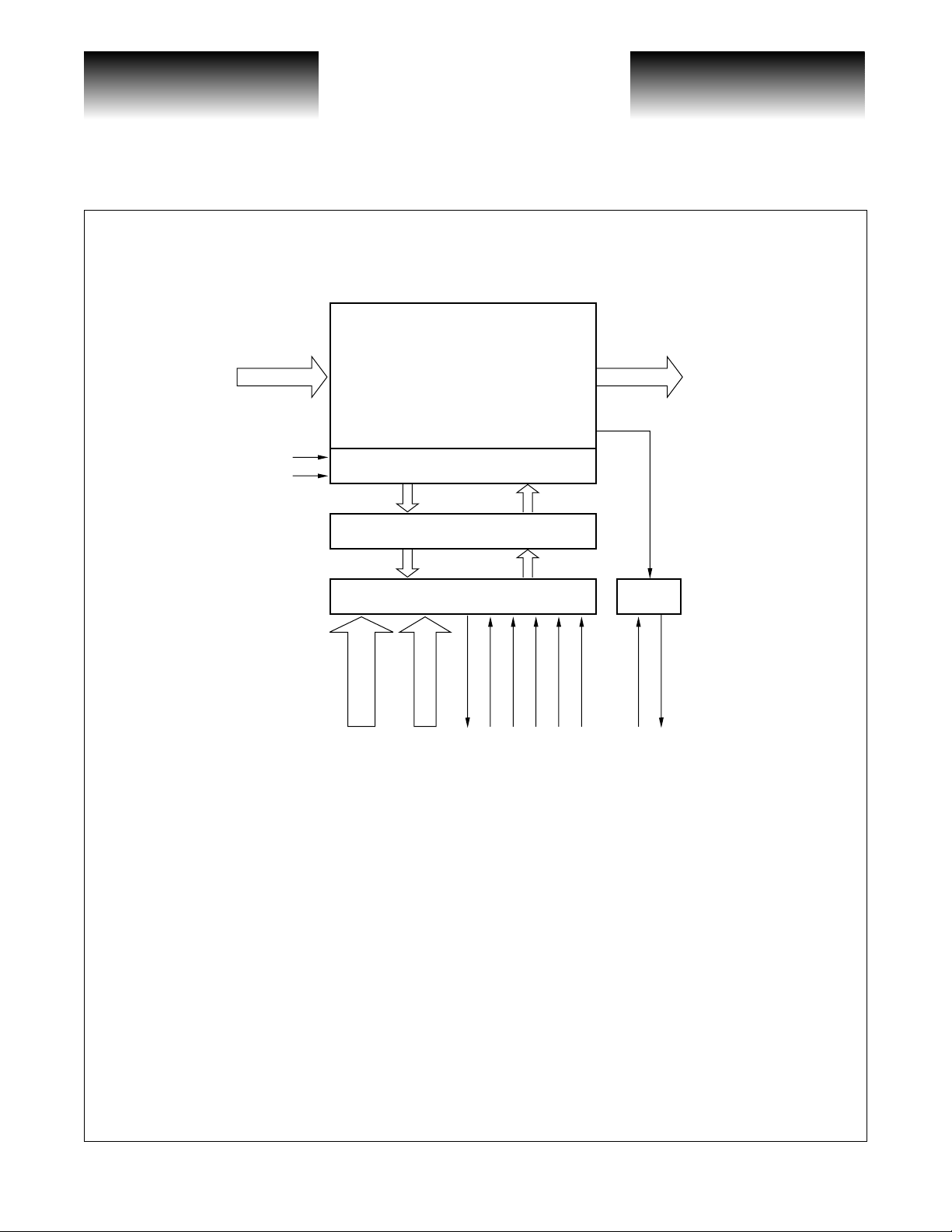

Functional Block Diagram

A, AN[0:67]

CONFIG

INITB

68x69 Switch Core

Core Program Registers

Program Memory

Program Interface

Preliminary Data Sheet

VSC837

Y , YN[0:67]

th

Internal 69

Output

Activity

Monitor

CSB

LOAD

BURST

SDOUT

OUTCHAN[18:0]

INCHAN[6:0]

SERIAL

ALE_SCN

ACTCLK

ACTIVITY

Functional Description

Input / Output Characteristics

All input data must be differential and should be nominally biased to +2.0V or AC-coupled. Other levels

are allowed as described under the Input Termination section. On-chip terminations are provided, with a nomi-

nal impedance of 100

coupling.

For direct interconnection of multiple VSC837 devices, a CML termination mode is provided by tying the

ITC pin to V

CC

loads for an open-drain or open-collector differential output.

Data outputs are provided through differential current switches with on-chip back-termination. The output

circuit is capable of dri ving ex ternal 5 0

electronically switchable to enable a power savings of 2W (max) by reducing the output driver current.

Ω differential. All input termination resistors float with an internal bias provided for AC-

, which ties the center point of the 100Ω te rminatio n to VCC, causing the terminat ions to act as

Ω far-end termination (recommended). The output back -terminatio ns are

Page 2 G52309-0, Rev 3.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/16/01

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC837

68x68 Crosspoint Switch

Programming Interface

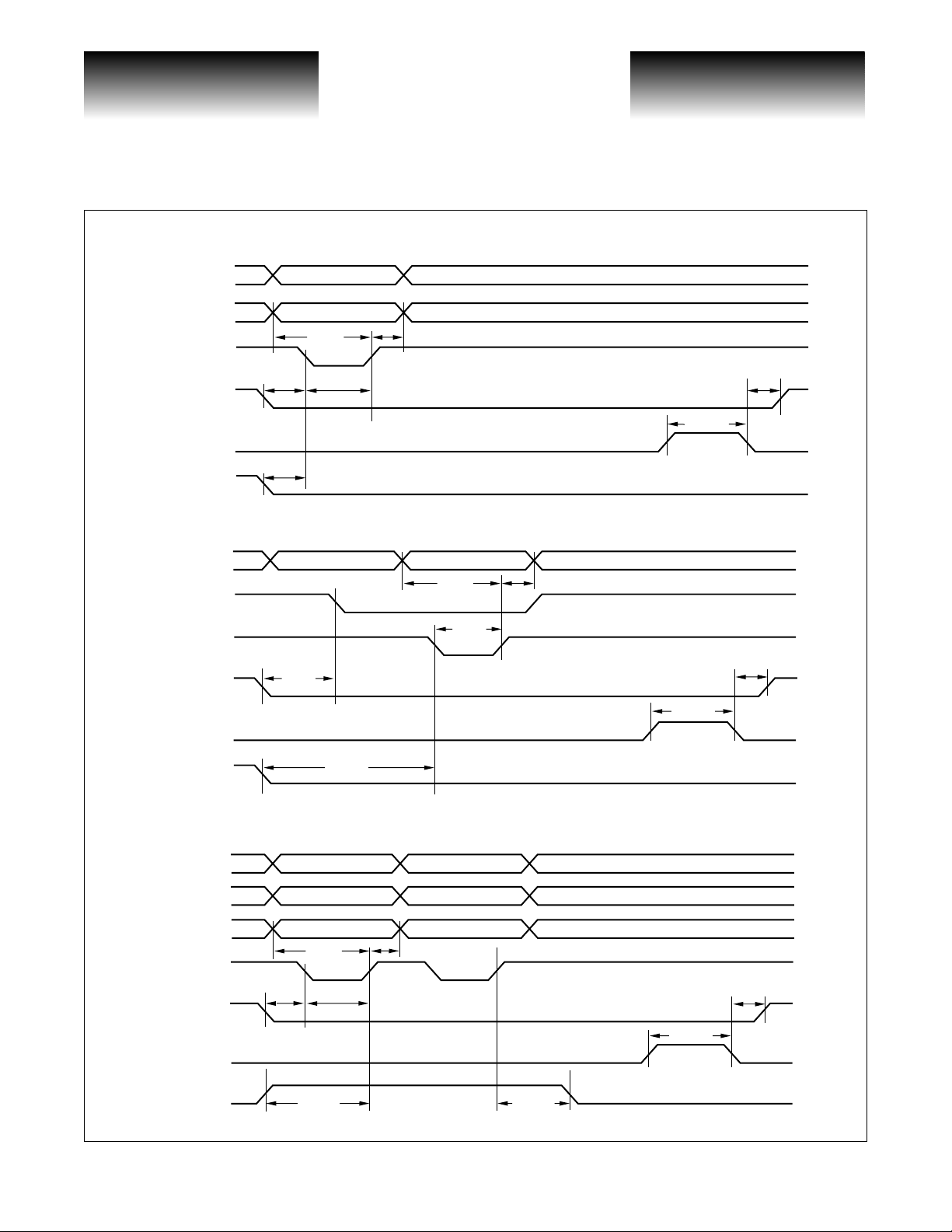

Parallel Mode

In parallel mode (SERIAL=0, BURST=0), the binary word on INCHAN[6:0] is t he numerical identifie r of

the input that will be routed to the specified output. OUTCHAN[6:0] is the numerical identifier of the output

being programmed. A rising edge on the LOAD signal will transfer the programming data to the shadow register in the program me mor y. Raising CONFIG (asynchr onou sly) wi ll t ransf er th e pr og ramm ing data to th e ma in

latches in the program mem ory and cau se the int ernal select signa ls in the core to re-confi gure th e multip lexer.

Lowering CONFIG will latch the main latches. CONFIG may be tied HIGH to enable programming take effect

instantaneously.

This interface may be used with multiplexed address/data buses by using only INCHAN[6:0] without

OUTCHAN[6:0] and dropping ALE when the address of the output to be programmed is present on

INCHAN[6:0]. After the address is latched, the input address may be presented on INCHAN [6:0] and programming proceeds as above.

No read-back capability is provided in parallel mode. Read-back for diagnostic purposes is provided in

serial mode via the scan function.

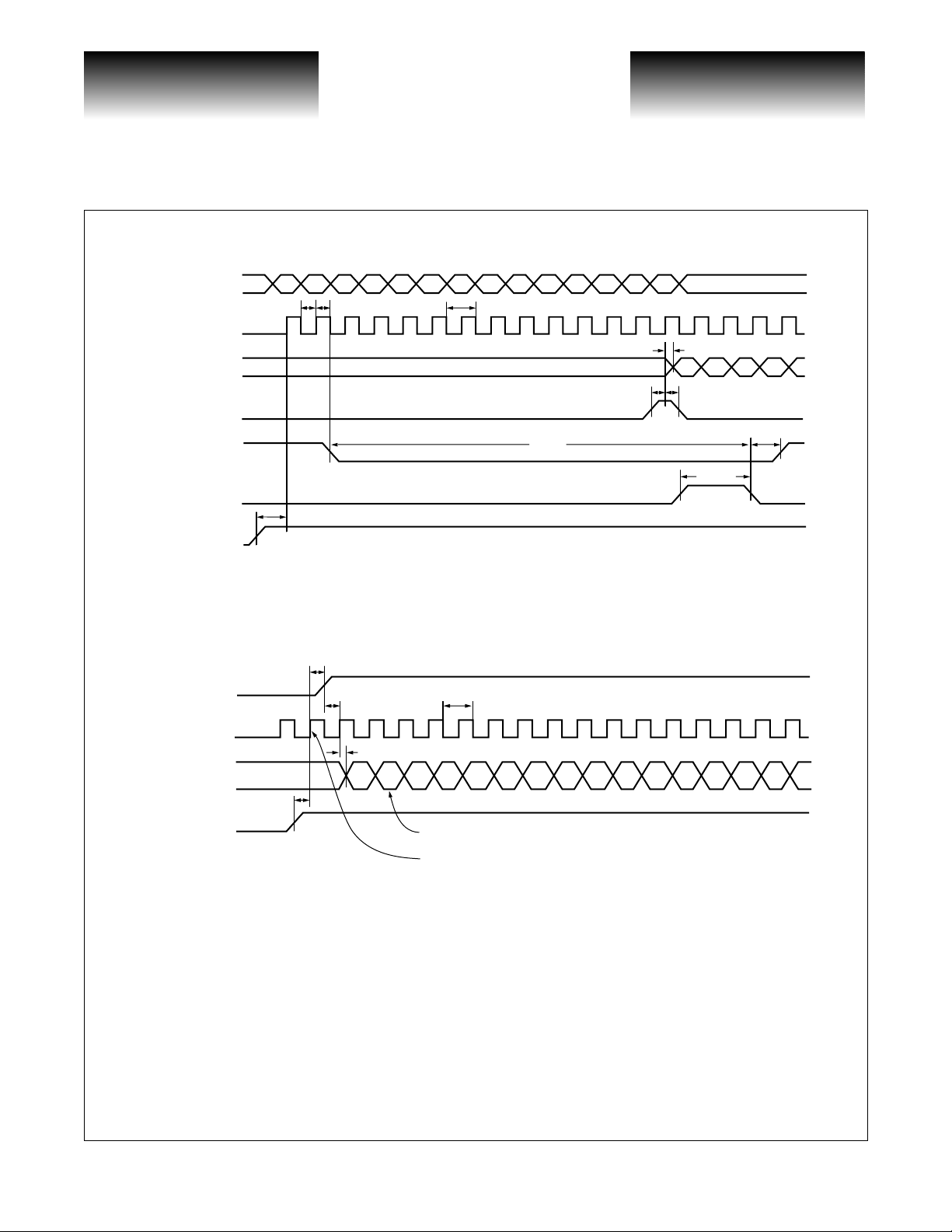

Serial Mode

In serial mode (SERIAL=1, BURST=0), the INCHAN0 pin becomes the serial data input and the

INCHAN1 pin becomes the serial clock (rising edge triggered). A serial word of the form [Output][Input] is

shifted into the internal shift register, and the LOAD pin is asserted (HIGH) coincident with the last bit of the

data word to signal that the word is to be applied. This transfers the input ident ifier to the shado w register of t he

addressed output. CONFIG is then applied (asynchronously) to transfer one or more program commands to the

main latches of the program memories.

The SDOUT pin follows the data on the INCHAN0_SDIN pin 14 clock cycles later. This enables the user

to chain the serial ports of several crosspoints, shift program data for all switches through such a chain, and

assert LOAD on all switches simultaneously to program all of the connections simultaneously.

The output field is 7 bits long, representing the binary numerical identifier of the output to be programmed.

The input field is 7 bits long, representing the numerical identifier of the input that will be routed to the specified output.

3.2Gb/s

Serial Read-Back

Read-back of the program memor y contents is acco mplished in serial m ode by s etting the ALE_SCN pin

HIGH. This will serially shift out the contents of the main latches in the program memories, slice 68 first and

slice 0 last, and MSB-first, LSB-last for each 7-bit word. One rising edge of INCHAN1_SCLK with

ALE_SCN=0 and SERIAL=1 must occur to load the entire 483-bit shift register prior to shifting out data. At a

clock rate of 66MHz, this operation takes 7.26

G52309-0, Rev 3.0 Page 3

02/16/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

µs.

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

3.2Gb/s

68x68 Crosspoint Switch

Burst Mode

Burst mode programming (BURS T=1, SE RIAL=0) e nabl es an input to be broadcast to any group of 1 t o 17

outputs with a single command. In this mode, rising edges on the LOAD pin will trigger program operations.

The INCHAN[6:0] pins represent the input to be broadcast. The OUTCHAN[18:17] pins represent the page

(quarter) of the program memory to access, and each of the OUTCHA N[16:0] pins represent s 1 of the 17 outputs within that page. A ’1’ on any of those pins will cause that output to be programmed to connect to the input

named on INCHAN[6:0].

No read-back capability is provided in burst mode. See Serial Read-Back section above.

Activity Monitoring

The activity monito r observes the output of the internal 69 th output fro m the core. By p rogrammin g the

69th output to observe various inputs, the input signals can be scanned for activity or lack thereof. Each rising

edge of ACTCLK causes the monitor to read out the act ivity state from t he previous ACT CLK period and cl ears

the internal activity state until a data transition triggers it again. There must be a min imum of o ne ri si ng a nd o ne

falling edge on the observed input data pin during the ACTCLK period for activity to be detected. After poweron the output of ACTIVITY after the first ACTCLK rising edge is unknown.

Selective Power-Down

Unused input and output channels can be made to consume little or no power via one of two methods of

selective power-down.

Preliminary Data Sheet

VSC837

Software Power-Down

Using this feature, unused outputs may be disabled, saving approximately 170 mW per channel for maximum dissipation conditions. This is accomplished by programming each unused output to look at input 127 (7F

Hex), which represents a non-existent input channel. The channel may be subsequently activated by programming a valid input address. It is recommended, however, that any changes in power programming only be executed as part of an initialization sequence to guard against the effects of any switching transients that might

result from changing the power supply current sudden ly. Software mode does not affect the functioning or

power of unused input channels.

Hardware Power-Down

Using this feature, the power associated with given pairs of inp uts may be shut of f by ty ing the corresponding V

tion conditions. The power associated with give n pairs of outputs, including their c ontribution to the core

power, can be shut off by tying the corresponding V

output pair is saved under the maximum dissipation conditions.

ing inputs and outputs will always be on and consuming power. See Figure 6 and Table 10 for the location of

these pins.

pin to VCC (see Table 10). Approximately 160 mW per input pair is saved under t he max imum di ssipa-

EE

pin to VCC (see Table 10). Approximately 360 mW per

EE

Certain V

pins must always be active. In oth er words, t ied to t he most ne gative supp ly, so the correspond-

EE

Page 4 G52309-0, Rev 3.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

02/16/01

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC837

68x68 Crosspoint Switch

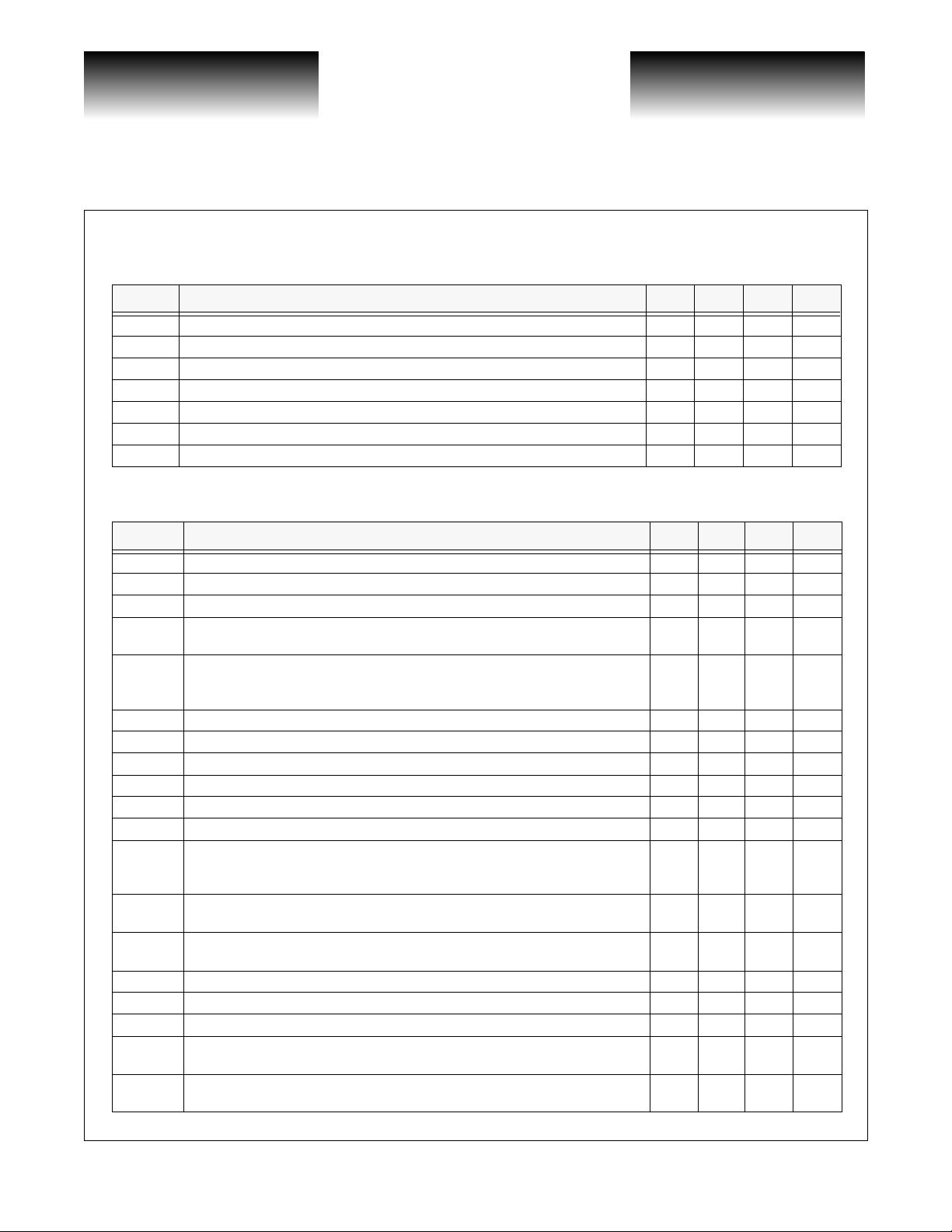

AC Characteristics

Table 1: Data Path

Symbol Parameter Min Typ Max Units

f

RATE

t

SKW

t

PDAY

, t

t

R

, t

t

R

t

JR

t

JP

NOTES:(1) Tested on a sample basis only. (2) Br oadband (unfiltered) deterministic jitter added to a jitter-free input, 223-1 PRBS data pattern.

T a ble 2: Program Interface Timing

Symbol Parameter Min Typ Max Units

t

sWRB

t

hWRB

t

pwLW

t

sCSB

t

hCSB

t

pwCFG

t

sSDIN

t

hSDIN

t

perSCLK

t

sLOAD

t

hLOAD

t

sSERIAL

t

hSERIAL

t

sBURST

t

hBURST

t

dsDOUT

t

pwINITB

t

sSCAN

t

hSCAN

Maximum Data Rate ——3.2 Gb/s

Channel-to-channel delay skew — 300 — ps

Propagation Delay from an A input to a Y output — 750 — ps

High-speed input rise/fall times, 20% to 80% ——150 ps

F

High-speed outpu t rise/fall times, 20% to 80% ——150 ps

F

Output added delay jitter, rms

Output added delay jitter, peak-to-peak

Setup time from INCHAN[6:0] or OUTCHAN[6:0] to rising edge of WRB 3.35 ——ns

Hold time from rising edge of WRB to INCHAN[6:0] or OUTCHAN[6:0] 1.45 ——ns

Pulse width (HIGH or LOW) on LOAD 6.75 ——ns

Setup time from CSB to falling edge of LOAD or ALE_SCN in parallel or burst

mode, or rising edge of LOAD in serial mode.

Hold time of CSB rising edge after LOAD or ALE_SCN rising in parallel or

burst mode, or falling edge of LOAD in serial mode, or falling edge of CONFIG

in any mode.

Pulse width (HIGH or LOW) on CONFIG 6.75 ——ns

Setup time from INCHAN0_SDIN to INCHAN1_SCLK rising 1.65 ——ns

Hold time of INCHAN0_SDIN after INCHAN1_SCLK rising 1.0 —— ns

Minimum period of S CLK in serial mode 15 —— ns

Setup time from LOAD to INCHAN1_SCLK rising 1.85 ——ns

Hold time of LOAD after INCHAN1_SCLK rising 0.95 ——ns

Setup time from SERIAL rising to INCHAN1_SCLK rising when entering serial

mode or SERIAL falling to LOAD falling when entering parallel mode or

SERIAL falling to LOAD rising when entering burst mode.

Hold time from INCHAN1_SCLK rising to SERIAL falling when exiting serial

mode.

Setup time from BURST rising to LOAD rising when entering burst mode or

BURST falling to LOAD falling when entering parallel mode.

Hold time from LOAD rising to BURST falling when exiting burst mode. 2.45 —— ns

Delay from INCHAN1_SCLK rising to SDOUT, 20pF load. ——6.20 ns

Pulse width (HIGH or LOW) on INITB 6.75 ——ns

Setup time from ALE_SCN to INCHAN1_SCLK rising when starting or

completing a serial read-back sequence.

Hold time of ALE_SCN after INCHAN1_SCLK rising when starting or

completing a serial read-back sequence.

(1, 2)

(1, 2)

——10 ps

——40 ps

0 —— ns

0 —— ns

0.90 —— ns

0 —— ns

1.85 —— ns

1.65 —— ns

1.0 —— ns

3.2Gb/s

G52309-0, Rev 3.0 Page 5

02/16/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

3.2Gb/s

68x68 Crosspoint Switch

Figure 1: Parallel Mode—Separate Address/Data (leave ALE_SCN pin HIGH)

OUTCHAN[6:0]

INCHAN[6:0]

LOAD

t

sCSB

CSB

CONFIG

t

sSERIAL

SERIAL

INCHAN[6:0]

ALE_SCN

LOAD

CSB

CONFIG

Preliminary Data Sheet

Output Address

Input Address

t

sWRB

t

pwLW

Figure 2: Parallel Mode—Multiplexed Address/Data

Output Address Input Address

t

sCSB

t

hWRB

t

sWRB

t

pwLW

t

hWRB

t

pwCFG

t

pwCFG

VSC837

t

hCSB

t

hCSB

t

SERIAL

sSERIAL

Figure 3: Burst Mode

OUTCHAN[18:17]

OUTCHAN[16:0]

INCHAN[6:0]

LOAD

CSB

CONFIG

BURST

Page 6 G52309-0, Rev 3.0

Output Page Output Page

Output ID Bits Output ID Bits

Input Address Input Address

t

sWRB

t

sCSBtpwLW

t

sBURST

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

t

hWRB

Internet: www.vitesse.com

t

hBURST

t

pwCFG

t

hCSB

02/16/01

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Data Sheet

VSC837

Figure 4: Serial Mode (leave ALE_SCN pin LOW during programming)

INCHAN0_SDIN

INCHAN1_SCLK

SDOUT

LOAD

CSB

CONFIG

SERIAL

O6 O5 O4 O3 O2 O1 O0 I6 I5 I4 I3

t

sSDIN

t

sSERIAL

O(n) = Output Address Bit (n), I(n) = Input Address Bit (n)

t

hSDIN

t

perSCLK

t

sCSB

I2 I1 I0

t

sLOAD

3.2Gb/s

68x68 Crosspoint Switch

t

dsDOUT

O6 O5 O4 O3

t

hLOAD

t

hCSB

t

pwCFG

ALE_SCN

INCHAN1_SCLK

SDOUT

SERIAL

t

sSERIAL

t

hSCAN

Figure 5: Serial Read-Back

t

sSCAN

t

dsDOUT

68 68 68 68 68 68 68 67 67 67 67 67 67 67

B6 B5 B4 B3 B2 B1 B0 B6 B5 B4 B3 B2 B1 B0

MSB of program memory for output 68

Read-back shift register (483 bits long) is loaded here

on rising edge of INCHAN1_SCLK with SERIAL HIGH

and ALE_SCN LOW

t

perSCLK

66

B6

G52309-0, Rev 3.0 Page 7

02/16/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

3.2Gb/s

Preliminary Data Sheet

68x68 Crosspoint Switch

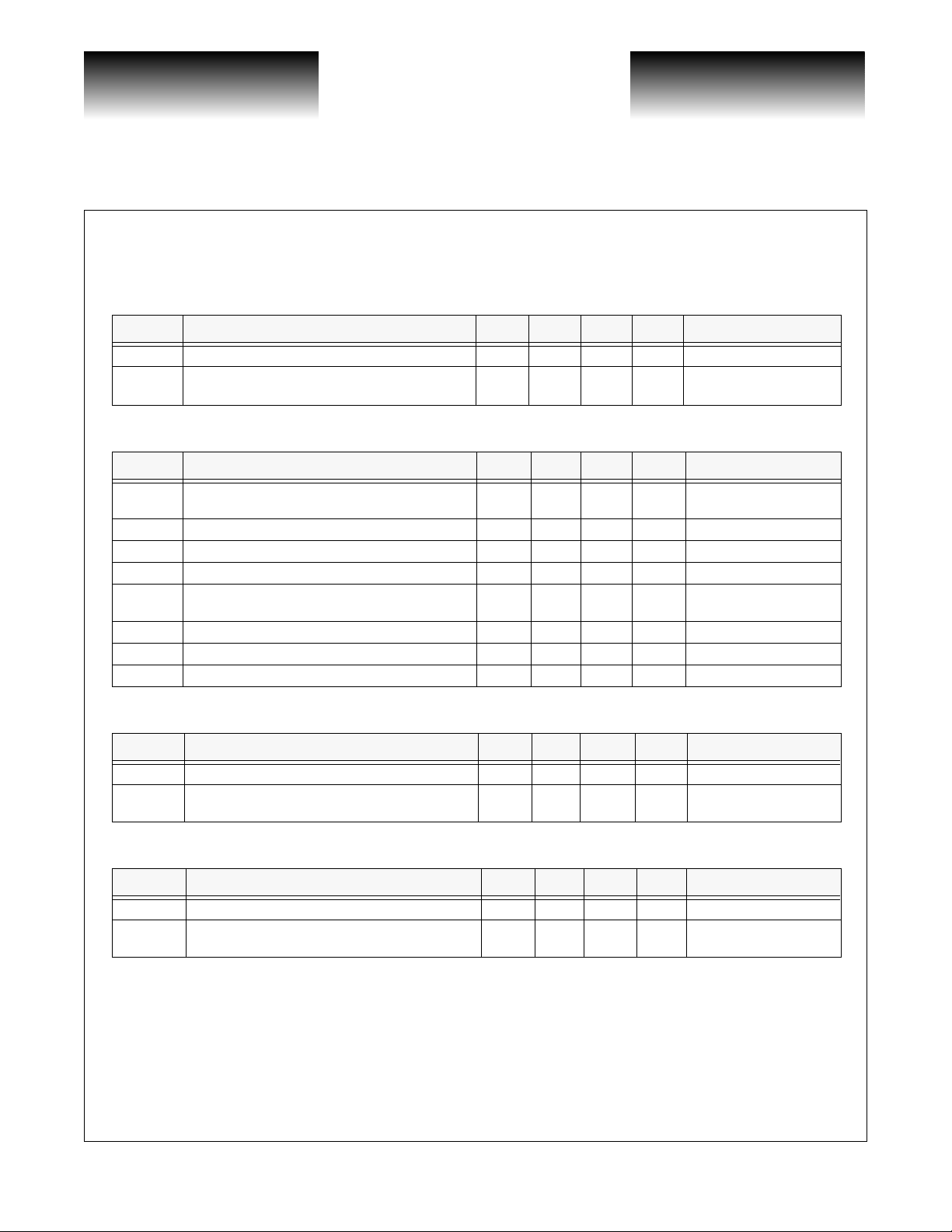

DC Characteristics

All characteristics are over the specified operating conditions.

Table 3: Power Supply Requirements

Symbol Parameter Min Typ Max Units Conditions

I

CC

P

T

Table 4: Control Port Input Levels (TTL/CMOS)

Symbol Parameter Min Typ Max Units Conditions

V

IH

V

IL

I

IH

I

IL

V

OH

V

OL

V

OHPU

V

OLPU

VCC supply current 5600 6095 mA

Total chip power (with I

terminations ON, high drive)

Input HIGH voltage 1.7

Input LOW voltage 0 0.8 V

Input HIGH current TBD µA

Input LOW current TBD µA

Output HIGH voltage

Output LOW voltage 0 0.2 V DC load < 2mA

VOH with external pull-up 2.4 V 250Ω to 3.3V(5%)

VOL with external pull-up 0.4 V 250Ω to 3.3V(5%)

TERM

= 0 and back-

VCC-

0.2

13 16 W

VCC+

1.0

V

CC

V

V DC load < 500µA

VSC837

Table 5: Signal Input Levels (high-speed signal path)

Symbol Parameter Min Typ Max Units Conditions

V

IN

V

ICM

Table 6: Signal Output Levels (high-speed signal path)

Input voltage amplitude 150 1100 mV See Note 1

V

Input common-mode voltage

CC

0.7

-

V

-

CC

0.2

VSee Note 2

TERM_CTRL=ON, DRIVE_CTRL=HI

Symbol Parameter Min Typ Max Units Conditions

V

OUT

V

OCM

NOTES: (1) Mean peak-to-peak amplitude measurement of either true or complement of the differential signal. (2) VCC = V

Page 8 G52309-0, Rev 3.0

Output differe nti al vo lta g e 400 600 mV See Note 1, 3

Output common-mode voltage

(3) Terminated in 50

Ω to V

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

VCC-

0.3

. This termination is used for testing the part, but other termin ations are allowed—see Table 9.

CC

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VCC-

0.2

V See Note 2, 3

= 2.5V, VEE = 0V.

CCP

02/16/01

Loading...

Loading...