VITESSE VSC8144-FECQQ Datasheet

PS031601.3.0

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800)-VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Product Summary

VSC8144-FEC

2.488Gb/s to 2.667Gb/s 4:1 SONET/SDH Transceiver with Integrated Clock Generator

Features

General Description

The VSC8144-FEC is a SONET/SDH compatible multi-rate transceiver with integrated clock generator for use in

SONET/SDH systems operating at OC-48, OC-24, OC-12, OC-3, SONET FEC, or Gigab it Ethernet data rat es. The

internal clock gene rato r us es a Phase Locked Loop (PLL) to mu lti ply ei the r a 77 .76 MHz , 15 5.5 2M Hz, or 622.08MHz or

(associated FEC rates) reference clock for internal logic and output retiming. The 4-bit parallel LVDS interface

incorporates an on -board FI FO to address lo op timing de sign issues. Facility an d Equipment Loopbacks ca n be

configured separ ately or sim ultaneously. The device oper ates with 2. 5 W maximum powe r and is packa ged in a

thermally enhanced 100-pin PQFP package.

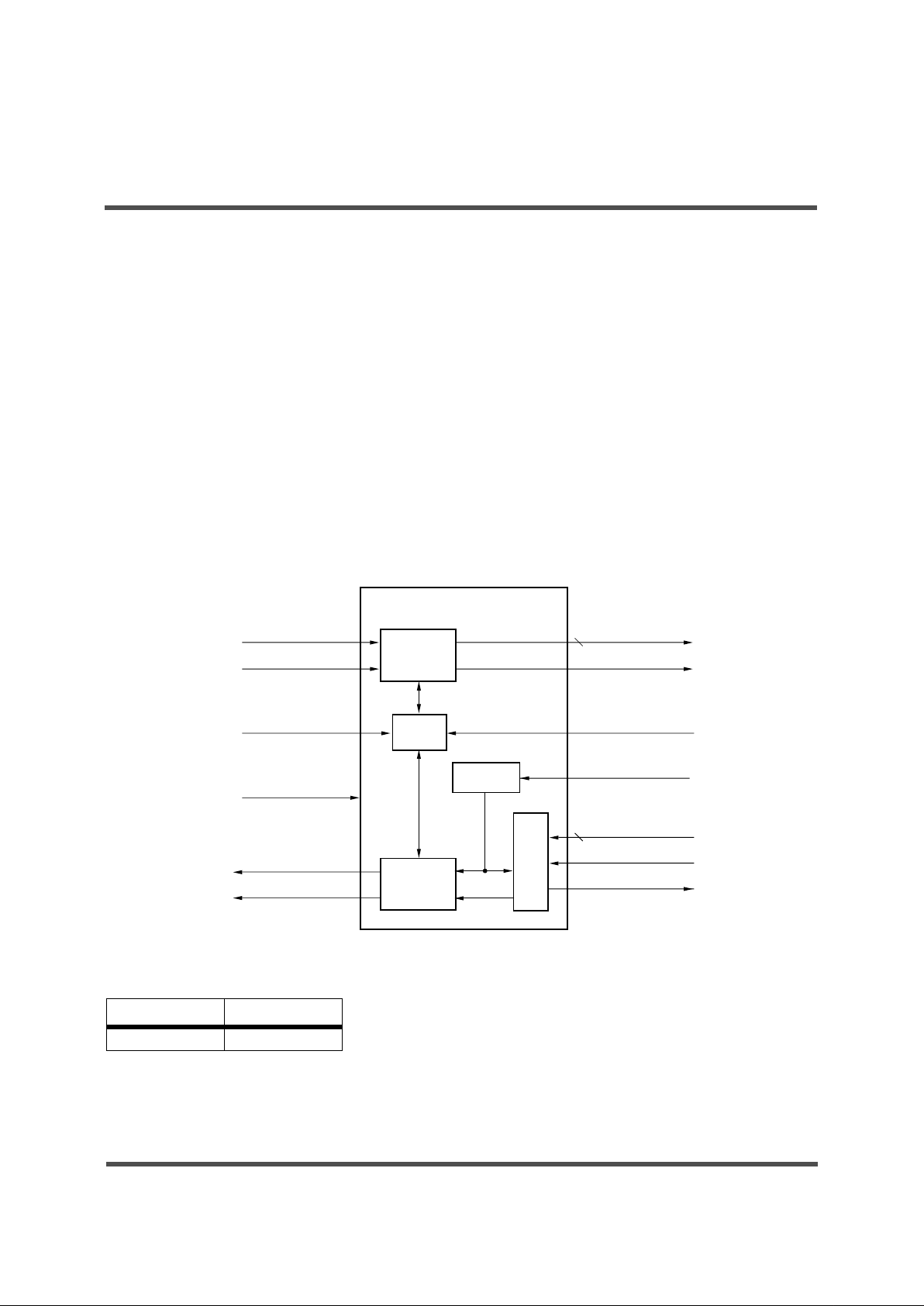

Block Diagram

Order Information

Notice

Vitesse Semiconductor Corporation (“Vitesse”) provides this document for informational purposes only. This document contains pre-production information about Vitesse products in their concept, development and/or testing phase. All information in this document, including descriptions of features, functions, performance, technical

specifications and availability, is subject to change without notice at any time. Nothing contained in this document shall be construed as extending any warr anty o r

promise, express or implied, that any Vitesse product will be available as described or will be suitable for or will accomplish any particular task.

Vitesse products are not intended for use in life support appliances, devices or systems. Use of a Vitesse product in such applications without written consent is prohibited.

Product Package

VSC8144-FECQQ 100-Pin PQFP

• Multi-Rate Transceiver for SONET OC-48, OC-24,

OC-12, OC-3, SONET FEC and Gigabit Ethernet Rates

• 4-Bit LV DS Low-Speed Interfa ce

• On-Chip PLL-Based Clock Generator

• High-Speed Clock Output

• Equipment, Facility and Split Loopback Modes

• Exceeds Bellcore Jitter Performance

• Single 3.3V Power Supply

• 2.5 W Maximum Power Dissipation

• 100-Pin PQFP (14x14x2mm)

DEMUX

CMU

Test

FIFO

High-Speed Data

High-Speed Clock

High-Speed Loopback

Low-Speed Data

Low-Speed Clock

Low-Speed Loopback

Reference Clock

MUX

High-Speed Data

High-Speed Clock

Low-Speed Data

4

Low-Speed Clock

Low-Speed Clock

OC-48/12/3 GbE/FEC

Control

VSC8144-FEC

4

Loading...

Loading...