VITESSE VSC8122-FECQP Datasheet

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

VSC8122-FEC

Multi-Rate SONET/SDH FEC

Clock and Data Recovery IC

G52300-0, Rev 4.1 Page 1

03/01/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Features

General Description

The VSC8122-FEC is a single chip clock recovery IC for use in SONET OC-48, OC-24, OC-12, OC-3, or

Gigabit Ethernet systems operating at their respective 2.488Gb/s (up to 2.66606Gb/s FEC), 1.244Gb/s,

622Mb/s, 155Mb/s, or 1. 25Gb/s data rates. It compl ies wit h SONET jitt er tole rance, jitter tran sfer and jit ter generation specifications.

Alarm functions support typical telecom system applications. The Loss of Lock (LOL) output indicates

when the device goes out of lock, which would most often occur in the event of a loss of valid data. The

NOREF output flags when the reference input to the VSC8122-FEC either is removed, or goes severely out of

tolerance.

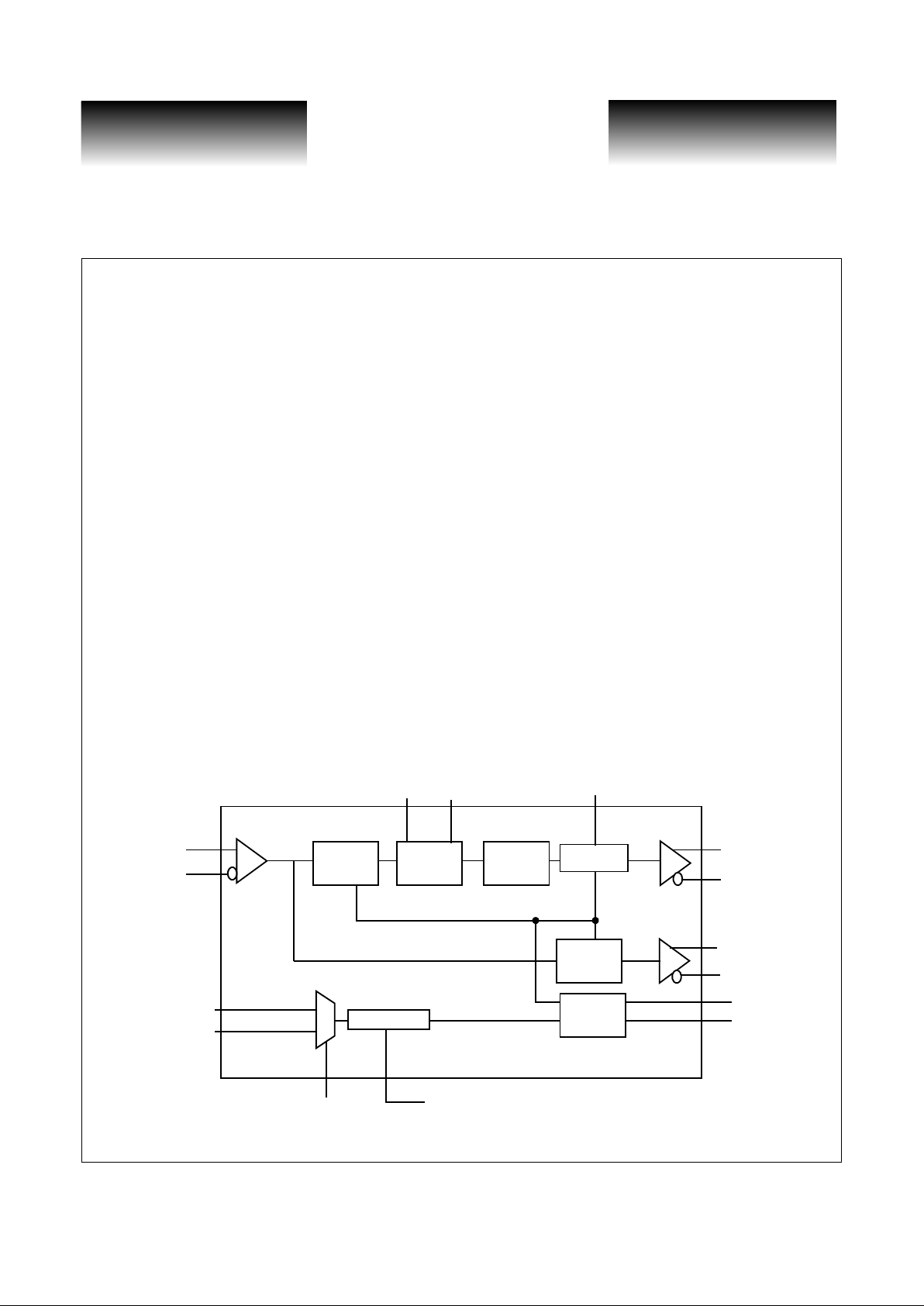

VSC8122-FEC Block Diagram

• Multi-Rate OC-3, OC-12, OC-24, OC-48 Clock

and Data Recovery

• Supports OC-48 FEC Rates

• Supports Gigabit Ethernet

• Differential Back Terminated I/O

• Maintains Clock Output in the Absence of Data

• Selectable Reference Clock

• Loss of Lock Indicator

• Exceeds SONET/SDH Requirements for Jitter

Tolerance, Jitter Transfer and Jitter Generation

• 3.3V Supply Operation

• 1W Typical Power

• 10x10 mm 64-Pin PQFP Packaging

DI+

DI-

Ph/Freq.

Detector

Loop

Filter

VCO

Data

Retiming

Lock

Detect

CO+

CO-

DO+

DO-

LOL

NOREF

REFCK1 +/REFCK0 +/-

REF_SEL[1:0]

REF_INPUTSEL

FSEL[1:0]

Divider

Divider

FILTI+/-

FILTO+/-

Multi-Rate SONET/SDH FEC

Clock and Data Recovery IC

Data Sheet

VSC8122-FEC

VITESSE

SEMICONDUCTOR CORPORATION

Page 2 G52300-0, Rev 4.1

03/01/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Functional Description

Data Input

The data input receiver is internally terminated by a center-tapped resistor network. For differential input

AC-coupling, the network is terminated to the appropriate termination voltage, VTERM through a blocking

capacitor, C

AC

, to ground. The input requires a differential signal with a peak-to-peak voltage on both the true

and complement of a minimum of 250mV. These inputs are required to be AC-coupled to permit use with a

variety of limiting amplifiers

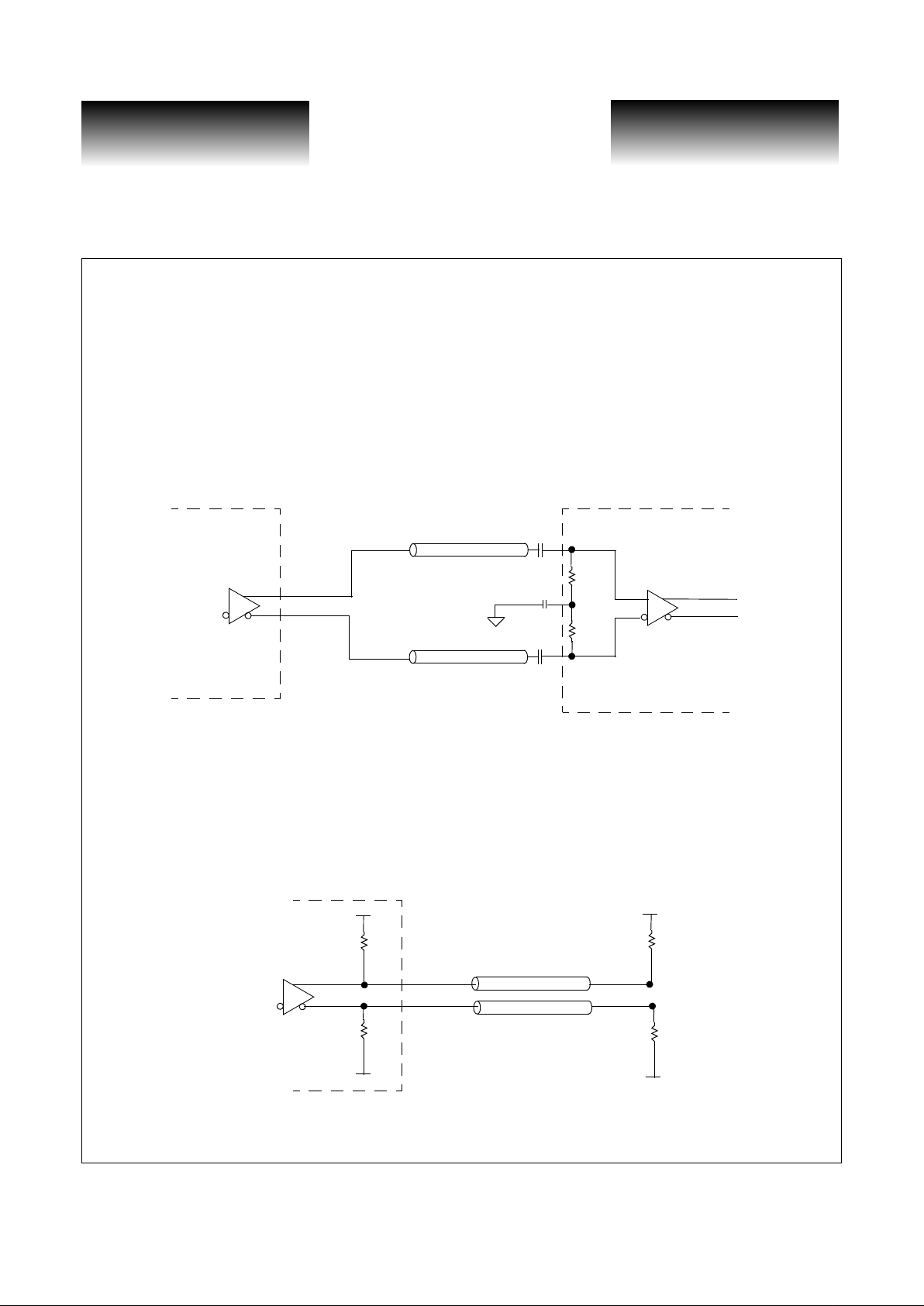

Figure 1: Input Termination (AC coupled)

High-Speed Clock and Data Outputs

The VSC8122-FEC high-speed clock and data outputs can be DC terminated, 50Ω to VCC as indicated in

Figure 2.

Figure 2: High-Speed Clock and Data Output DC Termination.

VSC8122-FECLimiting Amp

0.1 µF

0.1 µF

DI+

DI-

Zo = 50Ω

Z

o

= 50Ω

50Ω

50Ω

VTERM

C

AC

VSC8122-FEC

Zo = 50Ω

Z

o

= 50Ω

V

CC

V

CC

V

CC

50Ω

50Ω

100Ω

100Ω

CO+ / DO+

CO- / DO-

V

CC

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

VSC8122-FEC

Multi-Rate SONET/SDH FEC

Clock and Data Recovery IC

G52300-0, Rev 4.1 Page 3

03/01/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

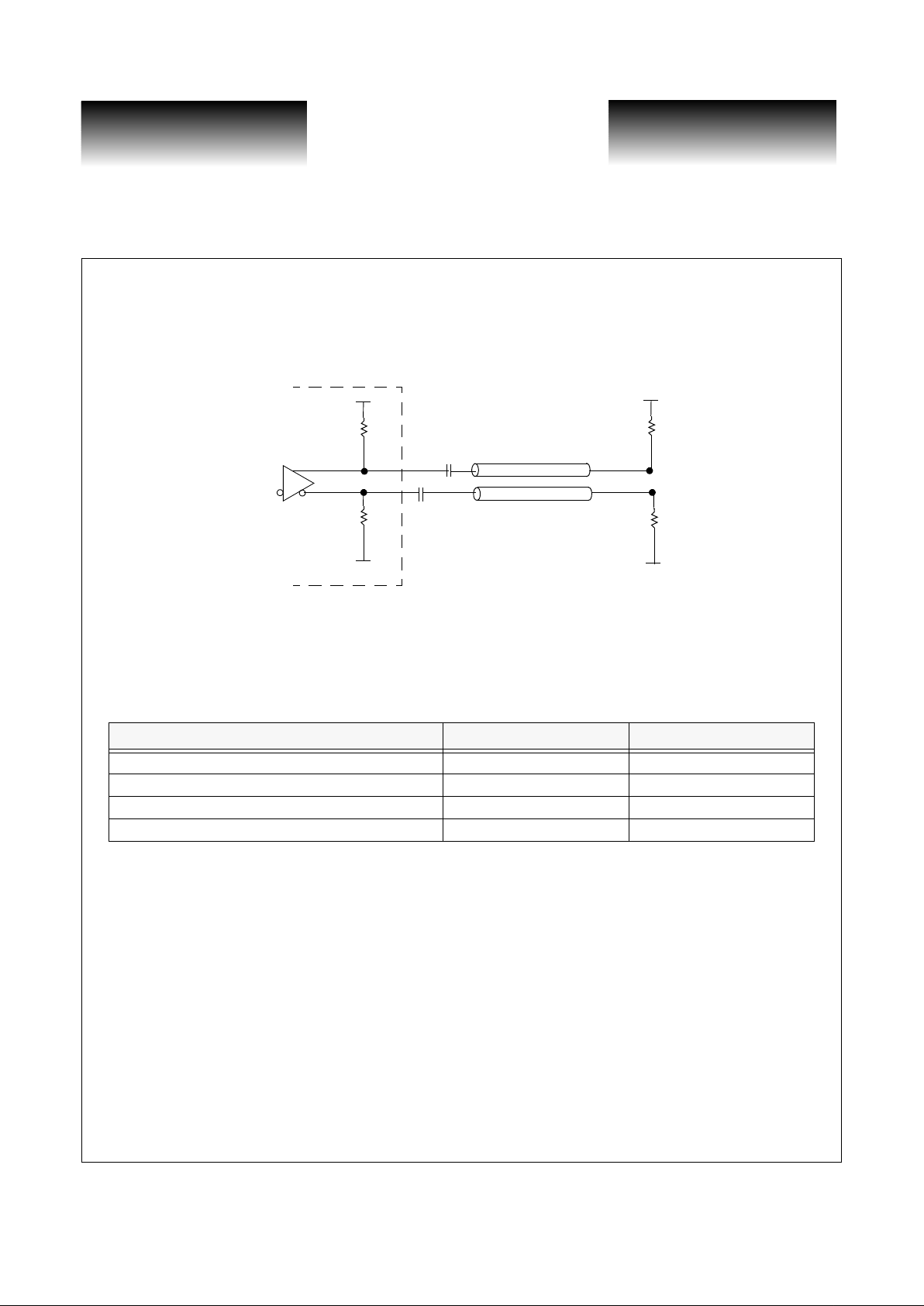

Outputs can also be AC terminated as shown in Figure 3. The output differential voltage and common-

mode voltage range are specified in Table 4, High-Speed Inputs and Outputs

.

Figure 3: High-Speed Clock and Data Output AC Termination.

Clock Recovery

The VSC8122-FEC has a selectable input dat a rat e. Two pins (FSEL0 and FSEL1) select the data rate to be

provided to the VSC8122-FEC.

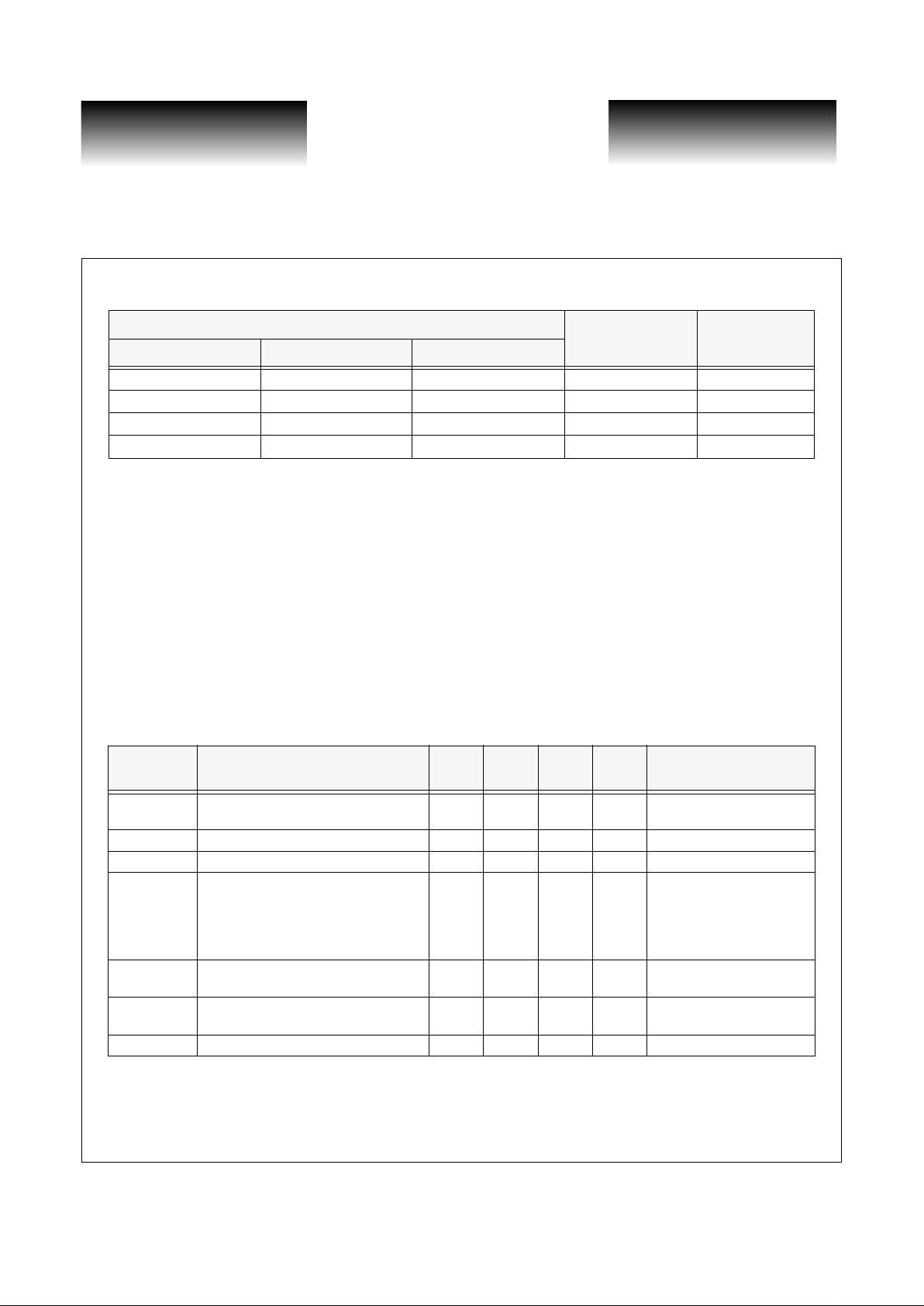

Table 1: Input Data Rate Select

The incoming data is presented both to the clock recovery circuit and the data retiming circuit. When there

is a phase error between the i ncoming data a nd the on- chip VCO, th e loop filter raises or lowers the control voltage of the VCO to null the phase difference.

The lock detector monitors the frequency difference between the REFCK (optionally divided by a prescaler), and the recovered clock divided by 128. In the event of the loss of an input signa l, or if the input is

switching randomly, the VCO will move in one direct ion. At t he time th e VCO dif fe rs by more than 1MHz from

the REFCK based 2.488GHz rate (up to 2.66606Gb/s FEC), the lock detector will assert the LOL output. LOL

is designed to be asserted from between 2.3µs and 100µs after the interruption of data. The VCO will continue

to be frequency-locked at approximately 1MHz off of the REFCK based 2.48832GHz rate (up to 2.66606Gb/s

FEC).

When NRZ data is again presente d at the d ata inp ut, the p hase dete ctor w ill permi t the VC O to lock to the

incoming data. Hysteresis is provided which delays the deassertion of LOL until approximately 160us following the restoration of valid data.

Input Data Rate FSEL0 FSEL1

2.488Gb/s - 2.66606Gb/s

00

1.244Gb/s or 1.25Gb/s

10

622Mb/s or 625Mb/s

01

155.52Mb/s or 156.25Mb/s

11

VSC8122-FEC

Zo = 50Ω

Z

o

= 50Ω

V

TERM

V

TERM

V

CC

V

CC

50Ω

50Ω

100Ω

100Ω

CO+ / DO+

CO- / DO-

0.1 µF

0.1 µF

Multi-Rate SONET/SDH FEC

Clock and Data Recovery IC

Data Sheet

VSC8122-FEC

VITESSE

SEMICONDUCTOR CORPORATION

Page 4 G52300-0, Rev 4.1

03/01/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

The NOREF output will go high to indicate that there is no signal on the REFCK input, o r that the REFCK

is more than approximately 25% above or below the expected value.

Two sets of reference frequencies for the VSC8122-FEC are shown in Table 2. SONET reference cl ock fr equencies are as indicated, with Gigabit Eth ernet frequen cie s list ed in parenthesis. FEC rate frequencies are indicated at rates for use with the VSC9210 FEC device operating at 2.65Gb/s. The two different sets of reference

clocks are needed since the reference clock for SONET and Gigabit Ethernet application s will be slightly dif ferent. Internally, the VSC8122-FEC requires a 19.44MHz reference (or 19 .53MHz r eference for Gig abit Ethernet).

The customer can select to provide either the 19.44MHz reference (or 19.53MHz reference for Gigabit

Ethernet), or the 2x, 4x or 8x of that reference at 38.88MHz (39.06MHz), 77.76MHz (78.13MHz) or 155MHz

(156.25MHz). For FEC rates, the customer can select the appropriate frequency as indicated in Table 2. The

REF_SEL[1:0] inputs will program the internal divider as required to use the selected REFCK frequency.

Two reference clock inputs are provided, REFCK1 and REFCK0, to allow “on the fly switching” between

SONET and Gigabit Etherne t appl icati ons if de sired . Since S ONET and Gi gabit Et hern et requi re di ff eren t refer ence clock frequencies, the VSC8122-FEC allows the user to toggle between the two reference clock frequencies REFCK1 and REFCK0 to supply the appropriate input clock. REF_INPUTSEL is used to toggle between

the two reference clock input frequencies. REF_INPUTSEL= “0” selects REFCK0, REF_INPUTSEL= “1”

selects REFCK1. Either ref erence c lock input (REF CK1, REFC K0) can be used f or SONET or Gig abit Et hernet

reference frequencies. PECL levels are recommended fo r REFCK input s (see Figure 4). If a reference clock is

unused, it is recommended that one of its inputs be tied to VCC through a 5.1kΩ resistor, the other one to GND

through a 5.1kΩ resistor.

Figure 4: REFCK Input Levels

REFCK0 /

VSC8122-FEC

REFCK1

PECL Level REFCK Inpu ts (recommended)

NON- PECL Level REFCK Inputs

50Ω

V

TERM

** For differential REFCK input signals, 100Ω termination between true and complement

REFCK signals can be su bstituted for the 50Ω to V

TERM

termination on each line.

* V

TERM

can be to any power supply, as long as PECL levels are supplied to REFCK inputs.

Typically, V

EE

(typ. GND) is us ed as V

TERM

.

VSC8122-FEC

0.1µf

REFCK0 /

50Ω

V

TERM

REFCK1

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

VSC8122-FEC

Multi-Rate SONET/SDH FEC

Clock and Data Recovery IC

G52300-0, Rev 4.1 Page 5

03/01/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Table 2: Reference Frequency

NOTES: (1) Indicates FEC reference clock frequency for use wit h VSC9210 FEC d evice running at 2.65Gb/s. (Ref erence clock

frequencies can operate at f requencies up to 2.666 06GHz / Y, where Y = 16, 32, 64, 128.). (2) I ndicates recommended

reference clock frequencies.

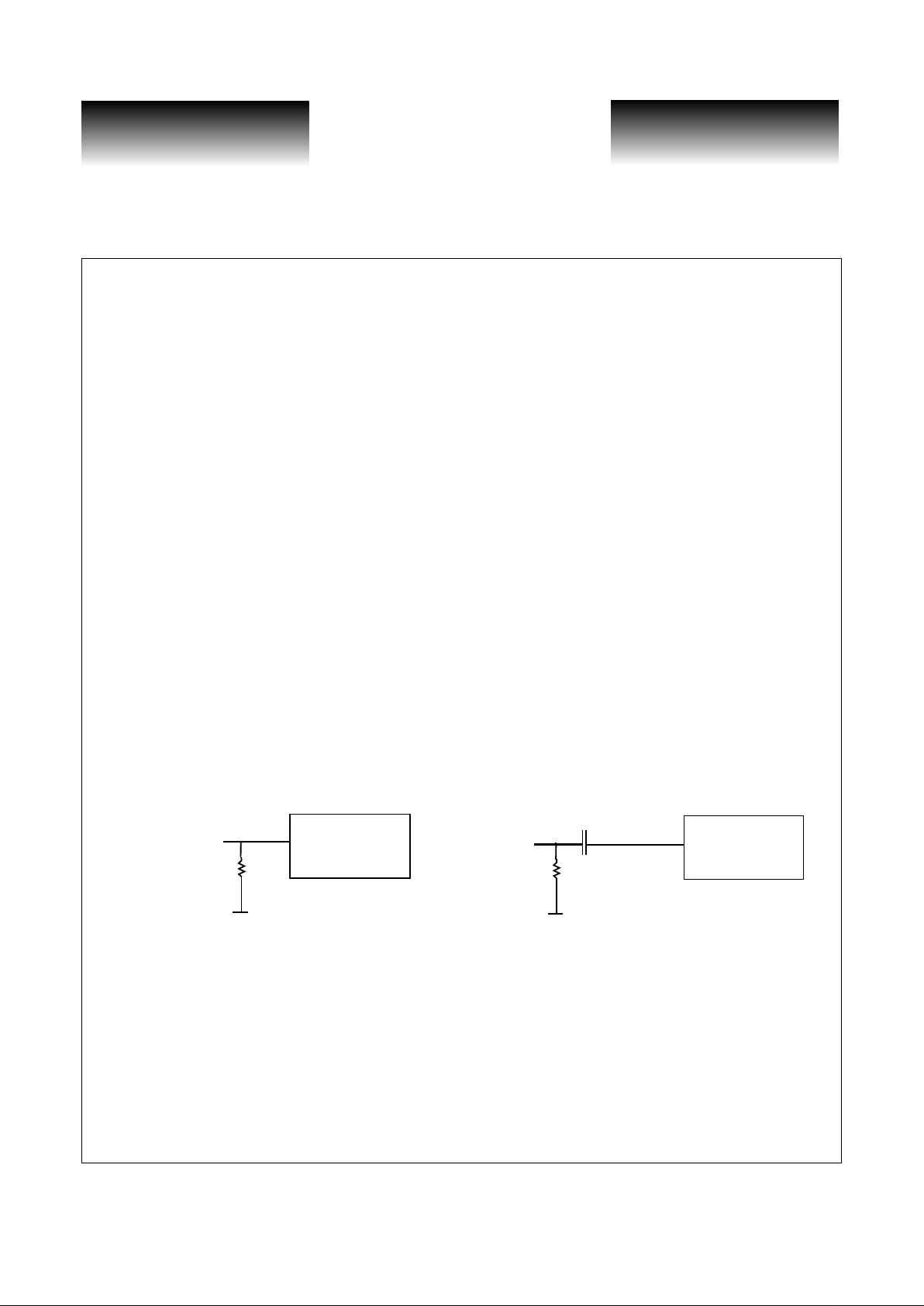

Loop Filter

The Phase Locked Loop (PLL) on the VSC8122-FEC employs two external capacitors. The PLL design is

fully differential; therefore, the loop filter must also be fully differential. One capacitor sh ould be connected

between FILTAO and FILTAI, with the other connected between FILTAON and FILTAIN. Recommended

capacitors are low inductance 1.0µF (0603 or 0805) ceramic SMT X7R devices, 6.3 WVDC or greater.

AC Characteristics (Over recommended operating cond itions )

Ta ble 3: AC Characteristics

Reference Frequency

REF_SEL0 REF_SEL1

OC-48 OC-48 FEC Gigabit Ethernet

19.44MHz 20.74MHz

(1)

19.53MHz

00

38.88MHz 41.47MHz

(1)

39.06MHz

10

77.76MHz 82.9MHz

(1,2)

78.13MHz

01

155.52MHz 165.89MHz

(1,2)

156.25MHz

11

Parameter

s

Description Min Max Units Conditions

t

pd

Center of output data eye from rising

edge of CO+

-75 +75 ps

t

r

, t

f

DO± rise and fall times — 150 ps. 20% to 80% into 50Ω load .

tr, t

f

CO± rise and fall times — 135 ps 20% to 80% into 50Ω load.

Jitter

gen

Jitter Generation — 3.6

ps rms

Measured at the high-speed

data output for jitter in the

12kHz - 20MHz band.

Assume 1.2ps rms input

data jitter.

Jitter

tol

Jitter Tolerance ———

Exceeds SONET/SDH

mask

LBW Loop Bandwidth — 2.0 MHz

-3dB point of jitter transfer

curve

Jitter

peak

Jitter Peaking — 0.1 dB

Loading...

Loading...