VITESSE VSC8113QB2, VSC8113QB1, VSC8113QB Datasheet

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

SC8113

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

Features

• Operates at Either STS-3/STM-1 (155.52Mb/s)

or STS-12/STM-4 (622.08Mb/s) Data Rates

• Compatible with Industry ATM UNI Devices

• On Chip Clock Generation of the

622.08MHz High Speed Clock (Mux)

or

• On Chip Clock Recovery of the

622.08MHz High Speed Clock (Demux)

• 8 Bit Parallel TTL Interface

• SONET/SDH Frame Recovery

• Lock Detect for both CRU and CMU

155.52MHz

155.52MHz or

• Loss of Signal (LOS) Input & LOS Detection

• +3.3V/5V programmable PECL Serial Interface

• Provides Equipment, Facilities and Split Loopback Modes as well as Loop Timing Mode

• Provide TTL & PECL reference clock inputs

• Meets Bellcore, ITU and ANSI Specifications for

Jitter Performance

• Low Power - 1.0 Watts Typical

• 100 PQFP Package

General Description

The VSC8113 is an ATM/SONET/SDH compatible transceiver integrating an on-chip Clock Multiplication

Unit (PLL) for the high speed clock as well as a clock and data recovery unit (CRU) with 8 bit serial-to-parallel

and parallel-to-serial data conversion. The PLL clock is used for serialization in the transmit direction (Mux).

The recovered clock is used for deserializatio n in the receive direction (Demux). Th e demultiplexer contains

SONET/SDH frame detection and recovery. The device provides both facility and equipment loopback modes

and two loop timing modes. The part is packa ged in a 100PQFP with integrat ed hea t sp reader fo r opt i mum t her mal performance and reduced cost. The VSC8113 provides an integrated solution for ATM physical layers and

SONET/SDH systems applications.

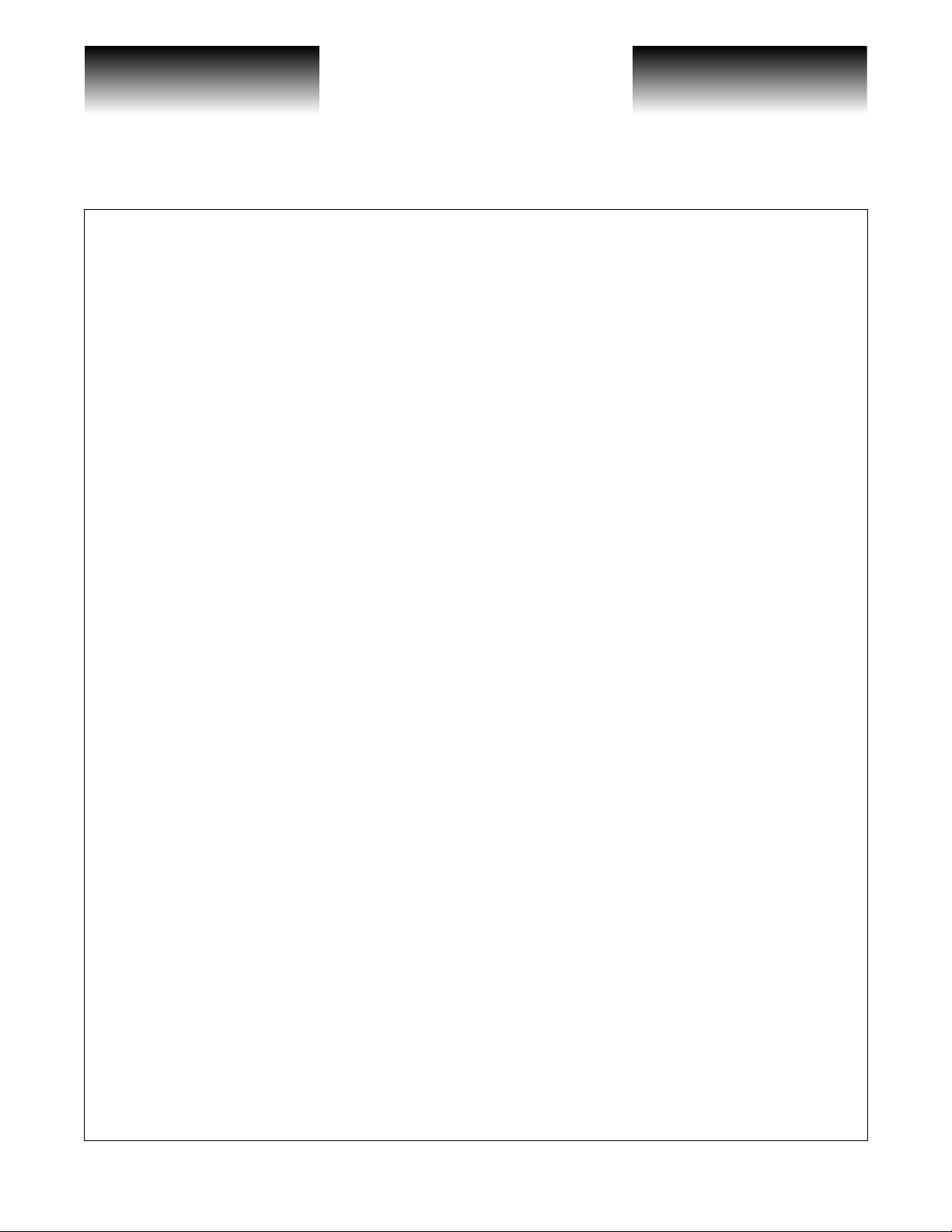

Functional Description

The VSC8113 is designed to provide a SONET/SDH compliant interface between the high spee d optical

networks and the lower speed User Network Interface devices such as the PM5355 S/UNI-622. The VSC8113

converts 8 bit parallel data at 77.76Mb/s or 19Mb/s to a serial bit stream at 622.08Mb/s or 155.52Mb/s respectively. The device also provides a Facility Loopback function which loops the received high speed data and

clock (optionally recovered on-chip) directly to the high speed transmit outputs. A Clock Multiplier Unit

(CMU) is integrated into the transmit circuit to generate the high speed clock for the serial output data stream

from input reference frequencies of 19.44, 38.88, 51.84 or 77.76 MHz. The CMU can be bypassed with the

received/recovered clock in loop timing mode thus synchronizin g the entire part to a sing le clock. The blo ck

diagram on page 2 shows the major functional blocks associated with the VSC8113.

The receive section provides the serial-to-parallel c onversion, converting the 155.52Mb/s or 622Mb/s bit

stream to an 8 bit parallel o utput at 19.44Mb /s or 77. 76MHz respectively. A Clock Reco v ery Unit (CRU) is integrated into the receive circuit to recover the high speed clock from the received serial data stream. The receive

section provides an Equipment Loopback function which will loop the low speed transmit data and clock back

through the receive section to the 8 bit par allel data bus and clock outputs.The V SC8113 also pr ovides the

option of selecting between either its internal CRU’s recovered clock and data signals or optics containing a

G52154-0, Rev 4.2

3/19/99 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

VITESSE SEMICONDUCTOR CORPORATION

Page 1

VITESSE

SEMICONDUCTOR CORPORATION

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

Data Sheet

VSC8113

CRU clock and data signals. (In this mode the VSC8113 operates just like the VSC8111). The receive section

also contains a SONET/SDH f rame detector cir cuit which is use d to provide frame pluse s during the A1, A2

boundary in the serial to parallel converter . This only occurs when OOF is high. Both internal and external LOS

functions are supported.

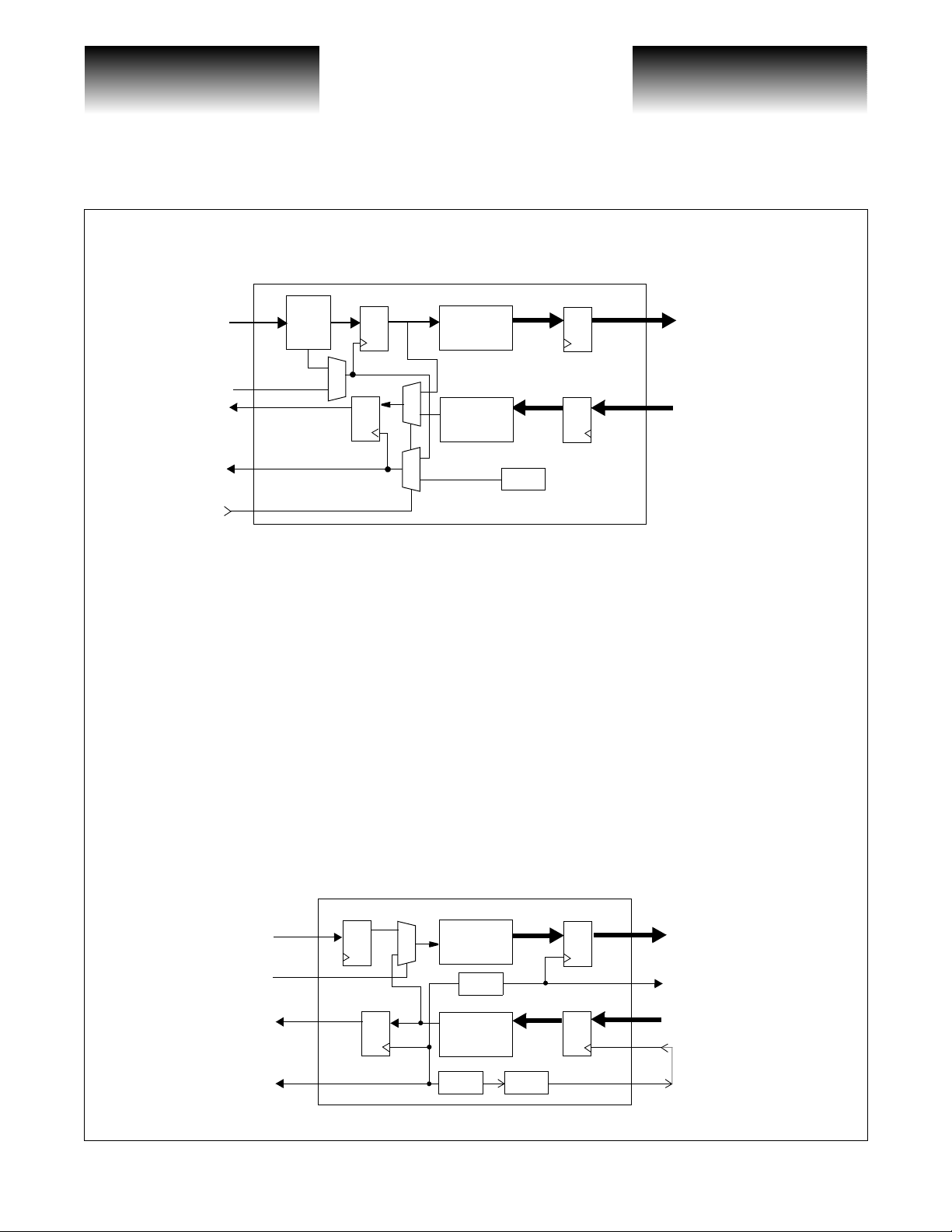

VSC8113 Block Diagram

EQULOOP

TXDATAOUT+/-

TXCLKOUT+/-

FACLOOP

CMULOCKDET

DQ

DQ

FRAMER

0

1

0

1

1

0

1

0

01

1:8

DEMUX

Divide-by-8

8:1

MUX

Divide-by-8

Divide-by-3/12

DQ

QD

8

8

OOF

FP

RXOUT[7:0]

RXLSCKOUT

TXIN[7:0]

TXLSCKIN

TXLSCKOUT

RX50MCK

LOOPTIM0

DSBLCRU

1

RXDATAIN+/-

CRUEQLP

CRULOCKDET

RXCLKIN+/-

LOSOUT

CRUREFCLK

CRUREFSEL

0

1

0

CRU

REC-DATA

REC-CLK

Page 2

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896 3/19/99

10

1

0

0

1

losdet

cmurefclk

CMU

VITESSE SEMICONDUCTOR CORPORATION

1

0

REFCLKP+/REFCLK

LOOPTIM1

EQULOOP

LOSPECL

LOSTTL

LOSDETEN_

G52154-0, Rev 4.2

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

SC8113

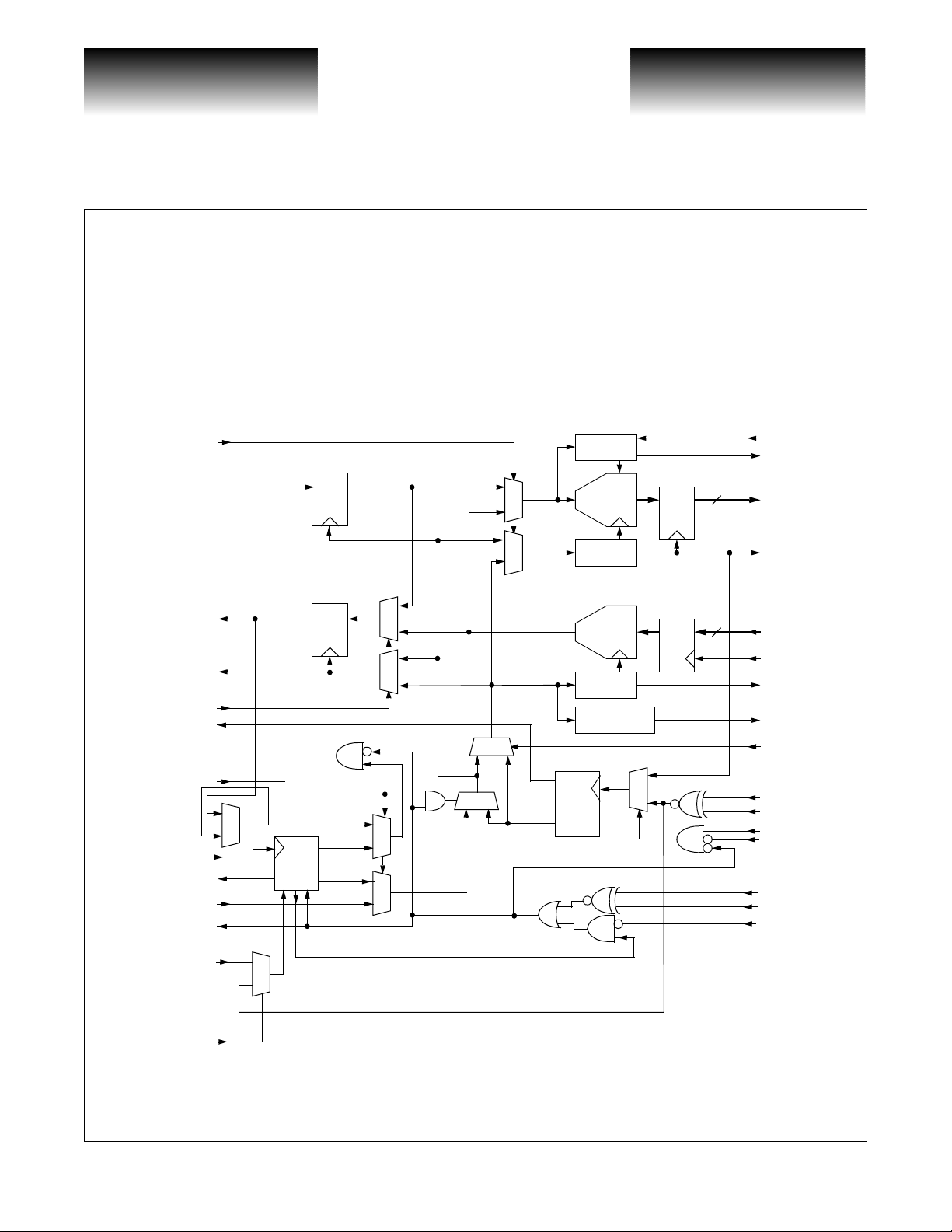

Transmit Section

Byte-wide data is presented to TXIN[7:0] and is clocked into the part on the rising edge of TXLSC KIN.

See Figure 1. The data is then serialized (MSB leading) and presented at the TXDATAOUT+/- pins.

TXDATAOUT is clocked out on the falling edge of TXCLKOUT+. The serial output stream is synchronized to

the CMU generated clock whic h is a phase locked and frequen cy scaled version of the inp ut reference cloc k.

External control inputs B0-B2 and STS-12 select the multiply ratio of the CMU for either STS-3 (155MbS) or

STS-12 (622Mb/s) transmission (see Table 12). A divide-by-8 version of the CMU clock (TXLSCKOUT)

should be used to synchronize the transmit interface of the UNI device to the transmit input registers on the

VSC8113 (see Application Notes, p. 20).

Figure 1: Data and Clock Transmit Block Diagram

TXDATAOUT+

TXDATAOUT-

TXCLKOUT+

TXCLKOUT-

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

VSC8113 PM5355

DQDQ

TXIN[7:0]

TXLSCKIN

DQ

REFCLK

Receive Section

High speed Non-Return to Zero (NRZ) serial data at 155Mb/s or 622Mb/s are received by the RXDATAIN

inputs. The CRU recovers the high speed clock from the serial data input. The serial data is converted to bytewide parallel data and presented on RXOUT[7:0] pins. A divide-by-8 version of the high-speed clock

(RXLSCKOUT) should be used to synch r onize t he byte-serial RXOUT[7:0] data with the receive portion of the

UNI device. The on-chip CRU is by-passed by setting the DSBLCRU input high. In this mode, the serial input

data and corresponding clock are received by the RXDATAIN and RXCLKIN inputs respectively. RXDATAIN

is clocked in on the rising edge of RXCLKIN+. See Figure 2.

The receive section also includes frame detection a nd recovery circuitry which detec ts the SONET/SDH

frame, aligns the received serial data on byte boundaries, and initiates a frame pulse on FP coincident with the

byte aligned data. The frame recovery is initiated when OOF is held high which must occur at lea s t 4 byte clock

cycles before the A1A2 boundary. The OOF input control is a level-sensitive signal, and th e VSC8113 will continually perform frame detection and recovery as long as this pin is held high even if 1 or more frames has been

detected. Frame detection and recovery occurs when a series of three A1 bytes followed by three A2 bytes has

been detected. The paralle l outp ut data on R XOUT[7:0] wil l be b yt e alig ned startin g on the thi rd A2 b yte. Wh en

a frame is detected, a single byte clock pe riod long pulse is g enerated o n FP which i s synchronize d with the

byte-aligned third A2 byte on RXOUT[7:0]. The frame detector sends a FP pulse only if OOF is high.

Divide-by-8CMU

TXLSCKOUT

G52154-0, Rev 4.2

3/19/99 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

VITESSE SEMICONDUCTOR CORPORATION

Page 3

VITESSE

SEMICONDUCTOR CORPORATION

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

Data Sheet

VSC8113

Loss of Signal

The VSC8113 features Loss of Signal (LOS) detection. Loss of Signal is declared if the incoming serial

data stream has no transition continuously for more than 128 bits. During an LOS condition, the VSC 8113

forces the receive data low which is an indication for an y do wnstre am equipment that an optical interfac e fail ure

has occurred. The receive section continues to be clocked by the CRU as it is now locked to the “CRUREFCLK” unless “DSBLCRU” is active in which case it will be clocked by the CMU. This LOS condition will be

removed when the part detects more than 16 transitions in a 128 bit time window. This LOS detection feature

can be disabled by applying a high level to LOSDETEN_ input. The VSC8113 also has a TTL input LOSTTL

and a PECL input LOSPECL to force the part into a Loss of Signal state. Most optics have a PECL output usually called “SD” or “FLAG” indicating a lack of or presence of optical power. Depending on the optics manufactured this signal is either active high or active low. The LOSTTL and LOSPECL inputs are XNOR’d to

generate an internal LOS control signal. See Figure 2. The optics “SD” output should be connected to

LOSPECL. The LOSTTL input should be tied low if the optics “SD” output is active high. If it’s active low tie

LOSTTL high. The inverse is true if the optics use “FLAG” for loss of signal.

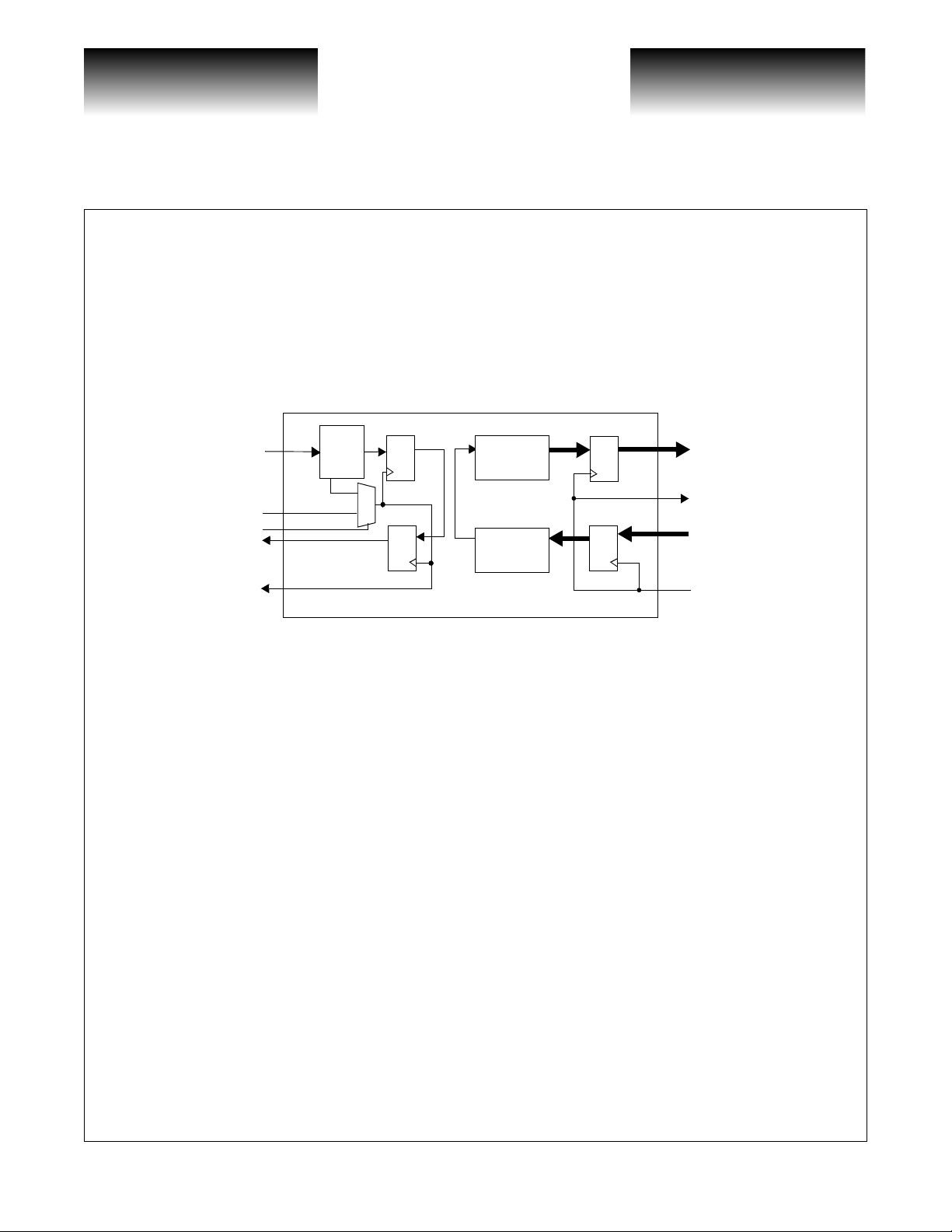

Figure 2: Data and Clock Receive Block Diagram

VSC8113

PM5355

LOSPECL

LOSTTL

LOSDETEN_

DSBLCRU

RXDATAIN+/-

CRULOCKDET

RXCLKIN+/-

CRU

DQ

DQ

1

0

0

0

1

1

CMU

Divide-by-8

DQ

RXOUT[7:0]

FP

RXLSCKOUT

DQ

DQ

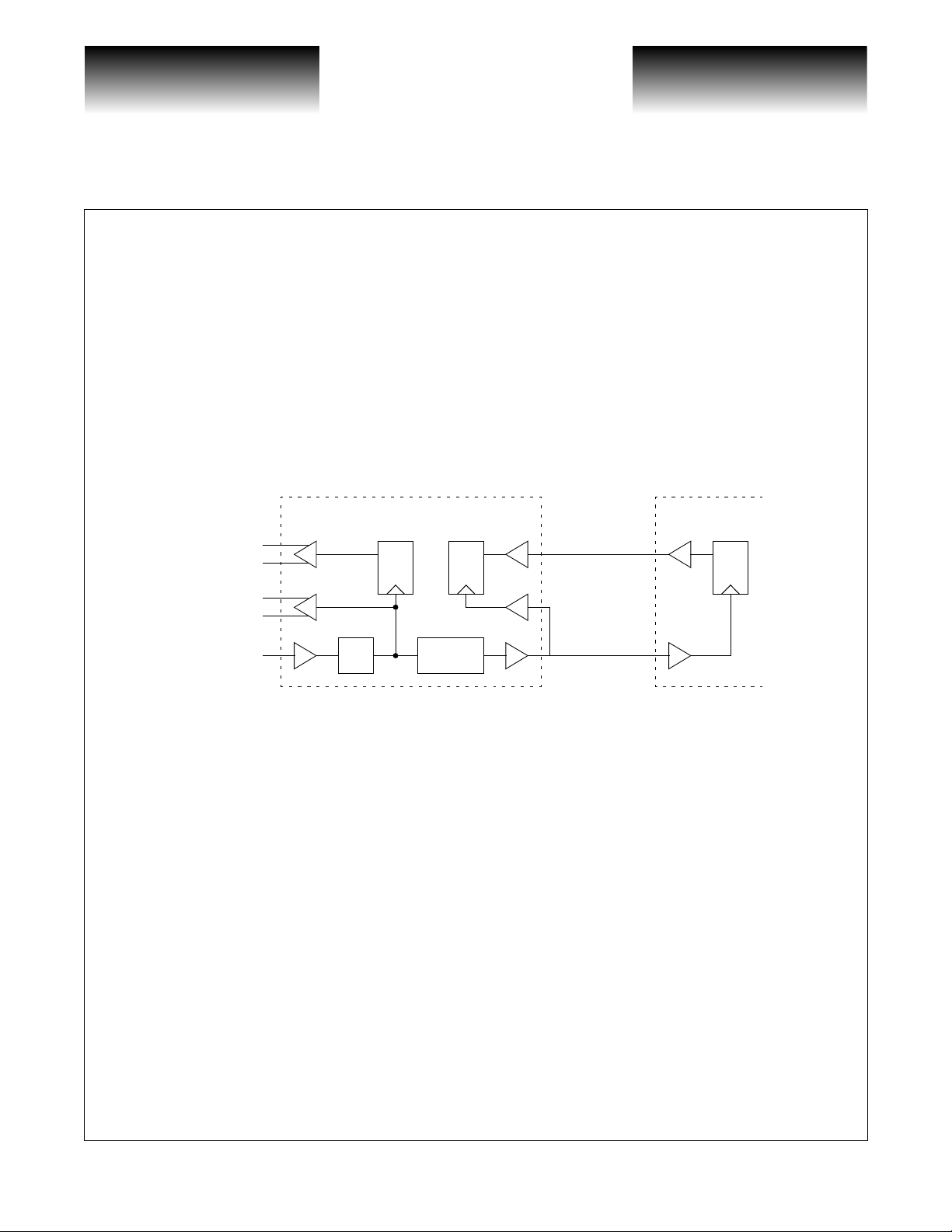

Facility Loopback

The Facility Loopback function is controlled by the FACLOOP signal. When the FACLOOP signal is set

high, the Facility Loopback mode is activated and the high speed serial receive data (RXDATAIN) is presented

at the high speed transmit output (TXDATAOUT). See Figure 3. In addition, the high speed received/recovered

clock is selected and p resented at the high speed tra nsmit clock outp ut (TXCLKOUT). In Facility Loopback

mode the high speed recei v e dat a (RXDATAIN) is also co nverted to parall el data and presented at the low speed

receive data output pins (RXOUT[7:0]). The receive clock (RXCLKIN) is also divided down and presented at

the low speed clock output (RXLSCKOUT).

Page 4

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896 3/19/99

VITESSE SEMICONDUCTOR CORPORATION

G52154-0, Rev 4.2

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

SC8113

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

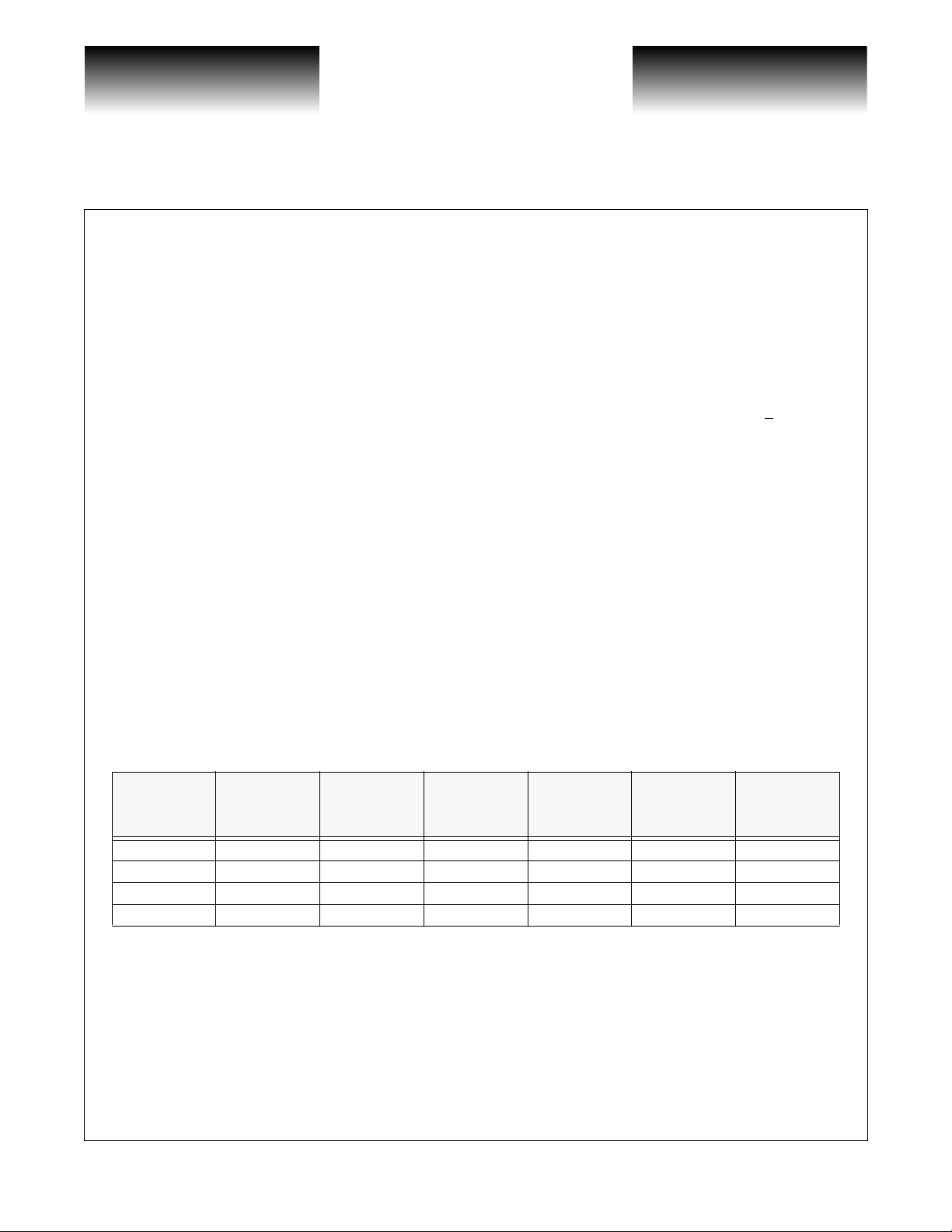

Figure 3: Facility Loopback Data Path

RXDATAIN

RXCLKIN

TXDATAOUT

TXCLKOUT

FACLOOP

Recovered

Clock

CRU

Q

0

1

Q

1

D

0

1

0

1:8

Serial to

Parallel

Parallel to

Serial

PLL

D

Q

Q

D

RXOUT[7:0]

TXIN[7:0]8:1

D

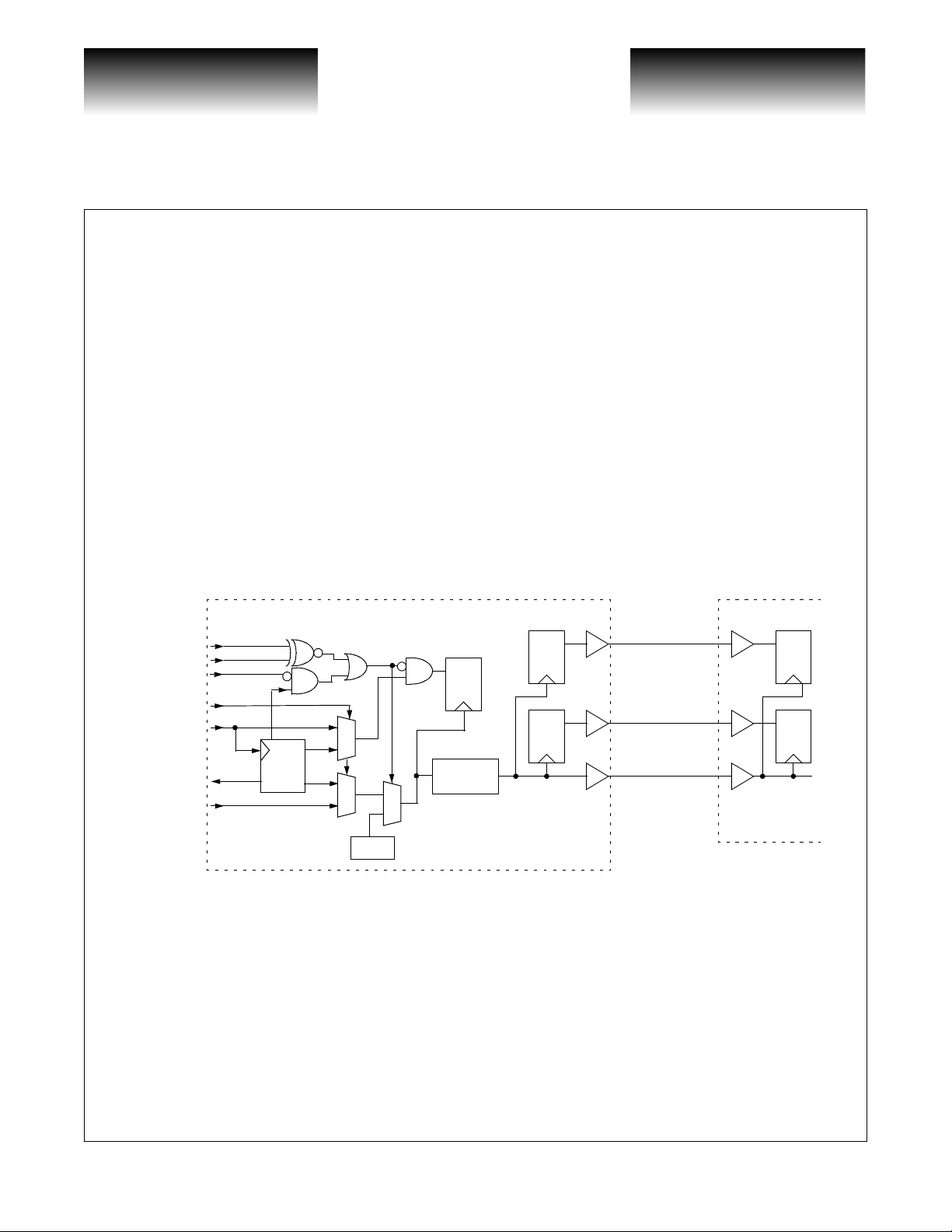

Equipment Loopback

The Equipment Loopback function is controlled by the EQULOOP signal. When the EQULOOP signal is

set high, the Equipment Loopback mode is activated and the high speed transmit data generated from the parallel to serial conversion of the low speed data (TXIN[7:0]) is selected and converted back to parallel data in the

receiver section and presented at the low speed parallel outputs (RXOUT[7:0]). See Figure 4. The internally

generated 155/622MHz clock i s used t o g enerate t he low speed receive clock output (RXLSCKOUT). In Equipment Loopback mode the transmit data (TXIN[7:0]) is serialized and presented at the high speed output

(TXDATAOUT) along with the high speed transmit clock (TXCLKOUT) which is generated by the on-chip

clock multiplier unit.

CRU Equipment Loopback

Exactly the same as equipment loopback, the point where the transmit data is looped back is moved all the

way back to the high speed I/O. When the CRUEQLP signal is set high, transmit data is looped back to the

CRU, replacing RXDATAIN±

Figure 4: Equipment Loopback Data Path

D

RXDATAIN

EQULOOP

TXDATAOUT

TXCLKOUT

G52154-0, Rev 4.2

Q

0

1

Q

D

VITESSE SEMICONDUCTOR CORPORATION

1:8

Serial to

Parallel

÷ 8

8:1

Parallel to

Serial

PLL ÷ 8

3/19/99 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

D

Q

Q

D

RXOUT[7:0]

RXLSCKOUT

TXIN[7:0]

TXLSCKIN

TXLSCKOUT

Page 5

VITESSE

SEMICONDUCTOR CORPORATION

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

Data Sheet

VSC8113

Split Loopback

Equipment and facility loopback modes can be enabled simultaneously. In this case, high-speed serial data

received (RXDATAIN) and received/recovered clock are mux’d through to the high-speed serial outputs

(TXDATAOUT) and (TXCLKOUT). The low-speed transmit byte wide bus(TXIN[7:0]) and (TXLSCKIN) are

mux’d into the low-speed byte wide receive output bus (RXOUT[7:0]) and (RXLSCKOUT). See Figure 5.

Figure 5: Split Loopback Datapath

D

RXDATAIN

RXCLKIN

DSBLCRU

TXDATAOUT

TXCLKOUT

Recovered

Clock

CRU

Q

0

1

Q

D

1:8

Serial to

Parallel

8:1

Parallel to

Serial

D

Q

Q

D

RXOUT[7:0]

RXLSCKOUT

TXIN[[7:0]

TXLSCKIN

Loop Timing

LOOPTIM0 mode bypasses the CMU when the LOOPTIM0 input is asserted high. In this mode the CMU

is bypassed by using the receive clock (RXCLKIN), and the entire part is synchronously clocked from a single

external source.

LOOPTIM1 mode bypasses the REFCLK input and uses the divide-by-8 version of the receive clock as the

reference input to the CMU. This mode is selected by asserting the LOOPTIM1 input high. The part is forced

out of this mode if it is in the Loss of Signal state or in Equipment Loopback to prevent the CMU from feeding

its own clock back.

Clock Synthesis

The VSC8113 uses an integrated phase-locked loop (PLL) for c lock synthesis of the 622MHz hig h speed

clock used for serialization in the transmitter section. The PLL is comprised of a phase-frequency detector

(PFD), an integrating operation amplifier and a voltage controlled oscillator (VCO) configured in classic feedback system. The PFD compa res the s elected divided down versio n of the 622M Hz VCO (select pi ns B0-B2

select divide-b y ra tios of 8, 12 , 16 a nd 32, see Table 12) and the reference clock. The int egrat or pro vi des a transfer function betw een inp ut phase e rror and out put v olta ge contr ol. T he VCO port ion o f the PLL is a v olt age controlled ring-oscillator with a center frequency of 622MHz.

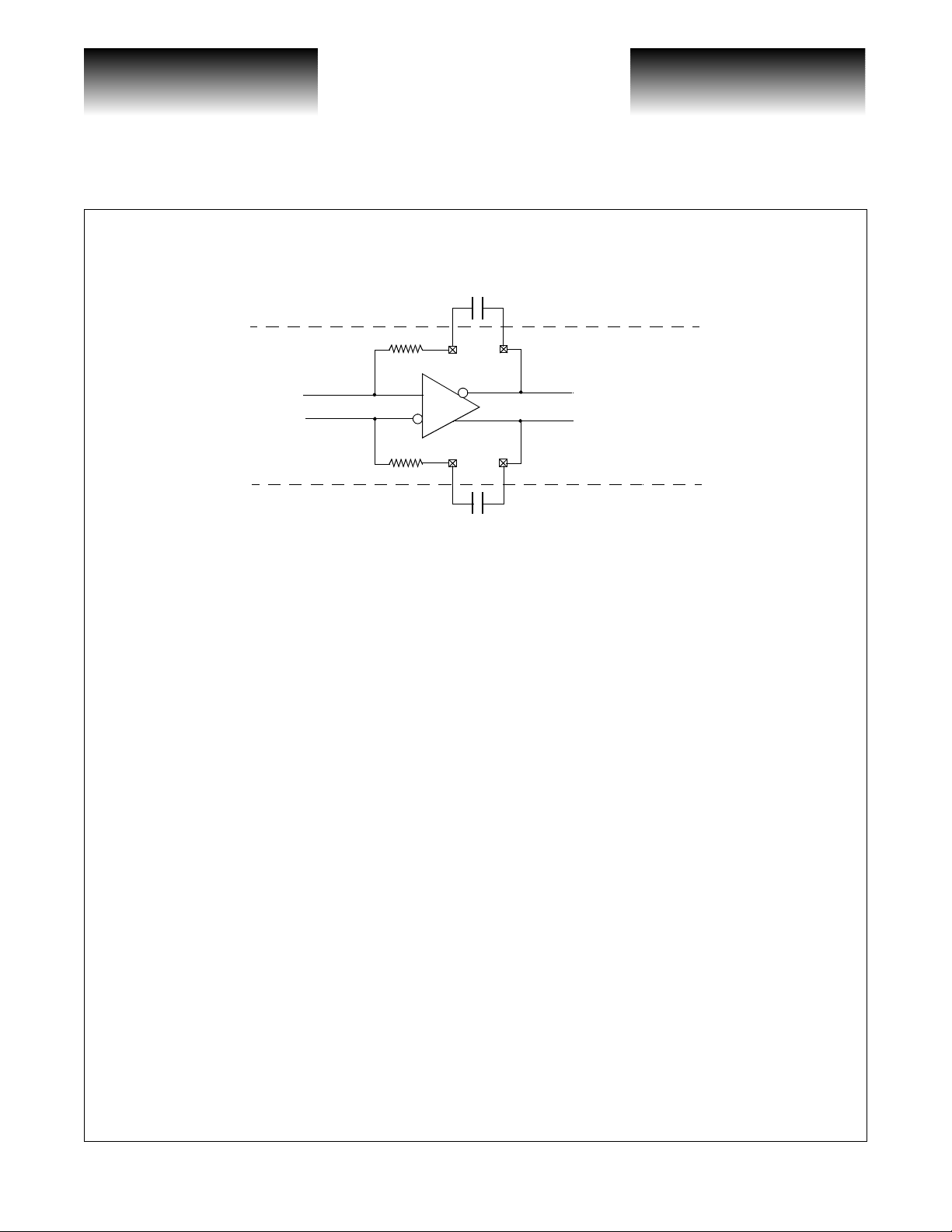

The reactive elements of the integrator are located off-chip and are connected to the feedback loop of the

amplifier through the CP1, CP2, CN1 and CN2 p ins. The configuration of thes e external surface moun ted

capacitors is shown in Figure 6. Table 1 shows the recommended external capacitor values for the configurable

reference frequencies.

Page 6

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896 3/19/99

VITESSE SEMICONDUCTOR CORPORATION

G52154-0, Rev 4.2

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

SC8113

Good analog design practices should be applied to the board design for these external components. Tightly

controlled analog ground and power planes should be provided for the PLL portion of the circuitry. The dedicated PLL power (VDDANA) and ground (VSSANA) pins should have quiet supply planes to minimize jitter

generation within the clock synthesis unit. This is accomplished by either using a ferrite bead or a C-L-C choke

(π filter) on the (VDDANA) power pins. Note: Vitesse recommends a (π filter) C-L-C choke over using a ferrite

bead. All ground planes should be tied together using multiple vias.

The VSC8113 features a lock detect function for the CMU, called “CMULOCKDET”. It generates low

going pulses when the CMU is locked to the incoming REFCLK. This is accomplished by comparing the phase

of the synthesized clock to the reference clock. If the “CMULOCKDET” output remains high for >

CMU is locked.

Reference Clocks

To improve jitter performance and to provide flexibility, an additional differential PECL reference clock

input is provided. This reference clock is internally XNOR’d with a TTL reference clock input to generate the

reference for the CMU. Vitesse reco mmends u s ing t he di fferential PECL i nput and tieing the unused TTL r efer ence clock low. If the TTL reference clock is used the positive side of the differential PECL reference clock

“REFCLKP+” should be tied to ground. “REFCLKP+/-” are internally biased with on-chip resistors to 1.65

volts, see figure 14 for schematic of internal biasing of differential I/O’s.

The CRU has the option of either using the CMU’s reference clock or its own independent reference clock

“CRUREFCLK”. If the CMU reference clock is used, it must be 78MHz. This is accomplished with the control

signal “CRUREFSEL”. The “CRUREFCLK” should be used if the system is being operated in either a regeneration or looptiming mode. In either of these modes the quality of the “CRUREFCLK” is not a concern, thus it

can be driven by a simple 77.76MHz crystal, the key is its’ independent of the CMU’s reference clock.

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

10µs, the

Table 1: Recommended External Capacitor Values

Reference

Frequency

[MHz]

19.44 32 0.1 0.1 X7R 0603/0803 +/-10%

38.88 16 0.1 0.1 X7R 0603/0803 +/-10%

51.84 12 0.1 0.1 X7R 0603/0803 +/-10%

77.76 8 0.1 0.1 X7R 0603/0803 +/-10%

G52154-0, Rev 4.2

3/19/99 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Divide Ratio CP CN Type Size Tol.

VITESSE SEMICONDUCTOR CORPORATION

Page 7

VITESSE

SEMICONDUCTOR CORPORATION

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

Figure 6: External Integrator Capacitor

CP = 0.1 µF

CP1

+

-

CN1 CN2

Clock Recovery

The fully monolithic Clock Recovery Unit (CRU) consists of a Phase Detector, a Frequency Detector, a

Loop Filter and a Voltage Controlled Oscillator (VCO). The phase detector compares the phase information of

the incoming data with the recovered clock. The frequency detector compares the frequency component of the

data input with the recovered clock to provide the pull in energy during lock acquisition. The LoopFilter integrates the phase information from the phase and frequency detectors and provides the control voltage to the

VCO.

The CRU provides a lock detect function. If the frequencies of the serial data stream and the CRU’s recovered clock are different, a data bit in the seri al data stream wil l occasional ly be dropped. If the Fre quenc y Detector does not detect this condition in a moving 1.5 µs window, the CRULOCKDET output is asserted to signal

that the CRU is frequency locked to the serial data stream. This output is forced low if it detects that a data bit is

dropped or if the recovered clock frequency drifts more than 5% from the CMU’s output frequency.

CP2

CN = 0.1 µF

Data Sheet

VSC8113

Page 8

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896 3/19/99

VITESSE SEMICONDUCTOR CORPORATION

G52154-0, Rev 4.2

VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

SC8113

Jitter Tolerance

Jitter Tolerance is the ability of the Clock Recovery Unit to track timing variation in the received data

stream. The bellcore and ITU specifications allow the received optical data to conta in jitter. The amount that

must be tolerated is a functio n of the f requenc y of t he jitter. At high frequencies the specifications do not r equire

the CRU to tolerate large amounts, wh er eas at l ow frequen cies many unit i nt e rvals (bit t i me s) of jitter ha ve to be

tolerated. The CRU is designed to tolerate th is jitter with margin over the specification limits, see Fi gure 7. The

CRU obtains and maintains lock ba sed on the data t ransition informa tion. W hen t here is no tra nsition on the

data stream, the recovered clock frequency can drift. The VSC811 3 can maintain lock over 100 bits of no

switching on data stream.

ATM/SONET/SDH 622 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

Figure 7: Jitter Tolerance

JITTER(UI P-P)

150

Bellcore Requirement

60

VSC8113 Guaranteed

Jitter Tolerance

15

1.5

0.15

10 30 300 25K 250K

6

0.6

2.5M

JITTER FREQ(HZ)

G52154-0, Rev 4.2

3/19/99 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

VITESSE SEMICONDUCTOR CORPORATION

Page 9

Loading...

Loading...