VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

SC7122

Features

• Supports ANSI X3T11 1.0625 Gbit/sec

FC-AL Disk Attach for Resiliency

• Fully Differential for Minimum

Jitter Accumulation.

• Quad PBC’s in Single Package

Quad Port Bypass Circuit for 1.0625 Gbit/sec

Fibre Channel Arbitrated Loop Disk Arrays

• TTL Bypass Select

• High Speed, PECL I/O’s Referenced to V

• 0.35W Typical Power Dissipation

• 3.3V Power Supply

• 44-Pin, 10mm PQFP

General Description

The VSC7122 is a Quad Port Bypass Circuit (PBC). Four Fibre Channel PBC’s are cascaded into a single

part to minimize part count, cost, high frequency routing, and jitter accumulation. Port Bypass Circuits are used

to provide resiliency in Fibre Channel Arbitrated Loop (FC-AL) architectures. PBC’s are used within FC-AL

disk arrays to allow for resiliency and hot swapping of FC-AL drives.

A Port Bypass Circuit is a 2:1 Multiplexer with two modes of operation: NORMAL and BYPASS. In NORMAL mode, the disk drive is connected to the loop. Data goes from the 7122’s L_SOn pin to the Disk Drive RX

input and data from the disk drive TX output goes to the 7122’s L_SIn pin. Refer to Figure 2 for disk drive

application. In BYPASS mode, the disk drive is either absent or non-functional and data bypasses to the next

available disk drive. Normal mode is enabled with a HIGH on the SEL pin and BYPASS mode is enabled by a

LOW on the SEL pin. Direct Attach Fibre Channel Disk Drives have an “LRC Interlock” signal defined to control the SEL function.

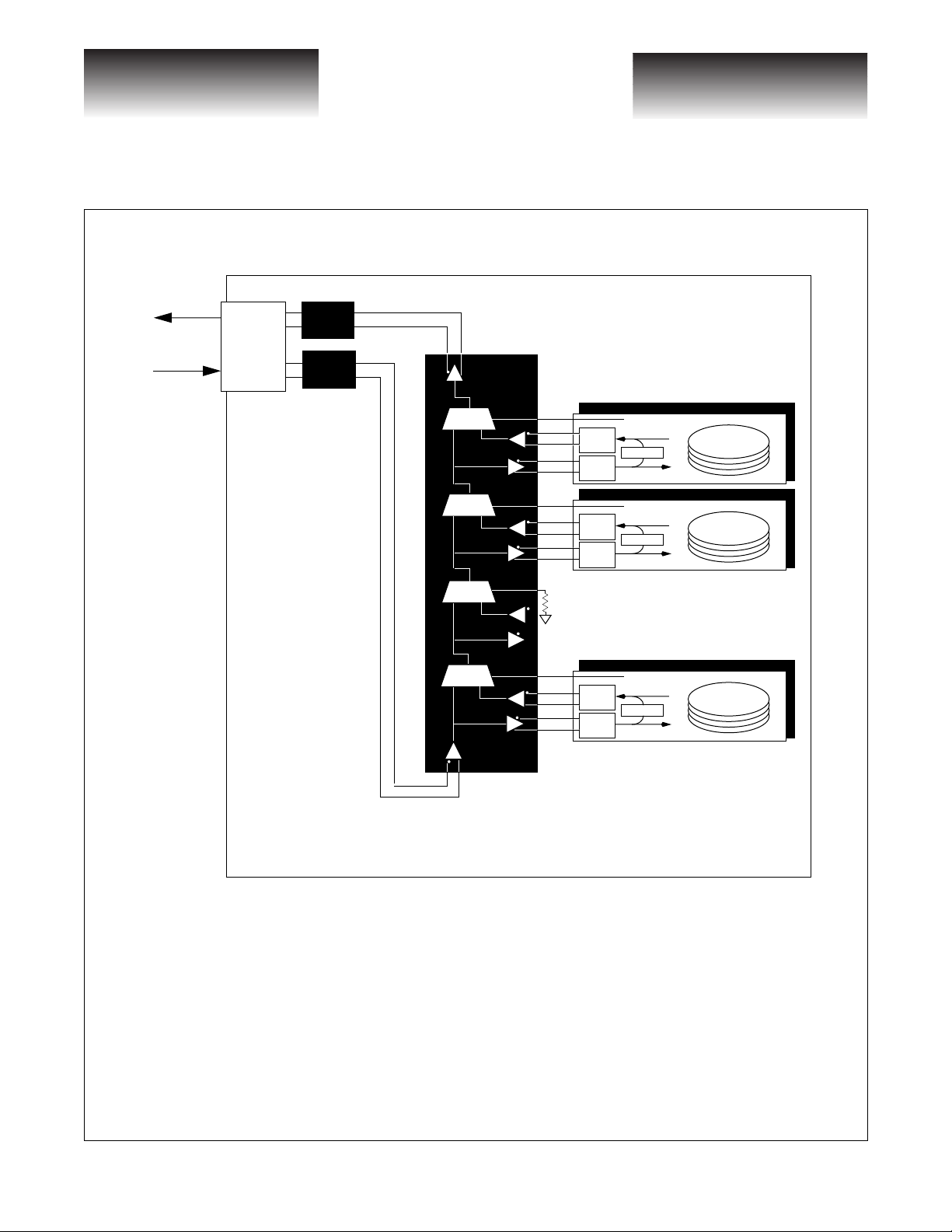

Using a VSC7122 in a single loop of a disk array is illustrated in Figure 2: “Disk Array Application”. FCAL drives are all expected to be dual loop. The VSC7122 is cascaded in a manner such that all the 7122’s internal PBC’s are used in the same loop. For dual loop implementations, two or more VSC7122’s should be used.

Allocating each VSC7122 to only one of two loops preserves redundancy, prevents a single point of failure and

lends itself to on-line maintainability.

The VSC7122 is very similar to the VSC7121 except that LSO+ outputs are all full power outputs identical

to OUT. This is useful in passive backplanes to provide additional amplitude on long traces.

DD

.

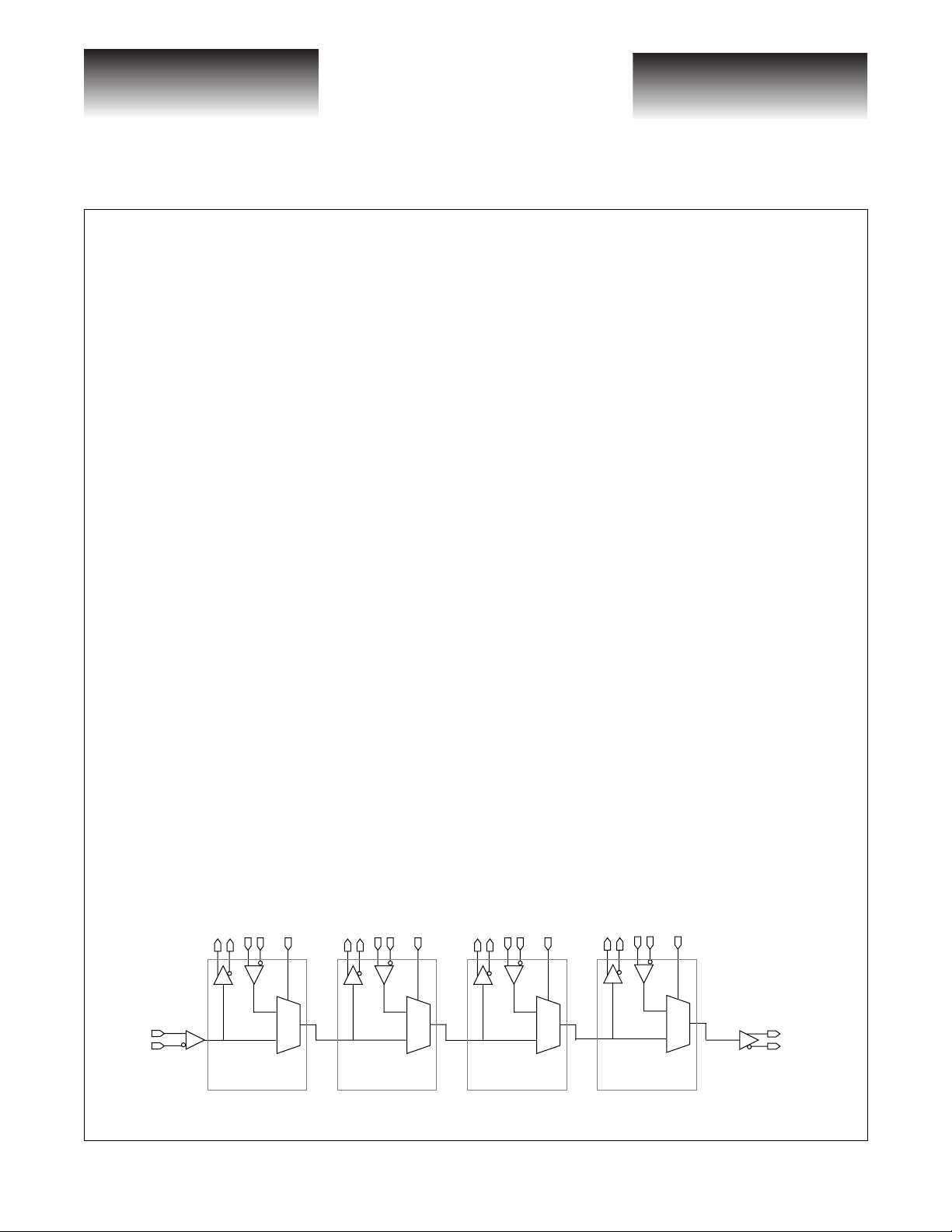

7122 Block Diagram

LSI4+

LSI4-

LSO4+

LSI1+

LSI1-

LSO1+

LSO1-

IN+

IN-

PBC1

G52155-0, Rev. 2.1

8/31/98 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

SEL1

1

00

LSI2+

LSI2-

LSO2+

LSO2-

PBC2 PBC3 PBC4

VITESSE SEMICONDUCTOR CORPORATION Page 1

SEL2

1

LSO3+

LSO3-

LSI3+

LSI3-

SEL3

1

0

LSO4-

SEL4

1

0

OUT+

OUT-

2

VITESSE

SEMICONDUCTOR CORPORATION

Quad Port Bypass Circuit for 1.0625 Gbit/sec

Fibre Channel Arbitrated Loop Disk Arrays

The VSC7122 can be cascaded through the IN and OUT pins for arrays of disk drives greater than 4. For

disk arrays with a noninteger multiple of 4 disk drives, the unused PBC’s can be hardwired to bypass with a

external pulldown resistor.

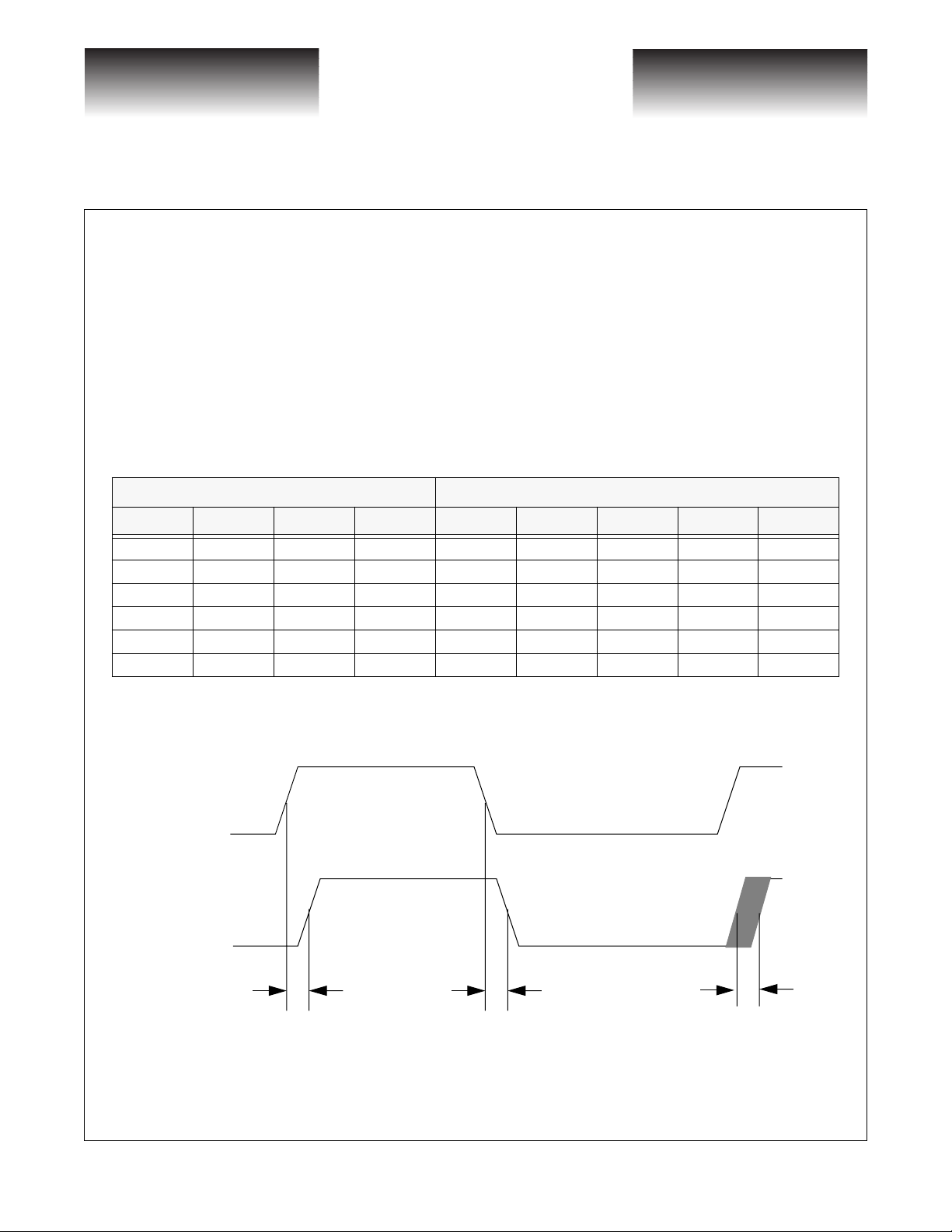

T able 1 is a truth table detailing the data flow through the VSC7122. Figure 1 shows a timing diagram of the

data relationship in the VSC7122. There are no critical timing (setup, hold, or delay) parameters for the

VSC7122 as this part routes the serial data encoded with the baud clock that is extracted by a Fibre Channel

receiver. The primary AC parameter of importance is the jitter or data eye degradation inserted by the port

bypass circuit. The design of the VSC7122 minimizes jitter accummulation by using fully differential circuits.

This provides for symmetric rise and fall delays as well as noise rejection.

Table 1: Truth Table

SELECT STATE

SEL1 SEL2 SEL3 SEL4 OUT SO4 SO3 SO2 SO1

LLLLININININ

L L L H SI4 IN IN IN

L L H L SI3 SI3 IN IN

L H L L SI2 SI2 SI2 IN

H L L L SI1 SI1 SI1 SI1

HHHHSI4SI3SI2SI1

Advance Product Information

VSC712

DATA OUTPUTS

IN

IN

IN

IN

IN

IN

Page 2

IN+/-

LSI1+/-

LSI2+/-

LSI3+/-

LSI4+/-

OUT+/LSO1+/LSO2+/LSO3+/LSO4+/-

Figure 1: Timing Waveforms

T

1

VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896 8/31/98

T

2

T

jitter

G52155-0, Rev. 2.1

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

SC7122

Figure 2: Disk Array Application

7120

Dual SC

or

DB-9

Optics

or

Copper

7120

7120

7120

0

VSC7122 QUAD PORT BYPASS CIRCUIT

0

0

Quad Port Bypass Circuit for 1.0625 Gbit/sec

Fibre Channel Arbitrated Loop Disk Arrays

1

1

1

normal

normal

bypass

LRC Interlock

TX

E_STORE

RX

LRC Interlock

TX

E_STORE

RX

Pulldown for Bypass

in Absense of Disk Drive

FC-AL DISK DRIVE

FC-AL DISK DRIVE

JBOD

normal

1

0

TX

RX

LRC Interlock

E_STORE

FC-AL DISK DRIVE

G52155-0, Rev. 2.1

8/31/98 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

VITESSE SEMICONDUCTOR CORPORATION Page 3

2

µ

µ

VITESSE

SEMICONDUCTOR CORPORATION

/2 ∆

∆

Quad Port Bypass Circuit for 1.0625 Gbit/sec

Fibre Channel Arbitrated Loop Disk Arrays

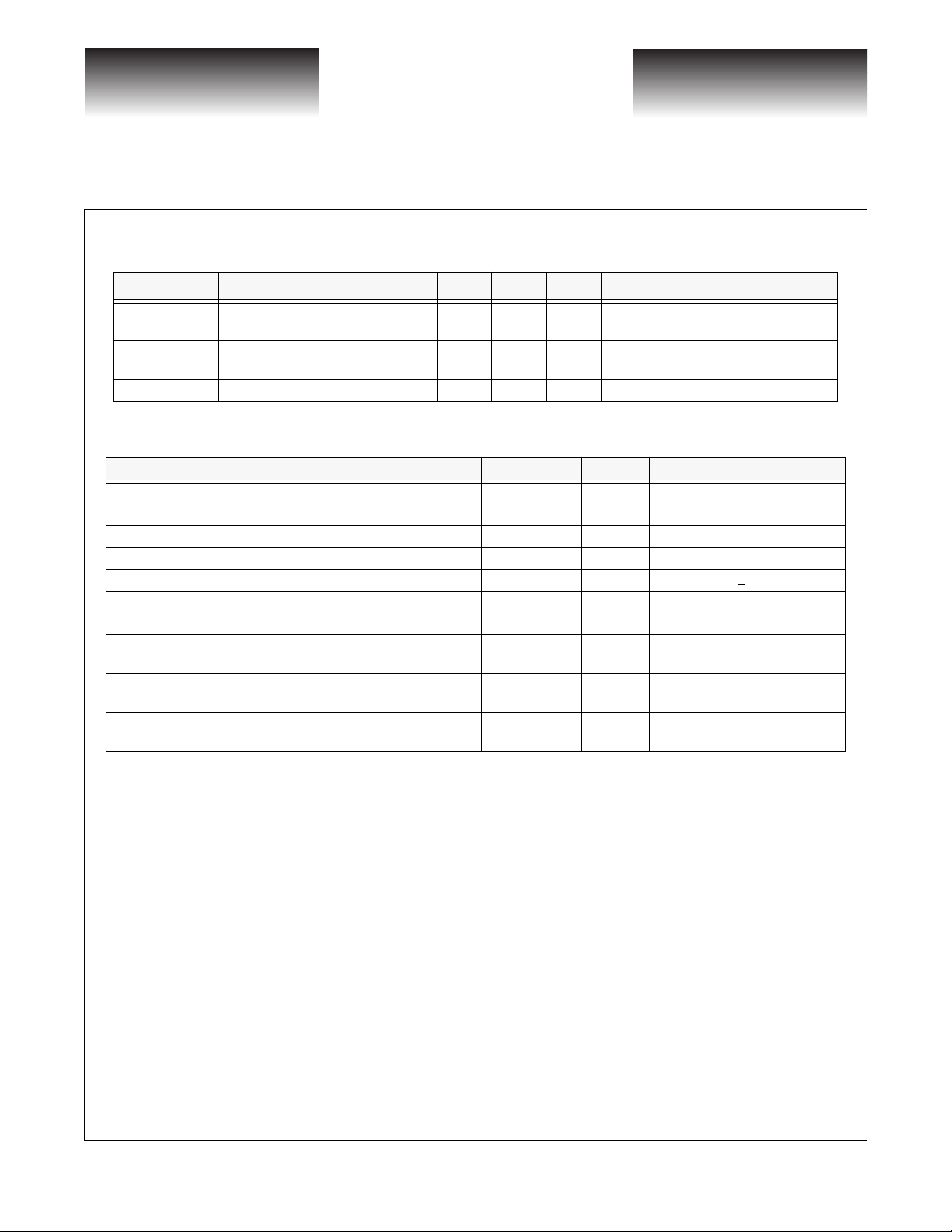

Table 2: AC Characteristics

Parameters

Flow-Through Propagation Delay

Rising Edge to Rising Edge

Flow through Propagation Delay

Falling Edge to Falling Edge

Serial data rise and fall time — 300 ps. 20% to 80%, tested on a sample basis

T

SDR

T

1

T

2

, T

SDF

Table 3: DC Characteristics

Parameters

V

IH(TTL)

V

IL(TTL)

I

IH(TTL)

I

IL(TTL)

V

I

DD

P

∆

V

V

OUT50

V

OUT75

DD

D

IN

Input HIGH voltage (SEL - TTL) 2.0 — 5.5 V I

Input LOW voltage (SEL - TTL) 0 — 0.8 V —

Input HIGH current (SEL- TTL) — 50 500

Input LOW current (SEL - TTL) — — -500

Supply voltage 3.10 — 3.50 V V

Supply current — — 150 mA Outputs open, V

Power Dissipation 0.35 0.5 W Outputs open, V

Receiver differential peak-to-peak

Input Sensitivity, IN+/- & L_SIn+/Output differential peak-to-peak

voltage swing

Output differential peak-to-peak

voltage swing

(Over recommended operating conditions).

Description Min. Max. Units Conditions

(Over recommended operating conditions).

Description Min Typ Max Units Conditions

300 2600 mVp-p

1000 — 2200 mVp-p 50 Ω to V

1200 2200 mVp-p 75 Ω to V

Advance Product Information

7.0 ns

7.0 ns

VSC712

Delay with all circuits bypassed. 75

Ohm Load

Delay with all circuits bypassed. 75

Ohm load.

< 6.6 mA @ V

IH

AV

AV

= 2.4 V

IN

= 0.5 V

IN

= 3.30V +

DD

AC Coupled.

Internally biased at V

DD

DD

– 2.0 V

– 2.0 V

5%

DD

DD

= 5.5 V

IH

= V

= V

DD

DD

DD

max

max

Page 4

VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896 8/31/98

G52155-0, Rev. 2.1

Loading...

Loading...