VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

64x64 Crosspoint Switch

SC6464

Features

• Synchronous or Asynchronous Operation

• 500Mb/s Asynchronous Operation

• 250Mb/s Synchronous Operation

• <

750ps Output to Output Skew (Synchronous)

• <

1.5ns Skew Input to Output (Asynchronous)

General Description

The VSC6464 is a 64x64 asynchronous (flow-through) or synchronous (clocked) high-speed crosspoint

switch. Any input can be multiplexed to any, some, or all outputs. The switch is fully non-blocking. All I/Os are

single-ended ECL. The part is packaged in a 208-pin plastic quad flat pack and consumes less than 8 Watts from

a single -2V power supply.

In the asynchronous mode, high speed digital data up to 500Mb/s can be switched with less than 25% pulse

width distortion. Skew is less than 1.5 ns between any two paths through the switch. In broadcast operation (one

input routed to two or more outputs), any two outputs will exhibit less than 750ps of skew.

In the synchronous mode, high-speed digital data up to 250 Mb/s can be switched with less than 750ps output-to-output skew. The input and output registers have separate clock inputs.

• Single Ended ECL I/O

• Separate Input and Output Register Clocks

• Single Supply: -2V +

• Commercial (0

5% @ 8 Watts (Max.)

o

to +70oC) T emperature Range

• Package: 208PQFP

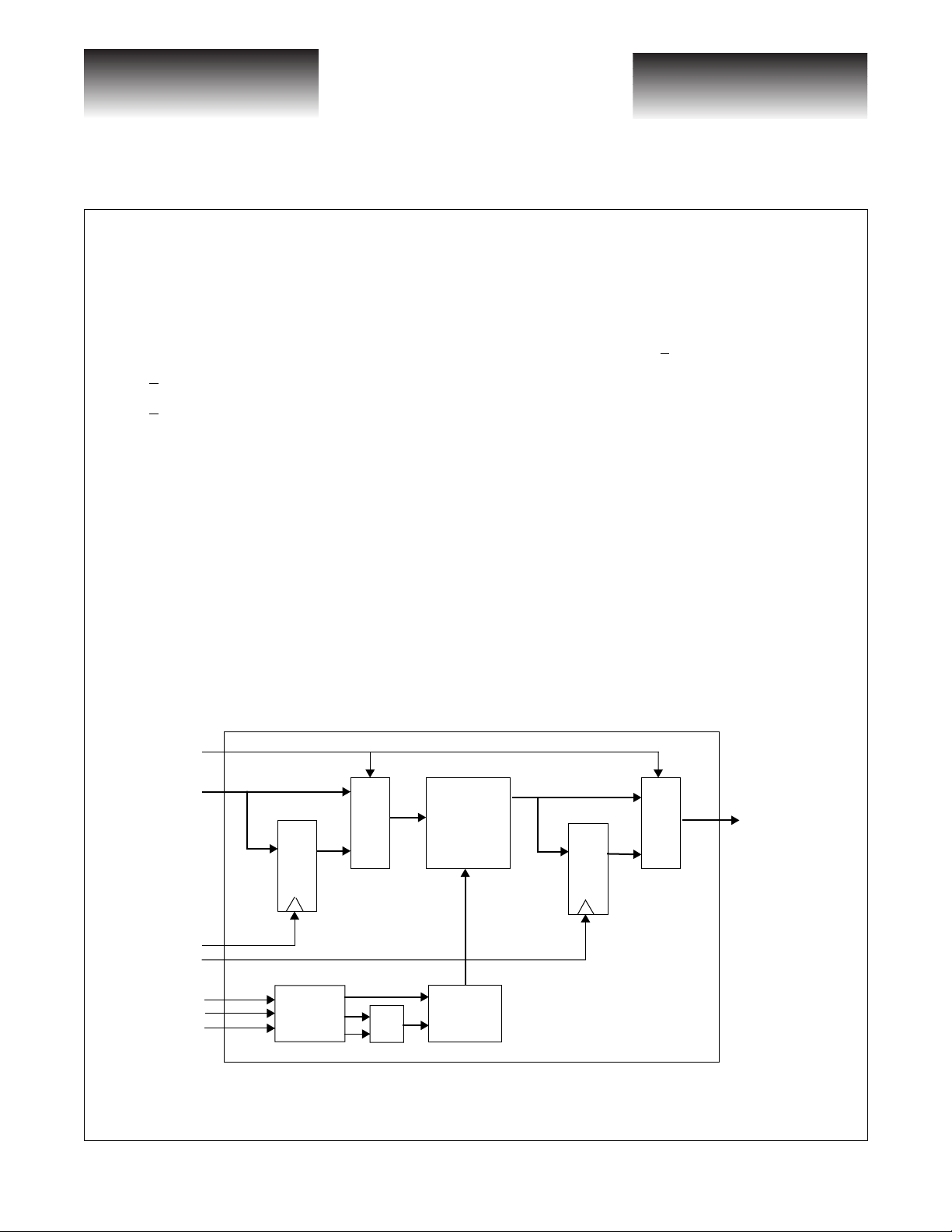

VSC6464 Functional Block Diagram

MODE

DIN<63:0>

CKI

CKO

SERS

SERD

SERC

REG

SERIAL

TO

PARALLEL

2:1

MUX

DEC

64 x 64:1

MUX

64 6-BIT

REGISTERS

REG

2:1

MUX

DOUT<63:0>

G52219-0, Rev. 2.0

8/4/98 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

VITESSE

SEMICONDUCTOR CORPORATION

Page 1

VITESSE

SEMICONDUCTOR CORPORATION

4x64 Crosspoint Switch

Advance Product Information

VSC6464

Functional Description

This Crosspoint Switch connects any of the 64 inputs to any combination of 64 output channels, according

to a user defined bit pattern stored in each channel’s control register.

Signals from the 64 inputs (DIN_0 through DIN_63) are connected to the 64 output channels (DOUT_0

through DOUT_63) through sixty-four 64:1 multiplexers. The traffic pattern is controllable by data stored in

sixty-four 6-bit control registers with each register corresponding to an output channel. The six bits are a binary

numerical representation of the input channel selected (i.e.: 000000 corresponds to DIN_0, 000001 corresponds

to DIN_1, etc.). An additional six bit re gister is used to address the output channel being programmed. These six

bits are a binary numerical representation of the output channel (ie.: 000000 corresponds to DOUT_0, 000001

corresponds to DOUT_1, etc.). All twelve configuration bits are loaded through a three-pin serial port.

The crosspoint is configured through a serial data port consisting of three pins: SERS, SERC, and SERD.

SERS is used to select the crosspoint for configuration. SERC is a serial clock signal whose rising edge samples

the serial data on SERD when SERS is active (HI). The serial data stream applied to SERD consists of the six

bits of address, followed by the six bits of data. Address information is used to identify one of the 64 output

channels, a valid value is between 0 and 63. Data information selects a specific input to be directed to the

addressed output, valid values are between 0 and 63. Both address and data information are received MSB first.

A serial load cycle consists of activ ating serial select (SERS), pulsing serial clock 12 times (with valid data surrounding each rising edge), then deactivating serial select (SERS). Deactivating serial select before the twelfth

rising edge of SERC will abort the load cycle. Serial select (SERS) must be deactivated for 10ns following a

power up. Any additional clocking of SERC during a load cycle, beyond that described above, is ignored.

The MODE pin determines the operating mode of the Crosspoint: synchronous or asynchronous, as shown

in T able 1.

A test output (TESTO) is provided for internal visibility, this signal will go high when a thirteenth rising

edge is applied during a load cycle; TESTO goes low when either SERS is lowered, or a fourteenth SERC edge

is received during a load cycle. This output can be left unconnected if desired, to reduce noise and power dissipation.

Table 1: Crosspoint Mode (MODE)

Function

Asynchronous 64x64 0

Synchronous 64x64 1

Page 2

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896 8/4/98

VITESSE

MODE

SEMICONDUCTOR CORPORATION

G52219-0, Rev. 2.0

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

SC6464

AC Characteristics

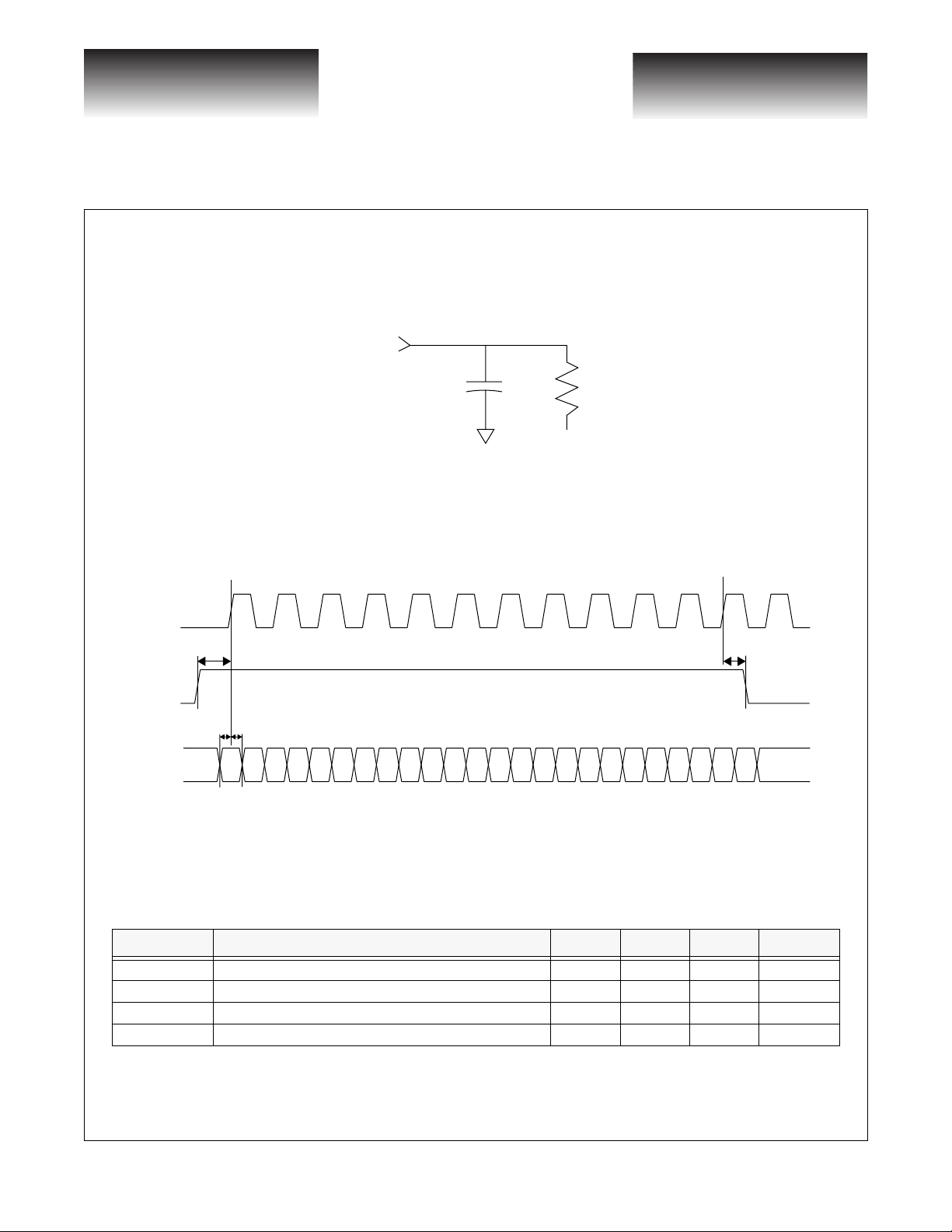

SERC

(Over recommended operating conditions)

Output

Figure 2 VSC6464 Configuration Timing Diagram

Figure 1 Output Loading

V

64x64 Crosspoint Switch

50Ω4pF

TT

T

SS

SERS

T

T

DH

DS

A4

SERD

Note: A5 is MSB of A<5:0>, D5 is MSB of D<5:0>.

Table 2: VSC6464 Asynchronous Timing Table

Parameters

T

SS

T

SH

T

DS

T

DH

A5

SERS setup time with respect to SERC 10 - - ns

SERS hold time with respect to SERC 10 - - ns

SERD setup time with respect to SERC 10 - - ns

SERD setup time with respect to SERC 10 - - ns

A2 A1 A0 D5 D4 D2 D1 D0D3

A3

Description Min Typ Max Units

T

SH

G52219-0, Rev. 2.0

8/4/98 741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

VITESSE

SEMICONDUCTOR CORPORATION

Page 3