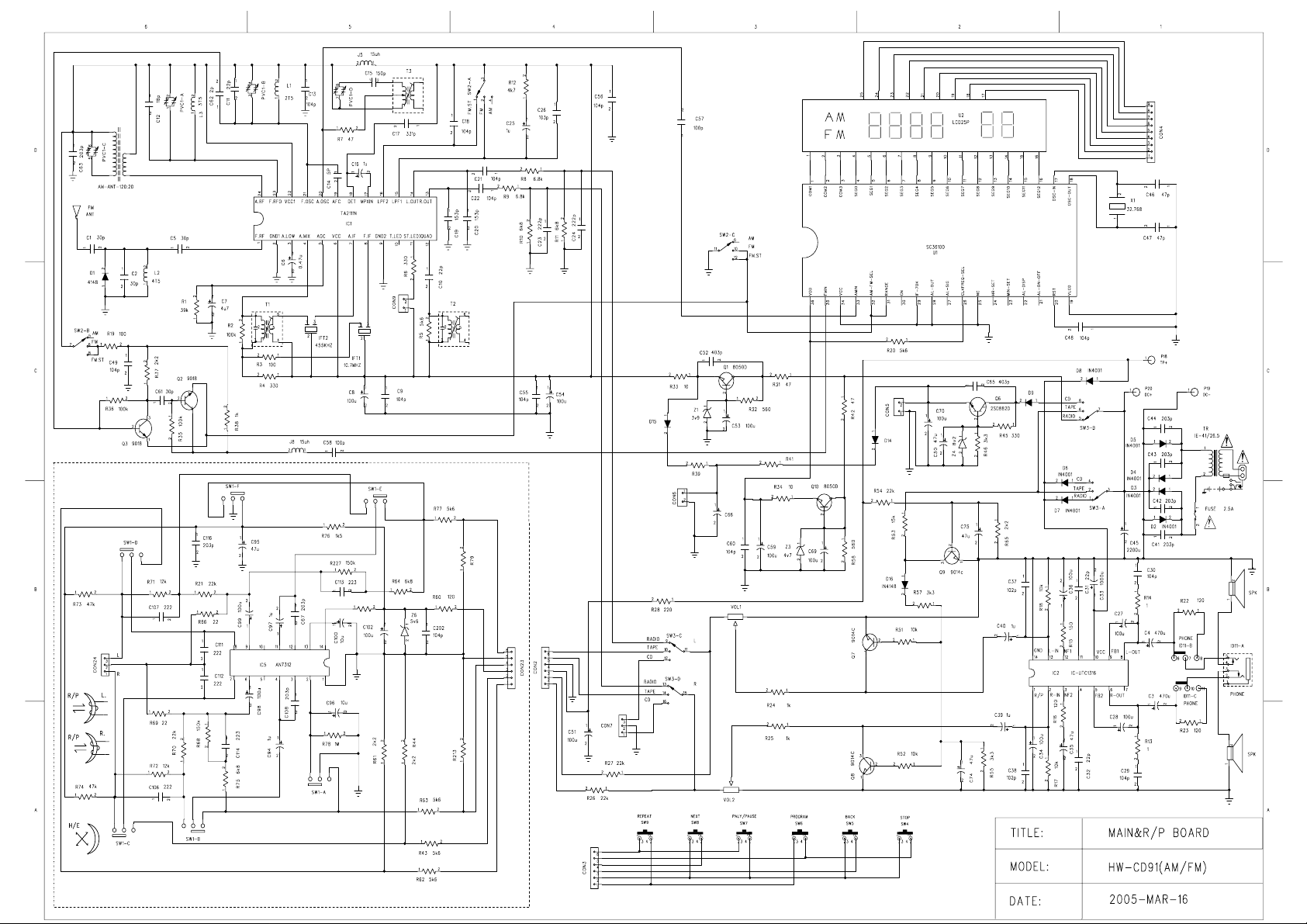

Vitek HW-CD91 electrical diagram

CD90MAN1.SCH-1 - Mon Nov 14 08:20:26 2005

2SPEED

MIC_VM3

MIC_ATO3

MIC_AIN3

LIM5

2SPEED5

CLOSE5

OPEN5

CLOP_SW5

IRI3

VFD_STB3

VFD_CLK3

VFD_DAT3

9226_RESET5

9226_MLT5

9226_MDATA5

9226_MCLK5

9226_ISTAT5

EFMI5

LOCK5

SMON5

SMEF5

SMDP5

SMDS5

WDCK5

PAD03

PAD13

GUNIO/OPEN3

DRAM_RAS

DRAM_CAS

DRAM_WE

SDRAM_CLK

DRAM_BA0

DRAM_DQM0

CVBSC

CVBSY

R96

100

D7

1N4148

1 2

VCC18

VCC33

XT2 27MHz

R14 4.7K

C3

10P

DRAM_D14

DRAM_D15

PAD0

DRAM_A0

DRAM_A1

DRAM_A2

DRAM_A3

DRAM_A4

DRAM_A5

DRAM_A6

DRAM_A7

DRAM_A8

DRAM_A9

DRAM_A10

PAD1

DRAM_BA0

DRAM_RAS

DRAM_CAS

DRAM_WE

DRAM_DQM0

CLKIN_1

CLKIO_1

C4

100P

GND

VCC33

R67

4K7

VCC33

Q1

9014

RESET

C22

0.1U

103

DD14

104

DD15

105

GPIOA1

106

DA0

107

DA1

108

DA2

109

DA3

110

DA4

111

DA5

112

DA6

113

DA7

114

VSS_CORE

115

VDD_CORE

116

VSS_IO

117

VDD_IO

118

DA8

119

DA9

120

DA10

121

GPIOA5

122

BA0

123

RAS0_B

124

CAS_B

125

WE_B

126

DQM0

127

CLKIN_1

128

CLKIO_1

GND

R4 2R2

BC19

0.1U

GND

MICVCC

GND

VCC33

DRAM_D11

DRAM_D12

DRAM_D13

DRAM_D10

100

102

DD11

DD12

DD13

ROM_DATA0

VDD_PLL

VSS_PLL

345

2

1

ROM_D0

ROM_D1

SDRAM_CLK

DRAM_D9

DRAM_D6

DRAM_D3

DRAM_D5

DRAM_D2

DRAM_D1

DRAM_D7

DRAM_D0

DRAM_D4

98

DD10

9799101

DD9

DD8

96959493929190

GPIOA0

VDD_IO

DD7

VSS_IO

8584838280

888786

89

DD2

DD1

DD0

DD6

DD5

DD4

DD3

AVDD

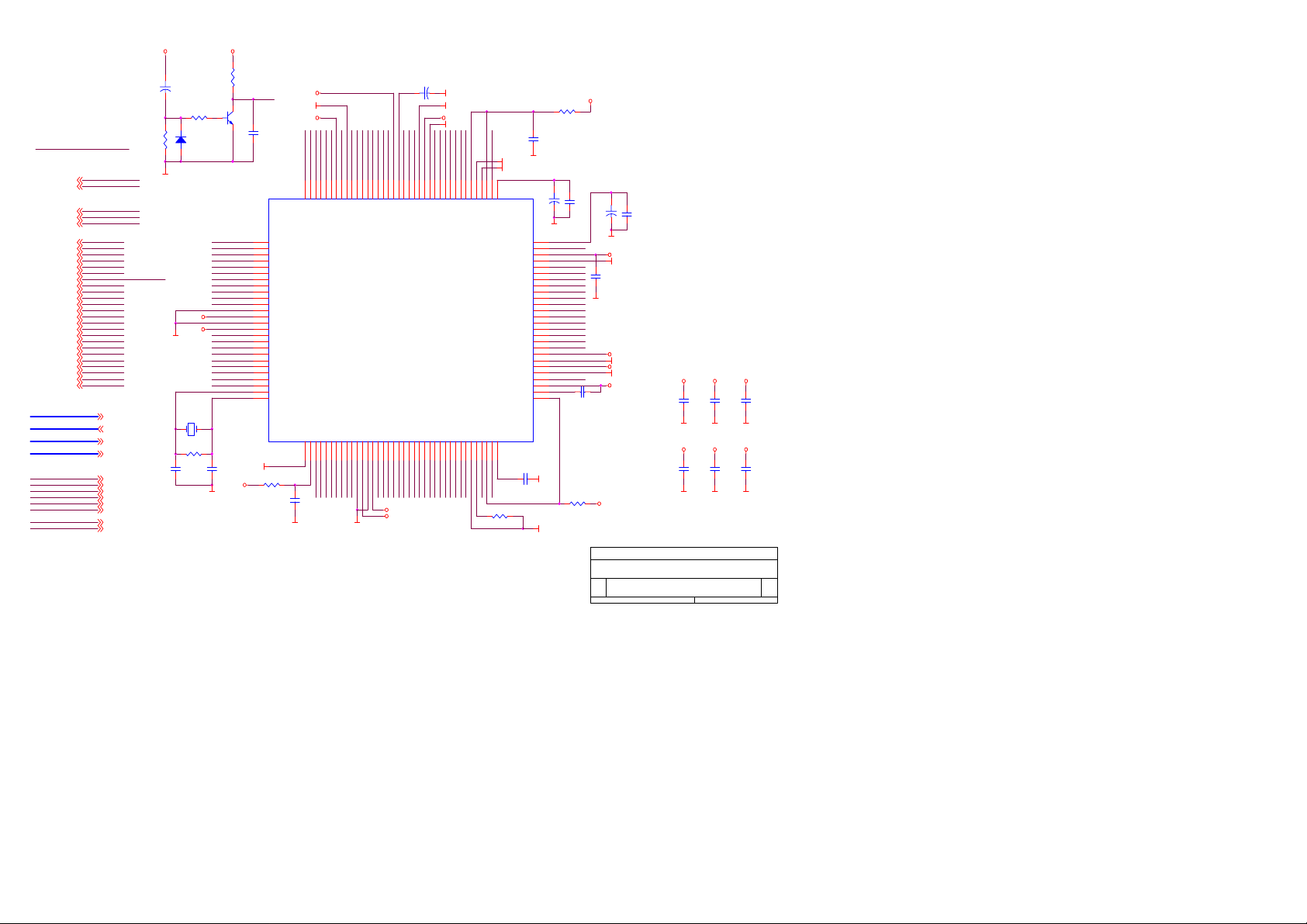

SAMSUNG S5L9294

VDD_IO

VSS_CORE

VDD_CORE

ROM_ADDR0

ROM_ADDR1

ROM_ADDR2

ROM_DATA4

ROM_DATA5

ROM_DATA1

ROM_DATA2

ROM_DATA3

7891011

6

ROM_D3 DRAM_D8

ROM_D5

ROM_D4

ROM_D2

ROM_DATA6

ROM_D6

ROM_ADDR3

ROM_DATA7

VSS_IO

121314151617181920212223242526272830323435

ROM_D7

ROM_A3

ROM_A0

ROM_A1

ROM_A2

VCC18

VCC33

GND

TC24 10U

+

MICGND

MICGND

VCC33

GND

MIC_ATO

MIC_VM

SMDP

MIC_AIN

SMDS

SMEF

WDCK

MIC_VRB

817978777675747372717069686766

VM

AIN

ATO

VRB

AVSS

SMEF

SMDS

SMDP

MDCK

VSS_IO

VDD_IO

ROM_ADDR4

ROM_ADDR5

ROM_ADDR6

ROM_ADDR7

ROM_ADDR8

ROM_ADDR9

ROM_ADDR10

ROM_ADDR11

ROM_ADDR12

ROM_ADDR13

ROM_ADDR14

29

ROM_A14

ROM_A12

ROM_A13

ROM_A11

ROM_A10

ROM_A8

ROM_A9

ROM_A6

ROM_A5

ROM_A7

ROM_A4

EFMI

GPIO37

LOCK

EFMI

LOCK

SMON

VSSD_PLL

VDDD_PLL

ROM_ADDR15

ROM_ADDR17

FSADJ

ROM_ADDR16

AVSS_TV

31

33

FSADJ

ROM_A15

ROM_A17

ROM_A16

ROUT

GND

AGND

65

VHALF

RCHOUT

VSSA_PLL

VDDA_PLL

VDDA_DAC

MDATA_9226

RESET_9226

VDD_CORE

VBIAS

CVBSC

VREFIN

CVBSY

383736

VBIAS

CVBSY

CVBSC

VREFIN

R70 470

BC8

0.1U

VHALF

U3

VREF

LCHOUT

VSSA_DAC

GPIOA17

ISTAT_9226

MCLK_9226

MLT_9226

VFD_DATA

VFD_CLK

VFD_STB

IRI

CLOP_SW

OPEN

CLOSE

RESET_B

VSS_CORE

VDD_IO

VSS_IO

GPIOA8

AVDD_TV

COMP

VREFOUT

C21

0.1U

VCC18

R68 2R2

GND

C20

TC17

+

0.1U

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

10U

VGND

VGND

AGND

VREF

LOUT

GUNIO

9226_ISTAT

9226_MCLK

9226_MDATA

9226_MLT

9226_RESET

VFD_DAT

VFD_CLK

VFD_STB

IRI

CLOP_SW

OPEN

CLOSE

RESET

LIM

COMP

C18 0.1U

R23 33K

C19

TC6

+

0.1U

10U

AGND

AVCC33

AGND

C26

0.1U

AGND

VCC18

GND

VCC33

GND

VVCC3

VVCC3

SAMTEK SEMICON DEVICES H.K.LTD.

Title

S5L9294-128

Size Document Number Rev

B

SAMTEK 9294 DEMO BOARD

Date: Sheet

BC15

0.1U

BC18

0.1U

VCC33

GND

VCC18

GND

BC16

0.1U

BC19

0.1U

VCC33

GND

VCC18

GND

VCC33

BC17

0.1U

GND

VCC18

BC20

0.1U

GND

of

15Wednesday, October 22, 2003

2

VCC5

TC23

+

10U

GPIO37

ROUT

ROUT3

LOUT

LOUT3

MIC_VM

MIC_ATO

MIC_AIN

LIM

2SPEED

CLOSE

OPEN

CLOP_SW

IRI

VFD_STB

VFD_CLK

VFD_DAT

9226_RESET

9226_MLT

9226_MDATA

9226_MCLK

9226_ISTAT

EFMI

LOCK

SMON

SMEF

SMDP

SMDS

WDCK

PAD0

PAD1

GUNIO/OPEN

ROM_A[0..18] 2

ROM_D[0..7] 2

DRAM_A[0..10] 2

DRAM_D[0..15] 2

DRAM_RAS 2

DRAM_CAS 2

DRAM_WE 2

SDRAM_CLK 2

DRAM_BA0 2

DRAM_DQM0 2

CVBSC 3

CVBSY 3

R3

10K

GND

GND

Loading...

Loading...