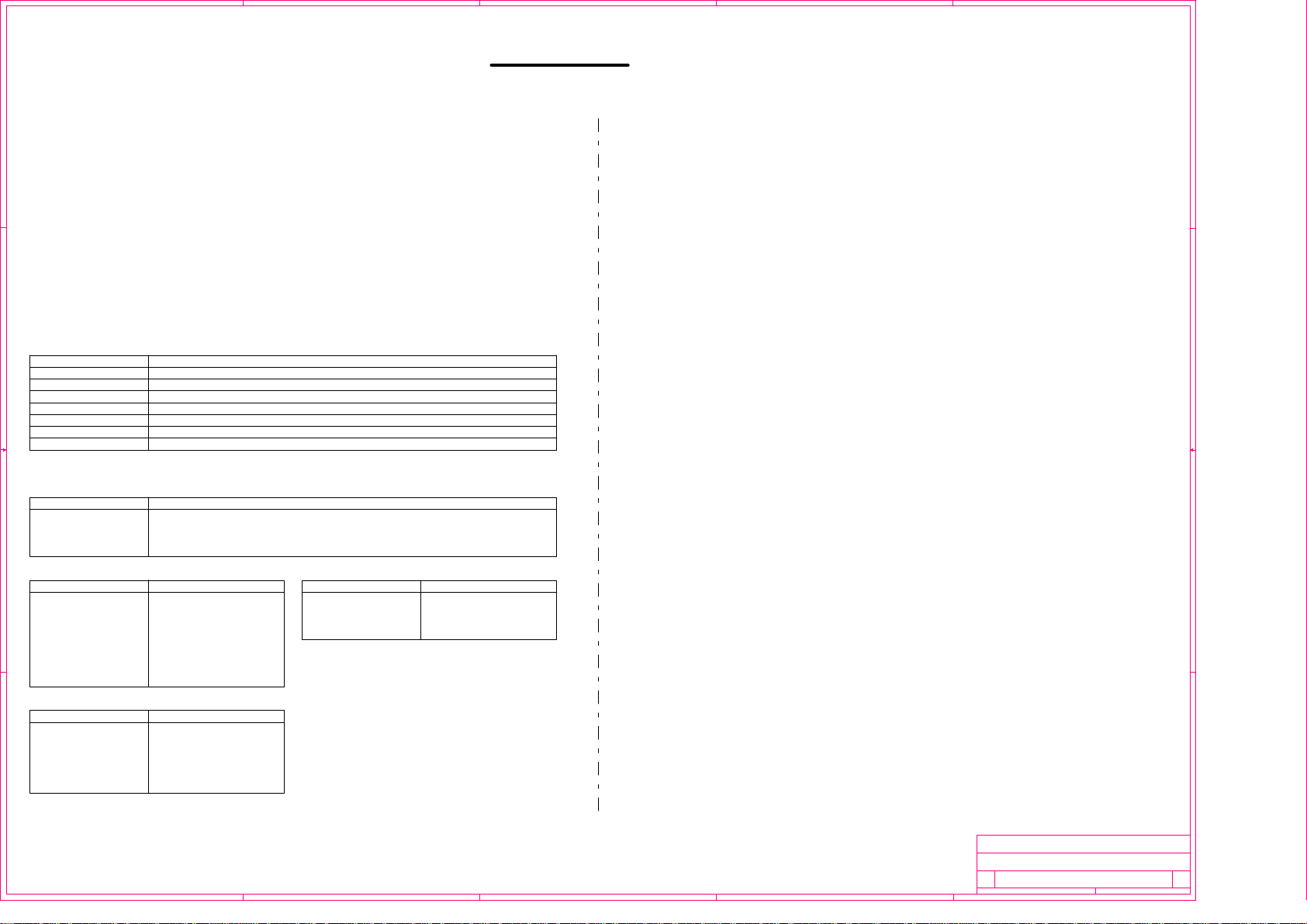

Vitek ES66x8 Schematic

5

4

3

2

1

ESCHER-H1 REV-A6 ES66x8 + HOP1200 PICKUP + OUTPUT

Layout---------ESCHER-H1 REV-A6B6

D D

Background

This DVD design is based on ESS Vibratto-II ES66x8 single chip DVD mpeg and servo processor. The ES66x8 is built upon

ESS proven Programmable Multimedia Processor architecture with integrated servo DSP. A complete DVD design using

ES6603 RF-Amp can support all major popular optical pickup heads. With ES66x8 unify memory architecture, the w hole

system memory is reduced to a minimum. ES66x8 provides the best price performance DVD solution in the industry .

andy_ho@esste ch.com.hk

System Clock Requirement

ES66x8 require a 27MHz clock to operate. This 27MHz can either be generated externally and feed into pin 3 and pin 4 or

thru a 27MHz crystal attached to pin 2 and 3. This 27Mhz will be used for all video processing reference. In addition, internal

multiplier will generate a much higher operating frequency f o r t h e i n t e rn a l R I S C + DS P c ode to operate. Audio clock is

generated from ES66x8 by its internal PL L c i r c ui t r y.

SDRAM Usage

ES66x8 support the use of higher density 4Mx16 SDRAM. A sinlge o f 4 Mx 16 S DR AM is s uf f ici en t f or th e whole sys te m t o

operate.

C C

System Configuration

CHIP

ES66x8

64MBit SDRAM

8Mbit EPROM/FLASH

24C01 SERIAL EE

WM8706

WM8746

WM8739

LCSx#

LCS0#

LCS1#

LCS2#

LCS3#

B B

AUXx

AUX0

AUX1

AUX2

AUX3

AUX4

AUX5

AUX6

AUX7

FUNCTION

Single chip processor that handles all system control, DVD decoding and servo control.

Data storage and frame buff e r

Program storage

System setup configuration s t o r a ge

2-Channel AudioDAC

6-Channel AudioDAC

2-Channel AudioADC

FUNCTION

SPARE

74HCT374 (U16) I/O EXPAND CONTROL

ROM EMULATOR

ROM/FLASH

FUNCTION

I2C DATA

I2C CLOCK

MICMUTE / HSYNC

SCARTCTL / VSYNC

IR

VFD DATA

VFD CS

VFD CLK

EAUXx

EAXU00 AUDIODAC MD

EAUX01

EAUX03

FUNCTION

AUDIODAC MC

AUDIODAC MLEAUX02

AUDIOADC CSB#

Revision History

Rev-A1

1. Base on HQ ES66x8 reference design and our previous ES60X8 reference design to f or m t he sc hem at ic .

Rev-A2

1. Change ES66x8 from 208 pins package to 216 pins package.

2. Base on HQ's new pin assignment, redefine all the pins of ES66x8.

Rev-A3

1. Rearrange AUX/EAUX pins usage (AUX2/3/5, EAUX23/4, EAUX30/1/2, E AUX43)

2. Swap SLED+/- and DCMO+/- at J12.

Rev-A4

1. Change back to 208-pin package again by reclaiming XGPIO[0..3] f r om t h e s e r v o s i d e.

Rev-A5

1.Add pull low resistor R73 on T S D 2.

2.Delete two ZERO circuit.

3.Change DD2 from OPEN to IN4148.

4.Change R92 from 1K to OP E N.

5.Add LA20 to FLASH and emulator.

6.Exchange PB and PR.

Rev-A6

1.Add LJP1,RL1.

2.Delete C39,C41,C49,C51,C61,C62.

3.Delete R32,R34,R35,R37.

4.Correct the flash package.

5.Change net EAUX00 to EAUX40,EAUX01 to EAUX41,EAUX02 to EAUX42 , E AU X 03 t o E A UX 43 .

6.Change scart interface from 11pin to 14pin,add two control signals a n d a po wer VCC.

7.Add pull_high resistor RN4 .

XGPIOx

XGPIO4

XGPIO5

XGPIO6

XGPIO7

XGPIO8

A A

XGPIO9

FUNCTION

MOCTL / RS232 DET

DRVSB

OUTSW

CLOSE

HOMESW

INSW

5

ESS TECHNOLOGY, INC.

Title

INDEX

Size Document Number Rev

Escher-H1

4

3

2

Date: Sheet of

1

15Saturday, May 14, 2005

A6

5

4

3

2

1

D D

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

U5

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

DSCK

R33 33

R120 33

DOE#

R121 33

CS0#

R156 33

R177

OPEN

R178

OPEN

RAS0#

CAS#

DWE#

DQM

R158 33

R159 33

R44 33

R163 33

R164 33

C C

VCC

R175

RAS1#

RAS2#

R180 0

R181

OPEN

R179 0

OPEN

VCC

R176

OPEN

GND

DSCK+

DOE#+

CS0#+

RAS0#+

CAS#+

DWE#+

RAS1#+

RAS2#+

DQM+

23

24

25

26

29

30

31

32

33

34

22

35

38

37

19

18

17

16

15

39

20

21

36

40

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

CLK

CKE

CS

RAS

CAS

WE

DQML

DQMH

BA0

BA1

NC

NC

4Mx16 SDRAM (7ns)

32/64MBIT SDRAM

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VCCQ

VCCQ

VCCQ

VCCQ

VSSQ

VSSQ

VSSQ

VSSQ

VCC33

DB0

2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

VCC

VCC

VCC

VSS

VSS

VSS

DB1

4

DB2

5

DB3

7

DB4

8

DB5

10

DB6

11

DB7

13

DB8

42

DB9

44

DB10

45

DB11

47

DB12

48

DB13

50

DB14

51

DB15

53

1

14

27

3

9

43

49

6

12

46

52

28

41

54

CS1#

MA[0..11]

DSCK+

R172 33 OPEN

R173 33 OPEN

MA[0..11]

DSCK+

GND

B B

MA9

MA10

RAS0#+

CAS#+

DWE#+

DQM+

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10 DB10

MA11

R174 33 OPEN

CS0#+

RAS0#+

CAS#+

DWE#+

DQM+

U7

VCC3 VCC3

21

A0

22

A1

23

A2

24

A3

27

A4

28

A5

29

A6

30

A7

31

A8

32

A9

20

A10

19

BA/A11

35

CLK

34

CKE

18

CS

17

RAS

16

CAS

15

WE

14

DQML

36

DQMH

33

NC

37

NC

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VCCQ

VCCQ

VCCQ

VCCQ

VSSQ

VSSQ

VSSQ

VSSQ

2

DQ0

3

DQ1

5

DQ2

6

DQ3

8

DQ4

9

DQ5

11

DQ6

12

DQ7

39

DQ8

40

DQ9

42

43

45

46

48

49

1

VCC

25

VCC

7

13

38

44

4

10

41

47

26

VSS

50

VSS

SDRAM 512KX16X2 (9ns)OPEN

U19

21

A0

22

A1

23

A2

24

A3

27

A4

28

A5

29

A6

30

A7

31

A8

32

A9

20

A10

19

BA/A11

35

CLK

34

CKE

18

CS

17

RAS

16

CAS

15

WE

14

DQML

36

DQMH

33

NC

37

NC

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VCCQ

VCCQ

VCCQ

VCCQ

VSSQ

VSSQ

VSSQ

VSSQ

VCC3VCC3

2

DQ0

3

DQ1

5

DQ2

6

DQ3

8

DQ4

9

DQ5

11

DQ6

12

DQ7

39

DQ8

40

DQ9

42

43

45

46

48

49

1

VCC

25

VCC

7

13

38

44

4

10

41

47

26

VSS

50

VSS

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11MA11

DB12

DB13

DB14

DB15

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB11

DB12

DB13

DB14

DB15

DB[0..15]

SDRAM 512KX16X2 (9ns)OPEN

A A

Title

<Title>

Size Document Number Rev

<Doc> <RevCode>

C

5

4

3

2

Date: Sheet

1

of

11Saturday, May 14, 2005

5

D D

4

3

2

1

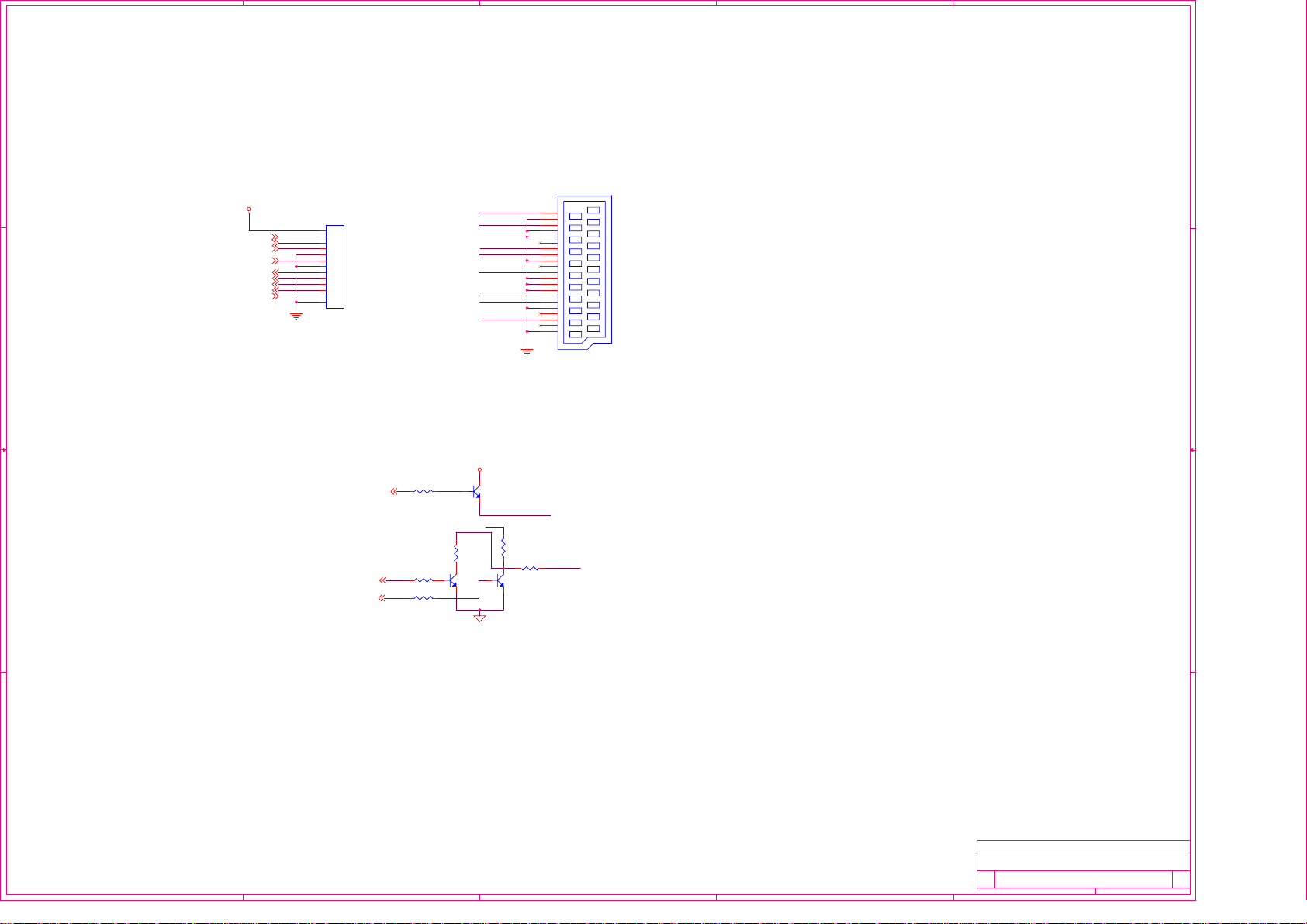

+12V

J3

GNDV

1

2

3

4

5

6

7

8

9

10

11

12

13

CON13

UDAC

YDAC

CDAC

VDAC

SCARTCTL0

SCARTCTL1

SCARTCTL2

VCC

FDAC

C C

SCRAT L

SCRAT R

UDAC

SCART_TV

YDAC

CDAC

RGB/CVBS#

VDAC

GNDV

1

L

2

GND

3

R

4

GND

5

GND

6

NC

7

UDAC

8

VCC

9

GND

10

10

11

YDAC

12

GND

13

GND

14

GND

15

CDAC

16

3.3V

17

GND

18

NC

19

VDAC

20

NC

21

GND

SCRAT

VCC

J10

SCARTCTL0

B B

SCARTCTL1

SCARTCTL2

R108 10K

R100 1K

R99 1K

R106

2.2K

Q5 3904

0V------CVBS

3V------RGB

RGB/VCBS#

+12V

Q7

3904

R107

2.2K

0V--TV

6V--AV 16:9

12V--AV 4:3

100

R104

SCART_TV

Q11

3904

GND

A A

Title

<Title>

Size Document Number Rev

<Doc> <RevCode>

C

5

4

3

2

Date: Sheet

1

of

11Saturday, May 14, 2005

Loading...

Loading...